The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

TECHNISCHE UNIVERSITÄT WIEN

VIENNA UNIVERSITY OF TECHNOLOGY

Dissertation

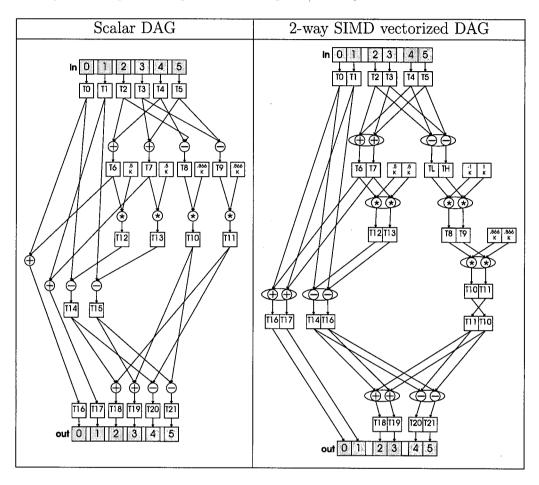

# FFT Specific Compilation on IBM Blue Gene

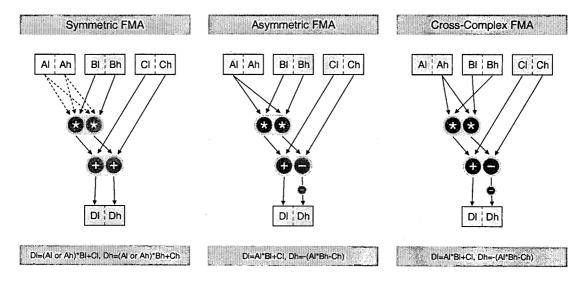

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

Ao. Univ.-Prof. Dipl.-Ing. Dr. techn. Christoph W. Überhuber E101 – Institut für Analysis und Scientific Computing

> eingereicht an der Technischen Universität Wien Fakultät für Informatik

> > von

Dipl.-Ing. Stefan Kral

Matrikelnummer 9625239 Anzengrubergasse 61/1/6 2380 Perchtoldsdorf

Perchtoldsdorf, am 22. Mai 2006

Sterlhel

#### Vorwort

Algorithmen zur digitalen Transformation von Signalen sind im Scientific Computing von größter Bedeutung und werden in zahlreichen Gebieten angewendet—von der Echtzeit-Signalverarbeitung in eingebetteten Systemen bis zur numerischen Lösung partieller Differentialgleichungen im Rahmen komplexer Simulationen auf Supercomputern.

Die Entwicklung und Publikation der schnellen Fourier-Transformation (FFT) durch Cooley und Tukey leitete die Entwicklung einer neuen Klasse schneller Signalverarbeitungsalgorithmen ein, die – im Gegensatz zur direkten Auswertung des entsprechenden Matrix-Vektor-Produktes – nicht eine Berechnungskomplexität von  $O(N^2)$ , sondern nur von  $O(N\log N)$  haben. Für eine bestimmte Transformation gibt es aber nicht nur einen eindeutig bestimmten schnellen Algorithmus, sondern eine ganze Vielzahl äquivalenter Algorithmen. Diese Algorithmen unterscheiden sich nur unwesentlich im Hinblick auf ihren Rechenaufwand, umso mehr aber in ihrem Speicherzugriffsverhalten, was auf modernen Computersystemen mit ihren mehrstufigen Speicherhierarchien zu enormen Laufzeitunterschieden führen kann.

Automatische Performance-Tuning-Systeme, wie zum Beispiel die den Stateof-the-art verkörpernden Signalverarbeitungs-Programmbibliotheken FFTW und

SPIRAL, führen auf einem gegebenen Computersystem eine Suche nach dem optimalen Algorithmus im Raum aller äquivalenten Algorithmen und Implementierungen durch. Da der Output von Performance-Tuning-Systemen aber in Form

von C-Code erfolgt, ist deren Leistung durch die Qualität der verfügbaren Compiler beschränkt.

Die vorliegende Arbeit stellt einen neu entwickelten Special-Purpose-Compiler vor, der für die Übersetzung laufzeitkritischer Codes existierende C Compiler ersetzt. Dieser Compiler, die Vienna MAP compiler tool-chain, besteht aus den folgenden Komponenten, die speziell den Bedürfnisse von Signalverarbeitungscodes angepasst sind: (i) Der MAP Vectorizer extrahiert 2-weg SIMD-Parallelismus in numerischen Straight-Line-Codes. (ii) Der MAP Optimizer führt lokale Codeverbesserungen durch, wie sie von versierten Assembler-Programmierern manuell ausgeführt werden. (iii) Zuletzt erzeugt das MAP Backend Assemblercode für die Zielarchitektur.

Die wichtigste Ziel-Architektur des MAP-Compilers ist der IBM PowerPC 440 FP2 Prozessor, der in IBM Blue-Gene-Systemen – den derzeit schnellsten Super-computern der Welt – eingesetzt wird. FFTW-Grundroutinen, die mit Hilfe der Blue-Gene-Version des MAP-Compilers übersetzt werden, erreichen eine Effizienz von bis zu 80% und damit die dreifache Leistung jener Objekt-Codes, die von der aktuellsten Version des optimierenden IBM XL C Compilers erzeugt werden.

#### Preface

Digital signal transforms are core algorithms in computational science and engineering, ranging from real-time signal processing in small-scale problems with stringent time constraints up to large-scale simulations based on partial differential equation solvers running on the world's largest supercomputers.

Starting with Cooley and Tukey's work on the fast Fourier transform (FFT), a vast class of fast signal transform algorithms has been developed, pushing the computational complexity down from  $O(N^2)$  to  $O(N \log N)$ . In practice, however, there is not just one unique algorithm, but a large number of fast algorithms for computing one specific transform. These diverse algorithms are equivalent, but may differ significantly with regard to their memory access behavior, which causes tremendous runtime differences on all common-place machines with deep memory hierarchies.

Automatic performance tuning systems—like the state-of-the-art signal transform libraries FFTW and SPIRAL—search the space of suitable algorithms and implementations, automatically generating a large number of promising codes. To obtain the best performing code on a given target hardware, the search process is guided by empirical runtime measurements. However, as the program generators used in automatic performance tuning systems produce high-level C code, the performance of these systems is clearly limited by the quality of available compilers.

The thesis at hand presents a newly developed special-purpose compiler—the Vienna MAP compiler tool chain—as a replacement for general purpose high-level compilers in the context of automatic performance tuning systems. The MAP tool chain is composed of several generic components, consecutively focusing on specific properties of signal transform codes. (i) The MAP vectorizer extracts 2-way SIMD-style parallelism out of numerical straight line code. (ii) The MAP optimizer performs local code improvements similar to the ones that experienced programmers would achieve by hand. (iii) Finally, the MAP backend produces assembly code for the specific target architecture.

The primary target architecture of the MAP compiler is IBM's PowerPC 440 FP2 processor used in all Blue Gene systems, currently being the fastest supercomputers worldwide. FFTW's core routines were compiled by the Blue Gene version of the MAP compiler. The resulting assembly code boasts an unprecedented performance—reaching a level of 80% efficiency. That way, MAP compiled codes are up to three times as fast as object codes obtained with the latest version of IBM's optimizing XL C compiler.

#### Acknowledgements

I want to thank everybody who supported me in writing this thesis.

First, and most importantly, I want to thank my family—my mother Anna, my father Alfred, and my sister Maria. You probably don't know how much strength I get out of our family ties.

Next, I want to thank my advisor, Christoph Ueberhuber, for his encouragement, his patience, and for the enormous amount of feedback and support.

Also, I want to thank all members of Aurora group 5, in particular Franz Franchetti for motivating me to work on Blue Gene and for his ideas regarding code optimization on Blue Gene, Juergen Lorenz for his experiments and hints on compilers, Andreas Bonelli for his patience in explaining tensor products to me, and the late Herbert Karner for guiding my first steps in the field of applied mathematics.

I want to thank the authors of FfTW, Matteo Frigo and Steven Johnson, for their cooperation and their encouragement.

Also, I want to thank the following people at IBM—for their advice, organisational skills, and for helping me carry out experiments on pre-release Blue Gene hardware: Gheoghe Almasi, Jose Brunheroto, John Gunnels, Manish Gupta, Jose Moreira, and Ramendra Sahoo.

Finally, I want to thank the US Department of Energy at Lawrence Livermore National Laboratory (LLNL) and the Austrian Science Fund (FWF, SFB AURORA) for their financial support.

STEFAN KRAL

### Contents

| 1 | Introduction                                |     |

|---|---------------------------------------------|-----|

|   | 1.1 Parts of a Computer System              | 2   |

|   | 1.2 Maximizing Peak Performance             | 5   |

|   | 1.3 Maximizing Efficiency                   |     |

|   | 1.4 Optimizing Signal Transform Performance |     |

|   | 1.5 The Vienna MAP Compiler Tool Chain      | 14  |

| 2 | Fast Algorithms for Linear Transforms       |     |

|   | 2.1 Discrete Linear Transforms              | 17  |

|   | 2.2 The Fast Fourier Transform              | 23  |

| 3 | Software and Hardware Architecture          |     |

|   | 3.1 Automatic Performance Tuning Software   |     |

|   | 3.2 Short Vector SIMD Extensions            |     |

|   | 3.3 2-Way SIMD Basics                       |     |

|   | 3.4 The Blue Gene Processor                 | 39  |

| 4 | The MAP 2-way SIMD Vectorizer               |     |

|   | 4.1 Basic Properties                        |     |

|   | 4.2 Implementation Basics                   |     |

|   | 4.3 Implementation Details                  | 52  |

| 5 | <b>-</b>                                    |     |

|   | 5.1 Scalar Rules                            |     |

|   | 5.2 Generic SIMD Rules                      |     |

|   | 5.3 Target Architecture Specific SIMD Rules |     |

|   | 5.4 Substitution Rules                      | 63  |

| 6 |                                             |     |

|   | 6.1 Resource Allocation                     |     |

|   | 6.2 Scheduling                              | 76  |

| 7 |                                             |     |

|   | 7.1 Input Code Representation               |     |

|   | 7.2 Intermediate Code Representation        |     |

|   | 7.3 FFT Example Codes                       | 87  |

| 0 | Dogulta                                     | 199 |

| ${\bf A}$        | MAP     | Backend Source Codes            |      |  |  |  |  |  |  |     |   |  |  | 126 |

|------------------|---------|---------------------------------|------|--|--|--|--|--|--|-----|---|--|--|-----|

|                  | A.1     | Generic Auxiliary Modules       |      |  |  |  |  |  |  |     |   |  |  | 126 |

|                  | A.2     | Input and Output of Prolog Term | ns . |  |  |  |  |  |  |     |   |  |  | 136 |

|                  | A.3     | Instruction Definitions         |      |  |  |  |  |  |  |     |   |  |  | 145 |

|                  | A.4     | List-based Scheduling           |      |  |  |  |  |  |  |     |   |  |  | 146 |

|                  | A.5     | Register Allocation             |      |  |  |  |  |  |  |     |   |  |  | 153 |

| Bi               | bliogra | aphy                            |      |  |  |  |  |  |  |     | • |  |  | 159 |

| Curriculum Vitae |         |                                 |      |  |  |  |  |  |  | 167 |   |  |  |     |

:

i :

#### Chapter 1

#### Introduction

Digital signal transforms are core algorithms in computational science and engineering, ranging from real-time signal processing in small-scale problems with stringent time constraints up to large-scale simulations based on partial differential equation solvers running on the world's largest supercomputers.

This wide range of applications—each having its particular requirements with regard to type of transformation (linear vs. non-linear), data types (fixed-point vs. floating-point arithmetic), data formats (real, interleaved complex, split complex), one or multi-dimensional data—is covered by a large class of digital signal transform algorithms, packaged into libraries providing application programmers with well-tested, well-documented tools fitting a vast area of problems.

In the field of compute-intensive scientific numerical software, speed is a highly relevant demand on digital signal transform codes. Minimizing the runtime required for transforming data allows dealing with ever more complex problems and ever larger data sets. Thus, time is a major driving force in the development of software for computational science and engineering applications.

By transforming the power equation of physics, i.e., power = work/time, it follows that

$$Time = \frac{Work}{Peak-Performance \times Efficiency}.$$

(1.1)

This equation shows that there are basically three ways for minimizing the runtime required for solving a particular problem. Firstly, the work that needs to be done could be reduced, i. e., the algorithms' complexity could be minimized. Secondly, the peak performance of the computer system might be increased. Finally, the efficiency is to be maximized, i. e., the percentage of the peak performance actually achieved by the algorithm implemented on a given computer system has to be made as large as possible.

The three factors of runtime equation (1.1) are certainly not independent of each other. For example, new hardware features that help to increase the peak performance of a computer system may decrease the efficiency of certain programs and may often require new types of algorithms to achieve a proportional runtime reduction.

#### 1.1 Parts of a Computer System

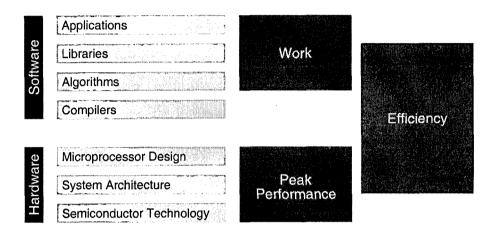

In the context of minimizing the time required for transforming digital signal data, the components of a general purpose computer system take different roles. Fig. 1.1 shows a hierarchy of the relevant parts of a computer system—comprising hardware and software—and symbolizes their impact on actual performance.

Figure 1.1: Hardware and Software Components of a Computer System. Any component of a computer system (depicted on the left) has an individual influence on the three factors of equation (1.1), i.e., work, efficiency, and peak performance. The peak performance of a system is determined by the hardware alone, work (complexity) is solely a software issue, while efficiency depends on both hardware and software.

#### 1.1.1 Hardware Components

Hardware development—among other goals—aims at (i) pushing the aggregated peak performance of a computer system and at (ii) promoting high efficiency, i. e., making available a satisfactory percentage of the theoretical peak performance to many applications.

Semiconductor Technology provides the engineering processes required for producing highly integrated microprocessors as well as memory and logic chips.

In 1965 Intel co-founder Gordon E. Moore predicted that it would be technically feasible to regularly double the number of circuit elements integrated into a single chip, provided the market demand grew constantly to finance the required research and development.

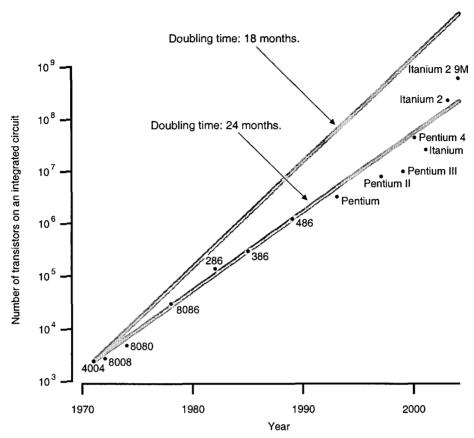

Moore's prediction—commonly referred to as "Moore's Law" (see Fig. 1.2)—has held true for the past 40 years. It turned out to be an important factor in achieving the unbroken exponential growth of performance, as miniaturization progress allows increasing clock frequencies and to integrate more and more complex features.

Figure 1.2: Moore's Law. The illustration shows the number of feature elements integrated into a selection of Intel microprocessors, ranging from the 4 bit 740 kHz "4004" to the 64 bit 1.6 GHz "Itanium 2 9M". The discussion of hardware development will focus on the widely used IA-32 (x86) processor family (8086, 286, 386, 486, and Pentium).

The semiconductor industry expects Moore's law to remain valid for the next 10 to 15 years, as reflected in the *international technology roadmap for semiconductors* (ITRS) [44].

System Architecture defines the large-scale structure and configuration of a computer system. A single system usually comprises several microprocessors, variable amounts of shared or distributed memory organized in a memory hierarchy, as well as peripherals like permanent storage devices, networking infrastructure, and audio/video hardware—typically linked by a high-speed interconnect optimized for high throughput and low access time.

Microprocessor Design produces processor models that can be mapped onto silicon utilizing the available process technology, defining both details directly visible to an assembly programmer—like the *instruction set architecture* (ISA) and the *application binary interface* (ABI)—as well as micro-architectural details about *how* instruction sequences are processed internally.

System architecture and microprocessor design turn the exponential growth of the number of circuits on a chip—made possible by advances in semiconductor technology—into a tantamount performance growth of cost-efficient computer systems, suitable for scientific, commercial, and particularly for personal computing, and, to an increasing extent, for the consumer electronics mass-markets, represented, for instance, by video game consoles.

While microprocessor design directly focuses on maximizing the performance of individual processing components, system architecture tries to aggregate the respective components in a way that leads to an optimal overall performance.

#### 1.1.2 Software Components

Software development, as opposed to hardware development, aims at (i) minimizing the workload and at (ii) maximizing efficiency.

Algorithms are responsible for carrying out the workload of applications. For many problems in science and engineering, there are large sets of algorithms available to choose from for solving well-defined parts of a given problem or for combining solutions of subproblems. Individual algorithms may differ in many respects, including memory footprint, arithmetic complexity, best-case vs. worst-case number of operations, memory access patterns, size, steadfastness, generality, maintainability, and, quite likely, many more.

On a high-level, any particular algorithm requires a specific amount of work to solve a given problem, which is quite often characterized by abstract measures like asymptotic complexity classes.

On the actual implementation level, algorithms expressed by means of a programming language often have a profound impact on the efficiency of the code output by the compiler.

Libraries comprise a collection of algorithms in form of computer code, needed for solving a class of problems in some specific domain, conveniently offered through a documented library-application interface. Low-level libraries shield applications from specific target processor details. For instance, PAPI [66] provides an abstract interface to performance counters for enabling accurate runtime measurements.

**Applications** in computational science and engineering often utilize optimized libraries to solve specific subproblems efficiently.

Compilers transform a wide range of codes written in some high-level language into assembly code, aiming at good utilization of the target hardware and its specific features.

Optimizing compilers for general purpose microprocessors usually focus on maximizing speed or on minimizing code size. Special purpose compilers like optimizing compilers for digital signal processors (DSPs) may additionally focus on special issues like minimizing energy consumption [58].

For at least two reasons, compilers have significantly pushed back assembly hand coding efforts in almost any domain. Firstly, high-level languages allow programmers to focus on the software and to ignore hardware-specific features, which improves portability and maintainability of the codes and raises human productivity. Secondly, programmers gradually gained well-earned trust in the ability of the compilers to produce high-quality assembly code—one of the main reasons for the success of one of the earliest wide-spread high-level programming languages, Fortran [6].

**System Software.** The operating system has been deliberately left out of the following considerations, because its influence on the focus of this thesis—single-threaded codes working on data present in memory—is of minor importance.

#### 1.2 Maximizing Peak Performance

Apart from raising the clock frequency, several techniques have proven successful for increasing the peak performance of a single chip and have found their way into the mainstream of general purpose computing during the past years. All these techniques directly aim at increasing parallelism, for instance, by raising the number of functional units available.

**Dedicated Hardware Support** for basic scalar data types is a necessary prerequisite for achieving competitive performance. For instance, starting with the Intel 486, the IA-32 family includes dedicated on-chip hardware for the support of floating-point arithmetic, which is more than ten times faster than emulating floating-point operations in software.

The amount of hardware features supplying basic floating-point operations differs considerably between various processor families, a fact reflected in the size of the instruction set. For instance, PowerPC processors offer a fused multiply-add (FMA) instruction, i.e., a floating-point instruction that combines a multiplication with a dependent addition, thus providing a means for effectively doubling the theoretical peak performance.

Instruction Pipelining can improve the instruction throughput by subdividing instructions into different stages, overlapping the execution of different instructions at different stages.

Because of the cost of mispredicted branches and because of dependencies between instructions, pipeline lengths cannot be arbitrarily increased without degrading the performance of the majority of codes. Such efficiency related issues are the reason why various hardware techniques like branch optimization and out-of-order execution, presented in the next section, have found their way into modern processor design.

Pipelining was a novel feature of the RISC design of the SPARC and the MIPS processor families [67], introduced in 1985. These processors have been highly successful on the workstation market, and set the stage for all modern processors featuring a RISC-style core. Eventually, this technology entered the desktop sector, with the Intel 486 in 1989.

Over the past twenty years, the number of instruction pipeline stages in general purpose processors has risen more than previously considered [67]. While the classic RISC pipeline had only five stages—instruction fetch, instruction decode, execute, memory access, and writeback—pipelines in contemporary processors have around 15 stages, the Intel Pentium 4 being a noticable exception with more than 30 pipeline stages. With their new architecture introduced in 2006, Intel made a considerable step back and reduced the pipeline length to 14.

Instruction Level Parallelism. Executing multiple instructions in parallel can be accomplished by either super-scalar execution or by explicitly parallel instruction computing (EPIC).

With super-scalar execution, the processor hardware is responsible for extracting parallelism out of a sequence of instructions. With EPIC, this responsibility is transferred to the compiler, thus allowing for a simpler design of the hardware.

All current mass-market processors are based on super-scalar execution, usually allowing to execute up to a handful instructions of different types (memory, integer, and floating-point) in parallel.

SIMD Style Parallelism. Starting with the mid-1990s, many processors included *single-instruction multiple-data* (SIMD) style instruction set extensions for efficiently dealing with relatively short vectors of fixed-lengths, which consist of scalar integer, floating-point, or pixel data.

Hardware support for SIMD style parallelism is still gaining momentum, with the latest example being Intel's Core Duo processor, introduced in 2006. Core Duo significantly improves upon previous designs with regard to the throughput of SIMD instructions.

Multi-core Computing. Since the end of the 1990s, the continual combined increase of clock frequencies and pipeline depths has slowed down significantly. To further increase the peak performance, chip manufacturers started integrating multiple independent processor cores onto a single chip.

The first multi-core processors had two cores and targeted servers and workstations: IBM Power 4 (2000), HP PA-8800 (2003), Sun UltraSPARC IV (2004), AMD Opteron (2005), and Intel Xeon DP (2005).

In 2005, AMD and Intel introduced two new dual-core processors for desktop computers: the Athlon 64 X2 and the Intel Pentium 4D.

Multi-core technology entered the video game console market in late 2005, when Microsoft's Xbox 360—featuring the triple-core PowerPC-based IBM Xenon processor—became available.

As of mid-2006, another two important milestones were reached. First, Intel introduced Core Duo, the first dual-core processor for notebook computers. Then, Sun released the eight-core UltraSPARC T1 processor, which specifically targets multi-threaded web-servers, offering both multiple cores and chip-level multi-threading with up to four logical threads per core.

Ongoing and Future Development. Future processor development of general purpose processors will most likely see only marginal increases in pipeline depths and in the amount of super-scalar execution supported.

SIMD support is very likely to be improved (i) by adding useful new instructions that are currently still missing in most SIMD instruction set extensions and (ii) by adding more functional units available for use by SIMD instructions.

The number of cores integrated into one chip will steadily rise. The IBM cell processor, which comprises one main PowerPC core and eight synergistic processor units (SPU), will become available in late 2006 with the release of Sony's Playstation 3 game console. General purpose quadruple-core processors for both servers and desktop computers are anticipated for 2007. Also for 2007, Sun plans to release the UltraSPARC T2 that executes up to eight logical threads per core.

#### 1.3 Maximizing Efficiency

In the past thirty years, development in process technology, general purpose computer hardware, and computer software has been influenced more and more by the demands of the mass market, particularly by personal computers.

Multi-level Memory Hierarchies. The need for cost-effective, highly-integrated random access memory (RAM) with moderate power consumption, put dynamic RAM (DRAM) ahead of static RAM (SRAM). As DRAM is significantly slower than SRAM, with the performance gap widening year by year, multiple levels of caches, varying in speed and size, were added as a buffer between the processor(s) and main memory.

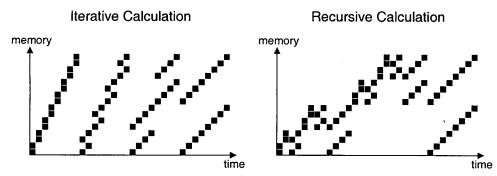

While caches are usually fully transparent to the programmer, they may become a severe performance obstacle if an application does not exhibit high temporal and spatial locality of reference (see Fig. 1.3).

Modern processor hardware automatically prefetches data that are likely to be needed in the near future, and additionally supports software-directed prefetching. Both prefetching methods may contribute to increased performance, but may also deteriorate performance, if the data being prefetched are not used in time.

To reduce latencies, caches are often integrated into the processor leading to a mixed Harvard/von-Neumann architecture with unified level 2 and level 3 caches, a unified address space, but with the level 1 caches being split for instructions and data.

Processor Micro-Architecture Improvements aim at a high execution efficiency of processor cores.

Branch optimization—static or dynamic branch prediction and speculative execution—aims at minimizing branch related pipeline stalls.

Out-of-order execution enables the processor core to execute instructions in an order that is different from the one present in the machine code, i. e., instructions may be delayed until all required operands are available. Out-of-order execution has proven useful for increasing efficiency in the presence of long instruction pipelines and high memory latencies.

Chip-Level Multithreading. Based on the assumption that most threads are not utilizing all available multiple execution units at the same time, simultaneous multithreading allows the issuing of multiple instructions from multiple threads in one cycle, with multiple "logical" threads of execution competing for the very same computational resources.

While this technique may also be used for error detection and recovery, the main focus lies on increasing the throughput of a system running multiple threads.

Progress in Compiler Development. To produce high quality output for a wide range of input codes, modern compilers include sophisticated optimization mechanisms, addressing scalar, vector and parallel codes. Some optimizing compilers allow their decisions to be guided by data gained from dynamic profiling. The level of efficiency reached by a compiler depends on how well an input code in high-level language can be mapped to assembly code that exploits hardware specific features to a satisfactory degree.

#### 1.4 Optimizing Signal Transform Performance

State-of-the-art signal transform software to be run on general purpose computers achieves high performance by explicitly addressing two issues that are not handled by existing general purpose compilers. Firstly, they aim at a minimization of the work required for any particular transform. And secondly, they focus on optimizing the order of memory access operations.

#### 1.4.1 Minimizing Work

An important and often very successful way of minimizing the time required to solve a particular problem is to minimize the algorithm's complexity, i.e., to reduce the algorithmic workload that needs to be done. In some areas, like solving special linear systems, complexity reduction of algorithms was as successful as progress in hardware development reflected by Moore's law.

Fast Signal Transforms. In the case of linear digital signal transforms, the development of a revolutionary new class of algorithms with reduced arithmetic

complexity has been initiated by the (re-)discovery of the fast Fourier transform (FFT) by Cooley and Tukey in 1965. The FFT is based on a factorization of the discrete Fourier transform (DFT) matrix into a product of sparse matrices, done in a recursive fashion.

Similar decompositions were derived for many other linear signal transforms, like the Walsh-Hadamard transform (WHT), various discrete cosine transforms (DCT), or certain wavelet transforms—and all are based on the same principles as Cooley and Tukey's approach.

Because of its great influence on "the development and practice of science and engineering", the FFT has been named one of the "Top Ten Algorithms of the 20th Century", the result of an international voting compiled by Dongarra and Sullivan [18].

Reduced Arithmetic Complexity. The divide-and-conquer style decomposition of the transform matrix pushes the problem complexity of the respective transform from  $O(N^2)$ , i.e., the complexity of general matrix-vector products, down to  $O(N \log N)$ . This kind of complexity reduction is particularly valuable because its speed-up effect gets bigger and bigger with increasing problem size.

For example, on general purpose sequential computers, well-written FFT codes always outperform straight-forward DFT codes implementing a full matrix-vector product, even for the smallest problem sizes. This performance advantage of the FFT over the DFT even increases as the problem size gets larger.

#### 1.4.2 Efficiency Issues

The advent of deep memory hierarchies made clear that "making the common case fast in an economical way" may work well for many codes, but had a severe impact on the efficiency of digital signal transform codes.

Locality of Reference. While the formulation of many fast algorithms in Cooley-Tukey style naturally leads to a recursive implementation, considerable effort has been put into the design of FFT codes in iterative style, assuming that iterative constructs like loops have significantly lower overhead than recursive subroutine calls. Loop nested signal transformation algorithms, however, do not exhibit high locality of reference, which inevitably leads to a performance deterioration, in particular if the access speed of main memory is low.

To compare the locality of reference of iterative vs. recursive algorithms, Fig. 1.3 illustrates two in-place 16-point radix-2 Cooley-Tukey style algorithms calculating the Walsh-Hadamard transform (WHT). The illustration on the left shows the behavior of an iterative algorithm, the one on the right the behavior of an equivalent recursive version.

The different memory access patterns illustrated by Fig. 1.3 are responsible for several problems. Firstly, the iterative access pattern is more prone to cache capacity misses, as the algorithm's storage access operations linearly progress

Figure 1.3: Comparison of Memory Access Patterns of Two WHT<sub>16</sub> Implementations. In both address-space/time diagrams, a consecutive part of memory holding the signal data being transformed is presented on the y-axis, while the x-axis marks advances in time. A dot at position (i,j) tells that the algorithm accesses the i<sup>th</sup> element of some data vector at the j<sup>th</sup> time-step of the calculation.

over the entire data several times, while the recursive algorithm splits the original transform into two, solves them separately and combines the respective results. Secondly, common-place systems with  $2^k$ -way set associative caches, may have a lot more cache conflict misses running an iterative algorithm than by running an equivalent recursive version, especially if the vector size is a power of two, like in the chosen example.

Problems Arising from Cache Associativity. As Cooley-Tukey style algorithms have a lower arithmetic operation count for power-of-two than for non-power-of-two vector lengths, a bizarre situation occurs on systems with  $2^k$ -way set associative caches: Algorithms with the lowest operation count are the ones that are hit the hardest by cache conflict misses due to the order of memory access operations.

Choice of an Efficient Algorithm. Iterative signal transform algorithms have low control-flow related overhead. Recursive algorithms have better locality of reference. To get the best of both worlds, iterative and recursive algorithms may be combined.

For a given transform type, there is, in general, an exponentially growing number of different iterative/recursive Cooley-Tukey style algorithms. All these different algorithm versions perform a comparable number of arithmetic operations—often within a very narrow range of a few percent—and still, their performance varies significantly, mostly because of different orders of memory accesses.

#### 1.4.3 Automatic Performance Tuning

The step from programming one fixed algorithm for solving a given problem towards searching the space of possible algorithmic implementations marks the appearance of a new paradigm in high-performance computing, automatic performance tuning.

Based upon empiric runtime measurement instead of explicit performance modeling, automatic performance tuning allows creating portable software that covers *all* performance critical aspects of a target machine, including those that cannot be modeled easily, like memory access behavior. Taking runtime as the objective function of the planning process does not only focus on hardware related issues, but also on the software side, i. e., algorithms and compilers.

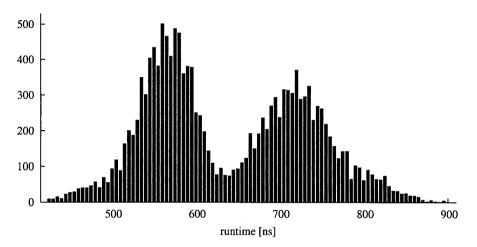

Figure 1.4: Runtime Comparison of 15,778 Implementations of a DCT<sub>16</sub><sup>IV</sup>. This diagram from [71] shows a histogram of runtimes for 15,778 straight-line codes computing the type IV discrete cosine transform for vectors of length 16, DCT<sub>16</sub><sup>IV</sup>. All codes were automatically generated by SPIRAL, compiled using GCC 2.95, and measured on an Intel Pentium 4 with 1.8 GHz. While the number of arithmetic operations performed by these codes differs only by a few percent—the number of additions ranges from 96 to 104 and the number of multiplications from 48 to 56—their runtime spans from 430 to 900 nanoseconds, more than a factor of 2. Only 1.5% of the codes are within a 10% range of the fastest code found.

One of the motivations for automatic performance tuning is to overcome the limitations of existing general purpose compilers. Fig. 1.4 shows that general purpose compilers may exhibit paradox behavior when applied to comparatively long sequences of straight line code. To obtain satisfactory performance, the following options are available, each having its own advantages and shortcomings.

- (i) Spiral puts the compiler into the optimization loop, which guards against compiler idiosyncrasies, as a large number of codes are actually generated and evaluated. However, the size of this optimization loop significantly contributes to long adaptation times.

- (ii) FfTW has a somewhat smaller optimization loop, which speeds up the automatic adaptation process, but also necessitates an adaptation of the domain-specific code generator to the peculiarities of the compilers used [28].

- (iii) The work presented in this thesis aims at overcoming all the compilerrelated problems by replacing the general purpose compiler by a domain-specific compiler, the MAP tool chain. By focusing on straight line code, the design and implementation of the MAP compiler is kept as simple as possible. Although this

approach is considerably less portable than the other ones, it is a successful way to higher performance.

Automatic performance tuning has been introduced as an algorithmic method for achieving high efficiency of code operating on large data sets, relieving compilers of the responsibility to optimize the order of data access operations acting on deep memory hierarchies. This paradigm has been particularly successful for libraries in the field of digital signal transforms [69, 30] and in linear algebra [16].

#### FFTW - The Fastest Fourier Transform in the West

In 1997, Matteo Frigo and Steven G. Johnson presented FfTW [29, 30], the "Fastest Fourier Transform in the West", a portable, high-performance library for computing complex and real discrete Fourier transforms in one or many dimensions. In the meantime, FfTW has become the de-facto standard in FfT software.

Planning. Unlike other FFT libraries, FFTW does not rely on one fixed algorithm to perform a requested transform, but uses a separate stage of planning to determine how to efficiently solve a specific problem on some given target machine using a fixed set of DFT kernel routines called codelets. As planning is guided by empirical measurement, it is quite likely that—for non-trivial problem sizes—FFTW actually executes two different algorithms when run on two sufficiently different machines. The knowledge gained in the planning stage, called "wisdom", may be stored for later reuse. When performing a transformation, FFTW traverses plans, calling the specified kernel routines as requested.

Automatic FFT Code Generation. FFTW's kernel routines are generated automatically by a special purpose FFT code generator called genfft. Apart from many others, genfft is a remarkable piece of software because of two reasons. Firstly, it was able to automatically derive new algorithms previously unknown in the signal processing community. And secondly, genfft demonstrated how high-level code can profit both from domain specific optimization techniques like FFT-graph based high-level scheduling and compiler specific tricks like providing tight life-spans for temporary variables to the C compiler.

Acceptance and Recognition. FFTW is the well-established de-facto standard for computing the DFT, ranging from desktop computers—where it has been integrated into the MATLAB system—up to the largest supercomputers like IBM's Blue Gene systems. It offers portable high performance on a wide range of machines, often beating other available free and commercial libraries, especially in cases that require the processing of large amounts of data. In recognition of their efforts, the authors of FFTW were awarded the prestigious James H. Wilkinson Prize for Numerical Software in 1999. Current development of FFTW is presented in [30].

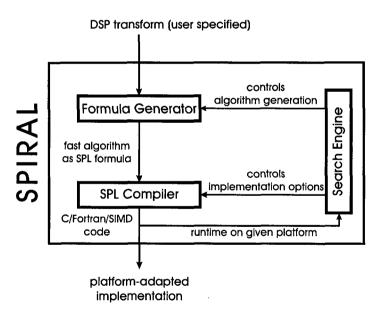

## SPIRAL – Signal Processing Algorithms Implementation Research for Adaptive Libraries

SPIRAL [61] is a generator system for DSP transform software and hardware, primarily developed by a group of researchers at Carnegie-Mellon University. SPIRAL operates on its own special-purpose high-level language—the *signal processing language* (SPL)—that allows describing linear signal transformations concisely in a special mathematical notation and to explicitly express relevant semantic information.

Similar to Fftw, Spiral performs a search for the best-suited implementation of a given transform. Unlike Fftw, Spiral is not packaged as a stand-alone library including a number of widely used codes, but rather as a library generator. The current status and ongoing development in Spiral is presented in [69].

#### 1.4.4 Utilizing SIMD Extensions

High-level compilers have long shielded the application programmer from the complexity of many internal features of orthogonal processor architectures.

This situation changed considerably when special purpose SIMD instruction set extensions were added to general purpose processors to push the performance of multimedia applications.

Compiler Support for SIMD Instructions may be provided by general purpose compilers in two different ways.

Firstly, a compiler may completely hide the complexity of these features, by offering automatic SIMD vectorization of loops or basic blocks, possibly aided by user-supplied directives ("pragmas").

Secondly, the compiler may take the easy way out and expose the complexity of the extensions, supplying special vector types and ISA specific intrinsic functions operating on values of these types. This does not only push the responsibility for the utilization from the compiler to its users, but also results in non-portable code because of the inherent differences of existing SIMD instruction set extensions.

Compiler Inadequacies. Several experiments have shown disappointing results of general purpose compilers when handling digital signal transform codes (see Fig. 1.4). This has the following reasons.

Firstly, most codes to be compiled in the context of performance tuning systems are automatically generated by a program generator and can be very large, pushing some compilers to their limit.

Secondly, the code may not profit from loop-level vectorization, which tries to identify multiple independent iterations of a loop that can be executed simulatenously using vector instructions, simply because it does have any.

Thirdly, there may be more than one way to map a scalar code to short vector SIMD hardware. Unless a vectorizer performs a tremendous amount of search, it is very likely to produce SIMD code with poor performance.

Finally, linear transform code has a rich internal structure that cannot be seen directly in the code. Knowledge about this particular structure can be utilized to guide the vectorization process, and thus allows producing satisfactory output in reasonable time.

High-Level Vectorization. Due to the limitations of existing compilers, existing successful approaches for automatically creating high-performance SIMD enabled digital signal transform code address vectorization on the algorithmic (or the library) level, performing algebraic manipulations of high-level domain specific language constructs, utilizing rich semantic information. The resulting code is then transformed to non-portable high-level code with intrinsics.

#### 1.5 The Vienna MAP Compiler Tool Chain

SIMD extensions led to a revival of hand coding and hand tuning of non-portable code, especially in a number of performance critical applications.

This thesis presents special compilation techniques for creating single-threaded high-performance digital signal transforms codes, closing the performance gap between code generated by general purpose compilers and assembly code written by skilled hand-coders.

The Vienna MAP compiler has been developed to focus on compute intensive straight line codes as generated automatically by special purpose program generators like FFTW's genfft.

Structure of the Compiler. The Vienna MAP compiler comprises a set of relatively generic components, arranged in the form of a flexible tool chain, that allows for easy experimentation with different arrangements of compilation phases, including feedback driven optimization loops.

Unlike other program generators, MAP does not produce C code, but covers the entire range of compilation, from domain-specific high-level code to target specific assembly code.

Human-readable Representations. All input, output, and intermediate program representations are fully human-readable. The compiler does not only allow introspection at any given point, but also the injection of code into the compiler.

The injection of code helps with the development and maintenance of the compiler and aids the understanding of details of the compilation process, which can get quite complex, due to interactions between tool chain components.

The intermediate representation supports the annotation of instructions to preserve high-level information (e.g., about variable aliasing, variable types, etc.) throughout the compilation.

**Optimizations** performed by the MAP compiler include newly developed techniques for utilizing advanced hardware features like 2-way SIMD-style functional

# Gflop/s Complex 1D FFT on an IBM PowerPC 440 FP2 | map-vect | map-vect | vlc\_mapvect | vlc\_scalar | vlc\_scalar | vlc\_vect | vlc

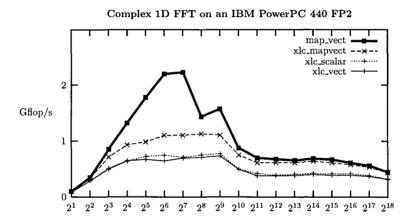

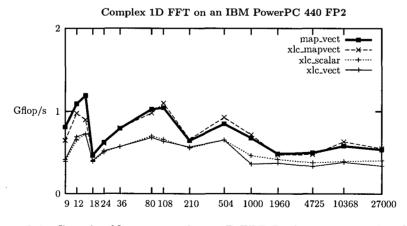

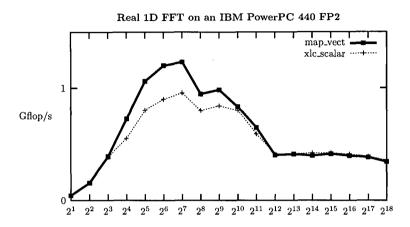

# Figure 1.5: Performance Comparison for Power-of-two 1D FFTs. This plot shows the performance of FFT routines compiled by the following compilers and settings. $xlc\_scalar$ uses the IBM XL C compiler without automatic vectorization. $xlc\_vect$ uses IBM XL C with automatic vectorization. $xlc\_mapvect$ uses the MAP vectorizer and optimizer, producing C code with SIMD intrinsics compiled by IBM XL C. $map\_vect$ uses the MAP vectorizer, optimizer, and backend.

units and FMA operations, as well as established compiler backend techniques, like optimal register allocation and list-based instruction scheduling for super-scalar architectures.

Maintainability and Portability. Many components of the MAP tool chain (e.g., vectorizer, register allocator, and instruction scheduler) can easily be adapted to any current target architecture by using parameter files that describe relevant parts of the target architecture.

Implementation on IBM's Blue Gene Systems. The newly developed techniques have been integrated into a special version of the MAP tool chain aiming at the Blue Gene systems' IBM PowerPC 440 FP2 processors.

To assess the performance gain obtained with the presented techniques, code produced by the MAP compiler was integrated into the automatic performance tuning library FFTW to create a state-of-the-art high-performance PowerPC specific version of FFTW targeting at IBM's Blue Gene supercomputer series, i.e., FFTW-GEL for Blue Gene.

Fig. 1.5 compares the performance of FFT routines on a single processor of an IBM Blue Gene system, clearly demonstrating that all parts of the MAP compiler significantly improve the floating-point performance. In the best case, MAP reaches as much as 80% of the optimum performance, thus beating the latest version of IBM's optimizing XL C compiler by up to a factor of three.

FFTW-GEL for Blue Gene has been used in a number of applications, including the runner-up of the 2005 Gordon Bell Award, the large-scale molecular dynamics simulation code QBOX [39], which achieved a sustained floating-point performance of 60 Tflop/s. Recent developments of application codes utilizing FfTW-GEL reach an even more outstanding performance level.

#### **Synopsis**

This thesis consists of three main parts: (i) Foundations, (ii) the Vienna MAP compiler, and (iii) experimental results.

#### **Foundations**

Chapter 2 provides the mathematical foundations of discrete linear transforms and in particular of the fast Fourier transform.

Chapter 3 presents the software architecture of automatic performance tuning software and the SIMD instruction set extensions available on modern microprocessors, particularly focusing on the peculiarities of the Blue Gene processor.

#### The Vienna MAP Compiler

The main part of thesis presents the newly developed special-purpose Vienna MAP compiler for IBM Blue Gene in detail.

Chapter 4 describes a new method for the automatic 2-way SIMD vectorization of numerical straight line code, which produces globally optimal code in a large number of cases, including complex FFT kernels of arbitrary lengths and real FFT kernels of even lengths.

Chapter 5 illustrates domain-specific peephole optimization techniques aiming at a good utilization of target specific hardware features like SIMD FMAs.

Chapter 6 describes domain-specific backend optimization techniques and their implementation in a backend specifically designed for the IBM PowerPC 440 FP2 processor.

Chapter 7 illustrates the functioning of the Vienna MAP compiler as a whole, describing its input, its output, its ways of intermediate program representation, as well as its compilation process by tracking a selection of example codes through all relevant stages.

#### **Experimental Results**

Chapter 8 presents and discusses performance data of code generated by the Vienna MAP compiler, which have been measured recently on state-of-the-art Blue Gene systems that are currently the fastest computers worldwide.

#### Chapter 2

#### Fast Algorithms for Linear Transforms

Discrete linear transforms are important tools used in a wide range of real-life applications, ranging from spectal analysis of signals, to the lossy compression of video and audio data, to voice recognition, to the multiplication of large integers or polynomials, to solving partial differential equations.

This chapter defines and discusses discrete linear transforms and fast algorithms for such transforms, following the methodology introduced by the SPI-RAL team [61]. The approach is based on Kronecker product factorizations of transform matrices and on recursive factorization rules.

#### 2.1 Discrete Linear Transforms

This section defines discrete linear transforms as a foundation for the specific discussion of fast Fourier transform algorithms in the next section. In this thesis, the main focus is on the discrete Fourier transform and its fast algorithms based on the Cooley-Tukey recursion.

Discrete linear transforms are represented by real or complex valued matrices and their application means to calculate a matrix-vector product. Thus, they express a base change in the vector space of sampled data.

**Definition 2.1.1 (Real Discrete Linear Transform)** Let  $x \in \mathbb{R}^n$ ,  $y \in \mathbb{R}^m$ , and  $M \in \mathbb{R}^{m \times n}$ . The real linear transform of x is obtained by the matrix-vector multiplication

$$y = M x$$

.

Examples of real discrete linear transforms include the Walsh-Hadamard transform as well as all sine and cosine transforms.

**Definition 2.1.2 (Complex Discrete Linear Transform)** Let  $x \in \mathbb{C}^n$ ,  $M \in \mathbb{C}^{m \times n}$ , and  $y \in \mathbb{C}^m$ . The complex linear transform of x is given by the matrix-vector multiplication

$$y = M x$$

.

A particularly important example of complex discrete linear transforms and the main focus in this thesis is the discrete Fourier transform (DFT), which, for size N, is given by the following two definitions.

**Definition 2.1.3 (Discrete Fourier Transform Matrix)** The matrix DFT<sub>N</sub> is defined for any  $N \in \mathbb{N}$  with  $i = \sqrt{-1}$  by

DFT<sub>N</sub> =

$$(e^{2\pi i k \ell/N} | k, \ell = 0, 1, ..., N - 1)$$

.

The values  $\omega_N^{k\ell} = e^{2\pi i k\ell/N}$  are called twiddle factors.

Example (DFT Matrices) The first five DFT matrices are

DFT<sub>1</sub> = (1), DFT<sub>2</sub> =

$$\begin{pmatrix} 1 & 1 \\ 1 & -1 \end{pmatrix}$$

, DFT<sub>3</sub> =  $\begin{pmatrix} 1 & 1 & 1 \\ 1 & e^{-2\pi i/3} & e^{-4\pi i/3} \\ 1 & e^{-4\pi i/3} & e^{-2\pi i/3} \end{pmatrix}$

$$DFT_4 = \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & -i & -1 & i \\ 1 & -1 & 1 & -1 \\ 1 & i & -1 & -i \end{pmatrix}, \quad DFT_5 = \begin{pmatrix} 1 & 1 & 1 & 1 & 1 \\ 1 & e^{-2\pi i/5} & e^{-4\pi i/5} & e^{-6\pi i/5} & e^{-8\pi i/5} \\ 1 & e^{-4\pi i/5} & e^{-8\pi i/5} & e^{-2\pi i/5} & e^{-6\pi i/5} \\ 1 & e^{-6\pi i/5} & e^{-2\pi i/5} & e^{-4\pi i/5} \\ 1 & e^{-8\pi i/5} & e^{-6\pi i/5} & e^{-4\pi i/5} \end{pmatrix}.$$

DFT<sub>4</sub> is the largest DFT matrix having only trivial twiddle-factors, i. e., 1,i,-1, and -i.

**Definition 2.1.4 (Discrete Fourier Transform)** The discrete Fourier transform  $y \in \mathbb{C}^N$  of a data vector  $x \in \mathbb{C}^N$  is given by the matrix-vector product

$$y = DFT_N x$$

.

#### 2.1.1 Fast Algorithms

Many discrete linear transforms can be calculated by using fast algorithms, which reduce the algorithmic complexity from  $O(N^2)$ —as required by the direct evaluation of a matrix-vector product—down to  $O(N \log N)$ . This complexity reduction, and the resulting runtime reduction, makes these transforms suitable for the processing for large amounts of data.

**Example (FFT)** The complexity reduction factor obtained by using an FFT algorithm instead of plain matrix-vector multiplication is approximately  $2N^2/(5N\log_2 N)$ . For  $N=2^{20}$  this complexity reduction is equivalent to the progress of 20 years in hardware development.

Mathematically, any fast algorithm for a discrete linear transform can be viewed as a factorization of the transform matrix into a product of sparse matrices. It is a specific property of discrete linear transforms that these factorizations are highly structured and can be written in a very concise way using the formalism of Kronecker (tensor) products [82].

Two particularly important classes of sparse matrices arising in FFT factorizations are stride permutation matrices and twiddle factor matrices. The product of an input vector with these sparse matrices can be performed with O(N) cost.

The permutation operator  $L_n^{mn}$  sorts the components of x according to their index modulo n. Thus, components with indices equal to  $0 \mod n$  come first, followed by the components with indices equal to  $1 \mod n$ , and so on.

**Definition 2.1.5 (Stride Permutation)** For a vector  $x \in \mathbb{C}^{mn}$  with

$$x = \sum_{k=0}^{mn-1} x_k e_k^{mn}$$

with  $e_k^{mn} = e_i^n \otimes e_j^m$ , and  $x_k \in \mathbb{C}$ ,

the stride permutation  $L_n^{mn}$  is defined by its action on the tensor basis of  $\mathbb{C}^{mn}$ :

$$L_n^{mn}(e_i^n \otimes e_j^m) = e_j^m \otimes e_i^n.$$

Twiddle factor matrices are certain diagonal matrices, whose elements are roots of unity.

**Definition 2.1.6 (Twiddle Factor Matrix)** Let  $\omega_N = e^{2\pi i/N}$  denote the Nth root of unity. The twiddle factor matrix, denoted by  $T_m^{mn}$ , is a diagonal matrix defined by

$$T_{m}^{mn}(e_{i}^{m} \otimes e_{j}^{n}) = \omega_{mn}^{ij}(e_{i}^{m} \otimes e_{j}^{n}), \quad i = 0, 1, \dots, m - 1, \ j = 0, 1, \dots, n - 1,$$

$$T_{m}^{mn} = \bigoplus_{i=0}^{m-1} \bigoplus_{j=0}^{n-1} \omega_{mn}^{ij} = \bigoplus_{i=0}^{m-1} \Omega_{n,i}(\omega_{mn}),$$

where  $\Omega_{n,k}(\alpha) = \operatorname{diag}(1,\alpha,\ldots,\alpha^{n-1})^k$ .

Example (DFT<sub>4</sub>) Consider a sparse factorization, i.e., a fast algorithm, for DFT<sub>4</sub>. Using the mathematical notation from [82] it follows that

$$DFT_{4} = \begin{pmatrix} 1 & 1 & 1 & 1 \\ 1 & i & -1 & -i \\ 1 & -1 & 1 & -1 \\ 1 & -i & -1 & i \end{pmatrix}$$

$$= \begin{pmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ \frac{1}{1} & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \end{pmatrix} \cdot \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & i \end{pmatrix} \cdot \begin{pmatrix} 1 & 1 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & -1 \end{pmatrix} \cdot \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix}$$

$$= (DFT_{2} \otimes I_{2}) \cdot T_{2}^{4} \cdot (I_{2} \otimes DFT_{2}) \cdot L_{2}^{4}.$$

$$(2.1)$$

$T_2^4$  denotes the twiddle matrix diag(1,1,1,i).  $L_2^4$  denotes a stride permutation that swaps the two middle elements  $x_1$  and  $x_2$  of four-dimensional vectors, i. e.,

$$\left(egin{array}{c} x_0\ x_2\ x_1\ x_3 \end{array}

ight) = \mathrm{L}_2^4 \, \left(egin{array}{c} x_0\ x_1\ x_2\ x_3 \end{array}

ight).$$

#### 2.1.2 Automatic Derivation of Fast Algorithms

In [22] a method has been introduced that *automatically* derives fast algorithms for a given transform and size. This method is based on algebraic symmetries of the transformation matrices utilized by the software package AREP [21], a library for the computer algebra system GAP [37] used in SPIRAL. AREP is able to factorize transform matrices and to find fast algorithms automatically. In [68] an algebraic derivation of fast sine and cosine transform algorithms is described.

#### 2.1.3 Recursive Rules

One key element in factorizing a discrete linear transform matrix into sparse factor matrices is the application of breakdown rules.

A breakdown rule describes the factorization of a given transform matrix into into several transforms of smaller sizes. These smaller transforms, which may be of a different type, can be further expanded. Thus, rules can be applied recursively to reduce a large linear transform to a number of smaller discrete linear transforms.

The applicability of breakdown rules depends on the transform size, implicitly encoded into the left-hand side of a rule. For instance, in the following definitions, the rule for breaking down a WHT may only be used for transform lengths being a power-of-two. Variables occuring on the left-hand side of a rule are used as parameters of the expression on the right-hand side.

In the following examples  $P_n$ ,  $P'_n$ , and  $P''_n$  denote permutation matrices,  $S_n$  denotes a bidiagonal matrix and  $D_n$  a diagonal matrix [85].

**Example (Walsh-Hadamard Transform)** The WHT<sub>N</sub> for  $N = 2^k$  is given by

$$WHT_{2^k} = \overbrace{DFT_2 \otimes \ldots \otimes DFT_2}^{k \text{ times}}.$$

A particular example of a breakdown rule for this transform is

$$WHT_{2^{k}} = \prod_{i=1}^{k} \left( I_{2^{k_{1} + \dots + k_{i-1}}} \otimes WHT_{2^{k_{i}}} \otimes I_{2^{k_{i+1} + \dots + k_{t}}} \right), \quad k = k_{1} + \dots + k_{t}.$$

(2.2)

Example (Discrete Cosine Transform) The matrix  $DCT_N$  for arbitrary N is given by

$$DCT_N = (\cos((\ell + 1/2)k\pi/N) \mid k, \ell = 0, 1, ..., N - 1).$$

A corresponding breakdown rule is

$$DCT_{2n} = P_{2n} (DCT_n \oplus S_{2n} DCT_n D_{2n}) P'_{2n} (I_n \otimes DFT_2) P''_{2n}$$

**Example (Discrete Fourier Transform)** A rule for the DFT<sub>N</sub> matrix is given by

$$DFT_{mn} = (DFT_m \otimes I_n) T_n^{mn} (I_m \otimes DFT_n) L_m^{mn}.$$

(2.3)

(2.3) is the Cooley-Tukey FFT written in Kronecker product notation [45]. This particular rule will be discussed in more detail in Section 2.2.

Transforms of higher dimension are captured in the framework of breakdown rules in a natural way. For example, if M is the matrix of an  $N \times N$  transform, then the corresponding two-dimensional transform is given by  $M \otimes M$ . Using the respective property of the tensor product, the breakdown rule

$$M \otimes M = (M \otimes I_N) (I_N \otimes M) \tag{2.4}$$

is obtained.

#### 2.1.4 Formulas and Base Cases

Eventually a mathematical formula is obtained when all transforms are expanded into base cases.

Example (Fully Expanded Formula for WHT<sub>8</sub>) According to rule (2.2), WHT<sub>8</sub> can fully be expanded into

$$(DFT_2 \otimes I_4)(I_2 \otimes DFT_2 \otimes I_2)(I_4 \otimes DFT_2)$$

with DFT<sub>2</sub> being the base case.

#### 2.1.5 Trees and Recursion

The recursive decomposition of a discrete linear transform into smaller ones using recursion rules can be expressed by trees. The authors of FfTW call these trees plans while the Spiral team calls them rule trees. In these trees the essence of the recursion—the type and sizes of the child transforms—is specified.

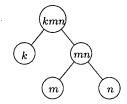

As an illustrative example, rule trees for a recursion rule that breaks down a transform of size N into two smaller transforms is discussed. Fig. 2.1 shows a tree of a discrete linear transform of size N=mn that is decomposed into two smaller transforms of the same type of size m and n. The node marked with mn is the parent node of the child nodes lying directly below, which indicate transforms of size m and n.

Figure 2.1: Tree representation of a discrete linear transform of size N=mn with one recursion step applied.

Analogously, Fig. 2.2 shows a tree of a discrete linear transform of size N = kmn where in a first step the transform is decomposed into discrete linear transforms of size k and mn. In a second step the transform of size mn is further decomposed into transforms of size m and n.

In general, the splitting rules are *not* commutative with respect to m and n. Thus, the trees are generally *not* symmetric. Left and right child nodes have to

Figure 2.2: Right-expanded tree, two recursive steps.

be distinguished, which is done simply by left and right branches. Every tree has one *root node*, i. e., a node having no parent nodes. Nodes without children are called *leaf nodes*. All remaining nodes are intermediate nodes.

The upmost recursive decomposition in a tree, the one of the root node, is called the *top level decomposition*. If its two branches are equivalent the tree is called *balanced*, if they are nearly equivalent it is said to be "somewhat balanced." But there also exist trees that are not balanced at all. They may be even extremely unsymmetrical. A tree with just leafs as left children is formed strictly to the right. Such a tree is called *right-expanded*, its contrary *left-expanded*.

#### 2.1.6 The Search Space

By selecting different breakdown rules, a given discrete linear transform expands to a large number of formulas that correspond to different fast algorithms. For example, for  $N = 2^k$ , there are k-1 ways to apply rule (2.3) to DFT<sub>N</sub>. A similar degree of freedom recursively applies to the smaller DFTs obtained, which leads to  $O(5^k/k^{3/2})$  different formulas for DFT<sub>2</sub><sup>k</sup>. In the case of the DFT, allowing breakdown rules other than (2.3) further extends the formula space.

The problem of finding an efficient formula for a given transform translates into a search problem in the space of formulas for that specific transform. The size of the search space depends on the rules and transforms actually used.

The conventional approach to solving the search problem is to make an educated guess (using some machine characteristics as hints) which formula might lead to an efficient implementation and then to continue by optimizing this formula.

The automatic performance tuning systems SPIRAL and FFTW use a radically different approach. Instead of explicitly modeling machine characteristics and their impact on performance, both systems use intelligent search, guided by empirical runtime measurements, to find implementations well-adapted to some particular target. SPIRAL uses various search strategies and fully expands the formulas. FFTW uses dynamic programming and restricts its search to the coarse grain structure of the algorithm [30]. The rules are hardcoded into the executor while the fine grain structure is fixed by the codelet generator genfft at compile time.

#### 2.2 The Fast Fourier Transform

In the last section, discrete linear transforms and the discrete Fourier transform were briefly introduced using a special mathematical notation, which made clear that such transforms feature an intrinsic recursive structure.

In this section, different types of the Cooley-Tukey recursion are presented. The difference between conventional iterative algorithms and the recursive approach used by Spiral and Fftw is discussed. Conventional iterative algorithms and vector computer algorithms are summarized.

#### 2.2.1 The Cooley-Tukey Recursion

In 1965 Cooley and Tukey [13] published the fast Fourier transform for problem sizes being powers of two. Other authors extended the idea from powers of two to arbitrarily composed numbers. A summary of the historic development of the FFT, whose origins date back to Carl Friedrich Gauss, can be found in [82].

In the decades following Cooley and Tukey's publication, FFT algorithms were obtained by applying breakdown rules recursively and then manipulating the resulting formulas to obtain the respective iterative algorithms. However, in the context of this thesis, the recursive rules are more important than the iterative algorithms. Section 2.2.2 discusses the difference between the iterative and the recursive approach.

There are four equivalent formulations of the Cooley-Tukey recursion rule, shown in Theorem 2.2.1. These versions can be transformed into each other by exploiting algebraic identities of tensor products, effectively choosing whether the identity matrix is the left or the right factor of the first and the second tensor product occuring in the rule.

#### Theorem 2.2.1 (Cooley-Tukey Breakdown Rules) For $mn \geq 2$

$$DFT_{mn} = (DFT_m \otimes I_n) \quad T_n^{mn} \quad (I_m \otimes DFT_n) L_m^{mn}$$

$$= L_n^{mn} (I_m \otimes DFT_n) \quad T_n^{mn} \quad (DFT_m \otimes I_n)$$

$$= (DFT_m \otimes I_n) T_n^{mn} L_m^{mn} (DFT_n \otimes I_m)$$

$$= L_m^{mn} (I_n \otimes DFT_m) L_n^{mn} T_n^{mn} (I_m \otimes DFT_n) L_m^{mn} .$$

(Parallel)

With decimation in time (DIT), the initial step is a permutation, which allows to perform the transform out-of-place without any additional copying overhead. The vector (or four-step) and the parallel (or six-step) FFT rules aim at a formulation exhibiting terms that are inherently well-suited for expressing vector or parallel operations. Vector and parallel rules are usually applied only once on top-level.

The parallel rule of Theorem 2.2.1 was developed by Bailey [7]. A second recursive application of this rule is the prerequisite for parallel one-dimensional FFT algorithms which overlap communication and computation [25, 47].

#### 2.2.2 Iterative vs. Recursive FFT Algorithms

This section outlines the two basic strategies in organizing FFT programs. For the implementation of an FFT algorithm there are two radically different strategies for successively applying one of Cooley-Tukey breakdown rules.

In recursive FFT algorithms, the multiplication by the DFT matrix is performed by calling program modules that compute the subproblems according to the chosen rule. The child problems are further decomposed by recursively calling the same program again and again until the DFTs are small enough to be executed directly by optimized leaf routines. This approach is used by Spiral and FfTw.

Iterative FFT code contains the entire matrix decomposition explicitly and manages all tasks directly. Thus, all recursive decomposition steps are flatted and the computation is done stagewise leading to conventional triple loop FFT implementations [82] that perform the DFT computation stagewise. Each stage requires an additional pass through the data vector.

#### Recursive FFTs

While divide-and-conquer descriptions of the FFT are standard in introductory texts, almost all non-adaptive high performance FFTs use an iterative implementation. This is due to the widespread opinion that recursive implementations of divide-and-conquer algorithms are too expensive. This belief is based on the fact that the required function calls were among the computationally most expensive instructions for a long time.

However, an intriguing feature of divide-and-conquer algorithms is that they should run well on computers with deep memory hierarchies without the need for blocking or tiling. Each successive divide step in the divide-and-conquer process generates subproblems that touch successively smaller portions of data, thus increasing locality of reference. For any level of the memory hierarchy, there is a level of division below which all the data touched by the subproblem will fit into that level of the memory hierarchy. Therefore, a divide-and-conquer algorithm can be viewed as an algorithm that is blocked for all levels of the memory hierarchy.

This idea of achieving optimal use of caches on all levels of a memory hierarchy without knowledge of their sizes is referred to as *cache-obliviousness* [32].

In the recent development of computer systems, memory access operations became more and more expensive when compared to function calls. Several years ago FfTW [29] broke with the tradition of iterative FfTs and implemented a recursive hardware adaptive FfT computation.

SPIRAL [61, 69] extended this recursive approach to all kinds of discrete linear transforms. For each transform and problem size SPIRAL generates intrinsically recursive code, that is partially unrolled for even higher performance.

#### Iterative FFTs

All conventional non-adaptive FFT algorithms and their implementation have an iterative structure. The first FFT algorithm published by Cooley and Tukey was a right-expanded radix-2 factorized FFT, whose decomposition strategy was clear and explicitly implemented. For decades the execution of an FFT was seen as a sequence of computational stages; each stage corresponding to one factor of the products that define algorithms in the modern notation.

Typically, Cooley-Tukey type FFT algorithms for dealing with data vectors of length  $N = 2^n$  are implemented in form of a *triple-loop* [82].

While the design and programming of such implementations is rather easy [82], their performance is often not optimal because vector lengths vary from stage to stage and therefore the cache usage far from being optimal. Yet, as long as the input vector fits into the cache memory entirely the iterative strategy was superior because there is no overhead due to additional program organization, which was expensive on earlier computer generations. On current computer systems, however, such a clear statement is not possible any more.

#### Vector Computer FFT Algorithms and Short Vector Extensions

The two Stockham FFT algorithms [80, 82] and the 4-step FFT algorithm have been designed specifically for conventional vector computers. In principle, these algorithms could be used also on current processors featuring short vector SIMD extensions, but they have several drawbacks there.

Complex Arithmetic. Vector computer FFT algorithms are formulated using complex matrices. Thus, it is necessary to reformulate complex transforms using real matrices and formulas to capture the level of details required for implementations successfully utilizing short vector SIMD extensions.

**Vector Length and Stride.** All three algorithms mentioned above are optimized for *long vectors*. The Stockham algorithms are optimized for *fixed stride* but not for *unit stride* memory access. Accordingly, these algorithms do not produce good performance when running on short vector SIMD extensions.

Iterative Algorithms. The very nature of the two Stockham FFT algorithms and the 4-step FFT algorithm is an iterative one, which conflicts with the requirements of Spiral and FfTW to support adaptivity.

Thus, algorithms specifically designed for conventional vector computers are not suitable for the short vector SIMD extensions of modern processors. To harness the performance potential offered by SIMD extensions, methods specifically addressing the specific features and limitations of the respective SIMD instruction set extensions are required.

#### Chapter 3

#### Software and Hardware Architecture

In the context of producing efficient digital signal transform codes, a number of software and hardware features need to be taken in account.

Section 3.1 is devoted to current software architecture in scientific computing and presents the state-of-the-art in architecture adaptive numerical software used in the field of linear algebra and digital signal transforms [62]. The following three sections are devoted to modern hardware architecture. Section 3.2 describes short vector SIMD ISA extensions, focusing on their basic properties, their utilization, as well as similarities to vector supercomputers. A basic discussion of 2-way SIMD instructions follows in Section 3.3. Finally, Section 3.4 introduces the IBM PowerPC 440 FP2, the processor used in IBM's Blue Gene supercomputers, and describes its most important features, characteristics, and limitations.

#### 3.1 Automatic Performance Tuning Software

Automatic performance tuning goes a step beyond standard compiler optimization. It is a problem specific approach and thus is able to achieve much more than general purpose compilers are capable of. For instance, ATLAS' search for the correct loop tiling for carrying out a matrix-matrix product is a loop transformation a compiler could do in principle (and some compilers actually try to do), if the compiler had an accurate machine model to deduce the correct tiling. But compilers do not reach ATLAS' performance by far. The same phenomenon occurs with the source code scheduling done by SPIRAL and FFTW for their automatically generated straight line code, which should be done satisfactorily by the target compiler. Again, available general purpose compilers fail to produce well-performing object code.

#### 3.1.1 Compiler Optimization Methodology

Modern compilers make extensive use of optimization techniques to improve the object code's performance. Most advanced optimization techniques depend on static program analyses based on simplified machine models. These optimization techniques include high-level loop transformations, such as loop unrolling and tiling. These methods have been extensively studied for over 30 years and have produced, in many cases, satisfactory results. However, the underlying machine models are inherently inaccurate, and transformations are not independent from

each other in their effect on performance. Thus, the compiler's task of deciding the best sequence of transformations is a very difficult one [2].

Typically, compilers use heuristics that are based on averaging observed behavior for a small set of benchmarks. Furthermore, while processors and memory hierarchies are typically modeled by static analysis, this does not account for the behavior of the entire system. For instance, the register allocation policy and strategy for introducing spill code in the backend of the compiler may have a significant impact on the resulting performance. Thus, static analysis is a means to improving program performance, which is limited by compile-time decidability.

#### 3.1.2 The Program Generator Approach

One of the foundations of source code adaptation at compile-time is automatic code generation. In this approach, a code generator, i. e., a program that produces other programs, is used. The code generator takes as parameters certain information concerning the source code adaptations to be made, e.g., instruction cache size, choice of combined or separate multiply and add instructions, lengths of floating-point and fetch pipelines, and so on. Depending on these parameters, the code generator produces source code hopefully having the desired characteristics.

## 3.1.3 Compile Time Adaptive Algorithms Using Feedback Information

Not any important architectural variable can be handled by *parameterized* compile-time adaptation. Adaptation to some architectural variables would require a modification of the underlying source code. This brings in the need for the second method of software adaptation, compile-time adaptation by *feedback directed* code generation, which involves actually generating different implementations of the very same algorithm and selecting the best performing one.

There are at least two different ways to proceed:

- (i) The simplest approach is to get the programmer to supply various hand-tuned implementations, and then to choose a suitable one.

- (ii) The second method is based on automatic code generation. In this approach, parameterized code generators are used. Performance optimization with respect to a particular hardware platform is achieved by searching, i.e., varying the generator's parameters, benchmarking the resulting routines, and selecting the fastest implementation. This approach is also known as automated empirical optimization of software (AEOS) [88].

In the remainder of this section, existing performance tuning software is described briefly.

#### **PHiPAC**

Portable high-performance ANSI C (Phipac) was the first system that implemented the "generate and search" methodology [9]. Phipac's code generator produces matrix-matrix multiply implementations with various loop unrolling depths, varying register and L1- and L2-cache tile sizes, different software pipelining strategies, and enables other options. The output of the generator is C code, both to make the system portable and to shift responsibility to the compiler for performing the final register allocation and instruction scheduling. The search phase benchmarks code produced by the generator under various options to select the best performing implementation.

#### **ATLAS**

The automatically tuned linear algebra software (ATLAS) project is an ongoing research effort of Jack Dongarra's group at the University of Tennessee, Knoxville, focusing on empirical techniques in order to produce software having portable performance. Initially, the goal of the ATLAS project was to provide a portably efficient implementation of the basic linear algebra subroutines (BLAS). Now ATLAS provides at least some level of support for all of the BLAS, and first tentative extensions beyond this level have been taken.

While originally the ATLAS project's principle objective was to develop an efficient library, today the field of investigation has been extended. Within a couple of years new methodologies to develop self-adapting programs have become established, the AEOS approach has been established, thus forming a new sector in software evolution. ATLAS' adaptation approaches are typical AEOS methods; even the concept of AEOS—automated empirical optimization of software—was coined by ATLAS' developers [88]. In this manner, the second main goal of the ATLAS project is a general investigation in program adaptation using AEOS methodology.