Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR !NFORMATIK

Faculty of Informatics

# Hardware Description with Timing Requirements

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

# **Diplom-Ingenieur**

im Rahmen des Studiums

# **Technische Informatik**

eingereicht von

# Stefan Resch

Matrikelnummer 0425306

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung Betreuer: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger Mitwirkung: Univ.Ass. Dipl.-Ing. Dr.techn. Matthias Függer

Wien, 22. November 2011

(Unterschrift Verfasser)

(Unterschrift Betreuer)

FAKULTÄT FÜR !NFORMATIK

Faculty of Informatics

# Erklärung zur Verfassung der Arbeit

Stefan Resch Koberweingasse 2/37 1150 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 22. November 2011

(Unterschrift Verfasser)

To my family.

#### Kurzfassung

Hardware Designs die für sicherheitskritische Anwendungen entwickelt werden müssen unter allen Umständen korrekt funktionieren. Eine Möglichkeit dies sicherzustellen ist durch (i) Beschreiben der Spezifikation in einem formalen Framework und (ii) Beweisen des korrekten Verhaltens der Designs auf der Abstraktionsebene dieses Frameworks. Bei diesem Ansatz bleibt immer noch eine Beweislücke zwischen der Darstellung des Designs im Framework und dessen Codierung in einer für die Fertigung verwendeten Hardware Beschreibungssprache.

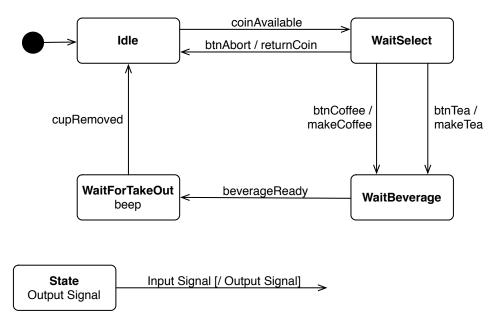

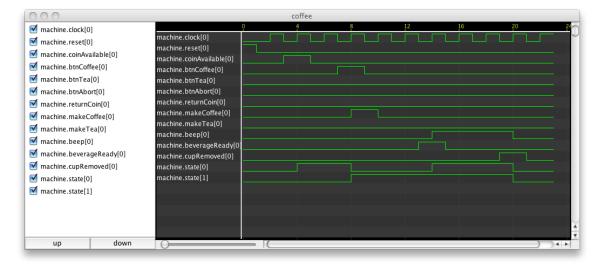

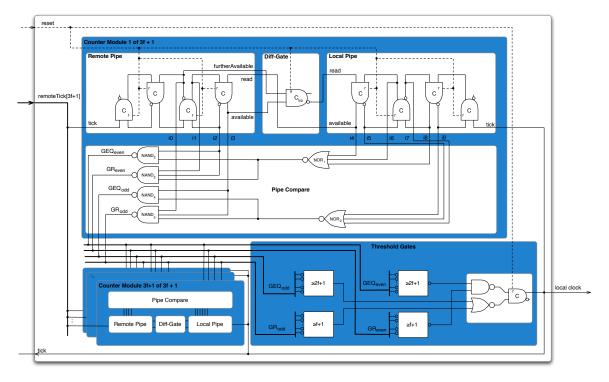

In dieser Arbeit wird die neue Hardware Beschreibungssprache Dhdl vorgestellt. Dhdl erweitert das Formal Modeling and Analysis Framework von Függer [9]. Dadurch wird die Beweislücke zwischen der formalen Analyse und der Hardware Implementierung geschlossen. Mit dem Dhdl spezifischen, semantischen Zeitmodell können auch Simulationsergebnisse von Dhdl in das Formale Framework rückgeführt werden. Die Möglichkeit Zusicherungen über das Zeitverhalten direkt im Dhdl Design selbst zu spezifizieren ist ein großer Vorteil gegenüber aktuell verwendeten Beschreibungssprachen wie VHDL. Um die breite Anwendbarkeit von Dhdl zu zeigen wurden zwei Designs implementiert und deren Zeitverhalten analysiert: ein synchrones, am Beispiel einer einfachen Kaffeemaschine, und ein asynchrones, am Beispiel des DARTS Pulse Generation Algorithmus [21].

#### Abstract

Hardware designs intended for use in high reliability missions are required to behave correctly under all circumstances. One way of establishing their validity is by (i) stating a specification in terms of a formal framework and (ii) proving them correct within the framework. However, a proof gap between the formally stated design and the actual specification in terms of a hardware description language remains.

In this thesis, a novel hardware description language, called Dhdl, is introduced. Dhdl is tailored to the formal modeling and analysis framework defined by Függer in [9]. Thereby, it closes the gap between formal proof methods and hardware implementation. With its semantically defined timing model it is even possible to translate traces back to the modeling and analysis framework. The ability to specify timing properties within the design itself is a major advantage of Dhdl to currently popular hardware description languages like VHDL. To demonstrate the wide applicability of Dhdl, both a synchronous (a simple coffee machine) and an asynchronous hardware design, namely the pulse generation algorithm of DARTS [21], have been implemented and their timing constraints have been analyzed.

#### Acknowledgments

I want to thank Matthias Függer and Andreas Steininger for giving me the opportunity to choose this topic, and for their helpful feedback. I would also like to say thank you to Michael Zehender for introducing me to the method of test driven development and his feedback on the usability of Dhdl. Special thanks to Cristina Niculescu, my friends and my family who supported me during my studies.

# Contents

| 1 | Introduction |                                                               |   |  |  |  |  |  |

|---|--------------|---------------------------------------------------------------|---|--|--|--|--|--|

|   | 1.1          | Motivation for a New Hardware Programming Language            |   |  |  |  |  |  |

|   | 1.2          | 2 About Time                                                  |   |  |  |  |  |  |

|   | 1.3          |                                                               | 2 |  |  |  |  |  |

|   | 1.4          |                                                               | 2 |  |  |  |  |  |

|   | 1.5          | Remarks                                                       | 3 |  |  |  |  |  |

|   | 1.6          | Structure of the Thesis                                       | 3 |  |  |  |  |  |

| 2 | Cau          | Causal Time                                                   |   |  |  |  |  |  |

|   | 2.1          | Timing Behavior in the Functional Simulation                  | 5 |  |  |  |  |  |

|   | 2.2          | Compatibility with the Formal Analysis and Modeling Framework | 5 |  |  |  |  |  |

|   | 2.3          | Timing Assertions for Generated Circuits                      | 5 |  |  |  |  |  |

| 3 | Defi         | nition Concepts                                               | 6 |  |  |  |  |  |

|   | 3.1          | -                                                             | 6 |  |  |  |  |  |

|   |              | 3.1.1 Types                                                   | 7 |  |  |  |  |  |

|   |              | 3.1.2 Expressions                                             | 7 |  |  |  |  |  |

|   |              | 3.1.3 Delay Annotation                                        | 7 |  |  |  |  |  |

|   |              | 3.1.4 Extended Description Concepts                           | 8 |  |  |  |  |  |

|   | 3.2          | Simulation Definition                                         | 0 |  |  |  |  |  |

|   |              | 3.2.1 Simulation Run Procedure                                | 1 |  |  |  |  |  |

|   |              | 3.2.2 Simulation Environment                                  | 1 |  |  |  |  |  |

|   |              | 3.2.3 Results                                                 | 2 |  |  |  |  |  |

|   |              | 3.2.4 Language Features                                       | 2 |  |  |  |  |  |

|   | 3.3          | Package Definition                                            | 3 |  |  |  |  |  |

| 4 | Dhd          | l Implementation and Interaction 1                            | 4 |  |  |  |  |  |

|   | 4.1          | Technology Decisions                                          | 4 |  |  |  |  |  |

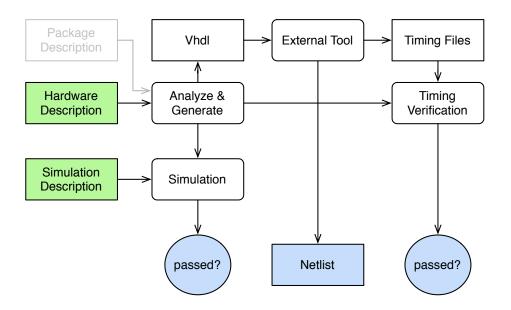

|   | 4.2          | The Dhdl Development Flow                                     | 4 |  |  |  |  |  |

|   |              |                                                               | 5 |  |  |  |  |  |

|   |              | 4.2.2 Generate                                                | 5 |  |  |  |  |  |

|   |              | 4.2.3 Simulation                                              | 6 |  |  |  |  |  |

|   |              | 4.2.4 External Tool                                           | 6 |  |  |  |  |  |

|   |             | 4.2.5 Timing Verification                                  |

|---|-------------|------------------------------------------------------------|

|   | 4.3         | Specific Issues                                            |

|   |             | 4.3.1 Network Representation                               |

|   |             | 4.3.2    Hardware Description Parsing    17                |

|   |             | 4.3.3Expression Optimization18                             |

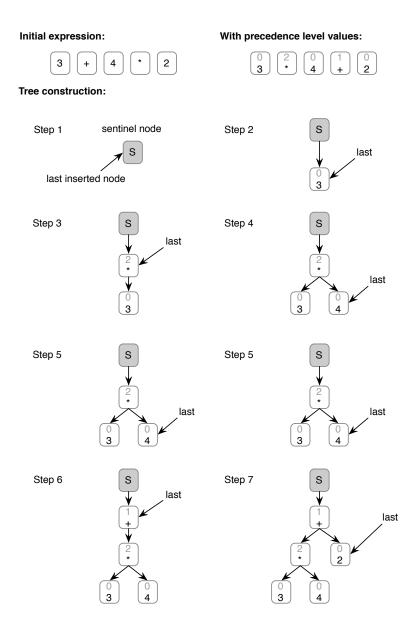

|   |             | 4.3.4    Expression Parsing with Operator Precedence    18 |

|   |             | 4.3.5         Simulator Generation         18              |

| _ | ~           |                                                            |

| 5 | Sem         |                                                            |

|   | 5.1         | Basic Definitions    21                                    |

|   | 5.2         | Syntax                                                     |

|   | 5.3         | $\mathcal{W}$ Semantics                                    |

|   | 5.4         | Rules                                                      |

|   |             | 5.4.1 System Definition Rules                              |

|   |             | 5.4.2 Simulation Rules                                     |

|   |             | 5.4.3 Initial Configuration                                |

|   |             | 5.4.4 Termination                                          |

|   |             | 5.4.5 Functions                                            |

|   |             | 5.4.6 Integration to the Formal Framework 34               |

|   | <b>D</b> 4  |                                                            |

| 6 |             | ence Designs 35                                            |

|   | 6.1         | All Aspects of a Small Design                              |

|   |             | 5.1.1 Reference Design Specification                       |

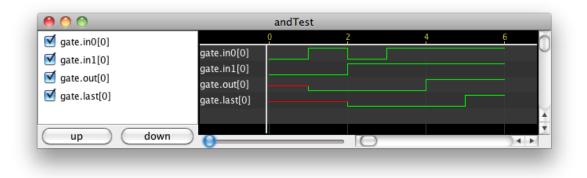

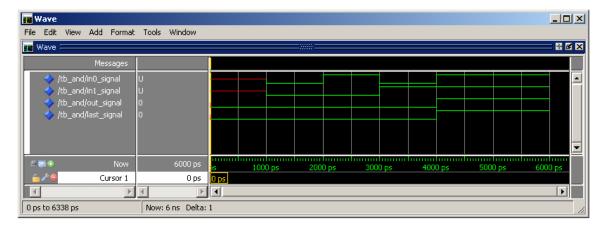

|   |             | 5.1.2 Dhdl Simulation                                      |

|   |             | 5.1.3 Generated VHDL Code                                  |

|   |             | 5.1.4 VHDL Simulation                                      |

|   |             | 5.1.5         Timing Assertions         38                 |

|   |             | 5.1.6Testing on a Development Board39                      |

|   |             | 5.1.7Semantic Interpretation39                             |

|   | 6.2         | Synchronous Design                                         |

|   | 6.3         | Asynchronous Design                                        |

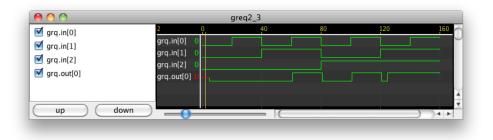

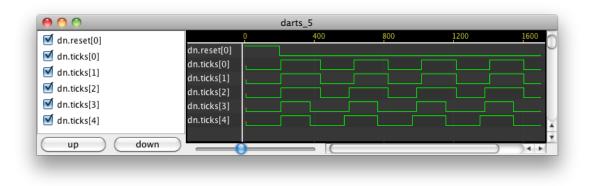

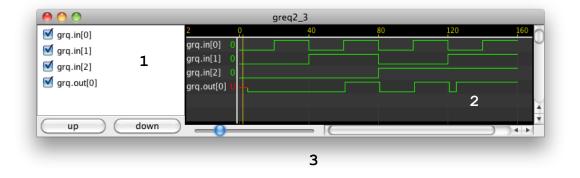

|   |             | 5.3.1 Simulation                                           |

|   |             | 5.3.2 Timing Analysis                                      |

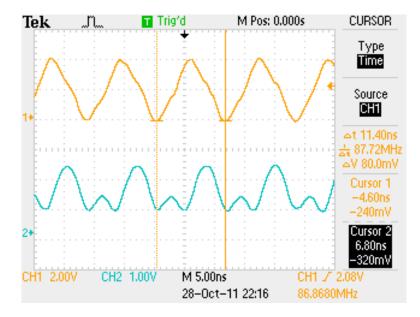

|   |             | 5.3.3Executing on a Development Board46                    |

| _ | G           |                                                            |

| 7 | Con         | usions 49                                                  |

| Α | Dhd         | Language Specification 51                                  |

| A |             | ntroduction                                                |

|   | <b>A</b> .1 |                                                            |

|   |             |                                                            |

|   | ۸ D         | *                                                          |

|   | A.2         | Common Definitions                                         |

|   |             | A.2.1 Basic Language Elements                              |

|   |             | A.2.2 Code Structure                                       |

|   |             |                                                            |

|             | A.2.3                                          | Types                                                                                                                                                                                                                                                                                                                                                                                                                       | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | A.2.4                                          | Operators                                                                                                                                                                                                                                                                                                                                                                                                                   | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.2.5                                          | Expressions                                                                                                                                                                                                                                                                                                                                                                                                                 | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.3         | Hardwa                                         | are Description                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.1                                          | Packages                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.2                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                           | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.3                                          | Module                                                                                                                                                                                                                                                                                                                                                                                                                      | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.4                                          | Port                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.5                                          | Members                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.6                                          |                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.7                                          |                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.8                                          |                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.3.9                                          |                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                | 5                                                                                                                                                                                                                                                                                                                                                                                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.4         |                                                | 6 6                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | A.4.2                                          |                                                                                                                                                                                                                                                                                                                                                                                                                             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.5         |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | -                                              |                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 110         |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.7         |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 107       | •                                              |                                                                                                                                                                                                                                                                                                                                                                                                                             | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | , .<br>77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A.8         |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | <br>79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 110         |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                | e v                                                                                                                                                                                                                                                                                                                                                                                                                         | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.9         |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.10        |                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                           | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Refe        | rence D                                        | Design Details 8                                                                                                                                                                                                                                                                                                                                                                                                            | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |