Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothe der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### DISSERTATION

# Design Space Exploration for the Development of Embedded Systems

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Dipl.-Ing. Martin Holzer Josef-Kollmannstraße 10/2/4, 2500 Baden geboren in Baden am 19. November 1970 Matrikelnummer: 9025189

| M/: A :1.0000    |  |

|------------------|--|

| Wien, April 2008 |  |

### Advisor

Univ.Prof. Dipl.-Ing. Dr.techn. Markus Rupp Vienna University of Technology Institute of Communications and Radio-Frequency Engineering

### Examiner

Univ.Prof. Dipl.-Ing. Dr.techn. Axel Jantsch Royal Institute of Technology Department of Electronics, Communication, and Software Systems

## **ABSTRACT**

The evolution of electronic devices has made a tremendous progress within the last 50 years. In today's world they can be found nearly everywhere, such as cell phones, camcorders, and antiblock-brakes. The design of such complex systems, that consist of hardware and software has to cope with several obstacles like for example high system complexity and increasing economical demands like shortened time-to-market. Those barriers become especially visible in the wireless domain. Here, design productivity lacks behind the possible computational complexity famously described by Moore's law. The importance to cope efficiently with these problems of system design has been highlighted by the International Technology Roadmap for Semiconductors.

This thesis examines one of the design tasks namely design space exploration. Since the description of systems raises constantly its level of abstraction which causes a higher ability for exploring design variants, the automatic derivation of alternatives becomes a high importance. Current approaches for design space exploration are based on manual exploration and hence suffer from a time consuming exploration, leading to sub-optimal solutions. Even automated approaches are restricted due to the high system complexity and need to be enhanced. In this thesis a fast and efficient design space exploration approach is proposed. This is based on the characterisation of a system description, the estimation of design properties, and the automatic evaluation of design variants.

Thus, as first step a set of system description properties is derived that builds a basis for an initial quantitative description of an algorithm. This system characterisation is embedded in a design framework the Open Tool Integration Environment (OTIE) that closes the fragmentation of the design flow, caused by incompatible tools. This framework exhibits its ability for representing a design at various abstraction levels.

Another important ingredient for the design space exploration is the fast and accurate estimation of final implementation properties such as area consumption and execution time. In this thesis an estimation model for predicting the execution cycle count and the hardware complexity is proposed based on the aforementioned metrics. Those rapid estimation methods that are based on static characterisation preserve relative ordering where a fidelity value of 100% is achievable. Furthermore, those estimations are applied to the characterisation of one function regarding its timing profile and the minimisation of the overall execution time for structural verification. A new method which combines execution time profiling and feasible path analysis of the control flow graph is presented. This allows for exact estimation of the process run time interval. Furthermore, a new extension of Poole's algorithm for identifying a basis is presented that allows for reducing the time effort for structural verification significantly.

Finally, the various implementation variants of an algorithm have to be efficiently explored to

vi Abstract

achieve optimal designs. Those variants are determined by algorithmic transformations like loop unrolling or tree height reduction. The exponential growth of this implementation variants with the system size causes an impossible coverage of the complete design space. Hence, an evolutionary algorithm with a two-staged fitness function and an extreme value elitism feature is presented that allows for increasing the coverage of the design space exploration by more than 20% compared to existing approaches. Furthermore, the trade-offs for time and area for a given task set are utilised to increase the efficiency of a schedule for run-time reconfigurable systems. An algorithm is presented that reduces the number of design alternatives that are used for the scheduling. A depth first search algorithm is applied that constructs solutions in feasible time compared to a classical level strip packing formulation with comparable performance results. With the extension to a heuristic algorithm the typical run time is further reduced to several seconds.

**Keywords:** design space exploration, embedded systems, hardware metrics, single system description, design data base, structural verification, multi-objective optimisation, run time reconfigurable computing.

### ZUSAMMENFASSUNG

Die Entwicklung elektronischer Geräte hat innerhalb der letzten 50 Jahre enorme Fortschritte gemacht. Elektronische Komponenten können in fast allen Bereichen des täglichen Lebens angetroffen werden, wie z.B. in Mobiltelefonen, Camcordern, oder Antiblockiersystemen. Die Entwicklung von diesen Systemen bestehend aus Hardware und Software hat einige technische Schwierigkeiten, wie z.B. hohe Systemkomplexität und ökonomischen Anforderungen wie die immer kürzer werdenden Produktzyklen zu überwinden. Diese Barrieren treffen im besonderen Maß auf den Mobilkommunikationsbereich zu. Hier werden wesentlich höhere Fortschritte im Bereich der physikalischen Integration von Transistoren, bestimmt durch das Mooresche Gesetz, als bei der Entwicklungsproduktivität erzielt. Die entscheidende Bedeutung einer automatisierten Entwicklung zur Produktivitätssteigerung wurde bereits von der International Technology Roadmap for Semiconductors aufgezeigt.

Diese Arbeit befasst sich mit einem bestimmten Arbeitsschritt, nämlich der Analyse des Entwurfsraums, wobei einer automatischen Analyse immer größere Bedeutung zukommt. Zur Zeit wird diese Aufgabe mit hohem zeitlichen Aufwand manuell durchgeführt und führt oft nur zu suboptimalen Lösungen. Sogar automatisierte Ansätze stoßen aufgrund der Systemkomplexität schnell an ihre Grenzen. In dieser Arbeit wird eine schnelle und effiziente Entwurfsraumanalyse basierend auf einer statischen Analyse der Systembeschreibung, einer schnellen Schätzung von Implementierungsaspekten und der effizienten Generierung von Implementierungsalternativen vorgestellt.

Dazu wird zuerst eine algorithmische Beschreibung analysiert und markante Metriken ermittelt, um eine quantifizierte Charakterisierung zu erhalten. Diese automatische Systemcharakterisierung ist in eine Entwicklungsumgebung namens Open Tool Integration Environment (OTIE) eingebettet, welche die Lücken im Entwicklungsfluss bedingt durch inkompatible Entwicklungsprogramme schließt. Diese Entwicklungsumgebung erlaubt es, die unterschiedlichen Abstraktionsebenen einer Systembeschreibung zu erfassen.

Ein weiterer wichtiger Schritt zur Entwurfsraumermittlung ist die genaue und schnelle Abschätzung von Implementierungseigenschaften wie z.B. Ausführungszeit und Flächenverbrauch mittels der zuvor beschriebenen Metriken. Diese schnellen Schätzmethoden basierend auf statischen Metriken erhalten die relative Ordnung zueinander wobei ein Zuversichtswert von 100% erreicht wird. Diese Schätzungsmethoden werden verwendet, um eine Funktion bezüglich ihres Ausführungszeitprofils zu charakterisieren und um den Verifikationsaufwand für strukturelles Testen zu minimieren. Eine neue Methode, die Ausführungszeitanalyse und zulässige Pfadanalyse kombiniert, wird vorgestellt. Diese Methode erlaubt eine exakte Abschätzung des Laufzeitintervalls. Weiters wird eine Erweiterung des Pooleschen Algorithmus zur Bestimmung einer Verifikationsbasis vorgestellt, die den zeitlichen Aufwand für strukturelles Testen erheblich reduziert.

viii Zusammenfassung

Zuletzt bestimmen Implementierungsvarianten aufgrund algorithmischer Transformationen wie z.B. loop-unrolling den zu untersuchenden Entwurfsraum. Das exponentielle Wachstum dieser Varianten mit der Systemgröße macht es aber unmögliche diese Varianten vollständig aufzuzählen. Ein genetischer Algorithmus mit einer zweiphasigen Fitnessfunktion und einem Elitismusschema wird vorgestellt, der eine Verbesserung der Entwurfsraumabdeckung von mehr als 20% gegenüber bestehen Methoden erreicht. Weiters wird diese Entwurfsraumanalyse verwendet, um die Ausnutzung von zur Laufzeit rekonfigurierbarer Systeme zu erhöhen. Ein Algorithmus wird vorgestellt, der die Anzahl von Implementierungsalternativen reduziert, um die Problemgröße zu verkleinern. Weiters wird eine Tiefensuche wird verwendet, um eine Lösung verglichen mit einer klassischen Formulierung als ganzzahliges lineares Programmierungsproblem mit praktikablen Zeitauwand zu erreichen. Eine weitere Erweiterung von diesem Algorithmus zu einer Heuristik reduziert die Laufzeit auf wenige Sekunden.

**Schlagwörter:** Entwurfsraumanalyse, Eingebettete Systeme, Hardwaremetriken, Systembeschreibung, Entwicklungsdatenbank, Strukturelle Verifikation, Mehrzieloptimierung, rekonfigurierbare Rechensysteme.

# **ACKNOWLEDGEMENTS**

This thesis would no exist with the support of many other people. Hence, I want to express my gratitude to my supervisor Professor Markus Rupp for encouraging me for working towards a PhD and his support of my thesis. My thankfulness is also directed to Professor Axel Jantsch for agreeing to act as my second supervisor and who gave valuable comments for the improvement of this thesis.

My sincere appreciation goes to my colleagues Pavle Belanović, Bastian Knerr, Christoph Angerer, Naeem Zafar Azeemi, and Daniel Micusik for various fruitful discussions and an inspiring working environment.

Furthermore, I want to acknowledge the support of my colleagues Thomas Herndl and Guillaume Sauzon from Infineon Technologies especially for the joint work on the automatic generation of virtual prototypes.

This work has been funded by the Christian Doppler Laboratory for Design Methodology of Signal Processing Algorithms.

# CONTENTS

| 1 | Intro | oduction 1                              |

|---|-------|-----------------------------------------|

|   | 1.1   | Motivation                              |

|   | 1.2   | Embedded System Design                  |

|   |       | 1.2.1 Design Languages                  |

|   |       | 1.2.2 Design Tasks                      |

|   | 1.3   | Contributions and Outline of the Thesis |

| 2 | Syst  | em Description Metrics                  |

|   | 2.1   | Overview                                |

|   | 2.2   | Graph Prerequisites                     |

|   | 2.3   | Graph Representations                   |

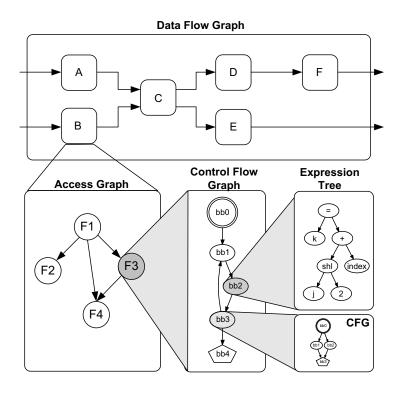

|   |       | 2.3.1 Data Flow Graph                   |

|   |       | 2.3.2 Access Graph                      |

|   |       | 2.3.3 Control Flow Graph                |

|   |       | 2.3.4 Data Flow Representations         |

|   | 2.4   | Structural Metrics                      |

|   |       | 2.4.1 Cyclomatic Complexity             |

|   |       | 2.4.2 Degree of Parallelism             |

|   | 2.5   | Linguistic Metrics                      |

|   |       | 2.5.1 Program Vocabulary                |

|   |       | 2.5.2 Memory Oriented Metrics           |

|   |       | 2.5.3 Control Oriented Metrics          |

|   | 2.6   | Implementation Affinity                 |

|   | 2.7   | Example                                 |

|   | 2.8   | Summary                                 |

| 3 | Integ | grated Design Methodology 37            |

|   | 3.1   | Fragmentation of the Design Flow        |

|   | 3.2   | Overview                                |

|   | 3.3   | Single System Description               |

|   | 3.0   | 3.3.1 Design Database                   |

|   |       | 3.3.2 OTIE Interface                    |

|   | 3.4   | Design Analysis                         |

|   | 3.5   | HTML Visualisation                      |

xii Contents

|    | 2.6        | C., manager,                                   | 48       |

|----|------------|------------------------------------------------|----------|

|    | 3.6        | Summary                                        | 40       |

| 4  | Estin      | nation of Design Properties                    | 51       |

|    | 4.1        | Overview                                       | 51       |

|    | 4.2        | High Level Synthesis                           | 53       |

|    | 4.3        | Control Cycles                                 | 56       |

|    |            | <ul><li>4.3.1 Execution Time Profile</li></ul> | 61<br>63 |

|    |            | 4.3.3 Structural Verification in Minimal Time  | 65       |

|    | 4.4        | Hardware Complexity                            | 71       |

|    | 4.5        | Summary                                        | 72       |

| _  | D          | •                                              | 75       |

| 5  |            | gn Space Exploration                           | 75<br>75 |

|    | 5.1<br>5.2 | Overview                                       | 75<br>77 |

|    | 5.2        | Trade-Off between Area and Timing              | 77       |

|    |            | 5.2.2 Loop Unrolling                           | 78       |

|    |            | 5.2.3 Design Space                             | 78       |

|    | 5.3        | Multi-objective Optimisation                   | 79       |

|    | 5.4        | Genetic Algorithm                              | 81       |

|    |            | 5.4.1 Fitness Function                         | 82       |

|    |            | 5.4.2 Elitism with Extreme Values              | 85       |

|    | 5.5        | Performance Analysis                           | 86       |

|    | 5.6        | Run Time Reconfigurable Computing              | 94       |

|    |            | <ul><li>5.6.1 Scheduling Problem</li></ul>     | 96<br>97 |

|    |            | 5.6.3 Results                                  | 99       |

|    | 5.7        | Summary                                        | 100      |

| _  |            | •                                              |          |

| 6  | Conc       | clusions                                       | 101      |

| Αŗ | pend       | dices                                          | 103      |

| Α  | Nota       | ation                                          | 105      |

| В  | List       | of Variables                                   | 107      |

| C  | Inter      | mediate Format                                 | 109      |

| _  |            | XML Format                                     | 109      |

|    |            | GXL Format                                     | 119      |

| D  |            | gn Space Exploration Results                   | 127      |

| E  |            | chmark Algorithms                              | 131      |

|    | Denc       | JUHAIK AIROHLIIIIS                             | 1.51     |

| Contents               | xiii |

|------------------------|------|

| F Dijkstra's Algorithm | 139  |

| G List of Acronyms     | 141  |

# LIST OF FIGURES

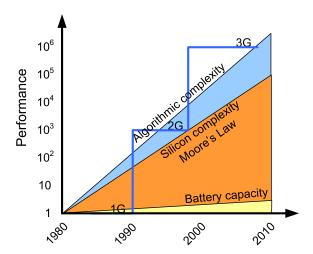

| 1.1  | Algorithmic complexity outpaces silicon complexity.                                                                                                                                           | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

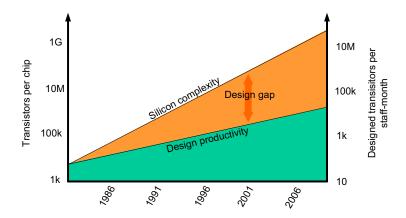

| 1.2  | Design productivity crisis                                                                                                                                                                    | 3  |

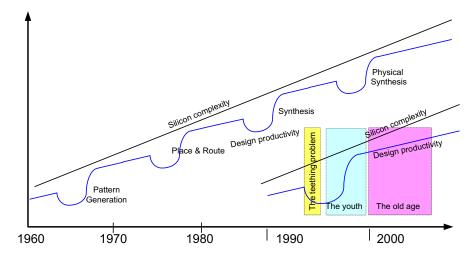

| 1.3  | Deployment of new electronic design automation technologies by the industry and the life cycle of a new technology.                                                                           | 3  |

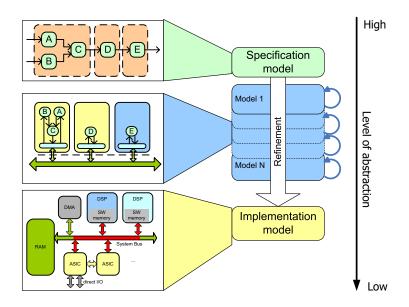

| 1.4  | Design flow for embedded systems                                                                                                                                                              | 6  |

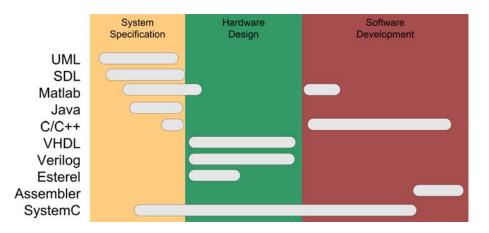

| 1.5  | Hardware/software design languages covering different levels of abstraction                                                                                                                   | 6  |

| 1.6  | Up to 90% of the costs are determined at the first part of the design                                                                                                                         | 7  |

| 1.7  | Design space exploration on different levels of abstraction                                                                                                                                   | 8  |

| 1.8  | Overview of the EDA tool support for the entire design process                                                                                                                                | 9  |

| 1.9  | Automatic design space exploration versus manual approach                                                                                                                                     | 10 |

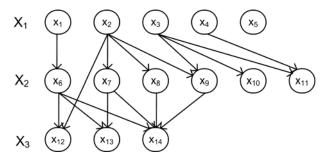

| 2.1  | System decomposition into hierarchical graph structures                                                                                                                                       | 17 |

| 2.2  | Simple SDFG and decomposition into its SAG                                                                                                                                                    | 18 |

| 2.3  | Access graph                                                                                                                                                                                  | 18 |

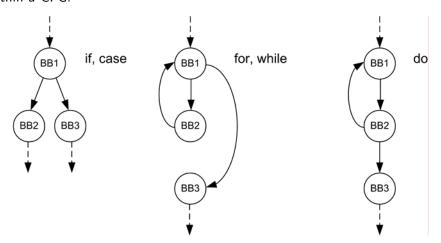

| 2.4  | Programming statements and their corresponding graph structure within a CFG.                                                                                                                  | 19 |

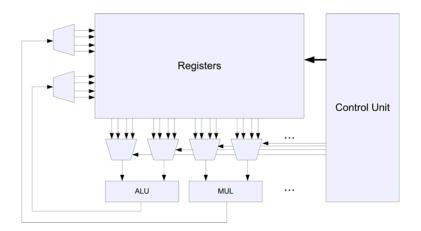

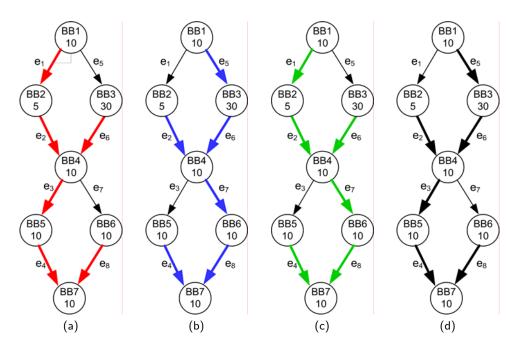

| 2.5  | Example of a CFG. The basic blocks are annotated with the corresponding Cycle Count (CC) that is needed to execute the internal DFG.                                                          | 21 |

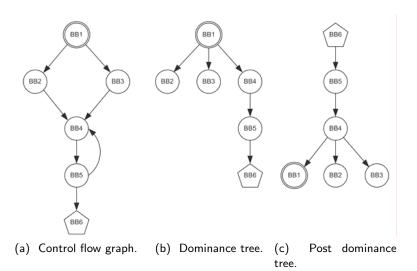

| 2.6  | A CFG and its dominace tree representations                                                                                                                                                   | 23 |

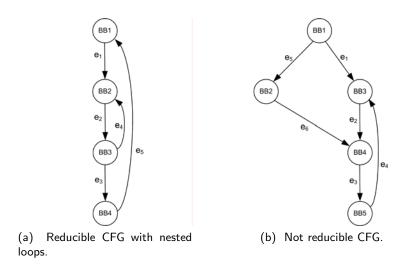

| 2.7  | Reducability of CFG.                                                                                                                                                                          | 24 |

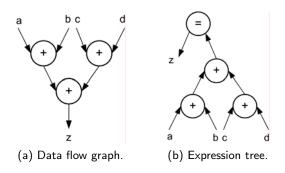

| 2.8  | Graphical data flow representations.                                                                                                                                                          | 24 |

| 2.9  | CFG of the code example in Listing 2.2                                                                                                                                                        | 26 |

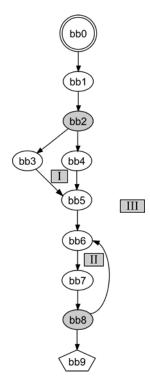

| 2.10 | Control flow graph with a cyclomatic complexity of three, which equals the number of regions (I, II, III) surrounded by the graph. Basic blocks that represent a control statement are shaded | 27 |

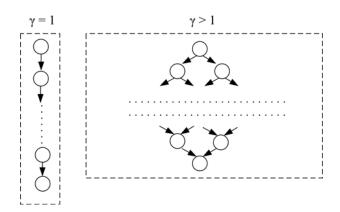

| 2 11 | Degree of parallelism for $\gamma=1$ and $\gamma>1$                                                                                                                                           | 28 |

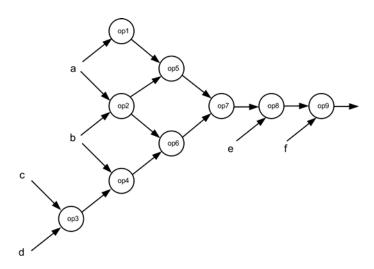

|      | Degree of parallelism for a DFG                                                                                                                                                               | 28 |

|      |                                                                                                                                                                                               | 20 |

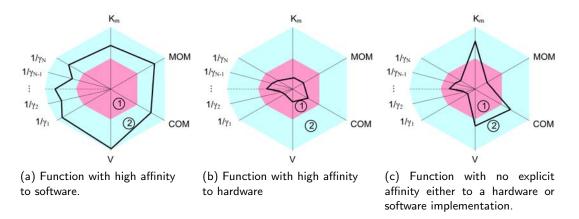

| 2.13 | Kiviat charts for different functions indicating their affinity either to be implemented in hardware or software.                                                                             | 32 |

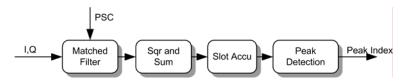

| 2.14 | Block diagram of the cell searcher                                                                                                                                                            | 32 |

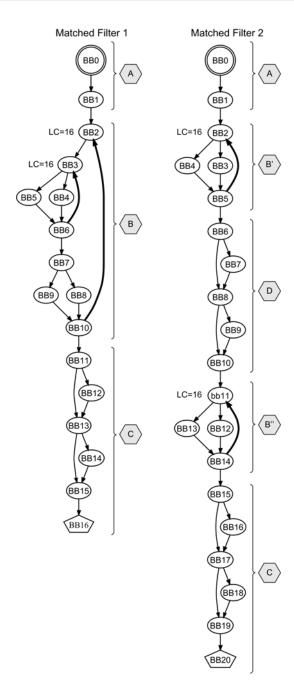

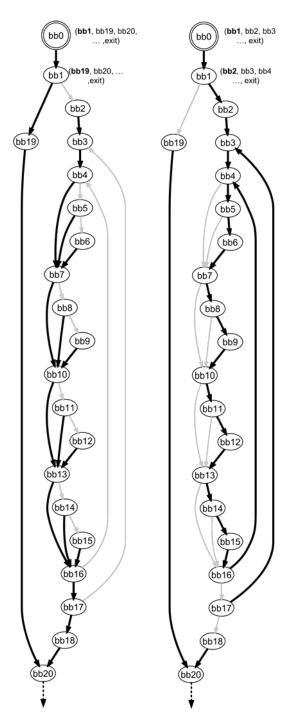

| 2.15 | Control flow graphs of two different matched filter implementations                                                                                                                           | 34 |

xvi List of Figures

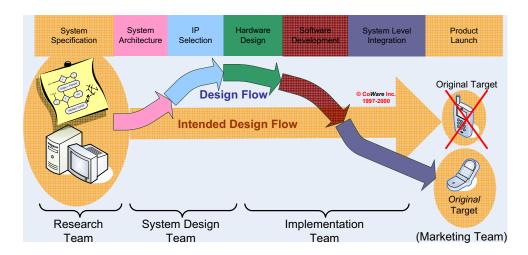

| 3.1  | Fragmentation of the design flow.                                                                                                                                                                                      | 38 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

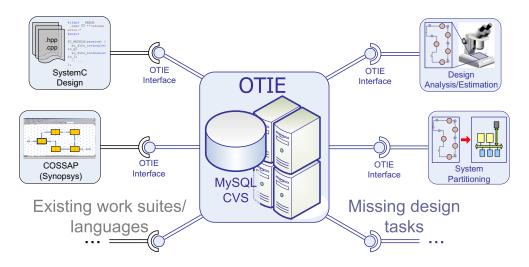

| 3.2  | Open Tool Integration Environment.                                                                                                                                                                                     | 40 |

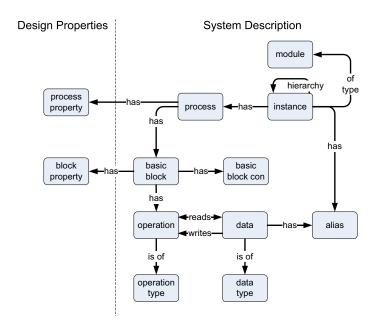

| 3.3  | The structure of the design data base                                                                                                                                                                                  | 41 |

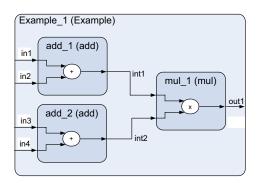

| 3.4  | Design Example                                                                                                                                                                                                         | 43 |

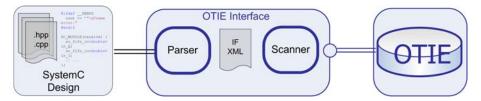

| 3.5  | Concept of the OTIE interface                                                                                                                                                                                          | 44 |

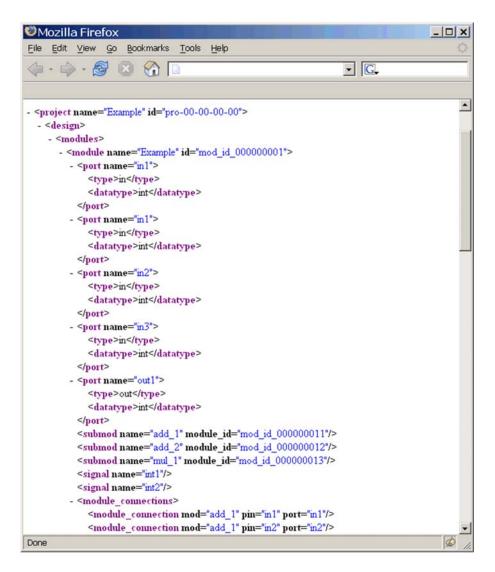

| 3.6  | XML-based Intermediate Format                                                                                                                                                                                          | 45 |

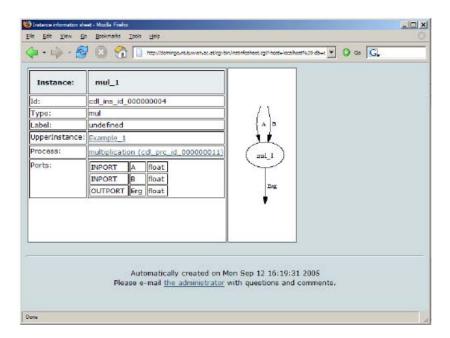

| 3.7  | Information page of one process.                                                                                                                                                                                       | 47 |

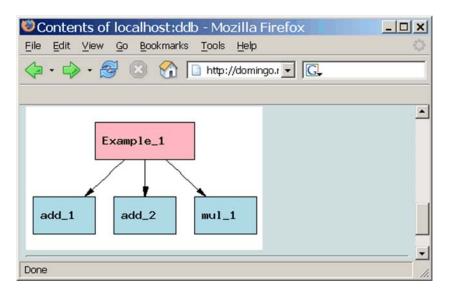

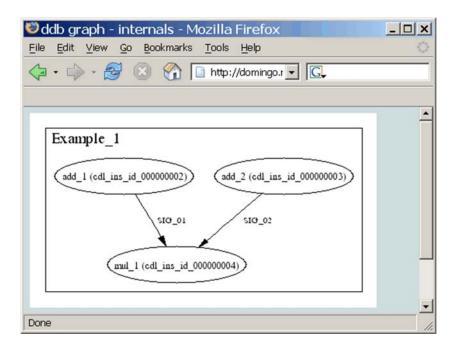

| 3.8  | Hierarchical view of a system                                                                                                                                                                                          | 47 |

| 3.9  | Visualisation of the data flow                                                                                                                                                                                         | 48 |

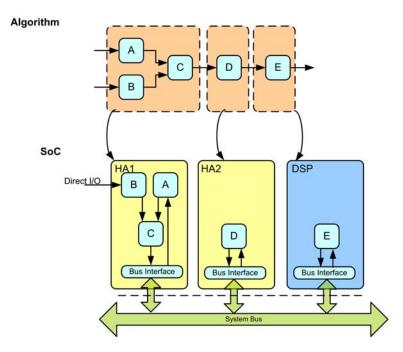

| 4.1  | HW/SW partitioning of an algorithm and its implementation by several hardware accelerators                                                                                                                             | 54 |

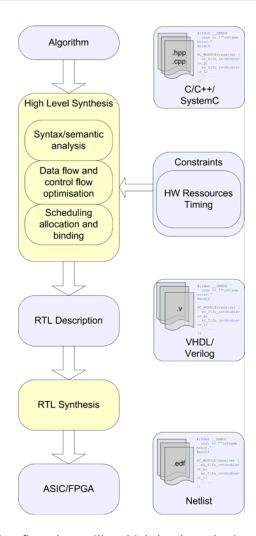

| 4.2  | Design flow that utilises high level synthesis and RTL synthesis                                                                                                                                                       | 55 |

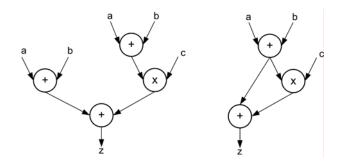

| 4.3  | Elimination of the common sub expression $a+b$                                                                                                                                                                         | 56 |

| 4.4  | Tree height reduction of the expression $z=a+b+c+d$                                                                                                                                                                    | 56 |

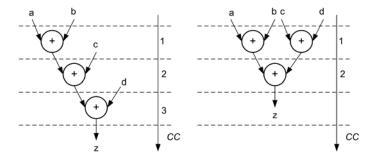

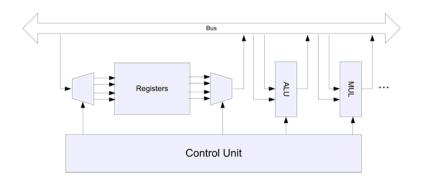

| 4.5  | Multiplexer architecture                                                                                                                                                                                               | 57 |

| 4.6  | Bus architecture                                                                                                                                                                                                       | 57 |

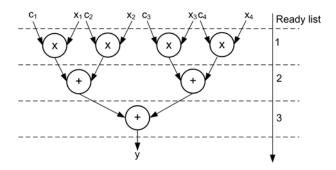

| 4.7  | Ready lists for the DDG of a filter function                                                                                                                                                                           | 58 |

| 4.8  | Optimal schedules with different resource constraints                                                                                                                                                                  | 59 |

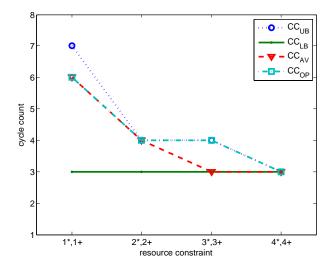

| 4.9  | Comparison of cycle count estimations                                                                                                                                                                                  | 60 |

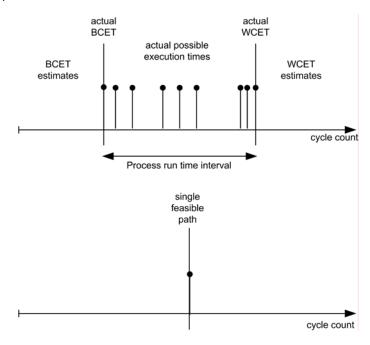

| 4.10 | Execution time of different execution paths of a function                                                                                                                                                              | 61 |

| 4.11 | Determining feasible paths of a CFG                                                                                                                                                                                    | 62 |

| 4.12 | Execution time profile for the predcase 1 function from the $MPEG$ algorithm                                                                                                                                           | 65 |

| 4.13 | Simple example of a CFG. The basic blocks are annotated with the corresponding cycle count that is needed to execute the internal DFG                                                                                  | 65 |

| 4.14 | Control flow graph with four different selections of the default edges indicated by                                                                                                                                    |    |

|      | bold edges                                                                                                                                                                                                             | 67 |

| 4.15 | A section of the control flow graph of the <i>predcase2</i> function. On the left side the edges of the shortest path are highlighted in bold. On the right side edges of the longest path search are highlighted bold | 69 |

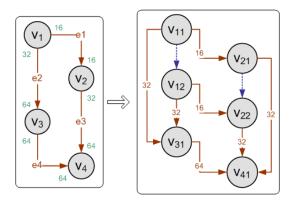

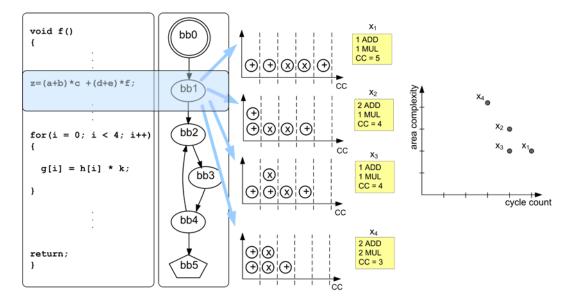

| 5.1  | Design alternatives for an algebraic expression                                                                                                                                                                        | 78 |

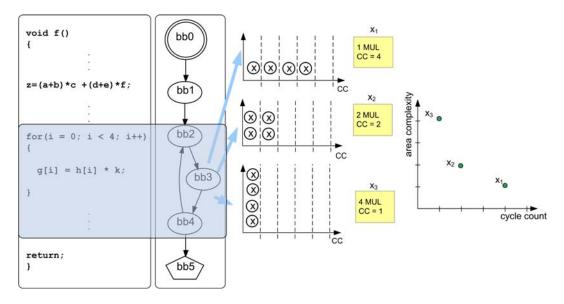

| 5.2  | Design alternatives with loop unrolling                                                                                                                                                                                | 79 |

| 5.3  | Multi-objective Optimisation                                                                                                                                                                                           | 80 |

| 5.4  | Design space for area and timing trade-off                                                                                                                                                                             | 81 |

| 5.5  | Chromosome representation of a design point for the genetic algorithm                                                                                                                                                  | 82 |

| 5.6  | Structogram of a genetic algorithm.                                                                                                                                                                                    | 82 |

| 5.7  | Rank ordering of a population                                                                                                                                                                                          | 83 |

List of Figures xvii

| 5.8  | Directed acyclic dominance graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

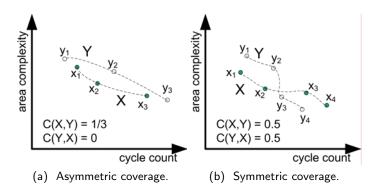

| 5.9  | Different coverage scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86  |

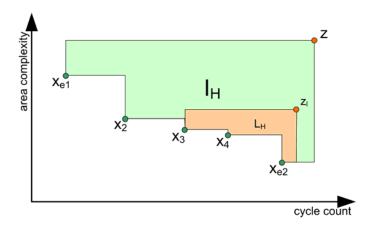

| 5.10 | Hyper volume indicator $\mathcal{I}_H$ and local hyper volume indicator $\mathcal{L}_H$ for a Pareto front.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87  |

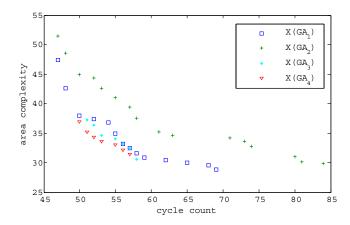

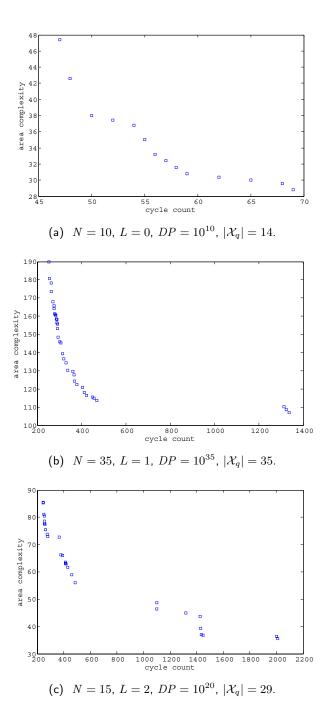

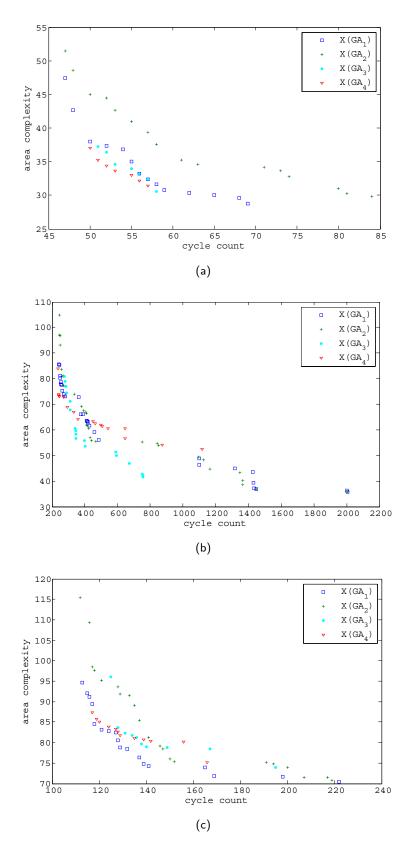

| 5.11 | Approximation sets for the CFG13 derived with $GA_1$ , $GA_2$ , $GA_3$ , and $GA_4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89  |

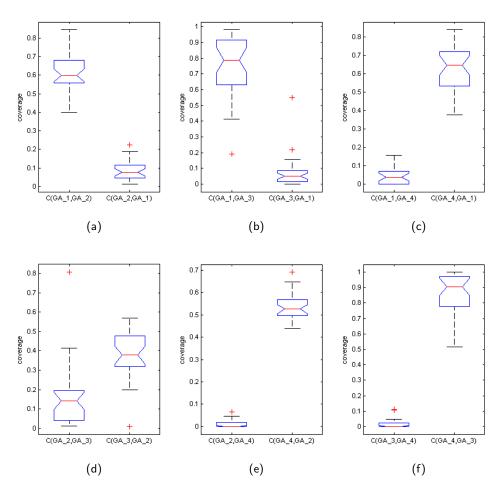

| 5.12 | Box plots of the achieved coverage of the genetic algorithms for the control flow graph CFG <sub>23</sub> . The coverage of $\mathcal{X}_q(GA_1)$ compared to $\mathcal{X}_q(GA_2)$ , $\mathcal{X}_q(GA_3)$ , and $\mathcal{X}_q(GA_4)$ is depicted in the first row (Figure 5.12a, Figure 5.12a, and Figure 5.12a. The coverage of $\mathcal{X}_q(GA_2)$ compared to $\mathcal{X}_q(GA_3)$ and $\mathcal{X}_q(GA_4)$ is depicted in the second row (Figure 5.12d and Figure 5.12f). The coverage of $\mathcal{X}_q(GA_3)$ compared to $\mathcal{X}_q(GA_4)$ is presented in Figure 5.12f | 90  |

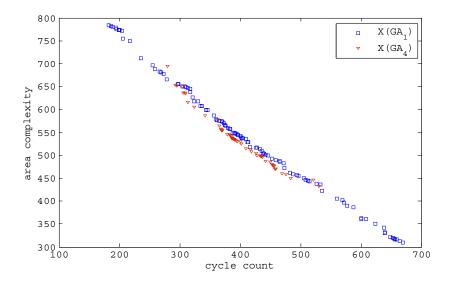

| 5.13 | Quality sets derived by the genetic algorithms $GA_1$ and $GA_4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 91  |

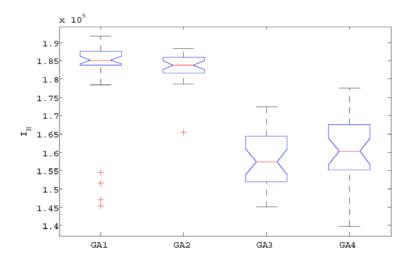

| 5.14 | Boxplot of the hyper volume indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91  |

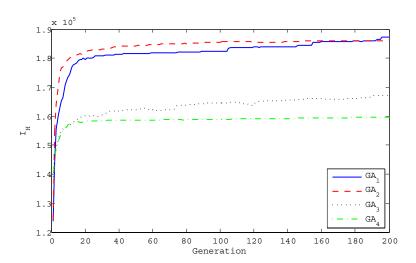

| 5.15 | Convergency of the Hyper volume indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92  |

| 5.16 | Examples for different Pareto fronts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 93  |

| 5.17 | Software defined radio platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94  |

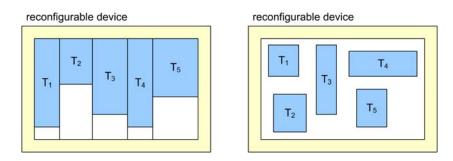

| 5.18 | 1D and 2D area models for the partial run-time reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95  |

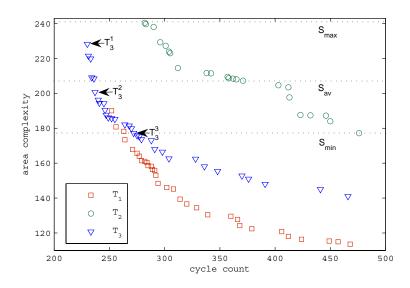

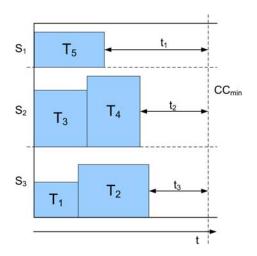

| 5.19 | Slot size and task variant determination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97  |

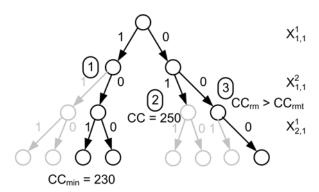

| 5.20 | Decision tree for the branch and cut algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98  |

| 5.21 | Remaining cycle count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98  |

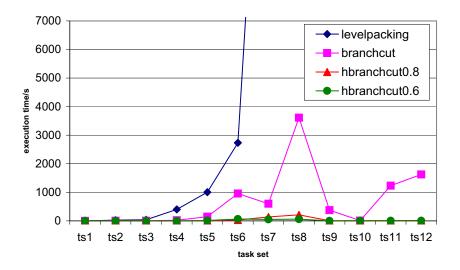

| 5.22 | Execution time of the scheduling algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 99  |

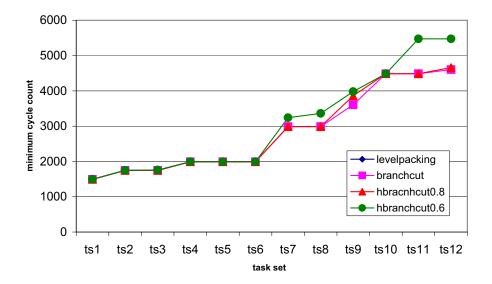

| 5.23 | Optimisation results of the scheduling algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100 |

| C.1  | Structure of the IF representation of the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 111 |

| D.1  | Convergency of the ranked fonts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127 |

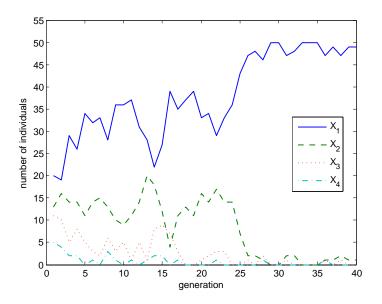

| D.2  | Evolvement of the population over several generations of the genetic algorithm $\mathrm{GA}_4$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 128 |

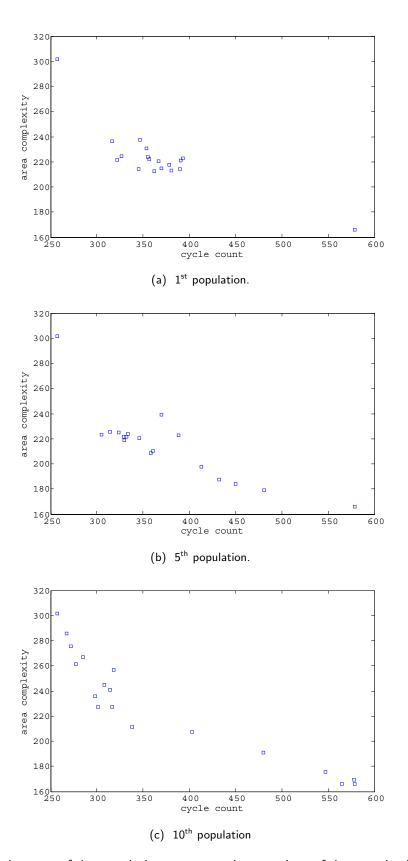

| D.3  | Examples for Pareto fronts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 129 |

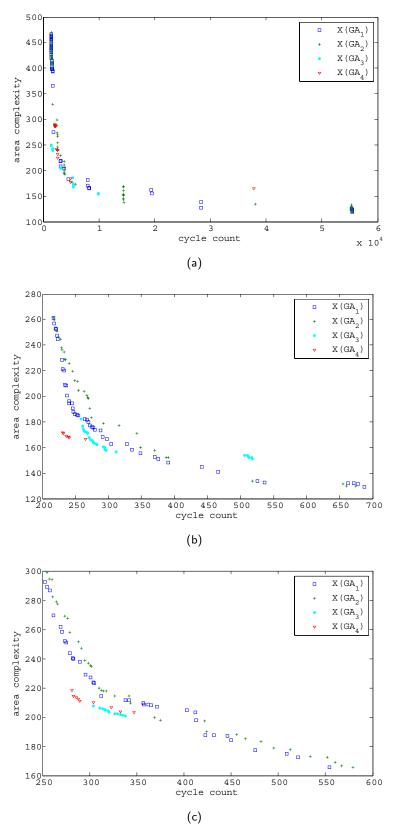

| D.4  | Examples for Pareto fronts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 130 |

# LIST OF TABLES

| 1.1 | Performance development of processors                                                                                                                     | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Set of operators                                                                                                                                          | 29 |

| 2.2 | Indication of metrics regarding its affinity to HW or SW, $\uparrow$ indicates an affinity for high values and $\downarrow$ an affinity for small values. | 31 |

| 2.3 | Metrics for control, memory usage, cyclomatic complexity, and parallelism                                                                                 | 33 |

| 4.1 | Upper bound for ready list with different resource constraints                                                                                            | 58 |

| 4.2 | Average cycle count based on statistics                                                                                                                   | 59 |

| 4.3 | Cycle count derived with optimal schedules                                                                                                                | 60 |

| 4.4 | BCET and WCET execution time prediction                                                                                                                   | 63 |

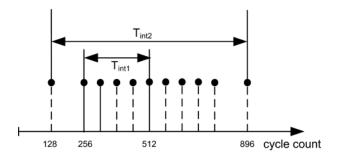

| 4.5 | Number of feasible paths and process run time interval                                                                                                    | 64 |

| 4.6 | Minimal and maximal timing for testing of the <i>predcase2</i> function                                                                                   | 70 |

| 4.7 | Gate count for functional units in dependance on the bit widths $n$ and $m$ of its inputs                                                                 | 72 |

| 5.1 | Features of the various genetic algorithms $GA_1,\ldots,GA_4$                                                                                             | 87 |

| 5.2 | Performance comparison of the different optimisers for the control flow graph CFG <sub>13</sub> .                                                         | 88 |

## 1 INTRODUCTION

"The beginning is the most important part of the work."  $$\operatorname{PLATO}$$

In today's world embedded systems are nearly everywhere. Persons of a developed nation get in touch with about 100 embedded systems per day. An embedded system is a special purpose computer such as for example cell phones, anti-block brakes, camcorders, digital cameras, DVD players, or washers. Usually, they execute a single program repeatedly and continually react to changes in the system's environment and must respond in real-time. Complexity of such systems varies from rather simple devices to very complex ones. For example a BMW745i utilises more than 100 micro processors with about 2 Mio. lines of source code which are responsible for the engine control, break system, airbag deployment, door locks, and the entertainment system [109]. The design goals of such systems are rather demanding and include low unit cost and Non Recurring Engineering Cost (NRE), small size, high performance, low power, and high flexibility.

### 1.1 Motivation

The success of embedded systems is based on the enormous advances in system integration. Gordon Moore, one of the founders of INTEL, presented in a talk in 1965 his investigations about the number of integrated transistors on recently fabricated integrated circuits. He presented that the number of integrated transistors on a device doubles each year. This effect is nowadays slowed down to about 18 months, but holds on and is called Moore's Law [123]. In the beginning, the higher integration density, by reducing the gate length of the transistors, allowed for increasing processing frequency and therefore more processing power. Whereas now the reachable higher density is used for example to enlarge memory like caches, this does not directly influence processing performance anymore. In the case of cache enlargement only the speed of read and write operation is increased. For example, the benchmarks from the Standard Performance Evaluation Corporation (SPEC) [70] of a Pentium-III at 500MHz compared to a Pentium-III at 1000MHz has increased by a factor of 2.5 for integer and by a factor of 2 for floating point operations, whereas the corresponding number of transistors has tripled from about 10 Mio. to 30 Mio. to achieve this performance increase (Table 1.1). Although Moore's law is expected to be limited ultimately by hard physical or economical boundaries, it still holds and the International Technology Roadmap for Semiconductors in 2005 [58] predicts a further validity until 2020.

One of the most challenging areas for the design of embedded systems are modern communication systems. Here, particularly in the wireless domain, complexity of the algorithms grows

2 1 Introduction

| Processor           | Transistors | SPEC integer | SPEC float |

|---------------------|-------------|--------------|------------|

| Pentium-III 500MHz  | 9.5 Mio.    | 20.6         | 14.7       |

| Pentium-III 1000MHz | 28.5 Mio.   | 46.8         | 32.2       |

Table 1.1: Performance development of processors.

at an astounding rate. While the analog first generation (1G) of wireless communication has been dedicated merely to voice communication, the digital systems of the second generation (2G) and even more the third generation (3G) support additionally data communication at rates up to several Mbps. Here, a raise of computational complexity from one technology generation to the next one by a factor of 1000 has been observed. This rate is so high that the demand of algorithmic complexity now significantly outpaces the above discussed growth in available computational performance of the underlying silicon implementations (Figure 1.1). Also the increase of battery capacity stays far behind the actual needs of portable devices. Furthermore, algorithmic

Figure 1.1: Algorithmic complexity outpaces silicon complexity.

complexity even more rapidly outpaces design productivity, expressed as the average number of transistors designed per staff/month [57, 162, 163]. In other words, current approaches for the design of a wireless embedded system are proving inadequate in the struggle to keep up with system complexity. In 1999 Sematech [3] called this problem *design productivity crisis*, which is nowadays well known under the name productivity gap or *design gap* (Figure 1.2).

The Electronic Design Automation (EDA) industry has faced this trend the last years and is nowadays confronted with even more design technology gaps. For example test cost has grown exponentially relative to manufacturing cost, verification engineers outnumber design engineers [16,80], and security applications need even more processing performance.

Additionally, economical aspects like time-to-market are very decisive, especially in markets where

1.1. Motivation 3

Figure 1.2: Design productivity crisis.

Figure 1.3: Deployment of new electronic design automation technologies by the industry and the life cycle of a new technology.

product cycles of 18 months can be found. Here, launching a product six months early, triples profits, whereas being six-months late results in breaking even [17].

The EDA industry observed this effect already several times in the past and overcame it by new technologies like test pattern generation, place and route, synthesis of RTL code to gates, placement, and global routing by physical synthesis (Figure 1.3). A more detailed look into the deployment of new technologies by the industry shows that firstly the productivity decreases (*The teething problem*), and after a time of getting used to the new technology a period of high productivity follows (*The youth*). Finally, a new technology gets well established (*The old age*) in the product development process.

Currently, industry is in such a phase out period. Thus many new concepts so far have been proposed to solve the problem as there are for example optimal hardware/software co-design, co-simulation on different design levels, and new design languages to overcome the fragmentation

4 1 Introduction

of the design process. One of the latest combined efforts of the EDA industry focusses on electronic system level design. The key here is to move to higher levels of abstraction, to start at the architectural level and refine down from there. The tools to support this will have to simultaneously address large, high-level blocks such as processors and large peripherals, and the gate-level details. Additionally, integration of hardware and software should be supported as well as capabilities for optimisations regarding system throughput and power consumption.

### 1.2 Embedded System Design

Embedded systems incorporate Hardware (HW) and Software (SW) parts which affect the design process itself resulting in a HW/SW co-design flow. Due to high complexity of such systems it is not possible to derive directly an efficient implementation. Therefore, the design of an embedded system incorporates a number of abstractions, ideally allowing for a smooth refinement process. The refinement of such a system considers communication and computation separately. Here, the levels of abstraction can be identified for time (from untimed to timed) or the granularity of data (from complex data types to simple types). In the following common models of abstraction are described (Figure 1.4):

Specification Model: Usually, at first a specification model of the algorithm is written which is free from implementation details. It is untimed and models data transfer through accesses to variables. Depending on the domain of application, specific models of computation (finite state machine, discrete event, synchronous reactive) are used for an efficient algorithm description. For example in the wireless domain algorithms are usually described by a Synchronous Data Flow Graph (SDFG) at first introduced by E.A. Lee and D.G. Messerschmitt [112] in 1987 where functions (A,B,C,D,E as depicted in Figure 1.4) inter-communicate with fixed data rates.

Transaction-Level Model (TLM): Transaction-level modelling has been proposed in the year 2000 by T. Grötker [165]. In a transaction level model the details of communication among computational components are separated from the details of computation components. Communication is modelled by channels while transaction requests take place by calling interface functions of these channel models. Unnecessary details of the communication and computation are hidden. Here, the main advantage of this model is to speed up simulation.

Bus-Functional Model (BFM): The BFM is a model that can generate different bus transactions for a given device which is not limited to microprocessor. Here, protocol channels are used that are time/cycle accurate and pin-accurate. Note, it is not necessary that all channels have to be modelled at this level. A heterogenous approach may be applicable.

Cycle-accurate computational model: Here, the computation within functional blocks is cycle accurate whereas the communication is modelled on a higher level of abstraction. The hardware is modelled on Register Transfer Level (RTL). This means that the behaviour is defined in terms of the flow of signals or transfer of data between registers, and the logical operations performed on those signals. Furthermore, general purpose processors are modelled in terms of cycle accurate instruction set architectures.

Virtual Prototype (VP): A virtual prototype enables earlier development and testing of the software. In this technique, SW reflects the behaviour of the HW and implements the HW interface to the SW, as it will be realised later in HW. Such a VP can be implemented faster than the HW itself because all the HW implementation details specific to the chosen technology can be neglected and high-level description languages can be used instead of hardware description languages. A first implementation of a VP by J. Cockx [40] in the year 2000 has for the most part focused on its use in the hardware/software co-simulation of the embedded system. While this early effort was targeted towards increasing the efficiency and quality of the design process through novel modifications of the co-simulation process, a transition method (even a manual one) from an algorithmic description to the VP was not shown. First automatic generation approaches for VPs are presented by A. Hemani et al. [77] in the year 2000 and A. Hoffmann and H. Meyr [80] in the year 2002. A further automatic VP generation approach is presented in [20, M. Holzer et al.]<sup>1</sup>

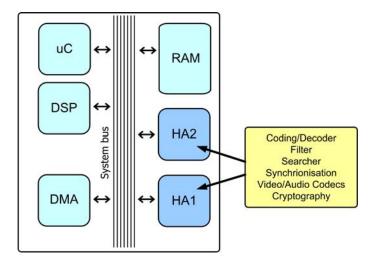

Implementation model: Such a model has cycle-accurate communication as well as computation. The components are defined in terms of their register transfer or instruction set architecture. An implementation model may utilise a heterogenous architecture that consists of processing elements (DSPs, ASICs), memory, and a bus system. As stated before, in the last decades new development approaches and tools have allowed for the design of ever more complex hardware. Higher integration and thus increasing miniaturisation have led to a shift from using distributed hardware components towards heterogeneous System-on-Chip (SoC) designs [26]. Such SoCs consisted at first only of a single processor, HW accelerators, memory and a bus system. Rather simple HW accelerators emerged to more sophisticated Application Specific Integrated Processors (ASIP) [81]. The integration of an entire product onto a single complex IC may include, one or more processor core(s) ( $\mu$ Ps or DSPs), memory, peripherals, custom blocks, reconfigurable blocks, and busses. State of the art SoCs incorporate multiple processing cores. Even further research is going on by replacing the classical interconnection structure of standard bus systems with distributed communication structures (network on chip [94]).

#### 1.2.1 Design Languages

For the design of a system consisting of hardware and software parts different design languages are applicable on different abstraction levels (Figure 1.5). The system design starts with design languages where general concepts of a product are described. Mostly languages with strong graphical visualisation capabilities are used for this task like the Unified Modelling Language (UML) [6] or the Specification and Description Language (SDL) [5]. Furthermore algorithmic descriptions usually start with languages embedded in special design environments, that support the designer with pre-defined libraries of system components (e.g. filter, modulation schemes, channel models for signal processing applications).

Based on its widespread use also languages like C or Java are found for describing systems on

<sup>&</sup>lt;sup>1</sup> Cited work which I authored or co-authored is indicated with M. Holzer et al.

6 1 Introduction

Figure 1.4: Design flow for embedded systems.

Figure 1.5: Hardware/software design languages covering different levels of abstraction.

architectural level or building a virtual prototype [76, 169]. On the lowest level of abstraction assembler and hardware description languages like VHDL, Verilog are deployed. One of the last major contributions for the co-design of HW/SW systems is SystemC [165]. This language has been introduced in 1999 by the Open SystemC Initiative (OSCI) [2] and is supported by many EDA companies (ARM, Cadence, CoWare, Synopsys, Mentor Graphics, NEC, Fujitsu). SystemC is an open C++ library which allows for the description of a system on different abstraction levels while staying in the same design language (one-code paradigm). The first version of SystemC provides hardware related concepts like concurrency and signals. Version 2 generalises the hardware related communication structures to so called channels. Within Version 3 the abilities for

incorporating the features of an operating system will be provided. Version 1 and 2 are nowadays available and ratified as IEEE Standard, the release of Version 3 has been postponed several times. Instead, OSCI concentrated its work on enriching the available versions of SystemC with special libraries (Verification Library, Transaction Level Modelling Library). Furthermore, extensions of SystemC-AMS targets the co-simulation of digital and analogue systems.

#### 1.2.2 Design Tasks

Various design tasks have to be considered for the implementation of an embedded system. Typically, a design methodology formalises the implementation flow. Such a design methodology is a set of abstraction levels together with a set of transformation rules which transform one abstraction level into another [64]. Most typical tasks for the HW/SW co-design are listed in the following:

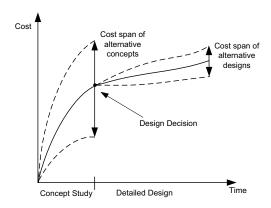

• System Characterisation Early design decisions have a huge impact on the final system performance [127], about 90% of the overall costs are determined in the first stages of a design. Figure 1.6 depicts the evolution of the cost during the development time [14] where it can be seen that early design decisions have a much higher resulting cost span than design decisions taken at the end of the development time. Therefore, it is of paramount

Figure 1.6: Up to 90% of the costs are determined at the first part of the design.

importance to base the design decisions on reliable characteristics. Those characteristics of the code are called metrics and can be identified on different levels of abstraction. The terms metric and measure are used as synonyms in literature whereas a metric is in general a measurement which maps an empirical object to a numerical object.

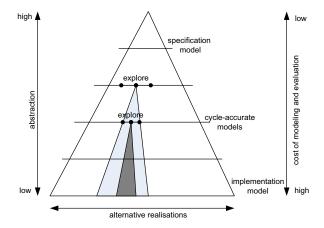

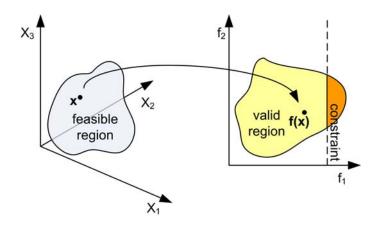

Design Space Exploration: Design Space Exploration (DSE) refers to the process of investigating implementation variants regarding their optimal solution. In the case of multiple objectives like minimisation of time, area, and power not only a single optimal solution exist.

8 1 Introduction

Here, a set of equally acceptable design points has to be considered for the further development flow. Due to the high system complexity manual design exploration approaches lead to suboptimal solution. Thus, in order to gain full advantage of the design space exploration this task has to be performed automatically with additional tools that allow for discovering trade-offs on each level of abstraction (Figure 1.7).

Figure 1.7: Design space exploration on different levels of abstraction.

- Floating-point to fixed-point conversion: The algorithmic model usually uses floating-point

formats in order to disburden the designer from having to take numeric effects into consideration. At the end of the design process only fixed-point numeric formats are used.

Thus, during the design process it is necessary to perform a conversion from floating-point

to fixed-point data types [133].

- *HW/SW partitioning*: HW/SW partitioning can in general be described as the mapping of the interconnected functional objects that constitute the behaviour of the algorithm onto a chosen architecture model [105, M. Holzer et al.].

- Platform based design: Platform-based design focusses on a specific application domain.

The platform embodies the hardware architecture, embedded software architecture, and design methodologies for IP authoring and integration. Derivative designs may be rapidly implemented from a single platform that has a fixed part and a variable part [37, 101].

- High Level Synthesis (HLS): One of the trends for boosting design productivity is increasing

the level of abstraction. The majority of modern design flows describe the system register

transfer level. Furthermore, advances to higher abstraction levels are at the one hand provided by languages for simulation (e.g. SystemC) and on the other hand by the capability

of high level synthesis. High level synthesis refers to the process of deriving an RTL description from and algorithmic description. This process has been investigated by many research

projects like for example in the SPARK [71] environment and is also adopted to commercially

available tools (behavioural compiler from SYNOPSYS, CatapultC from Mentor Graphics). A survey of high level design synthesis techniques is given by Jantsch [172].

- Verification: Verification is the process of evaluating a system or component to determine

whether the products of a given development phase satisfy the condition imposed at the

start of the phase. This correctness can be verified by simulation or formal methods like for

example equivalence-check [20, M. Holzer et al.].

- Rapid prototyping: Rapid Prototyping describes the fast development of a working entity

to prove that a new theory could really be applied and to have a first impression of the

development effort for turning it into a product. Due to the high complexity of modern

systems prototyping has become nearly as challenging as designing the product itself [147,

148].

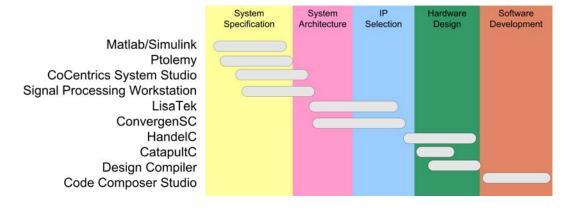

In Figure 1.8 several tools from different vendors are shown and their coverage of abstraction levels. Especially in the market of EDA tools two big players like Synopsys and Cadence have dominated the market. Their tools mainly focus on the VHDL to RTL synthesis and place and route tasks. Other emerging companies have tried to tackle specific problems as mentioned before like Coware (architecture exploration).

Figure 1.8: Overview of the EDA tool support for the entire design process.

Despite all the efforts of solving specific tasks of the design flow, the problem of integrating all those tools together, in order to provide a seamless design flow has been neglected. A designer is forced to integrate those tools in their specific order into a design flow.

### 1.3 Contributions and Outline of the Thesis

One of the major capabilities of accelerating the design flow is to focus on tools and methods that are concerned with exploring a design on the highest possible level of abstraction. The contribution of this thesis is the the efficient generation of design trade-offs regarding area and execution time. This is based on the derivation of design characteristics with static methods and

1 Introduction

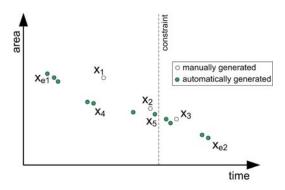

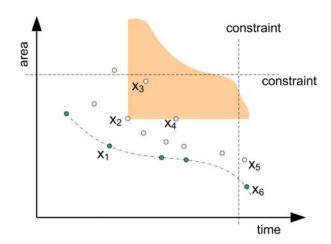

the estimation of implementation properties. Design space exploration currently reveals several disadvantages as already in the previous section mentioned. This design task is usually manually performed or with low support of tools. Hence, it is a time consuming process and thus it is usually only affordable to discover only a small portion of all possible design alternatives. In this thesis a novel methodology is presented that generates Pareto optimal design alternatives which cover the design space to a high extend. Specifically, the efficient generation of design trade-offs allows for an easy identification of extrema, i.e. design solution with maximum/minimum execution time  $(x_{e1} \text{ and } x_{e2} \text{ in Figure 1.9})$ . Another aspect of the presented design space exploration concerns the treatment of loops. Here, the proposed approach identifies optimal solutions regarding the loop unrolling factors (in Figure 1.9 solution  $x_4$  is an implementation with less area and time effort than  $x_1$ ). Finally, the proposed automatic approach discovers a high density of equally acceptable solutions. Thus, for a given constraint concerning for example execution time a design alternative can be identified that suits optimally (in Figure 1.9 design alternative  $x_5$  requires less area than  $x_2$  and still adheres to the given execution time constraint). Certainly, design space exploration has to cope with several additional cost functions like for example power, complexity, verification effort, or implementation effort. Nevertheless, as described before even only the consideration of time and area trade-offs allows for a significant improvement of the design flow.

Figure 1.9: Automatic design space exploration versus manual approach.

This thesis is based on the following publications, which will be referred to in the overview of the chapters at the end of this section.

- M. Holzer, B. Knerr, P. Belanović, and M. Rupp, "Efficient Design Methods for Embedded Communication Systems," EURASIP Journal on Embedded Systems, Volume 2006, pages 1 - 18, 2006.

- M. Holzer, B. Knerr, and M. Rupp, "Design Space Exploration for Real-time Reconfigurable Computing", in Proc. Asilomar Conference on Signals, System, and Computers, Pacific Grove, CA, USA, November 2007.

- M. Holzer, B. Knerr, and M. Rupp, "Design Space Exploration with Evolutionary Multiobjective Optimisation," in Proc. Symposium on Industrial Embedded Systems (SIES), pages 126 - 133, Lisbon, Portugal, July, 2007.

- M. Holzer, B. Knerr, and M. Rupp, "Structural Verification in Minimal Time," in Proc. System on Chip, pages 151 154, Tampere, Finland, November, 2006.

- M. Holzer and B. Knerr, "Pareto Front Generation for a Tradeoff between Area and Timing," in Proc. Austrochip 2006 Tagungsband, pages 131 - 134, Vienna, Austria, October, 2006.

- M. Holzer and M. Rupp, "Static Code Analysis of Functional Descriptions in SystemC," in Proc. DELTA 2006 Third IEEE International Workshop on Electronic Design, Test and Applications, pages 243 - 248, Kuala Lumpur, Malaysia, January, 2006.

- M. Holzer and M. Rupp, "Static Estimation of Execution Times for Hardware Accelerators in System-on-Chips," in Proc. Proceedings of International Symposium on System-on-Chip 2005, pages 62 65, Tampere, Finland, November, 2005.

- M. Holzer, P. Belanović, B. Knerr, and M. Rupp, "Automatic Design Techniques for Embedded Systems," in Proc. Proceedings of GI/ITG/GMM Workshop Modellierung und Verifikation, Munich, Germany, April, 2005.

- M. Holzer, B. Knerr, P. Belanović, G. Sauzon, and M. Rupp, "Faster Complex SoC Design by Virtual Prototyping," in Proc. Proceedings of CITSA International Conference on Cybernetics and Information Technologies, Systems and Applications, pages 305 - 309, Orlando, Florida, USA, July, 2004.

- M. Holzer, P. Belanović, B. Knerr, and M. Rupp, "Design Methodology for Signal Processing in Wireless Systems," in Proc. Informationstagung Mikroelektronik, pages 303 307, Vienna, Austria, October, 2003.

- M. Holzer, P. Belanović, and M. Rupp "A Consistent Design Methodology to Meet SDR Challenges," in Proc. 9th Wireless World Research Forum Meeting, Zürich, Switzerland, July, 2003.

The content of the individual chapters is briefly described in the following:

**Chapter 1** describes the technological advances that allow for the design of complex embedded systems. Furthermore, current design problems like the design productivity gap are highlighted. The design of embedded systems is described and a focus is given on languages and tools that are utilised within the design process. The importance of two major design tasks like system characterisation and design space exploration is shown and their capability for improving the design process.

Chapter 2 is dedicated to the characterisation of algorithms for the HW/SW co-design process. The usage of metrics for the algorithm already has quite a long history in the development of software [73,118]. Algorithmic characterisation for hardware has been mainly performed on the lowest level of abstraction (e.g. VHDL) [39]. Only a few approaches consider SystemC [7]. Thus, in this chapter a new set of structural and linguistic metrics which are specially suited to describe the features of an algorithm regarding complexity, operation reuse, and memory access, is presented [89,103, M. Holzer et al.]. A grouping of those metrics to an affinity value is presented which allows for a first identification whether a function is more likely to be mapped to specific

1 Introduction

hardware components like a DSP, micro controller or an ASIC/FPGA. Finally, the derivation of metrics and graph structures is exhibited within an example.

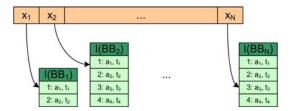

In **Chapter 3** a novel design methodology is presented that features the characterisation techniques of Chapter 2. The problem of lacking consistency within the design process has been identified by several approaches [98, 164]. Nevertheless, most of them support only the lower abstraction levels of the design process. As a basic concept of this design methodology a single system description [82, 87, 88, M. Holzer et al.] is introduced which allows for capturing the refinement process of a design starting at the highest level of abstraction (e.g. SystemC). This is based on a database model that stores the algorithm description itself and its characterisation properties that are presented in Chapter 2. Via open interfaces the communication to several existing electronic design automation tools is supported.

In **Chapter 4** estimation functions for cycle count and area complexity are discussed. The main objective for the estimation of implementation properties like area and timing has been accuracy [55, 139]. In contrast to this a new approach for estimation functions is presented in this chapter that targets the preservation of relative ordering (homomorphism) of the estimations. These estimations are based on the metrics that are presented in Chapter 2 [90, M. Holzer et al.]. Furthermore, the estimation of these properties is utilised for a detailed profiling of the execution cycle of a control flow graph. Another application of the cycle count estimation aims for the minimisation of the verification effort. Here, a novel algorithm for minimising the structural verification effort is presented [84, M. Holzer et al.].

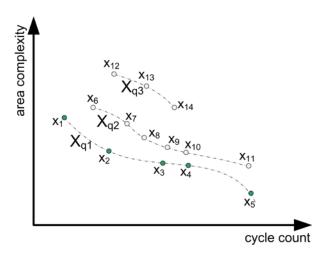

In **Chapter 5** design space exploration for trade-offs between area and timing is discussed. Traditionally, the performance of alternative designs is *manually explored* which is significantly based on the experience of the designer. *Exhaustive search* tries to identify all possible design points. This is certainly only applicable for small problems because usually the design space grows exponentially with the number of parameters and the size of the problem. Hence, heuristic approaches are most promising candidates for this optimisation problem [9, 41, 156]. In this chapter the generation of area timing trade-offs is formulated as multi-objective optimisation problem [83, M. Holzer et al.]. Here, the generation of Pareto optimal design points is shown with an evolutionary genetic algorithm that features enhanced approaches for the fitness function as well as the preservation of an equal distribution of the set of Pareto optimal points [86, M. Holzer et al.]. The performance of different fitness and elitism schemes is discussed on various control flow graphs. Finally, the design space exploration for one task is applied to run-time reconfigurable computing [85, M. Holzer et al.]. Here, a novel scheduling algorithms is presented that utilises several implementation trade-offs in order to minimise overall execution time.

Finally, **Chapter 6** summarises the main contributions of the thesis and gives an outlook to further extensions to the presented work.

## 2 SYSTEM DESCRIPTION METRICS

"Since the measuring device has been constructed by the observer, we have to remember that what we observe is not nature in itself, but nature exposed to our method of questioning."

WERNER KARL HEISENBERG

This chapter is devoted to the identification of the properties of an algorithmic description. A focus on properties is set which can be identified by static analysis of the algorithm. This means no simulation run of the algorithm is needed. These properties establish a first characterisation of the algorithm which allows for its first analysis regarding its inherent features, thus providing the possibility to compare different implementation variants quantitatively. Additionally, those properties will allow for the estimation of final implementation properties like area and timing as will be described in more detail in Chapter 4. This chapter starts with a review of metrics in the software area and their further evolvement for the hardware/software design flow. Since most of the presented metrics are heavily based on the analysis of graph structures, a basic introduction to graph theory is given. This is followed by a system decomposition into a hierarchical structure of various graphs. Next, a set of of system description properties is presented. Those properties are grouped into properties related to structure or linguistic features. The already existing software metrics cyclomatic complexity and program vocabulary are reviewed in the context of hardware description. Furthermore, the existing hardware related metrics parallelism is extended towards an operation dependent parallelism metric. Furthermore, the vocabulary match between an algorithm and the vocabulary of the target hardware is newly introduced as well as a refinement of the memory access metric regarding read and write accesses. A new measure for the affinity of an algorithm to be implemented in hardware or software is presented by grouping together a subset of the presented metrics. Finally, the utilisation of the metrics that are highlighted in this chapter is demonstrated within an example design of a UMTS cell searching algorithm.

### 2.1 Overview

Since the first programming languages appeared, the interest of the software engineering community in the measurement of software properties emerged and is ongoing until nowadays [153]. A software metric is defined as a numerical rating with the purpose to measure properties like complexity, reliability, length, quality, or performance of the algorithm. In this context metrics are at first defined by a measurement procedure which assigns an entity, e.g. a software program, a numerical value. In a second step this value can be interpreted as a measure for a property like complexity. More formally spoken this is a mapping of an empirical object to a numerical object.

Note, that the term metric has in the context of software engineering not that exact mathematical definition as a distance measure, even if the metrics presented in this thesis share properties like to be non negative. One of the main targets which emphasises the usability of a metric, is that the mapping procedure preserves the relations within a homomorphism<sup>1</sup>. This means if a metric is used as quantitative expression of a feature like complexity of a function, then a metric that describes this feature should preserve the relations. So if an implementation of an algorithm  $f_1$  is considered empirically more complex than the implementation  $f_2$ , then a derivation of a complexity metric with a function g should preserve this circumstance  $g(f_1) > g(f_2)$ .

The usage of metrics within the design process are manyfold: The identification of algorithm properties allows to conduct the design process. This is usually achieved with metrics that describe the quality, complexity, and readability of an implementation. Other metrics might describe data and control dependencies, granularity, parallelism, and regularity [166]. Another usage of metrics can be identified within the estimation of final properties of the implementation. Implementation properties might be for example code size, timing, or memory usage. Estimations that concern the development process itself are the volume of a project or the expected implementation effort. Hence, gathering properties of an algorithm leads to a deeper insight and understanding, thus allowing for a comparison of different implementations of one algorithm against each other.

The first target of this chapter is to identify metrics for the HW/SW codesign flow which allow for a first characterisation. A second target is to provide a fundament for Chapter 4 where the estimation of implementation features like area and time is based on these metrics.

The usage of these metrics already has quite a long history in the development of software. Different metrics have been defined for functional programming languages like Pascal or C. One of the earliest proposed software metrics is the measure Lines of Code (LOC) which has been mainly used as complexity measure and is still being used today [27, 137].