Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR INFORMATIK

**Faculty of Informatics**

# Elaboration of a Fault-Tolerance Strategy for Space-borne Digital Signal Processing Applications

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## Technische Informatik

eingereicht von

## Bernhard Fuchs, BSc.

Matrikelnummer 0527603

an der Fakultät für Informatik der Technischen Universität Wien

> Betreuung: Ao.Univ.-Prof. Dipl.-Ing. Dr. techn. Andreas Steininger Mitwirkung: Dipl.-Ing. Dr. techn. Manfred Sust - RUAG Space GmbH Austria

Wien, 19.03.2012

(Unterschrift Verfasser)

(Unterschrift Betreuung)

## Elaboration of a Fault-Tolerance Strategy for Space-borne Digital Signal Processing Applications

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

## **Computer Engineering**

by

## Bernhard Fuchs, BSc.

Registration Number 0527603

to the Faculty of Informatics at the Vienna University of Technology

> Advisor: Ao.Univ.-Prof. Dipl.-Ing. Dr. techn. Andreas Steininger Assistance: Dipl.-Ing. Dr. techn. Manfred Sust - RUAG Space GmbH Austria

Vienna, 19.03.2012

(Signature of Author)

(Signature of Advisor)

# Erklärung zur Verfassung der Arbeit

Bernhard Fuchs, BSc. Pfeilgasse 3/13, 1080 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

# Acknowledgements

It is a pleasure to thank the many people who made this thesis possible. First of all i want to thank my advisor Ao.Univ.-Prof. Dipl.-Ing. Dr. techn. Andreas Steininger. With his enthusiasm, his inspiration, and his great efforts to explain things clearly and simply, he helped to make computer science fun for me.

Secondly, i want to thank Dipl.-Ing. Dr. techn. Manfred Sust for his excellent support in all matters during the whole time. I would have been lost without him. I also want to thank all my colleagues at RUAG Space Austria for their kind support, reviewing and guidance. This has been of great value in this study.

I wish to thank Karin Larnhof for helping me get through the difficult times, and for all the emotional support, entertainment, and caring she provided.

Lastly, and most importantly, I wish to thank my parents, Christa Fuchs and Anton Fuchs. They bore me, raised me, supported me, taught me, and loved me. To them I dedicate this thesis.

## Abstract

Programmable Digital Signal Processing (DSP) is of paramount importance for the success of contemporary space missions in support of earth observation, astro-sciences and telecommunications. The present thesis aims at contributing to solving the problem of combining intrinsically contradicting requirements such as high signal processing performance, data throughput and flexibility on the one hand with robustness and high availability in the hostile space environment on the other. For economic reasons, the problem is tackled on systematic rather than technological level giving preference to pure software solutions implemented on commercial off-the-shelf (COTS) processing platforms. The applicability of commercial components to space applications is very limited due to ionizing radiation which may cause permanent modifications of the used materials and consequently of the electrical characteristics, referred to as total-ionizingdose (TID) effects, as well as single-event effects, experienced as soft errors in form of bit-flips or detrimentally as destructive latch-ups. Consequently, spaceborne signal processors are either fast but highly optimized for particular applications, thus, inflexible or programmable, slow and based on outdated semi-conductor technologies and processor architectures. The latter is due to the fact that for a commercial component to become a real space component it must have ample heritage, be screened or even modified for satisfying space-quality assurance requirements and it must be applied long enough to justify these investments. On the other hand, modern deepsub-micron processes are not only superior with respect to low capacitances and, thus, high processing speed but also with respect to TID and latch-up insensitivity so that they can be easier qualified for space. However, the vulnerability with respect to single-event upsets remains, resulting in intolerably low system availability.

The objectives of the present thesis have been the selection of a modern programmable DSP as well as the identification, derivation, evaluation and experimental validation of fault-tolerance (FT) mechanisms such as software-based FT, an external FT-controller as well as a combination thereof, to be applied to this component in order to establish a spaceborne DSP-system satisfying payload dependability requirements. Typical applications of such a system are data and image processing, including filtering, decimation, coding and spectral analysis. Careful selection of FT-methods as well as optimal alloying of FT- and DSP-algorithms has been shown to be crucial for maintaining the full performance of either algorithm class and for ensuring software-product maintainability. Statistical measurements performed with the most promising candidate FT-mechanisms integrated along with typical DSP-algorithms have shown that software-only solutions, although economically attractive, fail in providing the required

availability in combination with the desired processing power, while these goals can be fully met, if software FT-techniques are combined with an external FT-controller.

## Kurzfassung

Programmierbare digitale Signalverarbeitung (DSP) ist von außerordentlicher Bedeutung für den Erfolg von Weltraummissionen zu Zwecken der Erdbeobachtung, astrophysikalischen Forschung und Telekommunikation. Die vorliegende Arbeit liefert wesentliche Beiträge, bestehende Fortschrittsbarrieren, bewirkt durch die angesichts der Umweltbedingungen im Weltraum einander grundlegend widersprechenden Anforderungen von hoher Prozessorleistung, gepaart mit Flexibilität einerseits und hoher Zuverlässigkeit und Verfügbarkeit andererseits, zu überwinden. Aus wirtschaftlichen Gründen wird nicht auf neue Halbleitertechnologien gesetzt sondern auf Systemebene eingegriffen, wobei vorerst reine Software-Lösungen zur Anwendung auf Standard-Prozessorplattformen der Vorzug gegeben wird. Der Gebrauch von Standard-Elektronik im Weltraum ist aufgrund der dort herrschenden ionisierenden Strahlung nur sehr eingeschränkt möglich. Neben permanenten Veränderungen der mechanischen und elektrischen Eigenschaften durch Dosis-Effekte und Bauteilzerstörung durch Latch-Ups, sind so genannte Single-Event-Effekte, die in Form spontaner Bit-Fehler wahrgenommen werden, von Bedeutung. Aus diesen Gründen steht leistungsfähige weltraumtaugliche Signalverarbeitungselektronik fast ausschließlich nur in Form von hochspezialisierten integrierten Schaltungen zur Verfügung, während programmierbare, flexible Signalprozessoren auf veralteten Technologien beruhen und daher bei weitem nicht den Anforderungen gerecht werden können. Zum Einsatz veralteter Technologien kommt es wegen des in sie bestehenden Vertrauens und der langen Dauer einer Komponentenqualifikation, sowie wegen der wirtschaftliche Notwendigkeit, einmal für den Weltraum qualifizierte Bauelemente möglichst lange einzusetzen. Allerdings haben technologische Verbesserungen zur Erhöhung der Taktraten digitaler Bausteine auch zu einer Verringerung von Dosiseffekten und Latch-Ups geführt, sodass moderne Komponenten leichter für Weltraumanwendungen qualifiziert werden könnten, wären sie nicht nach wie vor empfindlich in Bezug auf Single-Event-Effekte (SEEs).

Ziel der vorliegenden Arbeit war es, moderne Signalprozessoren in Bezug auf ihre Weltraumtauglichkeit zu untersuchen, eine potentiell geeignete Komponente auszuwählen sowie nach Software-Algorithmen zur Erhöhung der Fehlertoleranz (FT) im Zusammenhang mit Single-Event-Effekten zu forschen. Dazu wurden sowohl reine Soft- und Hardware-Lösungen wie auch auch ein Hybridkonzept theoretisch untersucht sowie Messungen an einer Hardware-Realisierung durchgeführt und evaluiert. Das Hauptanwendungsgebiet einer derartigen DSP-Plattform liegt in den Bereichen der Datenkompression und Bildverarbeitung und umfasst unter anderem Filterung, Dezimation, Kodierung und Spektralanalyse. Da es bei diesen Anwendungen um größtmöglichen Datendurchsatz geht, FT-Algorithmen aber funktionsbedingt Prozessor-Ressourcen stark beanspruchen, war einerseits der FT-Algorithmenwahl besondere Beachtung zu schenken, andererseits mussten innovative Methoden zur Verschränkung von FT- und DSP-Algorithmen gefunden werden, um deren ursprünglich individuell optimierte Eigenschaften auch in der Kombination zu erhalten und darüber hinaus die Möglichkeit zur Weiterentwicklung und Wartung nach diesen Konzepten entstandener Flug-Software zu gewährleisten. Auf experimentellem Weg konnte gezeigt werden, dass reine Software Lösungen zwar wirtschaftlich interessant sind, aber den gestellten Anforderungen in Bezug auf Verlässlichkeit nicht gerecht werden. Demonstriert wurde aber auch, dass alle zu Beginn der Arbeit gestellten Ziele erfüllt werden können, wenn die Softwaremethoden durch externe Hardware in Form eines FT-Controllers unterstützt werden.

# Contents

| 1 | Intr | oductio | n                                     | 1  |

|---|------|---------|---------------------------------------|----|

|   | 1.1  | Backgi  | round                                 | 1  |

|   | 1.2  | Metho   | dology                                | 3  |

|   | 1.3  | Structu | ure of the Thesis                     | 3  |

| 2 | The  | Probler | m of Radiation in Space               | 5  |

|   | 2.1  | Introdu | uction                                | 5  |

|   | 2.2  | Single  | Event Effects (SEE)                   | 9  |

|   | 2.3  | Total D | Dose Effects                          | 11 |

|   | 2.4  | Displa  | cement Damage                         | 12 |

|   | 2.5  | Missio  | on Orbits                             | 13 |

|   |      | 2.5.1   | Low Earth Orbit (LEO)                 | 13 |

|   |      | 2.5.2   | Highly Elliptical Orbit (HEO)         | 13 |

|   |      | 2.5.3   |                                       | 14 |

|   |      | 2.5.4   | Planetary and Interplanetary          | 14 |

| 3 | Har  | dware a | and Software Fault Tolerance          | 15 |

| - | 3.1  |         |                                       | 16 |

|   | 3.2  |         |                                       | 17 |

|   | 3.3  |         |                                       | 20 |

|   | 3.4  |         | · · · · · · · · · · · · · · · · · · · | 20 |

|   |      | 3.4.1   |                                       | 21 |

|   |      | 3.4.2   |                                       | 22 |

|   |      | 3.4.3   |                                       | 23 |

|   |      |         |                                       | 24 |

|   |      |         | 5 8                                   | 24 |

|   |      |         | 8                                     | 25 |

|   |      |         | 6                                     | 27 |

|   |      | 3.4.4   |                                       | 28 |

|   |      | 3.4.5   | 1                                     | 30 |

|   |      | 3.4.6   | 8                                     | 31 |

|   | 3.5  |         | e e                                   | 31 |

|   |      | 3.5.1   |                                       | 32 |

|   |      | -       |                                       |    |

|   |                                 | 3.5.2                                                                                                                                     | Software Based Scrubbing                                                                                                                                                                                                                                                                                                                                                        | 32                                                                                                 |

|---|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|   |                                 | 3.5.3                                                                                                                                     | Control Flow Checking                                                                                                                                                                                                                                                                                                                                                           | 33                                                                                                 |

|   |                                 |                                                                                                                                           | 3.5.3.1 Control Flow Checking Using Software Signatures                                                                                                                                                                                                                                                                                                                         | 33                                                                                                 |

|   |                                 | 3.5.4                                                                                                                                     | Time Triple Modular Redundancy                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                 |

|   |                                 | 3.5.5                                                                                                                                     | Error Detection by inserting Duplicate Instructions - EDDI                                                                                                                                                                                                                                                                                                                      | 38                                                                                                 |

|   |                                 | 3.5.6                                                                                                                                     | Undetected Faults                                                                                                                                                                                                                                                                                                                                                               | 39                                                                                                 |

|   | 3.6                             | Combi                                                                                                                                     | ned Hardware and Software Fault-Tolerance                                                                                                                                                                                                                                                                                                                                       | 39                                                                                                 |

| 4 | Digi                            | tal Sign                                                                                                                                  | al Processing Platform                                                                                                                                                                                                                                                                                                                                                          | 41                                                                                                 |

|   | 4.1                             | SMV3                                                                                                                                      | 20C6701 Digital Signal Processor - DSP                                                                                                                                                                                                                                                                                                                                          | 42                                                                                                 |

|   |                                 | 4.1.1                                                                                                                                     | Radiation Tolerance                                                                                                                                                                                                                                                                                                                                                             | 43                                                                                                 |

|   |                                 | 4.1.2                                                                                                                                     | Radiation Relevant Processor Behaviour                                                                                                                                                                                                                                                                                                                                          | 44                                                                                                 |

|   |                                 |                                                                                                                                           | 4.1.2.1 Delay Slots and Functional Unit Latency                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                 |

|   |                                 |                                                                                                                                           | 4.1.2.2 Instruction Fetching and Parallelism                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                 |

|   |                                 | 4.1.3                                                                                                                                     | Conditional Operations                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                 |

|   | 4.2                             | SEU T                                                                                                                                     | hreat Scenarios                                                                                                                                                                                                                                                                                                                                                                 | 46                                                                                                 |

|   |                                 | 4.2.1                                                                                                                                     | Opcode Hamming Distance                                                                                                                                                                                                                                                                                                                                                         | 48                                                                                                 |

|   | 4.3                             | Failure                                                                                                                                   | Model                                                                                                                                                                                                                                                                                                                                                                           | 48                                                                                                 |

|   |                                 | 4.3.1                                                                                                                                     | p-bit mutation                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                                                 |

|   |                                 | 4.3.2                                                                                                                                     | creg mutation                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                                                 |

|   |                                 | 4.3.3                                                                                                                                     | Opcode Illegalisation                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                                 |

|   |                                 | 4.3.4                                                                                                                                     | Architectural Barriers                                                                                                                                                                                                                                                                                                                                                          | 50                                                                                                 |

|   |                                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                    |

|   |                                 |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                    |

| 5 |                                 | -                                                                                                                                         | d Experimental Implementation                                                                                                                                                                                                                                                                                                                                                   | 53                                                                                                 |

| 5 | 5.1                             | Introdu                                                                                                                                   | lection                                                                                                                                                                                                                                                                                                                                                                         | 53                                                                                                 |

| 5 | 5.1<br>5.2                      | Introdu<br>Memor                                                                                                                          | rction                                                                                                                                                                                                                                                                                                                                                                          | 53<br>54                                                                                           |

| 5 | 5.1<br>5.2<br>5.3               | Introdu<br>Memor<br>Progra                                                                                                                | Iction                                                                                                                                                                                                                                                                                                                                                                          | 53<br>54<br>56                                                                                     |

| 5 | 5.1<br>5.2<br>5.3<br>5.4        | Introdu<br>Memor<br>Progra<br>Softwa                                                                                                      | Iction                                                                                                                                                                                                                                                                                                                                                                          | 53<br>54<br>56<br>57                                                                               |

| 5 | 5.1<br>5.2<br>5.3               | Introdu<br>Memor<br>Progra<br>Softwa                                                                                                      | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60                                                                         |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1                                                                                   | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63                                                                   |

| 5 | 5.1<br>5.2<br>5.3<br>5.4        | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro                                                                         | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64                                                             |

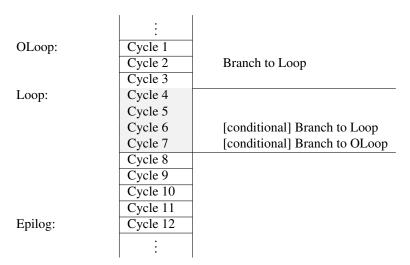

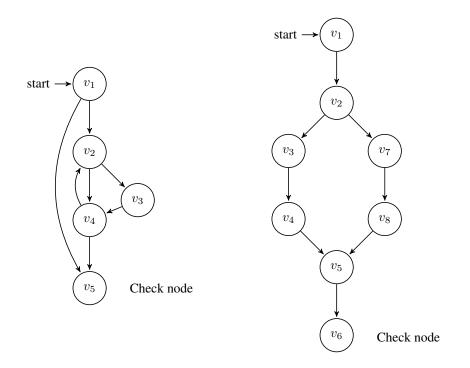

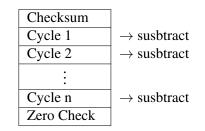

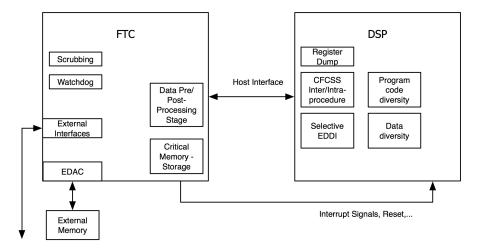

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1                                                                | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65                                                       |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2                                                       | Inction       Inction         ry Layout       Inction         mming Language       Inction         ire EDAC       Inction         Checking       Inction         Comparison of Software EDAC and Mirror Checking       Inction         I Flow Checking by Software Signatures       Inction         Branch Delay Slot Handling       Inction         Loop Kernels       Inction | 53<br>54<br>56<br>57<br>60<br>63<br>64                                                             |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2                                                       | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65                                                       |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2                                                       | Inction       Inction         ry Layout       Inction         mming Language       Inction         ire EDAC       Inction         Checking       Inction         Comparison of Software EDAC and Mirror Checking       Inction         I Flow Checking by Software Signatures       Inction         Branch Delay Slot Handling       Inction         Loop Kernels       Inction | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66                                                 |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2                                                       | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67                                           |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2                                                       | Inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67                                     |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2<br>5.6.3                                              | inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67<br>67                               |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2<br>5.6.3                                              | inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67<br>67<br>70                         |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.4<br>5.6.5                   | inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67<br>67<br>70<br>71                   |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.5<br>5.6.6                   | inction                                                                                                                                                                                                                                                                                                                                                                         | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67<br>67<br>70<br>71<br>73             |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.5<br>5.6.6<br>5.6.6<br>5.6.7 | action                                                                                                                                                                                                                                                                                                                                                                          | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67<br>69<br>70<br>71<br>73<br>73       |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Introdu<br>Memor<br>Progra<br>Softwa<br>Mirror<br>5.5.1<br>Contro<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.5<br>5.6.6<br>5.6.7<br>5.6.8 | action                                                                                                                                                                                                                                                                                                                                                                          | 53<br>54<br>56<br>57<br>60<br>63<br>64<br>65<br>66<br>67<br>67<br>67<br>70<br>71<br>73<br>73<br>74 |

| 6  | Faul   | t Injection                                                                  | 81  |

|----|--------|------------------------------------------------------------------------------|-----|

|    | 6.1    | Fault Injection Environment                                                  | 81  |

|    | 6.2    | Experiment Setup                                                             | 83  |

|    | 6.3    | Experiment Flow                                                              | 85  |

|    | 6.4    | Experimental Results                                                         | 87  |

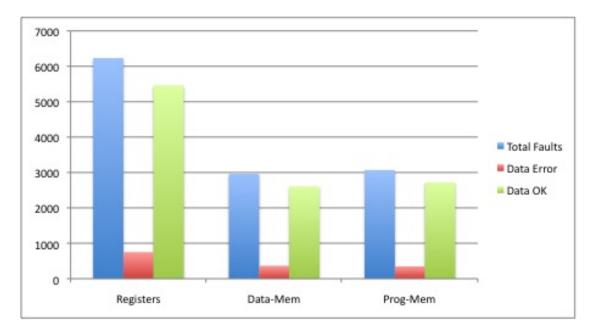

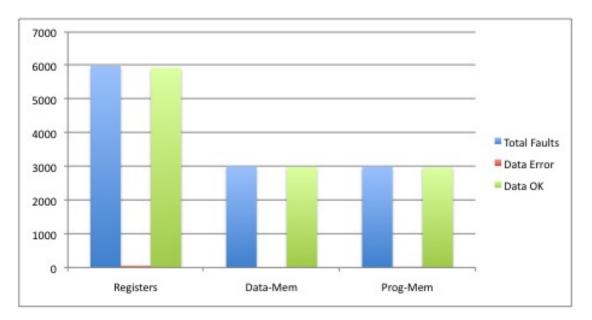

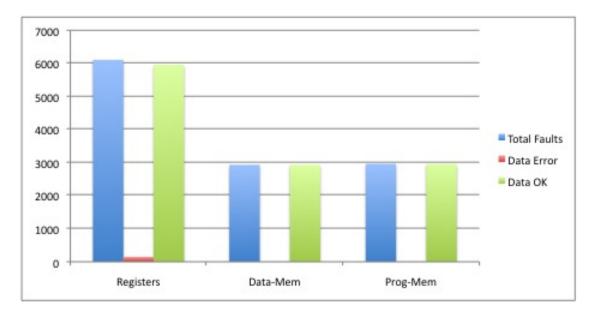

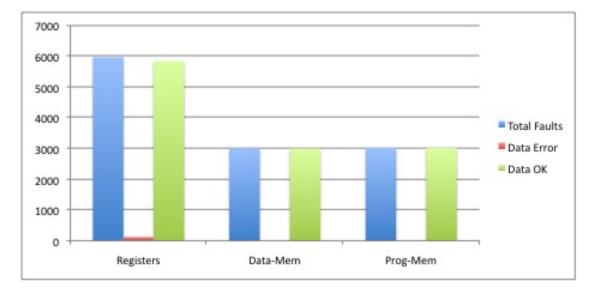

|    |        | 6.4.1 Experiment 1: Detected CFEs                                            | 87  |

|    |        | 6.4.2 Experiment 2: Errors in the Output data (Data Errors - DEs)            | 88  |

|    |        | 6.4.3 Experiment 3: No Effect-Faults                                         | 89  |

|    |        | 6.4.4 Experiment 4: Illegal Opcode                                           | 90  |

|    |        | 6.4.5 Experiment 5: Mixed Intra/Inter Procedure Checking                     | 91  |

|    | 6.5    | Test Evaluation                                                              | 93  |

| 7  | Con    | clusions and Outlook                                                         | 95  |

| A  | Арр    | endix                                                                        | 97  |

|    | A.1    | SMV320C6701 - Radiation performance                                          | 97  |

|    | A.2    | Control Flow Checking using Software Signatures - Intra Procedure            | 99  |

|    |        | A.2.1 Single Precision Matrix Multiplication - CFCSS sheet                   | 100 |

|    |        | A.2.2 Single Precision Matrix Transpose - CFCSS sheet                        | 101 |

|    |        | A.2.3 Single precision maximum value of vector - CFCSS sheet                 | 102 |

|    |        | A.2.4 Single precision floating-point radix-2 FFT with complex input - CFCSS |     |

|    |        | sheet                                                                        | 103 |

|    | A.3    | Texas Instruments Software Design Flow                                       | 104 |

|    | A.4    | Fault Injection Experiments                                                  | 105 |

| Bi | bliogr | aphy                                                                         | 109 |

## CHAPTER

## Introduction

In this chapter an introduction on motivation for the topic from a political perspective will be presented. Industry has to deal with the fact that radiation-hard components originated from the United States can only be used, if their usage is a-priori permitted by US-authorities. This background lays the foundation for the problem which is present when working with radiation-tolerant hardware.

#### 1.1 Background

Space flight plays an important role in our daily life. The first European earth observation satellite named ERS-1 was launched in 1991. Its success paved the way for future space missions, especially for earth observation. ERS-2 followed while ERS-1 was still in orbit, which even allowed for tandem operation of the two spacecraft. At their time of launch the two ERS satellites were the most sophisticated earth observation spacecraft ever developed and launched by Europe. These highly successful satellites collected a wealth of valuable data on Earth's land surfaces, oceans, and polar caps and were called upon to monitor natural disasters such as severe flooding or earthquakes in remote parts of the world.

Because of the information gained from those missions, the European Space Agency (ESA) decided to extend the Earth Observation program to investigate our planet in more detail. The overall success of a mission depends on both quality and amount of science data generated during flight and, therefore, on the total time all devices forming the instrument suite are fully operational. Consequently, space electronics is built from highly reliable components, designed with apropriate margins (de-rating), incorporating redundancy concepts to further increase reliability. Peculiar environmental conditions require careful consideration of mechanical and thermal stress experienced during launch and cruise. In this context ionizing radiation is a particular threat for space systems so that the radiation tolerance of electrical components is of paramount importance. The malfunction of such an cost expensive spacecraft could result in a huge finan-

cial loss or even the end of a mission.

Radiation induced Single Event Effects (SEEs) cause serious problems. Depending on the mission profile, radiation effects may cause transient faults like a Single Event Transients (SETs) which could be experienced as temporary "bitflips", referred to as Single Event Upsets (SEUs), or even as permanant faults such as Single Event Latchups (SELs), which usually result in the destruction and therefore loss of the affected device. To cope with effects like these, special radiation tolerant hardware can be used. Radiation tolerant devices are equipped with additional logic to provide fault tolerance, e.g. via error detection and correction (EDAC), Triple Modular Redundancy (TMR) or improved manufacturing processes. For historical, political and technological reasons, most radiation tolerant components are fabricated in the United States and the *International Traffic in Arms Regulation*<sup>1</sup> (ITAR) restricts the use of radiation hardened devices outside the US. Many organizations and manufactures try to use components which are not covered by ITAR. As a result the amount of hardware components actually available to the European space engineering community is very limited.

Apparently, this problem is most pronounced for applications with demanding requirements concerning processing speed, data throughput and storage as experienced in the context of Digital Signal Processing (DSP) desperately needed for on-board data reduction to guarantee sufficient scientific return in spite of limited data-down-link capacity<sup>2</sup>. Possible technical solutions are

- **Application Specific Integrated Circuits (ASICs)** Respective state-of-the-art technology is available in Europe. However, as the channel widths have decreased, ASIC manufacturing costs have increased to the extent that full custom implementations for individual missions have become unaffordable. Due to the nature of space systems engineering, ASIC re-use (or even design re-use) is rarely possible for DSP-circuitry due to the fact that requirements are highly specific for each mission and exhibit (unnecessary) differences for different space agencies and customers.

- **Programmable Processors** A European component with reasonable performance for control applications is available with the LEON-FT<sup>3</sup> micro-processor. A state-of-the-art European DSP is not available. Respective US components are under ITAR and Japanese devices are not sold as components but only as part of systems.

- **Field Programmable Gate Arrays (FPGAs)** A good approach which is commonly chosen is the use of reprogrammable logic devices. However, most companies providing spacegrade FPGAs are located in the United States which again leads to problems with ITAR. There also exists a European company which produces space-grade FPGAs but these devices can only be used at low clock frequencies, up to 20 MHz, and they can host only very small designs.

<sup>&</sup>lt;sup>1</sup>http://www.pmddtc.state.gov/regulations\_laws/itar\_official.html

<sup>2</sup>http://spacewire.esa.int/edp-page/presentations/ADCSS09\_Trautner\_NGDSP%

20V1.0.pdf

<sup>&</sup>lt;sup>3</sup>http://www.esa.int/TEC/Microelectronics/SEMUD70CYTE\_0.html

A viable option seems to be a processor platform based on a Texas Instruments (TI) digital signal processor. Although TI is an american company, the available space qualified DSPs are not covered by ITAR which enables its free use. However, the radiation tolerance attained by the rad-hard fabrication technology is not perfect and therefore the former mentioned radiation effects can still affect the device in many ways.

This thesis will present a firm concept to ensure fault-tolerance on a TI-DSP based radiation tolerant platform under the given constraints and demonstrate its capabilities by means of a running prototype system which is capable of processing a high amount of data with high performance, using optimized algorithms and fault olerance mechanisms.

#### **1.2 Methodology**

First of all an approach for the quantification and the rating of possible fault scenarios for the used platform will be established. This information is mainly based on a radiation report from Texas Instruments [30] and mission experience reported in other publications. Next, state of the art hardware and software fault-tolerance approaches will be evaluated and discussed.

Although the aim is a pure software solution, approaches using additional hardware will be discussed too. Because computation performance is constrained by the DSP and by the realtime environment, a theoretical evaluation is undertaken to eliminate all infeasible solutions at an early stage.

This is followed by the establishment of fundamental requirements which need to be satisfied by the system. Based on the fact that it is clearly impossible to implement a software solution without a cutback in performance, deductions which are necessary to ensure a given tolerance level will be shown. To give an insight on performance and fault-tolerance, all evaluations are done on typical signal processing algorithms, typical in the sense that they can be found in most spaceborne data processing applications. The assessment of actual performance and availability has been done via measurements on a physical prototype. To simulate SEU effects a fault injection tool has been implemented and the results gained from fault-injection experiments can be compared with theoretical predictions and simulations.

#### **1.3** Structure of the Thesis

This thesis is structured into seven chapters. Following this introduction, Chapter two will recapitulate the basics of failure models which apply to space-grade components and in particular to the devices investigated within the frame of this thesis work. Chapter three will give an overview on commonly used hardware and software fault tolerant approaches in combat to radiation effects in space. Followed by a brief introduction to failure modeling and a listing of likely threat scenarios and their potential consequences, Chapter four will present the development platform supporting the present investigations. The implementation of a fault tolerant system for the selected demonstrator application forms the focus of Chapter five. It will be shown that it is possible to implement the application with adequate availability. Based on the knowledge gained in Chapter five, fault injection techniques will be used to evaluate the fault distribution, their effects and their outcome. The results will be presented in Chapter six. Chapter seven concludes the thesis and discusses open questions and future enhancements.

# CHAPTER 2

# **The Problem of Radiation in Space**

"Space weather is working its way into the national consciousness as we see an increasing number of problems with parts of our technological infrastructure such as satellite failures and widespread electrical power brownouts and blackouts"<sup>1</sup>

#### 2.1 Introduction

The physical space environment is markedly different from circumstances to which terrestrial electronics is exposed. In space radiation based errors like *single event effects* (SEEs) have become a major issue. However, it is the presence of ionizing radiation and its effect on semi-conductors, that creates a fault environment which is unique to space applications, threatening electronic circuit reliability.

Since their first observation by Guenzer and Wolicki in 1979 [19], the importance of *soft-error* effects, their causes and the methods for their mitigation, have rapidly increased. In the same year Ziegler and Lanford published an article [68] which presents a way to predict the number of faults induced by cosmic rays. They also predicted that SEEs are not limited to memories and that a similar upset phenomena could arise even at sea level.

Concentrating on effects in space two main radiation sources need to be considered:

- High energy protons, especially for low earth orbits (LEO)

- Cosmic rays, a heavy ion compunds of either solar or galactic origin.

<sup>&</sup>lt;sup>1</sup>The National Space Weather Program, 1999

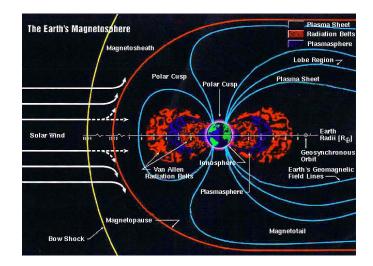

Figure 2.1: Geomagnetic field [Source: NASA Marshall Space Flight Center]

Plasma effects can be ignored in this context since plasma energies are in a range of less than 1 eV  $^2$  to keV which is very low compared to the energy of ionizing radiation.

Due to the strong influence of the geomagnetic field, particle motion and location are also to be considered. It is known that the sun also has an impact on ionizing radiation levels and magnetic field characteristics, influenced by the eleven year solar cycle which is divided into four years of *solar min* followed by seven years of *solar max*, it is known that sun flares are a major contribution to the overall ionizing radiation level. Figure 2.1 shows particle motion and location influenced by the geomagnetic field.

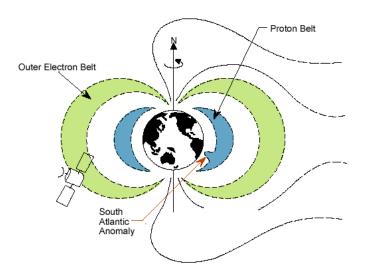

The regions of interest for an earth observation mission are mainly the Van Allen Belts. As shown in Figure 2.2 the Van Allen Belts consist of the inner proton and the outer electron belt. The south atlantic anomaly (SAA), which is also shown, causes an increased flux of energetic particles at its location and therefore exposes a higher level of radiation to objects in this region. Particles trapped in the SAA as well as electrons belonging to the outer electron belt, which reaches down to the earth's surface close to the polar regions are the greatest threat for satellites in low-earth orbit (LEO). The trapped particles in the outer Van Allen Belt include electrons with an energy level of up to 7 MeV. Due to the low energy level shielding, against these particles is easy. On the other hand, there are mainly protons trapped inside the inner belt with an energy level of less than 500 MeV, which roughly varies inversely with altitude. Consequently, dose is affected by altitude and geomagnetic latitude.

Based on the information provided up to now, Table 2.1 aims at a classification of radiation according to root cause and affected orbits.

<sup>&</sup>lt;sup>2</sup>Energy Unit: Electron Volt (eV) one eV is the energy gained by an electron by acceleration due to a potential difference of 1V. Energy in radiation is usually in the unit of MeV ( $10^6$ eV) or KeV ( $10^3$ eV).  $1eV = 1.6 \cdot 10^{-19} J$ ,  $1MeV = 1.6 \cdot 10^{-13} J$

Figure 2.2: Trapped Radiation Belts Around Earth [Source: NASA Jet Propulsion Laboratory]

| <b>Radiation Source</b>  | Effects of Solar Cycle                                                                            | Variations                              | <b>Types of Orbits Affected</b> |

|--------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------|

| Trapped Protons          | - Solar Min - Higher                                                                              | -Geomagnetic Field                      | - LEO                           |

|                          | - Solar Max - Lower                                                                               | - Solar Flares                          | - HEO                           |

|                          |                                                                                                   | - Geomagnetic Storms                    | - Transfer Orbits               |

| Galactic Cosmic Ray Ions | - Solar Min - Higher                                                                              | Ionization Level                        | - LEO                           |

|                          | - Solar Max - Lower                                                                               |                                         | - GEO                           |

|                          |                                                                                                   |                                         | - HEO                           |

|                          |                                                                                                   |                                         | - Interplanetary                |

| Solar Flare Protons      | - Large Numbers During Solar Max                                                                  | - Distance from Sun Outside 1 AU        | - LEO $(I > 45^{\circ})$        |

|                          | - Few During Solar Min                                                                            | - Orbit Attenuation                     | - GEO                           |

|                          |                                                                                                   | - Location of Flare on Sun              | - HEO                           |

|                          |                                                                                                   |                                         | - Interplanetary                |

| Solar Flare Heavy Ions   | - Large Numbers During Solar Max                                                                  | - Distance from Sun Outside 1 AU        | - LEO                           |

|                          | - Few During Solar Min                                                                            | - Orbit Attenuation                     | - GEO                           |

|                          |                                                                                                   | - Location of Flare on Sun              | - HEO                           |

|                          |                                                                                                   |                                         | - Interplanetary                |

| Table 2.1: S             | Table 2.1: Summary of Radiation Sources [Source: NASA - Single Event Effect Criticality Analysis] | :: NASA - Single Event Effect Criticali | ty Analysis]                    |

| Analysis]          |

|--------------------|

| Effect Criticality |

| ngle Event         |

| NASA - Si          |

| [Source:           |

| on Sources         |

| of Radiation       |

| Summary c          |

| able 2.1: 9        |

### 2.2 Single Event Effects (SEE)

The former mentioned physical effects create the basis for the following description. If radiation exceeds a certain level their physical effects can cause electronic disturbances like SEEs, which vary depending on their energy level and their location. Practically, space radiation is described by the so called radiation spectrum, which is the density of particles of a particular radiation type as a function of particle energy.

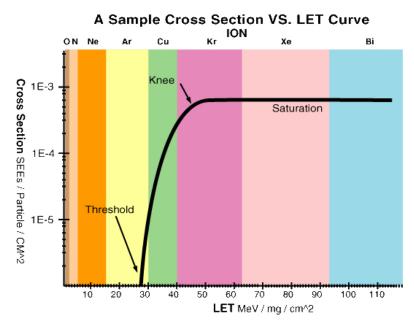

SEEs can be described as a function of the charge deposit into a node of an integrated circuit in terms of linear energy transfer (LET) that denotes the energy imparted by the particle and is directly proportional to the response of the circuit. In other words, LET expresses the relevant characteristic of a particles passage through material. It gives up energy as a function of the distance it travels through the material and the density of the material.

$$L_{\Delta} = \frac{dE_{\Delta}}{dx} \tag{2.1}$$

LET is typically expressed in  $MeV \cdot cm^2/mg$ . The linear energy transfer threshold of a device  $-LET_{th}$  is by definition the minimum amount of energy required to cause an SEE in this device at a particle fluence of  $10^7 \ ions/cm^2$ . A device having a  $LET_{th} > 100MeV \cdot cm^2/mg$  is considered practically SEE immune. Conversely a low  $LET_{th}$  implies high sensitivity.

The cross section CS, or  $\sigma$ , which is a function of the *LET* measures the probability for an SEE to occur. To define the upper limit the saturation cross section  $CS_{sat}$  or  $\sigma_{sat}$  is used. In other words  $\sigma$  is referred as the number of upsets observed divided by the number of ions per  $cm^2$ .  $\sigma_{sat}$  and  $LET_{th}$  are the key measures for SEEs. The following example shows how the cross section is calculated:

#### **Cross Section Estimation Example – SEU-Testing of 8 Bit Memory**

- 1. write 0000.0000 into memory

- 2. irradiate device with a known number of particles per  $cm^2$  (F)

- 3. stop irradiation

- 4. read out memory e.g.  $0100.0010 \rightarrow 2$  upsets (N)

The resulting cross section  $\sigma$  can be calculated using equation 2.2

$$\sigma_{SEU} = \frac{N}{F} [cm^2] \tag{2.2}$$

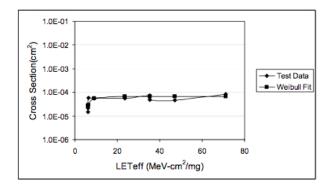

Because the cross section is measured for one particular LET, more experiments and calculations with different LET levels are necessary. Figure 2.3 shows the cross section as a function of LET for a particular device. Also, threshold and the saturation are visible.

Figure 2.3: Cross section vs. LET

SEEs caused by energetic particles are divided into 2 categories:

- Permanent faults:

- Single Event Latchup (SEL)

- Single Event Burnout (SEB)

- Single Event Gate Rupture (SEGR)

- Transient faults:

- Single Event Upset (SEU)

- Single Event Functional Interrupt (SEFI)

Since for many of those terms slightly different definitions can be found in literature, this work refers to the following space radiation definitions used by Ken LaBel, NASA Goddard Space Flight Center<sup>3</sup>:

• **Single Event Latchup (SEL)** is a potentially destructive condition involving parasitic circuit elements forming a silicon controlled rectifier (SCR). In traditional SEL, the current may destroy the device, if not limited and removed "in time". A "microlatch" is a subset of SEL where the device current remains

<sup>&</sup>lt;sup>3</sup>http://klabs.org/richcontent/Tutorial/Radiation\_Definitions.htm

below the maximum specified for the device.

A removal of power to the device is required in all non-catastrophic SEL conditions in order to recover device operation.

- **Single Event Burnout (SEB)** is a highly localized burnout of the drain-source channel in power MOSFETs. SEB is a destructive condition.

- Single Event Gate Rupture (SEGR) is the burnout of a gate insulator in a power MOSFET. SEGR is a destructive condition.

- Single Event Upset (SEU) is a change of state or transient induced by an ionizing particle such as a cosmic ray or proton in a device. This may occur in digital, analog and optical components or may have effects in surrounding circuitry. These are "soft" bit errors in that a reset or rewriting of the device causes normal behaviour thereafter. A full SEU analysis considers the system effects of an upset.

- Single Event Functional Interrupt (SEFI) is a condition where the device stops operating in its normal mode, and usually requires a power reset or other special sequence to resume normal operations. It is a special case of SEU changing an internal control signal. One example would be a DRAM entering the test mode defined by JEDEC <sup>4</sup>. Another example is a microcircuit with IEEE 1149.1 JTAG circuitry leaving the TEST\_LOGIC\_RESET state and loading an unintended instruction into the instruction register (IR). Like other SEUs, the system effects must be properly analyzed. For example, a JTAG upset can cause the device to draw high currents or turn inputs into an outputs. The latter could, for example, drive a clock line to ground; thus, an independent clock signal should be used for the TCLK pin on devices without the optional TRST pin.

A complete summary of faults based on radiation can also be found in the the European standard E-ST-10-12C from the "European Cooperation for Space Standardization".<sup>5</sup>

## 2.3 Total Dose Effects

Total ionization dose (TID) is the non-reversible effect of ionizing radiation accumulated on a space mission over time. Ionizing radiation can generate electron-hole pairs in semiconductors and in insulators such as silicon dioxide. In principle, it is possible for the electrons and holes to recombine or to be transported away by an electric field. However, holes that have lower mobility than electrons are often trapped at interfaces between semiconductor and insulator or within the bulk material. The deposited charge changes the potential which can in turn cause an increase in the leakage currents which may increase power consumption, change the devices time constants, reduce gain, and change the threshold voltage of a metal-oxide semiconductor (MOS) transistor. In addition electron can get caught in non-conductive material. With increasing exposure, there

<sup>&</sup>lt;sup>4</sup>JEDEC standards http://www.jedec.org/

<sup>&</sup>lt;sup>5</sup>European Cooperation for Space Standardization http://www.ecss.nl/

is a continuing decrease in functionality until the device eventually fails. In other words, TID to an electronic device is the equivalent of a sunburn to the human skin. The measurement is done in terms of the absorbed dose which represents the absorbed energy. The unit for this measurement is *rad* (radiation absorbed dose) or the SI unit *gray* (Gy).

$$1 Gy = 100 rad = 1 J/kg$$

(2.3)

Dose must always be referred to the absorbing material. TID effects on semiconductors can be summarized as follows:

- MOS transistors

- Threshold voltage shift  $(\Delta V t)$

- Leakage currents between source and drain, and between adjacent MOS-transistors

- Transconductance decrease

- Weak inversion slope decrease

- Bipolar transistors

- Gain decrease

- JFET transistors

- Decrease of P-JFET transconductance

- No TID effect on N-JFET

- Silicon resistors

- Resistance of P-Silicon resistor increases

- No effect on N-silicon resistors

- MOS capacitors

- no TID effect

#### 2.4 Displacement Damage

Displacement damage is the result of non-ionizing radiation that causes atomic displacements when radiation interacts with atomic nuclei, displacing or removing them from their lattice sites. This upsets the periodicity of the lattice in the material, creating lattice defects. Displacement damage, also known as bulk damage, is caused by the cumulative effects of non-ionizing radiation that include protons and ions at all energies, electrons greater than about 150 keV, and neutrons from onboard radioactive power sources or secondary particles from the initial interactions. In short, displacement damage is the accumulation of crystal lattice defects caused by high energy radiation. The most important consequence of displacement damage in a semiconductor is a reduction in the lifetime of the minority carriers. Displacement damage is similar to

TID, which means that the effect is cumulative, although it is more complex to characterize than TID. A commonly used method to quantify displacement damage is non-ionizing energy loss (NIEL) [61].

#### 2.5 Mission Orbits

There are extremely large variations in the level of radiation effects depending upon the trajectory through the radiation source. Satellites flying at Low Earth Orbits (LEOs), Highly Elliptical Orbits (HEOs), Geostationary Orbits (GEOs) and planetary and interplanetary missions experience very different environmental conditions [29].

At the beginning of this Chapter the susceptibility of electronic components to space radiation was explained. Also, a threshold for SEE immunity based on the energy level was derived. The following description shall help to understand how the level of radiation depends on a space vehicle's location in space. Although the presentation is qualitative, it gives a good indication for the probability of ocuurence of radiation induced effects.

#### 2.5.1 Low Earth Orbit (LEO)

Satellites flying in LEO are passing regions of the Van-Allen Belts, filled with trapped protons and electrons, several times a day. The resulting flux varies largely depending on inclination and orbit. This is the most important characteristic of a LEO orbit with respect to radiation. The greatest inclination dependencies occur in the range of  $0^{\circ} < I < 30^{\circ}$ . The largest variation of the resulting flux is located between 200km up to 600km. At an altitude in excess of 600 km the flux only changes gradually. The location of the flux peaks depends on the energy of the particles. For trapped protons with an energy of E > 10MeV it is found at about 4000km altitude.

The geomagnetic field works as a shield protecting satellites against cosmic rays and solar flare particles. This protection mechanism varies stronger with inclination than it does with altitude. Consequently, the exposure to radiation increases with increasing altitude as well as with increasing inclination. If the inclination reaches the pole regions, the spacecraft is outside the geomagnetic field lines and therefore fully exposed to cosmic rays and to solar flare particles for a significant portion of the orbit. Under normal space-weather conditions an inclination of  $45^{\circ}$  helps to shield the satellite completely against solar flare protons.

During strong solar events the geomagnetic field is distorted, resulting in cosmic ray and solar flare particles reaching previously unattainable altitudes and inclinations. The same effect applies to cosmic ray particles during strong magnetic storms.

#### 2.5.2 Highly Elliptical Orbit (HEO)

Highly elliptical orbits are similar to LEO orbits, in that they pass through the Van Allen belts every day. However, because of their high apogee altitude (greater than about 30,000km), satel-

lites in this kind of orbit also have to endure long exposure to the cosmic ray and solar flare environments, regardless of their inclination. The levels of trapped proton flux that HEOs encounter depend on the perigee position of the orbit including altitude, latitude, and longitude. If this position drifts during the course of the mission, the degree of drift must be taken into account when predicting proton flux levels [29]. Because of the orbit altitude ranging from 400 km (perigee) to 46,000 km (apogee) HEOs also accumulate high TID-levels due to both, the trapped proton exposure and the electrons in the outer belts where the spacecraft spends a significant amount of time during each apogee pass.

#### 2.5.3 Geostationary Orbit (GEO)

At geostationary altitudes the only trapped protons that are present are below energy levels necessary to initiate nuclear events that could cause SEEs in materials surrounding the sensitive region of the device. However, GEOs are almost fully exposed to the galactic cosmic ray and solar flare particles. Protons below 40-50 MeV are normally geomagnetically attenuated, however, this attenuation breaks down during solar flare events and during geomagnetic storms. Field lines crossing the equator at about 7 earth radii during normal conditions can be compressed to about 4 earth radii during these events. As a result, particles previously deflected have access to much lower latitudes and altitudes.

#### 2.5.4 Planetary and Interplanetary

The evaluation of the radiation environment for these missions can be extremely complex depending on the number of times the trajectory passes through the earth's radiation belts, how close the spacecraft gets to the sun, and how well known the environment of other planets is. Each of these factors must be very carefully taken into account along the exact mission trajectory.

# CHAPTER 3

# Hardware and Software Fault Tolerance

In 1980 a joint committee on "Fundamental Concepts and Terminology" was formed by the technical committee on Fault-Tolerant Computing of the IEEE Computer Society and the "International Federation for Information Processing" (IFIP), Working Group 10.4, "Dependable Computing and Fault Tolerance." This laid the foundation for many important actions on dependable systems.

Designing a reliable system requires finding a way to prevent failures caused by logical faults arising from various problems. Available electronic components provide little support for error detection and recovery and even less for the alleviation of strange behaviour caused by SEEs. Therefore, some kind of replication is required to attain acceptable fault-coverage.

The optimal redundant configuration for the implementation of a reliable computational component depends on the relative importance of operational correctness, life time and cost. Uninterrupted operational correctness generally requires multiple devices to be simultaneously on-line; long-life generally requires unpowered spares to be available. Both of these must be weighed against mass, power, real estate and the cost associated with the use of multiple devices. As described earlier, the primary goal of this thesis is to determine a DSP-platform architecture offering affordable protection against high transient error rates which have to be expected, if commercial or industry-standard electronic components are deployed in space.

This chapter summarizes the broad spectrum of techniques available to the designer of reliable digital systems. Techniques leading to increased reliability/availability can be divided into two groups of basic approaches.

- Fault intolerance (or fault-avoidance)

- Fault tolerance

### 3.1 Fault-Error-Chain

Before continuing some basic definitions are necessary. It is mandatory to understand the difference between faults, errors and failures:

- Fault: adjudged or hypothesized cause of an error

- Error: that part of state which may lead to a failure

- Failure: occurs when delivered services deviate from the specification

$fault \rightarrow error \rightarrow failure \rightarrow fault \rightarrow error \rightarrow failure \rightarrow \cdots$

In other words it can be described as follows: An error is a manifestation of a fault in a system, which could lead to system failure<sup>1</sup>.

In general the occurrence of the first failure does not end in contained behaviour. Although a failure is the first deviation that can be observed from outside, it is necessary to consider that a failure can propagate onto the next level. A failure in one service may propagate into another service as a fault.

The next illustration shall increase the ability to recognize the importance of the fault-errorchain.

$\cdots \rightarrow event \rightarrow cause \rightarrow state \rightarrow event \rightarrow cause \rightarrow state \rightarrow \cdots$

The goal is to break this fault-error-chain and thereby increase the dependability of a system. The development of a dependable computing system calls for the combined utilization of a set of methods and techniques which can be classed in the following manner [31]:

- Fault prevention: how to prevent fault occurrence or introduction

- Fault tolerance: how to ensure a service up to fulfilling the system's function in the presence of faults

- Fault removal: how to reduce the presence (number, seriousness) of faults

- Fault forecasting: how to estimate the present number, the future incidence, and the consequences of faults

Depending on system and environment, not all of the above techniques may be applicable.

<sup>&</sup>lt;sup>1</sup>Singhal/Shivaratri

### **3.2 Basics of Fault Tolerance**

Fault intolerance results from conservative design practices such as the use of highly reliable components. The goal of fault intolerance is to reduce the possibility of a fault to occur in the first place. Techniques in this category are aimed at defining methodologies and standards that control the development process and prevent the introduction of faults. Some well known methodologies we would like to mention here as examples are shielding and the application of quality standards such as ISO9000<sup>2</sup>, ECSS<sup>3</sup>, DO178B<sup>4</sup>, etc. are included here. However, even with the most careful avoidance techniques faults cannot be completely avoided and system failures will occasionally occur.

Fault Tolerance aims at with putting mechanisms in place allowing a system to still deliver the required service in the presence of faults, albeit some (graceful) degradation may have to be taken into account. Additional information provided and exploitet with this technique allows for interrupting the error chain at the transition from fault to error.

The necessary redundancy may be provided in two ways: time and space. Spatial redundancy, always requires additional hardware, viz. the addition of extra gates and may introduce additional information in form of coding. Hardware deals which the addition of extra gates, memory cells, bus lines, functional units and also the supply of extra information (e.g. coding) to guard against failures.

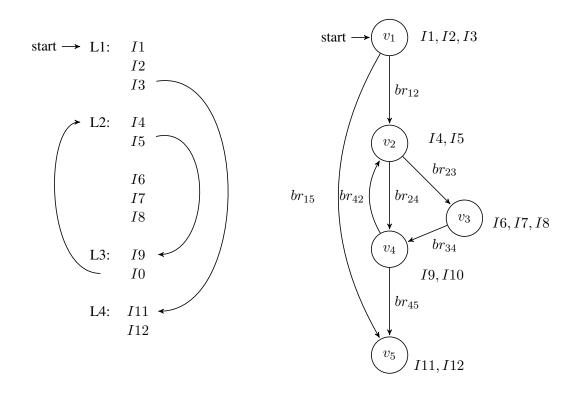

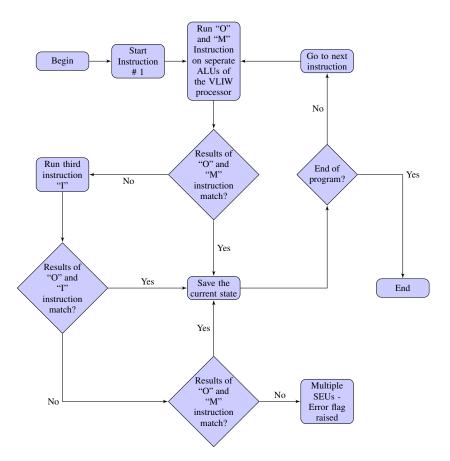

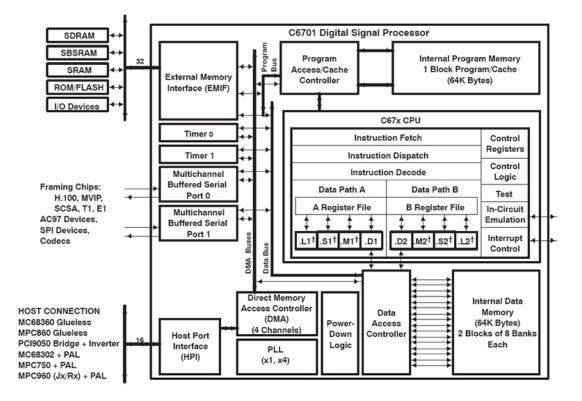

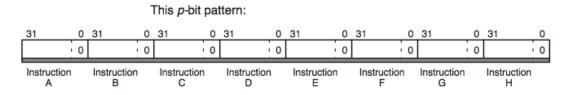

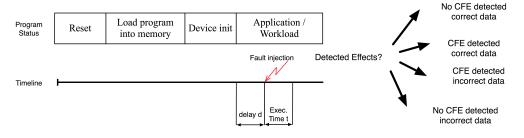

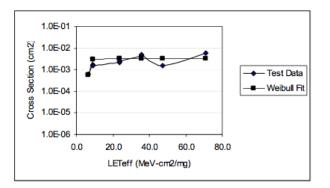

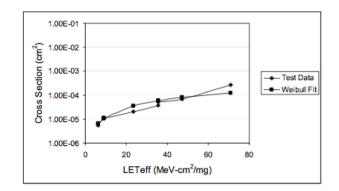

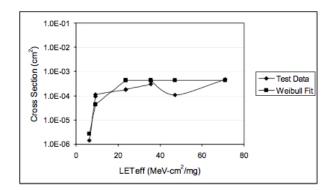

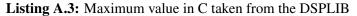

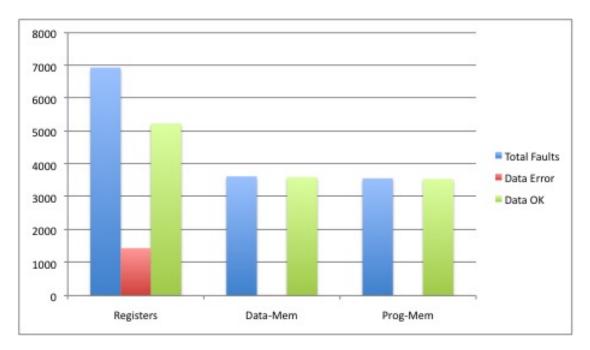

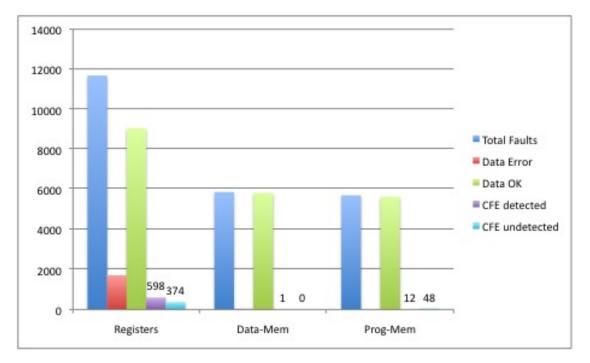

Time redundancy may be exclusively implemented in software and entails multiple or repeated execution of the same instruction and comparing the results in a straightforward or more sophisticated manner. Table 3.1 summarizes some techniques presented in [59].