# Reconfigurable Complementary and Combinational Logic Based on Monolithic and Single-Crystalline Al-Si Heterostructures

Raphael Böckle, Masiar Sistani, Martina Bažíková, Lukas Wind, Zahra Sadre-Momtaz, Martien I. den Hertog, Corban G. E. Murphey, James F. Cahoon, and Walter M. Weber\*

Metal-semiconductor heterostructures providing geometrically reproducible and abrupt Schottky nanojunctions are highly anticipated for the realization of emerging electronic technologies. This specifically holds for reconfigurable field-effect transistors, capable of dynamically altering the operation mode between n- or p-type even during run-time. Targeting the enhancement of fabrication reproducibility and electrical balancing between operation modes, here a nanoscale Al-Si-Al nanowire heterostructure with single elementary, monocrystalline Al leads and sharp Schottky junctions is implemented. Utilizing a three top-gate architecture, reconfiguration on transistor level is enabled. Having devised symmetric on-currents as well as threshold voltages for n- and p-type operation as a necessary requirement to exploit complementary reconfigurable circuits, selected implementations of logic gates such as inverters and combinational wired-AND gates are reported. In this respect, exploiting the advantages of the proposed multi-gate transistor architecture and offering additional logical inputs, the device functionality can be expanded by transforming a single transistor into a logic gate. Importantly, the demonstrated Al-Si material system and thereof shown logic gates show high compatibility with state-of-the-art complementary metal-oxide semiconductor technology. Additionally, exploiting reconfiguration at the device level, this platform may pave the way for future adaptive computing systems with lowpower consumption and reduced footprint, enabling novel circuit paradigms.

R. Böckle, M. Sistani, M. Bažíková, L. Wind, W. M. Weber Institute of Solid State Electronics Technische Universität Wien Gußhausstraße 25-25a, Vienna 1040, Austria E-mail: walter.weber@tuwien.ac.at Z. Sadre-Momtaz, M. I. den Hertog Institut Néel, CNRS/UGA UPR2940, Grenoble 38042, France

C. G. E. Murphey, J. F. Cahoon Department of Chemistry University of North Carolina Chapel Hill, NC 27599-3290, USA

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202200567.

© 2022 The Authors. Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/aelm.202200567

# 1. Introduction

Modern society is highly depending and relying on electronic computing devices, as for example, employed in efficient servers, personal computers, and mobiles, and currently being explored toward the realization of emerging computing paradigms, such as "artificial intelligence" and the "Internet of Things".<sup>[1]</sup> A key enabler for these paradigms is the complementary metal-oxide-semiconductor (CMOS) technology, which utilizes the concept of complementary n- and p-type field-effect transistors (FET) to construct Boolean logic gates. Importantly, in CMOS technology the logic functions are fixed by the physical layout of interconnects and the definition of doped regions and thus do not allow for a flexible alteration of the circuits after production. The continuous shrinking of feature sizes of these Si metal-oxide-semiconductor field-effect transistors (MOSFETs) has been providing performance enhancement and higher power efficiency throughout the last decades. However, classical scalability is limited  $^{\left[ 2\right] }$  and the static nature of the

MOSFET primitives was not developed to provide runtimeadaptability as required for new circuit paradigms. A concept to overcome the static nature in CMOS technology and reduce overall circuit area and power consumption are reconfigurable FETs (RFETs),<sup>[3-5]</sup> encompassing a broad family of devices that enable a reconfiguration of the dominant carrier type based on either Schottky-barrier field-effect transistors (SBFET),[4,6-9] or steep slope band-to-band tunneling transistors (TFET),[10-13] capable of dynamically altering the device operation between n- and p-type. This device concept thus gives rise to a paradigm change where devices, circuits, and even systems are actively and dynamically reconfigured after manufacturing or, as particularly noteworthy, even during run-time, enabling an adaption to the needed logic function of a circuit. Importantly, this "fine-grain" approach is fundamentally different to the already available "coarse-grain" approach followed in field programmable gate arrays (FPGAs)<sup>[14]</sup> based on signal routing to predefined logic blocks, resulting in high latency in data

transfer and substantial chip area consumption. Reconfigurable electronics utilizing RFETs on the other hand is enabled by a device layout with independent gates inducing in addition to the gated region in conventional FETs an additional energy barrier along the channel, effectively blocking the undesired charge carrier type, and thus enabling unipolar n- or p-type operation. In this respect, the most common approach is utilizing metal-semiconductor heterostructures embedded in a SBFET.<sup>[15]</sup> In this configuration, RFETs have already been fabricated based on Si,<sup>[4,8,16]</sup> Ge,<sup>[17–19]</sup> and also on 2D layered systems, like WSe<sub>2</sub><sup>[20,21]</sup> or MoTe<sub>2</sub>,<sup>[22,23]</sup> and recently with black phosphorous.<sup>[24]</sup> Latest generation RFETs facilitate a device layout with three independent top-gates to induce additional energy barriers in the channel, enabling an even more effective suppression of the undesired charge carrier type and therefore favoring n- or p-type operation, respectively.<sup>[4,25]</sup> Simultaneously with more sophisticated device architectures, the development of the first logic gates, exploiting reconfiguration on a logic gate level, emerged. A graspable example is a NAND gate, which can be dynamically reprogrammed to NOR functionality when built from RFETs.<sup>[26]</sup> Additionally, it has been predicted by simulations that exploiting three-gate RFETs, compact realizations of XOR and majority (MAJ) based combinatorial circuits can be envisioned using a lower number of transistors than in classical CMOS technology.<sup>[8]</sup> Based on these investigations a number of circuit level features, such as dynamic reconfiguration,<sup>[26,27]</sup> intrinsic XOR,<sup>[28]</sup> and wired-AND capabilities<sup>[29]</sup> as well as control of threshold voltage,<sup>[30]</sup> and suppression of parasitic charge sharing effects in dynamic logic gates,<sup>[31,32]</sup> have been demonstrated for RFETs, providing additional benefits over their CMOS counterparts. In this respect, fabricating reliable and reproducible metal-semiconductor junctions is essential, as the injection of charge carriers highly depends on the metal-semiconductor interface, junction area, and its incorporated energy barrier. In consequence the on-current as well as the threshold voltage symmetry depends on the material choice. For Si and Ge based RFETs and SBFETs this has been achieved by thermally induced solid state reactions forming different kinds of intruded metal-silicide<sup>[33,34]</sup> and -germanide<sup>[35]</sup> segments. In the latter case of Ge channels a thermally driven exchange reaction is also able to provide intruded single elementary metals providing a flat, clean and sharp junctions.<sup>[36]</sup> Such exchange reacted Al-Ge<sup>[37]</sup> and Al-Si<sup>[38]</sup> junctions overcome difficulties with the reproducibility of Schottky junctions as the process avoids instability issues otherwise common during intermetallic phase formation of metal silicides and germanides.<sup>[33,39]</sup> For RFETs and other emerging devices an accurate control of phase formation becomes necessary as different phases and related lattice strain yield a variability in barrier heights and thus in the electronic injection properties.<sup>[40]</sup> Further on, phase instabilities lead to a junction patchiness that translates into additional variability of electrical performance.<sup>[41]</sup> Indeed, commonly employed metal-silicides make the addition of further alloying elements such as for example, Pt or Sn in nickel-silicides necessary to improve morphology and stabilize crystallographic phases.<sup>[42,43]</sup> Thus, it can be argued that the addition of further elements restricts the flexibility in semiconductor processing and introduces a change in Schottky barrier height,<sup>[44]</sup> that would be otherwise avoided

with the appropriate use of single element metals as exploited here with Al. In this context, the Al-Si exchange mechanism forming single-elementary Al contacts to Si channels, shows less device-to-device variation<sup>[38,45]</sup> and allows subsequent annealing steps without changing the composition of the metallic lead.

## 2. Results and Discussion

In this paper, we report on a CMOS compatible RFET platform utilizing nanoscale monolithic Al-Si heterostructures, obtained from a thermally induced heterostructure formation, with abrupt single-elemental metal-Si interfaces and highly symmetric effective Schottky barriers for electrons and holes. Across the discussion of results, the metal-semiconductor combination and its suitability for the proposed devices will become evident for realizing complementary logic gates.

For device fabrication and as a simple integration vehicle, vapor-liquid-solid (VLS)-grown, single-crystal, nominally intrinsic Si nanowires (NWs) with (112) orientation and diameters of approximately  $d_{NW} = 80$  nm are employed. Measured by scanning transmission electron microscopy (STEM), the NWs are enwrapped in a 8.5-9.7 nm thick thermally-grown SiO<sub>2</sub> shell and are further integrated into a SBFET architecture. A thermally induced Al-Si exchange reaction at T = 774 K was utilized to define the Si channel length monolithically embedded in an Al-Si-Al NW heterostructure providing the necessary single elementary metal contacts and sharp metal-semiconductor junctions.<sup>[38]</sup> In this work, NWs are used as a prototyping vehicle to demonstrate the capabilities of Al-Si based RFETs and logic circuits. In this respect, the exact placement of VLS-grown NWs bears a challenge in CMOS integration and the realization of complex logic circuits. Nevertheless, a feasible approach to overcome this issue is to use in-plane solid-liquidsolid grown NWs<sup>[46]</sup> in combination with guided or patterned ledges. Thereby, NW thickness, alignment, orientation, and pitch can be controlled even when stacking NWs vertically along sidewall grooves.<sup>[47]</sup> Notably, it was shown that the Al-Si exchange mechanism also works in silicon-on-insulator (SOI) based nanosheets and thus should allow the realization of RFETs and more complex logic circuits using top-down fabrication.<sup>[38]</sup> Due to the stable crystal phase of the intruded metallic segments, the applied Al-Si exchange appears to show significantly reduced geometric, crystallographic, and morphologic variabilities compared to state-of-the-art thermally induced Ni<sub>x</sub>Si<sub>1-x</sub>-Si NW heterostructures.<sup>[48,49]</sup> Embedded in a threeindependent gate transistor architecture the functionality enhanced operation compared to that of a conventional MOSFET is reached (see Figure S1, Supporting Information). Through the use of the polarity gate (PG) electrodes, which are placed directly atop the abrupt Al-Si junctions, the off-current is efficiently suppressed and furthermore reconfiguration of transistor polarity is achieved. Setting a positive program voltage V<sub>PG</sub> leads to predominant electron conduction and blocking of holes, whereas a negative  $V_{PG}$  results in predominant hole conduction. Thus, the device operation can be altered between nand p-type modes even at run-time. In correlation to a conventional MOSFET the control gate (CG) allows to adjust the

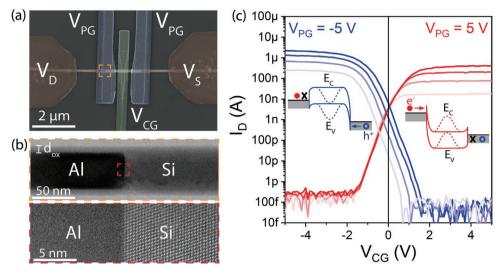

**Figure 1.** a) Colored SEM image of an Al-Si-Al heterostructure with  $L_{Si} = 1.5 \,\mu$ m embedded in a three-gate FET architecture enabling RFET operation. b) BF STEM image showing the Al-Si interface of the NW heterostructure, where the Si region is oriented in the [110] zone axis. The NW is envrapped in a thermally grown SiO<sub>2</sub> shell with a thickness of  $d_{ox} = 9$  nm. The lower panel shows a HAADF STEM zoomed-in view of the Al-Si interface indicating a sharp metal-semiconductor junction. c) Subthreshold transfer characteristic for bias voltages of  $V_D = 0.25$ , 0.5, 0.75, and 1 V showing unipolar n-type (red) and p-type (blue) operation set by  $V_{PG}$ . The schematic band diagrams of n- and p-type device operation are inserted, where the solid and dotted lines depict the on- and off-states for n- and p-type operation, respectively.

charge carrier density in the channel and thus to turn the transistor on and off by setting the corresponding voltage. The detailed underlying physical mechanism of RFETs was thoroughly elaborated and investigated in the past.<sup>[50-52]</sup> Although different operation modes exist<sup>[50]</sup> the most efficient gate-tunability is achieved by placing the CG top-gate electrode inbetween the PGs, allowing to directly capacitively couple to the semiconductor active region and avoiding coupling to the Schottky junctions.<sup>[53]</sup> Figure 1a shows a scanning electron microscopy (SEM) top view image of such a RFET with  $L_{Si} = 1.5 \ \mu m$ . Importantly, the PGs are electrically interconnected, which supports the realization of a symmetric device architecture. Electrically connecting the PGs allows to increase the performance in terms of reducing the complexity as well as achieving low off-currents in comparison to asymmetrically biasing the PG electrodes. Note that independently (and asymmetrically) biasing the PGs would, under some circumstances, lead to more symmetric currents, but with considerable costs in reduced on-currents and signal overhead. Self-aligned techniques have readily been shown for the fabrication of such structures,<sup>[8]</sup> simplifying device fabrication and facilitating downscaling of the devices. Although we focus on fairly large channel lengths for demonstration purposes the RFET concept is physically scalable, [54] recently scalability down to 10 nm nodes has been verified by device TCAD simulations.<sup>[55,56]</sup> Nevertheless, the structural sizes of RFETs are by far exceeding state-of-the-art CMOS MOSFETs. However, they allow a circuit design that significantly reduces the chip area for the same logic operation compared to standard CMOS technology. Bright field (BF) and high angle annular dark field (HAADF) STEM images of the Al-Si junction enwrapped in a 9 nm thick SiO<sub>2</sub> shell of the abrupt Al-Si interface are shown in Figure 1b. The shown NW was grown in (111) direction. Figure 1c shows the subthreshold transfer characteristic of both program modes for different drain biases V<sub>D</sub>, ranging from 250 mV to 1 V in 250 mV steps. Note that,  $V_D$  was set to positive biases and thus causing the fanning to be evident in the p-type transfer characteristic due to the induced band bending mechanism (see Figure S2, Supporting Information). Remarkably, at  $V_D = 1$  V an  $I_{\rm on}/I_{\rm off}$  ratio of 10<sup>7</sup> is achieved for  $|V_{\rm CG}| = 5$  V. Importantly and different to conventional MOSFETs, the off-current is V<sub>D</sub>-independent and ultra-low (below the sensitivity limit of our measurement equipment). This indicates efficient suppression of the static power consumption in the off-state as well as suppression of gate induced barrier lowering (GIDL) as enabled by the RFET device principle. Interestingly, the on-current (in brackets normalized to the diameter of the NW) for n-type operation is  $I_{on}^n = 422$  nA (4.7  $\mu$ A  $\mu$ m<sup>-1</sup>) and  $I_{on}^p = 2.26 \mu$ A (25.4  $\mu$ A  $\mu$ m<sup>-1</sup>) for p-type operation. Regarding the on-currents the diameter (here:  $d_{\rm NW}$  = 80 nm) needs to be taken into account as well, as it is not possible to fully deplete the semiconductor in comparison to thinner NWs.[57] Lately, it was shown that the Al-Si exchange can also be used on SOI-based nanosheets,<sup>[38]</sup> allowing a convenient way to increase on-current by fabricating parallel arrays of nanosheets. It was also shown that contact printed NWs allow to be integrated in parallel arrays as well.<sup>[58]</sup> Consequently, the proposed Al-Si NW RFET, revealed an on-current level symmetry factor of ≈5 between n- and p-type operation. At a first glance the difference seems large but it is substantially lower compared to prior-art Si based RFETs with state-of-the-art nickel silicide contacts, [57,59-61] reaching asymmetry ratios 2-5 times larger than with the here proposed Al-Si system. The relatively high symmetry was achieved without any additional efforts, as that is, precise strain engineering<sup>[62]</sup> or asymmetric biasing of program voltages. A more detailed comparison of the most relevant transistor parameters of Si- and Ge-based RFETs can be found in the supporting information (see Table S1, Supporting Information).

Analyzing the effective Schottky barrier heights (eSBHs) of the proposed material system at different biases, reveals 119 meV for electron injection and 82 meV for hole injection, indicating substantial barriers for both polarities and explaining the observed level of symmetry of the on-currents. Although, somewhat similar effective eSBHs for both carrier types were measured,<sup>[38]</sup> a small difference is still evident. This can be attributed to the fact, that the effective tunneling masses of electrons and holes in Si differ, further influencing the tunneling probability<sup>[63]</sup> and thus the on-state of the RFET. Due to the excellent quality of the thermally grown SiO<sub>2</sub> gate dielectric in respect to the density of trap states<sup>[63]</sup> and fixed charges, as well as minimal Au and amorphous Si contamination of the as-grown NW surface,<sup>[64]</sup> no remarkable shift of the threshold voltage is observable. The high quality of the surface oxide is also reflected in the minimal hysteresis, observed when sweeping  $V_{CG}$  (see Figure S3, Supporting Information). Evaluating temperaturedependent transfer characteristics at elevated temperatures showed that the characteristic gets shifted to higher current values, likely reflecting a higher intrinsic carrier concentration and higher rate of injection of charge carriers from the Al-Si heterojunctions (see Figure S4, Supporting Information). In n-type operation a threshold voltage of  $V_{\rm th}$  = 500 mV and in p-type operation  $V_{\rm th} = -600$  mV was extracted by utilizing the transconductance method (see Figure S5, Supporting Information).<sup>[65]</sup> The presented device shows subthreshold slopes of S = 216 and 366 mV dec<sup>-1</sup> for n- and p-type, respectively. In order to lower the inverse subthreshold slope *S* and the threshold voltage  $V_{\rm th}$  for future implementation of the presented Al-Si based RFET platform, the effective gate oxide thickness (EOT) needs to be reduced, either by thinning down the SiO<sub>2</sub> or implementing conventional high- $\kappa$  gate dielectrics.<sup>[66]</sup>

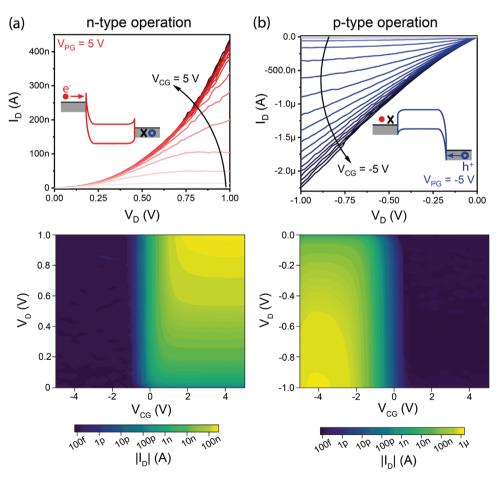

To complement the electrical characterization of the proposed Al-Si NW RFET, the output characteristic as well as the conductance map of the n- and p-type operation mode is discussed. **Figure 2**a shows the I/V characteristic for n-type operation in combination with the corresponding drain–source conductance map for positive drain biases  $V_D$  and positive  $V_{PG}$ . The respective I/V characteristic as well as conductance map for the p-type operation is illustrated in Figure 2b with negative bias voltages  $V_D$  and negative  $V_{PG}$ . In both operation modes, a nonlinear increase of the  $V_{CG}$ -dependent I/Vs is evident, which is a signature of the progressive tuning of the barrier shape and is a typical feature of SBFETs.<sup>[53,62]</sup> Importantly, the conductance maps reveal the well-defined on- and off-state of the proposed Al-Si NW RFET. This representation

**Figure 2.** Linear *I/V* characteristic and semi-logarithmic conductance map of the a) n-type ( $V_{PG} = 5$  V) and b) p-type ( $V_{PG} = -5$  V) operation. Here,  $V_{CG}$  was increased in 250 mV steps. The respective band diagrams for the on-state are shown in the insets. The conductance maps reveal unipolar characteristics and well-defined on- and off-states in both operation modes.

confirms the operational stability of our devices, for example, due to voltage variabilities in the applied circuits. Consequently, these conductance maps allow us to derive optimal operation points of the device. Due to the relatively high on-current as well as threshold voltage symmetry, the Al-Si material system allows the realization of well-defined operation modes of RFETs, enabling reconfigurable logic gates. For the Al-Si-Al based RFET, an absolute value of  $|V_{PG}| = |V_{CG}| = V_D = 3$  V was determined for the ideal operation of logic gates, as this bias level sufficiently tunes the incorporated energy landscape of the semiconductor as well as drives an appropriate drain current. In this respect, additional investigations (see Figure S6, Supporting Information) were carried out to evaluate equal voltage levels for the top-gate voltages as well as drain biases. We want to note, that the application of a shorter channel region and a thinner or different gate-dielectric with higher  $\kappa$  would allow to decrease the supply voltages without performance penalty.<sup>[54]</sup>

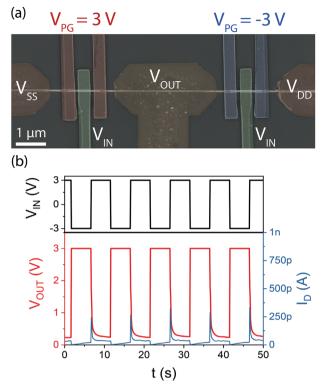

To illustrate the capabilities of the Al-Si material system for reconfigurable logic, the proposed RFETs were first integrated into a complementary inverter utilizing the presented Al-Si RFET devices. To this end, one RFET is operated in n-mode (pull-down transistor) by applying  $V_{PG} = 3$  V, whereas the pull-up transistor is operated in p-mode with  $V_{PG} = -3$  V. This reveals one of the key advantages of RFETs, which is the capability to use the exact same device layout that is, geometry and composition for both n- and p-type operation, enabling a vast variety of applications such as functional diverse adaptive computing and hardware secure circuits.<sup>[24,27,67]</sup> Demonstrating this fundamental logic gate, the proposed Al-Si NW RFET architecture proofs the applicability of the Al-Si RFET platform to be implemented in complementary logic gates. Figure 3 shows the realized complementary inverter based on the presented Al-Si RFET device. As the NWs exhibit overall lengths of  $L \approx 20 \ \mu m$ , the inverter can be implemented in 1D, that is, along a single NW, as also showed by Heinzig et al., in NiSi2-Si NW RFETs<sup>[68]</sup> encompassing in our case two Si regions and three Al segments. Therein one segment is configured deliberately as n- or p-type mode. Figure 3b shows the transient operation of the inverter:  $V_{IN}$  is driven by a function generator to determine the response on the output. Utilizing this configuration allows us to analyze the output signal V<sub>OUT</sub> and shows the expected toggling between the supply voltages  $V_{DD}$  and  $V_{SS}$ , where  $V_{DD} = 3$  V and  $V_{SS} = 0$  V. Note that the input signal is fed to both RFETs via the CGs. Importantly, the operation is ensured with a single voltage of 3 V. The complementary nature of the proposed inverter becomes evident by evaluating the current through the two RFETs in series, which reveals negligible current flow at the stable states and only current-peaks of ≈200 pA at the transient condition exactly at the switching points of the input voltage. Exchanging the potential of V<sub>PG</sub> and in consequence also configuring both RFETs to the opposite mode, leads to qualitatively the same results, which is an important prerequisite for circuit and layout designers, as the flexibility of the proposed inverter is highly increased in comparison to static CMOS technology when building up more complex combinational logic gates. Care was taken to adjust the supply-rail voltages  $V_{DD}$  and  $V_{SS}$ appropriately. To manage this signal overhead in more complex gates a concept for exchanging the supply line voltages on-thefly was presented by Trommer et al.<sup>[26]</sup> Through the use of a

**Figure 3.** a) Colored SEM image of two Al-Si-Al NW heterostructurebased RFETs in series, realizing a complementary inverter by exploiting reconfiguration on transistor level. b) Transient operation of the proposed inverter with top-gate voltages as well as a drain bias of |3V|. The drain current  $I_D$  shows an explicit complementary function of the presented inverter.

single inverter the supply lines as well as the program voltage can be flipped jointly, allowing for a full output swing of the logic gates.

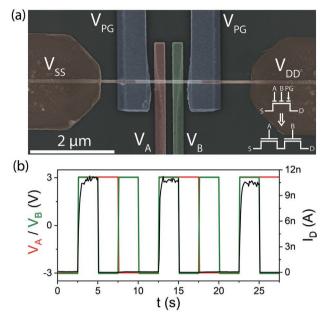

As an extension to the complementary design of the inverter, the realization of a wired-AND gate can be facilitated by adding a second CG in the middle of the Si channel, resulting in an additional electrode to turn the RFET on and off. Consequently, the two CGs can be used as input signals enabling a wired-AND gate.<sup>[25,29]</sup> Figure 4a shows a colored SEM image of the used device architecture with two CGs between the PGs. As for the wired-AND gate the current through the transistor defines the logical output, adapting to conventional CMOS technology, a resistor or even another three top-gate Al-Si NW RFET can be used to convert the current to a logical output at a desired voltage level. This once more underscores the flexibility of the presented device architecture. Due to its suitability to drive appropriate currents, it is well-suited as a replacement for NAND logic realized with conventional MOSFET technology (see Figure S7, Supporting Information). Moreover, it allows the reduction of the transistor count in multiple input NAND and NOR circuits, as two MOSFETs can be combined in a single device (inset in Figure 4a). Importantly, the number of inputs can be increased for the realization of multi-input logic cells, as its capability is merely limited by the length of the semiconducting channel. In this respect, top-down fabricated nanostructures<sup>[38]</sup> are of high relevance as the NW

**Figure 4.** a) Colored SEM image of a multi control-gate Al-Si-Al NW heterostructure based RFET, realizing a wired-AND gate. In the right lower inset the equivalent symbol in comparison to conventional CMOS technology is illustrated. b) Transient operation of the proposed gate operated in *n*-mode ( $V_{PG} = 3$  V).  $V_A$  is driven with 0.1 Hz and  $V_B$  with 0.2 Hz. Here,  $V_{DD} = 3$  V and  $V_{SS} = 0$  V. The current  $I_{DD}$  through the device defines the output of the wired-AND gate.

positioning can be carried out deterministically. Analyzing the transient operation mode of the wired-AND gate in Figure 4b reveals its capability of properly suppressing the current in the off-state as well as shows on-currents of ≈10 nA in n-type operation mode. The excellent current driveability allows the realization of logical gates with dedicated pull-up and pull-down networks, as proposed alternatively to conventional NAND logic cells (see Figure S7, Supporting Information). While the current levels of a device based on a single NW reveals currents in the nA range, utilizing a parallel array of NWs by top-down fabrication would allow an effective up-scaling of the current.<sup>[69]</sup> As the wired-AND gate is an extension of the previously presented RFET, this logic cell can also be operated in p-type operation mode by setting  $V_{PG} = -3$  V. In this configuration the current is driven when both input signals,  $V_{\rm A}$  and  $V_{\rm B}$  are at -3 V, expressing a high degree of flexibility for circuit and layout designers in addition to the symmetric device layout of the RFET device architecture. As this paper demonstrates the capability of the Al-Si material system to be integrated as basic logic cells, no dedicated investigations on higher frequencies were done. Nevertheless, mixed mode TCAD simulations have already shown operability of Si-based RFETs in the GHz-regime.<sup>[54]</sup>

# 3. Conclusion

In conclusion, we have embedded a monocrystalline Al-Si-Al NW heterostrucutre with abrupt Schottky nanojunctions and single elementary metal leads into a three-gate RFET ADVANCED ELECTRONIC MATERIALS www.advelectronicmat.de

architecture capable of dynamically switching between n- and p-type operation. Key advantage of the proposed platform is a high degree of symmetry in terms of on-currents and threshold voltages. Operating the device in n- or p-type operation mode lead to on-currents  $I_{on}^{n} = 422 \text{ nA}/I_{on}^{p} = 2.26 \mu\text{A}$ , threshold voltages  $V_{th}^n = 500 \text{ mV}/V_{th}^p = -600 \text{ mV}$  and subthreshold slopes  $S^n = 216 \text{ mV dec}^{-1}/S^p = 366 \text{ mV dec}^{-1}$ . Evaluating the output characteristic and investigating the corresponding conductance maps, an optimal operation point for the realization of a complementary inverter was determined operating at the same voltage levels for both the supply and the input voltage (here: [3 V]). The inverter was realized implementing two RFETs in series based on a single NW. Underlining the flexibility of the presented RFET platform, a CMOS compatible wired-AND gate is shown based on a dual CG device architecture. Such multi-CG RFETs allow a reduction in the transistor count in logic circuits such as NAND gates, where multiple MOSFETs can be combined in a single device. Most importantly, systematically investigating multi-gate transistor architectures, we have demonstrated a high degree of flexibility of the proposed Al-Si based RFETs, which can become a key enabler for the realization of reconfigurable electronics based on single elementary metal-semiconductor heterostructures. Most notably, concepts like the proposed wired-AND feature a high potential as an extension to conventional CMOS technology. In this respect, our investigations might provide a significant step toward beyond-CMOS logic enabling diversification and alternative computing paradigms.

# 4. Experimental Section

Device Fabrication: The Si NWs used were grown by a Au particle mediated growth via the vapor liquid solid growth mechanism. The NWs typical had diameters of  $d_{NW} = 80$  nm and predominant (111) crystal axis direction. The nominally undoped nanowires were thermally oxidized at T = 1174 K in O<sub>2</sub> atmosphere for 3 min and annealed for 3 min in N<sub>2</sub> atmosphere to employ a high-quality SiO<sub>2</sub> gate-oxide. The oxidized Si NWs were drop-casted onto a 100 nm thick thermally grown SiO<sub>2</sub> layer atop of a 500  $\mu$ m thick highly p-doped Si substrate. Al contacts to the Si NWs were patterned by electron beam lithography, 15 s of BHF (7:1) etching to remove the SiO<sub>2</sub>-shell at the contact area, and subsequent 125 nm Al sputter deposition and lift-off techniques. Rapid thermal annealing at a temperature of T = 774 K in forming-gas atmosphere was employed to initiate the Al-Si exchange to achieve the desired Si channel length. For RFET integration, omega-shaped Ti/Au top gates were fabricated using electron beam lithography, Ti/Au evaporation (8 nm Ti, 125 nm Au), and lift-off techniques.

BF and HAADF STEM: BF STEM was performed on Al-Si-Al NW heterostructures fabricated on 40 nm thick Si<sub>3</sub>N<sub>4</sub> membranes using a probe-corrected FEI Titan Themis, working at 200 kV. The Al-Si interface in the shown images was viewed along the [110] direction of observation of the Si crystal.

*Electrical Characterization*: The electrical measurements were performed using a combination of a HP 4156B semiconductor analyzer and a probe station. To minimize the influence of ambient light as well as electromagnetic fields, the probe station was placed in a dark box. The input signals for the inverter and wired-AND gate were generated by a Yokogawa FG300 function generator connected to VMUs of the semiconductor analyzer. Temperature dependent measurements as well as measurements to extract the effective Schottky barrier heights were performed in vacuum using a LakeShore PS-100 cryogenic probe station and a Keysight B1500A semiconductor analyzer.

ADVANCED SCIENCE NEWS \_\_\_\_\_

## **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

# Acknowledgements

The authors gratefully acknowledge financial support by the Austrian Science Fund (FWF) project No.: I 5383-N. The NW synthesis was supported by grant DMR-2121643 from the U.S. National Science Foundation. The authors further thank the Center for Micro- and Nanostructures for providing the cleanroom facilities.

## **Conflict of Interest**

The authors declare no conflict of interest.

## **Author Contributions**

M.S. and R.B. performed the device fabrication. R.B., L.W., and M.S. conducted the electrical measurements. M.I.d.H. carried out the TEM analysis. Z.S.-M. fabricated the SiN membranes used for TEM investigation. C.G.E.M. and J.F.C. have grown the Si NWs. M.S and W.M.W. conceived the project and contributed essentially to the experimental design. All authors analyzed the results and agreed on the manuscript.

#### **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Keywords**

aluminum, logic gates, metal-semiconductor heterostructures, reconfigurable electronics, Schottky barrier field-effect transistors, silicon

Received: May 22, 2022 Revised: August 4, 2022 Published online:

- [1] A. Haroun, X. Le, S. Gao, B. Dong, T. He, Z. Zhang, F. Wen, S. Xu, C. Lee, *Nano Express* **2021**, *2*, 022005.

- [2] K. J. Kuhn, IEEE Trans. Electron Devices 2012, 59, 1813.

- [3] W. Weber, A. Heinzig, J. Trommer, D. Martin, M. Grube, T. Mikolajick, Solid-State Electron. 2014, 102, 12.

- [4] A. Heinzig, S. Slesazeck, F. Kreupl, T. Mikolajick, W. M. Weber, *Nano Lett.* **2012**, *12*, 119.

- [5] T. Mikolajick, G. Galderisi, S. Rai, M. Simon, R. Böckle, M. Sistani, C. Cakirlar, N. Bhattacharjee, T. Mauersberger, A. Heinzig, A. Kumar, W. Weber, J. Trommer, *Solid-State Electron.* **2022**, *194*, 108381.

- [6] W. M. Weber, L. Geelhaar, L. Lamagna, M. Fanciulli, F. Kreupl, E. Unger, H. Riechert, G. Scarpa, P. Lugli, in 2008 8th IEEE Conf. on Nanotechnology, IEEE, Piscataway, NJ 2008, p. 580.

- [7] F. Wessely, T. Krauss, U. Schwalke, Solid-State Electron. 2012, 70, 33.

- [8] M. De Marchi, D. Sacchetto, S. Frache, J. Zhang, P.-E. Gaillardon, Y. Leblebici, G. De Micheli, in *Proc. 2012 Int. Electron Devices Meeting*, IEEE, Piscataway, NJ **2012**, pp. 8.4.1–8.4.4.

- [9] M. Mongillo, P. Spathis, G. Katsaros, P. Gentile, S. De Franceschi, Nano Lett. 2012, 12, 3074.

- [10] K. E. Moselund, H. E. Riel, US9293467B2, 2013.

- [11] R. Ranjith, R. S. Komaragiri, K. J. Suja, in Proc. 2016 IEEE Annual India Conf., INDICON 2016, IEEE, Piscataway, NJ 2017, pp. 1–6.

- [12] W. J. Lee, H. T. kwon, H.-S. Choi, D. Wee, S. Kim, Y. Kim, *IEICE Electron. Express* 2017, 14, 20170758.

- [13] P. Wu, T. Ameen, H. Zhang, L. A. Bendersky, H. Ilatikhameneh, G. Klimeck, R. Rahman, A. V. Davydov, J. Appenzeller, ACS Nano 2019, 13, 377.

- [14] K. Vipin, S. A. Fahmy, ACM Comput. Surv. 2018, 51, 72.

- [15] S. J. Park, D. Y. Jeon, V. Sessi, J. Trommer, A. Heinzig, T. Mikolajick, G. T. Kim, W. M. Weber, ACS Appl. Mater. Interfaces 2020, 12, 43927.

- [16] T. Baldauf, A. Heinzig, J. Trommer, T. Mikolajick, W. M. Weber, IEEE Electron Device Lett. 2015, 36, 991.

- [17] R. Böckle, M. Sistani, B. Lipovec, D. Pohl, B. Rellinghaus, A. Lugstein, W. M. Weber, Adv. Mater. Technol. 2022, 7, 2100647.

- [18] J. Trommer, A. Heinzig, U. Mühle, M. Löffler, A. Winzer, P. M. Jordan, J. Beister, T. Baldauf, M. Geidel, B. Adolphi, E. Zschech, T. Mikolajick, W. M. Weber, ACS Nano 2017, 11, 1704.

- [19] M. Sistani, R. Böckle, D. Falkensteiner, M. A. Luong, M. I. Den Hertog, A. Lugstein, W. M. Weber, ACS Nano 2021, 15, 18135.

- [20] G. V. Resta, S. Sutar, Y. Balaji, D. Lin, P. Raghavan, I. Radu, F. Catthoor, A. Thean, P. E. Gaillardon, G. De Micheli, *Sci. Rep.* 2016, 6, 29448.

- [21] C. S. Pang, Z. Chen, in Proc. Device Research Conf. Conf. Digest, DRC, IEEE, Piscataway, NJ 2018, pp. 1–2.

- [22] S. Nakaharai, M. Yamamoto, K. Ueno, Y. F. Lin, S. L. Li, K. Tsukagoshi, ACS Nano 2015, 9, 5976.

- [23] S. Larentis, B. Fallahazad, H. C. Movva, K. Kim, A. Rai, T. Taniguchi, K. Watanabe, S. K. Banerjee, E. Tutuc, ACS Nano 2017, 11, 4832.

- [24] P. Wu, D. Reis, X. S. Hu, J. Appenzeller, Nat. Electron. 2021, 4, 45.

- [25] J. Trommer, A. Heinzig, T. Baldauf, T. Mikolajick, W. M. Weber, M. Raitza, M. Völp, in *Proc. of the 2016 Design, Automation and Test in Europe Conf. and Exhibition*, IEEE, Piscataway, NJ **2016**, pp. 169–174.

- [26] J. Trommer, A. Heinzig, S. Slesazeck, T. Mikolajick, W. M. Weber, IEEE Electron Device Lett. 2014, 35, 141.

- [27] S. Rai, A. Rupani, P. Nath, A. Kumar, in *Proc. of IEEE Computer Society Annual Symposium on VLSI, ISVLSI*, IEEE, Piscataway, NJ 2019, pp. 663–669.

- [28] M. D. Marchi, J. Zhang, S. Frache, D. Sacchetto, P.-E. Gaillardon, Y. Leblebici, G. D. Micheli, *IEEE Electron Device Lett.* 2014, 35, 880.

- [29] M. Simon, J. Trommer, B. Liang, D. Fischer, T. Baldauf, M. B. Khan, A. Heinzig, M. Knaut, Y. M. Georgiev, A. Erbe, J. W. Bartha, T. Mikolaiick, W. M. Weber, in *Proc. Device Research Conf. - Conf. Digest, DRC*, IEEE, Piscataway, NJ **2018**, pp. 1–2.

- [30] J. Zhang, P. E. Gaillardon, G. De Micheli, in Proc. IEEE Int. Symp. Circuits System, IEEE, Piscataway, NJ 2013, pp. 2111–2114.

- [31] J. Trommer, M. Simon, S. Slesazeck, W. M. Weber, T. Mikolajick, IEEE J. Electron Devices Soc. 2020, 8, 740.

- [32] D. Vana, P. E. Gaillardon, A. Teman, IEEE Trans. Nanotechnol. 2020, 19, 123.

- [33] N. Breil, C. Lavoie, A. Ozcan, F. Baumann, N. Klymko, K. Nummy, B. Sun, J. Jordan-Sweet, J. Yu, F. Zhu, S. Narasimha, M. Chudzik, *Microelectron. Eng.* 2015, 137, 79.

- [34] J. A. Kittl, A. Lauwers, O. Chamirian, M. Van Dal, A. Akheyar, M. De Potter, R. Lindsay, K. Maex, *Microelectron. Eng.* 2003, 70, 158.

- [35] J. A. Kittl, K. Opsomer, C. Torregiani, C. Demeurisse, S. Mertens, D. P. Brunco, M. J. Van Dal, A. Lauwers, *Mater. Sci. Eng.*, B 2008, 154–155, 144.

#### **ADVANCED** SCIENCE NEWS

www.advancedsciencenews.com

- [36] K. El hajraoui, M. A. Luong, E. Robin, F. Brunbauer, C. Zeiner, A. Lugstein, P. Gentile, J.-L. Rouvière, M. Den Hertog, *Nano Lett.* 2019, 19, 2897.

- [37] M. Sistani, M. A. Luong, M. I. den Hertog, E. Robin, M. Spies, B. Fernandez, J. Yao, E. Bertagnolli, A. Lugstein, *Nano Lett.* 2018, 18, 7692.

- [38] L. Wind, R. Böckle, M. Sistani, P. Schweizer, X. Maeder, J. Michler, C. G. Murphey, J. Cahoon, W. M. Weber, ACS Appl. Mater. Interfaces 2022, 14, 26238.

- [39] W. M. Weber, J. Trommer, A. Heinzig, T. Mikolajick, in *Functionality-Enhanced Devices: An Alternative to Moore's Law* (Ed: P.-E. Gaillardon), Institution of Engineering and Technology, Savoy Place, London 2018, ch. 2, p. 13.

- [40] F. Fuchs, M. Bilal Khan, D. Deb, D. Pohl, J. Schuster, W. M. Weber, U. Mühle, M. Löffler, Y. M. Georgiev, A. Erbe, S. Gemming, J. Appl. Phys. 2020, 128, 085301.

- [41] S. F. Feste, M. Zhang, J. Knoch, S. Mantl, Solid-State Electron. 2009, 53, 418.

- [42] C. Lavoie, C. Detavernier, C. Cabral, F. M. d'Heurle, A. J. Kellock, J. Jordan-Sweet, J. M. Harper, *Microelectron. Eng.* 2006, 83, 2042.

- [43] B. Zhang, W. Yu, Q. T. Zhao, G. Mussler, L. Jin, D. Buca, B. Holländer, J. M. Hartmann, M. Zhang, X. Wang, S. Mantl, *Appl. Phys. Lett.* 2011, *98*, 252101.

- [44] L. Knoll, Q. T. Zhao, S. Habicht, C. Urban, K. K. Bourdelle, S. Mantl, in Proc. 2010 Int. Workshop on Junction Technology Extended Abstracts, IEEE, Piscataway, NJ 2010, pp. 1–5.

- [45] M. B. Khan, D. Deb, J. Kerbusch, F. Fuchs, M. Löffler, S. Banerjee, U. Mühle, W. M. Weber, S. Gemming, J. Schuster, A. Erbe, Y. M. Georgiev, Appl. Sci. 2019, 9, 3462.

- [46] L. Yu, P. R. I. Cabarrocas, Phys. Rev. B Conden. Matter Mater. Phys. 2010, 81, 085323.

- [47] R. Hu, S. Xu, J. Wang, Y. Shi, J. Xu, K. Chen, L. Yu, Nano Lett. 2020, 20, 7489.

- [48] M. B. Khan, D. Deb, J. Kerbusch, F. Fuchs, M. Löffler, S. Banerjee, U. Mühle, W. M. Weber, S. Gemming, J. Schuster, A. Erbe, Y. M. Georgiev, Appl. Sci. 2019, 9, 3462.

- [49] M. Simon, R. Mizuta, Y. Fan, A. Tahn, D. Pohl, J. Trommer, S. Hofmann, T. Mikolajick, W. M. Weber, ACS Appl. Nano Mater. 2021, 4, 4371.

- [50] T. Mikolajick, A. Heinzig, J. Trommer, T. Baldauf, W. M. Weber, Semicond. Sci. Technol. 2017, 32, 043001.

- [51] W. M. Weber, A. Heinzig, J. Trommer, D. Martin, M. Grube, T. Mikolajick, Solid-State Electron. 2014, 102, 12.

- [52] W. M. Weber, J. Trommer, M. Grube, A. Heinzig, M. Konig, T. Mikolajick, in *Design, Automation and Test in Europe Conf. and Exhibition*, 2014, IEEE, Piscataway, NJ 2014, pp. 1–6.

- [53] J. Knoch, M. Zhang, J. Appenzeller, S. Mantl, Appl. Phys. A 2007, 87, 351.

- [54] T. Baldauf, A. Heinzig, T. Mikolajick, W. M. Weber, in Proc. 2019 Joint Int. EUROSOI Workshop and Int. Conf. on Ultimate Integration on Silicon, IEEE, Piscataway, NJ 2019, pp. 1–4.

- [55] P. Cadareanu, P.-E. Gaillardon, in Proc. 2019 IEEE 14th Nanotechnology Materials and Devices Conf. (NMDC), IEEE, Piscataway, NJ 2019, pp. 1–4.

- [56] G. Gore, P. Cadareanu, E. Giacomin, P. E. Gaillardon, in *Proc. IEEE/ IFIP Int. Conf. on VLSI and System-on-Chip*, IEEE, Piscataway, NJ 2019, pp. 172–177.

- [57] A. Heinzig, S. Slesazeck, F. Kreupl, T. Mikolajick, W. M. Weber, *Nano Lett.* 2012, 12, 119.

- [58] S. Pregl, A. Heinzig, L. Baraban, G. Cuniberti, T. Mikolajick, W. M. Weber, *IEEE Trans. Nanotechnol.* 2016, 15, 549.

- [59] D. Sacchetto, Y. Leblebici, G. De Micheli, IEEE Electron Device Lett. 2012, 33, 143.

- [60] T. Krauss, F. Wessely, U. Schwalke, ECS J. Solid State Sci. Technol. 2015, 4, 46.

- [61] L. Yojo, R. C. Rangel, K. R. Sasaki, J. A. Martino, in Proc. SBMicro 2017-32nd Symp. on Microelectronics Technology and Devices, IEEE, Piscataway, NJ 2017, pp. 1–4.

- [62] M. Simon, B. Liang, D. Fischer, M. Knaut, A. Tahn, T. Mikolajick, W. M. Weber, *IEEE Electron Device Lett.* 2020, 41, 1110.

- [63] G. Pridham, Electron. Power 1970, 16, 34.

- [64] S. Kim, D. J. Hill, C. W. Pinion, J. D. Christesen, J. R. McBride, J. F. Cahoon, ACS Nano 2017, 11, 4453.

- [65] D. K. Schroder, Semiconductor Material and Device Characterization, John Wiley & Sons, Inc., Hoboken, NJ, **2005**.

- [66] J. Choi, Y. Mao, J. Chang, Mater. Sci. Eng., R 2011, 72, 97.

- [67] T. Mikolajick, G. Galderisi, M. Simon, S. Rai, A. Kumar, A. Heinzig, W. Weber, J. Trommer, *Solid-State Electron*. **2021**, *186*, 108036.

- [68] A. Heinzig, T. Mikolajick, J. Trommer, D. Grimm, W. M. Weber, *Nano Lett.* 2013, 13, 4176.

- [69] S. Pregl, L. Baraban, V. Sessi, T. Mikolajick, W. M. Weber, G. Cuniberti, *IEEE Sens. J.* 2018, 18, 967.