Die approbierte Originalversion dieser Diplom-/Masterarbeit ist an der Hauptbibliothek der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

## **DIPLOMARBEIT**

# A versatile networked embedded platform for KNX/EIB

ausgeführt am

Institut für Rechnergestützte Automation Arbeitsgruppe Automatisierungssysteme der Technischen Universität Wien

unter der Anleitung von

ao. Univ.-Prof. Dipl.-Ing. Dr. Wolfgang Kastner und Univ.-Ass. Dipl.-Ing. Georg Neugschwandtner

durch

Friedrich Praus Hyrtlgasse 18/22 1160 Wien

Wien, 18.10.2005

## **Abstract**

The deployment of home and building automation systems allows to increase comfort, safety and security and reduce operational cost. Today such systems typically follow a hierarchical distributed approach. While control networks interconnect smart sensors and actuators, a backbone network provides the infrastructure for management tasks. Devices interconnecting these networks have a strategic role. Especially in the home domain, the integration of various control and data networks is essential for maximum benefit.

The European Installation Bus (KNX/EIB) is a popular control network designed to enhance electrical installations in buildings. It uses a proprietary twisted pair (TP) medium to interconnect devices like smart light switches and dimmers. The objective of this thesis is to design an embedded and versatile platform for ongoing development in the area of home and building automation systems with a focus on KNX/EIB TP. Besides two KNX/EIB TP interfaces, it provides RS-232, USB and Ethernet connectivity. The platform moreover has sufficient processing power and storage, enabling it to act as a "smart router" or gateway.

The thesis first presents a classification of control network devices. It then discusses the hardware and software requirements for the desired platform. A detailed presentation of its design, implementation and operation with respect to hardware and software follows.

## Kurzfassung

Der Einsatz von Heim- und Gebäudeautomatisierungssystemen ermöglicht gesteigerten Komfort, erhöhte Sicherheit und niedrigere Betriebskosten. Solche Systeme folgen heute in der Regel einem hierarchischen verteilten Ansatz. Während Automationsnetzwerke intelligente Sensoren und Aktuatoren verbinden, stellt ein Backbone die notwendige Infrastruktur für Managementaufgaben zur Verfügung. Geräte, die diese Netzwerke verbinden, nehmen eine strategische Position ein. Insbesondere im Heimbereich ist die Integration verschiedener Automations- und Datennetze unabdingbar, um das Potential auszuschöpfen.

Der weit verbreitete Europäische Installationsbus (KNX/EIB) ergänzt die klassische Elektroinstallation im Gebäude durch ein Automationsnetzwerk. Er verwendet ein eigenes Twisted-Pair (TP) Medium um beispielsweise intelligente Lichtschalter und Dimmer zu verknüpfen. Das Ziel dieser Arbeit ist eine vielseitige Embedded-Plattform zu entwerfen, die für zukünftige Arbeiten im Bereich der Heim- und Gebäudeautomation mit Fokus auf KNX/EIB TP herangezogen werden kann. Neben zwei KNX/EIB TP Schnittstellen beinhaltet sie RS-232, USB und Ethernet. Die Plattform stellt darüber hinaus ausreichend Rechenleistung und Speicherkapazität zur Verfügung, um als "intelligenter Router" oder Gateway zu dienen.

Die vorliegende Diplomarbeit klassifiziert zunächst Geräte der Gebäude- und Heimautomation. Nachfolgend werden Hardware- und Software-Anforderungen für die zu entwickelnde Plattform diskutiert. Eine Präsentation des Designs, der praktischen Umsetzung und der Anwendung sowohl der Hard- als auch der Software bildet den Kernpunkt der Arbeit.

# **Danksagung**

Ich möchte mich an dieser Stelle bei allen Menschen bedanken, die mich während meines Studiums und besonders bei der Erstellung dieser Diplomarbeit begleitet haben.

Mein besonderer Dank gilt meinen Eltern für die Förderung meiner Ausbildung und ihre ständige Unterstützung.

Weiters möchte ich meinem Betreuer Wolfgang Kastner sowie Georg Neugschwandtner für die großartige Betreung und ständige Hilfsbereitschaft danken.

Vielen Dank an Bernhard Greissing für die Hilfe bei der Platinenbestückung. Ohne ihn wäre diese nicht so schnell, einfach und perfekt gelungen. Großen Dank auch an Oliver Alt für die ständige Hilfe.

Einen herzlichen Dank auch an meine Studienkollegen Woif, Jensi, Benno und Gerd für die gegenseitige Unterstützung, abwechslungsreiche Studienzeit und das Korrekturlesen.

# **Contents**

| 1 | Intr | oduction                                   | 9  |

|---|------|--------------------------------------------|----|

|   | 1.1  | Home and Building Automation               | 9  |

|   | 1.2  | KNX/EIB overview                           | 12 |

|   | 1.3  | KNX/EIB device classes and market overview | 13 |

|   |      | 1.3.1 Interaction devices                  | 15 |

|   |      | 1.3.2 Routers                              | 16 |

|   |      | 1.3.3 Gateways                             | 17 |

|   |      | 1.3.4 PC-based                             | 19 |

|   | 1.4  | Outlook on remaining sections              | 20 |

| 2 | Inte | rfaces                                     | 21 |

|   | 2.1  | Serial interfacing                         | 22 |

|   |      | 2.1.1 BCU                                  | 24 |

|   |      | 2.1.2 BIM                                  | 26 |

|   |      | 2.1.3 TP-UART                              | 26 |

|   | 2.2  | USB interfacing                            | 27 |

|   |      | 2.2.1 Introduction to USB                  | 27 |

|   |      | 2.2.2 KNX on USB                           | 31 |

|   | 2.3  | IP interfacing                             | 36 |

|   |      | 2.3.1 EIBlib/IP                            | 36 |

|   |      | 2.3.2 EIBnet/IP                            | 38 |

| 3 | Reg  | uirements                                  | 45 |

|   | 3.1  | Hardware                                   | 46 |

|   |      | 3.1.1 Microcontroller                      | 46 |

|   |      | 3.1.2 Ethernet controller                  | 47 |

|   |      | 3.1.3 KNX/EIB connection                   | 47 |

|   |      | 3.1.4 USB support                          | 47 |

|   |      | 3.1.5 Additional components                | 47 |

|   | 3.2  | Software                                   | 48 |

|   |      | 3.2.1 Development                          | 48 |

|   |      | 3.2.2 Implementation                       | 48 |

| 4 | Har  | dware                                      | 49 |

|   | 4.1  | Selection of components                    | 49 |

|   |      | 4.1.1 Microcontroller                      | 50 |

|    |         | 4.1.2   | Ethernet controller    | . 52 |

|----|---------|---------|------------------------|------|

|    |         | 4.1.3   | KNX/EIB connection     | . 54 |

|    | 4.2     | Design  |                        | . 55 |

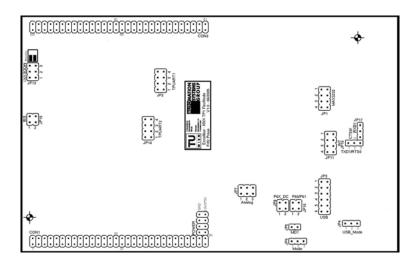

|    |         | 4.2.1   | PCB design             | . 57 |

|    |         | 4.2.2   | Power supply           | . 58 |

|    |         | 4.2.3   | MB90F334A              | . 59 |

|    |         | 4.2.4   | CS8900A                | . 61 |

|    |         | 4.2.5   | RS232                  | . 63 |

|    |         | 4.2.6   | TP-UART                | . 63 |

|    |         | 4.2.7   | USB connection         | . 64 |

|    |         | 4.2.8   | SD/MMC card connection | . 64 |

|    | 4.3     | Usage   |                        | . 65 |

| _  | ~ .     |         |                        |      |

| 5  | Softv   |         |                        | 70   |

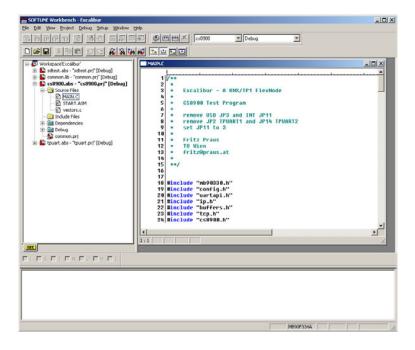

|    | 5.1     |         | sation and usage       |      |

|    |         | 5.1.1   | Development tools      |      |

|    |         | 5.1.2   | Usage                  |      |

|    | 5.2     |         | vel firmware           |      |

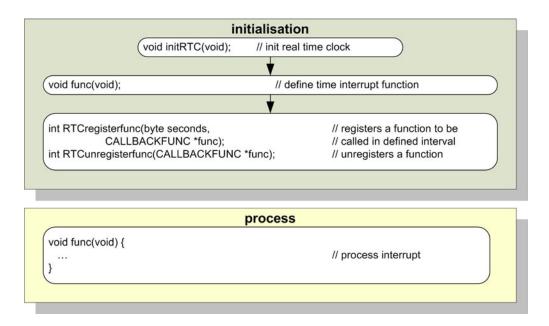

|    |         | 5.2.1   | Timer                  |      |

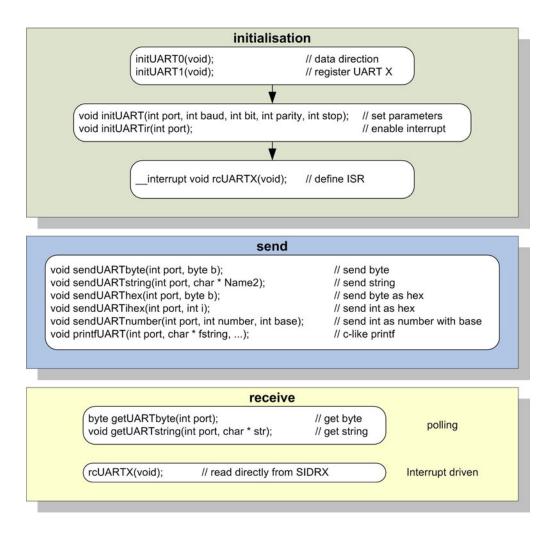

|    |         | 5.2.2   | UART                   |      |

|    |         | 5.2.3   | TP-UART                |      |

|    |         | 5.2.4   | SD/MMC                 |      |

|    |         | 5.2.5   | CS8900A                |      |

|    |         | 5.2.6   | USB                    |      |

|    |         | 5.2.7   | Test tools             |      |

|    | 5.3     |         | rk protocol stacks     |      |

|    |         | 5.3.1   | IP                     |      |

|    |         | 5.3.2   | Webserver              |      |

|    |         | 5.3.3   | BASys integration      | . 95 |

|    |         | 5.3.4   | EIBnet/IP              | . 95 |

|    |         | 5.3.5   | cEMI                   | . 97 |

|    |         | 5.3.6   | Tweety                 | . 98 |

| 6  | Sum     | mory o  | nd outlook             | 99   |

| U  | Suill   | mary al | iiu vuuvok             | 77   |

| Li | st of F | igures  |                        | 101  |

| Li | st of T | ables   |                        | 103  |

| Ac | cronyı      | ms                              | 104 |

|----|-------------|---------------------------------|-----|

| Re | feren       | ces                             | 108 |

| A  | App         | endix                           | 114 |

|    | <b>A.</b> 1 | Internet links                  | 114 |

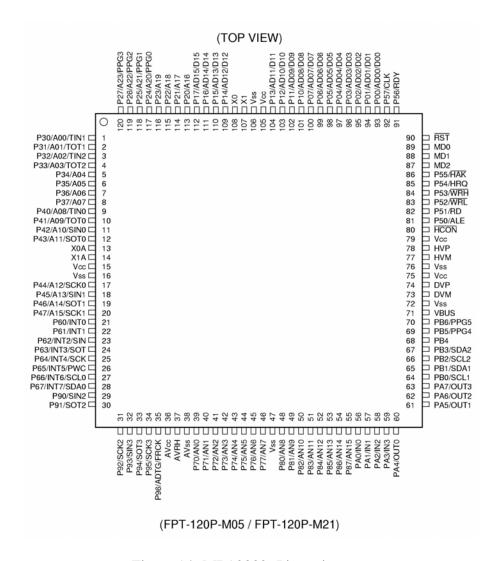

|    | A.2         | MB90330: Pin description        | 115 |

|    | A.3         | MB90330: Memory map             | 122 |

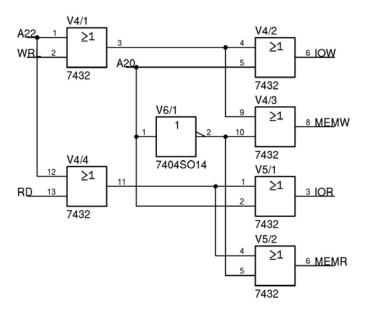

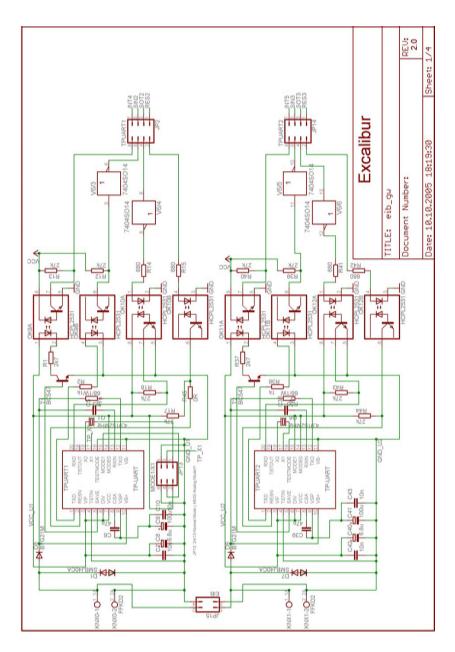

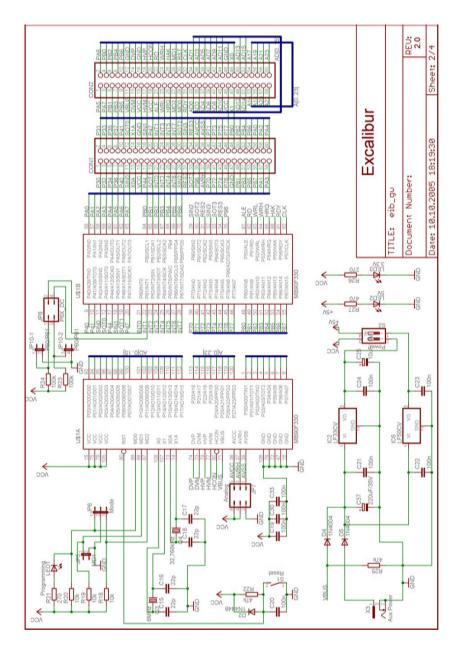

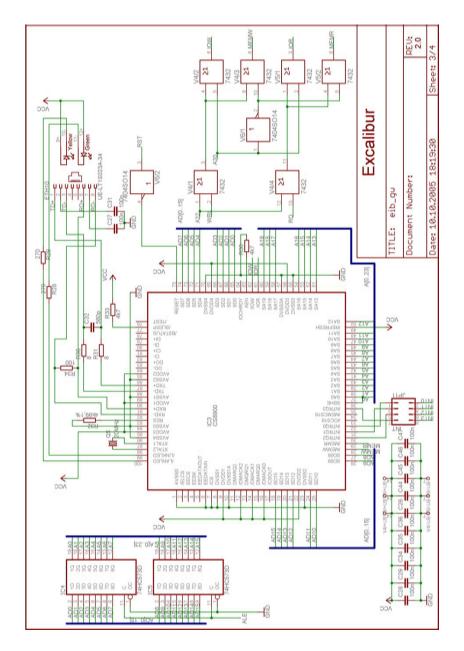

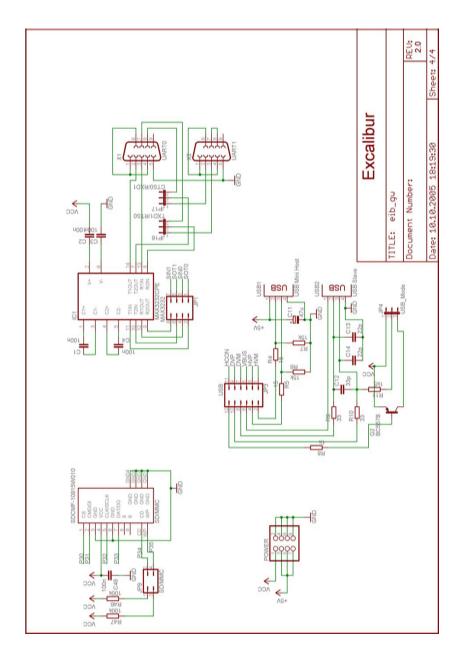

|    | A.4         | KNXcalibur: Schematic diagram   | 123 |

|    | A.5         | KNXcalibur: Part list           | 127 |

|    | A.6         | KNXcalibur: Component placement | 130 |

|    | Δ7          | KNXcalibur: Roard               | 132 |

| "Whoso shall pull this Sword forth of the stone Is rightwise king, born of all England." |

|------------------------------------------------------------------------------------------|

| Cram, Ralph Adams, Excalibur: An Arthurian Drama (1893)                                  |

|                                                                                          |

|                                                                                          |

| Excalibur is considered as one of the most powerful fictional swords.                    |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

## 1 Introduction

## 1.1 Home and Building Automation

Home Automation Systems (HASs) and Building Automation Systems (BASs) aim at improving interaction and communication between devices typically found in buildings. The term HAS refers to small-scale installations in the residential context whereas the term BAS denotes large functional buildings like office buildings and hospitals. Requirements, expectations and complexity are different in both domains, but for both the exchange of control data is a key issue. Small, sporadically occurring data amounts have to be transferred robustly over long distances.

The core application area is environmental control with other possibilities being integrated more and more. Devices potentially participating in HASs and BASs can be classified according to their function [37]:

- Lighting and window blinds

- Heating, Ventilation and Air conditioning (HVAC) systems, including domestic water heating

- White goods (household appliances), like a washing machine or stove

- Brown goods (audio/video or home theatre equipment, game consoles)

- Communications equipment (intercom system, telephone)

- Information processing and presentation equipment (PCs, tablet PCs, PDA)

- Security and access control

- Safety alarm system

- Elevators and sundry special domains

In an automated building or home, for example, light in a room can be turned off when nobody is present or be automatically turned on if sensors detect a human being. Functions of a HVAC system can not only be affected by the current temperature, but also by other associated factors: A HVAC system can be turned off in a particular room when a window is opened and turned on again when the window is shut.

Although this classification can be applied to HAS as well as to BAS, different priorities due to different importance for integration exist. For BAS the key driving factor is economic utility. Improved control and regulation of energy consuming devices allow to reduce ongoing costs. In a small-scale HAS increasing comfort, safety and security is decisive and saving of energy is a nice benefit. Moreover, information and infotainment systems, like the "smart fridge" [64] are becoming more important.

For both domains central and remote access to the controlled functions is of concern. A central monitoring and control centre in a BAS can further reduce costs, by providing services allowing detection, localisation and correction of faulty conditions at an early stage with minimal effort. In a HAS the "peace of mind" sense is the driving factor. The user is, for instance, able to find out the condition of windows (i.e. open/closed) or the alarm equipment without actually being on site. Refer to [38] for a detailed classification, description and discussion of the above mentioned groups.

To provide the above mentioned services, the underlying system has to fulfil certain features. The traditional approach assumes a *three-level functional hierarchy*, split into management level, automation level and field level.

The field level forms the lowest part in the hierarchy. This level interacts directly with the physical environment by either collecting data or affecting the environment. Typical devices are sensors and actuators. The field level prepares and preprocesses data which then can be transmitted for further processing to other nodes.

The automatic control takes place at the automation level: It operates on data prepared by the field level and provides automatic control, including all kinds of autonomously executed sequences. Data is collected from the field level, processed and transmitted to other nodes.

At management level, information from throughout the entire system is accessible providing a global view of the whole system. Supervisory control and management of the automation functions is performed. The management level may also include logging and backup servers to collect and archive statistical data. Additionally, interconnections to other networks are also possible at this level.

Horizontal communication denotes communication among devices at the same level. If the data is transmitted between different levels, this is called *vertical communication* [65]. Normally automation systems are designed distributed. Communication is quite often performed in a peer-to-peer manner. The lack of a central controlling instance avoids introducing a single point of failure and bottlenecks. It can be observed that the amount of data to be transferred increases at higher

levels. At field level the exchange of control data is of major concern. Small packets have to be transferred and therefore the needed bandwidth (few KBits/s) is significantly smaller than the bandwidth (several MBits/s) at higher levels. Each level of the presented three-level hierarchy fulfils a certain function. On the other hand each device of an automation system implements a particular function. The trend goes towards "intelligent" devices implementing functionality from more than one of the presented levels. A smart sensor, for example, implements more and more functions of the automation level, too. However, it is still not able to fulfil the requirements of management level. Therefore the three-level functional hierarchy is implemented as a flatter two-level architecture consisting of control network and backbone network.

An automation system can consist of many hundred control network devices interacting with the surrounding and communicating among each other. They form the lowest part in HAS or BAS hierarchy and perform more and more logical functions. Due to the mass of devices, component prices have to be low and treatment should be easy: Installation and configuration have to be as simple as possible. Technologies such as link power<sup>1</sup> should be utilised. Earlier, sensors and actuators were simple and not very powerful. Parameters of a sensor, for instance, have traditionally been preset and fixed in hardware, but due to increasing processing power and miniaturisation of electronic devices, they are made "intelligent" by equipping them with microprocessors. This allows to alter the behaviour if necessary. Manifold possibilities arise and great flexibility can be achieved, not only in the business/industrial domain, but also regarding smart homes. However, the network stack, messages and overhead still have to be kept small.

Typical representatives of Control Networks (CNs) are the LONWorks (LON) standard [6, 7, 8] described in [44] and KNX/EIB (see [40, 21]). CNs should transfer local control data robustly under relaxed timing requirements and over long distances. They interconnect actuators and sensors at room level. At the electrical level CNs should permit easy cabling with a flexible network topology. Furthermore, large cable lengths should be possible. Communication is quite often performed in a peer-to-peer manner. Limited resources are present at field level nowadays. Therefore it is not economically feasible to use IP at this low level yet.

The backbone network is responsible for interconnecting control networks. The communication system features high bandwidth. Quite often an IP network is used, frequently employing the Building Automation and Control Networking

<sup>&</sup>lt;sup>1</sup>Using link power, communication and power signal are transported via the same cable.

Protocol (BACnet) standard [9, 34] (for description see [41, 12]). Devices connected to the backbone network have comparatively high computational power and form central parts of the system. Refer to [38, 23] for a detailed discussion on communication systems for building automation and control.

It has to be mentioned, that special care has to be taken concerning safety critical devices/systems, like fire alarm systems, due to their high dependability requirements. A non working or just sporadically working light can be annoying, but no harm is caused. A malfunctioning fire alarm system in a HAS or BAS can cause catastrophic consequences. For this reason, safety critical systems are often kept separate from other building control systems.

## 1.2 KNX/EIB overview

The European Installation Bus (KNX/EIB) is designed to enhance electrical installations in HAS and BAS. It is a typical representative of a CN and it is based on an open specification. Konnex (KNX) is responsible for centrally maintaining the specification as well as managing Intellectual Property Rights (IPR) concerning the standard and the involved companies. KNX/EIB is well-established in central Europe, i.e. Germany, Austria and Switzerland. It is found primarily in large building installations with main application areas being lighting, control of window blinds and HVAC systems. Due to rather high component prices, the pure cost-benefit calculation regarding saving of energy does not seem to be economically feasible in home area [48, 46]. Here increase of comfort, safety and security is the major reason for using KNX/EIB.

KNX/EIB features a decentralised design. It is a peer-to-peer network system: Nodes<sup>2</sup> communicate directly with each other using a distributed algorithm for medium access. There are hardly any central control nodes that solely fulfil regulation functions as, for instance, a Programmable Logic Controller (PLC) does. In fact, control and working logic is located at every single node. To put it differently: Every single sensor or actuator implementing the KNX standard is able to handle network communication as well as implementation of the desired logic on its own.

A key feature in KNX/EIB is group communication based on a publishersubscriber model, allowing to address an arbitrary number of receivers by way of a single message. A sender uses a logical group address as its destination address. Receiving stations know their dedicated group (or groups) and can accordingly

<sup>&</sup>lt;sup>2</sup>A node can be anything from a simple sensor/actuator to a PC-based management server.

ignore or process incoming messages. Hence, a sender does not require information about – it cannot even determine – which nodes actually are receivers of a message. This addressing scheme is present in *process data exchange*. Only for *configuration and management purposes* point-to-point messages are used.

KNX/EIB allows various media. The primary used medium is shielded or unshielded Twisted Pair (TP) cabling known as *KNX TP1*. 29 V DC power and the actual signal are carried by the cable. Data is transmitted at 9600 b/s. Medium access is controlled using Carrier Sense Multiple Access (CSMA) with bit-wise arbitration on message priority and node address. TP1 allows a free topology with cable lengths of up to 1000 m per physical segment. A hierarchical three or two layer structure is possible using routers. See Section 1.3 for a detailed classification of devices. Integration of KNX/EIB into existing installations can be achieved using *powerline* as communication system. The mains distribution cables are spread well over the entire building and can constitute a sub-network to the communication system. Unreliability of the medium, however, requires sophisticated methods at protocol level. Speed is limited to 1200 b/s respectively 2400 b/s depending on used technology.

To further extend KNX/EIB, *KNX Radio Frequency (RF)* can be used. A subband in the 868 MHz frequency band, reserved for short-range devices, is used. For a detailed description of KNX/EIB refer to [37], for an introduction to KNX/EIB interfaces refer to Section 2.

### 1.3 KNX/EIB device classes and market overview

The following section is going to give a brief introduction into KNX/EIB device classes. Different requirements – technical ones and practical ones –, various abstraction levels and complexity levels can be considered to divide KNX/EIB related devices into classes. The position in hierarchy and functions of the developed hardware should be explained and the requirements like memory, storage and processing power should be determined and justified.

Table 1 shows a classification consisting of four categories which are most suitable for this thesis. The following aspects are discussed:

- Devices

- Examples: available devices

- Level: classification according to the three-level functional hierarchy presented in Section 1.1

- Function: general purpose of devices

- Installation domain: location, where devices are typically found

- Processing power

- Memory: volatile memory (e.g. RAM)

- Telegram rate: Average load (e.g. number of packets a device has to be able to process) under typical operating conditions

- Response time of the device: timing requirements regarding user interaction (e.g. time between pressing a switch and a light going on)

- Connectivity / network stack: number of required network connections and size of according network stack(s)

- Storage: permanent storage (for e.g. filter tables, historical data, ...)

- Application size: complexity and size of corresponding software (e.g. application logic in sensors, visualisation tool, ...)

- User interface: possibilities for users to interact with the system (e.g. light switch, terminal for PC-based devices, ...)

- Costs

Furthermore, some state of the art devices and systems will be presented in this section. A further introduction to home area network technologies (Bluetooth, Firewire, ...) is given in [2].

| Class   | Interaction devices     | Routers              | Gateways | PC-based                                                               |

|---------|-------------------------|----------------------|----------|------------------------------------------------------------------------|

| Devices | sensors, actu-<br>ators | couplers,<br>routers | gateways | control and monitoring systems, visualisation systems, logging servers |

| Examples      | 4-way binary  | line-/area    | ISDN,           | Gira Home-    |

|---------------|---------------|---------------|-----------------|---------------|

|               | switch,       | coupler,      | Bluetooth,      | server,       |

|               |               | EIBnet/IP     | HTTP, WAP,      |               |

|               |               | router,       | Firewire,       |               |

| Level         | field         | field         | automation      | management    |

| Function      | environmental | network       | network in-     | central       |

|               | control       | bridging      | terconnection   | control/main- |

|               |               |               |                 | tenance       |

| Installation  | field/cabinet | cabinet       | cabinet/office  | office        |

| domain        |               |               |                 |               |

| Processing    | low           | low           | middle          | high          |

| power         |               |               |                 |               |

| Memory        | low           | low           | moderate        | high          |

| Telegram rate | low           | moderate      | low/moderate    | high          |

| Response      | critical      | critical      | critical/modera | teow          |

| time          |               |               |                 |               |

| Connectivity  | single and    | single and    | 2 or more and   | 2 or more and |

| / network     | small         | small / 2 and | big             | big           |

| stack         |               | moderate      |                 |               |

| Storage       | low           | low/moderate  | moderate        | high          |

| Application   | moderate      | low           | moderate        | high          |

| size          |               |               |                 |               |

| User          | simple        | none          | none/simple     | complex       |

| interface     |               |               |                 |               |

| Costs         | low           | low           | moderate        | high          |

Table 1: KNX/EIB device classification

## 1.3.1 Interaction devices

Devices belonging to this class provide the function of an automation system. In KNX/EIB they contain part of the system's logic and functionality. The domain of interaction devices is stretched widely. What possibilities do current systems, especially KNX/EIB offer? HVAC systems have been the first devices to be auto-

mated due to resulting lower building energy consumption. Main application areas are in industrial complexes and business buildings. However, flexible HVAC systems are finding their ways into the home automation area. Single room controlled heating, cooling and ventilation solutions are possible and affordable. Artificial lighting, shading and shutter systems, centrally or de-centrally controlled, can be realised. Supervision of doors, windows or even Residual Current Device (RCD) devices can be achieved with simple binary sensors and analysed centrally. What is more, integration of safety systems such as fire detection sensors, alarm equipments or handicapped emergency call systems is possible. Visit, for example [49] or [48] for off-the-shelf available devices.

#### 1.3.2 Routers

The catch-all term router is used in this thesis for devices interconnecting networks which share the "same protocol": Routers transfer messages, interpreting and altering them up to layer three of the ISO/OSI model.

The most primitive routers in KNX/EIB are *couplers*. They make the hierarchical structure of the system possible by connecting electrically independent parts of an installation for data transfer. Filtering by use of special tables in couplers reduces telegram traffic throughout the installation. In KNX/EIB different types of couplers are distinguished according to their position in hierarchy and used medium. Couplers for the same medium (e.g. KNX TP1 - KNX TP1) as well as couplers for different media (e.g. KNX TP1 - KNX powerline) exist. Their function, however, is mostly identical and therefore only KNX TP1 - to - TP1 couplers are discussed.

All types of couplers contain microcontrollers and RAM for filtering tables and message buffers. Filtering tables can be programmed via software<sup>3</sup>. *Line repeaters* have been used in the original EIB specification (also called TP64) to extend the maximum line length and maximum number of 64 devices per electrical segment. With the current KNX TP1 specification, up to 255 devices can be connected to a line and repeaters are only used to extend the line length to up to 4000m. Different lines are connected by *line couplers*. Up to 15 lines can be connected to form a main line. Typically such main lines form a control network on every floor of a building. By the help of *backbone couplers* up to 15 lines can be connected to the backbone line.

<sup>&</sup>lt;sup>3</sup>Filter tables can be programmed via EIB Tool Software (ETS).

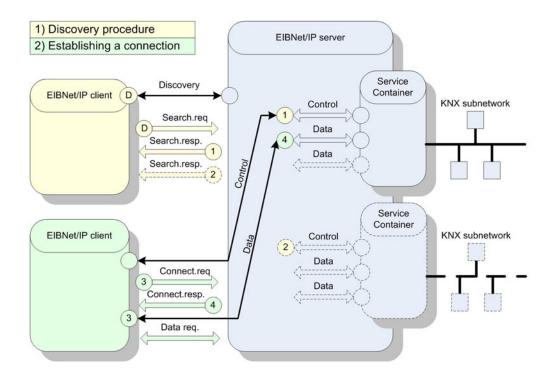

It has to be mentioned, that these standard couplers do not overcome the limitations of CNs, which are small bandwidth and short range. To create a high performance backbone more advanced and powerful networks have to be used. Due to its widespread deployment, IP is commonly used. The first approach was to tunnel standard KNX/EIB frames in point-to-point IP frames and provide remote access through the legacy *EIBlib/IP* ("iETS") (see Section 2.3.1) protocol. For this reason special tunnelling routers located at backbone level have been used. iETS has been replaced by the EIBnet/IP standard (see Section 2.3.2), which is currently awaiting voting for inclusion into the KNX standard. It addresses point-to-point tunnelling as well as routing functions and allows local control networks to be connected by a high performance backbone network. See Section 2 for protocol descriptions.

Of course, enhanced performance and flexibility do not come for free. First of all, neither KNX/EIB, EIBlib/IP nor EIBnet/IP do address security issues in order to keep the protocol simple. So the network has to be separated from the real IP world or be secured by, for instance, a Virtual Private Network (VPN) connection (refer to [32] for a detailed discussion). What is more, timing problems arise when simply extending the network size. Troubles with Medium Access Control (MAC) as well as other timing constraints circumvent arbitrary extensions. Of course, all participants in the network must handle the CN protocol.

#### 1.3.3 Gateways

Gateways handle interconnection between different types – meaning that network protocols differ – of networks. They convert information at application level – layer 7 of the ISO/OSI model – and hence data mappings between the different network entities have to be maintained, which obviously is not possible for all types of messages. Generally it can be stated that this mapping is limited to process data exchange (e.g. group communication in KNX/EIB). Gateways allow integration of many different devices. Connection to brown goods can be realised with, for example, a Firewire-Echonet home automation network gateway. See [63] for details. Integration of white goods like washing machines or fridges can be achieved with, for instance, technologies like serve@home or Miele@home. Quite often, such gateways are based on a web browser with possible Java or Flash plugins. In HAS the concept *residential gateway* is quite common. A single central gateway forms the basis for a tight integration of all sort of consumer de-

vices. It provides access to the outside world by, for instance, ISDN or Ethernet and solves problems like where devices are located, when devices are connected or which capabilities devices feature. To put it differently: Residential gateways provide automatic service detection, support for multiple physical network technologies and remote management and can therefore also be seen as members of the PC-based device class. A separator between the two closely related classes can be drawn regarding the user interface. Gateways typically provide additional network and protocol interfaces, whereas PC-based systems provide a rich user interface. Refer to [11] or visit for example [18].

Security is of great concern for gateways because they often connect non-secure home networks to the "bad" outside world. Various possibilities exist but the reader is left to his own resources [18, 63, 11, 32]. Of course, gateways also should provide a simple user interface and should be easy to set up. Hardware requirements are rather high due to the required processing power and memory<sup>4</sup>. Simple KNX TP1 - KNX TP1 couplers with, for example, an 8-bit CPU and with very limited RAM are not powerful enough. For KNX/EIB a lot of gateways already exist. See Table 2 for an overview of available devices – from compact nodes to PC-class related technologies, listed for completeness. For Internet links see Appendix A.1.

| Company           | Product  | Function                  | Interfaces                              | EIB inter-<br>face |

|-------------------|----------|---------------------------|-----------------------------------------|--------------------|

| 4.D.D.            | TD 1 C   | 1 1 1001                  | • • • • • • • • • • • • • • • • • • • • |                    |

| ABB               | Telefon- | control via ISDN          | voice, e-mail,                          | integrated         |

|                   | Gateway  |                           | SMS                                     |                    |

|                   | TG/S 3.1 |                           |                                         |                    |

| ABB               | DALI-    | interconnection of up to  | DALI                                    | integrated         |

|                   | gateway  | 128 DALI devices          |                                         |                    |

|                   | DG/S 8.1 |                           |                                         |                    |

| Adyna             | IC.1 DR- | visualisation and control | Domoport, HTTP                          | integrated         |

|                   | EIB      | via ISDN, Ethernet and    |                                         |                    |

|                   |          | USB                       |                                         |                    |

| Amann GmbH        | EWMS     | interconnection of BAC-   | BACnet, Ethernet                        | integrated         |

|                   |          | net devices               |                                         | _                  |

| ASTON GmbH        | iPort    | KNX/EIB-ISDN-             | SMS, WAP,                               | integrated         |

|                   |          | Ethernet gateway          | HTTP                                    |                    |

| b.a.b-technologie | eibPort  | visualisation and control | SMS, WAP, iETS                          | integrated         |

| GmbH              |          | via ISDN and Ethernet     |                                         |                    |

<sup>&</sup>lt;sup>4</sup>Excalibur is a typical gateway. It features a 16 bit CPU with 24 MHz, 384 Kb ROM and 24 Kb RAM.

|                 | T111.1     |                           | GL (G. YYY) D  | DOLL -     |

|-----------------|------------|---------------------------|----------------|------------|

| Daetwyler Ca-   | Eiblet one | visualisation and control | SMS, WAP,      | BCU 2,     |

| bles+Systems    |            | via Ethernet              | HTTP, e-mail   | FM         |

|                 |            |                           |                | (Radio     |

|                 |            |                           |                | module)    |

| Disch GmbH      | DISCH      | visualisation via Ether-  | iETS, SNMP,    | integrated |

|                 | Gateway    | net                       | WAP, HTTP,     |            |

|                 | IP         |                           | e-mail         |            |

| ELKA Elektronik | EIB-       | interconnection of de-    | RS232/485,     | integrated |

| GmbH            | Gateway    | vices (e.g. PLC) via      | DMX            |            |

|                 | RS232/485, | RS232/485 or of the       |                |            |

|                 | DMX        | DMX512 bus                |                |            |

| Hager           | Th006,     | visualisation and control | Domoport, WAP, | integrated |

|                 | Th007      | via ISDN, Ethernet and    | HTTP           |            |

|                 |            | USB                       |                |            |

| Albrecht Jung   | KNX/EIB    | control via Bluetooth     | Bluetooth      | integrated |

| GmbH & Co. KG   | Bluetooth- |                           |                | -          |

|                 | Gateway    |                           |                |            |

| Schlaps&Partner | CCEIBSPS   | PLC for EIB with ISDN     | HTTP, iETS     | integrated |

| •               |            | and Ethernet connection   |                |            |

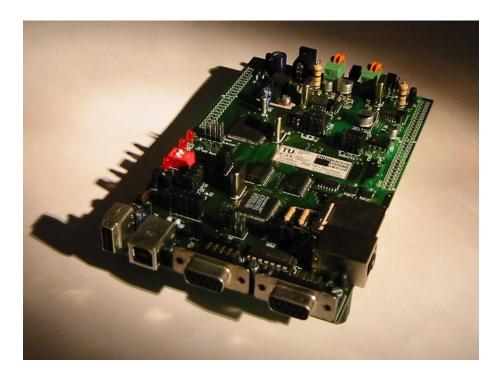

| TU-Wien         | KNXcalibur | flexible, embedded KNX    | EIBnet/IP,     | 2x inte-   |

|                 |            | TP1 prototype with Eth-   | BASys, HTTP    | grated     |

|                 |            | ernet, USB, RS-232 and    | •              | •          |

|                 |            | SD/MMC card               |                |            |

|                 |            |                           |                |            |

Table 2: KNX/EIB gateways (based on [49] and [48])

### 1.3.4 PC-based

Gateways usually just provide a connection to a bus but can also perform simple server tasks like running an integrated web server. Complex visualisation and user-interfaces, however, are limited to PC-based class devices. They are located at a central point and obtain their data using vertical communication from all over the BAS network. Often, LAN technologies are used for this purpose. The approved way of transporting a protocol over another protocol – like for example IP over Ethernet or EIBnet/IP – is very suitable and widespread. Central PC-based access to a BAS allows easier configuration and integration of devices, visualisation of control loops as well as management. Of course, connection points for remote management or access need to be secured.

For KNX/EIB many PC-based solutions exist. As mentioned in Section 1.3.3, some gateways are very powerful and hence can also be seen as PC-based devices. They offer similar facilities as the following discussed PC-based devices. In the HAS domain two representatives of visualisations are readily available on the market. Domoport [18] is a web based service, where the gateway is located at a safe place at the provider. The user can login on the website and then a connection to his/her home is established. This way Domoport certified devices located in the home can be controlled remotely. Gira homeserver (see Appendix A.1) allows querying and controlling devices locally on the KNX/EIB bus as well as remote access through a web portal provided by Gira.

Supervisory Control And Data Acquisition (SCADA) systems, sometimes also referred to as Centralised Control and Monitoring Systems (CCMSs), were introduced in the business area to allow central processing without having to handle each device separately and without actually being on site. Possibilities with such central devices are extensive. Abnormal or faulty conditions can be detected, localised and corrected at an early stage with minimum effort. Direct access for corporate management level can be granted, which simplifies data acquisition for facility management tasks such as cost allocation and accounting. What is more, historical operational data can be gained to assist in further optimisation of control loops and saving costs. For business area applications check, for example, Iphon, NETxEIB or IT-GmbH. See Appendix A.1 for Internet links to the above mentioned products.

## 1.4 Outlook on remaining sections

- Section 2 gives an overview of current technologies and interfaces to connect to the KNX/EIB bus.

- Section 3 describes the requirements, constraints and initial thoughts about the gateway.

- Section 4 depicts the design and outline of the hardware.

- Section 5 outlines the implemented software layers and firmware.

- Section 6 is the place to look for thoughts about further extensions, improvements and optimisations.

## 2 Interfaces

This section provides a survey of current technologies and interfaces to connect to the KNX/EIB bus. Depending on the application, these possibilities have various advantages as well as downsides. Selection of the appropriate interface depends on available resources (Central Processing Unit (CPU), memory, ...) of the application, desired control over the bus and abstraction level. Various protocols have to be implemented, which differ in complexity (stateful, stateless,...) and memory requirements. Especially response time requirements of the application regarding network communication have to be considered.

A typical KNX/EIB device usually consists of three parts:

- Bus Attachment Unit (BAU): Responsible for providing a connection to the KNX medium. It usually consists of a transmission unit, memory (Read Only Memory (ROM), Random Access Memory (RAM), Electrically Erasable Programmable ROM (EEPROM)) and a microcontroller.

- Physical External Interface (PEI): Standardised<sup>5</sup> interface providing a well-known attachment point for interconnection to the BAU. Various modes of communication exist from simple digital I/O to synchronous/asynchronous serial protocols.

- Application module: Forms the user visible part of a KNX/EIB device. The

term "application module" covers devices like push buttons, motion sensors, RS232 interfaces or USB interfaces. Depending on the used device, a

different application program can be loaded to the BAU to make the device

work. Various application module types are defined in KNX/EIB, which

can be detected in hardware with the help of a special resistor.

Section 2.1 gives a survey of specified serial interfaces and BAUs. Bus Coupling Unit (BCU) and Bus Interface Module (BIM) (Section 2.1) based solutions can be used as a stand alone device: Layer 7 of standard ISO/OSI model can be implemented directly on the device. Simple application modules (sensors, actuators, ...) can be connected to the BAU via the PEI as digital or analog I/O. Due to limited resources on both types of BCUs/BIMs, the associated application programs have to be kept very small. If the available resources are insufficient, three possibilities exist to interconnect own applications using the BAUs: RS232

<sup>&</sup>lt;sup>5</sup>The interface is standardised in hardware as well as in basic transport protocol. 21 different types are specified.

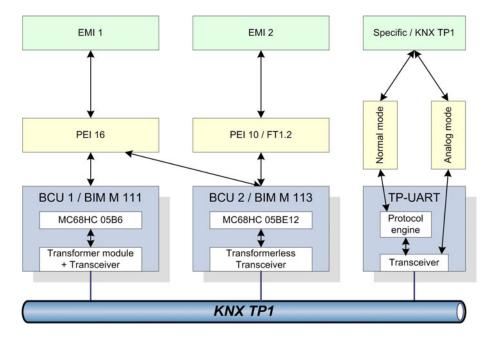

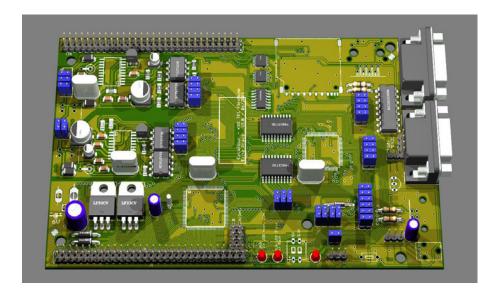

Figure 1: KNX TP1 BAUs

is discussed in Section 2.1. It is continuously used due to its simplicity regarding implementation. Section 2.2 gives an introduction to USB and the KNX on USB protocol and Section 2.3 describes standardised IP interfaces.

## 2.1 Serial interfacing

For this section only the asynchronous serial protocols of the PEI and the RS232 interfaces as application modules or their corresponding counterparts (on e.g. TP-UART) are relevant. Response time, protocol and hardware requirements will be discussed in a way that allows the appropriate BAU for an application like this platform to be selected. Moreover, the actual external messages being transported via the PEI are presented. All external messages together form the External Message Interface (EMI), for which currently the versions EMI 1, EMI 2 ([40] Part 3/6/3) and common External Message Interface (cEMI) ([40] AN033) exist. They differ in layer access management<sup>6</sup>, available services and service encoding. The

<sup>&</sup>lt;sup>6</sup>Layer access management allows an application to directly access a KNX communication layer (application layer, network layer, ...).

cEMI format is intended to be used for the next generation of KNX devices and will not discussed here.

To connect the BAUs via Universal Asynchronous Receive Transmit (UART) to the external user application, two possibilities are common:

- 1. TTL logic level: The BAUs can be integrated into the user application and be directly connected to the hardware. TTL logic level is used.

- 2. RS232: The BAUs are connected via a serial cable. EIA-232, also known as RS232 forms a widespread and common standard [20]. A RS232 level converter needs to be attached to the UART and communication can take place. Operating Systems (OSs) support RS232 communication via the COM interface. Speed is limited, for KNX/EIB communication, however, it is quite sufficient.

Table 3 gives an overview about capabilities of the different BAUs. Details are discussed in Section 2.1.1, Section 2.1.2 and Section 2.1.3.

|                            | BCU 1 / BIM111 | BCU 2 / BIM 113 | TP-UART    |

|----------------------------|----------------|-----------------|------------|

| layer 1 access             | Х              | Х               | ✓          |

| layer 2 raw access         | r              | r/w             | r/w        |

| layer 7                    | ✓              | ✓               | Х          |

| support-standalone         |                |                 |            |

| UART interface             | ✓              | ✓               | ✓          |

| wires                      | 5              | 3               | 2/3        |

| required response time     | $<3$ ms $^7$   | <3.3ms          | <2 - 2.5ms |

| for com. partner at serial |                |                 |            |

| interface                  |                |                 |            |

| EMI 1 support              | ✓              | ✓               | Х          |

| EMI 2 support              | Х              | ✓               | Х          |

| cEMI support               | Х              | Х               | Х          |

Table 3: Comparison TP1 bus attachment units

$<sup>^{7}</sup>$ To achieve a constant transfer rate of 9600 bps, a response time of <1 ms is required for toggling the CTS/RTS lines.

#### 2.1.1 BCU

The Bus Coupling Unit (BCU) is a well-defined BAU fulfilling the specified standard in ([40] Part 09/04/01). It serves as a modular mounting platform for application modules and may contain a specific, rather simple application program or just serve as a bus interface. In any case, an OS handling part of the KNX/EIB communication is present. On the one hand this simplifies bus access but on the other hand the user may not have the desired control over the bus. BCUs usually are intended to be flush mounted and inserted into wall-boxes.

Two different BCU types are defined. The *TP1 BCU 1* features a MC68HC05B6 or compatible type CPU running at 2 MHz with 176 bytes RAM, 256 bytes EEP-ROM and 5936 bytes ROM.

It supports the serial asynchronous *PEI type 16* protocol to transfer messages between the external user application and the BAU's communication stack. A 5-wire connection with the lines RxD, TxD, CTS, RTS and 0 V is used. The protocol consists of four phases:

- 1. Hardware handshake communication request: The communication request is a request/response protocol making use of the RTS and CTS lines. The sender initiates a connection by setting the RTS line to 0 and waiting for the receiver to lower the CTS line. Then data is transmitted. This handshake takes place on each octet transfer.

- 2. Software handshake transfer of length octet: This handshake takes place on the first octet exchange and is used for determining the communication direction. Both communication partners transfer the length of the data requested to send or FF<sub>h</sub>, if no data needs to be exchanged. In case of simultaneous requests, the BAU is considered as master.

- 3. Data exchange: The communication initiator sends its data octets and the receiver responds in parallel with  $00_h$  octets at speed of 9600 bps (8 data bits, no parity bit, one stop bit).

- 4. Pause: After transfer both communication partners have to wait for a 3 ms timeout.

Overall communication speed in PEI type 16 protocol is controlled by help of the hardware handshake. The individual octets, however, are transferred at a fixed speed of 9600 bps. Apparently no hard response time requirements are present. Only the line timeout of 3 ms has to be detected. The data exchange process

implicates that no duplex transfer of messages is possibly, meaning that a communication partner can either receive or transmit at a time, but not both.

Messages transferred via the BCU 1 PEI are in *EMI 1* format, where the actual message format depends on the used PEI type. In EMI 1 any KNX protocol layer can be switched on or off, so that the desired layer can be accessed directly. This is achieved, by writing directly to the BCU's "system status" memory location (1 byte) with a PC\_SetValue.req or A\_Memory\_Write.req. It has to be mentioned that only some combinations of layer selections make sense and that some layers have to be turned on to make, for instance, the internal user application work. Activating the bus monitor, which passes every KNX/EIB frame to the PEI, disables the user application and object servers.

The *TP1 BCU 2* uses a MC68HC05BE12 CPU running at 2.4576 MHz. It has 384 bytes RAM, 991 bytes EEPROM and 11904 bytes ROM. It is connected to the KNX/EIB via a FZE 1066 transceiver and is fully compatible to the BCU 1. All BCU 1 services, including PEI type 16, are supported.

BCU 2 supports the *PEI type 10*, allowing usage of the standardised FT1.2 (subset of [33]) protocol or a manufacturer specific protocol, which then needs a download of the appropriate counterpart to the BAU. FT1.2 provides reliable data transmission and allows data flow in both directions. It uses a 3-wire connection with the lines RxD, TxD and 0 V. Transmission is performed with 8 data bits and 1 stop bit with even parity. The transmission rate can be selected. Communication flow is controlled with a software send/confirm service: After transmission of a message, the receiver should respond with a positive confirm frame or with a negative confirm frame. Only after reception of such a message, the sender is allowed to send further messages. No critical timings are present.

PEI type 10 uses the *EMI 2* format. It fully includes EMI 1 services and further extends them. Message destination is dependent on a static redirection table. In normal mode all messages are directed to their default destination (link layer messages to link layer, application layer messages to internal user application, ...). With the help of PEI\_Switch.req messages this layer access can be remapped, to transfer desired messages to the PEI instead of their default destination. The internal user application is then disabled. One type of service is of special interest: The L\_Plain\_Data.req allows raw data to be transmitted to the KNX/EIB, giving full access to the bus.

| MSB Octet 0 LSB                                                                          | Octet 1                | Octet 2                                                                | Octet 3                                                    | Octet 4                                                                                                              | Oc              | tet 5                 | Octet 6                                             | Last Octet (7 - 22)               |

|------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------------------------------------------|-----------------------------------|

| 1 0 R 1 C C 0 0                                                                          | ZZZZLLLL               |                                                                        |                                                            |                                                                                                                      | DRRR            | LLLL                  |                                                     | PPPPPPP                           |

| Control R=1 First Transm. R=0 Rptd. Frame CC Priority 00 System 10 High 01 Normal 11 Low | Always an<br>(physical | Source Address<br>(low)<br>individual<br>) address<br>(L) / Device (I) | or group add<br>determined by t<br>(Destination<br>0 Indiv | Destination Addr. (low) e format as source) ress; the type is MSB of Octet 5 Address Flag): idual Address up Address | Routing Counter | (Length of N-SDU) - 1 | N-SDU<br>1 octet minimum<br>plus 0-15 additional oc | Check Octet Odd Horizontal Parity |

|                                                                                          |                        | Layer 2                                                                |                                                            |                                                                                                                      | Lyr. 3          | Layer 2               | Layer 4/7                                           | Layer 2                           |

Figure 2: KNX TP1 standard data frame (from [37])

#### 2.1.2 BIM

The name Bus Interface Module (BIM), equally to the name BCU, is used for devices complying fully with the standard in ([40] Part 09/04/02). BIMs are designed for piggyback use to be directly mounted on Printed Circuit Boards (PCBs), and hence they have no housing. The *BIM M 111* corresponds to the TP1 BCU 1 and offers the same features. It has an integrated transformer module and a controller. The *BIM M 113* corresponds to the BCU 2. It uses a transformer-less transceiver and the MC68HC05BE12 CPU. On both types of BIMs only a partially implemented PEI connector is present.

#### **2.1.3 TP-UART**

The Twisted Pair - Universal Asynchronous Receive Transmit (TP-UART) Integrated Circuit (IC) is a transceiver, which supports connecting layer 2 devices like microcontrollers, smart sensors, actuators or any other types of applications to the KNX/EIB TP1. The host controller can either be directly connected or optionally connected via optical couplers. Communication to the host controller is realised with a UART interface. It has a 64 byte telegram buffer and there are no critical timing requirements during transmission using the UART. The protocol format (i.e. message interface) is native KNX TP1 (see Figure 2), tunnelled in specific TP-UART frames. The TP-UART consists of an analog part (transceiver) and a digital part (protocol engine), allowing two different types of operation:

• Analog mode: This mode allows direct control of the EIB bus level. The TP-UART functions as a transceiver and only the analog part of the IC is working. The host has immediate control over the high and the low levels of the TP1 network, meaning that the RxD and TxD pins of the host are directly logically related to the bus level. Bit timing has to be implemented by the host.

• Normal mode: Both parts, analog and digital, are working. The host can communicate with the IC using the following constraints and protocol: The baud rate is 9600 bps or 19200 bps, depending on hardware configuration. The telegram structure is 1 start bit – 8 data bits – 1 parity bit – 1 stop bit. Each data byte transmitted to the TP-UART is prefixed with a control byte. Telegrams from EIB bus are transmitted transparently to the host, which has to detect the end of a telegram after a receive timeout of 2 - 2.5 ms. The TP-UART allows busmonitor mode and it supports the host with the Immediate Acknowledgement (IACK) service, used for confirming reception of a KNX/EIB telegram on the same electrical segment: IACKs ensure that an addressed device has received a message and is processing it.

For a detailed discussion of the device refer to specification [68].

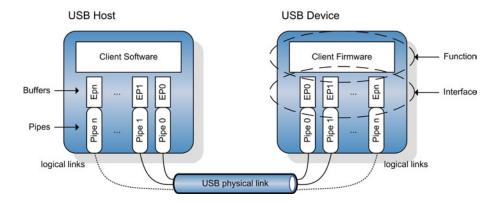

## 2.2 USB interfacing

This section describes the protocol to connect a KNX USB Interface Device to KNX tools like ETS over USB. A summary of required and relevant parts of [74] is given, nevertheless the reader should be familiar with the USB specification. KNX on USB describes the tunnelling of the KNX frame formats EMI 1, EMI 2 and cEMI over USB frames. Discovery and self-description mechanisms as well as the establishment of communication links of USB are utilised.

## 2.2.1 Introduction to USB

The Universal Serial Bus (USB) evolved from the needs of an easy to use, expandable, low-cost, flexible, robust and fast bus to interconnect many different devices to a PC. Real-time data, such as voice, audio and video as well as "slow" human interface devices like keyboards are possible. Transfer rates of up to 480 Mb/s can be achieved.

#### APPLICATIONS **ATTRIBUTES PERFORMANCE** Kevboard, Mouse **Lowest Cost** LOW-SPEED Stylus Ease-of-Use Interactive Devices Dynamic Attach-Detach **Game Peripherals** Virtual Reality Peripherals Multiple Peripherals • 10 - 100 kb/s **Lower Cost FULL-SPEED POTS** Ease-of-Use Broadband · Phone, Audio, **Dynamic Attach-Detach** Compressed Video Audio **Multiple Peripherals** Microphone **Guaranteed Bandwidth** • 500 kb/s - 10 Mb/s **Guaranteed Latency HIGH-SPEED** Video **Low Cost** Storage Ease-of-Use · Video, Storage Imaging **Dynamic Attach-Detach** 25 – 400 Mb/s **Broadband Multiple Peripherals Guaranteed Bandwidth Guaranteed Latency** High Bandwidth

Figure 3: USB device classes (from [74])

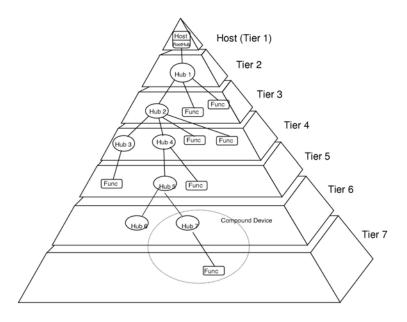

A *USB system* consists of USB interconnect, USB devices and a USB host. Currently USB devices are broken up into:

- Hubs, providing additional USB attachment points

- Functions, providing capabilities to the system

USB hubs form the basis for the plug-and-play architecture of USB. They simplify USB connectivity from the user's point of view and expand single attachments points to multiple attachment points. A hub consists of a high speed upstream port, connected to another hub or host and several downstream ports. Architecture allows transmission at high speed at upstream port, even if full/low-speed devices are connected at downstream ports.

Functions are devices that are plugged into a port of a hub and are able to transmit or receive data over the USB. Typical functions can be seen in Figure 3 and are, for instance, keyboards or mice.

Figure 4: USB topology (from [74])

Each USB system consists of exactly one *USB host*. The USB Host is responsible for detection of attachment and removal of USB devices, management of USB standard control and data flow, collection of status and activity statistics as well as control of the electrical interface including the provision of a limited amount of power for USB devices. To provide one or more attachment points, the root hub is integrated within the host system.

The USB connects USB devices with the USB host. The USB bus topology is a tiered star with hubs in the centres of each star (see Figure 4). Each wire segment is a point-to-point connection between either the host and a hub or function, or between a hub connected to another hub or function.

To move data across the USB, an interaction between various layers is required. Refer to ([74] Section 5) for detailed information about physical and firmware requirements of the host and device. Here the *data flow model* required for the implementer will be presented. From a logical view, USB devices seem to be connected directly to the root port of the USB host. The different USB functions are presented to application developers and they can attach their client software to them: A so called pipe-endpoint model is used for that. The physical

Figure 5: USB pipe-endpoint concept

link of the USB is divided into several logical links. Each logical link is represented as an endpoint featuring its own buffer/FIFO memory. A logical USB device appears to the system as a collection of endpoints. These endpoints are grouped into sets that form an interface, which in turn are the view to the function. See Figure 5 for illustration.

Endpoint 0 is associated to pipe 0 and is the Default Control Pipe, being present in every USB device. The USB System Software uses this endpoint to initialise, configure and manage the logical device. Client software uses pipe bundles and endpoint sets to manage an interface. Data is transferred from the buffer on the host to the endpoint on the device upon request of the client software. The Host Controller then packs the data, coordinates bus access time and moves data over the USB.

USB defines four transfer types:

- Control transfers: Bursty, non-periodic, host software-initiated request/response communication

- Isochronous transfers: Periodic, continuous communication, typically timerelevant information, guaranteed bandwidth, no retry in case of error, bounded-latency

- Interrupt transfers: Low-frequency, bounded-latency communication

- Bulk transfers: Non-periodic, large-packet bursty communication, guaranteed delivery but no guarantee on bandwidth or latency

The use of a certain transfer type and hence device class is not affected by the kind of application, but by the demands of the application concerning the underlying communication system. Devices sharing the same transport requirements can also share a single class driver because of this segmentation. Video applications, for instance, make use of isochronous transfers whereas Human Interface Devices (HIDs) have different and much simpler requirements and therefore use interrupt pipes. Combinations of multiple classes are also possible. Applications with data requirements outside this specification must provide their own drivers and class specification.

#### **2.2.2** KNX on USB

To connect KNX/EIB to the USB ([40] AN037), two main goals have been aspired to:

- Support of only one USB Device Class to minimise compatibility problems and implementation effort

- Support of a widespread and standardised USB Device Class with host drivers available

The *Human Interface Device (HID)* class has been selected to be supported by KNX system tools. Host drivers for nearly all OS exist and hardware components are available for implementing the USB device side. Main characteristics of the USB 1.1 HID Class are interrupt transfers and maximum transfer unit of 64 octets, which are sufficient for KNX on USB. The HID Class uses two pipes – the default control pipe and an interrupt pipe – and at least 3 endpoints. The control pipe is used for standard USB requests like transferring USB control and class data, transmitting data when polled by the HID class driver and receiving data from the host. The interrupt pipe is used for receiving asynchronous data from the device as well as transmitting low latency data to the device. The interrupt out endpoint at the device is optional for HID class devices. If defined, data from the host is transmitted to this endpoint. However, if it is not defined, data is transmitted via the control endpoint. For KNX on USB the interrupt out endpoint at the device is mandatory. See Table 4 for details.

| Pipe           | Endpoint | Transfer Type | FIFO/Buffer | Description      |

|----------------|----------|---------------|-------------|------------------|

|                |          |               | length      |                  |

| Control Pipe   | EP0 In   | Control       | 8 octets    | Standard USB     |

|                |          |               |             | Requests         |

|                | EP0 Out  | Control       | 8 octets    |                  |

| Interrupt Pipe | EP1 In   | Interrupt     | 64 octets   | KNX data trans-  |

|                |          |               |             | fer (tunnelling) |

|                | EP1 Out  | Interrupt     | 64 octets   | KNX local device |

|                |          |               |             | management       |

Table 4: KNX HID USB class interface

In the Interrupt Pipe data is transferred in packets<sup>8</sup> with a maximum length of 64 octets. Requests longer than 64 octets should be split up into more than one USB HID frame. In the following, the KNX HID frame format will be discussed (also see Figure 6). A report frame consists of the KNX HID Report Header and the KNX HID Report Body. The header consists of the Report ID, which can be used by the HID Class host driver to distinguish incoming data. If a device has only one input, output and feature report structure, this prefix can be neglected. For KNX on USB, however, it is used and has a fixed value of  $01_h$ . The sequence number should always start with 01<sub>h</sub> for a KNX frame tunnelled via USB. If a KNX frame exceeds the maximum length of the KNX HID report body (61 octets), it is transmitted in multiple reports and the sequence number is incremented for every following report. Currently, the maximum number of KNX octets is 255 octets. Hence, the biggest sequence number used is five. Reports with unexpected sequence numbers should be ignored by the receiver. The packet type is used to determine the position of a report in a report sequence: A logical OR over the three least significant bits identifies a packet (see Figure 6). If the length of the report is, for instance, smaller than 61 octets. packet type value is  $03_h$  (0011<sub>b</sub> = start and end packet) because one frame is sufficient for transporting all octets. *Datalength* defines the size of the KNX HID report body.

The KNX HID report body consists of a transfer protocol header, only present in the start packet, and the USB transfer protocol body. The *protocol version* octet of the header is currently fixed to '0' with a resulting *header length* of  $08_h$ .

<sup>&</sup>lt;sup>8</sup>Also called reports (HID Spec Glossary [74]): A data structure returned by the device to the host (or vice versa). Some devices may have multiple report structures, each representing only a few items. For example, a keyboard with an integrated pointing device could report key data independently of pointing data on the same endpoint.

The *body length* is the size of the EMI frame plus one octet for message code. Since the extended frame format on TP1 allows 255 octets for KNX frames, the total USB transfer body can be greater than 255 and therefore two octets for body length are present. To identify the transported protocol, the *protocol ID* is used. Specification allows transporting of KNX, M-Bus and BatiBus frames as well as bus access server features. The latter will be discussed in the next paragraph. *EMI ID* encodes the transported EMI type. EMI 1, EMI 2 and cEMI, the future single frame format, are supported. *Manufacturer code* should be  $0000_h$  for a KNX link layer tunnel. In case of not fully complying to the specification of protocol stated in protocol ID field, the own manufacturer's KNX member ID should be filled in. The timeout for KNX tunnelling is 1 second, meaning that the device receives a frame, transmits it to KNX medium and sends an acknowledgement within this period. If the tunnelled EMI format is not supported by the device, it is free to neglect the frame or give an error code.

For successfully connecting and recognising a KNX USB device, several parameters are of concern. Every device has a vendor ID and a product ID. These parameters are part of the USB device descriptor, which can be read by the USB host via the default control pipe. The vendor ID is a 2 byte identifier assigned by USB Implementers Forum. Companies developing USB devices can apply for an own ID or reuse existing IDs via OEM agreements. The product ID is a unique identifier assigned by the manufacturer. For use as a KNX USB device, these parameters are irrelevant. Furthermore, every device has a iManufacturer part in the USB device descriptor, which points to a human readable name of the USB device. This name, for example, shows up in the "New hardware found" dialogue of the Windows OS. Upon connecting a USB device to a Windows host, the OS reads its vendorID and the productID and searches INF files for these parameters to decide which drivers to load. Devices are grouped into various device classes by Windows. Konnex association provides the necessary values – GUID, class name and an additional descriptor<sup>9</sup> –, which are stored in the INF file distributed by the manufacturer with the device. Every device sticking to this interface and hence belonging to this common class fulfils the requirements to be discovered and managed by system tools like ETS.

<sup>&</sup>lt;sup>9</sup>The class GUID is fixed to {01F95DC2-D064-47bc-83DD-19CE43587D2E} and is handled internally by Windows. The class name is "KNXNET" and additional descriptors are "Provider-Name", "ManufacturerName", "DeviceDesc" and "DeviceClassName"

| ReportID Seq                         |                                                                                                                     | NNA HID Report header                                                                                                         | _              |                                                        |                                       |                                           | KNX                                                                                                                      | KNX HID Report Body                | t Body                                                                                     |                                                |                                            |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------|---------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|

| Sed                                  | PacketInfo                                                                                                          | 0                                                                                                                             | Data<br>length |                                                        | KNX                                   | USB Trans<br>(only in                     | KNX USB Transfer Protocol Header (only in start packet)                                                                  | leader                             |                                                                                            | KNX USB Tra                                    | KNX USB Transfer Protocol Body             |

|                                      | Sequence Pad<br>number ty                                                                                           | Packet<br>type                                                                                                                |                | Protocol<br>Version                                    | Header<br>Length                      | Body<br>Length                            | Protocol ID                                                                                                              | EMI ID /<br>Service<br>Identifier  | Manufacturer<br>Code                                                                       | EMI Message<br>Code /<br>Feature<br>Identifier | Data<br>(cEMI/EMI1/EMI2) /<br>Feature Data |

| 01h                                  |                                                                                                                     |                                                                                                                               |                | 00h                                                    | 08h                                   |                                           |                                                                                                                          |                                    | 00h 00h                                                                                    |                                                |                                            |

| Fixed to '01h' for KNX data exchange | Bit 2: 1=partial packet; 0=not partial packet<br>Bit 3: not used  Oh reserved: should not be used  1h-5h nth packet | Bit 0: 1=start packet; 0=not start packet Bit 1: 1=end packet; 0=not end packet Bit 2: 1=partial packet: 0=pat partial packet |                | revision of the KNX USB Transfer Protocol fixed to '0' | fixed to '8' for protocol version '0' | length of EMI frame plus EMI Message Code | 00h reserved<br>01h KNX Tunnel<br>02h M-Bus Tunnel<br>03h Batibus Tunnel<br><i>0Fh Bus Access Server Feature Service</i> | 01h EMI 1<br>02h EMI 2<br>03h cEMI | 0000h for KNX Link Layer Tunnel<br>Manufacturer KNX member ID<br>for own application layer |                                                |                                            |

| octet                                | 1 octet                                                                                                             | a ·                                                                                                                           | 1 octet        | 1 octet                                                | 1 octet                               | 2 octets                                  | 2 octets                                                                                                                 | ets                                | 2 octets                                                                                   | 1 octet                                        | max. 52 octets                             |

Figure 6: KNX on USB frame format

Implementations not using a cEMI server – like EMI 1 and EMI 2 on BCU 1 or BCU 2 – do not support discovery or management functions. To overcome this limit, a dedicated *bus access server feature protocol* has been proposed: Features of a device should be detected and managed separately and stateless by so called *device feature services*. cEMI capable devices should also support these messages. As seen in Figure 6, the bus access server feature uses the protocol identifier  $0F_h$  of the KNX USB transfer protocol header. The selected device feature service is identified by the 1 octet field "service identifier". Possible additional data can be attached to the end of the whole message. The following feature services, listed with identifiers, exist:

- Device feature get (01<sub>h</sub>): This feature is the only confirmed service. A device feature response should be transmitted within 1 second after reception of the get request.

- Device feature response  $(02_h)$ : A variable length of data is supported. Length can be gained from the body length field decremented by one.

- Device feature set  $(03_h)$ : This frame is transmitted exclusively by the bus access client to set a parameter of the bus access server.

- Device feature info  $(04_h)$ : This frame is transmitted by the server and is not confirmed by the bus access client.

Currently there are five device features, listed with feature identifier, defined:

- Supported EMI type (01<sub>h</sub>): This type is used to get the supported EMI type(s). The value is encoded in 16 bits bit 0 determines EMI 1 support, bit 1 EMI 2 support and bit 3 cEMI support. For each supported type, the corresponding bit should be set to 1. The KNX USB access client should determine the supported EMI types upon first connect. If the desired EMI format is not supported, the client should not transmit any tunnelling frames. If the server supports more than one type, the client should select the desired format.

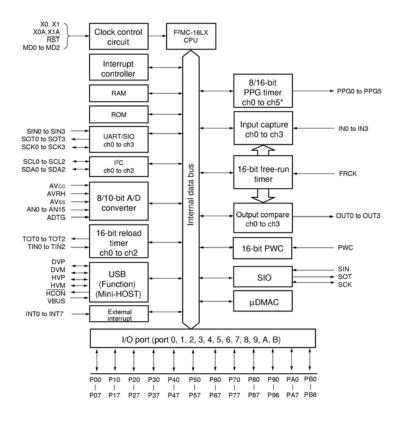

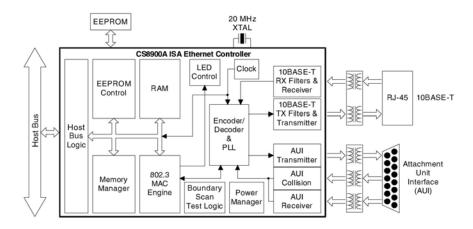

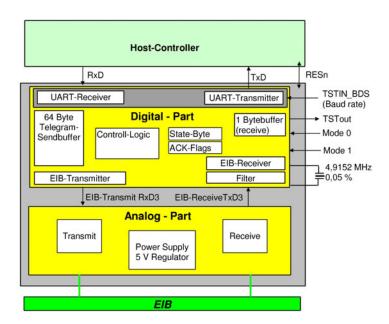

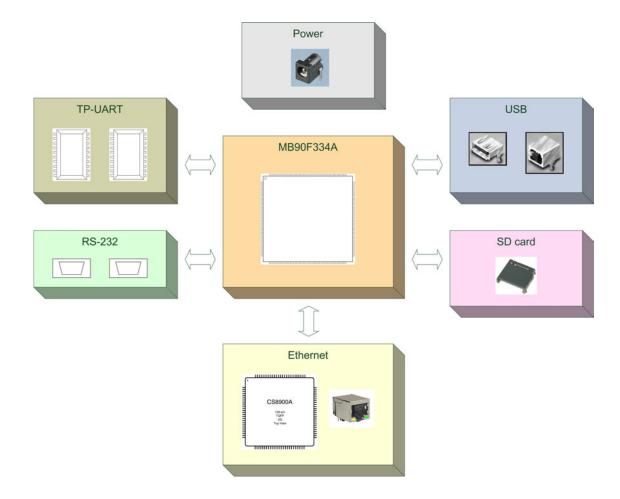

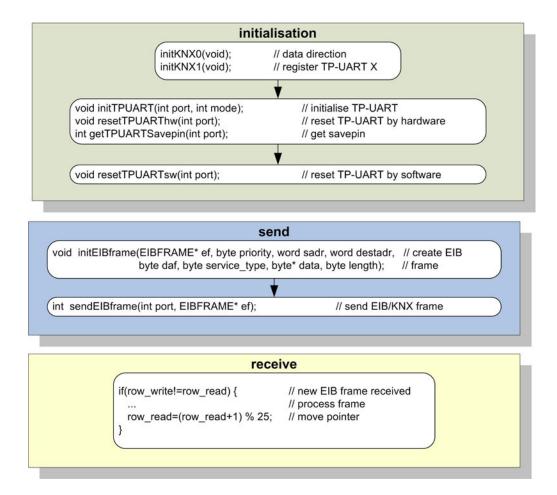

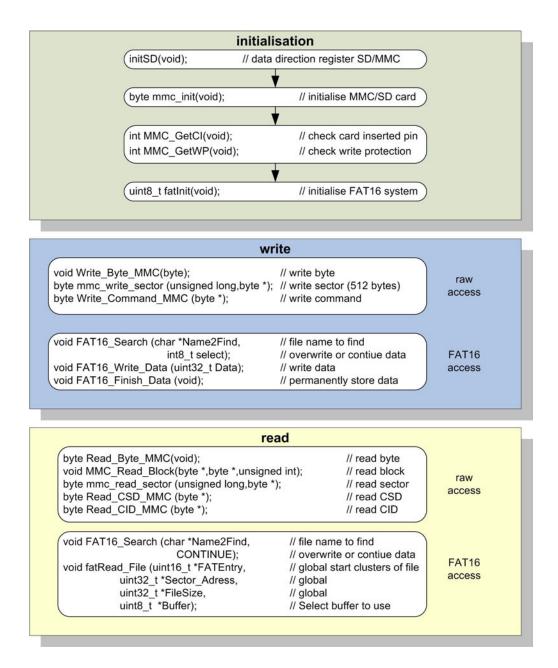

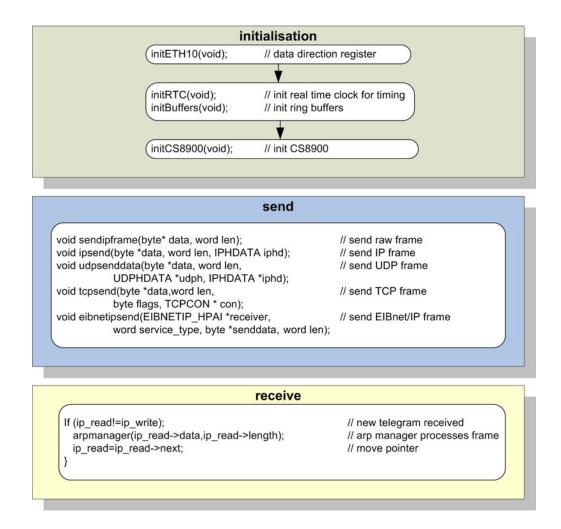

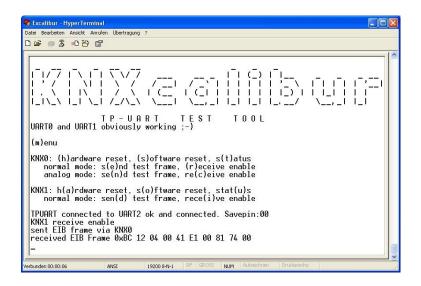

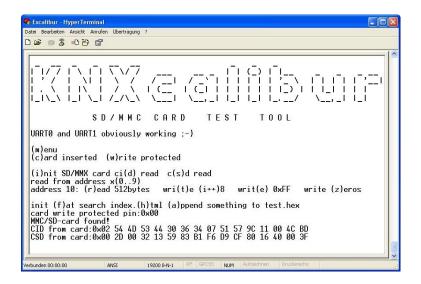

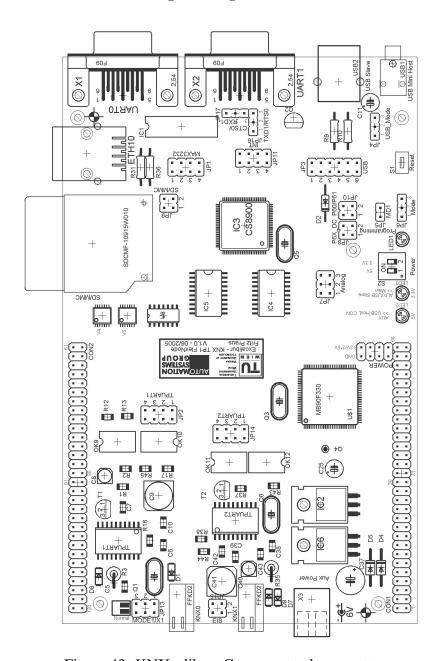

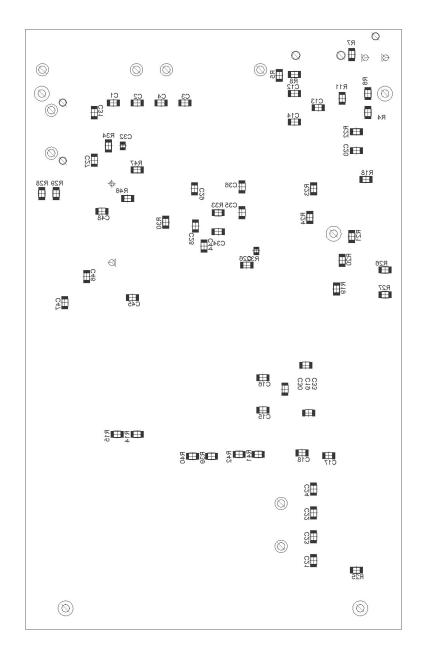

- Host device descriptor type 0 (02<sub>h</sub>): With this feature, the supported local device management procedures can be obtained. This feature is most useful for BCU 1 and BCU 2 based KNX USB devices, because cEMI allows management itself.