The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### DISSERTATION

# The Time-Triggered System-on-Chip Architecture

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Doktors der technischen Wissenschaften

unter der Leitung von

o. Univ.-Prof. Dr. Hermann Kopetz Institut für Technische Informatik 182/1

eingereicht an der

Technischen Universität Wien, Fakultät für Informatik

durch

Dipl.-Ing. Christian Peter Paukovits, Bakk. techn.  ${\rm Matr.-Nr.~0127145}$  Linzer Straße 429 / 5 / 5204, A–1140 Wien

Wien, im Dezember 2008 .....

| Markenzeichen und ähnliche geschützte Begriffe sind teilweise nicht speziell gekennzeichnet, und es liegt daher in der Verantwortung des Lesers, diese im Zweifelsfalle zu überprüfen. Ich sehe es nicht als meine Aufgabe als Wissenschaftler, Markennamen zu recherchieren. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trademarks and similar terms protected by law are partially not particularly denoted in this thesis. If in doubt, it is in the responsibility of the reader to verify the terms used. It is not my task as a scientist to investigate trademarks.                             |

| iii                                                                                                                                                                                                                                                                           |

# The Time-Triggered System-on-Chip Architecture

The Time-Triggered System-on-Chip (TTSoC) architecture provides a component-based design methodology, which addresses complexity management of System-on-Chip designs equipped with billions of transistors. Abstraction, determinism, and encapsulation are the means to achieve a consequent decoupling of computational components from the communication infrastructure, which entails error containment and promotes composability.

This thesis presents a real implementation of the TTSoC architecture based on FPGA technology. Intellectual Property (IP)-cores contain the processing units, in which jobs of application subsystems are executed. Each IP-core has one Trusted Interface Subsystem (TISS) attached, which realizes the major part of the TTSoC architecture's core services such as the time-triggered communication service. The TISS offers these core services to the IP-cores through the Uniform Network Interface (UNI). Each pair of IP-core and attached TISS forms a micro component, which is regarded as architectural unit. Micro components are interconnected through the Time-Triggered Network-on-Chip (TTNoC).

Micro components communicate with each other by means of encapsulated communication channels. Their endpoints – the ports – contain application-level messages, which are exchanged between micro components. The real communication within encapsulated communication channels is abstracted from the IP-core. Communication is synchronized by means of a notion of a global time base, which entails a periodic control system in order to temporally align communication. The TISS harnesses the global time base in order to determine the instants, when a communication activity takes place. Additionally, it controls the flow of messages from send port to receive port of an encapsulated communication channel.

On-the-fly reconfiguration allows the TTSoC architecture to change system parameters during live operation, which is used to adapt the system to changing resource demands or environmental conditions.

To let a given IP-core take part in the TTSoC architecture, a TISS causes a hardware overhead of 10~% and below on FPGA technology. The monetary costs on ASIC technology can be estimated in the magnitude of fractions of one-digit dollar cent.

# Die Time-Triggered System-on-Chip Architektur

Die Time-Triggered System-on-Chip (TTSoC) Architektur ermöglicht eine komponentenbasierte Designmethodologie, welche Komplexitätsmanagement von System-on-Chip Designs mit Milliarden von Transistoren anspricht. Abstraktion, Determinismus und Kapselung sind die Mittel zur konsequenten Entkoppelung von Rechnerkomponenten und Kommunikationsinfrastruktur, wodurch Fehlerisolation und Kompositionalität erzielt wird.

Diese Dissertation präsentiert eine auf FPGA Technologie basierende, reale Implementierung der TTSoC Architektur. Intellectual Property (IP)-cores enthalten die Rechnereinheiten, in denen Jobs von Applikationssubsystemen exekutiert werden. Jeder IP-core hat ein Trusted Interface Subsystem (TISS) angeschlossen, das den Großteil der Systemdienste wie den zeitgesteuerten Kommunikationsdienst der TTSoC Architektur realisiert. Das TISS bietet diese Systemdienste über das Uniform Network Interface (UNI) den IP-cores an. Jedes Paar von IP-core und TISS formt eine Mikrokomponente, die als Architektureinheit betrachtet wird. Mikrokomponenten sind durch das Time-Triggered Network-on-Chip (TTNoC) verbunden.

Mikrokomponenten kommunizieren miteinander mittels gekapselter Kommunikationskanäle. Deren Enden – die Ports – enthalten Nachrichten auf Applikationsebene, die zwischen Mikrokomponenten ausgetauscht werden. Die tatsächliche Kommunikation innerhalb der gekapselten Kommunikationskanäle wird für die IP-cores abstrahiert. Kommunikation wird anhand einer globalen Zeitbasis synchronisiert, die ein periodisches Kontrollsystem mitbringt, um Kommunikation zeitlich auszurichten. Das TISS nutzt die globale Zeitbasis zur Bestimmung der Zeitpunkte, wann Kommunikationsaktivitäten stattfinden. Zusätzlich kontrolliert es den Fluss von Nachrichten zwischen Sende- und Empfangsports eines gekapselten Kommunikationskanals.

Fliegende Rekonfiguration erlaubt der TTSoC Architektur, Systemparameter im laufenden Betrieb zu ändern, was zur Anpassung des Systems an wechselnde Ressourcenanforderungen oder Umweltbedingungen benutzt wird.

Zur Befähigung zur Teilnahme an der TTSoC Architektur für einen IP-core verursacht ein TISS einen Hardwareaufschlag von höchstens 10~% in FPGA Technologie. Die Kosten in ASIC Technologie können in die Größenordnung von Bruchteilen einstelliger Dollarcent Beträge geschätzt werden.

#### Acknowledgments

This work was conducted during my affiliation as a research assistant with the Institut für Technische Informatik, Technische Universität Wien.

I address my gratitude to the advisor of this thesis, Prof. Dr. Hermann Kopetz, who has enabled this affiliation. He has been supporting me with valuable suggestions and formed my academic career. In this context, I would like to mention Dr. Wilfried Elmenreich for his engagement as consultor for this work.

Furthermore, I would like to thank the fellows at the Institut für Technische Informatik, Technische Universität Wien for the countless exhilarating discussions on all kinds of topics. In this context, I would like to mention<sup>1</sup> Sven Bünte, Bernhard Frömel, Albrecht Kadlec, and Michael Zolda.

Special thanks to Christian El Salloum for lots of constructive discussions about the design and implementation of the Time-Triggered System-on-Chip architecture.

Finally, I give my appreciation to Maria Ochsenreiter for her engagement in organisation and her support to come to grips with my affiliation at the Institut für Technische Informatik. Thanks to Leo Mayerhofer for his technical aid during the past two years.

— Christian Paukovits December 2008

<sup>&</sup>lt;sup>1</sup>in alphabetical order

#### Danksagung

Diese Arbeit entstand im Rahmen meiner Forschungstätigkeit am Institut für Technische Informatik, Abteilung Echtzeitsystem, an der Technischen Universität Wien.

Besonderen Dank richte ich an den Betreuer dieser Dissertation, Prof. Dr. Hermann Kopetz, der mir die Forschungstätigkeit am Institut für Technische Informatik ermöglicht hat. Er hat mich stets durch wertvolle Anregungen unterstützt und so meinen wissenschaftlichen Werdegang geprägt. In diesem Sinne möchte ich Dr. Wilfried Elmenreich für sein Engagement als Berater für diese Arbeit erwähnen.

Außerdem bedanke ich mich bei den Kollegen des Instituts für Technische Informatik, Technische Universität Wien für die zahllosen anregenden Diskussionen zu verschiedensten Themen. In diesem Sinne möchte ich erwähnen<sup>2</sup>: Sven Bünte, Bernhard Frömel, Albrecht Kadlec und Michael Zolda.

Mein besonderer Dank geht an Christian El Salloum für die Vielzahl an konstruktiven Diskussionen zu Design und Implementierung der Time-Triggered System-on-Chip Architektur.

Schließlich drücke ich meine Anerkennung für Maria Ochsenreiter für ihr Engagement in organisatorischen Belangen und ihre Hilfestellung, um mich am Institut für Technische Informatik zurecht zu finden, aus. Danke auch an Leo Mayerhofer für die technische Unterstützung während der letzten zwei Jahre.

— Christian Paukovits Dezember 2008

<sup>&</sup>lt;sup>2</sup>in alphabetischer Reihenfolge

## Contents

| 1 | Inti | roduct           | ion                                           | 1  |

|---|------|------------------|-----------------------------------------------|----|

|   | 1.1  | Motiv            | ation                                         | 2  |

|   | 1.2  | Contr            | ibution                                       | 3  |

|   | 1.3  | Struct           | ture of this Thesis                           | 4  |

| 2 | Cor  | $\mathbf{cepts}$ | of the TTSoC Architecture                     | 7  |

|   | 2.1  | Featur           | res and Key Properties                        | 7  |

|   |      | 2.1.1            | Elevation of the Level of Design Abstractions | 7  |

|   |      | 2.1.2            | Determinism & Predictability                  | 8  |

|   |      | 2.1.3            | Error Containment through Encapsulation       | 8  |

|   |      | 2.1.4            | Global Time Base & Clock Domains              | 9  |

|   |      | 2.1.5            | Integrated Resource Management                | 10 |

|   | 2.2  | Core S           | Services                                      | 11 |

|   | 2.3  | Archit           | tecture Overview                              | 12 |

|   |      | 2.3.1            | Entities                                      | 12 |

|   |      | 2.3.2            | Micro Component                               | 13 |

|   |      | 2.3.3            | Requirements for the TSS                      | 14 |

|   |      | 2.3.4            | Elements of Resource Management               | 17 |

|   |      | 2.3.5            | Gateways                                      | 18 |

|   |      | 2.3.6            | Support for Diagnosis                         | 19 |

|   | 2.4  | Imple            | mentation Overview                            | 20 |

|   |      | 2.4.1            | The Five Layers                               | 21 |

|   |      | 2.4.2            | System Operation Frequency                    | 22 |

| 3 | $\mathbf{Rel}$ | ated $V$      | Vork                             | 23   |

|---|----------------|---------------|----------------------------------|------|

|   | 3.1            | The A         | AMBA Family                      | 23   |

|   |                | 3.1.1         | Advanced High-Performance Bus    | 24   |

|   |                | 3.1.2         | Multi-Layer AHB                  | 26   |

|   |                | 3.1.3         | AXI                              | 28   |

|   | 3.2            | Open          | Core Protocol                    | 30   |

|   | 3.3            | Æther         | real                             | 31   |

|   |                | 3.3.1         | Connections in Æthereal          | 31   |

|   |                | 3.3.2         | Structure of NIs                 | 33   |

|   |                | 3.3.3         | Reconfiguration in Æthereal      | 34   |

|   | 3.4            | Nostri        | um                               | 35   |

|   |                | 3.4.1         | Topology Decision                | 36   |

|   |                | 3.4.2         | Theory of Operation              | . 37 |

|   |                | 3.4.3         | Power Management in Nostrum      | 39   |

|   | 3.5            | MANO          | GO                               | 40   |

|   |                | 3.5.1         | Network Adapter                  | 40   |

|   |                | 3.5.2         | Routers in MANGO                 | 41   |

|   | 3.6            | $\times$ pipe | s                                | 42   |

|   | 3.7            | Comp          | arison                           | 43   |

| 4 | Con            | nmuni         | cation Service                   | 49   |

|   | 4.1            | Encap         | osulated Communication Channels  | 49   |

|   |                | 4.1.1         | Establishing Encapsulation       | 50   |

|   |                | 4.1.2         | Topology                         | 50   |

|   | 4.2            | Interfa       | ace to the Communication Service | 51   |

|   |                | 4.2.1         | State Ports                      | 51   |

|   |                | 4.2.2         | Event Ports                      | 52   |

|   | 4.3            | Pulsed        | d Data Streams                   | 52   |

|   |                | 4.3.1         | Periodic Control System          | 53   |

|   |                | 4.3.2         | Handling Collisions of Pulses    | 58   |

|   | 4.4            | Realiz        | eation of Pulsed Data Streams    | . 58 |

|   | 4.5            | Pulse         | Interleaving                     | 59   |

|   | 4.6            |               | ation of Bandwidth               |      |

|   | 4.7            | Messa         | ge Ordering                      | 62   |

|   |                | 4.7.1         | Total Temporal Ordering          | 62   |

|   |                | 179           | Consistent Delivery Order        | 63   |

| 5 | The | UNI    |                                        | <b>65</b> |

|---|-----|--------|----------------------------------------|-----------|

|   | 5.1 | Port I | nterface                               | 65        |

|   |     | 5.1.1  | Signal Specification                   | 66        |

|   |     | 5.1.2  | Memory Layout of State and Event Ports | 68        |

|   | 5.2 | Contro | ol Interface                           | 69        |

|   |     | 5.2.1  | Signal Specification                   | 70        |

|   |     | 5.2.2  | Port Configuration Memory              | 75        |

|   |     | 5.2.3  | Port Synchronization Memory            | 77        |

|   |     | 5.2.4  | Register File                          | 79        |

|   | 5.3 | Synchi | ronizing Access to Ports               | 83        |

|   |     | 5.3.1  | Synchronizing State Ports              | 83        |

|   |     | 5.3.2  | Synchronizing Event Ports              | 86        |

|   | 5.4 | Specia | l Services                             | 87        |

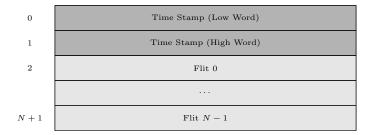

|   |     | 5.4.1  | Time Stamping                          | 87        |

|   |     | 5.4.2  | The Watchdog Service                   | 88        |

|   |     | 5.4.3  | The Generic Timer Service              | 89        |

|   |     | 5.4.4  | The Dissemination Service              | 90        |

| 6 | The | TTNo   | ho C                                   | 93        |

|   | 6.1 | Basics | of the TTNoC                           | 93        |

|   |     | 6.1.1  | Topological Considerations             | 93        |

|   |     | 6.1.2  | Lanes                                  | 94        |

|   |     | 6.1.3  | Operation of Fragment Switches         | 94        |

|   |     | 6.1.4  | Hops                                   | 95        |

|   | 6.2 | Switch | ing in the TTNoC                       | 96        |

|   |     | 6.2.1  | Switching opcodes                      | 96        |

|   |     | 6.2.2  | Routing Modes                          | 98        |

|   | 6.3 | Simult | aneous Routes                          | 98        |

|   | 6.4 | Multi- | casting                                | 99        |

| 7 | The  | TISS                   |                                           | 103   |

|---|------|------------------------|-------------------------------------------|-------|

|   | 7.1  | Struct                 | ure of the TISS                           | . 103 |

|   | 7.2  | Memo                   | ries in the TISS                          | . 105 |

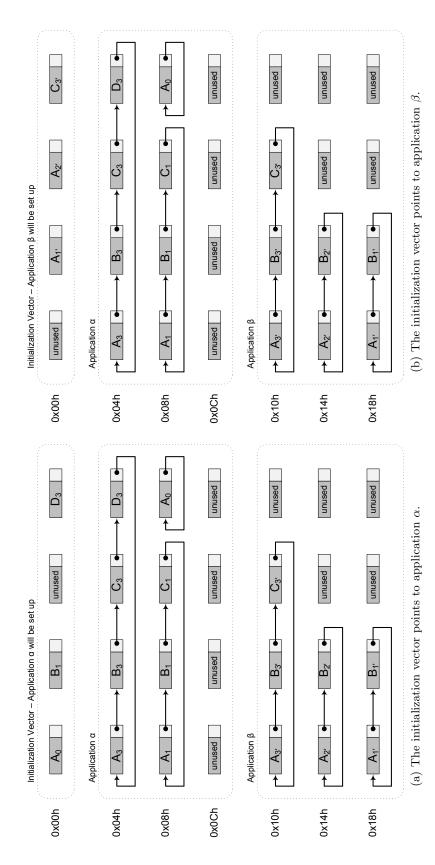

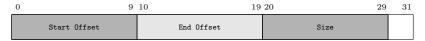

|   |      | 7.2.1                  | The Time-Triggered Communication Schedule | . 106 |

|   |      | 7.2.2                  | The Burst Configuration Memory            | . 111 |

|   |      | 7.2.3                  | The Routing Information Memory            | . 113 |

|   | 7.3  | Dispat                 | ching Bursts                              | . 113 |

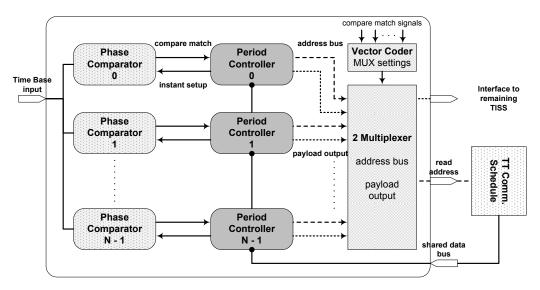

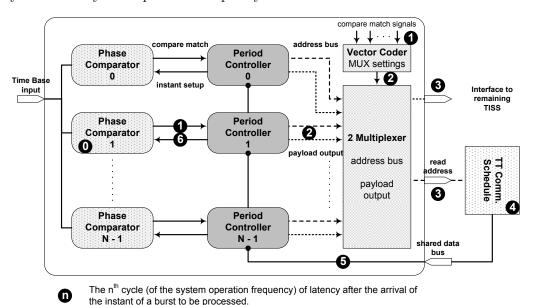

|   |      | 7.3.1                  | Structure of the Burst Dispatcher         | . 114 |

|   |      | 7.3.2                  | Timing of Dispatching                     | . 118 |

|   |      | 7.3.3                  | Activating and Deactivating Periods       | . 120 |

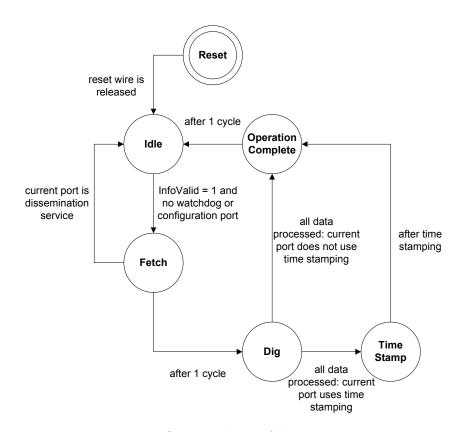

|   | 7.4  | The P                  | ort Manager                               | . 121 |

|   |      | 7.4.1                  | The State Machine of the Port Manager     | . 121 |

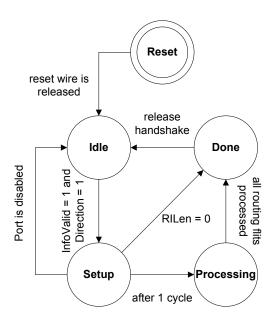

|   |      | 7.4.2                  | The Routing Processor                     | . 125 |

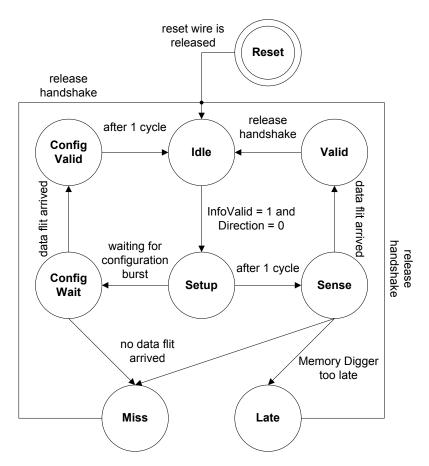

|   |      | 7.4.3                  | Establishing Receive Windows              | . 127 |

|   |      | 7.4.4                  | Address Calculation                       | . 130 |

|   |      | 7.4.5                  | Digging Application Data                  | . 133 |

|   |      | 7.4.6                  | Realizing Time Stamping                   | . 137 |

|   |      | 7.4.7                  | Managing Port Synchronization             | . 138 |

|   | 7.5  | Latence                | cies of Operations                        | . 140 |

|   |      | 7.5.1                  | Receive Operations                        | . 140 |

|   |      | 7.5.2                  | Send Operations                           | . 142 |

|   |      | 7.5.3                  | Example of Transmission                   | . 144 |

|   | 7.6  | Initiali               | ization of the TISS                       | . 144 |

|   |      | 7.6.1                  | What must be initialized?                 | . 146 |

|   |      | 7.6.2                  | Initialization of Period Controllers      | . 146 |

|   |      | 7.6.3                  | Scenarios of Start-up                     | . 147 |

| 8 | Inte | grated                 | Resource Management                       | 151   |

|   | 8.1  | $\operatorname{Scope}$ |                                           | . 151 |

|   | 8.2  | Resour                 | rce Management Strategies                 | . 153 |

|   |      | 8.2.1                  | Static Resource Management                | . 154 |

|   |      | 8.2.2                  | Dynamic Resource Management               | . 154 |

|   | 8.3  | Sequer                 | nce of Interaction                        | . 155 |

|   | 8.4  | On-the                 | e-fly Reconfiguration                     | . 156 |

|   |      | 8.4.1                  | Configuration Bursts                      | . 157 |

|   |      | 8.4.2                  | Protocol of Reconfiguration               | . 159 |

|   |      | 8.4.3                  | The Configurator                          | . 162 |

| 9   | Pro            | $\mathbf{totypes}$ | & Results                                                                    | 167   |

|-----|----------------|--------------------|------------------------------------------------------------------------------|-------|

|     | 9.1            | FPGA-              | based Prototypes                                                             | . 167 |

|     |                | 9.1.1              | Supported FPGAs                                                              | . 168 |

|     |                | 9.1.2              | Resource Usage                                                               | . 168 |

|     | 9.2            | Prototy            | pe Hardware                                                                  | . 173 |

|     | 9.3            | Design             | Example                                                                      | . 177 |

|     |                | 9.3.1              | Structure of the Design Example                                              | . 177 |

|     |                | 9.3.2              | The Need for Serialization                                                   | . 177 |

|     |                | 9.3.3              | Drawbacks of the MPSoC Development Kit                                       | . 179 |

| 10  | Con            | clusion            |                                                                              | 181   |

|     | 10.1           | Power A            | Awareness                                                                    | . 181 |

|     | 10.2           | Growth             | of the TISS $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | . 183 |

|     | 10.3           | Timing             | Issues                                                                       | . 185 |

|     |                | 10.3.1             | About Latency                                                                | . 185 |

|     |                | 10.3.2             | Justification for Bursts                                                     | . 186 |

|     | 10.4           | Feasibil           | ity of the TTSoC Architecture                                                | . 187 |

|     | 10.5           | Outlook            | ς                                                                            | . 188 |

| Lis | st of          | Acrony             | rms                                                                          | 193   |

| Bi  | bliog          | raphy              |                                                                              | 195   |

| In  | $\mathbf{dex}$ |                    |                                                                              | 205   |

| Cı  | ırricı         | ılum ${f V}$       | itae                                                                         | 209   |

# List of Figures

| 2.1  | Structure of the TTSoC architecture                                              | 13 |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | Time format used in the TSS $\dots$                                              | 15 |

| 2.3  | Temporal Alignment in Control Loops                                              | 16 |

| 2.4  | Schematics of the TTSoC prototype implementation                                 | 20 |

| 3.1  | Example of an AHB-based microcontroller design                                   | 24 |

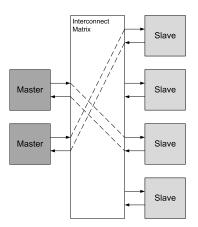

| 3.2  | Interconnection scheme of AHB                                                    | 25 |

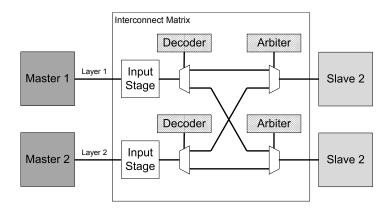

| 3.3  | Structure of Multi-Layer AHB                                                     | 26 |

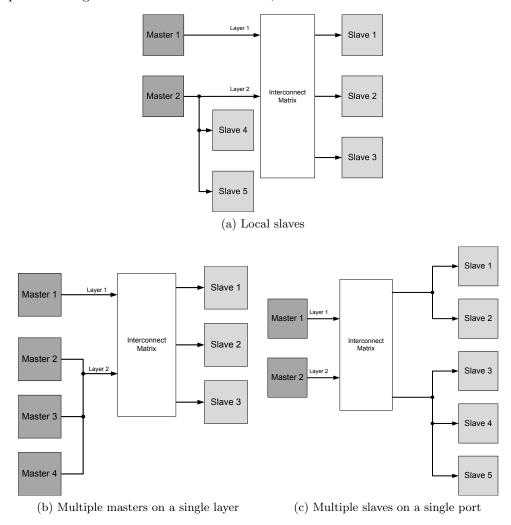

| 3.4  | Internal view on the Multi-Layer AHB interconnect matrix $\ \ \ldots \ \ \ldots$ | 26 |

| 3.5  | Possible groupings in Multi-Layer AHB $\ \ldots \ \ldots \ \ldots \ \ldots$      | 27 |

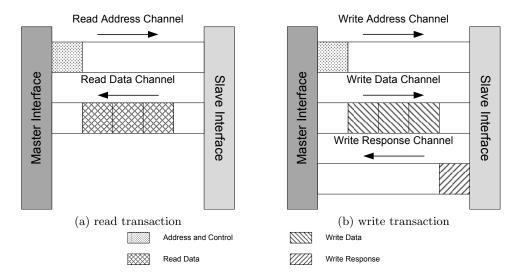

| 3.6  | Transactions in AHB AXI                                                          | 29 |

| 3.7  | Arrangement of OCP connections                                                   | 30 |

| 3.8  | Connection types in Æthereal                                                     | 32 |

| 3.9  | Æthereal credit-based flow control $\ldots \ldots \ldots \ldots \ldots$          | 32 |

| 3.10 | Æthereal NI kernel and shells                                                    | 34 |

| 3.11 | Temporally Disjoint Network                                                      | 37 |

| 3.12 | Looped Container                                                                 | 39 |

| 3.13 | Overview of MANGO                                                                | 40 |

| 3.14 | Types of NAs                                                                     | 41 |

| 4.1  | Example topology of encapsulated communication channels                          | 51 |

| 4.2  | The time format with period bits and phase slices for 16 periods ( $\delta=1$ )  | 54 |

| 4.3  | The time format with period bits and phase slices for 32 periods ( $\delta=1$ )  | 55 |

| 4.4  | Example of an pulsed data stream                                                 | 59 |

| 4.5  | Two conflicting pulses                                                           | 60 |

| 4.6  | Pulse Interleaving                                                               | 61 |

| 5.1  | Memory layout of an output state port with explicit synchronization .                | 68  |

|------|--------------------------------------------------------------------------------------|-----|

| 5.2  | Memory layout of an input state port with time stamps                                | 69  |

| 5.3  | Memory layout of an event port with time stamps                                      | 70  |

| 5.4  | Layout of a data word in the Port Configuration Memory                               | 75  |

| 5.5  | Layout of a data word in the Port Synchronization Memory with its interpretations    | 77  |

| 5.6  | Layout of the TISS's Register File                                                   | 80  |

| 5.7  | Layout of the Error Status Register                                                  | 82  |

| 6.1  | Structure of a lane                                                                  | 94  |

| 6.2  | Consuming a switching opcode                                                         | 96  |

| 6.3  | Example of a switching opcode                                                        | 97  |

| 6.4  | Scenarios of simultaneous routes                                                     | 96  |

| 6.5  | Multi-casting the in the TTNoC                                                       | 100 |

| 7.1  | Structure of the TISS                                                                | 104 |

| 7.2  | Layout of an entry in the Time-Triggered Communication Schedule                      | 106 |

| 7.3  | Layout of the Time-Triggered Communication Schedule with two fictitious applications | 109 |

| 7.4  | Layout of a data word in the Burst Configuration Memory                              | 111 |

| 7.5  | Structure of the Burst Dispatcher                                                    | 114 |

| 7.6  | Timing of activities in the Burst Dispatcher                                         | 118 |

| 7.7  | State machine of the Port Manager                                                    | 122 |

| 7.8  | State machine of the Routing Processor                                               | 126 |

| 7.9  | State machine of the Receive Window Detector                                         | 128 |

| 7.10 | State machine of the Memory Digger                                                   | 133 |

| 7.11 | Minimum latency of receive operations                                                | 141 |

| 7.12 | Latency of send operations                                                           | 143 |

| 7.13 | Example topology                                                                     | 144 |

| 7.14 | Example of latency at sending and receiving TISSs                                    | 145 |

| 8.1  | Schematic representation of integrated resource management                           | 155 |

| 8.2  | Incoming configuration bursts at micro components                                    | 158 |

| 8.3  | Protocol of reconfiguration in a configuration burst                                 | 160 |

| 8 4  | Layout of the control flit                                                           | 160 |

| 8.5 | Layout of the terminal flit                                               |

|-----|---------------------------------------------------------------------------|

| 8.6 | Entities of name space 11 visible to the TNA                              |

| 8.7 | State machine of the Configurator                                         |

|     |                                                                           |

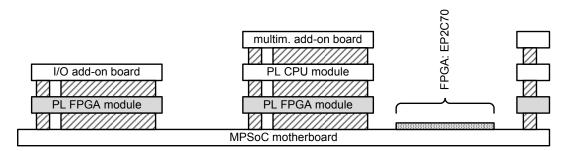

| 9.1 | Stacking add-on boards on the MPSoC Development Kit 174 $$                |

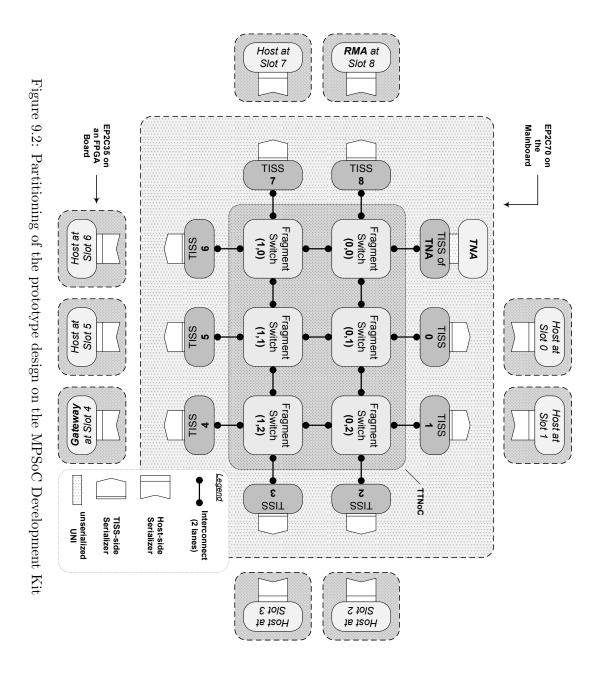

| 9.2 | Partitioning of the prototype design on the MPSoC Development Kit . $178$ |

| 9.3 | Serializing the UNI                                                       |

# List of Tables

| 3.1  | Comparison of characteristics                                                    |

|------|----------------------------------------------------------------------------------|

| 5.1  | Open Core Protocol (OCP) signals of the Port Interface                           |

| 5.2  | Currently supported Open Core Protocol (OCP) commands at the Port Interface      |

| 5.3  | Open Core Protocol (OCP) signals of the Control Interface $\dots 71$             |

| 5.4  | Encoding of the name spaces of the Control Interface                             |

| 5.5  | Currently supported Open Core Protocol (OCP) commands at the Control Interface   |

| 5.6  | Status codes at the OCPS_SResp handshaking signal                                |

| 5.7  | Signals in OCPS_SFlag and their associated interrupt events 74                   |

| 5.8  | Calculating new values of TISS Addr                                              |

| 5.9  | Determining status of event queues                                               |

| 7.1  | Input signals for the address calculation                                        |

| 7.2  | Events and actions for the Port Synchronization Controller $\dots 139$           |

| 8.1  | Mapping of name spaces to physical memories in the TISS 160                      |

| 9.1  | FPGA families and devices running the TTSoC architecture 168                     |

| 9.2  | Parameters of current implementation and realistic variation $\dots 169$         |

| 9.3  | Resource usage of entities of the TTSoC architecture (current implementation)    |

| 9.4  | Resource usage of entities of the TTSoC architecture (realistic variation) $171$ |

| 9.5  | Results of the synthesis with a 45 nm library                                    |

| 10.1 | Comparing resource usage of exemplary designs (Stratix III) 187                  |

### Chapter 1

### Introduction

During the past forty years, the semiconductor industry has developed chips of enormous complexity. The number of transistors per chip has increased so much that we are beyond a billion. This has enabled designers to pack several functional units onto one silicon die. The inherent miniaturization has led to better yield of wafers, thus reducing costs in production. Inspired by these improvements, embedded computing has taken the role of the most important segment of the computer industry.

Nevertheless, the increased complexity has pointed out cognitive limits of human designers. Nowadays, chip designs are so vast that they can hardly be understood. According to the 2005 semiconductor industry roadmap [Wil05], designers will face system design complexity and designer's productivity as key challenges on the way to the giga-scale System-on-Chip (SoC). This challenge can only be tackled if we lift the design process to a higher level of abstraction [Kop08a].

Even though the semiconductor industry has made considerable progress, the basic computational model has not changed significantly during this time. Pollack's rule [Gel01] says that the increase in performance of a sequential computer is only about the square root compared to the increase in the number of transistors. This implies that doubling the transistor count leads to a performance gain of about 40%.

Fortunately, the inherent concurrency in a typical embedded application (such as automotive electronics, avionics) offers the possibility to circumvent Pollack's rule. If an application can be partitioned into a set of nearly autonomous concurrent functions, then a nearly linear performance improvement can be achieved. The trick is to assign a dedicated processing element to each of these concurrent functions. Additionally, each dedicated processing element interacts via an Network-on-Chip (NoC) [Wol04] with its communication partners. This architectural approach is followed in numerous SoC architectures [BM06].

To address these challenges we introduce a novel system architecture: the *Time-Triggered System-on-Chip* architecture. This architecture offers a component-based design methodology, which is intended to take on the complexity of SoCs equipped with billions of transistors. The means to achieve this goal is the consequent decoupling of the computational components from the communication infrastructure.

1.1 Motivation 1 Introduction

The Time-Triggered System-on-Chip (TTSoC) architecture provides an architectural framework that supports *composability* [KO02, Sif05]. Composability denotes the side-effect-free composition of component services – solely based on interface specifications – to form larger systems-of-systems. For this purpose, the computational components are interconnected through a predictable and deterministic NoC with inherent error containment.

#### 1.1 Motivation

The Time-Triggered Architecture (TTA) [KB03] has established a platform for distributed embedded (hard) real-time system [TS06]. It provides deterministic communication based on a notion of global time with synchronized clocks, endorses composability in application design, and contributes to fault tolerance.

In recent years the TTA has spawned industrially applied products that are based on its concepts.

- TTP/C is a time-triggered communication protocol that focuses on safety-critical distributed real-time systems. Its intended domain of application are automotive control systems, aircraft control systems, industrial and power plants, or air traffic control.

- TTP/A is a field bus targeted at low-cost distributed embedded systems. Its main usage is in the field of micro controllers, where it is intended to connect sensors and actuators.

- Time-Triggered Ethernet (TTE) aims at the same application domains like TTP/C, however it uses the widely spread communication technology *Ethernet* [Gro05] for transmission. Time-Triggered Ethernet (TTE) integrates the time-triggered critical traffic and non-critical, event-driven legacy traffic, so that it is backwards compatible to Ethernet.

With the advent of Deep Submicron (DSM) technology in consumer mass markets, the idea of the SoC has gained vast popularity. Nowadays, we have the technological foundation to miniaturize the main concept of TTA to a "microscopic" dimension. In short, this is what the TTSoC architecture does. It is the fourth member of the TTA family, which consequently follows the time-triggered paradigm.

Certainly, the TTSoC architecture reflects the continuous evolution of the TTA. Even though the TTSoC architecture possesses the same basic capabilities as the original descendants of the TTA, it adds new concepts that give more mightiness to design applications in several domains.

One of the main objectives of the TTSoC architecture is abstraction between application design and underlying communication issues. Such abstraction is the means

1 Introduction 1.2 Contribution

to promote composability on an architectural level. In addition to this, encapsulation of communication channels is introduced to provide error containment. Error containment is a strong assumption and required to uphold composability. Finally, the TTSoC architecture is one of the first SoC architectures to include an integrated resource management, so that the system is able to adapt to changing conditions or application requirements in the field during live operation.

Another motivation is a cost argumentation. According to the 2007 semiconductor roadmap [Wil07a], the costs of designing ASICs, e.g., costs of lithographic masks, costs of verification of designs etc., will further increase in the near future. Consequently, it would be desirable to reuse a given design for multiple applications in different target domains. Hence, we need a "generic" system architecture, which fits the requirements of several target domains.

The TTSoC architecture is designed to satisfy the requirements of a batch of target domains from the field of distributed embedded (hard) real-time systems. Moreover, it allows to integrate subsystems of mixed criticality levels, such as control application with tough temporal constraints, or multimedia applications with vast bandwidth and performance requirements.

#### 1.2 Contribution

This thesis concerns the implementation of the TTSoC architecture. It answers the research questions:

- Is it feasible to build such a generic architecture that goes with the requirements of several target applications?

- If so, how would an implementation look like, how would its components work together?

- Finally, what does it cost to equip a given system design with that generic architecture?

Earlier work on the TTSoC architecture has explained the fundamental concepts, design choices, and interface specifications from the theoretical point of view. Contrary, this thesis presents a real implementation of the TTSoC architecture.

The first contribution is that this thesis includes a comprehensive description of the architecture-level interface, through which the *core services* are available. This is the interface, where the abstraction of communication issues takes place.

In this context, the concept of communication in the TTSoC architecture is covered. The thesis describes how we can leverage the mechanisms of the communication subsystem to establish high-level concepts such as determinism, error containment, message ordering, and temporal alignment of communication.

Also, this thesis introduces the design of a NoC, which interconnects participants of communication. This NoC yields characteristics of communication in the TTSoC architecture, thus the realization of that NoC is efficient with respect to area and power. The thesis presents the basics of switching and advanced capabilities such as support for native multi-casting in that NoC.

A major contribution is the answer to the second research question. The thesis explains, how communication is established, which architectural components are in charge of controlling communication, and how these components are implemented. In this context, we find the documentation concerning the implementation of the core services and auxiliary services (e.g., watchdog service, dissemination of diagnosis information) of the TTSoC architecture.

Furthermore, this thesis demonstrates how the TTSoC architecture handles integrated resource management, and how a reconfiguration of system parameters is achieved during live operation.

Finally, this thesis comprises results of working prototypes of the implementation, which allow to draw conclusions about the feasibility and costs of the TTSoC architecture. We state quantitative values about resource usage of the implementation on FPGA technology, and compare these values with other system designs. Also, this thesis includes a cost estimation for production of the implementation on ASIC technology.

#### 1.3 Structure of this Thesis

Chapter 2 gives background information about the TTSoC architecture. It explains the architectural concepts and fundamental properties. Further, it introduces the terminology used by the TTSoC architecture. Additionally, this introduction chapter sketches the tasks of architectural entities and illustrates an overview of the implementation of the TTSoC architecture.

Chapter 3 compares the TTSoC architecture with other approaches that have gained relevance in the research community.

The following chapter 4 is dedicated to the communication service of the TTSoC architecture. It mentions communication primitives and demonstrates, how the notion of a global time is exploited in the TTSoC architecture.

The architectural interface to the core services is covered in chapter 5, while the NoC of the TTSoC architecture is outlined in chapter 6.

Chapter 7 deals with the most important architectural component of the TTSoC architecture. It explains its structure, memories and subcomponents, and how these entities work together to realize the biggest part of the core services.

The integrated resource management and the reconfiguration during live operation are subject of chapter 8.

In chapter 9 the results of the prototypic implementation of the TTSoC architecture are listed. Moreover, this chapter features the hardware set-up, on which the prototypes have been built. Also, a design example of what the TTSoC architecture could look like in a real application scenario is presented.

The last chapter 10 discusses properties of the implementation of the TTSoC architecture, and draws conclusions based on these insights. In this context, it justifies design choices and outlines their optimality. Also, it gives an outlook of future work on the TTSoC architecture.

### Chapter 2

# Basic Concepts of the TTSoC Architecture

This chapter reveals the contributions and novelties of the TTSoC architecture. Also we show, how these features are organized in conceptual entities, and how these entities realize the TTSoC architecture in a prototypic implementation.

#### 2.1 Features and Key Properties

The TTSoC architecture is equipped with a batch of features and key properties. From these features we can derive a set of core services. Such core services provide an interface to applications built around the TTSoC architecture, which abstracts from the real implementation beneath that interface.

#### 2.1.1 Elevation of the Level of Design Abstractions

We promote the idea that complexity of an evolving design must be managed at a higher level of abstraction [Kop08a]. For this purpose, the aggregate properties of a component must be outlined into an interface specification. We must be able to stick components together by simply examining their interface specifications. Thus, the internal structure and the operations within the component can be neglected. Furthermore, it is possible to change or enhance the implementation of the components, for instance in response to technological improvements. As the implementation issues of the components are hidden behind the interface, no redesign of the overall system is necessary.

For this reason, we introduce the entity of a *micro component* in the TTSoC architecture. By definition, such a micro component is a unit of abstraction. A well-defined message-based interface informs about its functionality [GIJ<sup>+</sup>03]. The clear distinction of processing within a micro component and the interactions with

its surrounding results into a communication-centric model [BM02, WG02], which is appropriate for many applications.

#### 2.1.2 Determinism & Predictability

The TTSoC architecture entails determinism [Hoe04] with respect to the communication subsystem. Determinism denotes the property of a system (respectively its system model) to reason about the future behaviour (i.e., outputs) and the *state* [MT89] of the overall system based on the knowledge of an initial state and future inputs. We use the following (revised) definition of determinism:

A model of a distributed computer system (...) is said to behave deterministically if and only if, given a sparse time-base with an infinite sequence of intervals  $t_j$ , the state of the system  $\Sigma(t_0)$  at  $t_0$  (now), and a set of future Input Messages  $IM_1(t_{i1}), IM_2(t_{i2}), \ldots, IM_n(t_{in})$ , then the set of future Output Messages  $OM_1(t_{o1}), OM_2(t_{o1}), \ldots, OM_n(t_{on})$  and the state of System  $\Sigma(t_x)$  at all future intervals  $t_x$  is entailed. [Kop08b]

The TTSoC architecture supports a priori defined on-chip communication expressed in a Time-Triggered Communication Schedule [KB03]. The existence of such a Time-Triggered Communication Schedule fulfils the requirements of determinism, as all future instants, senders and receivers, as well as content of communication activities are known at any time. From a given initial state  $\Sigma(t_0)$  we can derive the state and future behaviour of the system at some later instant t' owing to the knowledge contained in the Time-Triggered Communication Schedule.

Such deterministic behaviour makes communication between micro components predictable. Besides this, a deterministic behaviour of components is required for the transparent masking of hardware errors by Triple Modular Redundancy (TMR) [Pol94]. Finally, Schütz argues in [Sch93] that determinism improves the testability of a system.

#### 2.1.3 Error Containment through Encapsulation

The TTSoC architecture introduces a strong assumption of encapsulation of communication. That is, the communication of each micro component is protected from the communication of other micro components. As a result, communication activities are free of interference and collisions, in general. So, with the non-existence of any conflicts in mind, no micro component will ever disrupt the communication and computation of an opponent. Therefore, we say that communication of micro components is "encapsulated".

One effect of encapsulation is *error containment* [OKSH07]. The communication activities of each micro component are "invisible" to other micro components among the communication subsystem. A misbehaviour of a given micro component, e.g., a

babbling idiot [BB01], will not harm the operation of other micro components. Thus, error containment aids to uphold the composability of a system and increases the robustness against design flaws in subsystems.

Another effect of encapsulation is *complexity reduction*. With the concept of encapsulation (and error containment) we avoid dealing with the behaviour of interfering subsystems. In general, such an unpleasant scenario is more difficult to understand than to reason about the behaviour of clearly encapsulated subsystems. It is essential to avoid all system mechanisms that increase the cognitive load for understanding, if we mean to reduce the cognitive complexity of a design [FCS01]. Also, the test and validation effort for an encapsulated subsystem is smaller than the test effort for interfering subsystems [Owe04].

The TTSoC architecture obtains encapsulation by means of the concept of encapsulated communication channels. Firstly, encapsulated communication channels add bandwidth guarantees and bounded latency to the property of encapsulation. Secondly, they entail two guarantees with respect to message ordering: total temporal ordering and consistent delivery order. Particularly the latter is a vital prerequisite to establish system properties such as replica determinism [Pol93] or to apply distributed consensus and agreement algorithms [Lyn97].

#### 2.1.4 Global Time Base & Clock Domains

In general, we can not assume that a state-of-the-art SoC comes up with a single clock signal for the entire chip. The reasons why designers introduce multiple clock domains embrace the handling of clock skew, the clocking down of individual Intellectual Property (IP)-blocks as part of power management, or the support for heterogeneous IP-blocks with different speeds (e.g., high-clocked special purpose hardware and a slower general purpose CPU).

The TTSoC architecture extends the approach of multiple clock domains. It does not solely bring in multiple clock domains on behalf of these technological issues, but also establishes a system-wide global time base. This global time base is a *sparse time base* [Kop92] and is generated through internal clock synchronization (i.e., within the SoC) and external clock synchronization (with respect to an external reference time).

The global time base yields in the *temporal coordination* of actions, e.g., communication activities, within the TTSoC architecture on each distributed micro component. Consequently, time stamps that have been noticed at different micro components can be related to each other. Additionally, time stamps are also meaningful outside the micro component where the event has been observed.

So, the TTSoC architecture features different clock domains by design:

• The global time base embodies an independent clock domain. The frequency associated with this clock domain determines the global granularity, to which actions in the system, e.g., communication activities, are synchronized.

- The communication subsystem itself is not driven by the global time base. Even though, the communication activities are synchronized by the global time base, the TTSoC architecture can harness two distinct arrangements of clock domains:

- 1. The real communication (i.e., transport of data between micro components) can take place at a frequency with a granularity that is finer than the global granularity of the global time base. As a consequence, there is another system-wide clock domain present, which is independent from the global time base.

- 2. Real communication involves different clock domains at each participant, which might also possess finer granularity than the global time base. In this case, the communication subsystem would employ an asynchronous handshake protocol across clock domain boundaries. Even though, there are several local clock domains involved, the communication activities are still synchronized by means of the common global time base.

- Micro components can include an arbitrary number of local clock domains, which are not visible outside the micro component's architectural borders. For instance, a micro component can be assembled by processor cores, memories, and IP-blocks, which run their own frequencies.

The existence of multiple clock domains, particularly of a global time base, entails the decoupling of synchronization of actions within the system and the operation of local entities. The global time base is allowed to maintain a relative slow clock domain compared to the remainder of the system. While the remainder of the system is driven by higher, local clock domains, there is only one slow clock domain that spans the whole system. This design feature helps designer to deal with clock skew and driver capacity issues of clock distribution networks in state-of-the-art chip designs, as the slow, system-wide clock domain is easy to handle, and the higher clock domains are local and independent from each other.

From the conceptual point of view, the decoupling owing to the global time base supports a further reduction of complexity. Application design focuses solely on communication activities, which are specified in the notion of the global time base. Therefore, application design and communication activities are decoupled from the implementation of the TTSoC architecture. Local modifications, for instance tuning frequencies in micro components and the communication subsystem, do not impose changes to the application design, as they are specified with respect to the independent global time base. Conversely, adapting the global time base has impact on the application design of course, but does not impair the implementation of the micro components.

#### 2.1.5 Integrated Resource Management

The TTSoC architecture supports integrated resource management. Integrated resource management addresses requirements with respect to communication resources

(e.g., bandwidth, latency, latency jitter), computational resources (e.g., dynamic allocation of micro components to application subsystems), and power (e.g., power limiter).

Integrated resource management facilitates an efficient utilization of mutually exclusive resource demands, if it is *a priori* known that the worst-case resource consumption in different subsystems cannot occur simultaneously.

Furthermore, in case of a permanent fault affecting only individual micro components, integrated resource management can relocate the application functionality to spare micro components in order to preserve the specified service of the SoC. Additionally, it builds an important cornerstone for the realization of power-aware systems [UK03]. Power management is identified as one of the great challenges in the SIA's semiconductor road map [Wil05].

#### 2.2 Core Services

With reference to the features and key properties mentioned in the section above, we define *core services* of the TTSoC architecture. The core services are:

- communication service The TTSoC architecture inherits a time-triggered communication service from the TTA. All participants of communication follow a global, a priori defined communication schedule, which synchronizes communication activities by means of a common synchronized global time base. Therefore, the time-triggered communication service entails predictability of communication, and allows to impose bandwidth guarantees and bounded latency.

- **clock synchronization** Communication is initiated by the progression of real time. Therefore, the TTSoC architecture establishes a global time base, which is replicated in each participant of communication. To achieve synchronous communication, this global time base must be kept within a given precision among all participants.

- integrated resource management The TTSoC architecture realizes the properties of integrated resource management introduced in section 2.1.5.

- diagnostic service The diagnostic service allows to monitor the wealth state of a system, i.e., a TTSoC system. In case of a deviation compared to specified behaviour, the diagnostic service is able to undertake measures to restore a defined operating condition. For this purpose, it takes usage of the communication service (plus clock synchronization service) and the integrated resource management.

The communication service and the clock synchronization service are intrinsically tied to each other. The communication service solely relies on the clock synchronization, while the clock synchronization solely serves the communication service.

Nevertheless, when we talk about the communication service, we implicitly also refer to the clock synchronization service.

The integrated resource management uses the communication service to coordinate the resources of the overall system and to achieve an *on-the-fly reconfiguration*, that is, the reconfiguration of parts of the overall system during run-time. In general, it is an additional feature of the TTSoC architecture. It could also exist on other architectures after adaption. Therefore, we regard it as stand-alone core service.

Note that the diagnostic service<sup>1</sup> is no core service directly, as it requires "real" core services to be realized.

#### 2.3 Architecture Overview

This section introduces the conceptual entities, which make up the TTSoC architecture. Moreover, we sketch their functionality and their contribution to the overall TTSoC architecture.

#### 2.3.1 Entities

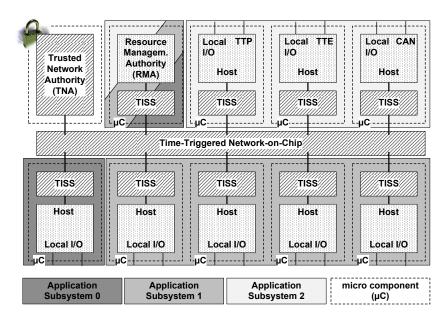

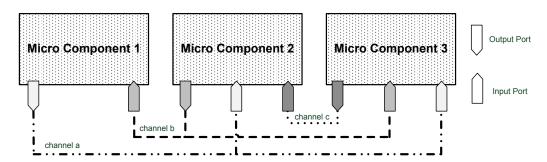

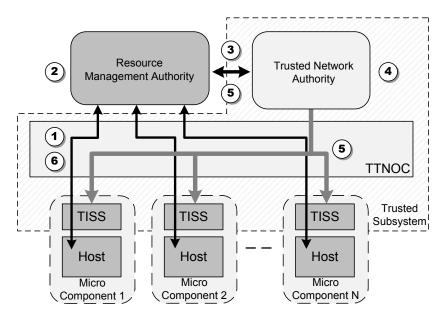

Figure 2.1 gives the structure of the TTSoC architecture and illustrates, how the single conceptual entities form an overall system.

The central element of the TTSoC architecture is the *Time-Triggered Network-on-Chip (TTNoC)* [PK08]. It interconnects multiple, possibly heterogeneous IP-blocks called *micro components*.

The TTSoC architecture also introduces a *Trusted Subsystem*. On the one hand, its tasks is to ensure that a fault (e.g., a software fault) within the *host* of a micro component cannot lead to a violation of the micro component's temporal interface specification. Otherwise, the communication between other micro components could be disrupted. For this reason, the Trusted Subsystem (TSS) prevents a faulty micro component from sending messages during the sending slots of any other micro component. On the other hand, the TSS realizes the core services of the TTSoC architecture.

Due to the support of integrated resource management, the TTSoC architecture establishes two special entities: the *Trusted Network Authority* and the *Resource Management Authority*. The objective of their interaction is to accept resource allocation requests from the micro components and reconfigure the SoC. For instance, they could initiate a dynamic update of the Time-Triggered Communication Schedule of the TSS, or switching between power modes (see section 2.3.4).

<sup>&</sup>lt;sup>1</sup>Yet, the diagnostic service is not covered in this thesis.

Figure 2.1: Structure of the TTSoC architecture

# 2.3.2 Micro Component

A TTSoC system can host multiple Distributed Application Subsystems (DASs) [OPHS06] (possibly of different criticality levels), which provide a part of the service of the overall system each. An example of a Distributed Application Subsystem (DAS) in the automotive domain is a braking subsystem. We call a nearly autonomous and possibly heterogeneous IP-block, which is used by a particular DAS, a micro component. A micro component is a self-contained computing element. For example, it can be implemented as a general purpose processor or as special purpose hardware. A DAS can be realized on a single micro component or by using a group of possibly heterogeneous micro components (either on one or multiple interconnected SoCs).

The interaction between the micro components of a DAS manifests solely in the exchange of messages through the Time-Triggered Network-on-Chip (TTNoC). Each micro component is **encapsulated**, i.e., the behaviour of a micro component can neither disrupt the computations nor the communication performed by other micro components. By design, encapsulation prevents temporal interference (e.g., delaying messages or computations in another micro component) and spatial interference (e.g., overwriting a message produced by another micro component). The only chance, when a faulty micro component can affect other micro components, is when a micro component gives faulty input (in the value domain) to other micro components via the sent messages.

With encapsulation we have the appropriate means to install TMR. TMR aids the detection and masking of failure of a micro component. Encapsulation is necessary to guarantee the independence of replicas. Otherwise, a faulty micro component

could disrupt communication or communication of the replicas. This would end in common mode failures.

Moreover, we use encapsulation to achieve the property of *composability* [Sif05]. Composability denotes the capability of a system to incrementally add new micro components, without overriding prior services of the already existing micro components. This is the requirement, if we want to seamlessly integrate independently developed DASs and micro components in the TTSoC architecture. The same applies to SoCs that encompass the application of subsystems of different criticality levels. In such a mixed criticality system, a failure of micro components of a non safety-critical application subsystem must not cause the failure of application subsystems of higher criticality.

We also pay tribute to encapsulation with the structure of a micro component. It comprises two parts: a host and a so-called Trusted Interface Subsystem, which is part of the TSS. The host implements the application services. By introducing the Trusted Interface Subsystem (TISS), the TTSoC architecture provides a dedicated architectural element that protects the access to the TTNoC. Each TISS contains a data structure, which stores a priori knowledge concerning the global instants in time of all message receptions and transmissions of the respective micro components – the Time-Triggered Communication Schedule. Since this Time-Triggered Communication Schedule cannot be modified by the host, a design fault or a hardware fault in the host cannot affect the exchange of messages in the TSS.

# 2.3.3 Requirements for the Trusted Subsystem

The TTNoC, which is a part of the TSS, interconnects the micro components of a TTSoC. Moreover, the scope of the TSS encompasses clock synchronization for the establishment of a global time base, as well as the predictable transport of periodic and sporadic messages.

# **Clock Synchronization**

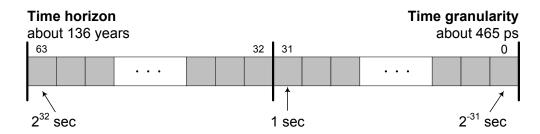

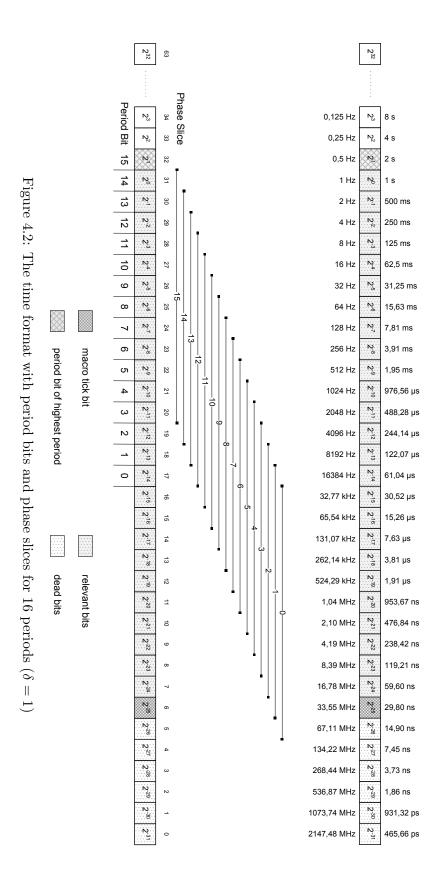

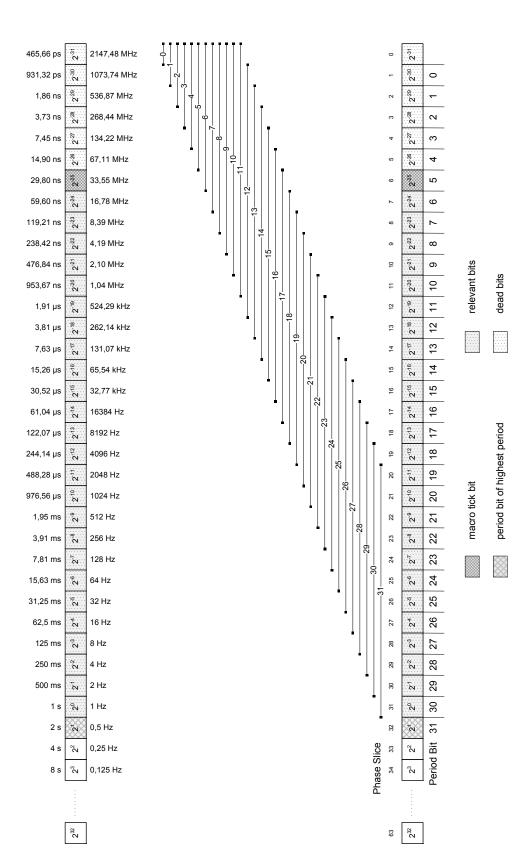

The TSS performs clock synchronization. The goal of clock synchronization is to provide a global time base for all micro components, even though there might be multiple clock domains in a TTSoC. The global time base is based on a uniform time format, which has been standardized by the OMG in the smart transducer interface standard [AC03].

A digital time format can be characterized by the three parameters: granularity, horizon and epoch. The granularity determines the minimum interval between two adjacent ticks of a clock. In other words, this is the smallest interval that can be measured with this time format. The reasonable granularity can be derived from the achieved precision of the clock synchronization [KO87]. The horizon determines the instant when the time is going to wrap around. The epoch denotes the instant when the measuring of the time begins.

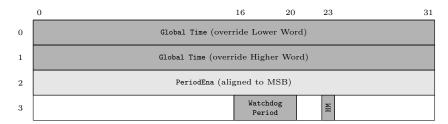

Figure 2.2: Time format used in the TSS

The time format of the global time base in the TSS (see Figure 2.2) is a binary time format that is based on the physical second. Fractions of a second are represented as 32 negative powers of two (down to about 465 picoseconds), and full seconds are presented in 32 positive powers of two (up to about 136 years). This time format is closely related to the time format of the GPS (General Positioning System) time and takes the epoch from GPS. In case there is no external synchronization [KO87], the epoch starts with the power-up instant.

# Predictable Transport of Messages

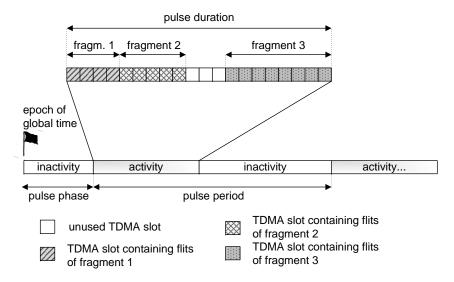

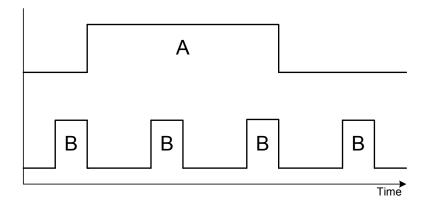

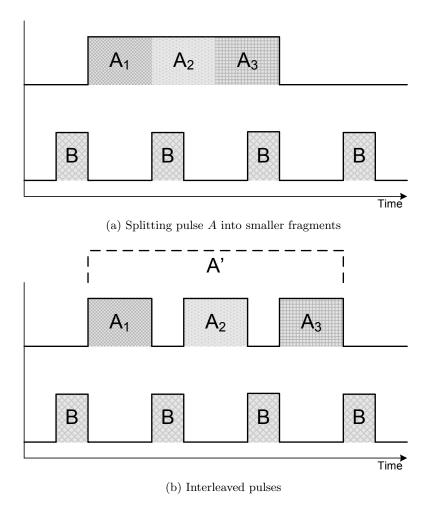

In the TTSoC architecture we divide the available bandwidth of the TTNoC into periodic, conflict-free sending slots by means of Time Division Multiple Access (TDMA). Such a TDMA slot can be used in two different ways. Either it transports data of periodic messages, or sporadic transmission of messages. In the latter case, the sender issues a messages, whenever it intends to notify a receiver about a new event.

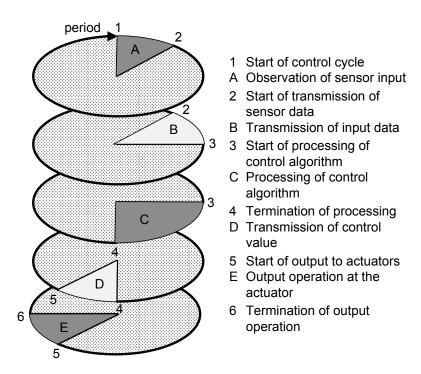

In addition to TDMA slots, we introduce the communication primitive of *pulsed data stream* [Kop06]. The purpose of a pulsed data stream is to model the allocation of TDMA slots. A pulsed data stream is a time-triggered, periodic, uni-directional data stream. It transports data in pulses, which possess a defined length and a defined topology. The pulsed data stream originates and *exactly one sender* and propagates to *at least one receiver*, which are identified *a priori*. Also, the period and phase in a periodic control system are given *a priori*.

Such pulsed behaviour is predestined for efficient transmission of large data in applications, which demand a temporal alignment of sender and receiver. This is particularly the case for those applications, which require a short latency between sender and receiver, for instance most real-time systems. For example, consider a fictitious control loop realized by three micro components. Micro component (A) performs sensor data acquisition, micro component (C) processes the control algorithm (C), and micro component (E) operates the actuator, as it is depicted in Figure 2.3<sup>2</sup>. In this application temporal alignment is vital to reduce the end-to-end latency of the control loop, which is an important quality characteristics. For instance, this requirement applies to the transmission of the control value (D) and the start of

$<sup>^{2}</sup>$ In this cyclic model of time, the perimeter represents the period of the control application.

Figure 2.3: Temporal Alignment in Control Loops

actuator output (see instant 5 in Figure 2.3), as well as the sensor data transmission (B) and the start of the processing of the control algorithm (see instant 3 in Figure 2.3). With pulsed data streams we can achieve an efficient, temporal alignment of data transmissions, which refer to (B) and (D) in Figure 2.3.

Contrary to the communication service of the TTSoC architecture, many existing NoCs only provide the feature of guaranteed bandwidth to individual senders. The lack of temporal alignment results in the following consequences [SOHK08]:

- either the short latency can not be guaranteed,

- a high bandwidth has to be granted to the sender throughout the entire period of the control cycle, although it is only required for a short interval, or

- the communication system has to be periodically reconfigured in order to free and re-allocate the non-used communication resources.

Similarly, in a fault-tolerant system that masks failures by TMR, a high bandwidth communication service is required for short intervals to exchange and vote on the state data of the replicated channels.

To sum up, a real-time communication network should consider these pulsed communication requirements and provide appropriate services. The TTSoC architecture addresses this issue, eventually.

# 2.3.4 Architectural Elements of Resource Management

Integrated resource management in the TTSoC architecture serves the purpose to dynamically assign computational resources (i.e., micro components) to application subsystems and to grant communication resources and power to the individual micro components.

We distinguish between two fundamentally different types of application subsystems [SOHK08].

Safety-critical application subsystems need to be certified to the highest criticality classes (e.g., class A according to DO-178B).

Non safety-critical applications subsystems do not require certification to the highest criticality classes.

In general, these two types of application subsystems desire fundamentally different (also conflicting) design paradigms. Safety-critical applications focus on simplicity and determinism. Therefore, it is straightforward to facilitate thorough verification and validation. In contrast, non safety-critical applications can provide more complex application services, whereas we do not have sufficient *a priori* knowledge about the environment. Moreover, the dynamics to handle evolving application scenarios and changing environments can be challenging.

In the TTSoC architecture, two distinct architectural elements deal with integrated resource management, namely the Trusted Network Authority (TNA) and the Resource Management Authority (RMA). The RMA computes new resource allocations for the non safety-critical application subsystems, while the TNA ensures that the new resource allocations have no adverse effect on the behaviour of the safety-critical application subsystems. As depicted in Figure 2.1, the TNA is part of the TSS of the TTSoC, whereas the RMA is not. A consequence of splitting the entire resource management into two distinct parts (whereas only one is part of the TSS) the certification of the TTSoC is significantly simplified. We explain this with the fact that checking the correctness of a resource allocation through the TNA is significantly simpler than its generation through the RMA.

### Resource Management Authority

The RMA is in charge of scheduling of available resources, which are allocated among the micro components. For this purpose the RMA leverages application-specific (e.g., communication topology) and system knowledge (e.g., temporal properties of the TTNoC). Nevertheless, the RMA is not allowed to change the configuration of the TSS directly, i.e., to update the affected TISSs.

# Trusted Network Authority

The TNA is some kind of guardian for the reconfiguration activities performed by the RMA. Therefore, the TNA goes through the resource reservations from the RMA and looks out for potential collisions on the TTNoC or any violations of resource reservations.

If an erroneous resource schedule is detected, the TNA turns away this new resource reservations from the RMA. Then, the current configuration remains unchanged.

In case of the TNA regards the reservations as correct, it updates the configuration of the micro components. Since the TNA is part of the TSS it possesses the privilege to reconfigure the micro components via the TISS.

# 2.3.5 Gateways

In ultra-dependable systems, a maximum failure rate of  $10^{-9}$  critical failures per hour is demanded [SWH95]. Today's technology does not support the manufacturing of chips with failure rates, which are low enough to meet these reliability requirements. Actually, component failure rates are usually in the magnitude of  $10^{-5}$  to  $10^{-6}$  [PMH98]. Unfortunately, ultra-dependable applications require the system as a whole to be more reliable than any one of its components. With this technological limits in mind, we can only achieve the required reliability by means of fault-tolerant strategies. Such strategies aim at a continuous operation despite the presence of component failures.

The TTSoC architecture supports gateways for accessing chip-external networks (e.g., TTP [KG94], TTE [KAGS05] and CAN [Bos91]). With such a gateway we can realize interoperability with public networks, for example the Internet, and the ability to interconnect multiple SoCs to a distributed system. As a result, we can build distributed systems that house applications for ultra-dependable systems based on the TTSoC architecture.

If the chip-external network is also time-triggered (e.g., TTP, TTE), we can leverage the TDMA schemes of both (the internal and the chip-external network) to synchronize communication across device borders. Consequently, a message that is sent on the chip-external network arrives at the micro components within a bounded delay with minimum jitter (solely depending on the granularity of the global time base). The alignment between messages on time-triggered networks ensures that replicated TTSoCs perceive a message at the same time, i.e., within the same inactivity interval of the global (sparse) time base [Kop92]. This property is significant for achieving replica determinism [Pol94] as required for active redundancy based on exact voting. Without synchronization between the TTNoC and the chip-external network, there could always occur a scenario in which one TTSoC forwards the message to the micro components in one period of the pulsed data stream, while another TTSoC would forward the message in the next period.

Furthermore, the introduced gateways can provide the TTSoC with an externally synchronized time base. For example, the global time base of the TTSoC can be synchronized to GPS. As a consequence, a time stamp assigned to an event is also meaningful outside the TTSoC. Last but not least, the global time base enables a global coordination of activities spanning multiple TTSoCs (e.g., output to actuators at the same global point in time).

# 2.3.6 Support for Diagnosis

The TTSoC architecture incorporates a dedicated architectural element for the purpose of diagnosis – the so-called *Diagnostic Unit* [SOH<sup>+</sup>07, POS<sup>+</sup>07]. Diagnosis is executed in three phases:

- 1. failure detection

- 2. dissemination

- 3. analysis

#### Failure Detection

Most architectural elements in the TTSoC architecture, for instance the TISSs, the TNA etc., perform failure detection in order to indicate faulty and abnormal behaviour of micro components.

The TISS is equipped with mechanisms to observe the behaviour of the attached host. For instance, a watchdog monitors the host, whether it has crashed or it is still alive. Other mechanisms recognize violations of message arrivals. The host performs an application-specific failure detection. These are not defined by the TTSoC architecture. The RMA checks the resource requests of the micro components against predefined constraints. Each invalid request is recorded since it might indicate a failure in the requesting component. The Diagnostic Unit (DU) uses message classification to detect failures in the overall system. For this purpose, the messages of all micro components are routed to the DU, which controls syntactic, temporal, and semantic correctness [POS<sup>+</sup>07].

#### Dissemination

Detected failures in the single entities are reported to the DU via the dissemination service. This special service produces failure indication messages. A failure indication message includes information concerning type of the occurred failure (e.g., crash failure of a host, invalid resource requests), the instant of detection, and the location within the TTSoC (i.e., the micro component). The dissemination service is associated with a dedicated time-triggered message for each micro component that is capable of delivering failure indication messages.

Figure 2.4: Schematics of the TTSoC prototype implementation

# **Analysis**

Based on the collected failure indication messages, the DU establishes a holistic view onto the system. Furthermore, the DU monitors the repeated occurrence of failure indications in order to distinguish between permanent and transient failures.

# 2.4 Implementation Overview

This section sketches the prototypic implementation of the TTSoC architecture. It introduces conceptual layers and the modules, which reside at these layers. Each module fulfils a functions that has been introduced earlier in this chapters.

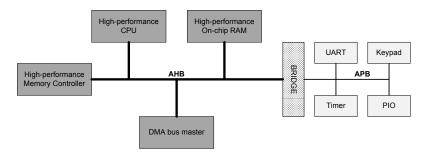

Figure 2.4 shows a vertical schematics of the implementation of the TTSoC architecture. We introduce 5 layers, which relate to the layers of the TCP/IP stack [Car96] or the ISO OSI reference model [Ros90] in naming and purpose.

# 2.4.1 The Five Layers

At the bottom the TTSoC architecture defines the TTNoC layer. This is the conceptual layer, where the realization of the TTNoC resides. Figure 2.4 mentions Fragment Switches that build the TTNoC. We dedicate chapter 6 to the implementation of the TTNoC.

The interface between the bottom TTNoC layer and the Data Link layer is the TTNoC interface. It is the physical connection between the Fragment Switch, which is closest to the TISS of a micro component and the bottom interface of the TISS.

The TISS spans over 3 layers with an own entity at each layer. Details about the TISS can be found in chapter 7.

At the bottom at the Data Link layer there resides the Burst Dispatcher. Its purpose is to handle the arbitration of the TTNoC. Therefore, the Burst Dispatcher includes the global time base, which synchronizes communication activities among micro components. The Time-Triggered Communication Schedule gives the necessary information, how this arbitration is managed.

Then, the Network Layer is in charge of building up communication channels between micro components. The routing information, which is used in the Routing Processor, determines the route of a communication channel along the TTNoC.

In the Transport Layer there resides the Port Manager. It relies on the services of the lower layers to realize major part of the communication service. It cares for access and synchronization of "ports", which are the end-points of communication channels. It controls the flow of fragments of messages for send and receive operations. Moreover, the Port Manager includes the Register File of the TISS, which houses status information and user settings. To provide its service the Port Manager is equipped with several memory entities: the Burst Configuration Memory, the Port Synchronization Memory, and the Port Configuration Memory.

The Uniform Network Interface (UNI) is the interface on top of the TISS. Physically, it is the interface between the TISS and the host. Logically, it provides access to the architectural core services implemented by the TSS. Chapter 5 contains a detailed description of the UNI.

The UNI is intended to be a generic interface to the Application Layer, where application-specific hosts can be attached. A host is made up of the Front-End and an application computer, which can be an own IP-block, a soft-core CPU such as the Altera Nios II<sup>TM</sup> Embedded Processor<sup>3</sup>, or an off-chip micro controller. To provide maximum portability, a Front-End is introduced to wrap the characteristics of the

$<sup>^3</sup>$ http://www.altera.com/products/ip/processors/nios2/ni2-index.html

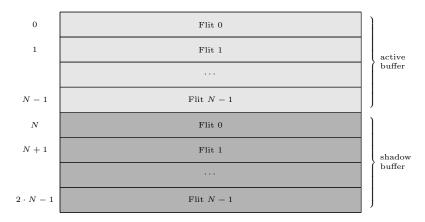

UNI to match the actual application computer. Besides this, the Front-End contains the *Port Memory*.

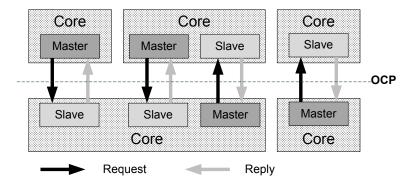

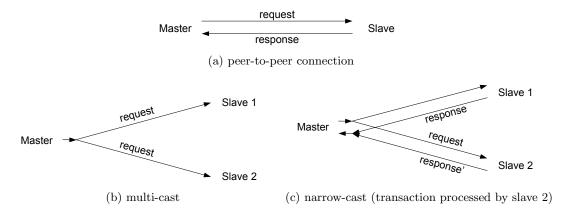

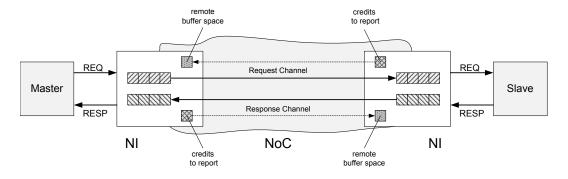

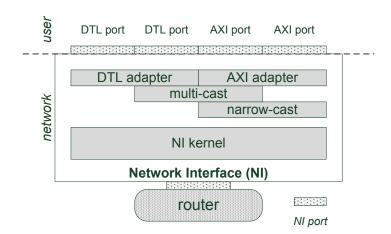

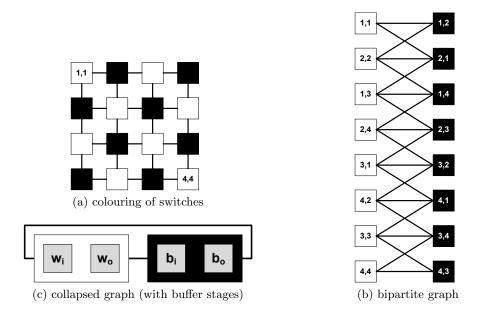

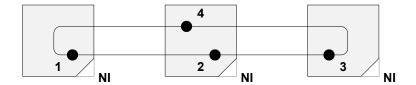

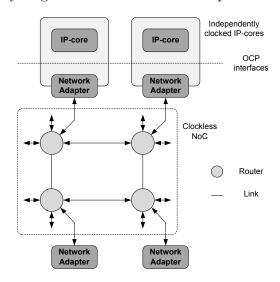

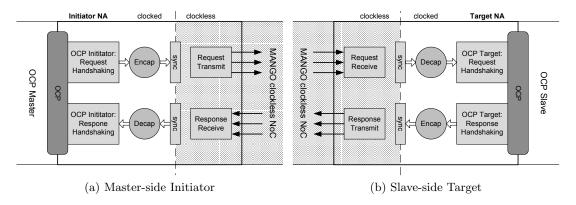

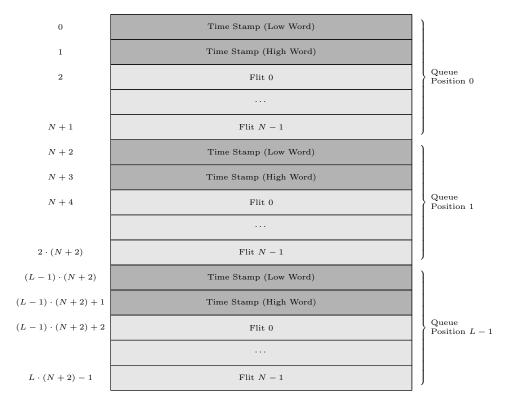

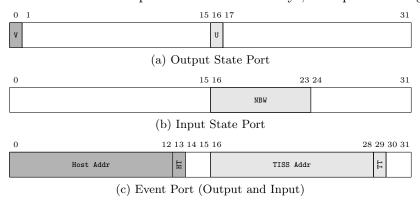

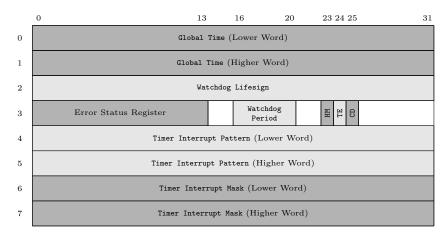

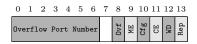

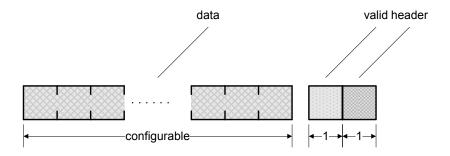

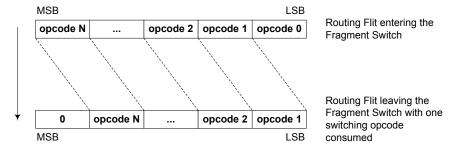

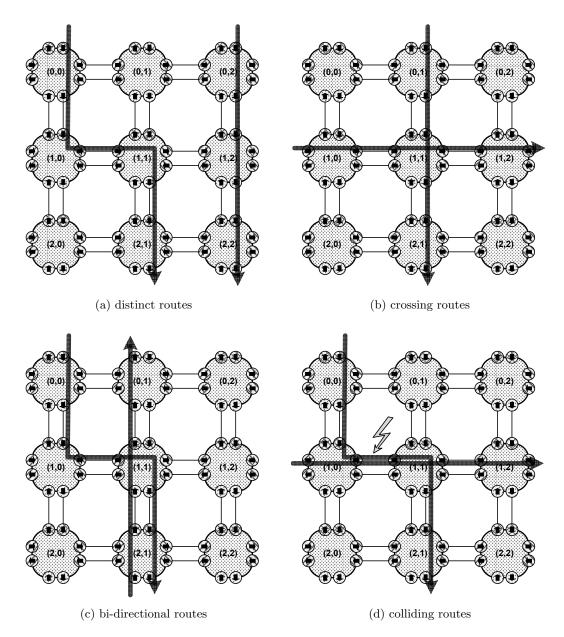

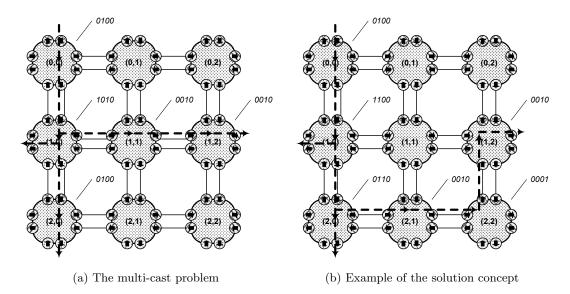

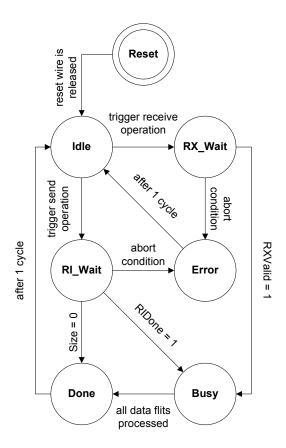

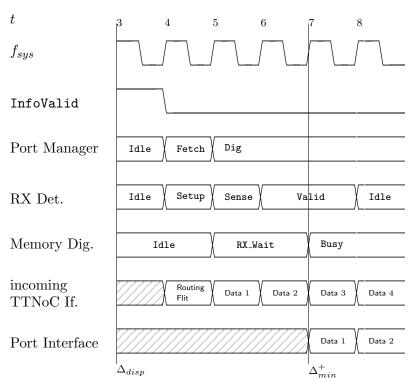

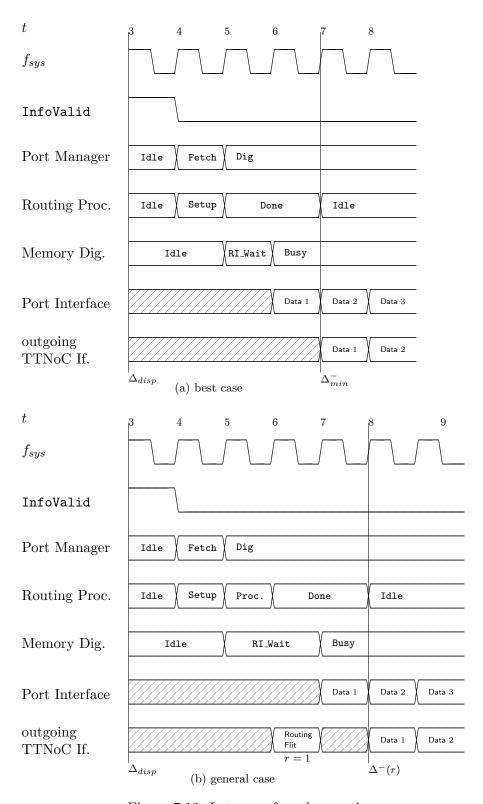

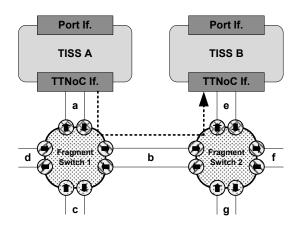

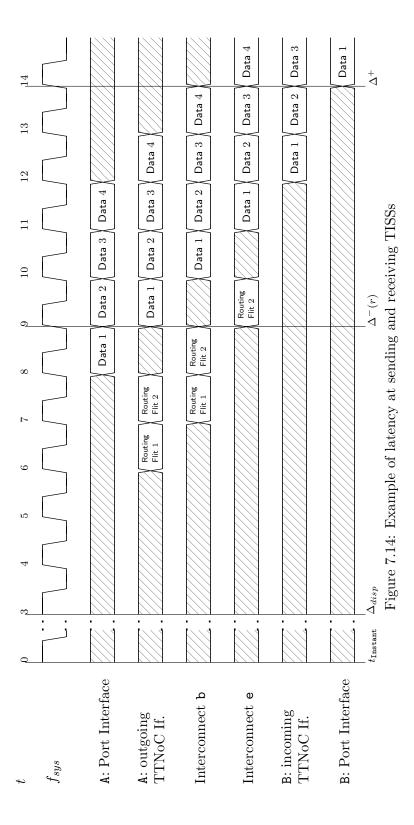

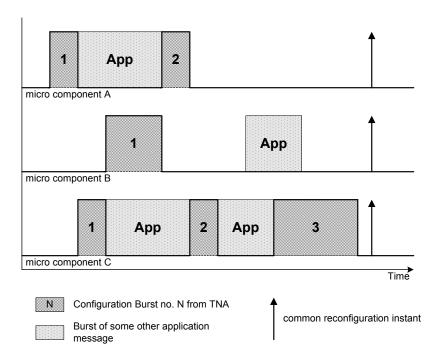

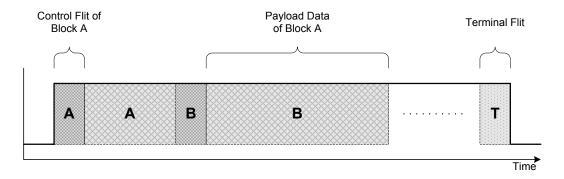

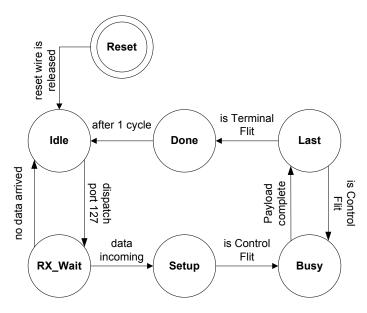

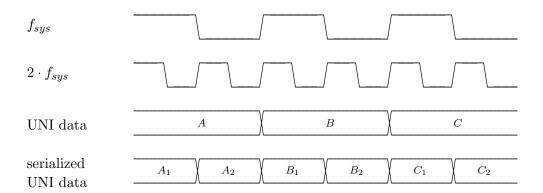

The Port Memory is a (true) dual-ported memory that is shared between the application computer of the host and the TISS. It houses the "ports", that is, "ports" contain the application data associated with messages of communication channels. The role of the Port Memory can take any kind of (true) dual-ported memory outside the TISS that is attached to the *Port Interface* (see section 5.1). Another possible implementation is a scratch pad or L1 cache of a microprocessor [HP06], whereas the CPU is attached at one side and the Port Interface at the other. Apparently, the implementation of the Port Memory is subject of the target hardware, in which the TTSoC architecture is hosted. The layout of the ports residing in the Port Memory is covered within the scope of the UNI, and therefore explained in chapter 5.