# Contributions to Efficiency and Robustness of Quasi Delay-Insensitive Circuits

DISSERTATION

zur Erlangung des akademischen Grades

Doktor der Technischen Wissenschaften

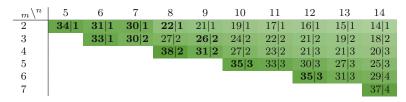

eingereicht von

Dipl.-Ing. Florian Huemer, BSc Matrikelnummer 0828465

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

Diese Dissertation haben begutachtet:

Prof. Matthias Függer

Prof. Alex Yakovlev

Wien, 17. Mai 2022

Florian Huemer

# Contributions to Efficiency and Robustness of Quasi Delay-Insensitive Circuits

# DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

# Doktor der Technischen Wissenschaften

by

Dipl.-Ing. Florian Huemer, BSc Registration Number 0828465

to the Faculty of Informatics

at the TU Wien

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

The dissertation has been reviewed by:

Prof. Matthias Függer

Prof. Alex Yakovlev

Vienna, 17th May, 2022

Florian Huemer

# Erklärung zur Verfassung der Arbeit

Dipl.-Ing. Florian Huemer, BSc

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 17. Mai 2022

Florian Huemer

# Acknowledgments

First of all, I want to thank Kimberly. Without your loving encouragement, help and devotion, especially during the last, very busy months when I put together this thesis, I would not have been able to achieve my goals with this work. Another huge "thank you" goes to Kiara. Your lighthearted and happy nature always sparks joy and is an incredible enrichment to our life. I also want to thank my parents for the great support through the early years of my studies.

Thanks to my adviser Andreas Steininger for introducing me into the world of asynchronous circuits and for the opportunity to work in this fascinating and multifaceted field. I am very grateful for your guidance throughout the years. Our numerous discussions and your specific view on problems always helped me in finding a path forward in my research.

Another special thank goes to Robert Najvirt for our collaborative work as well as for your insightful and valuable input for this work, which was always highly appreciated.

I also want to thank my current and past colleges at the Institute of Computer Engineering for their joint contribution in providing an excellent working environment. I could not have wished for a better setting for my studies. This includes, among many others, Arman, Giorgio, Heinz, Hugo, Krisztina, Kyrill, Martin, Raghda, Rojo, Roman, Thomas, Traude, Zaheer and of course Ulrich Schmid as the head of our working group. In addition to that extra special thanks go to Jürgen Maier and Florian Kriebel for the great cooperation during our joint teaching duties.

This research was partially supported by the project ENROL (grant I 3485-N31) of the Austrian Science Fund (FWF).

# Kurzfassung

Auf dem Gebiet der digitalen integrierten Schaltungen sind asynchrone und im speziellen quasi-laufzeitunabhängige (engl. quasi delay-insensitive (QDI)) Designs dafür bekannt, besonders robust gegenüber fertigungsbedingten Variationen bzw. Änderungen der Umgebungstemperatur sowie der Betriebsspannung zu sein (engl. process, voltage and timing (PVT) variations) – ein zunehmend erstrebenswertes Verhalten. Der Hauptgrund für diese Eigenschaften liegt darin, dass im QDI Design nur sehr wenige Signallaufzeitbedingungen notwendig sind, um das korrekte Verhalten einer Schaltung garantieren zu können. Dies steht im starken Kontrast zum starren zeitlichen Ablauf, der dem Funktionsprinzip synchroner Schaltungen zu Grunde liegt. Dieses flexible Zeitverhalten macht derartige QDI Designs prädestiniert für den Einsatz in einigen hoch relevanten Anwendungsgebieten – zwei davon stehen im Fokus dieser Dissertation. Die inhärente Robustheit gegenüber Laufzeitvariationen macht QDI Designs (i) bestens geeignet um laufzeitunabhängige (engl. delay-insensitive (DI)) Kommunikationskanäle für Inter- oder Intra-Chipverbindungen zu implementieren und (ii) eine vielversprechende Wahl für die Realisierung fehlertoleranter Systeme.

Der erste Teil dieser Arbeit wird sich daher mit der Untersuchung von laufzeitunabhängiger Kommunikation beschäftigen, welche die Implementierung hochflexibler Übertragungsstrecken erlaubt. Die einschlägige Fachliteratur zeigt, dass eine große Vielfalt an Möglichkeiten für die Realisierung solcher laufzeitunabhängigen Übertragungsstrecken existiert. Eine besondere Herausforderung, die sich dabei stellt, ist es, eine Balance zwischen verschiedenen, oft entgegengesetzten Optimierungskriterien für eine effiziente Implementierung zu finden. Durch eine umfassende Analyse von bereits bekannten, aber auch neu entwickelten Protokollen, Datenkodierungen und Schaltungen präsentiert diese Arbeit einige effiziente Lösungen und Optimierungsstrategien zur Realisierung von laufzeitunabhängiger Kommunikation. Weiters werden auch Schnittstellenmodule untersucht, die einen effizienten Datenaustausch zwischen synchronen und asynchronen Subsystemen einer Schaltung ermöglichen.

Der zweite Teil dieser Arbeit ist der Analyse der Fehlertoleranzaspekte von QDI Schaltungen gewidmet. Dabei wird der Fokus auf die Untersuchung von transienten Fehlern gelegt, welche sich typischerweise als kurze (wenige hundert Picosekunden dauernde) Spannungs- bzw. Stromspitzen in einer Schaltung manifestieren. Solche Fehler werden hauptsächlich durch kosmische Strahlung verursacht und beeinträchtigen eine Schaltung nur für einen begrenzten Zeitraum, verursachen also keinen permanenten Schaden. Der anhaltende Trend zu immer kleineren Strukturgrößen und Versorgungsspannungen macht digitale Schaltungen anfälliger für diesen Fehlertyp. Aus diesem Grund sind Maßnahmen zur Steigerung der Resilienz nicht nur für Systeme, die eine besonders hohe Zuverlässigkeit garantieren müssen, relevant, sondern in zunehmendem Maß auch für "normale" Verbraucherelektronik.

Die wissenschaftliche Untersuchung der Fehlertoleranzeigenschaften von QDI Schaltungen ist deshalb notwendig, weil sich deren Verhalten unter der Einwirkung von (transienten) Fehlern fundamental von dem synchroner Schaltungen unterscheidet, welche bereits gut erforscht sind. Ein einziger Fehler kann bei asynchronen Schaltungen beispielsweise zur Selbstblockierung (engl. deadlock) eines gesamten Systems oder zur Erzeugung neuer Datenelemente führen – Effekte, für die es in synchronen Schaltungen keine direkten Entsprechungen gibt. Das hat auch zur Folge, dass Maßnahmen zur Erkennung, Vermeidung und Behandlung von Fehlern, die für synchrone Designmethoden entwickelt wurden, nicht (immer) direkt auf asynchrone Schaltungen anwendbar sind. Deshalb beschäftigt sich diese Dissertation speziell mit der Analyse der Auswirkungen von transienten Fehlern auf QDI Designs und untersucht mögliche Verfahren zur Behandlung der auftretenden Effekte. Dabei werden sowohl bekannte Verfahren aus der Literatur sowie eigene Entwicklungen untersucht. Darüber hinaus wird ein umfassendes Softwarepaket für die Erzeugung, Simulation und Verifikation von asynchronen Schaltungen präsentiert, das auch bei weiteren Forschungsarbeiten zu diesem Thema Verwendung findet.

# Abstract

In the field of digital integrated circuits asynchronous and especially quasi delay-insensitive (QDI) designs are known to have a high robustness against process, voltage and temperature variations – an increasingly desired property. This is because for QDI designs only very few timing assumptions and constraints are necessary to guarantee the correct behavior of a circuit, which is in strong contrast to the rigid timing scheme of the traditional synchronous design style. This characteristic key-property opens up many interesting and highly relevant application areas – two of are the focus of this thesis. The inherent robustness against timing variations makes QDI design styles and techniques (i) perfectly suited for constructing delay-insensitive (DI) communication channels for global inter- or intra-chip interconnect and (ii) a promising choice for the design of fault-tolerant systems.

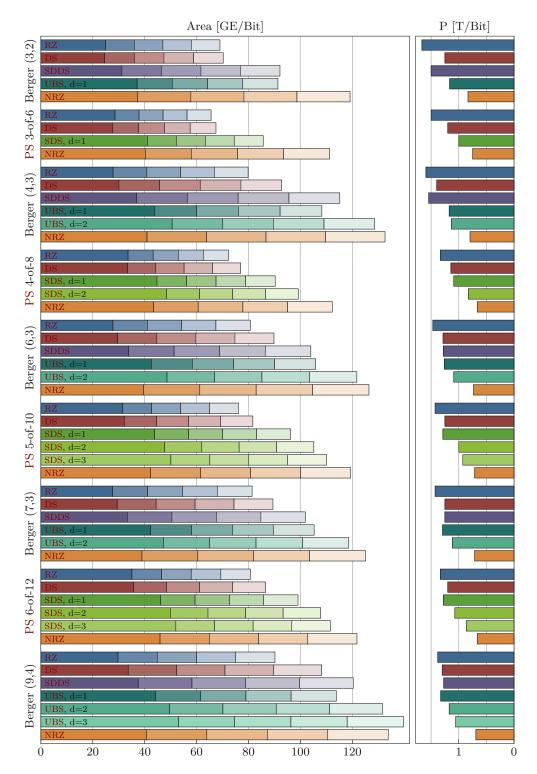

The first part of this work is, hence, devoted to the investigation of efficient ways to transmit information in a **DI** way, which allows for the construction of highly flexible communication links. Literature shows that there is a large design space for how such **DI** links can be implemented, with many different and often opposing optimization criteria. We provide a comprehensive analysis of available protocols and data encoding schemes and complement them with our own contributions to the field. Furthermore, we also investigate interface components that enable synchronous parts of a system to efficiently communicate with asynchronous ones.

The second part of this thesis explores the fault-tolerance aspects of QDI design. Here we focus our work on transient faults, i.e., short voltage spikes that affect a circuit over a certain amount of time (usually a few hundred picoseconds), which are primarily caused by cosmic radiation. The ongoing trend to ever smaller supply voltages and feature sizes makes circuits more prone to these types of faults. Thus, countermeasures against such effects are not exclusively relevant for highly dependable systems, but also for everyday end-user electronics.

Research into the fault-tolerance properties of QDI circuits is necessary, because their behavior under faults is fundamentally different from that of circuits constructed using the well understood synchronous paradigm. Here, even single faults can lead to the creation of additional erroneous data elements or complete system deadlocks – effects for which there is no direct counterpart in synchronous designs. This also means that faultmitigation and hardening strategies from synchronous design do not (always) directly translate over to the asynchronous world and that more specialized approaches are required. Hence, in this thesis, we analyze the effects of transient faults, investigate fault-mitigation strategies from literature and present and evaluate our own techniques. Moreover, we also contribute to the design of a comprehensive tool set to generate and simulate asynchronous circuits to enable further research in the future.

# Contents

| Kurzfassung          |                                           |                                            |               |  |   |

|----------------------|-------------------------------------------|--------------------------------------------|---------------|--|---|

| Abstract<br>Contents |                                           |                                            |               |  |   |

|                      |                                           |                                            |               |  | 1 |

|                      | $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Research Questions                         | $\frac{4}{5}$ |  |   |

| <b>2</b>             | Background and Related Work               |                                            |               |  |   |

|                      | 2.1                                       | Handshaking Protocols                      | 9             |  |   |

|                      | 2.2                                       | Delay Models                               | 12            |  |   |

|                      | 2.3                                       | Basic Asynchronous Circuit Elements        | 15            |  |   |

|                      | 2.4                                       | Channels and Static Data-Flow Structures   | 20            |  |   |

|                      | 2.5                                       | Bundled Data Circuits                      | 24            |  |   |

|                      | 2.6                                       | QDI Circuits                               | 25            |  |   |

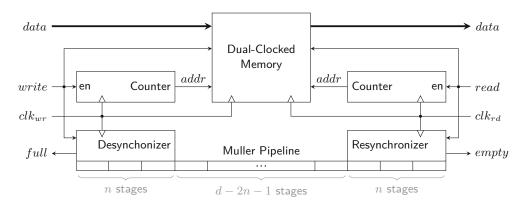

| 3                    | Crossing the Boundary to Asynchrony       |                                            |               |  |   |

|                      | 3.1                                       | Related Work                               | 35            |  |   |

|                      | 3.2                                       | Sampling Muller Pipelines                  | 36            |  |   |

|                      | 3.3                                       | Proposed Approach                          | 41            |  |   |

|                      | 3.4                                       | Desynchronizer                             | 43            |  |   |

|                      | 3.5                                       | Resynchronizer                             | 46            |  |   |

|                      | 3.6                                       | Results                                    | 49            |  |   |

|                      | 3.7                                       | Conclusion                                 | 52            |  |   |

| 4                    | Efficient Delay-Insensitive Communication |                                            |               |  |   |

|                      | 4.1                                       | Delay-Insensitive Codes                    | 57            |  |   |

|                      | 4.2                                       | Partially Systematic Constant-Weight Codes | 59            |  |   |

|                      | 4.3                                       | Hybrid Protocols                           | 66            |  |   |

|                      | 4.4                                       | Completion Detection                       | 73            |  |   |

|                      | 4.5                                       | Link Architecture                          | 85            |  |   |

|                      | 4.6                                       | Results                                    | 91            |  |   |

xiii

|                                | 4.7                | Conclusion                            | 101 |  |  |

|--------------------------------|--------------------|---------------------------------------|-----|--|--|

| 5                              | Asy                | nchronous Circuit Description         | 103 |  |  |

|                                | 5.1                | Language Specification                | 105 |  |  |

|                                | 5.2                | Python Production Rule Package        | 115 |  |  |

|                                | 5.3                | Dual-Rail Logic Synthesis             | 124 |  |  |

|                                | 5.4                | Bounded Model Checking                | 138 |  |  |

|                                | 5.5                | Conclusion                            | 156 |  |  |

| 6                              | Fau                | lt-Tolerance in QDI Circuits          | 159 |  |  |

|                                | 6.1                | Related Work                          | 160 |  |  |

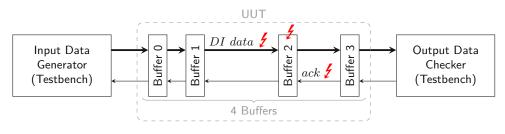

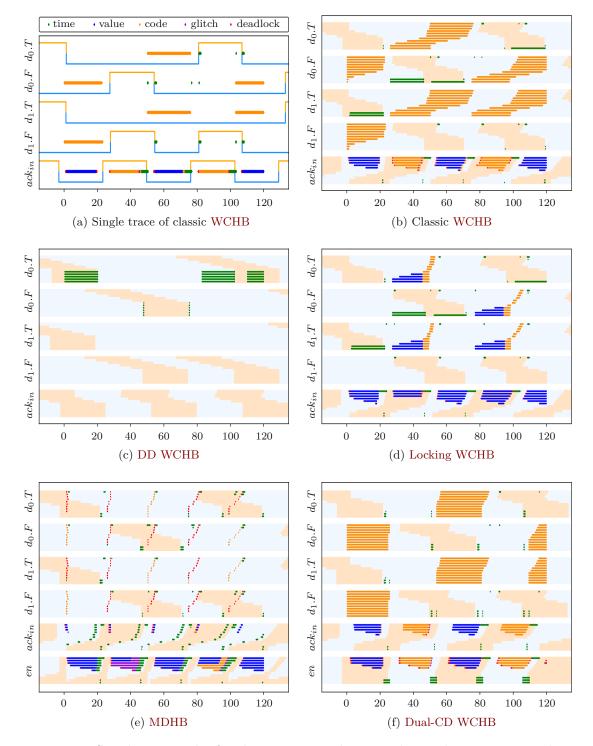

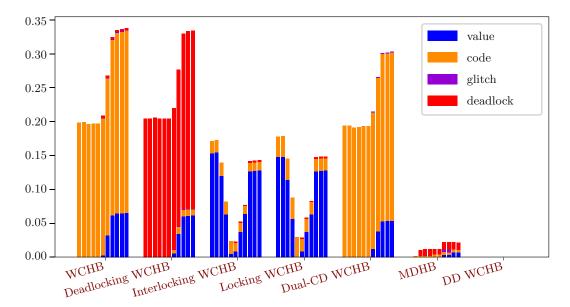

|                                | 6.2                | Fault Effects and Sensitivity Windows | 162 |  |  |

|                                | 6.3                | Fault Mitigation Strategies           | 164 |  |  |

|                                | 6.4                | Case Study: Pipeline                  | 165 |  |  |

|                                | 6.5                | Improved Buffer Designs               | 170 |  |  |

|                                | 6.6                | Case Study: Multiplier                | 173 |  |  |

|                                | 6.7                | Conclusion                            | 181 |  |  |

| 7 Conclusion and Future Work 1 |                    |                                       |     |  |  |

| List of Figures                |                    |                                       |     |  |  |

| List of Tables                 |                    |                                       |     |  |  |

| A                              | Acronyms           |                                       |     |  |  |

| G                              | Glossary           |                                       |     |  |  |

| Sc                             | Software and Tools |                                       |     |  |  |

| Bi                             | Bibliography       |                                       |     |  |  |

# CHAPTER

# Introduction

To organize the data transfer between storage elements in digital circuits (e.g., registers in a pipeline) the designer has basically two options. In the widely used synchronous design style all storage elements are (simultaneously) triggered by a clock signal, while asynchronous designs use local closed-loop handshakes to perform this task [Spa20].

Since the clock signal must be routed to every single flip-flop of a design it is, by its nature, a very high fan-out signal. However, at the same time it must exhibit a minimal amount of skew, because the rigid synchronous timing model demands that all flip-flops in a design are triggered at (virtually) the same time. This leads to the situation that a considerable amount of (electrical) energy and engineering resources have to be put into the clock tree of a synchronous chip to uphold this abstraction [DIBM03, Fri01, LKM10]. The ever-increasing miniaturization of semiconductor circuits and the accompanying rising in chip-complexity and clock rates further exacerbate these problems and challenges.

To determine the maximal possible clock frequency a design can be operated with, a static timing analysis is performed. This analysis essentially searches for the longest delay between any two flip-flops in a design, which is referred to as the critical path. The clock frequency must then be chosen such that the clock period allows for the signal traveling along the critical path to reach its destination before the next clock edge. Because of process, voltage and timing (PVT) variations, some timing margin has to be added to the critical path delay (which thus lowers the maximal clock frequency). This means that the speed of the circuit is determined solely by the slowest path in the design, even if this path may only be relevant in very rare cases. Nevertheless, the synchronous design style is indisputably popular for industrial/commercial designs because it models time as discrete steps, which greatly simplifies circuit design and speeds up the development process. Virtually all commercial electronic design automation (EDA) tools are specifically optimized for and tailored to synchronous design.

#### 1. INTRODUCTION

However, modern high-performance chips heavily use dynamic (voltage and) frequency scaling and often multiple separate clock domains [RMGW09, SMB<sup>+</sup>02], which undermines this abstraction to a certain degree. Hence, these designs naturally contain a large number of clock domain crossings which come with their own set of problems (metastability, latency, area overhead, etc.). This situation lead to the concept of Globally Asynchronous Locally Synchronous (GALS) Systems [Cha84, TGL07], which use synchronous "islands" communicating over some form of asynchronous interconnect [KSS<sup>+</sup>16].

For these reasons it makes sense to also consider an alternative. Since asynchronous design styles don't use a (global) clock signal they don't suffer from many of the discussed problems. However, they come with their own difficulties, challenges and drawbacks. Asynchronous design styles can (among other characteristics) be classified based on the timing assumptions imposed on the circuits.

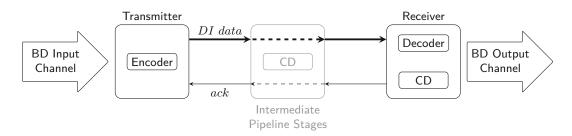

Bundled-data (BD) designs [SN07, Sut89] are quite similar to synchronous circuits as they use the same combinational logic to process binary data. However, instead of a clock signal they "bundle" the data that is transmitted from one storage element (the source) to the next (the sink) with an additional signal that indicates the validity of the data. This signal is usually referred to as *request* and can be viewed as a local replacement of the clock signal. It is used by the sink to trigger the capturing event of the transmitted data. As soon as the data is stored the sink uses the acknowledgment signal to inform the source that the data has been consumed and that new data can be sent<sup>1</sup>. Note that there is an immanent race condition between the request signal and the data that is being transmitted. It must be guaranteed that the request reaches the sink only after the data is stable at its input. In BD designs this timing constraint is usually fulfilled by inserting delay elements in the request paths. Thus, for correct circuit operation, it must be ensured that the delay on the request signal is at least as long as the critical path of the combinational logic between source and sink. Since for different input data, different critical paths through the combinational logic are relevant, it is even possible to dynamically select an appropriate delay using multiple different delay elements, depending on the actual data being processed – a strategy that improves the average-case performance of a circuit [Now96]. This is in contrast to the synchronous style which always has to accommodate the worst case. An important side-effect of the way asynchronous logic operates, is that there is only (switching) activity in the circuit when there is actually something being processed, which can have a positive impact on the power consumption of a chip. For synchronous designs, techniques like clock gating are required to achieve a similar effect. Asynchronous design styles further offer the benefit that circuits with different speeds can simply be connected without the need for clock domain crossing circuits, as would be needed for synchronous designs operating with different clock speeds.

Another possibility for implementing the request in an asynchronous circuit is to implicitly

<sup>&</sup>lt;sup>1</sup>This explanation assumes push channels. In pull channels the meaning of the request and acknowledgment signals are reversed, see [Spa20] for a more detailed discussion.

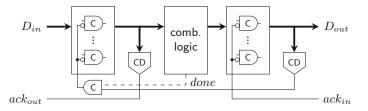

encode it in the data being transmitted. It is then the responsibility of the receiver to decide when this data is complete (i.e., valid) and can thus be consumed. This process is referred to as completion detection and the circuit that performs it is called completion detector (CD). It is only possible if the code used to encode the data has certain properties [Ver88]. Possible choices include constant-weight (e.g., dual-rail) and Berger codes. Of course such special encodings cause a certain overhead, especially when considering computational logic. In comparison to synchronous or BD circuits the data processing is very different and induces additional costs in terms of area and delay (and hence power). However, the huge advantage that comes with this design paradigm is that circuits can be implemented in a quasi delay-insensitive (QDI) way, which means that they are basically immune to delay variations<sup>2</sup>. This allows circuits to, e.g., easily cope with (power) optimization techniques like sub-threshold operation.

These properties open up promising application areas for QDI circuits. The robustness against timing variations makes delay-insensitive (DI) communication channels very interesting for global inter- or intra-chip interconnect [BF02,  $PFT^+07$ , Lin03, MG20], especially in the light of GALS systems. Moreover, asynchronous circuits in general and particularly QDI circuits are well-suited for systems that have to operate over a wide range of environment temperatures and supply voltages [KMM15, BRWG05]. Since their correct behavior doesn't rely on strict timing guarantees inside the circuit they can gracefully degrade performance and simply run slower if, e.g., the supply voltage is low. However, it is also worth noting that QDI circuits can be used to implement specialized high-performance hardware, which has been successfully demonstrated by Fulcrum Mircosystems with their network switches [DLD<sup>+</sup>14]. On a side note, there is also some indication that QDI circuits have some inherent robustness against power analysis attacks [HPL<sup>+</sup>16, LHCG17], which is important for security-critical applications.

**PVT** variations in digital circuits mainly cause delay faults. For a delay fault to manifest itself as an error in the value domain (i.e., a wrong binary value in some storage element) some timing assumption must be violated by it. However, as already discussed, asynchronous and especially **QDI** design styles have an inherent robustness against these faults. Unfortunately digital circuits are also affected by other environmental influences as well as internal defects which can directly cause value errors.

Basically faults can be classified as transient and permanent. Permanent faults, also referred to as hard-errors, result in physical damage to a circuit (gate oxide/interconnect wear-out, latchup, etc.) and cannot be corrected (although they may be tolerated to some degree) [WH11]. Transient faults, on the other hand, only affect a circuit over a limited period of time (usually a few hundred picoseconds) and cause a voltage spike on some internal node of the circuit, referred to as single-event transient (SET). If such a pulse is captured by a storage element it can manifest itself in the circuit's state, which is then referred to as a soft-error or single-event upset (SEU). In modern designs transient faults

<sup>&</sup>lt;sup>2</sup>As will be explained in more detail in Section 2.2, the only timing constraint in QDI circuits comes in the form of the isochronic fork assumption, which is also the reason why we speak of *quasi* delay-insensitive and not complete delay-insensitive circuits.

are mainly caused by cosmic radiation, i.e., high energy particles hitting a transistor in a chip [Bau05]. However, also cross-talk effects can play a role [MMK<sup>+</sup>02]. The ongoing trend to ever smaller supply voltages and feature sizes makes circuits more prone to these effects, because it reduces the critical charge a particle hit has to "overcome" to create an SET. Moreover, because the physical area a single transistor occupies is ever decreasing, the chance that a single particle hit affects multiple transistors is also increased. This altogether makes transient faults an issue not only for dependable, high-critically systems in harsh operation environment (like airplanes or space-probes) but also for everyday, non-safety-critical systems like consumer electronics [DDC05].

# 1.1 Research Questions

This thesis will focus on two aspects of QDI circuits which correspond to the two application areas identified in the discussion above. We want to (a) investigate efficient ways to transmit information in a DI way and (b) analyze existing QDI design styles for their behavior under transient faults and use this information to further improve their resilience to environmental influences.

## 1.1.1 Efficient DI Communication

For this research direction we start out by thoroughly investigating the current approaches for **DI** data transmission with regard to three main aspects:

• **DI** Codes (encoding/decoding overhead)

How are the data words (usually in unencoded binary representation) mapped to the code words of some DI code? What are the advantages and disadvantages of the different DI codes?

• Completion detection

What are the best known CDs for the different codes and are there any limitations to their QDI properties?

• Protocols and protocol converters Which protocols exist for DI communication and how do they impact both of the aforementioned points? How can the conversion between QDI and non-QDI asynchronous protocols be implemented most efficiently?

Based on this analysis we will then address the following research questions:

• While the mapping of data words to the code words is predefined for systematic codes like the Berger code, finding a good mapping for the non-systematic constant-weight codes is a non-trivial problem. From this observation, two questions arise: Is there a strategic way to perform this mapping? Can such a mapping simplify and, hence, improve the required encoders and decoders?

4

- Can the known CDs for constant-weight and Berger codes be further optimized with respect to area and delay? Can residual problems in the QDI properties be fixed?

- Are there areas in the design space of **DI** protocols, previously not explored by literature that have advantages over the state-of-the-art?

- How do the available and proposed design options compare to each other and how do they affect the overall overhead and performance of **DI** communication links?

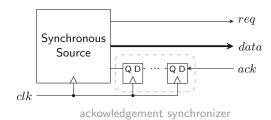

Another important research direction that we want to pursue in this thesis is the junction between the synchronous and asynchronous worlds. In particular we want to investigate how an efficient data transmission between a synchronous and an asynchronous timing domain can be implemented. This process of *timing domain crossing* is vital for all asynchronous systems that at some point have to exchange information with a synchronous system or have to provide some synchronous interface. Conversely, synchronous systems that want to leverage the benefits of asynchronous subsystems – like, e.g., in a GALS system – are in need of such conversion circuits. Obviously, these must be fast and energy efficient, otherwise they would undermine the original purpose of the conversion.

# 1.1.2 Fault Tolerance in QDI circuits

For the second part of this thesis we strive to answer the following questions:

- Is there some inherent fault resilience in **QDI** circuits (i.e., fault masking)? If so, where exactly does it originate from? Can it be leveraged or even enhanced?

- Are there certain parts or states of a QDI circuit that are specifically prone to faults? Can the system be operated in a way to minimize its fault susceptibility?

- What are the high-level effects of faults (e.g., deadlock, token generation, etc.)?

- Which circuit design strategies exist that can prevent some of the fault effects or make them at least less likely to affect the system?

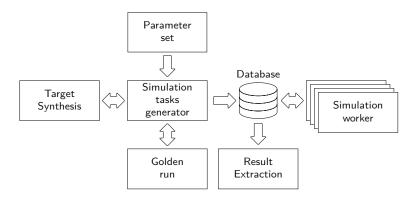

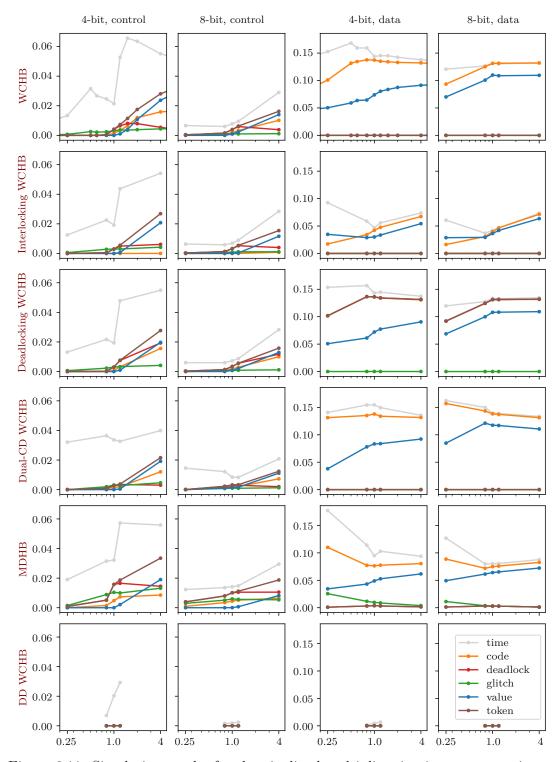

The main tool to investigate these research questions is simulation-based fault injection. Based on the analysis of the results gathered this way, we then present our own approaches for handling faults.

# 1.2 Organization

First, Chapter 2 gives a general overview of the field of asynchronous and specifically QDI circuits and discusses some related work. This will lay the foundation the following chapters build upon.

Chapters 3 and 4 tackle the research questions regarding DI communication, outlined in Section 1.1.1. First, Chapter 3 examines the challenges associated with passing data between synchronous and asynchronous timing domains and presents a novel solution to this problem. The results of this chapter have been published in

Florian Huemer and Andreas Steininger. Timing Domain Crossing using Muller Pipelines. In 26th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pages 44–53, May 2020

Then, Chapter 4 focuses on the actual DI codes, protocols and communication links and their associated overhead considering all the parameters posed in Section 1.1.1. The three publications that originate from this work appeared in

- Florian Huemer and Andreas Steininger. Partially Systematic Constant-Weight Codes for Delay-Insensitive Communication. In 24th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pages 17–25, May 2018

- Florian Huemer and Andreas Steininger. Advanced Delay-Insensitive 4-Phase Protocols. In Austrochip Workshop on Microelectronics (Austrochip), pages 50–55, Sep. 2018

- Florian Huemer and Andreas Steininger. Novel Approaches for Efficient Delay-Insensitive Communication. Journal of Low Power Electronics and Applications, 9(2), 2019

While the first two entries in this list are conference papers, the last one is an in-depth journal article that builds on top of them. The results of those two chapters are entirely my own work.

The second part of the thesis addresses the research questions outlined in Section 1.1.2, regarding the resilience of QDI circuits against (transient) faults and the tools we created to facilitate the required experiments for this investigation. Hence, Chapter 5 first presents our Python-based asynchronous circuit design tools package, that enables us to generate, verify and simulate the circuits needed in Chapter 6. Two selected parts of this Chapter 5 have been published in

- Florian Huemer and Andreas Steininger. Sorting Network based Full Adders for QDI Circuits. In Austrochip Workshop on Microelectronics (Austrochip), pages 21–28, Oct. 2020

- Florian Huemer, Robert Najvirt, and Andreas Steininger. On SAT-Based Model Checking of Speed-Independent Circuits. In *IEEE 25th International Symposium* on Design and Diagnostics of Electronic Circuits Systems (DDECS), pages 100–105, April 2022

6

I performed the majority of the research, conceptualization, design and implementation for the tools presented in this chapter. However, as this is a software project that is used by other people in our research group, I also received various useful suggestions for improvements and bugfixes, especially by Robert Najvirt.

Finally, Chapter 6 presents the research that is directly concerned with the topic of fault resilience of QDI circuits. Its results have been published in

- Florian Huemer, Robert Najvirt, and Andreas Steininger. Identification and Confinement of Fault Sensitivity Windows in QDI Logic. In Austrochip Workshop on Microelectronics (Austrochip), pages 29–36, Oct. 2020

- Patrick Behal, Florian Huemer, Robert Najvirt, Andreas Steininger, and Zaheer Tabassam. Towards Explaining the Fault Sensitivity of Different QDI Pipeline Styles. In 27th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pages 25–33, 2021

As part of a larger research project, those publications are collaborative works. However, I had a key role in the conceptualization and the design of the performed experiments as well as the analysis of the results. The proposed circuit improvements are entirely my own work. For performing the actual large-scale (fault-injection) simulations we relied on tools mainly development by Patrick Behal and Robert Najvirt [BHNS21].

Chapter 7 summarizes the results of my work and concludes the thesis.

# CHAPTER 2

# **Background and Related Work**

This chapter covers some of the basics of asynchronous design as well as common literature, that all followings chapters rely on. For a more thorough introduction we refer to [Spa20] and [BOF10].

## 2.1 Handshaking Protocols

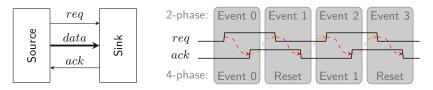

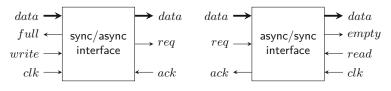

In contrast to the rigid time-driven regime of the synchronous design style, asynchronous circuits always use some form of closed-loop handshaking protocol to control the data transfer between storage elements (e.g., the individual buffer stages in a pipeline). As shown in Figure 2.1 this handshake (usually) involves two signals, which are referred to as request (req) and acknowledgment (ack). The rising edge of the req signal is typically used as an indicator by the source to notify the sink that new data is available. The sink then uses the ack signal to inform the source that it has received the data and that new data can be transmitted<sup>1</sup>.

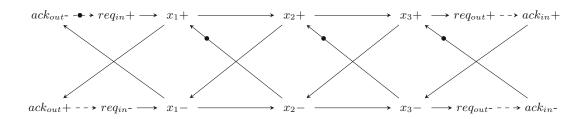

Figure 2.1: Asynchronous handshaking protocols

At this point we have to address the difference between 2-phase and 4-phase protocols, which is also shown in Figure 2.1. In the former case, every transition of req and ack conveys actual information. Hence, every handshaking cycle (labeled "Event 0-3" in the

<sup>&</sup>lt;sup>1</sup>This explanation assumes *push* channels. For *pull* channels the meaning of the request and acknowledgment signals are reversed, see [Spa20] for a more detailed discussion.

figure) consists of two transitions. 4-phase protocols, on the other side, always entail a reset phase where both signals return to zero again. This is also the reason why we will use the terms return-to-zero (RZ) and non-return-to-zero (NRZ) protocols, respectively.

In the following subsections we will discuss the two main classes of asynchronous protocols, namely **BD** and **DI** protocols. Note that there is also the option to let the source and sink communicate over just a single wire, which has been explored by Sutherland and Fairbanks in [SF01]. However, since this approach is not used in this work, we won't go into further detail on that.

### 2.1.1 Bundled Data Protocols

Note that there is an immanent race condition between the request signal and the data that is being transmitted. It must be guaranteed that the request reaches the sink only after the data is stable at its input. In the so called **BD** approach this is usually accomplished with a delay element in the request path. This requirement is not dissimilar from the setup-constraint in synchronous design and it has the same drawback, namely the need to know a bound for the propagation delay of the data path.

The advantage of this approach is that the transmitted data itself, does not need to be handled or encoded in any special way. In fact the data path of a BD circuit can be implemented exactly the same way as for a synchronous design. Moreover, when an RZ protocol is used typically only the handshaking signals (i.e., req and ack) go through the four phases (see Figure 2.1). The data can directly transition from one data word to the next.

The term **BD** stems from the fact that the data is *bundled* with the request and acknowledgment signals.

#### 2.1.2 Delay-Insensitive Protocols

The request mechanism does not need to be implemented as a dedicated signal. Another possibility is to implicitly encode the request into the transmitted data. It is then the responsibility of the receiver to decide when this data is complete (i.e., valid) and can thus be consumed. This process is referred to as completion detection and the component that performs this task is called a CD. It is only possible if the code used to encode the data has certain properties. Of course this encoding and the requirement for completion detection cause a certain overhead. However, it has the advantage that the communication is DI, i.e., the transitions on the individual wires (also referred to as rails) of a DI link may arrive in any order and there is no race condition between data and request (as with the BD approach).

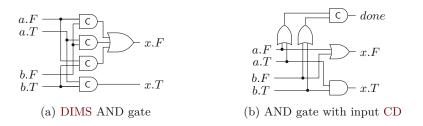

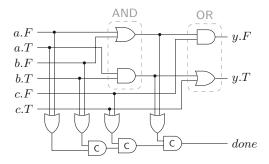

DI communication can also be implemented in a 2- or 4-phase scheme. In RZ protocols two successive code words (data phase) are always separated by a spacer (zero or null phase), which does not carry any information and is usually represented by logic zeros on all rails. Possible choices for the data encoding for 4-phase DI protocols are, e.g.,

constant-weight (m-of-n) or Berger codes [Ver88]. Further details on these codes will be presented in Section 4.1. In this section we will only use the dual-rail code, which technically also falls into the constant-weight category. The dual-rail code encodes each bit using two rails (i.e., wires) which we refer to as the true and false rail. Throughout this thesis we will use the point notation to denote the individual rails of a dual-rail signal. Hence, given the dual-rail bit d, d.T refers to its true rail, while d.F refers to its false rails, respectively.

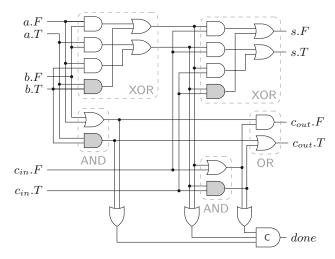

The dual-rail encoding is arguably the most simple DI code. Still, as will be explained in more detail in Section 2.6.2, combinational circuits (adhering to the QDI timing model, see Section 2.2) that operate on dual-rail encoded data easily entail more than double the hardware overhead, compared to a "classic" single-rail implementation of the same function. Circuits operating on more complex codes (with higher information density) that are often not even systematic (in contrast to the dual-rail code) would involve even higher hardware costs. Consequently, the dual-rail code is the only one of practical relevance for circuits that actually process data (in contrast to just transmitting it)<sup>2</sup>.

In order to decide whether dual-rail data is complete, the receiver only needs to check if there has been a transition on either the true or false rail of each received dual-rail signal pair. A task that can simply be implemented by an OR or NOR gate. However, more sophisticated codes often need much more complicated CDs, which will be thoroughly discussed in Section 4.4.

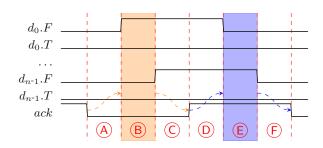

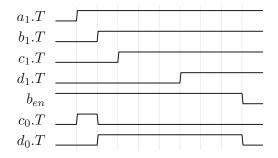

Figure 2.2 shows an example transmission of two dual-rail bits  $d_1$  and  $d_0$ . The order of the individual rails for the labels of the **DI** data trace in the figure is  $(d_1.T, d_1.F), (d_0.T, d_0.F)$ . The transmission starts out with a spacer, i.e., all data rails are zero. Then, the **DI** data bus transitions to the code word  $\mathbf{c}_n$ , which encodes a logic zero for both data bits (data phase). This condition is detected by the **CD** of the receiver and a rising transition on the *ack* signal is issued. After the acknowledgment the data rails return to the spacer again, which is in turn acknowledged by a falling transition on the *ack* signal. Then, another code word  $(\mathbf{c}_{n+1})$  is transmitted, which encodes the logic value  $d_1d_0 = 01$ .

Figure 2.2: RZ (4-phase) DI protocol

Note that a 4-phase protocol can also be implemented using a return-to-one scheme, where the spacer is implemented with logic ones on all wires. This approach is used by [MOPC13] to reduce energy consumption. To improve security by increasing a circuit's robustness against power analysis attacks, [SMBY05] proposes to dynamically switch between the all-one and all-zero spacer (either strictly alternating or randomly). The

<sup>&</sup>lt;sup>2</sup>Despite that, there is some research that also investigates other codes, e.g., [LG01] where a 1-of-4 code has been used.

authors further show that using different spacers for different circuit parts in a fine-grained manner, can also allow for area and throughput optimizations. To this end, [MBSC18] follows a similar strategy, although with a different gate-level logic style. However, strictly speaking, all of these techniques still use a 4-phase protocol.

For NRZ protocols, level or transition encoding can be used. With level-encoded protocols the currently transmitted value can directly be derived from the state of the DI bus. The Level-Endcoded Dual-Rail (LEDR) [DWD91] and Level-Encoded Transition Signaling (LETS) [MAMN08] protocols are examples for such a strategy.

For transition encoding every 4-phase DI code can be used. However, here the information is only contained in wire transition events (no matter the direction), the actual DI bus state is only meaningful when compared to the previous state. Hence, the actual transmitted code word can only be obtained by performing a bit-wise XOR between the current bit pattern on the bus and the previous one. Figure 2.3 visualizes this approach. Again two dual-rail bits with the binary values  $d_1d_0$  of 00, 01 and 10 are transmitted. The DI data bus starts with logic zero on all rails. Since the figure does not show the bus state prior to this value, we don't know which code word is being transmitted by it. After that the three data values are sent. Notice that there are no spacer phases where the data rails and the *ack* signal have to return to a known ground state. This has the obvious benefit of needing fewer bus transitions to transmit the same information when compared to 4-phase protocols. However, as will be shown in Chapter 4 there is significant area overhead associated with actual hardware implementations of this protocol. For example, the CD for the individual dual-rail signal pairs can no longer be implemented with an OR gate – now an XOR gate is required.

Figure 2.3: NRZ (2-phase) transition signaling DI protocol

In general it can be summarized that, for circuits that actually process data, practically only the RZ dual-rail protocol is relevant. All other codes and protocols find their application areas mainly in the transmission of data as will be discussed in Chapter 4.

## 2.2 Delay Models

As we will see in the following sections the design space for asynchronous circuits is quite large and diverse. One important classification aspect of asynchronous circuits or design styles are the imposed delay assumptions.

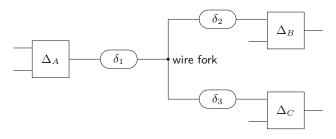

In this categorization the class of DI circuits uses the weakest timing assumptions. Here gate and wire delays can be completely arbitrary, the only restriction is that they have to be positive and finite. Consider the example circuit snippet shown in Figure 2.4.

Following the DI model, all gate delays  $\Delta_A$  to  $\Delta_C$  as well as the wire delays  $\delta_1$  to  $\delta_3$  may assume any positive value and the circuit would still be guaranteed to work correctly. However, as shown by Martin [Mar90], this class of circuits is very limited, as the selection of gates to construct such circuits is restricted to inverters and C gates (see Section 2.3.1).

To overcome these limitations, *isochronic forks* [vB92] are introduced, yielding the class of QDI circuits. While this delay model still does not impose any restrictions on gate delays, it demands that (some selected) wire forks must be *isochronic*, i.e., both signal paths after the fork must have the same delay. For the wire fork in Figure 2.4 this means that  $\delta_2 = \delta_3$  must hold. With this modification of the DI timing model, arbitrary circuits can be constructed. More detailed discussions of isochronic forks can be found in [Mar90, MM15]. However, as will be discussed in more detail below, in practice strict isochronicity is often not really required.

Figure 2.4: Asynchronous circuit model

For the class of speed-independent (SI) circuits [Mul59], we again have arbitrary gate delays. However, the wire delays are assumed to be zero ( $\delta_1 = \delta_2 = \delta_3 = 0$ ). Obviously, this timing model is the least realistic one, since interconnect delays play an important (and sometimes even dominating) role for modern technology nodes. However, if all wire forks in a circuit are regarded as isochronic, it is possible to merge the wire delays with the gate delays. For our example in Figure 2.4 this would add  $\delta_1$  and  $\delta_2$  to  $\Delta_A$ . Hence, an SI circuit is simply a QDI circuit where *all* forks are isochronic. There is also an interesting relation to DI circuits. A circuit is DI if a transformed circuit, where all wires have been replaced with buffers (after the fork points), is SI.

The models presented so far are precise (mathematical) concepts and apply to the gatelevel of asynchronous circuits. Self-timed (ST) circuits is a more general term and refers to circuits that need higher-level timing constraints or assumptions to work as intended. Such an assumption can for example ensure that the result of a certain (sub-) circuit must be available before another signal reaches its destination. These constraints are often enforced by the use of delay elements.

Note that an asynchronous design may apply different delay models for different parts of the design. As we will see in Section 2.5, the control logic for BD circuits is often SI or even DI, while the data path relies on timing assumptions enforced by delay elements making it ST.

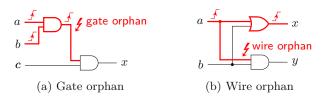

Figure 2.5: Examples for gate and wire orphans

Finally, we need to address the issue of gate and wire *orphans* and its relation to the presented delay models. From the definitions above we know that a circuit is considered DI, QDI or SI iff it operates correctly, despite of arbitrary gate (and wire) delays. Since under this condition, it is not possible to make any assumptions about the time it takes for a circuit (falling into one of these three categories) to process a set of input values, it must be possible to determine that the circuit is done processing by just observing its primary outputs. If the environment of a circuit is not able to unambiguously discern this situation, the next set of input values applied to the circuit may interfere with the previous one leading to incorrect behavior. An orphan transition is a transition that happens on some node (gate or wire) inside a circuit for some input pattern without having any influence on the primary outputs of the circuit (or sub-circuit). In other words it is an unobserved internal circuit transition. The unbounded delay model for gates (and wires) makes it impossible to make any assumptions about such events. Since the environment of a circuit eventually creates new input transitions in response to the observed output transitions, it is possible that an orphan interferes with actions inside a circuit caused by the new input transitions at unpredictable points in time. This can cause the circuit to produce invalid results or even deadlock.

We say that such a circuit contains gate or wire orphans, depending on where this transition can appear. Figure 2.5 demonstrates the difference between gate and wire orphans using two simple examples.

A gate orphan, as shown in Figure 2.5a, is produced by a gate G that changes its output value for some particular input pattern (i.e., a = b = 1, c = 0), but the output of G does not have any impact on the primary (observable) outputs of the circuit (i.e., x), because it is masked by some other gate. If a circuit is operated according to its specification and still contains gate orphans it cannot be considered DI, QDI or even SI.

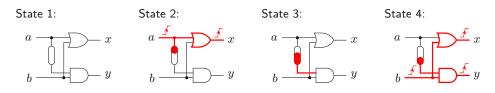

A wire orphan is an unobserved transition at some wire originating at a fork, as illustrated in Figure 2.5b. To show how a non-isochronic fork may lead to undesirable circuit behavior, let's examine the this example circuit a little more closely. For that purpose, consider the scenario shown in Figure 2.6. The figure shows how the state of the circuit from Figure 2.5b evolves over time, if we assume that the fork at the input a is non-isochronic. This is indicated by the delay element in the signal path going to the input of the AND gate. Initially (State 1) all inputs and output as well as all internal nodes of the circuit are low. Then, an input transition is applied to input a, which will set the output x driven by the OR gate (State 2). However, because of the long delay on the path to the AND gate, the transition will still be on its way to its destination when the environment already deasserted the input a again (State 3), constituting a wire orphan. The deassertion of a is correctly reflected by the deassertion of the output x, which in turn causes the environment to assert input b (State 4). However, because of the non-isochronicity of the fork the falling transition on input a still has not reached the AND gates, which means that the single input transition at b erroneously sets *both* outputs x and y.

Figure 2.6: Possible effect of a non-isochronic wire fork

This example shows how wire orphans can lead to problems in circuits if the delays on wire forks are not considered correctly. However, it also shows that there is not always the need for strict isochronicity. To fix the issue in the scenario in Figure 2.6, it is sufficient to demand that the delay (i.e., the skew between both paths after the fork) must be less than the time it takes the environment to switch the inputs from (a, b) = (1, 0) to (0, 0) and then to (0, 1) on top of the input-to-output delay caused by the OR gate. This condition is far easier to satisfy with an appropriate circuit layout than a "real" isochronic fork would be.

By definition QDI and SI circuits cannot contain wire orphans, since the isochronic fork assumption prevents this. However, for the DI model, wire orphans cannot be ruled out, and must be accounted for in the design.

We can conclude, that the presence for the potential of an orphan transition (gate or wire) automatically invalidates the DI, QDI or SI property of a circuit, as such a circuit would need additional timing assumptions to work correctly in every case.

## 2.3 Basic Asynchronous Circuit Elements

This section discusses some basic asynchronous circuits, circuit elements and specification methods used throughout the thesis.

## 2.3.1 Muller C Gate

An essential gate found in nearly every asynchronous circuit is the (Muller) C gate<sup>3</sup> [Mul59]. Figure 2.7a shows the circuit symbol that will be used throughout this thesis. Here a 2-input version is depicted, but conceptionally C gates can have any number of inputs. There are multiple ways to define the functionality of a C gate. In an informal

<sup>&</sup>lt;sup>3</sup>In literature also the term (Muller) C-Element is used.

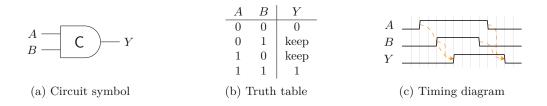

Figure 2.7: 2-input Muller C gate

way it might be described as an AND gate with hysteresis or an AND gate for transitions. This fact is also reflected by the circuit symbol.

For a more formal definition, consider Equation (2.1) describing the output of a 2-input C gate and the resulting truth table in Figure 2.7b. Notice that the output Y depends on the inputs A and B as well as the current state of the output itself, which we denoted with Y'.

$$Y = (A \land B) \lor (Y' \land (A \lor B)) \tag{2.1}$$

Thus, to set the output of a C gate to one, *all* inputs must be set to one (similarly to an AND gate). However, to reset the output back to zero again, *all* inputs must be set to zero as well. If only one input changes its logical value the output of the gate does not change ("keep" entries in the truth table). Figure 2.7c further illustrates this behavior using a timing diagram.

From this definition it is obvious that in order to implement a C gate some form of internal storage is required to keep track of its current state. There are multiple ways how this can be implemented in Complementary Metal-Oxide-Semiconductor (CMOS) logic [SEE98, MMC14]. The three main variants are referred to as the Martin, Sutherland and Van Berkel style C gate, which each have their own advantages and disadvantages [MOMC12]. The implementation costs for a 2-input C gate range form 8 to 12 transistors, which shows that they can be significantly more expensive than simple AND gates. Although, extending the CMOS C gate implementations to more than two inputs is possible, the resulting circuits quickly become quite large with several transistors in series in p- and n-stack. Hence, C gates with a high number of inputs are often broken up into (multi-level) C gate trees.

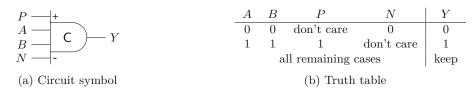

The C gate concept can also be extended to derive so called asymmetric C gates. Those gates have additional inputs marked with a plus or minus symbol (see Figure 2.8a). A positive input, i.e., one marked with a plus symbol, is only relevant for rising output transitions. This means that in order for an asymmetric C gate with positive inputs to switch its output to one, all normal as well as the positive inputs must be asserted. To switch back to zero only the normal inputs must be deasserted, the positive input may be kept asserted. Negative inputs have a similar effect for falling output transitions, i.e., an asymmetric C gate can only switch its output to zero if all normal and negative inputs are deasserted.

Figure 2.8: Asymmetric C gate with one positive, one negative two normal inputs

Asymmetric C gates can have any combination of positive, negative and normal inputs. Consider the example in Figure 2.8, showing an asymmetric C gate with one positive input P and one negative input N alongside its two normal inputs A and B. To set its output to one both of the normal inputs as well as the positive asymmetric input P must be asserted. To reset it A, B and N must be deasserted. The behavior can also be expressed using a Boolean formula in Equation (2.2).

$$Y = (A \land B \land P) \lor (Y' \land (A \lor B \lor N))$$

$$(2.2)$$

## 2.3.2 Muller Pipeline

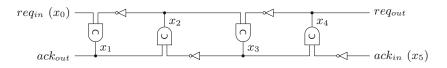

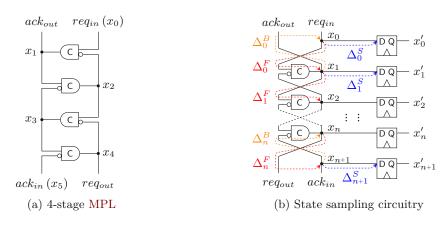

A Muller pipeline (MPL), such as the one shown in Figure 2.9, is a fundamental asynchronous circuit composed of C gates and inverters. Its purpose is to store and transport handshakes from its input  $(req_{in}, ack_{out})$  to its output port  $(req_{out}, ack_{in})$ , where each port consists of a request and an acknowledgment signal. In this sense it is also often described as a first in, first out (FIFO) buffer for transitions.

The MPL is completely agnostic to the handshaking protocol (2-phase vs. 4-phase). It is rather just a matter of interpretation, whether the stored transitions constitute 2-phase or 4-phase handshakes. Input handshakes can also be viewed as *tokens* that are fed into and travel through (or get stored in) the pipeline. In Figure 2.9 these tokens travel from left to right.

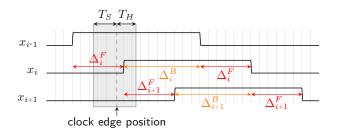

The operation principle of an MPL is quite straightforward. If the successor and predecessor of some node (i.e., C gate)  $x_i$   $(1 \le i \le n)$  in the pipeline differ in their logic values,  $x_i$  (eventually) takes on the value of its predecessor. The predecessor of  $x_1$  is  $x_0$ , i.e., the input request  $req_{in}$ , while the successor of  $x_n$  is  $x_{n+1}$ , i.e., the input acknowledgment  $ack_{in}$ .

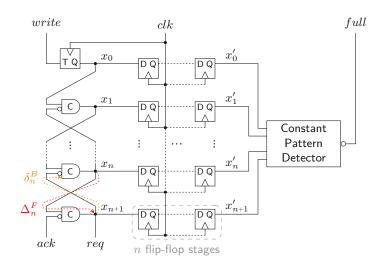

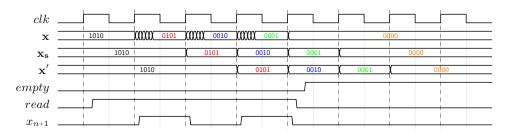

An MPL is considered empty when all its C gates store the same logic value, which must also be matched by input signals  $x_0$  and  $x_{n+1}$  ( $\forall_{0 \leq i \leq n} x_i = x_{i+1}$ ). A full pipeline is identified by a strictly alternating pattern on the circuit nodes  $x_0$  to  $x_{n+1}$  ( $\forall_{0 \leq i \leq n} x_i = \neg x_{i+1}$ ). Section 3.2 goes into further detail on the possible states of MPLs and also presents more formal definitions for them.

One interesting fact about the MPL is that it is a *completely* DI circuit, which means that it works correctly with arbitrary gate and wire delays. However, the MPL by itself

Figure 2.9: 4-stage Muller pipeline

is not yet a very useful circuit. It has nevertheless great significance as it is an often reoccurring structure in asynchronous designs and forms the (basic) control circuit for many pipelines, which will become clear in Section 2.5 and Section 2.6.

## 2.3.3 Asynchronous State Machines

Asynchronous state machines (also referred to as sequential or control circuits) play an important role in the design of asynchronous circuits. This section only examines SI circuits – so called Huffman circuits [Huf54], which rely on much stricter timing constraints, are not covered here.

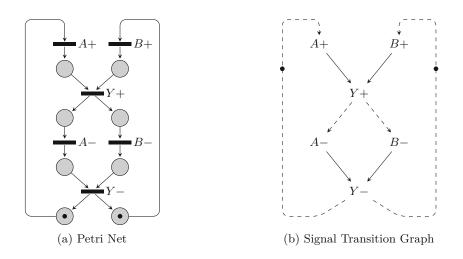

A convenient way to specify such circuits on an abstract level are Petri nets (PNs) [Pet62, Pet77] or more specifically Signal Transition Graphs (STGs) [RY85, Chu87]. These specifications can then be translated into gate-level SI circuits using fully automated software tools. For the STGs presented in this thesis Workcraft is used [PKY09].

STGs are a special type of PNs, a widely used model for distributed and concurrent systems. For the following explanations, consider the example of a PN specification of a Muller C gate. A PN is a directed graph that consists of two types of nodes: places (gray circles) and transitions (black bars). The predecessor nodes of a transition are always place nodes and vice versa, i.e., arcs always connect places and transitions. The PN is "executed" as tokens flow through it. Tokens (black circles) are stored in places. A transition can fire if there is a sufficient number of tokens at all of its inputs. If that is the case the tokens are removed from the input places and placed at the outputs of the transition. The exact number of tokens that are removed from the input places and put into the output places depends on the PN (and is usually specified by a label on the arc). If nothing is specified, as is the case with the C gate example at hand, exactly one token is removed from the input places.

Notice that the timing diagram of the C gate (shown in Figure 2.7c), can directly be translated into the PN.

As already mentioned STGs represent a special subclass of PNs. Here the transitions model real signal transitions and the edges of the graph indicate the causal and temporal order of these events. Signals can either be inputs to the STG or outputs that have to be generated by the STG. Internal signals are also allowed. For a PN to be a valid STG it must be free from deadlocks and the signal transitions for each variable must strictly alternate between rising (+) and falling (-) transitions for every possible execution path. For the purpose of circuit synthesis, it is usually also demanded that an STG has to be

Figure 2.10: C gate specifications

safe (or one-bounded), which means that there may never be more than one token in a place (all STGs presented in this work are safe) [KKY98]. It must further be guaranteed that once a transition is enabled it must fire, i.e., it may not be disabled again by another signal transition. Another important property is the so called "input free choice". This property demands that, if there are mutually exclusive paths through the graph then the selection which path is actually taken must be handled via mutually exclusive inputs to the STG. An immediate consequence of this constraint is that it is generally not possible to specify a mutex (i.e., a mutual exclusion element) with an STG. However, recently a slight extension has been proposed, which allows such conditions by introducing special mutex states in the STG [SKYL18].

For STGs, such as the one for the C gate shown in Figure 2.10b, places are not drawn if there is only a single incoming and outgoing edge, i.e., every edge can be considered to contain an implicit place. Hence, only for STGs containing choice, i.e., mutually exclusive paths, explicit places are needed. The initial state is indicated by the tokens on the appropriate edges. For further details please refer to [Spa20].

Note that STGs (as well as PNs) also have to model a (well-behaved) environment of the circuit. In the example at hand the environment simply sets both inputs when the output of the C gate is zero and resets them when the output is one. By convention we draw transitions that must be fulfilled by the environment using dashed lines.

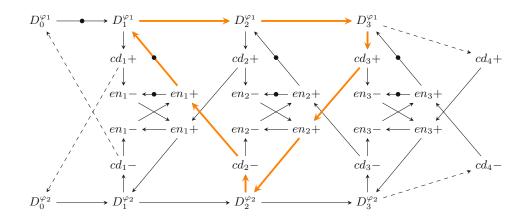

A slightly more complex example for an STG is shown in Figure 2.11. This STG specifies a 3-stage MPL with the inputs  $req_{in}$  and  $ack_{in}$  and the outputs  $req_{out}$  and  $ack_{out}$  as well as the three internal signals  $x_1$  to  $x_3$ . Using this visualization the operation rule of MPLs discussed in the previous section is clearly visible. Consider, for example the transition  $x_2+$ . The graph shows that in order for this transition to happen, the predecessor  $x_1$ must exhibit a rising transition while the successor  $x_3$  must transition to low.

Figure 2.11: STG describing a 3-stage MPL

## 2.4 Channels and Static Data-Flow Structures

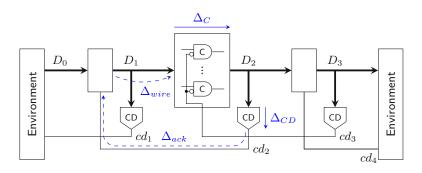

Before we discuss the actual implementation details of the various asynchronous design styles, we first introduce the concepts of channels and Static Data-Flow Stuctures (SDFSs). An asynchronous *channel* refers to a set of signals that are associated with each other and which are jointly used to convey (i.e., transmit) information. This includes data signals as well as their accompanying control signals (like *req* and *ack*). An asynchronous circuit can be viewed as a set of operations performed on such channels. This gives rise to the notion of SDFSs, which can be defined as directed graphs, where the edges are channels and the nodes are operations (such as combinational data transformations, storage/buffers or flow control elements). This representation corresponds to the register-transfer level (RTL) in synchronous circuits and facilitates abstract circuit design, that disregards the actual handshaking protocol (i.e., BD or DI) and the data encoding.

This section only focuses on 4-phase SDFSs (operating on 4-phase channels) since this thesis is mainly concerned with those types of circuits. Although Chapters 3 and 4 also deal with 2-phase channels and interfaces, only linear pipelines without any processing logic are used (hence, no need for SDFSs). However, with some modifications SDFSs can also be used to describe of 2-phase circuits. For more details we refer to [Spa20].

#### 2.4.1 Structure

As already mentioned SDFSs consist of different types of operation nodes that are shown in Figure 2.12. The notation introduced with this figure will be used throughout this thesis and is in accordance with [Spa20].

Figure 2.12: SDFS operations

20

The buffer (or latch) has a single input and output channel and stores data items, like registers in synchronous circuits do. These data items (conveyed by the channels) are referred to as tokens and will be explained in more detail in Section 2.4.2. A function or logic block applies a (Boolean) operation to the token on its (single) input channel and relays it to its (single) output channel. Using these two components it is already possible to design linear pipelines. However, for many practical applications feedback paths are required. Hence, we also need flow control components like fork, join, multiplexers, merge and demultiplexers<sup>4</sup>.

A fork takes a single input channel and splits it up into multiple output channels, each carrying either all the data of the input channel or only parts of it. The join performs the opposite operation, taking multiple input channels and combining them into a single output channel. The multiplexer also has multiple input channels, but only relays the token of one of them to its single output channel, depending on the token received on the control channel (top). A similar operation is performed by the merge component. However, here it must be guaranteed that there is only one token on one of the input channels (making the control input unnecessary). Finally, the demultiplexer takes an input token and relays it to a specific output channel, selected by the control input.

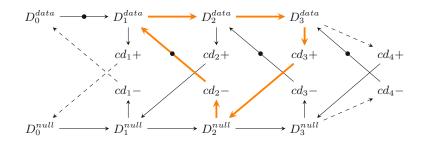

## 2.4.2 Token Flow

An SDFS models how data is processed by an asynchronous circuit. For that purpose, data items are represented as *tokens*, which flow through the system in accordance with a set of rules, called *token game semantic*. Note that multiple different rule sets exist, which may lead to different results when applied to the same graph [SPY07]. However, for the circuits discussed in this thesis there is no ambiguity, even under different token game semantics. Hence, we stick to an intuitive (informal) definition (refer to [SPY07] for strictly formal definitions of various token game semantics).

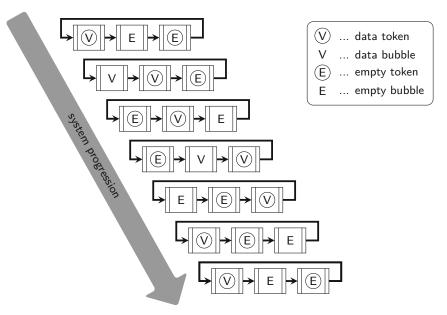

Since the behavior of 4-phase circuits is modeled, two types of tokens must be distinguished, namely data and empty tokens. Tokens can only be stored in buffers. In order for a token to enter and get stored in a buffer, the buffer must not already contain another token, i.e., it must be empty. To represent this absence of tokens the concept of *bubbles* is used. Whenever a token leaves a buffer it leaves behind such a bubble. Hence, we again have to distinguish between data and empty bubbles. Notice that those four types of flow elements (i.e., data tokens, empty tokens, data bubbles and empty bubbles) directly correspond to the four phases of the handshaking protocol. Asserting the request on a channel creates a data token, which becomes a data bubble when the associated acknowledgment is asserted. Following that event the request is deasserted again, creating an empty token that is eventually acknowledged to become an empty bubble. Thus, a bubble can be viewed as an old (already acknowledged and thus consumed) copy of the respective token.

$<sup>^{4}</sup>$ [Spa20] additionally defines the mutex and the arbiter component. However, since those elements are not used in the work, we don't cover them here.

A data token can only move forward to a buffer that contains an empty bubble, while an empty token can only enter a buffer that contains a data bubble. Hence, as tokens move forward through a circuit bubbles move backwards. Figure 2.13 shows how a single data token moves in a pipeline ring consisting of three buffers<sup>5</sup>.

Figure 2.13: Token progression in a 4-phase 3-stage pipeline ring SDFS

There are a few things to note about this example. It demonstrates that the minimal number of buffers for ring structures in (4-phase) SDFSs is three. Otherwise no token progression would be possible and the system would deadlock. Furthermore, each ring must contain at least one bubble, because again otherwise no token movement is possible. In fact, the performance of asynchronous circuits heavily depends on the number of bubbles, or more specifically the ratio of tokens and bubbles in the circuit. This means that sometimes it can be beneficial for the circuit performance to add additional buffers to facilitate a more efficient token flow. Also note that in a 4-phase pipeline that is completely full, only every second stage contains data tokens, since the other stages must hold empty tokens.

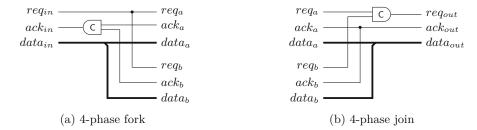

In contrast to buffers, flow control components don't store tokens but simply relay them from their input to their output channels. Presented with a token, a fork creates multiple output tokens. To implement this in hardware for a 4-phase BD channel the request signal is forked (see Figure 2.14a). The acknowledgment signals need to be joined using a C gate, since the fork must only generate an acknowledgment on its input channel when it has received acknowledgments on all output channels. For a join to generate an output token, tokens on all input channels must be present. Hence, a C gate is used to

$<sup>^{5}</sup>$ We use the letter V to denote data tokens/bubbles, in order to be consistent with the notation used in [Spa20], where data tokens (bubbles) are also referred to as "valid" tokens (bubbles).

join the individual request signals to generate the request for the output channel. The acknowledgment on the other hand can simply be relayed to all input channels.

Figure 2.14: Fork and join implementations for 4-phase BD channels

The fork and join circuits shown in Figure 2.14 can also be used for DI channels. The only modification that is required is the removal of the request signals, since the request is encoded in the data anyway.

The multiplexer and the demultiplexer operate in a slightly different way. For the multiplexer to produce an output data token, there must be a data token on the control input channel as well as a data token on the input data channel selected by this control token. Data tokens that might be pending on input data channels not selected by the control token are simply not relayed further or interacted with by the circuit. Such a token keeps sitting at the input data channel until an appropriate control token arrives. After the data token passed the multiplexer, an empty token must be provided by the same data input as well as the control input to complete the handshaking cycle on both of these channels. For the demultiplexer, the situation is similar. The data token at the input data channel is relayed to the output channel selected by the control channel token. After that, the following empty token on the data input channel will be relayed to the same output channel. Circuit implementations for these components and some special variations of them can be found in [Spa20].

Sections 2.5 and 2.6 will show how to implement buffers and pipelines with BD and QDI design styles. For the latter, also the implementation of function blocks will be discussed, since due to the DI encoding of the data it is not possible to simply use conventional combinational logic as is the case with BD circuits.

#### 2.4.3 Iterative Multiplier Example

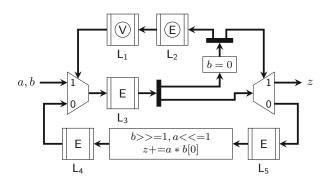

Figure 2.15 shows a slightly larger example for an SDFS specifying a multiplier circuit that uses an iterative approach to process the inputs a and b and produces the result z. The figure shows the basic flow control elements (fork, multiplexer and demultiplexer) as well as combinational blocks and buffers.

The circuit basically consists of two ring structures formed by the buffers  $L_3$ ,  $L_2$ ,  $L_1$  and  $L_3$ ,  $L_5$ ,  $L_4$ . The lower ring contains the actual data path, while the upper one contains

Figure 2.15: SDFS of an iterative multiplier circuit

the control logic for the multiplexer and demultiplexer. New tokens enter the circuit via the multiplexer at the input and then "rotate" in the circuit until the end condition b = 0is reached. This then leads to the result token in  $L_3$  being relayed to the output channel via the demultiplexer and enables a new token to enter the circuit. In [Spa20] this circuit would be identified as a typical application of the "while" template. Additional basic circuit templates for "for" and "if" constructs can also be found there.

# 2.5 Bundled Data Circuits

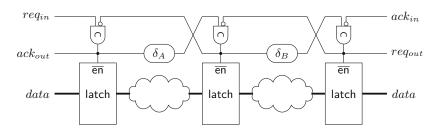

Over the years many different asynchronous design styles have been proposed. One of the most important and influential circuits in this context is certainly the MPL, which has already been covered in Section 2.3.2. The MPL can be utilized as control logic for the storage elements in BD circuits. Figure 2.16 demonstrates how this approach can be applied to construct a pipeline. The actual storage elements used in this circuit are D latches. The outputs of the C gates (comprising the MPL) are used to control whether the latches in a pipeline stage are opaque or transparent. In this configuration a 4-phase protocol has to be used to operate the pipeline. The figure shows two delay elements  $\delta_A$  and  $\delta_B$  that delay the request signal going from one pipeline stage to the next. These delays must be matched to the respective data path, i.e., the combinational logic in between the pipeline latches. For performance reasons the combinational delays of the stages should be balanced, because the slowest stage limits the throughput of the whole pipeline.

Note that, as already discussed in Section 2.4, in a full pipeline only every other stage contains actual data tokens. We can also see that here, when we look at the alternating pattern stored in the C gates of a full MPL. The pattern leads to only every other latch in the pipeline being opaque, i.e., storing a data token, the rest of the latches are transparent.

To operate an MPL-controlled BD circuit using a 2-phase handshaking protocol, different storage elements have to be used. For that purpose, Sutherland [Sut89] proposed so

Figure 2.16: 4-phase BD pipeline with MPL as handshake control circuit

called capture/pass latches. Another possibility are special double-edge triggered D flip-flops [YBA96].

The C gates in the MPL can be viewed as the simplest form of a 4-phase latch controller circuit which allow for little parallelism between the handshakes on the input and the output of a stage. Moreover, using it prevents the full utilization of the storage elements in a pipeline. To address this issue [FD96] describes advanced 4-phase latch controller circuits with different degrees of independence between input and output channels. A similar approach is also presented in [VSB10].

Another important and influential BD style, proposed by Singh and Nowick, is the MOUSETRAP pipeline [SN07]. This approach does not rely on C gates but instead uses a single XNOR gate and a D latch to control the pipeline's storage elements (D latches). MOUSETRAP operates using a 2-phase protocol and yields high-performance circuits.

Regarding 2-phase circuits, another notable design approach are so called Click elements [PtBdWM10]. Click-element-based pipelines use D flip-flops as storage elements. The pipeline stage controllers only use standard gates and a D flip-flop to store the current protocol phase, C gates are not required. This facilitates the integration of scan-chains, which is not so easy for, e.g., MPL- or MOUSETRAP-based circuits.

## 2.6 QDI Circuits

This section covers 4-phase QDI pipeline and logic styles. Since practically 2-phase circuits are not really used for building data processing circuits, they are not addressed here. However, Section 4.5 will show how to construct pipelines capable of transporting data using 2-phase DI protocols.

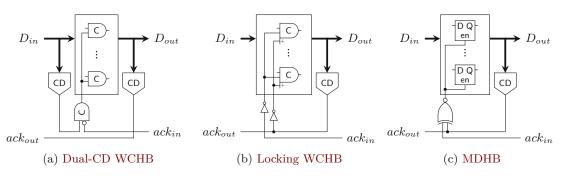

The QDI circuits used and covered by the work in this thesis, are mainly based on the Weak-Conditioned Half Buffer (WCHB) (Section 2.6.1) and the logic styles covered in Section 2.6.2. However, for the sake of completeness Section 2.6.3 briefly addresses asynchronous QDI design templates based on dual-rail domino logic.

Figure 2.17: 3-stage WCHB pipeline

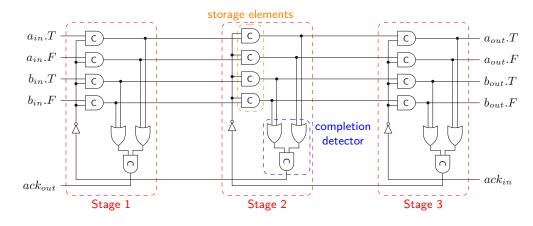

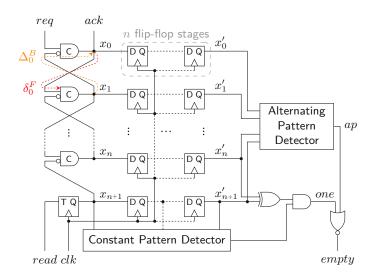

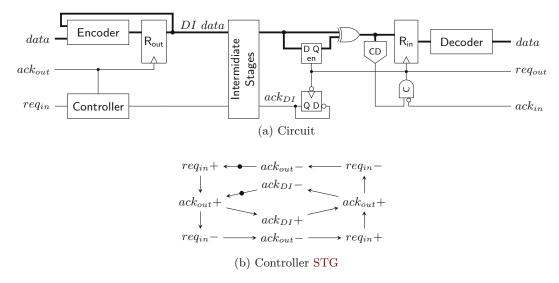

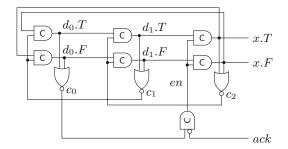

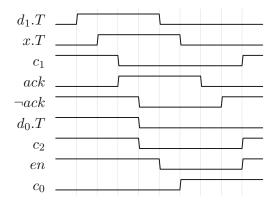

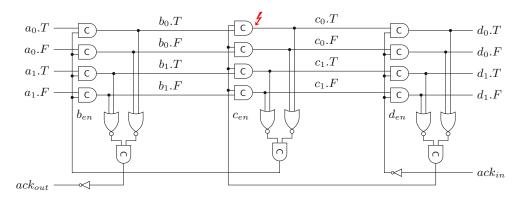

#### 2.6.1 Weak-Conditioned Half Buffer

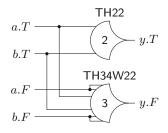

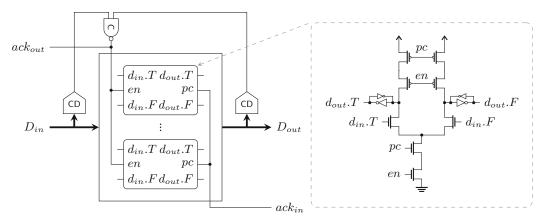

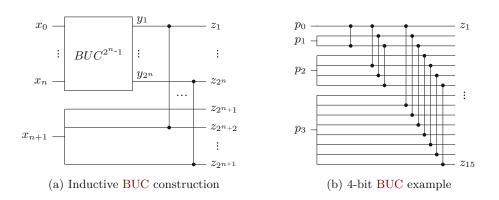

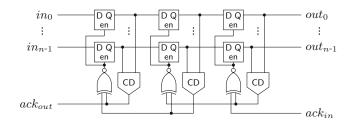

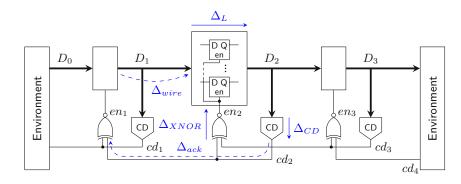

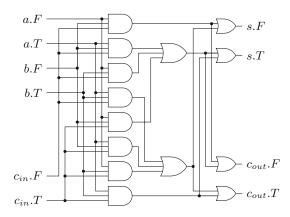

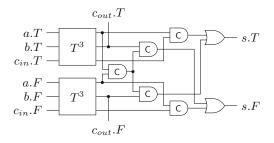

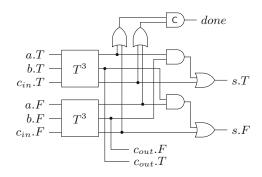

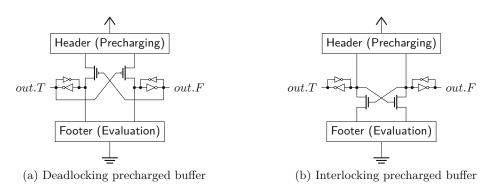

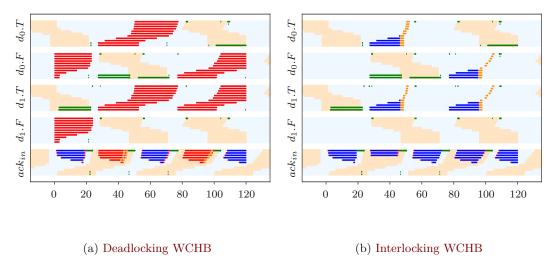

The arguably most basic way to construct QDI pipelines is using the WCHB, as demonstrated in Figure 2.17. The figure shows a 3-stage pipeline with a data width of two dual-rail bits (i.e., comprising four data rails). Each buffer consists of two main parts:

- The C gates used as storage elements for the incoming data, which are controlled by the acknowledgment signal of the succeeding stage.

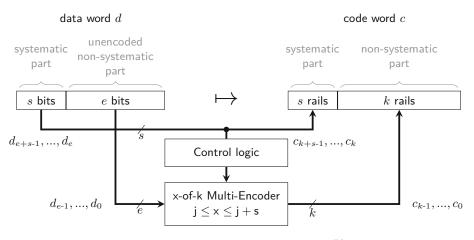

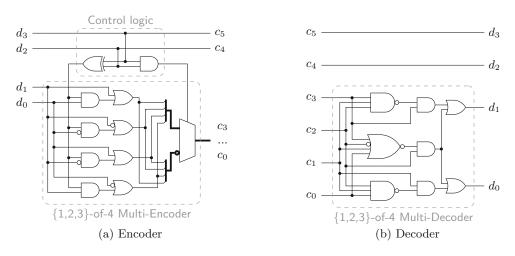

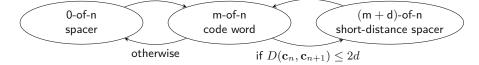

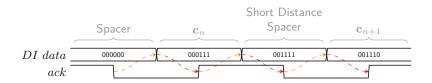

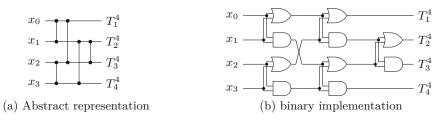

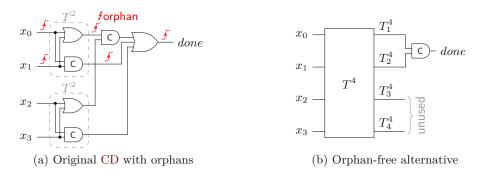

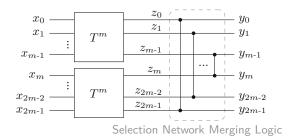

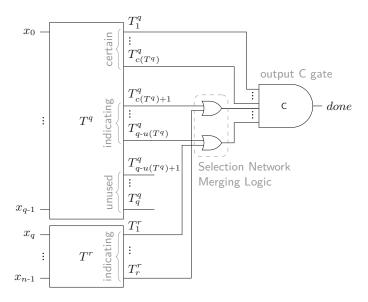

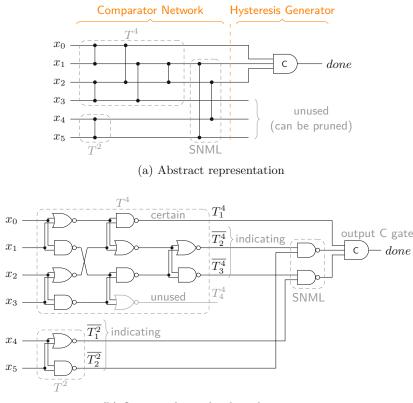

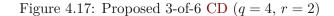

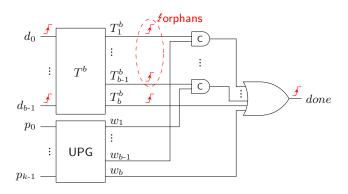

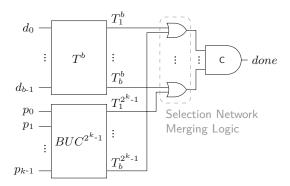

- A CD that monitors the output data signals and informs the preceding stage that a data or spacer token has been received.