The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### DISSERTATION

# Time-Predictable Java Chip-Multiprocessor

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines

Doktors der technischen Wissenschaften

unter der Leitung von

O.Univ.Prof. Dipl.-Ing. Dr. Herbert Grünbacher und Univ.Ass. Dipl.-Ing. Dr. Martin Schöberl Institut für Technische Informatik, Real-Time Systems Group

eingereicht an der Technischen Universität Wien, Fakultät für Informatik

von

Christof Pitter Matr.-Nr. 0327072 Markhofgasse 4/17, A-1030 Wien

Wien, im März 2009 \_\_\_\_\_

#### Time-Predictable Java Chip-Multiprocessor

Embedded systems are frequently used in real-time applications. Such applications must undergo timing analysis to ensure the timing constraints are met and the mission succeeds. Static worst-case execution time (WCET) analysis yields safe and precise upper bounds of tasks for a given hardware platform. It is preferred to measurement-based analysis methods because it guarantees to consider all possible execution times.

The purpose of this thesis is to design a novel chip-multiprocessor (CMP) solution for the development of Java real-time applications. This chip-multiprocessor system consists of a global physical memory accessible to all processors. A memory arbiter resolves concurrent access of multiple CPUs to the main memory. This architecture enables simple communication by accessing shared data objects. This thesis investigates if a shared memory multiprocessor can serve as a hardware platform for real-time applications. The great challenge is that tasks running on different CPUs of a CMP influence each others' execution times when accessing memory. Therefore, the system's arbiter must limit these interdependencies to be able to analyze WCETs of individual tasks. An adaptation of a static WCET tool for use with the multiprocessor architecture shall permit straightforward WCET analysis results.

In this study, the proposed CMP design is implemented using field-programmable gate array technology. Three different arbitration policies are developed: a fixed priority, a fair-based, and a time-sliced arbiter. Timing analysis approaches are carried out for the specified memory arbiters. Various CMP configurations with varying number of CPUs are evaluated, analyzed, and compared with respect to their real-time and average-case performance. Different benchmarks are used for executing programs on real hardware.

Results of this study have revealed that only the time-sliced memory arbitration scheme allows a calculation of viable WCET bounds of Java applications. A comparison of different CMP configurations shows that dynamic arbitration mechanisms are less predictable in the temporal domain but show better average-case program performance. The principal conclusion of this research demonstrates that timing analysis is possible for homogeneous multiprocessor systems with a shared memory.

#### Echtzeit Java Chip-Multiprozessor

Eingebettete Systeme werden häufig für sicherheitskritische Anwendungen verwendet. Solche Anwendungen erfordern eine Analyse des zeitlichen Verhaltens, um die zeitlichen Anforderungen garantieren und ein Fehlverhalten mit dramatischen Konsequenzen verhindern zu können. Die statische Worst-Case Execution Time (WCET) Analyse bestimmt sichere und präzise Grenzen für Programmausführungszeiten auf einer vorgegebenen Hardware-Plattform. Sie wird einer messbasierten Analyse vorgezogen, weil alle möglicherweise auftretenden Ausführungszeiten berücksichtigt werden.

Zweck dieser Dissertation ist die Entwicklung einer innovativen Chip-Multiprozessor (CMP) Lösung, für die Entwicklung von Echtzeitanwendungen mittels Java. Dieses symmetrische Multiprozessorsystem besteht aus mehreren CPUs und einem globalen Hauptspeicher. Ein Arbiter löst Speicherzugriffskonflikte zwischen mehreren Prozessoren auf. Die Kommunikation zwischen unterschiedlichen Prozessoren wird unter Verwendung von gemeinsam genutzter Variablen sichergestellt. Die Dissertation untersucht, ob ein symmetrischer Multiprozessor (SMP) als Plattform für Echtzeitanwendungen eingesetzt werden kann. Die große Herausforderung ist, dass sich die Ausführungszeiten der Tasks gegenseitig durch den gemeinsamen Speicherzugriff beeinflussen. Deshalb muss ein Arbiter diese gegenseitigen Beeinträchtigungen beschränken, um maximale Ausführungszeiten von individuellen Tasks analysieren zu können. Die Adaptierung eines bestehenden Analysetools für die Verwendung mit SMPs soll eine einfache Laufzeitbestimmung ermöglichen.

Ein Teil dieser Forschungsarbeit war die Implementierung des CMPs in der FPGA Technologie. Drei verschiedene Arbitertypen wurden entwickelt: ein Arbiter mit fixer Priorität, ein fairer Arbiter und ein Arbiter der die gemeinsame Speicherbandbreite in Zeitschlitze unterteilt. Das Zeitanalysekonzept wird individuell für jeden Arbiter ausführlich präsentiert. Verschiedene CMP-Konfigurationen mit unterschiedlicher Prozessoranzahl werden evaluiert, analysiert und in Bezug auf ihr Echtzeitverhalten bzw. auf ihre Rechenleistung verglichen. Dazu werden Benchmarks am Prototyp ausgeführt.

Die Dissertationsergebnisse bestätigen, dass nur der Arbiter mit dem Zeitschlitzverfahren eine Berechnung von brauchbaren, maximalen Ausführungszeiten zulässt. Der Vergleich von verschiedenen CMP-Konfigurationen zeigt, dass dynamische Arbitrieralgorithmen im Zeitbereich weniger vorhersagbar sind, jedoch größeres Leistungspotenzial besitzen. Diese Dissertation beweist, dass eine statische Zeitanalyse für einen SMP möglich ist.

#### Acknowledgements

The research for this thesis has been conducted during my employment as a research assistant at the Institute of Computer Engineering, Real-Time Systems Group within the Vienna University of Technology.

First, I would like to thank my adviser Professor Dr. Herbert Grünbacher for his skillful advice, valuable support, and helpful suggestions. I would like to extend my gratitude towards my secondary adviser Professor Dr. Reinhold Weiss for beneficial comments and suggestions on the thesis.

Special thanks go to my thesis co-adviser and colleague Martin Schöberl. We often had interesting and valuable discussions! I really appreciated your inspiration and motivation before upcoming paper submission deadlines. Your commitment and enthusiasm improved my work considerably during the last four years. Furthermore, I would like to thank Peter Puschner, Wolfgang Puffitsch, and Bernhard Gressl for constructive comments and helpful suggestions on the thesis.

I would like to acknowledge the financial support of the Austrian Federal Ministry of Transport, Innovation, and Technology (BMVIT). This work would not have been possible without their funding.

Special thanks go to my friends from all over the world, for keeping real life more interesting than the virtual one. They are an endless source of joy and inspiration and I would not be the same without them.

I am deeply grateful to Valerie and my family for their constant support. This thesis is dedicated to them.

# Contents

| 1 | Intr | roduction                                               | 1  |

|---|------|---------------------------------------------------------|----|

|   | 1.1  | Motivation                                              | 1  |

|   | 1.2  | Problem Definition and Objectives                       | 6  |

|   | 1.3  | Contributions                                           | 7  |

|   | 1.4  | Thesis Outline                                          | 9  |

| 2 | Tin  | ne Predictable CPU and DMA Shared Memory Access         | 15 |

|   | 2.1  | Introduction                                            | 16 |

|   | 2.2  | Related Work                                            | 17 |

|   | 2.3  | CPU/DMA shared memory access                            | 18 |

|   | 2.4  | Evaluation                                              | 21 |

|   | 2.5  | Conclusion and Future Work                              | 27 |

| 3 | Tov  | vards a Java Multiprocessor                             | 29 |

|   | 3.1  | Introduction                                            | 30 |

|   | 3.2  | Related Work                                            | 31 |

|   | 3.3  | CMP Architecture                                        | 33 |

|   | 3.4  | Implementation                                          | 39 |

|   | 3.5  | Experiments                                             | 43 |

|   | 3.6  | Conclusion                                              | 46 |

| 4 | Per  | formance Evaluation of a Java Chip-Multiprocessor       | 51 |

|   | 4.1  | Introduction                                            | 52 |

|   | 4.2  | Related Work                                            | 53 |

|   | 4.3  | Overview of JopCMP                                      | 56 |

|   | 4.4  | Performance Evaluation                                  | 61 |

|   | 4.5  | Conclusion and Future Work                              | 68 |

| 5 | Tin  | ne-Predictable Memory Arbitration for a Java Chip-Multi | -  |

|   | pro  | cessor                                                  | 73 |

|   | 5.1  | Introduction                                            | 74 |

|   | 5.2  | Related Work                                            | 75 |

|   | 5.3  | JopCMP Architecture                                     | 76 |

|   | 5.4  | WCET Analysis                                           | 79 |

|   |      |                                                         |    |

|   | 5.5  | Results                                                 | 86 |

| 6            | Fur            | ther Analysis and Evaluation                        | 95  |

|--------------|----------------|-----------------------------------------------------|-----|

|              | 6.1            | Memory Arbitration Revisited                        | 95  |

|              | 6.2            | Timing Analysis                                     |     |

|              | 6.3            | Performance Evaluation                              |     |

|              | 6.4            | Discussion                                          |     |

| 7            | Con            | iclusion and Outlook                                | 115 |

|              | 7.1            | Thesis Goal                                         | 115 |

|              | 7.2            | Research Compendium                                 | 116 |

|              | 7.3            | Thesis Relevance                                    | 117 |

|              | 7.4            | Outlook                                             |     |

|              | 7.5            | Summary                                             |     |

| $\mathbf{A}$ | Mea            | asurement-based Verification of Bytecode WCET Analy | -   |

|              | $\mathbf{sis}$ |                                                     | 123 |

|              | A.1            | Verification Goal                                   | 123 |

|              | A.2            | Verification Method                                 | 123 |

|              | A.3            | Verification Result of Bytecode iaload              | 124 |

| В            | Ana            | alyzed Bytecode WCETs                               | 127 |

| $\mathbf{C}$ | List           | of Acronyms                                         | 131 |

# List of Figures

| 1.1<br>1.2 | Example of safe upper execution time bounds                                   | 3<br>6 |

|------------|-------------------------------------------------------------------------------|--------|

| 2.1        | The blocked and the spread memory access scheme of the DMA task               | 19     |

| 2.2        | JopVga system                                                                 | 22     |

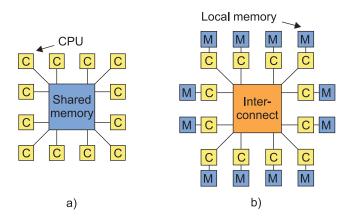

| 3.1        | CMP Memory Models: a) Shared memory model, b) Distributed shared memory model | 34     |

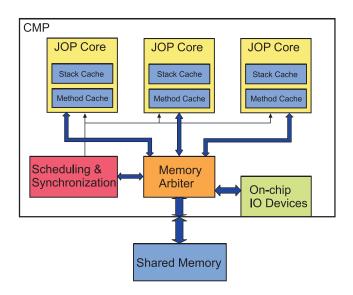

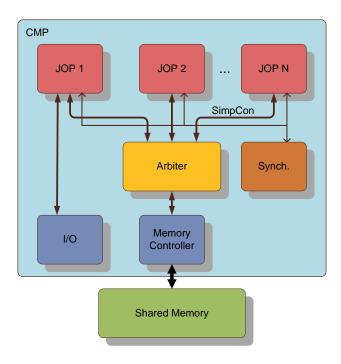

| 3.2        | Time predictable CMP architecture                                             | 38     |

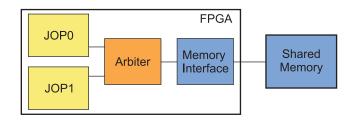

| 3.3        | Dual-core JopCMP system                                                       | 42     |

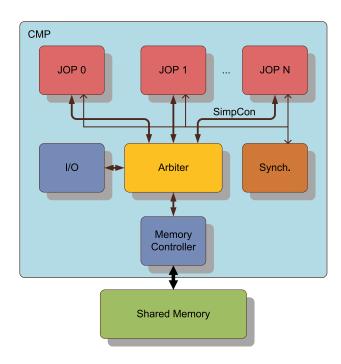

| 4.1        | Overview of JopCMP                                                            | 57     |

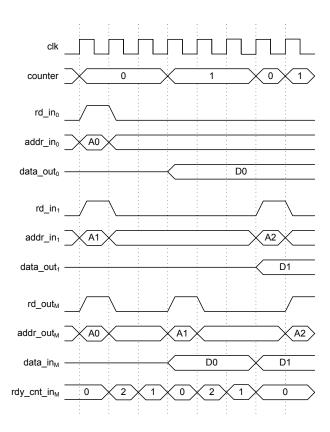

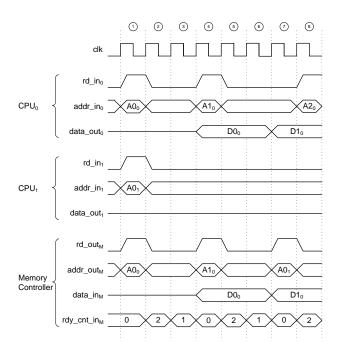

| 4.2        | Memory access arbitration of the fairness-based arbiter                       | 59     |

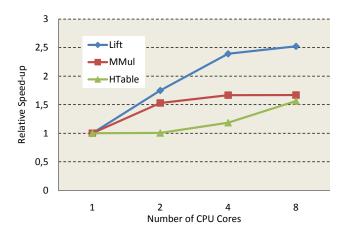

| 4.3        | Performance comparison of JopCMP, running three different benchmarks          | 66     |

|            |                                                                               |        |

| 5.1        | JopCMP Architecture                                                           | 77     |

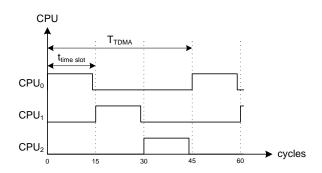

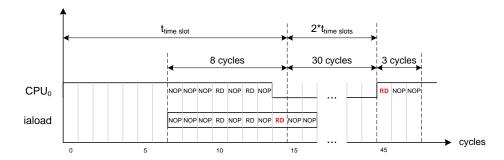

| 5.2        | Time slots of the CPUs                                                        | 84     |

| 5.3        | WCET calculation of iaload                                                    | 84     |

| 5.4        | Control flow graph of the simple loop                                         | 86     |

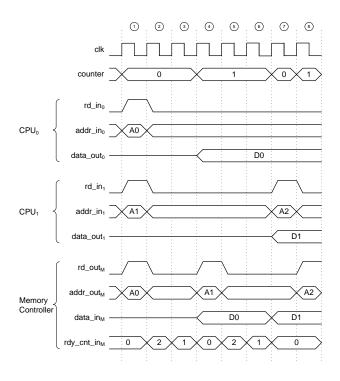

| 6.1        | Memory access arbitration of the fixed priority arbiter                       | 97     |

| 6.2        | Memory access arbitration of the fair arbiter                                 | 99     |

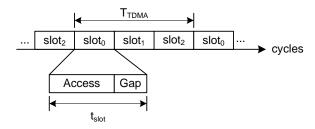

| 6.3        | TDMA period consisting of three time slots                                    | 100    |

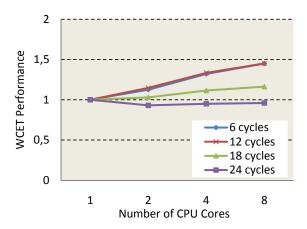

| 6.4        | WCET performance of the Lift benchmark                                        | 105    |

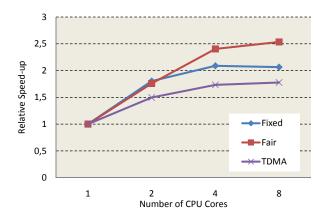

| 6.5        | Performance comparison of the Lift benchmark using different arbiters         | 107    |

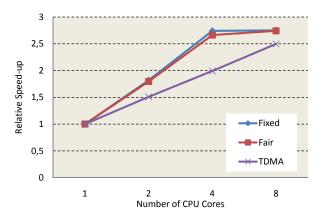

| 6.6        | Performance comparison of the MMul benchmark using dif-                       |        |

|            | •                                                                             | 108    |

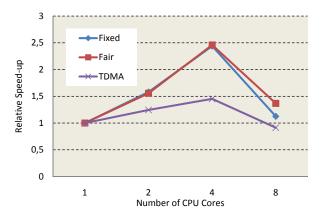

| 6.7        | Performance comparison of the ejip benchmark using different                  |        |

| -          | arbiters                                                                      | 110    |

|            |                                                                               |        |

# List of Tables

| 2.1 | Task set                                                      | 23 |

|-----|---------------------------------------------------------------|----|

| 2.2 | WCET estimates given in clock cycles                          | 25 |

| 2.3 | Task set for the WCET method                                  | 25 |

| 2.4 | Comparison of the response times of the task approach with    |    |

|     | blocked DMA ( $C_1$ and $R_1$ ) and the WCET method with      |    |

|     | spread DMA access $(C_2 \text{ and } R_2)$                    | 26 |

| 2.5 | Comparison of the system performances in iterations/s         | 27 |

| 3.1 | Benchmark results in iterations/s for a single-core JOP at    |    |

|     | different clock frequencies                                   | 43 |

| 3.2 | Benchmark results in iterations/s of a dual JopCMP system     |    |

|     | at a clock frequency of 80 MHz                                | 44 |

| 3.3 | Benchmark results in iterations/s of a tri-core JOP system at |    |

|     | a clock frequency of 75 MHz                                   | 45 |

| 3.4 | Comparison of resource consumption between JOP and the        |    |

|     | JopCMP versions                                               | 46 |

| 4.1 | Execution time and memory bandwidth utilization of Lift,      |    |

|     | Altde2 @ 90 MHz                                               | 64 |

| 4.2 | Execution time and memory bandwidth utilization of MMul,      |    |

|     | Altde2 @ 90 MHz                                               | 65 |

| 4.3 | Execution time and memory bandwidth utilization of HTable,    |    |

|     | Altde2 @ 90 MHz                                               | 65 |

| 4.4 | Execution time and memory bandwidth utilization of Lift,      |    |

|     | Cycore @ 60 MHz                                               | 67 |

| 4.5 | Performance and size of JopCMP relative to picoJava in the    |    |

|     | same FPGA board                                               | 68 |

| 4.6 | Synthesis Results on the Cyclone II FPGA (EP2C35)             | 69 |

| 5.1 | Bytecodes accessing the shared memory                         | 81 |

| 5.2 | Java bytecodes and basic blocks of the loop                   | 85 |

| 5.3 | Analyzed WCET of the loop example depending on the sys-       |    |

|     | tem configuration                                             | 87 |

| 5.4 | Analyzed WCET and measured execution time of the loop         |    |

|     | example                                                       | 88 |

| 5.5 | Analyzed WCET and measured execution time of the Lift benchmark    | 90  |

|-----|--------------------------------------------------------------------|-----|

| 6.1 | Analyzed WCET and measured execution time of the Lift benchmark    | 103 |

| 6.2 | Performance comparison of different arbiter types using the        | 103 |

| 0.2 | Lift benchmark                                                     | 107 |

| 6.3 | Performance comparison of different arbiter types using the        | 101 |

| 0.0 | MMul benchmark.                                                    | 108 |

| 6.4 | Performance comparison of different arbiter types using the        |     |

|     | ejip benchmark                                                     | 109 |

| 6.5 | Comparison of the arbitration policies                             | 111 |

| A.1 | Java bytecodes of sample assignment                                | 124 |

| B.1 | Bytecode WCETs depending on CMP configuration in clock             |     |

|     | cycles. The time slot size is varied between 3 and 30 cycles       | 127 |

| B.1 | Bytecode WCETs depending on CMP configuration in clock             |     |

|     | cycles. The time slot size is varied between 3 and 30 cycles. $$ . | 128 |

| B.2 | Bytecode WCETs depending on CMP configuration in clock             |     |

|     | cycles. The time slot size is varied between 6 and 12 cycles. $$ . | 128 |

| B.3 | Bytecode WCETs depending on a CMP system with larger               |     |

|     | memory access times                                                | 129 |

# Introduction

This thesis introduces a Time-Predictable Java Chip-Multiprocessor. It is a homogeneous chip-multiprocessor based on a Java processor core, an implementation of a Java Virtual Machine in hardware. It features a high-performance embedded system for Java real-time applications. This chapter describes the motivation for this project. Furthermore, an overview of the project's major contributions to the field and an outline of the thesis are given.

#### 1.1 Motivation

Today embedded systems are omnipresent in modern society and play an important role in our lives. According to [2], it has been estimated that 99% of all processors aim at the embedded systems market. Turley [16] states that only about 2% of microprocessors are used for personal computers. Embedded devices include household appliances like dish washers or coffee machines, consumer electronic devices like MP3-players or digital cameras. Telecommunication applications like personal digital assistants, cell phones, or networking appliances like switches or routers are further examples. The automotive industry is another key driver of the embedded system market. Today, every car contains from about 40 up to 70 electrical control units [3, 10]. All these applications represent only a random selection of the highest growing segment in the computing market.

#### 1.1.1 Real-Time Embedded Systems

Real-time embedded systems are embedded systems with timing requirements. An accurate definition of a real-time computer system can be found in [7] p. 2:

A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant at which these results are produced.

A real-time computer system has to produce logically correct results within a specified period of time. If a correct computation result is late, it will be considered useless. In case of a hard real-time system, a late computation may cause a critical system failure leading to disastrous consequences possibly endangering human life. A soft real-time system can tolerate results that occasionally miss their deadlines. The system still produces correct results [2], but accompanied by an inferior service quality (e.g. flickering of a user interface display).

Real-time embedded systems often have to handle concurrent tasks, such as communication with various peripheral systems, computing values for a control loop, or responding to external events. A natural way to handle these concurrent jobs is to split them up into individual tasks. A task is classified a hard real-time task, if a missed deadline may result in a catastrophe [2]. Every hard real-time system contains at least one so-called hard real-time task. Typical examples are embedded devices used in industries like automotive and rail traffic, medicine, avionics, industrial automation, or nuclear power plants.

Many embedded systems are used for applications that prioritize real-time behavior over processing power. Such real-time systems must undergo a timing analysis. Therefore, the worst-case execution time (WCET) of each application task in the system has to be a known factor. Only if these upper bounds are calculable can the task set be analyzed for schedulability on a given processor.

#### 1.1.2 Worst-Case Execution Time

The WCET is the amount of time a task eventually needs to execute under worst-case conditions on a given processor. In [17], Wilhelm et al. define the goal of WCET analysis concerning the upper bounds of execution time thus:

1. they have to be safe, and

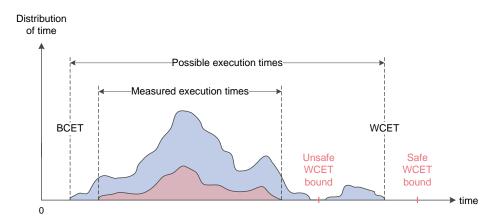

Figure 1.1: Example of safe upper execution time bounds.

#### 2. should be as tight as possible.

The calculated upper time bounds have to be safe in order to ensure hard real-time behavior; otherwise, unpredictable system reactions could put the mission at risk, leading to serious consequences. Moreover, the upper bounds should be as tight as possible to keep the overestimation low in order to conserve resources.

Figure 1.1 shows the variable execution times of a sample program. *Possible execution times* include the best-case execution time (BCET) and the WCET. Additionally, *measured execution times* are shown. The goal of WCET analysis is to find the WCET itself, or an upper bound that is safe and as tight as possible. Unsafe WCET bounds are smaller estimates than the WCET. All upper bounds larger than the WCET are safe. The larger they are, the higher the overestimation of the WCET.

There are three different methods to estimate the WCET of a given task: by measurement, static analysis, or a hybrid approach combining both methods. A WCET analysis by measurement gauges the execution time of a program code using various input data. The estimates are easy to obtain because the analysis is performed on the actual hardware. Therefore, it is especially useful if average-case performance is of interest. A large drawback of the measurement-based method is that the measured WCET result does not reliably confirm that the worst-case program path has been triggered [4], as shown in Figure 1.1.

The objective of a static WCET analysis is to find the maximum execution path and the WCET of a program. It provides a safe upper bound by analyzing the program before runtime, independent of any input values. Even though this method requires an elaborate creation of a precise processor

model, it is the only possibility to obtain a validated upper bound of the application code. Therefore, this analysis method is especially suitable for safety-critical systems.

A hybrid WCET analysis approach starts with a static analysis of the program. The code is split into partitions. Execution times from these code fragments are derived by measurement on real hardware. Finally, these execution times are added to the static analysis model, which calculates the WCET result. No processor model is needed like it is in the static analysis, but safe WCET bounds cannot be guaranteed.

In summary, measurement and hybrid-based analysis can be sufficient for soft real-time systems, but the author believes that static analysis should become the conventional approach to modern hard real-time systems.

#### 1.1.3 Chip-Multiprocessors

Modern applications demand ever-increasing processing power. They act as main drivers for the semiconductor industry. For over 35 years, transistors have been getting faster and clock frequency has adapted accordingly. Additionally, the number of transistors on an integrated circuit at a given cost doubles every 24 months, as described by Moore's Law [9]. The availability of more transistors facilitated an instruction-level parallelism (ILP) approach, which was the primary processor design objective between the mid-1980s and the start of the 21st century. According to [6], processor designers are now reaching the limits of exploiting ILP efficiently. Unfortunately, semiconductor technology has also reached its apex in recent years because of theoretical physical limits. As a result, the frequency, which used to increase exponentially, has leveled off [8].

According to [6], chip-multiprocessors (CMP) are the future in performance enhancement. The CMP technology integrates two or more processing units and a sophisticated communication network into a single integrated circuit. A major advantage of this approach is that any progress in processing power would not be accompanied by an increase in hardware complexity of single processors. Consequently, several processing units coexist on an integrated circuit, utilizing billions of transistors efficiently. According to [18], CMPs combine the significant demands of embedded systems: increased performance, lower power consumption, and cost efficiency.

#### 1.1.4 Java Technology

Traditionally, real-time applications have been designed using assembly languages. Due to hardware advancements and increasing program complexity in embedded system design, a higher level of abstraction was needed. Subsequently, the C programming language was introduced. More recently, embedded systems have been designed using the C++ programming language, because of its object-oriented feature and several enhancements of C. The increasing size and complexity of today's applications make ever higher demands on the design. The cost of debugging and maintaining the code increases continuously. In summary, the productivity suffers from low-level programming languages.

Java [5] has proven its success in the field of web, desktop and mobile applications. This high-level, object-oriented language has its advantages in the ease of program reuse, robustness, security, and portability. Java does not suffer the pitfalls of the C-based programming languages, e.g. the manual allocation and deallocation of memory or the use of pointers. Originally, the Java platform was not intended for use in real-time systems. The Real-Time Specification for Java (RTSJ) [1], submitted in 1998 and approved in 2002 by the Java Community Process, defines how real-time behavior can be achieved within the Java programming language. An update proposal (JSR-282) improves the RTSJ and includes new enhancements. A further specification for safety-critical Java (JSR-302) is expected soon. It will guarantee that Java-based applications can be certified under the safety-critical development standard in aviation DO-178B level A [11] and other safety critical standards for software.

A project called Java environment for parallel real-time development (JEOP-ARD) [14] exemplifies the large interest in real-time Java for multicore systems. The consortium of this European Commission funded project, consisting of ten academic and industrial partners, aims at the development of an independent software interface for Java real-time multiprocessor systems. This project uses the proposed processor architecture for the CMP platform evaluation.

The advantages of Java compared to low-level programming languages can be easily outlined from two points of view. From the manager's point of view, Java use shortens the system's time to market, because of the programmer's productivity increase. Additionally, Java developers are a dime a dozen compared to experts developing systems consisting of microprocessors running real-time operating systems. That combination requires great expertise in low-level embedded system programming. From the developer's point of view, Java is considered a simple and easy-to-use programming language compared to C or C++. A large advantage is the automatic memory allocation and garbage collection, which often introduces failures in C-type programs. Large applications are much easier to develop, maintain, and debug. Furthermore, its object-oriented programming model favors reusability.

The Java optimized processor (JOP) [12, 13] is an implementation of the Java Virtual Machine (JVM) in hardware. JOP translates Java bytecodes

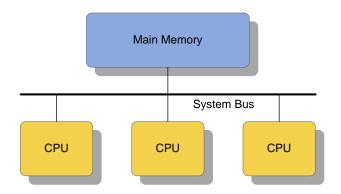

Figure 1.2: Shared memory multiprocessor.

into its own instruction set called microcode. These microcode instructions, implemented in hardware, are executed by the stack architecture. This processor has been designed from scratch to provide a time-predictable execution environment for embedded real-time systems.

#### 1.2 Problem Definition and Objectives

According to [6], two tightly linked major multiprocessor system models exist, the *shared memory model* and the *distributed shared memory model*. The core of the *shared memory model* is a global physical memory accessible to all processors. Multiple CPUs are connected to the memory via a system bus. This architecture enables simple data communication by accessing shared data objects of the common memory. A multiprocessor based on this model is called a symmetric (shared-memory) multiprocessor (SMP), because all processors have symmetric access to the shared memory (see Figure 1.2). It offers uniform memory access times for all CPUs.

In contrast, the distributed shared memory model implements a physically distributed memory system. It consists of multiple independent processing nodes with local memory modules, which are connected by an interconnection network. Each CPU can access its own local memory very quickly, but the time it takes to access a memory word located at a distant processing node is much longer. Therefore, this model is called non-uniform memory access (NUMA) architecture and is less appropriate for use in a time-predictable CMP. This thesis investigates SMP architectures.

A fundamental problem in parallel SMP computing is the access of multiple CPUs to the shared memory. A memory arbiter is needed to resolve concurrent access. For use in a time-predictable system, the realization of this memory arbitration mechanism presents two closely related challenges:

- Synchronization of memory access

- Timing analysis of memory access

The arbiter controls the memory access of multiple CPUs to the shared memory. Naturally, if one CPU is accessing the memory, no other CPU can access it simultaneously. They are forced to wait until the currently accessing CPU has completed its memory transfer. In this case, a memory arbiter resolves access conflicts by serializing the read and write operations of the CPUs. The access order is determined by the implemented arbitration algorithm.

In uniprocessor systems, only one processor accesses the memory and the WCET of a memory access can be predicted if memory access latency is predetermined by the memory technology used. However, tasks running on a CMP on different CPUs influence each others' execution times when accessing a shared resource [15], e.g. a shared memory. Therefore, the interdependencies between task execution times have to be removed. A well designed arbitration algorithm is needed to limit the WCET of a task running on a CPU, even though tasks executing on other CPUs may also access the main memory. Consequently, an analysis of WCET bounds is possible.

The objectives of this thesis can be summarized as follows:

- Design and implementation of a homogeneous chip-multiprocessor with global shared memory

- based on Java technology

- with time-predictable execution times, if memory provides predictable latencies

- verified by a prototype implementation in field-programmable gate array (FPGA) technology

- Adaptation of a WCET analysis tool tailored to the CMP

- Comparison and evaluation of different CMP configurations with respect to

- real-time performance (WCET)

- average-case performance (average-case execution time ACET)

#### 1.3 Contributions

This thesis presents a novel Java chip-multiprocessor with a new WCET analysis method that actually makes possible a timing analysis for homogeneous multiprocessor systems with a shared memory. The above mentioned

challenges and objectives are addressed in this thesis. The major contributions are as follows:

#### • Time-Predictable Multiprocessor Design

The proposed Java chip-multiprocessor is designed for maximum time predictability, where simple and accurate WCET analysis is more important than good average-case performance. Additionally, tight WCET bounds have been a design goal. The CMP architecture is based on multiple time-predictable Java processors and a shared memory. The global physical memory, accessible to all processors, stores all instructions and data. A memory arbiter controls the memory access of multiple CPUs. Synchronization guarantees coordinated access to shared objects among several processors. All components are interconnected with a System-on-Chip (SoC) bus. This CMP operates without caching shared data objects, therefore an identical data perspective is ensured for all CPUs throughout the execution of an application. Consequently, hardware demanding cache coherence mechanisms can be avoided. The proposed multiprocessor is tailored to utilize the multi-threaded nature of real-time applications.

#### • Memory Arbitration

A memory arbiter is responsible for controlling the memory access of multiple CPUs to the shared memory. Naturally, if one CPU is accessing the memory, other CPUs must not do so at the same time. They are forced to wait until the currently accessing CPU has completed its memory transfer. In this case, a memory arbiter resolves access conflicts by serializing the read and write operations of different CPUs.

In multiprocessor systems, tasks are running on different CPUs and influence each others' execution times when accessing a shared memory. Therefore, an arbitration algorithm is necessary, which is able to limit the WCET of a task running on a CPU, even though tasks executing on other CPUs may also access the main memory. A time-sliced arbiter that divides the memory bandwidth among the CPUs avoids interferences between task execution times. Consequently, an analysis of tight WCETs is rendered possible.

#### • Prototype Implementation

A prototype implementation enables CMP architecture validation. Two different hardware platforms have been used for evaluation purposes. They use two different FPGA technologies and have different memory bandwidth capacities. An integration of up to 8 cores could be verified using several different benchmarks.

One of this paper's major contributions is the implementation of three different arbitration policies: a fixed priority, a fair-based, and a time-sliced arbiter. They provide a basis for the comparison of arbitration policies with respect to WCET and average-case performance. Furthermore, several system components had to be designed and implemented, e.g. a synchronization process, and a CMP boot-up sequence.

#### • Static WCET Analysis

Static WCET analysis finds the worst-case execution time of a given program code for a specific processor model. Overestimation should be kept to a minimum. In a CMP system, tasks running on different CPUs shall not influence each others' execution times when accessing the shared memory. The WCET analysis is primarily dependent on the memory arbiter. In this paper, a static timing analysis approach of each arbitration policy is presented. Some of them turn out not to be viable for hard real-time systems because of their unacceptable WCET results. Only timing analysis using a time-sliced arbiter leads to realistic and viable WCET bounds.

One contribution of this thesis is the enhancement of JOP's WCET analysis tool for use with multiprocessor systems. The tool can be configured for analysis of different hardware platforms and system configurations.

#### • Performance Comparison

An implementation of a soft multiprocessor core in an FPGA holds several advantages: ease of rapid prototyping, high configuration and simple verification potential of particular components. Different CMP configurations are evaluated by varying the number of processors, their instruction cache sizes, the memory bandwidth, and arbitration policies. In our experiments, their average-case performance is compared by running different benchmarks on real hardware. Furthermore, CMP versions are compared to a complex Java processor.

#### 1.4 Thesis Outline

The next four chapters of the thesis present the published results of peerreviewed papers presented at international conferences. These papers appear as individual chapters. Each paper consists of an abstract, an introduction, a related work section, and the main research findings. Each article was written as an individual publication, therefore, a few statements may appear repetitive.

#### Time Predictable CPU and DMA Shared Memory Access

Christof Pitter and Martin Schoeberl. Proceedings of the International Conference on Field Programmable Logic and Applications (FPL 2007). Amsterdam, Netherlands, August 2007, pages 317-322.

Chapter 2 describes the starting point of my research. This paper evaluates two different timing analysis approaches of a system consisting of one CPU and a direct memory access (DMA) controller. The first implementation of a fixed priority arbiter is responsible for controlling the memory access of both processing units. The DMA controller can be modeled to appear as a hardware-based real-time task which accesses the memory with a regular pattern. Therefore, its WCET is known and the task can be easily integrated into the schedulability analysis. A novel WCET approach describes how each memory access (an occurring read or write access) of the DMA task can be included into the WCET of the application task. Consequently, the application task's WCET increases, but the DMA task can be omitted from the schedulability analysis. Experiments showed that this new approach leads to tighter response times and saves more processing resources for the CPU. In summary, this paper shows that it is possible to analyze the timing behavior of a system consisting of a CPU and a hardware task with a known access pattern both accessing a shared memory.

#### Towards a Java Multiprocessor

Christof Pitter and Martin Schoeberl. Proceedings of the 5th International Workshop on Java Technologies for Real-Time and Embedded Systems (JTRES 2007). Vienna, Austria, 2007, pages 144-151.

Chapter 3 introduces a novel Java multiprocessor architecture for embedded systems. This paper explains why a shared memory model is preferred to a distributed shared memory model for time-predictable multiprocessors. The proposed CMP design consists of a number of Java optimized processor (JOP) cores. Based on the work described in Chapter 2, several improvements on the fixed priority arbiter ensure a solution for simultaneous access of multiple CPUs to the shared main memory. Furthermore, the synchronization of shared data objects is examined. Another interesting aspect of a CMP system, the startup or boot-up, is described in detail. The first FPGA prototype using multiple JOP cores verifies the correct concurrent execution of application tasks. Finally, CMP versions made up of two/three JOPs enable a performance comparison between a single JOP and the CMP versions by running real applications on hardware. The resulting speed-ups encouraged further investigation into the proposed CMP architecture.

#### Performance Evaluation of a Java Chip-Multiprocessor

Christof Pitter and Martin Schoeberl. Proceedings of the International Symposium on Industrial Embedded Systems (SIES 2008). Montpellier, France, June 2008, pages 34-42.

Chapter 4 evaluates the Java CMP system with respect to average-case performance. Different hardware configurations with varying instruction cache sizes, number of processors, and memory bandwidth are compared. An implementation of a fair-based arbiter guarantees fair memory access among the CPUs. Experiments measure the performance by running three benchmarks on two different FPGA platforms: an embedded industry application, a computationally intensive matrix multiplication, and a synthetic benchmark that continuously accesses a shared data structure. Compared to Chapter 3, one of the prototype boards allows for an integration of up to eight CPUs. Performance results show that a multiprocessor version of a simpler and smaller architecture is more efficient (performance/die area) for parallel workloads than a complex Java processor.

#### Time-Predictable Memory Arbitration for a Java Chip-Multiprocessor

Christof Pitter. Proceedings of the 6th International Workshop on Java Technologies for Real-Time and Embedded Systems (JTRES 2008). Santa Clara, California, 2008, pages 115-122.

Based on the findings of Chapter 2 and 3, this paper proposes a real-time CMP system that allows WCET analysis of tasks running on a homogeneous Java CMP. The core of this CMP is a time-sliced arbiter that divides the memory access bandwidth into equal time slots, one for each CPU. Consequently, WCETs of Java bytecodes can be analyzed depending on the size of the time slot, number of CPUs in the system and memory access time. An adapted WCET analysis tool for use with a CMP system can utilize these results and generates temporal upper bounds for application tasks. A real-world application task is used to compare analyzed results with measured execution times.

#### Further Analysis and Evaluation

Chapter 6 is based on a submitted paper called A Real-Time Java Chip-Multiprocessor. This chapter is dedicated to compare and evaluate CMPs using implemented arbitration policies (fixed priority, fair-based, and a time-sliced policy) with respect to their real-time and average-case performance.

Various CMP configurations are evaluated using a larger application base than described in previously presented chapters.

#### Conclusion and Outlook

Chapter 7 concludes this thesis by giving a systematic summary of the research process. It recapitulates the main findings of the conducted experiments. Additionally, it provides some further ideas for future research.

#### Bibliography

- [1] Greg Bollella, James Gosling, Benjamin Brosgol, Peter Dibble, Steve Furr, and Mark Turnbull. *The Real-Time Specification for Java*. Java Series. Addison-Wesley, June 2000.

- [2] Alan Burns and Andrew J. Wellings. Real-time systems and programming languages: Ada 95, real-time Java, and real-time POSIX. International computer science series. Addison-Wesley, third edition, 2001. Revised edition of Real-time systems and their programming languages, 1990.

- [3] Axel Deicke. The electrical/electronic diagnostic concept of the new 7 series. In *Proceedings of Convergence International Congress & Exposition On Transportation Electronics*, Detroit, USA, October 2002.

- [4] Andreas Ermedahl and Jakob Engblom. Execution time analysis for embedded real-time systems. In Sang H. Son Insup Lee, Joseph Y-T. Leung, editor, *Handbook of Real-Time Embedded Systems*, pages 35.1 35.17. Chapman & Hall/CRC Taylor and Francis Group, August 2007.

- [5] James Gosling, Bill Joy, and Guy Steele. *The Java Language Specification*. The Java Series. Addison-Wesley, 1997.

- [6] John Hennessy and David Patterson. Computer Architecture: A Quantitative Approach, 4th ed. Morgan Kaufmann Publishers, 2006.

- [7] H. Kopetz. Real-time systems: design principles for distributed embedded applications. Kluwer Academic Publishers, 1997.

- [8] James Laudon and Lawrence Spracklen. The coming wave of multithreaded chip multiprocessors. *International Journal of Parallel Programming*, 35(3):299–330, June 2007.

- [9] Gordon E. Moore. Cramming more components onto integrated circuits. *Electronics*, 38(8):114–117, 1965.

- [10] Roman Obermaisser, Philipp Peti, and Fulvio Tagliabo. An integrated architecture for future car generations. *Real-Time Systems*, 36:101–133(33), July 2007.

- [11] RTCA. Software considerations in airborne systems and equipment certification. Guideline DO-178A, Radio Technical Commission for Aeronautics, One McPherson Square, 1425 K Street N.W., Suite 500, Washington DC 20005, USA, March 1985.

- [12] Martin Schoeberl. JOP: A Java Optimized Processor for Embedded Real-Time Systems. PhD thesis, Vienna University of Technology, 2005.

- [13] Martin Schoeberl. A Java processor architecture for embedded real-time systems. *Journal of Systems Architecture*, 54/1–2:265–286, 2008.

- [14] Fridtjof Siebert. Jeopard: Java environment for parallel real-time development. In *JTRES '08: Proceedings of the 6th international workshop on Java technologies for real-time and embedded systems*, pages 87–93, New York, NY, USA, 2008. ACM.

- [15] Lothar Thiele and Reinhard Wilhelm. Design for timing predictability. *Real-Time Systems*, 28(2-3):157–177, 2004.

- [16] James L. Turley. The Essential Guide to Semiconductors. Prentice Hall PTR, 2003.

- [17] Reinhard Wilhelm, Jakob Engblom, Andreas Ermedahl, Niklas Holsti, Stephan Thesing, David B. Whalley, Guillem Bernat, Christian Ferdinand, Reinhold Heckmann, Tulika Mitra, Frank Mueller, Isabelle Puaut, Peter P. Puschner, Jan Staschulat, and Per Stenström. The worst-case execution-time problem overview of methods and survey of tools. ACM Trans. Embedded Comput. Syst, 7(3):1–53, 2008.

- [18] Wayne Wolf. High-Performance Embedded Computing: Architectures, Applications, and Methodologies. Morgan Kaufmann Publishers Inc., San Francisco, CA, USA, 2006.

# 2

### Time Predictable CPU and DMA Shared Memory Access

#### Christof Pitter and Martin Schoeberl

Institute of Computer Engineering, Vienna University of Technology, Austria

Proceedings of the International Conference on Field Programmable Logic and Applications (FPL 2007). Amsterdam, Netherlands, August 2007, pages 317-322.

#### Abstract

In this paper, we propose a first step towards a time predictable computer architecture for single-chip multiprocessing (CMP). CMP is the actual trend in server and desktop systems. CMP is even considered for embedded real-time systems, where worst-case execution time (WCET) estimates are of primary importance. We attack the problem of WCET analysis for several processing units accessing a shared resource (the main memory) by support from the hardware. In this paper, we combine a time predictable Java processor and a direct memory access (DMA) unit with a regular access pattern (VGA controller). We analyze and evaluate different arbitration schemes with respect to schedulability analysis and WCET analysis. We also implement the various combinations in an FPGA. An FPGA is the ideal platform to verify

the different concepts and evaluate the results by running applications with industrial background in real hardware.

#### 2.1 Introduction

This paper presents a hard real-time system consisting of a hard real-time application running on a time predictable Java Optimized Processor (JOP) [10] and an additionally direct memory access (DMA) unit with a regular access pattern. This unit is represented by a video graphics array (VGA) controller. Both the CPU and the DMA unit share the main memory of the system. Meeting the deadlines of the tasks of the real-time application is of utmost importance. Therefore, the task set of the system requires a timing validation by schedulability analysis.

A real-time computer system has to produce logical correct results within a specified period of time. If a correct result of a computation is late, the result is considered useless. Such real-time systems (RTS) or safety-critical systems have to handle concurrent tasks, such as communication, calculating values for a control loop, user interface and supervision in embedded systems. A natural way to handle these concurrent jobs is to split them up into individual tasks. Every hard real-time system contains at least one so-called hard real-time task. A task is classified a hard real-time task when a missed deadline may cause a critical failure of the system. Non safety-critical tasks in such a system are soft real-time tasks. If a deadline is missed, the system will still produce correct results [4] but with degraded service.

Safety-critical systems must be predictable in the time domain. It is of utmost importance to be able to analyze the maximal time or WCET of the task. If and only if these upper bounds can be calculated, the schedulability analysis can be performed. They are necessary to test whether a task set can be scheduled on the target system or not [8].

There exist two possibilities for modeling and implementing the RTS consisting of the application running on the CPU and the DMA controller sharing the main memory:

- DMA as soft real-time task

- DMA as hard real-time task

In the first approach, the task of the DMA controller is represented as a soft real-time task. As a consequence, some interference (e.g. flickering on the VGA display) may occur when the deadline of the DMA is violated. Hence, the DMA task performs in a best-effort manner and can be excluded

from schedulability tests. Increasing the buffer size in the DMA controller can help to support a smooth communication between the shared memory and the DMA controller. Nevertheless, this kind of a system is of minor importance because hard RTSs are the target of this paper.

In the second attempt the DMA task as well as the hard real-time application running on the CPU has to meet its deadline. As a consequence, the system contains the application hard real-time tasks and the memory-streaming hard real-time task that are executed simultaneously. Although a VGA display is usually not accounted as a hard real-time task, it serves as a good example demanding a constant amount of data within a known period of time. In the future, the VGA will be replaced by another CPU.

The rest of the paper considers the second approach (hard RTS) and is structured as follows. Section 2.2 presents the related work. In Section 2.3, we explain the two basic options of analyzing the behavior of the RTS and describe how schedulability tests are carried out. Section 2.4 describes the JopVga system and the worst-case analysis results of several experiments. At the end, it discusses the acquired outcome of the paper. Finally, Section 2.5 concludes the paper and gives guidelines for future work.

#### 2.2 Related Work

In [2] Atanassov and Puschner describe the impact of dynamic RAM refresh on the execution time of real-time tasks. The use of DRAM memory in RTSs involves a major drawback because these memory cells have to be periodically refreshed. During the refresh, no memory request can be processed. As a consequence, the request is delayed and the execution time of the task increases.

Many researchers in the real-time community have turned their attention to timing-analysis tools described by Puschner and Burns [8]. The problem is that the available results for uniprocessors are not applicable to modern processor architectures [8, 12]. Multiprocessor systems consisting of shared memories and busses are hard to predict. In addition, the WCET of each individual task depends on the global system schedule.

Even though so much research has been done on multiprocessors, the timing analysis of the systems has been neglected. An example represents the scalable, homogeneous multiprocessor system by Gaisler Research AB. It consists of a centralized shared memory and up to four LEON processor cores that are based on the SPARC V8 architecture [5]. This embedded system is made available as a synthesizable VHDL model and therefore is well suited for SoC designs. LEON is introduced for European space projects as well as for military and demanding consumer applications. Nevertheless, no

literature concerning WCET analysis regarding the multiprocessor has been found.

Another example depicts the ARM11 MPCore [1]. It introduces a preintegrated symmetric multiprocessor consisting of up to four ARM11 microarchitecture processors. The 8-stage pipeline architecture, independent data and instruction caches and a memory management unit for the shared memory make a timing analysis difficult.

We believe that the impact of WCET of real-time tasks sharing a main memory has not received enough coverage in literature yet. This paper is a first step towards a time-predictable multiprocessor. Providing WCET guarantees and reliable schedules for a multiprocessor system becomes a great challenge.

#### 2.3 CPU/DMA shared memory access

In Section 2.1, we presented two possibilities of integrating the DMA task into the system. Either the DMA controller represents a soft real-time task or it is considered a hard real-time task. This paper addresses the second solution.

#### 2.3.1 Implementation of the DMA hardware controller

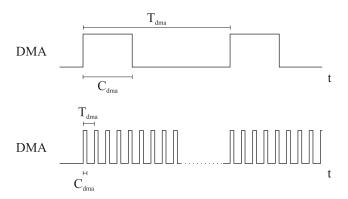

The DMA controller accesses the shared memory to read or write data autonomously of the CPU. The volume of the data transfer depends on the I/O-device. Therefore, the application of the device defines the quantity of memory requests within a fixed period of time. Two different options are evaluated to implement the memory access scheme of the DMA controller (see Figure 2.1):

- 1. The DMA controller accesses the shared memory in a blocked scheme. This approach is used for a fast copy of large blocks of the main memory to another device. Assume this task has the smallest period of all tasks within the system. Hence using fixed-priority scheduling [7] it has the highest priority. After the DMA task is completed, the other tasks of the CPU get permission to access the shared memory depending on their priority. This approach is a good representation of a multimedia task, such as streaming data, performed via DMA.

- 2. The DMA controller accesses the memory in a timely spread scheme denotes the other extreme. It generates a smaller period because all memory requests are timely spread on the original period. The highest

Figure 2.1: The blocked and the spread memory access scheme of the DMA task.

priority of this task is required. If this task does not hold the highest priority, the system will not function correctly because the DMA task will starve when the CPU's software tasks make extensive memory requests.

#### 2.3.2 Task vs. WCET based Analysis

There exist two possibilities to analyze the timing behavior of the RTS:

- DMA access represents an additional real-time task

- DMA access is included in the WCET analysis of each individual application task

The first method considers the DMA task in the schedulability analysis. Hence, all the tasks of the application running on the CPU and the DMA task have to be considered. This simple task set consists of independent periodic tasks with fixed priority. The DMA controller must have the highest priority. The resulting task set can be used for schedulability tests to analyze the timing behavior of the application running on the CPU.

The second approach models the RTS in a different way. The DMA controller and the CPU are accessing shared memory. We are interested in the WCET of the application in spite of the memory communication of the DMA. Therefore, the blocking delay, caused by each possible read or write access of the DMA controller, has to be added to the WCET estimations of the real-time tasks running on the CPU. The results serve bounded WCET estimates of each individual task. As a consequence, the WCET values for the tasks increase, but the DMA task can be omitted from the schedulability analysis.

#### 2.3.3 Schedulability Analysis

The major goal of this paper is the analysis of the timing behavior of the RTS depending on the different options of the memory access of the DMA controller.

Assume that the CPU of the system runs several real-time tasks that are accessing the shared memory. Additionally the DMA controller requests data of the main memory with a regular access pattern. Therefore, the system consists of the DMA task and the tasks of the real-time application running on the CPU. Using fixed-priority scheduling [7], the priorities of the tasks are ordered rate monotonic. The smaller the period the higher is the priority of the task. In order to ensure that all tasks can be completed within their deadlines schedulability tests are carried out.

#### Utilization-based schedulability test

In [7] it has been shown that a simple schedulability test can be carried out by taking the utilization of the several tasks into account. The utilization is the result of dividing the computation time by the period of the task. If Equation 2.1 holds then all tasks will meet their deadlines. Otherwise, the task set may or may not fail at run-time.  $C_i$  denotes the computation time of the task  $\tau_i$ ,  $T_i$  is the period of task  $\tau_i$  and N stands for the number of the tasks to schedule.

$$\sum_{i=1}^{N} (C_i/T_i) \le N(2^{1/N} - 1) \tag{2.1}$$

If the task set fails, the utilization-based schedulability test cannot guarantee that all tasks will meet their deadlines. Nevertheless, the task set may not fail at run-time.

#### Response time analysis

A more exact schedulability test by Joseph and Pandya is presented in [6]. The result of this response time analysis for a set of independent tasks provides a necessary and sufficient condition. If the result is positive the task set will be schedulable at run-time. The task set will not be schedulable if the test fails. The worst-case response time  $R_i$  of each individual task is calculated and then compared with the task's deadline or period respectively. The equation for the response time is:

$$R_i = C_i + \sum_{j \in hp(i)} \lceil R_i / T_j \rceil \cdot C_j \tag{2.2}$$

The expression hp(i) denotes all tasks with a higher priority than the task  $\tau_i$ . The smallest  $R_i$  that solves Equation 2.2 is the worst-case response time of  $\tau_i$ . A recurrence relationship can be formed that allows the calculation of the response time [3]:

$$w_i^{n+1} = C_i + \sum_{j \in hp(i)} \lceil w_i^n / T_j \rceil \cdot C_j$$

(2.3)

The solution is found when  $w_i^{n+1} = w_i^n$ . Then  $w_i^n$  represents  $R_i$ . If one task i has a larger response time than its deadline (or period  $T_i$ ) the task set cannot be scheduled.

#### 2.4 Evaluation

This section provides an overview of the JopVga system and the corresponding sample application. Furthermore the timing behavior of the RTS is analyzed. The results of the experiments and calculations are compared and classified.

#### 2.4.1 JopVga System

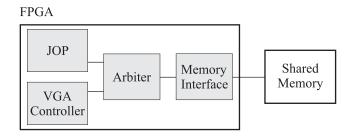

The JopVga system is the hardware used for our experiments. It consists of a time-predictable processor called JOP [10], a VGA controller, an arbiter, a memory interface and an SRAM memory. JOP, the VGA controller, the memory arbiter and the memory interface are implemented on an Altera Cyclone FPGA. As illustrated in Figure 2.2 the external memory is connected to the memory interface. This 1 MByte 32 Bit external SRAM device represents the shared memory of the JopVga system. A SoC bus, called SimpCon [11], connects JOP and the VGA controller with the arbiter. The arbiter is connected via SimpCon to the memory interface.

The arbiter is responsible for setting up the communication between the shared memory and the VGA controller and JOP respectively. It schedules the memory communication of both masters. The shared main memory of the system is divided into two segments: 640 KByte are dedicated to JOP and the remaining 384 KByte are used as frame buffer.

Both JOP and the VGA controller run at a clock frequency of 80 MHz, resulting in a period of 12.5 ns. The SRAM-based shared memory has an access time of 15 ns per 32 bit word. Hence every memory access needs at least 2 cycles. At the moment the arbiter as well as the VGA controller is not capable of using the pipelining approach of the memory access that is introduced by the SimpCon interface [11]. Each memory request of JOP

Figure 2.2: JopVga system.

takes 4 cycles and every VGA request takes 3 cycles. The bandwidth of the memory  $(BW_{mem})$  calculates to:

$$BW_{mem} = 4Byte/25ns = 160MByte/s (2.4)$$

The VGA controller uses a VGA resolution of  $1024 \cdot 768$  pixels with each pixel consisting of 4 bits. As a consequence the memory used for the VGA display results in 384 KByte ( $1024 \cdot 768 \cdot 0.5$  Byte). The horizontal frequency is 60 kHz, which results in a horizontal period of about 17  $\mu$ s per line and 17 ns per pixel. The vertical frequency is 75 Hz. Therefore the bandwidth used by the VGA calculates to:

$$BW_{vag} = (128 \cdot 4Byte)/17ns = 30.12MByte/s$$

(2.5)

Dividing  $BW_{vga}$  by  $BW_{mem}$  results in 18.83% of the memory bandwidth for the VGA controller. JOP has a bandwidth of 80 MByte/s which results in 50% of the memory bandwidth available.

#### **Application**

In order to estimate the worst-case execution time of a RTS all real-time tasks have to be taken into account. In the following the task set illustrated in Table 2.1 represents the periods and the computation times of the system under test. It consists of the VGA task  $\tau_{vga}$  and two tasks running on JOP  $\tau_{lift}$  and  $\tau_{kfl}$ . The priority of 3 depicts the highest prior task. This simple task set illustrates an RTS that is further analyzed using schedulability tests. The VGA task can be modeled as a periodic task with the highest priority and a fixed runtime. The computation time  $C_{vga}$  is calculated by multiplying 128 memory accesses times 3 cycles. Using a clock frequency of 80 MHz results in 4.8  $\mu$ s.  $T_{vga}$  is predetermined by the horizontal period of 17  $\mu$ s.

Two real-world examples with industrial background represent the two tasks running on JOP. Lift is a lift controller used in an automation factory. Kfl is one node of a distributed RTS to tilt the line over a train for easier loading

| Table 2.1: Task set. |             |             |          |  |  |

|----------------------|-------------|-------------|----------|--|--|

| au                   | $T (\mu s)$ | $C (\mu s)$ | Priority |  |  |

| $\tau_{vga}$         | 17          | 4.8         | 3        |  |  |

| $	au_{lift}$         | 500         | 162.7       | 2        |  |  |

| $	au_{kfl}$          | 3000        | 782.2       | 1        |  |  |

and unloading of goods wagon. Both applications consist of a main loop that is executed periodically. In our experiments we use both applications to represent two independent real-time tasks. The WCET of these two tasks are inferred from the WCET analysis tool [12]. In the second column of Table 2.2 the WCET estimates of the two tasks are given in clock cycles. Multiplying those estimates with the clock period result in  $\tau_{lift} = 162.7~\mu s$  and  $\tau_{kfl} = 782.2~\mu s$ .

#### 2.4.2 Analysis using the Task Approach

In this section the VGA controller represents another real-time task of the system that is taken into account in the analysis of the timing behavior. Both the blocked memory access scheme and the spread memory access scheme, as described in Section 2.3.1, are evaluated.

#### Blocked

Using the values of Table 2.1 the utilization of each individual task is calculated dividing the computation time  $C_i$  by the corresponding period  $T_i$  resulting in  $U_{vga} = 28.24\%$ ,  $U_{lift} = 32.54\%$  and  $U_{kfl} = 26.07\%$ . Applying the utilizations to Equation 2.1 results in an overall utilization of 86.85%. The overall utilization may not be more than  $3(2^{1/3} - 1) = 78.00\%$  because three tasks are involved. The condition does not hold and consequently this task set fails the utilization-based schedulability test. It cannot be guaranteed that all tasks meet their deadlines. Therefore, a response time analysis is carried out next.

The response time  $R_{vga}$  is the same as the computation time because this task has the highest priority.

$$R_{vga} = C_{vga} = 4.8\mu s \tag{2.6}$$

The response time of the next lower prior task  $\tau_{lift}$ , denoted as  $R_{lift}$ , is the addition of the computation time  $C_{lift}$  and the time of interference of all higher prior tasks (in that case the interference of  $\tau_{vga}$ ).

$$w_{lift}^{n+1} = C_{lift} + \lceil w_{lift}^n / T_{vga} \rceil \cdot C_{vga}$$

(2.7)

The response time is calculated using the values from Table 2.1. The response time of  $R_{lift}$  is found when  $w_{lift}^{n+1}$  equals to  $w_{lift}^{n}$ . It is 229.9  $\mu s$  which is less than  $T_{lift}$ . Finally,  $R_{kfl}$  has to be calculated.  $R_{kfl}$  is the addition of the computation time  $C_{kfl}$  and the time of interference of the two higher priority tasks  $\tau_{vga}$  and  $\tau_{lift}$ . The result of  $R_{kfl}$  is 1999.4  $\mu s$ . All the response times are smaller than their appropriate periods and hence the response time analysis has a positive outcome. This response time calculation ensures that the tasks will meet their deadlines because the successful analysis is sufficient and necessary [4] even though the utilization-based schedulability test could not be passed.

#### Spread

The VGA task accesses the memory in a timely spread scheme. The new values for the period and the computation time of  $\tau_{vga}$  are calculated by dividing the original period  $T_{vga}=17\mu s$  of Table 2.1 by the cycle time of 12.5ns. It results in 1360 cycles. We need 128 memory requests for each line on the VGA. Hence  $T_{vga}=10$  cycles and  $C_{vga}=3$  cycles. The remaining 80 cycles are not used. Hence the values for the VGA task change to  $T_{vga}=125$  ns and  $C_{vga}=37.5$  ns.

Using these values for JOP's tasks and the values for  $\tau_{lift}$  and  $\tau_{kfl}$  the utilization-based schedulability test logically results in a similar overall utilization of 88.61% as described in the previous section. A small divergence between the results can be explained by the remaining 80 cycles that are not used in this memory access scheme. Again, the utilization test is negative.

Therefore, the response time analysis is used.  $R_{vga}$  is equal to  $C_{vga} = 37.5$  ns.  $R_{lift}$  calculates to 232.5  $\mu$ s and  $R_{kfl} = 2279.6$   $\mu$ s. The positive result of the response time analysis shows that the task set can be scheduled. As in the utilization-based test, the remaining 80 cycles affect the results of  $R_{lift}$  and  $R_{kfl}$ . Both response times are larger than in the blocked memory access scheme. As a consequence, the spread memory access scheme is worse than the blocked scheme.

#### 2.4.3 Analysis using the WCET method

The second approach to include the DMA unit in the schedulability analysis is to model the DMA access in the WCET values for memory access of the software tasks. Each instruction that accesses memory has to include the maximum delay due to a possible memory access by the DMA unit.

Table 2.2: WCET estimates given in clock cycles.

| App  | JOP only | JOP with VGA | Increase |

|------|----------|--------------|----------|

| Kfl  | 62573    | 83131        | 33%      |

| Lift | 13016    | 16118        | 24%      |

Table 2.3: Task set for the WCET method.

| au           | $T (\mu s)$ | $C (\mu s)$ | Priority |

|--------------|-------------|-------------|----------|

| $	au_{lift}$ | 500         | 201.5       | 2        |

| $	au_{kfl}$  | 3000        | 1039.1      | 1        |

#### Blocked

Using the blocked memory access scheme and the WCET method for analysis is not a reasonable approach. One would have to account the delay of the whole block of memory requests of the VGA to each memory access of JOP. That results in a very conservative WCET for each memory access of JOP. Hence, it is not further investigated.

#### **Spread**

The WCET analysis tool [12] can be parameterized with respect to the memory access time (the wait states for memory read, memory write, and the cache load). The memory access from the VGA unit takes 2 cycles plus 1 cycle in the arbiter to switch between the two masters. Therefore, we add 3 cycles to the wait states.

Table 2.2 shows the WCET values in clock cycles for different applications for the stand-alone processor and when adding the DMA device. We see an increase of 24% to 33% of the WCET for the tasks.

These values are conservative as each memory access is modeled with the maximum blocking time. For a single memory access (such as bytecode getfield) this is the best we can do without further analysis of the instruction pattern. However, for cache loading we could include the access pattern (in our example one access per 10 clock cycles) into the analysis of the cache load time. Previously experiments showed that the load time for the method cache produces most of the memory requests. Consequently, with inclusion of the access pattern into the WCET analyzer tool, we can provide tighter WCET values. This is a new approach to WCET analysis, as in all current approaches the WCET analysis is independent from the schedulability analysis. Schedulability analysis is usually the next step and assumes known WCET values.

Table 2.4: Comparison of the response times of the task approach with blocked DMA ( $C_1$  and  $R_1$ ) and the WCET method with spread DMA access ( $C_2$  and  $R_2$ ).

| au           | T $(\mu s)$ | $C_1 (\mu s)$ | $R_1 \; (\mu \mathrm{s})$ | $C_2 \; (\mu \mathrm{s})$ | $R_2 (\mu s)$ |

|--------------|-------------|---------------|---------------------------|---------------------------|---------------|

| $	au_{vga}$  | 17          | 4.8           | 4.8                       | _                         | _             |

| $	au_{lift}$ | 500         | 162.7         | 229.9                     | 201.5                     | 201.5         |

| $	au_{kfl}$  | 3000        | 782.2         | 1999.4                    | 1039.1                    | 1845.1        |

The computation time values of Table 2.3 are calculated by multiplying the WCET estimates of  $\tau_{lift}$  and  $\tau_{kfl}$  from Table 2.2 with the clock period of 12.5 ns. The values for those two tasks are the basis for the schedulability test. The utilization-based test results in 74.94%. Only two tasks are taken into account and hence this result is less than  $2(2^{1/2} - 1) = 82.84\%$ . Even though this test is positive, we also investigate the response time analysis.

The response time analysis for the WCET estimates of the system with the VGA results in tighter response times than in the analysis using the task approach of Section 2.4.2.  $R_{lift}$  is the same as  $C_{lift} = 201.5 \ \mu s$  and  $R_{kfl}$  calculates to 1845.1  $\mu s$ .

#### 2.4.4 Discussion

Table 2.4 shows the results of the evaluation for both analyses: column 3 and 4 ( $C_1$  and  $R_1$ ) for the DMA task approach (showing the better solution with blocked DMA mode) and column 5 and 6 ( $C_2$  and  $R_2$ ) for the DMA-WCET approach. We can see that both  $\tau_{lift}$  and  $\tau_{kfl}$  have a higher WCET ( $C_2$ ) in the DMA-WCET approach. As we do not have to include the VGA task in the response time analysis, the response time  $R_2$  is less for both tasks despite the fact that  $C_2$  is higher.

The result shows that the inclusion of the DMA access into the WCET analysis provides tighter worst-case response times than considering the DMA as an additional task. The difference can be explained as follows: most instructions on JOP do not access the main memory; they use the internal stack cache for data. The pipeline is filled from the instruction cache most of the time. In the task approach, all instructions are *blocked* by the VGA task. The WCET analysis is more exact as it delays only those instructions, which do actually access the main memory and the cache load events.

To validate our calculations and measurements we run all mentioned task sets on real hardware and the JopVga system respectively. No deadline violation of any task could ever be observed when performing these experiments.

Table 2.5: Comparison of the system performances in iterations/s.

| App  | JOP only | blocked VGA | spread VGA |

|------|----------|-------------|------------|

| Kfl  | 12163    | 11562       | 11628      |

| Lift | 9643     | 9194        | 9356       |

#### 2.4.5 Benchmarks

Although the solution is aimed at RTSs, i.e. a time predictable system, the average case performance is still interesting. The system under test is the JopVga system. The FPGA platform enables us to compare the performance of the system with an enabled VGA controller versus one with a disabled VGA controller. The results are achieved by running real applications in real hardware. For our measurements, we use the embedded Java benchmark suite JavaBenchEmbedded as described in [9]. The result is iterations per second, which means a higher value illustrates a better performance. In Table 2.5, the benchmark results are shown.

The Kf1 application is slowed down just by 4.4% due to the memory contention with the spread VGA memory access scheme. The WCET estimates of the same task resulted in an increase of up to 33% (see Table 2.2). Another benchmark called Lift experiences an even smaller slowdown of 3.0% due to the contention with the VGA task. The WCET estimates of the same task resulted in an increase of 24%.

To recapitulate, although we use about one third of the memory bandwidth for the DMA unit both applications suffer less than that one third in their execution time. This result is a promising indication that the memory system is not the bottleneck of the single CPU with the VGA. There is enough headroom for further devices. The result is promising for our further plans on a CMP version with several JOPs sharing a single memory.

#### 2.5 Conclusion and Future Work

In this paper, we have analyzed a system with a processor and a DMA unit with respect to WCET and schedulability. We have found two ways to model the influence of the DMA unit to the application tasks: 1.) the DMA access as an additional real-time task and 2.) include the DMA memory access in the WCET analysis of the individual application tasks. We found that the second approach results in a tighter estimation and enables more processing resources for the application.

We will investigate the possibility to include a known memory access pattern

into the WCET analysis of the cache loading to find tighter WCET estimates. On a cache load, we can guarantee that only a maximum number of memory loads can conflict with the DMA unit. The next step is the application of our findings to a system with several CPUs – the CMP JOP system. In that case, the memory access pattern is less predictable. Therefore, the shared resource can only be modeled by the WCET approach.

# Bibliography

- [1] ARM. ARM11 MPCore Processor, technical reference manual. Available at: http://www.arm.com, August 2006.

- [2] Pavel Atanassov and Peter Puschner. Impact of dram refresh on the execution time of real-time tasks. In *Proc. IEEE International Workshop on Application of Reliable Computing and Communication*, pages 29–34, Dec. 2001.

- [3] Neil C. Audsley, Alan Burns, Robert I. Davis, Ken Tindell, and Andy J. Wellings. Fixed priority pre-emptive scheduling: An historical perspective. *Real-Time Systems*, 8(2-3):173–198, 1995.

- [4] Alan Burns and Andrew J. Wellings. Real-time systems and programming languages: Ada 95, real-time Java, and real-time POSIX. International computer science series. Addison-Wesley, third edition, 2001. Revised edition of Real-time systems and their programming languages, 1990.

- [5] SPARC International Inc. *The SPARC Architecture Manual: Version 8.* Prentice Hall, Englewood Cliffs, New Jersey 07632, 1992.

- [6] Mathai Joseph and Paritosh K. Pandya. Finding response times in a real-time system. *Comput. J*, 29(5):390–395, 1986.

- [7] C. L. Liu and James W. Layland. Scheduling algorithms for multiprogramming in a hard-real-time environment. *J. ACM*, 20(1):46–61, 1973.

- [8] Peter Puschner and Alan Burns. A review of worst-case execution-time analysis. *Journal of Real-Time Systems*, 18(2/3):115-128, May 2000.

- [9] Martin Schoeberl. Evaluation of a Java processor. In *Tagungsband Austrochip* 2005, pages 127–134, Vienna, Austria, October 2005.

- [10] Martin Schoeberl. JOP: A Java Optimized Processor for Embedded Real-Time Systems. PhD thesis, Vienna University of Technology, 2005.

- [11] Martin Schoeberl. SimpCon a simple and efficient SoC interconnect. Available at: http://www.opencores.org/, 2007.

- [12] Martin Schoeberl and Rasmus Pedersen. WCET analysis for a Java processor. In JTRES '06: Proceedings of the 4th international workshop on Java technologies for real-time and embedded systems, pages 202–211, New York, NY, USA, 2006. ACM Press.

# 3

# Towards a Java Multiprocessor

#### Christof Pitter and Martin Schoeberl

Institute of Computer Engineering, Vienna University of Technology, Austria