The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

FAKULTÄT FÜR !NFORMATIK

**Faculty of Informatics**

# Minimal Preconditions for Timing Anomalies in WCET Calculations

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

# **Diplom-Ingenieur**

im Rahmen des Studiums

# Technische Informatik

eingereicht von

# **Christoph Martinek**

Matrikelnummer 0425174

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung Betreuer: Ao.Univ.-Prof. Dipl.-Ing. Dr. tech. Peter Puschner

Wien, 20.04.2011

(Unterschrift Verfasser/in)

(Unterschrift Betreuer)

Christoph Martinek, Leobendorferstrasse 69/3, 2105 Unterrohrbach

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 20.04.2011,

#### Abstract

In real-time systems it has an important relevance to analyse the worst-case-executiontime (WCET). With the knowledge of the maximum execution time it is possible to predict the behaviour of time-critical systems. To get a detailed analysis of the timing behaviour, it is necessary to know about the control flow of a program in modern real-time systems, in which different cache- and pipeline-architectures are used. So called timing anomalies could get analysed with the information of the control flow and the instructions. Along with this, necessary conditions for their appearance could be determined. If timing anomalies occur, the attribute proportionality in timing behaviour is violated during an execution.

In this thesis the most important timing anomalies are characterized and techniques to calculate the WCET are presented. There are series timing anomalies, which appear on a number of different paths along an execution, and parallel timing anomalies, where the timingrelevant dynamic computer state (TRDCS) is partitioned into different hardware components.

It is necessary for a strong analysis to investigate timing anomalies in cache- and pipelinearchitectures. Timing anomalies combined with the cache replacement strategies FIFO, pseudo round robin and pseudo LRU are observed. Also pipeline-architectures like simple scalar-, scalar-, superscalar in-order and superscalar out-of-order-pipelines in association with timing anomalies are explored. For timing anomalies, which occur in these architectures, preconditions are elaborated. To classify a specific processor with a potential timing anomaly a checklist is created.

#### Kurzfassung

Bei Echtzeitsystemen ist die Analyse der Worst-Case-Execution-Time (WCET) von entscheidender Bedeutung. Die Kenntnis über diese maximale Ausführungszeit führt zu einer notwendigen Vorhersage des Zeitverhaltens bei zeitkritischen Systemen. Um eine detaillierte Untersuchung des Zeitverhaltens eines Programms durchzuführen, ist in modernen Echtzeitsystemen, in denen unterschiedliche Cache- und Pipeline-Architekturen vorkommen, das Wissen über den Verlauf einer Ausführung von Wichtigkeit. Mit diesen Informationen können Besonderheiten, nämlich sogenannte Zeitanomalien, analysiert und notwendige Bedingungen dafür hergeleitet werden. Beim Auftreten von Zeitanomalien wird im Verlauf einer Ausführung die Eigenschaft Proportionalität im zeitlichen Verhalten verletzt.

In dieser Diplomarbeit werden die wichtigsten Zeitanomalien charakterisiert und Methoden vorgestellt, mit denen sich gewisse Anomalien bezüglich der Berechnung der WCET berechnen lassen. Darunter fallen serielle Zeitanomalien, welche über eine Anzahl von unterschiedlichen Pfaden auftreten können, und parallele Anomalien, bei denen der timingrelevant dynamic computer state (TRDCS) in unterschiedliche Hardwarekomponenten aufgeteilt wird.

Für eine aussagekräftige Analyse ist eine genaue Erforschung von Zeitanomalien in verschiedenen Cache- sowie in Pipeline-Architekturen erforderlich. Es werden hier die Cache-Ersetzungsstrategien FIFO, Pseudo Round Robin und Pseudo LRU genauer betrachtet. Bei Pipeline-Architekturen werden Simple Scalar-, Scalar-, Superscalar In-Order und Superscalar Out-of-Order-Pipelines untersucht. Es werden Vorbedingungen für Zeitanomalien ausgearbeitet, die in diesen Architekturen auftreten können. Darüber hinaus wird gewissermaßen eine Checkliste erarbeitet, mit der Prozessoren betreffend der eintretenden Zeitanomalien eingestuft werden können.

# Contents

| Ab | ostrac             | t                                                    | i  |  |  |  |  |

|----|--------------------|------------------------------------------------------|----|--|--|--|--|

| Ku | Kurzfassung        |                                                      |    |  |  |  |  |

| Co | Contents           |                                                      |    |  |  |  |  |

| Li | List of Figures vi |                                                      |    |  |  |  |  |

| Li | st of T            | ables                                                | ix |  |  |  |  |

| 1  | Intro              | oduction                                             | 1  |  |  |  |  |

|    | 1.1                | Real-time computing                                  | 1  |  |  |  |  |

|    | 1.2                | Structural Organization                              | 2  |  |  |  |  |

| 2  | Basi               | c Concepts and Related Work on Timing Anomalies      | 3  |  |  |  |  |

|    | 2.1                | Overview                                             | 3  |  |  |  |  |

|    | 2.2                | WCET Analysis                                        | 3  |  |  |  |  |

|    | 2.3                | Timing Relevant Dynamic Computer State               | 3  |  |  |  |  |

|    | 2.4                | Notation                                             | 4  |  |  |  |  |

|    | 2.5                | Related Work on Timing Anomalies                     | 5  |  |  |  |  |

|    | 2.6                | Fundamental Definition of Timing Anomalies           | 6  |  |  |  |  |

|    | 2.7                | Timing Anomaly Definition by Lundqvist and Stenström | 6  |  |  |  |  |

|    | 2.8                | Timing Anomaly Definition by Reineke et al.          | 7  |  |  |  |  |

|    | 2.9                | Series Timing Anomalies                              | 7  |  |  |  |  |

|    | 2.10               | Parallel Timing Anomalies                            | 10 |  |  |  |  |

| 3  | Pipe               | ine Architectures                                    | 21 |  |  |  |  |

|    | 3.1                | Overview                                             | 21 |  |  |  |  |

|    | 3.2                | Simple Scalar Pipelines                              | 21 |  |  |  |  |

|    | 3.3                | Scalar Pipelines                                     | 23 |  |  |  |  |

|    | 3.4                | Superscalar In-Order Pipelines                       | 24 |  |  |  |  |

|    | 3.5                | Superscalar Out-Of-Order Pipelines                   | 25 |  |  |  |  |

| 4  | Cach               | e Architectures                                      | 27 |  |  |  |  |

## CONTENTS

|     | 4.1<br>4.2<br>4.3<br>4.4 | Overview                                               | 27<br>27<br>28<br>28 |  |

|-----|--------------------------|--------------------------------------------------------|----------------------|--|

| 5   |                          | ing Anomalies in Pipelines                             | 20<br>31             |  |

| 5   |                          |                                                        | -                    |  |

|     | 5.1                      | Overview                                               | 31                   |  |

|     | 5.2                      | Timing Anomalies in Simple Scalar Pipelines            | 31                   |  |

|     | 5.3                      | Timing Anomalies in Scalar Pipelines                   | 32                   |  |

|     | 5.4                      | Timing Anomalies in Superscalar Pipelines              | 40                   |  |

|     | 5.5                      | Timing Anomalies in Superscalar Out-Of-Order Pipelines | 48                   |  |

|     | 5.6                      | Summary                                                | 51                   |  |

| 6   | Timi                     | ng Anomalies in Caches                                 | 53                   |  |

|     | 6.1                      | Overview                                               | 53                   |  |

|     | 6.2                      | Definition of Timing Anomalies on Caches               | 53                   |  |

|     | 6.3                      | Timing Anomalies in FIFO Caches                        | 55                   |  |

|     | 6.4                      | Timing Anomalies in LRU Caches                         | 58                   |  |

|     | 6.5                      | Timing Anomalies in PLRU Caches                        | 61                   |  |

|     | 6.6                      | Summary                                                | 65                   |  |

|     |                          | •                                                      |                      |  |

| 7   | Para                     | llel Timing Anomalies                                  | 67                   |  |

|     | 7.1                      | Overview                                               | 67                   |  |

|     | 7.2                      | Analysis of Parallel Timing Anomalies                  | 67                   |  |

| 8   | Con                      | clusion                                                | 69                   |  |

| Bil | Bibliography             |                                                        |                      |  |

# **List of Figures**

| 2.1  | Timing Relevant Dynamic Computer State                                                                         | 4  |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2.2  | First Definition of Timing Anomalies                                                                           | 7  |

| 2.3  | Definition of Timing Anomalies by Reineke et al.                                                               | 8  |

| 2.4  | Definition of Series Timing Anomalies                                                                          | 11 |

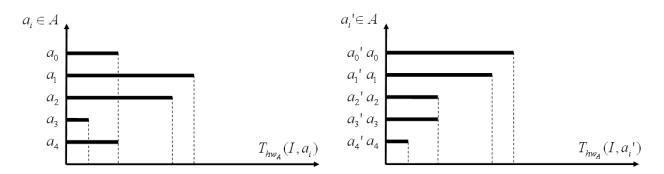

| 2.5  | Descending order of executions by $hw_A$                                                                       | 13 |

| 2.6  | Example of <i>TA-P-I</i> and <i>TA-P-A</i>                                                                     | 13 |

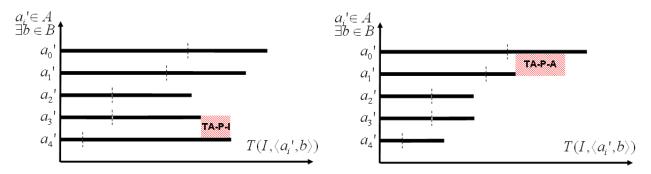

| 2.7  | Example of $TA$ - $P$ - $I$ , $TA$ - $P$ - $A$ for the same $b \in B$ and possible areas for no timing anomaly | 14 |

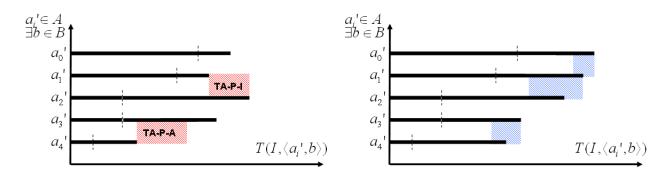

| 2.8  | Delta Composition principle                                                                                    | 14 |

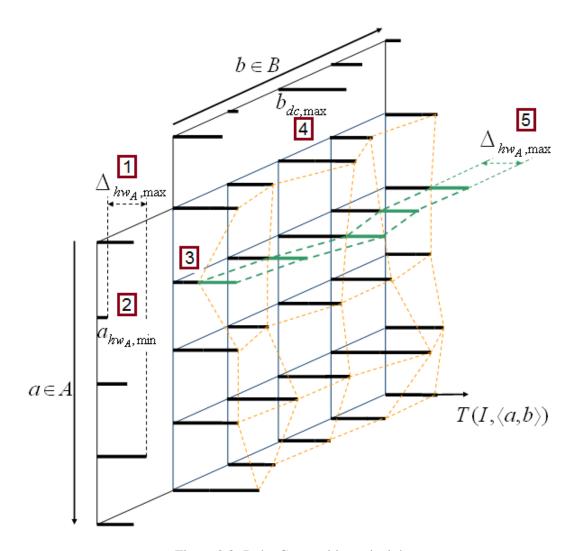

| 2.8  | Max Composition principle                                                                                      | 17 |

| 2.9  |                                                                                                                | 17 |

| 3.1  | Concept of Pipelines                                                                                           | 22 |

| 3.2  | Simple Scalar Pipeline                                                                                         | 22 |

| 3.3  | Structural Hazard                                                                                              | 23 |

| 3.4  | Data Hazard                                                                                                    | 23 |

| 3.5  | Merged Instructions illustrated as Blocks                                                                      | 24 |

| 3.6  | Scalar Pipeline                                                                                                | 24 |

| 3.7  | Superscalar In-Order Pipeline                                                                                  | 25 |

| 4.1  | 4-way PLRU Tree                                                                                                | 29 |

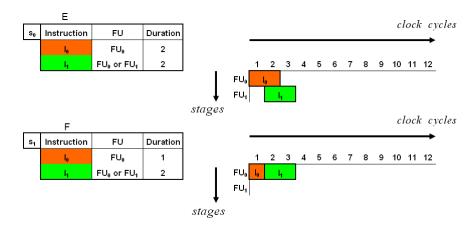

| 5.1  | Abstraction of Simple Scalar Pipeline                                                                          | 32 |

| 5.2  | Abstraction of Scalar Pipeline                                                                                 | 33 |

| 5.3  | Better pipeline visualization of complex pipeline processes                                                    | 34 |

| 5.4  | Scalar pipeline with no timing anomaly                                                                         | 35 |

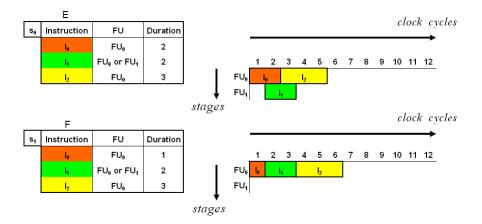

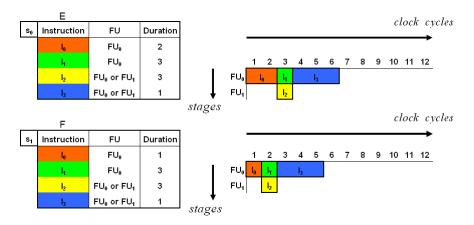

| 5.5  | Scalar pipeline with TA-S-I and 4 instructions                                                                 | 36 |

| 5.6  | Scalar pipeline with TA-S-A and 4 instructions                                                                 | 36 |

| 5.7  | Scalar pipeline with TA-S-I and 3 instructions                                                                 | 37 |

| 5.8  | Scalar pipeline trying to construct a TA-S-A with 3 instructions                                               | 38 |

| 5.9  | Scalar pipeline trying to construct TA-S-I and TA-S-A timing anomalies with 2 in-<br>structions                | 40 |

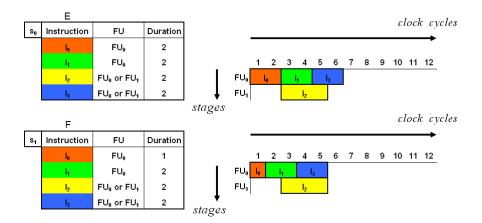

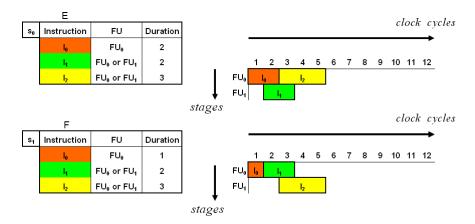

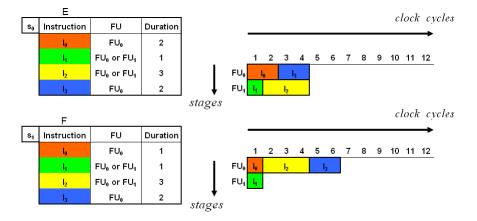

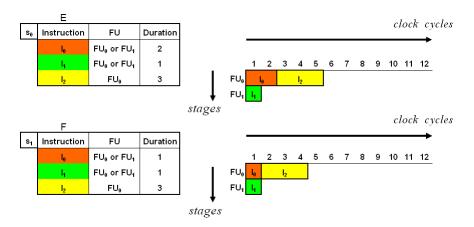

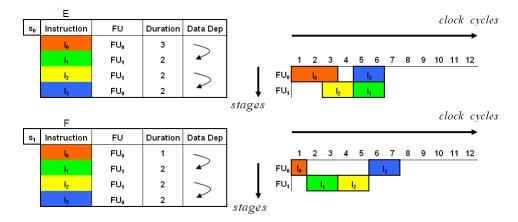

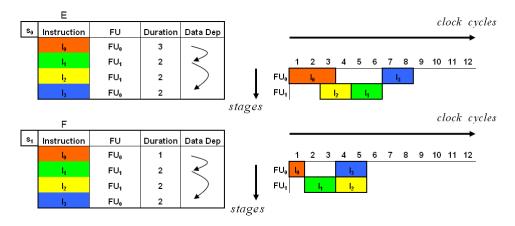

| 5.10 |                                                                                                                | 42 |

| 5.11 | Superscalar pipeline trying to construct a TA-S-A with 4 instructions and $I_1$ can be                         | .2 |

|      | executed at both function units                                                                                | 43 |

#### LIST OF FIGURES

| 5.12 | Superscalar pipeline trying to construct a TA-S-A with 4 instructions and $I_1$ can                                               | 43 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 5 10 | only be executed at $FU_0$                                                                                                        |    |

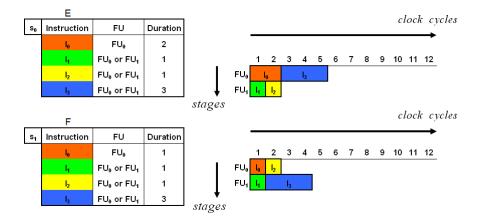

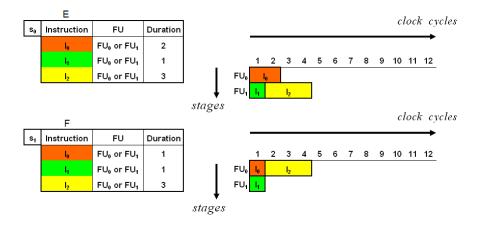

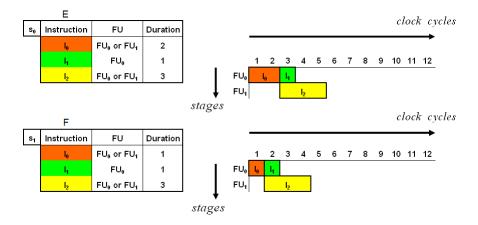

|      | Superscalar pipeline with TA-S-I and 4 instructions                                                                               | 44 |

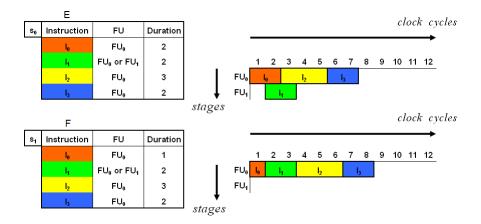

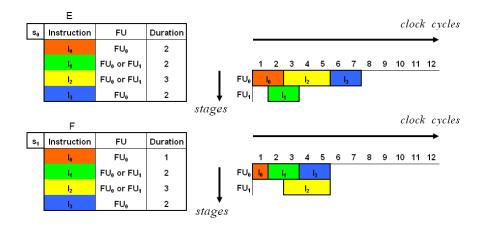

| 5.14 | Superscalar pipeline trying to construct a TA-S-I with 3 instructions and $I_0, I_1$ and                                          |    |

|      | $I_2$ can be executed at each function unit $\ldots \ldots \ldots$ | 45 |

| 5.15 | Superscalar pipeline trying to construct a TA-S-I with 3 instructions and $I_0, I_2$ can                                          |    |

|      | be executed at each function unit                                                                                                 | 46 |

| 5.16 | Superscalar pipeline with trying to construct a TA-S-I with 3 instructions and $I_0, I_1$                                         |    |

|      | can be executed at each function unit                                                                                             | 47 |

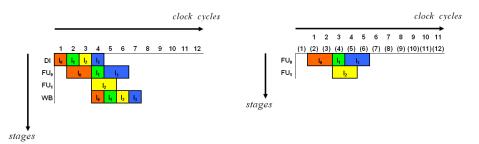

| 5.17 | Pipeline visualization of complex out-of-order pipeline processes                                                                 | 48 |

| 5.18 | Superscalar Out-Of-Order pipeline with TA-S-I and 4 instructions                                                                  | 49 |

| 5.19 | Superscalar Out-Of-Order pipeline with TA-S-A and 4 instructions                                                                  | 50 |

|      |                                                                                                                                   |    |

| 6.1  | Timing Anomalies of Cache Architectures                                                                                           | 54 |

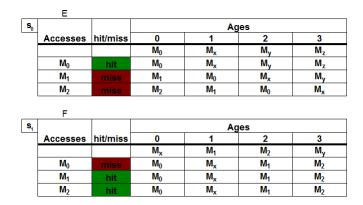

| 6.2  | 4-way associative FIFO, TA-S-I cache timing anomaly                                                                               | 56 |

| 6.3  | 4-way associative FIFO, TA-S-A cache timing anomaly                                                                               | 56 |

| 6.4  | 2-way associative FIFO, TA-S-I cache timing anomaly                                                                               | 57 |

| 6.5  | 2-way associative FIFO, TA-S-A cache timing anomaly                                                                               | 58 |

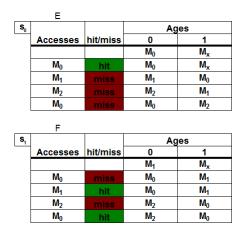

| 6.6  | 4-way associative LRU, TA-S-I cache timing anomaly                                                                                | 59 |

| 6.7  | 4-way associative LRU, TA-S-A cache timing anomaly                                                                                | 59 |

| 6.8  | 2-way associative LRU, best try to achieve a TA-S-I cache timing anomaly                                                          | 60 |

| 6.9  | 2-way associative LRU, TA-S-A cache timing anomaly                                                                                | 61 |

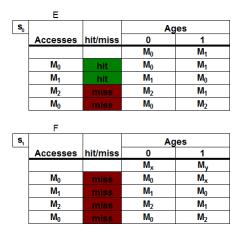

| 6.10 | 4-way associative PLRU, TA-S-I cache timing anomaly                                                                               | 62 |

| 6.11 |                                                                                                                                   | 63 |

| 6.12 | 2-way associative PLRU, best try to achieve a TA-S-I cache timing anomaly                                                         | 63 |

|      | 2-way associative PLRU, TA-S-A cache timing anomaly                                                                               | 65 |

|      |                                                                                                                                   |    |

# **List of Tables**

| 3.1 | Superscalar Out-Of-Order Pipeline: Resource Allocation Table | 26 |

|-----|--------------------------------------------------------------|----|

|     | <ul><li>4-way LRU cache: Filling with Age Update</li></ul>   |    |

| 5.1 | Summary of Timing Anomalies on Pipelines                     | 51 |

| 6.1 | Summary of Timing Anomalies on Caches                        | 66 |

# CHAPTER

1

# Introduction

## **1.1 Real-time computing**

In real-time systems there are deadlines in which a computation must be finished. These deadlines have to be satisfied within a specific time interval. The duration of this interval is irrelevant, but it must know a priori. That means, a real-time system does not only make a right computation, but also it must be right in the time domain. Thus there is an additional distinction in hardrespectively soft-real-time systems, based on the deadline restrictions.

#### Soft real-time systems

A soft real-time system can tolerate a missed deadline and admit a decreased service quality. An example of such a system is a video conference, where a video frame or an audio sequence could not be processed correctly. But those real-time systems should have an average load factor, that the majority of calculations are processed within the deadline interval.

#### Hard real-time systems

In hard real-time systems the deadlines must be met. If computations not satisfy the deadline, these computations are said to be failed. In this case such a failure can damage the whole system and furthermore human lives and the environment threatened. An example of a real-time system is the motor-management system of a car. In general hard real-time systems are applied in embedded systems, which react within a closely connection to its environment.

If all necessary computations are known a priori, then the system could be designed timecontrolled. In this design style there are time slots for each computation. Thereby it is possible to get a almost fully system load. But the computations must be finished within the allocated time slot. To derive the duration of a computation it is necessary to assume the worst case. Hence it is essential to calculate the worst-case-execution-time (WCET) of an instruction.

# **1.2 Structural Organization**

First we start with some basic concepts and definitions of timing anomalies in modern processor architectures in Chapter 2. Furthermore the notation is defined in the chapter and additional some composition techniques are explained.

In Chapter 3 the advantages of using pipeline architectures and the later analysed pipeline models are introduced.

The second part of the debated architectures, the caches, are presented in Chapter 4. Additional the functionality and concepts are discussed.

In Chapter 5 and 6 series timing anomalies are analysed regarding pipeline and cache architectures. Furthermore we differ between inversion and amplification timing anomalies and the minimal preconditions for their occurrence are under discussion.

In Chapter 7 the combination of the before treated architectures are in the focus of the parallel timing anomaly analysis, where an execution in the cache affects the behaviour of the pipeline execution.

# CHAPTER 2

# Basic Concepts and Related Work on Timing Anomalies

## 2.1 Overview

In this thesis the concentration is on timing anomalies occurring in the calculation of the WCET. Thus a short summary about the WCET calculation is presented first. Next the notation, which is used along the thesis, is shown. Finally timing anomalies are described and some composition techniques to compute the WCET are reported.

## 2.2 WCET Analysis

In modern processor architectures, where timing anomalies can appear in cache and pipeline architectures, the estimation of the WCET can only be done at substantial expense, see [19, 8, 2, 4]. For this analysis it is necessary to determine the longest possible path through an execution [6, 3]. This can be done with the control-flow analysis. With this we know a set of all possible paths along an execution and can now study them. A clever method is to use the 'divide and conquer'-concept, thus to derive the maximum duration of a statement and do this along the execution in a bottom-up manner. Unfortunately this method leads not always to an appropriate result for the WCET. This is due to the cache- and pipeline-architectures of modern processors. With these components so called timing anomalies can occur, the discussed subject of this thesis. These timing anomalies violate the notion of proportionality in the timing domain in a certain manner.

# 2.3 Timing Relevant Dynamic Computer State

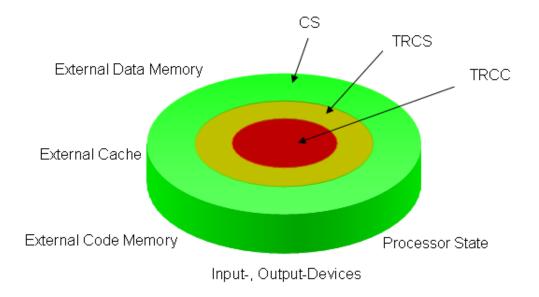

With the timing-relevant state model, which is introduced in [5], interesting computer states can be examined. In this model several computer states are defined. The first one is the overall

computer state CS, which includes all states for different components like external data memory, external cache, external code memory, input-, output-devices and of course the processor state. A subset of the CS is the timing-relevant computer state TRCS. In this set all elements which are relevant for the timing of an execution are combined. The next subset of the TRCS is the timing-relevant computer configuration TRCC. Within this set are timing-relevant elements, but they are constant. A graphical model of the definitions is presented with Figure 2.1. These definitions bring us finally to the timing-relevant dynamic computer state TRDCS, which contains those elements that are in the timing-relevant computer state, though they are not in the timing relevant computer configuration.

Thus in all following chapters only states in the TRDCS state are of interest. Note that timing anomalies, which are introduced in the next chapters, are trivial to produce in cases, where the whole state space or timing irrelevant states are involved. Therefore the concentration of the WCET analysis is only on the essential part of the Computer State, namely the TRDCS.

Figure 2.1: Timing Relevant Dynamic Computer State

# 2.4 Notation

For a detailed analysis it is necessary to get familiar with the formal definitions. The following definitions and achievements are principal obtained by [6].

**Definition 2.4.1** T(I, s) is the execution time of an instruction sequence I (which can consists of particular instruction  $I_1 \circ I_2 \circ I_3 \circ \ldots$ , where the  $\circ$  operator connect instructions in a sequential manner) beginning from the initial state  $s \in TRDCS$ .

**Definiton 2.4.2**  $T_{max}(I, S) = max(T(I, s)|s \in S)$  is the maximum of all execution times for instruction I with an initial state s of the set of potential initial states S.

**Definition 2.4.3**  $\Delta(I, s, s') = T(I, s') - T(I, s)$  is the difference of execution times of instruction sequence I for different initial states  $s, s' \in TRDCS$ .

**Definiton 2.4.4**  $\mathbb{IN}_I$  is the set of potential initial states of instruction *I*.

**Definiton 2.4.5**  $\mathbb{IN}_{I,max} = \{s \in \mathbb{IN}_I \land \forall s' \in \mathbb{IN}_I.T(I,s') \leq T(I,s)\}$  is the set of initial states of instruction I, where T(I,s) is maximal.

The following definitions apply to the partition of the TRDCS in hardware components of interest for the timing of the instruction. These definitions imagine, that two different components (like pipeline and cache) can analysed for itself and join the results for an overall analysis.

**Definition 2.4.6**  $T_{hw_A}(I, a)$  is the execution time for instruction I of hardware component  $hw_A$  with the initial local state  $a \in A$ , where A is the set of initial states for the TRDCS component  $hw_A$ . When another component is in progress and consume execution time, but hardware component  $hw_A$  is not involved, then this does not count to  $T_{hw_A}(I, a)$ .

**Definition 2.4.7**  $\Delta_{hw_A}(I, a, a') = T_{hw_A}(I, a') - T_{hw_A}(I, a)$  is the difference of the execution times for the instruction I for different initial states a and  $a' \in A$  for the hardware component  $hw_A$ .

#### 2.5 Related Work on Timing Anomalies

The first exploration of timing anomalies in association with WCET calculation is done by Lundqvist and Stenström in [9]. They introduced a concept, where a cache miss results in a decreasing execution time in an out-of-order pipeline and cache processor, namely a simplified PowerPC architecture processor. Also they assert, that in in-order pipelines no timing anomalies are appear, which was invalidated later. In this paper also a formal definition about timing anomalies are given and examples of domino effects are shown. Additionally a simple code modification method is displayed to inhibit timing anomalies.

In [1, 12] a more precise study on domino effects and the effect of an unbounded WCET. He shows some examples with the pseudo least recently used (PLRU) cache replacement strategy.

A classification in scheduling-, speculating- (also [14]) and cache-timing anomalies are given in [13]. Whereas the latter two classification classes can appear in in-order architectures.

In the paper of Wenzel et al. [18] they acquire the resource allocation criterion, which is a necessary, but not a sufficient condition for the appearance of timing anomalies. With this criterion it is possible to evaluate, if an anomaly can occur. But the resource allocation criterion limits the occurrence of anomalies in that sense, that only one instruction can change the timing. Also they provide, that timing anomalies can occur in simply models, like in-order architectures.

In [5] Kirner et al. presenting formal definitions of serial and parallel timing anomalies and categorize them in amplification and inversion classes. Also they had shown some composition

techniques for parallel timing anomalies, in particular the delta- and max-composition, and the series-composition for series timing anomalies. Furthermore parallel timing anomalies are described more in detail in case of a simultaneously appearance.

### 2.6 Fundamental Definition of Timing Anomalies

Lundqvist and Stenström were the first, who explored the phenomenon of timing anomalies and described them with the following words: "Previous timing analysis methods have assumed that the worst-case instruction execution time necessarily corresponds to the worst-case behaviour. We show that this assumption is wrong in dynamically scheduled processors." [9]. Furthermore they explained that a cache miss can provide a shorter overall execution than a cache hit.

In [13], Reineke et al. described a timing anomaly as the circumstances, where a local worstcase situation does not affect a global worst-case situation. Kirner et al. characterize a timing anomaly as a case where the persistence properties of proportionality and monotony in the timing behaviour invalidates the continuity characteristic in [6].

## 2.7 Timing Anomaly Definition by Lundqvist and Stenström

A first definition of timing anomalies was introduced by Lundqvist and Stenström in [9]. They described it in the following manner.

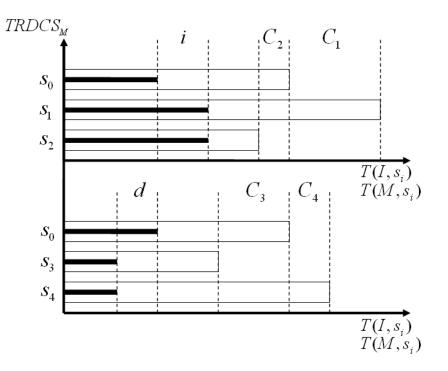

"Consider the execution of a sequence of instructions. Let us study two different cases where the latency of the first instruction is modified. In the first case, the latency is increased by i clock cycles. In the second case, the latency is decreased by d cycles. Let C be the future change in execution time resulting from the increase or decrease of the latency. Then:" ([9])

**Definition 2.7.1** "A timing anomaly is a situation where, in the first case, C > i or C < 0, or in the second case, C < -d or C > 0." (Definition 1 in [9])

That means a timing anomaly does not happen as described in [9], if the future change of the remaining execution C is in the interval  $0 \le C \le i$  in the first case or  $-d \le C \le 0$  in the second case. In Figure 2.2 these definitions are explained in a graphical manner.

The duration of the first instruction M is represented as thick black line and the duration of the overall execution I is indicated as a rectangle. The difference of the entire execution between  $T(I, s_0)$  and  $T(I, s_i)$  (with  $1 \le i \le 4$ ) is labelled as  $C_i$ .

In the first case,  $T(M, s_1)$  and  $T(M, s_2)$  need *i* more clock cycles for their executions than the reference execution  $T(M, s_0)$ . But the difference  $C_1 = T(I, s_1) - T(I, s_0)$  is greater than the difference of the first instruction  $i = T(M, s_1) - T(M, s_0)$ . This timing anomaly is discussed later as *amplification timing anomaly*. The difference  $C_2 = T(I, s_2) - T(I, s_0) < 0$  brings us to the timing anomaly we will later call *inversion timing anomaly*.

In the second diagram a decreased duration  $d = T(M, s_3) - T(M, s_0)$  of the first instruction M between the reference execution  $T(M, s_0)$  and  $T(M, s_3)$  (resp.  $T(M, s_4)$ ) is presented. Hence  $C_3 = T(I, s_3) - T(I, s_0)$  is smaller than -d. This results again in an amplification timing

Figure 2.2: First Definition of Timing Anomalies

anomaly, but in a decreasing way. On the other hand  $C_4 = T(I, s_4) - T(I, s_0) > 0$  and leads to an inversion timing anomaly.

## **2.8** Timing Anomaly Definition by Reineke et al.

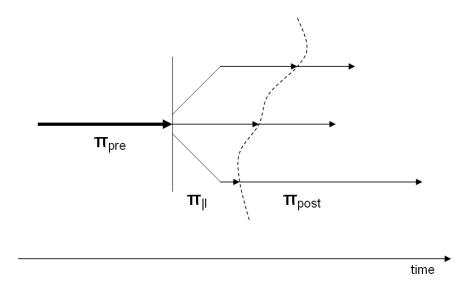

Reineke et al. defined a program execution, where a path  $\pi$  is partitioned in three parts ( $\pi_{pre}$ ,  $\pi_{|l}$  and  $\pi_{post}$ ), where *l* is a locally constraint for  $\pi_{|l}$  in [13]. Following the non-local worst-case path leads to a global worst-case path for the execution of  $\pi$ . In the Figure 2.3 this concept is illustrated with a realization, where the first execution has the local worst-case path; however the last execution (with the non-local worst-case path) is the crucial path for the WCET calculation.

## 2.9 Series Timing Anomalies

Timing anomalies which can be handled with the series decomposition technique (described later) are labelled as 'series timing anomalies'. This category of timing anomalies is in general observed, if an instruction sequence is split into two different streams (whereas an instruction stream can be consists of only one instruction). Then the relation between the execution of the first instruction stream and the whole instruction sequence is analysed and in case of a timing anomaly, this situation is called a series timing anomaly. Within the definition of the series timing anomalies, all initial states are elements from the TRDCS. These definitions based on the

definitions of Lundqvist and Stenström [9] and extended by Kirner et al. in [6].

Series timing anomalies differ in their impact on the timing behaviour. In case of *inversion series timing anomalies (TA-S-I)* the execution time of the whole instruction sequence change in an opposite direction than the first sequence. On the other hand if the execution of the whole instruction stream follows the direction of the alteration of the first instruction sequence execution and amplifies this change, this is called an *amplification series timing anomalies (TA-S-A)*. The followed definitions are mostly obtained from [6].

#### Definiton 2.9.1 TA-S-I

Assume an instruction sequence  $I = M \circ N$ , which consists of two non empty instruction sequences M and N and the initial states  $s, s' \in TRDCS$ . Then an inversion series timing anomaly is a situation, where:

$\begin{aligned} \exists s, s' \in \mathbb{IN}_M. \\ \Delta(M, s, s') > 0 \ \land \ \Delta(I, s, s') < 0 \end{aligned}$

#### Definiton 2.9.2 TA-S-A

Assume the same instruction sequence  $I = M \circ N$  as in the above definition and the initial states  $s, s' \in TRDCS$ . Then an amplification series timing anomaly is a situation, where:  $\exists s, s' \in \mathbb{IN}_M$ .  $0 < \Delta(M, s, s') < \Delta(I, s, s')$

The timing anomaly TA-S-I is also called '*strong timing anomaly*', because this anomaly cannot be analysed with the series decomposition without problems. The TA-S-A timing anomaly is named '*weak timing anomaly*', since a serious calculation of the WCET can be achieved with the series decomposition technique.

Figure 2.3: Definition of Timing Anomalies by Reineke et al.

The next definitions highlight the cases, where series timing anomalies affect the calculation of the WCET. For that reason these timing anomalies are termed '*worst-case series timing anomalies*'. Worst-case inversion anomalies of this kind are labelled as TAW-S-I and worst-case amplification anomalies as TAW-S-A.

#### Definiton 2.9.3 TAW-S-I

Assume an instruction sequence  $I = M \circ N$ , which consists of two non empty instruction sequences M and N and the initial states  $s, s' \in TRDCS$ . Then a worst-case inversion series timing anomaly is a situation, where:

$\exists s \in \mathbb{IN}_M, \forall s' \in \mathbb{IN}_{M,max}. \\ \Delta(M, s, s') > 0 \ \lor \ \Delta(I, s, s') < 0$

#### Definiton 2.9.4 TAW-S-A

Assume the same instruction sequence  $I = M \circ N$  as in the above definition and the initial states  $s, s' \in TRDCS$ . Then an amplification series timing anomaly is a situation, where:  $\exists s \in \mathbb{IN}_M, \forall s' \in \mathbb{IN}_{M,min}.$  $0 < \Delta(M, s, s') < \Delta(I, s, s')$

The difference of the worst-case series timing anomalies and the 'normal' series timing anomalies is first the quantifier of s' changes from  $\exists$  to  $\forall$  and second for TAW-S-I to  $\forall s' \in \mathbb{IN}_{M,max}$  and for TAW-S-A to  $\forall s' \in \mathbb{IN}_{M,min}$ . This causes a situation, in which the initial state s' is taken from the set  $\mathbb{IN}_{M,max}$  (in case of *TAW-S-I*) and thus a more pointed setting is created. In the case of *TAW-S-A* the initial state s' is in the set  $\mathbb{IN}_{M,min}$  and this results in a more precise definition of an amplification anomaly due to the WCET calculation.

#### **Series Decomposition**

To analyse series timing anomalies, the straight forward technique *series decomposition* is presented in [6]. With this technique it is possible to approximate one worst-case state for each control-flow node instead of k states for k input states and the maximum of two successive instructions is computed. This is an enormous advantage, because the number of collected states is growing exponentially with the program size. If this is done for each control-flow node across the entire execution, then the resulting maximum execution time is actual the WCET bound.

#### **Defintion 2.9.5** Series Composition

Assume an instruction sequence  $I = M \circ N$ , which consists of two non empty instruction sequences M and N and the initial state  $s \in TRDCS$ . Then the WCET of the series composition,  $T_{sc}$ , is calculated in the following manner:  $T_{sc}(M \circ N) = \max_{s \in \mathbb{IN}_{M,max}} T(M \circ N, s)$

Amplification timing anomalies do not invalidate this calculation technique and an upper bound for the WCET is provided for this kind of timing anomalies with this technique. The safeness of the series composition and a sufficient and necessary condition for a safe WCET bound is presented in the next theorem. The proof of the theorem and the theorem itself is shown in [6].

#### **Theorem 2.9.6** Safeness of Series Composition

"Assuming that the program to be analysed is decomposed into connected control-flow nodes and the set of possible subpathes (= sequences of control-flow nodes) of the program is denoted by the set SP, then Series-Composition allows to provide a safe WCET bound on processor hardware whose timing characteristics obey the following sufficient and necessary condition:  $\forall M \circ N \in SP, \forall s_1 \in IN_M, \exists s_2 \in IN_{M,max}.$  $\Delta(M, s_1, s_2) > 0 \rightarrow \Delta(M \circ N, s_1, s_2) \geq 0$ " ([6] Theorem 4.1 and Proof A.1)

That means that  $s_2$  is taken from the set  $\mathbb{IN}_{M,max}$  and this ensures, that the execution time of the instruction M and so  $T(M, s_2)$  is maximal. If the difference of  $T(M, s_2)$  and  $T(M, s_1)$  is greater than zero, then the difference of execution time of the instruction sequence of  $T(M \circ N, s_2)$  and  $T(M \circ N, s_1)$  must be also greater than or equal to zero.

If we take a precise look to the definition of the *TAW-S-I* timing anomaly one can notice that this is an opposite definition of the safeness condition of the series composition. Even by this reason the series composition can not ensure a serious WCET bound.

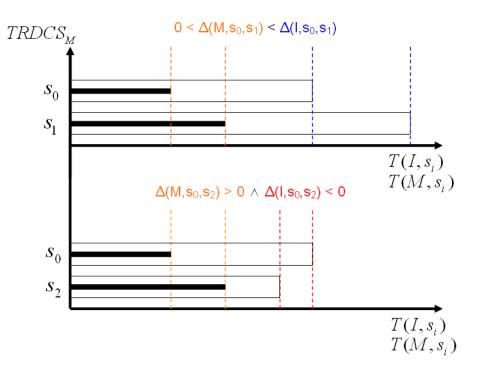

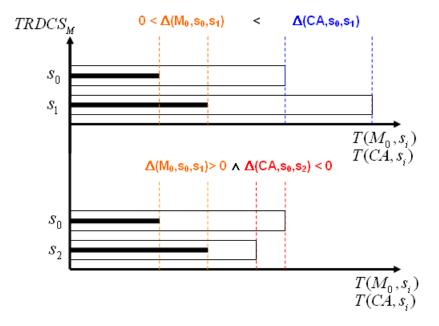

In Figure 2.4 the above definitions are explained graphically. In the first diagram the difference  $\Delta(M, s_0, s_1)$  is greater than zero and the difference of the instruction sequence  $\Delta(I, s_0, s_1)$ , with  $I = M \circ N$ , is also greater than  $\Delta(M, s_0, s_1)$ . This results in a series amplification timing anomaly *TA-S-A*.

In the second diagram the difference  $\Delta(M, s_0, s_2)$  is greater than zero (same as in the first diagram), but the difference  $\Delta(I, s_0, s_2)$  is smaller than zero. This is an indication of a series inversion timing anomaly *TA-S-I*.

If we compare the definitions of Lundqvist and Stenström with the definitions of Kirner et al., then we can determine similarities. The number of increased clock cycles *i* in the definitions of Lundqvist and Stenström correlates with  $\Delta(M, s_0, s_1)$  (resp.  $\Delta(M, s_0, s_2)$ ) of the definitions of Kirner et al. The difference of the overall execution times  $C_1$  and  $C_2$  are equivalent with  $\Delta(I, s_0, s_1)$  and  $\Delta(I, s_0, s_2)$ . Furthermore the additional term C < -d or C > 0 of Lundqvist and Stenström has been substituted by the permutation of the variables in the Delta-Term.

#### 2.10 Parallel Timing Anomalies

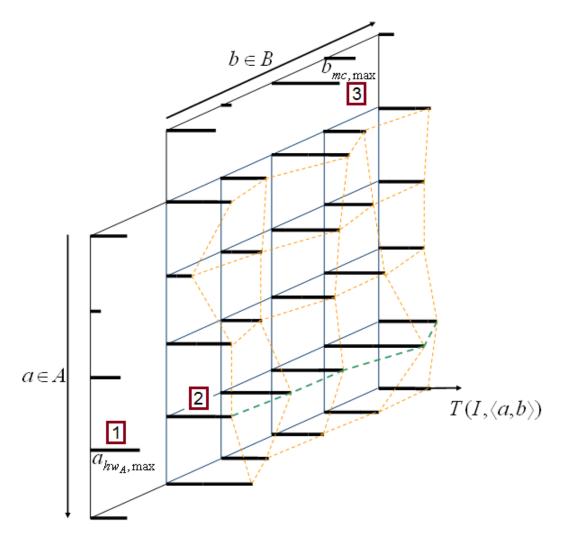

The idea of clarify *parallel timing anomalies* is to partition the TRDCS state space, which was introduced in Chapter 2.3, into two independent state spaces  $\text{TRDCS} = A \cup B$ , e.g. like that from caches and pipelines. Consider that each of the partition areas has a separate timing behaviour. If we observe parallel timing anomalies, then we focus on the comparison of the component latency  $T_{hw_A}(I, a)$  of the instruction I of hardware component  $hw_A$  (with  $a \in A$ ) and the overall execution time  $T(I, \langle a, b \rangle)$  with  $b \in B$ . The state  $\langle a, b \rangle$  is taken from the initial state set  $A \times B$ . The definitions are obtained from Kirner et al. [6].

#### Definiton 2.10.1 TA-P-I

Assume an instruction sequence I and a TRDCS initial state space, which is partitioned in two

Figure 2.4: Definition of Series Timing Anomalies

non-empty sets  $A \cup B$  with the component latency  $T_{hw_A}(I, a)$  of hardware component  $hw_A$  and the overall execution time  $T(I, \langle a, b \rangle)$ , with  $a \in A, b \in B$ . Then an inversion parallel timing anomaly is a situation, where:  $\exists a, a' \in A, \exists b \in B$ .

$\Delta_{hw_{A}}(I, a, a') > 0 \land \Delta(I, \langle a, b \rangle, \langle a', b \rangle) < 0$

#### Definiton 2.10.2 TA-P-A

Assume an instruction sequence I with the same partitioning as in the above definition and the identical execution times. Then an amplification parallel timing anomaly is a situation, where:  $\exists a, a' \in A, \exists b \in B.$  $0 < \Delta_{hw_A}(I, a, a') < \Delta(I, \langle a, b \rangle, \langle a', b \rangle)$

A more specific case for the above definitions, the *worst-case parallel timing anomalies*, are shown in the next definitions, like for the series timing anomalies. There are more specific situations indicate where the analysis with the *parallel decomposition* techniques (which will be presented below) could be difficult to handle. First, some helpful sets are introduced.

#### Defintion 2.10.3

$A_{min} = \{a \in A \mid \forall a' \in A. \ T_{hw_A}(I,a') \ge T_{hw_A}(I,a)\}$   $A_{max} = \{a \in A \mid \forall a' \in A. \ T_{hw_A}(I,a') \le T_{hw_A}(I,a)\}$  $B_{A,max}(a) = \{b \in B \mid \forall b' \in B. \ T(I, \langle a, b \rangle) \ge T(I, \langle a, b' \rangle)\}$

11

The set  $A_{min}$  describes the set of initial states, which have a minimal execution time for instruction I for hardware component  $hw_A$ . The elements of the set  $A_{max}$  lead for instruction Iand  $hw_A$  to a maximal execution time. Additionally the set  $B_{A,max}(a)$  includes the initial states  $b \in B$ , which achieve a maximal execution time  $T(I, \langle a, b \rangle)$ .

#### Definiton 2.10.4 TAW-P-I

Assume an instruction sequence I and a TRDCS initial state space, which is partitioned in two non-empty sets  $A \cup B$  with the component latency  $T_{hw_A}(I, a)$  of hardware component  $hw_A$  and the overall execution time  $T(I, \langle a, b \rangle)$ , with  $a \in A, b \in B$ . Then a worst-case inversion parallel timing anomaly is a situation, where:

$\exists a \in A, \exists b \in B, \forall a' \in A_{max}, \forall b' \in B_{A,max}(a'). \\ \Delta_{hw_A}(I, a, a') > 0 \lor \Delta(I, \langle a, b \rangle, \langle a', b \rangle) < 0$

#### Definiton 2.10.5 TAW-P-A

Assume an instruction sequence I with the same definitions as above. Then a amplification parallel timing anomaly is a situation, where:

$\exists a \in A, \exists b \in B, \forall a' \in A_{min}, \forall b' \in B_{A,max}(a'). \\ 0 < \Delta_{hw_A}(I, a', a) < \Delta(I, \langle a', b' \rangle, \langle a, b \rangle)$

Thus the worst-case inversion parallel timing anomaly originates when the difference between the executions with the initial states a and a',  $a' \in A_{max}$  of instruction I at the hardware component  $hw_A$  is greater than zero and the difference of the overall execution times is less than zero. Thus the characteristic of the execution of the overall execution proceeds in the opposite direction than the execution at  $hw_A$ . The fact, that a' is taken from the set  $A_{max}$  invokes a situation in which the term  $\Delta_{hw_A}(I, a, a')$  has a maximum value and the term  $\Delta(I, \langle a, b \rangle, \langle a', b \rangle)$ reaches a minimal value.

For the worst-case amplification parallel timing anomaly *TAW-P-A* the term  $\Delta_{hw_A}(I, a', a)$  (with  $a' \in A_{min}$ ) depicts a value which is slightly greater than zero. And the difference of  $T(I, \langle a, b \rangle)$  and  $T(I, \langle a', b' \rangle)$  (which forces the maximum execution time for the initial state a') is still greater than the first term.

#### **Illustration of Parallel Timing Anomalies**

In Chapter 2.9 an illustration of timing anomalies has been introduced for series timing anomalies. In the following the visualization for parallel timing anomalies is presented. First of all, the instructions which are executed in  $hw_A$  (with initial states  $a_i$ ,  $0 \le i \le 4$ ) are presented as black thick lines and are followed by the executions for the other hardware component (with initial states  $b_i$ , with  $0 \le i \le 4$ ) as black thick lines.

To identify timing anomalies easier, we order the executions T(I, a) based on the required time in descending order, Figure 2.5.

The initial states of the executions are relabeled with  $a'_i$ . Next the execution times  $T(I, \langle a'_i, b \rangle)$  for all  $a'_i \in A$  and one fixed  $b \in B$  are built. With this information timing anomalies can now be identified immediately. In the Figure 2.6 a *TA-P-I* example is displayed on the left. If we take a close look at the executions we can observe that  $\Delta_{hw_A}(I, a'_4, a'_3) > 0$  and  $\Delta(I, \langle a'_4, b \rangle, \langle a'_3, b \rangle) < 0$

Figure 2.5: Descending order of executions by  $hw_A$

0 and this is equivalent to the definition of the *TA-P-I*. Furthermore we can find that  $\Delta(I, \langle a'_3, b \rangle, \langle a'_2, b \rangle) < 0$ . Is this not also an *TA-P-I*? No, because the first term  $\Delta_{hw_A}(I, a'_3, a'_2) > 0$  is not fulfilled. If the difference of two executions at  $hw_A$  is zero, then there is no anomaly.

On the right side we notice a *TA-P-A* timing anomaly, due to the fact that  $0 < \Delta_{hw_A}(I, a'_1, a'_0)$ and this is less than  $\Delta(I, \langle a'_1, b \rangle, \langle a'_0, b \rangle)$ .

Figure 2.6: Example of TA-P-I and TA-P-A

Of course it is possible, that a TA-P-I and TA-P-A timing anomaly for the same  $b \in B$  might occur. On the left side in Figure 2.7 this case is shown.

Certainly we are interested in those cases where no timing anomalies occur. When the execution times  $T(I, a'_i)$  are in descending order, then no timing anomaly appears, if the execution times of  $T(I, \langle a'_i, b \rangle)$  are also in descending order or adjacent execution times are equal. Also no timing anomaly appear, if we subtract the difference of time from the actual and the successive execution of hardware component  $hw_A$  from the actual overall execution time  $T(I, \langle a'_i, b \rangle)$ . For executions with the same latency no timing anomaly can appear.

#### **Composition Techniques for WCET Analysis**

In this section some composition techniques are presented. There are helpful for calculating a bound for the WCET analysis. The principle of partitioning the TRDCS state set into two sets with their initial states  $a \in A, b \in B$  is needed for the shown techniques. The techniques assume

Figure 2.7: Example of *TA-P-I*, *TA-P-A* for the same  $b \in B$  and possible areas for no timing anomaly

two TRDCS state sets A and B and calculate the overall execution time for the instruction I and for each pair  $\langle a, b \rangle$  from the set  $A \times B$ .

#### **Delta Composition**

To get a WCET bound the following steps must be performed (visually represented at Figure 2.8):

- 1.  $\Delta_{hw_A,max} = \max_{a,a' \in A} |T_{hw_A}(I,a) T_{hw_A}(I,a')|$ : The maximum difference of execution times  $T_{hw_A}(I,a)$  for hardware component  $hw_A$  is calculated.

- 2.  $A_{min} = \{a \in A | \forall a' \in A.T_{hw_A}(I, a') \ge T_{hw_A}(I, a)\}$ : The set of initial states for hardware component  $hw_A$ , where execution times  $T_{hw_A}(I, a)$  are minimal is computed.

- T(I, (a<sub>hw<sub>A</sub>,min</sub>, b)): For all states, which are within the before calculated set A<sub>min</sub>, the entire execution times with fixed initial states a<sub>hw<sub>A</sub>,min</sub> are derived.

- 4.  $b_{dc,max} \in B_{A,max}(a_{hw_A,min}) = \{b \in B | \forall b' \in B.T(I, \langle a_{hw_A,min}, b \rangle) \geq T(I, \langle a_{hw_A,min}, b' \rangle)\}$ : One element *b* from the set  $B_{A,max}(a_{hw_A,min})$ , in which are initial states of set *B* that produce maximum overall execution times for the initial states  $a_{hw_A,min}$  of set *A*, is selected.

- 5.  $T(I, \langle a_{hw_A,min}, b_{dc,max} \rangle) + \Delta_{hw_A,max}$ : The difference of the first step is added to the overall execution times of step four.

The above presented steps can be formalized with the next definition:

**Definition 2.10.6**  $T_{dc}(I) = \max_{a \in A_{min}, b \in B} T(I, \langle a, b \rangle) + \Delta_{hw_A, max}$

14

CHAPTER 2. BASIC CONCEPTS AND RELATED WORK ON TIMING ANOMALIES

Figure 2.8: Delta Composition principle

In general the delta composition overestimates the WCET and if we analyse the steps defined above, we can detect that the worst case for the calculation of  $T_{dc}$  is when all initial states  $a \in A_{min}$ . But in this case there are no differences in the execution times and hence all states  $a \in A_{min}$  are not part of the TRDCS. Thus the worst-case is  $|A_{min}| = |A| - 1$  and the calculation for the delta composition requires  $O((|A| + |A_{min}| * |B|) * |I|)$ . This is explained by the search of  $\Delta_{hw_A,max}$  (step 1) and  $A_{min}$  (step 2) for |A|. The term  $|A_{min}| * |B|$  can be declared by the computation of the overall execution times  $T(I, \langle a_{hw_A,min}, b \rangle)$  and then multiplied by the instruction |I|.

#### Theorem 2.10.7 Safeness of Delta Composition

Assume the definitions from 2.10.4 and an execution of I with a partitioned TRDCS, then the following expression is sufficient and necessary for the safeness of the delta composition tech-

#### 2.10. PARALLEL TIMING ANOMALIES

nique:  $\forall a \in A, \forall b \in B, \exists a' \in A_{min}, \exists b' \in B_{A,max}(a').$  $\Delta_{hw_A}(I, a', a) > 0 \rightarrow \Delta(I, \langle a', b' \rangle, \langle a, b \rangle) \leq \Delta_{hw_A,max}$  ([6] Theorem 5.1 and Proof A.2)

That means, if the execution time of an instruction I for an arbitrary initial state a is greater than for  $a' (= a_{hw_A,min})$ , then the difference of the overall execution time between a pair of random initial states  $\langle a, b \rangle$  and  $\langle a', b' \rangle$  ( $b' \in B_{A,max}(a')$ ) must be less or equal to the maximum difference of the execution times for hardware component  $hw_A$ ,  $\Delta_{hw_A,max}$ . One can observe, that this is the opposite of the definition of *TAW-P-A*. With this steps it is possible to calculate a serious WCET bound in case of parallel inversion timing anomalies, because there is a local best case ( $a_{hw_A,min}$ ) and the difference to another initial state a ( $\Delta_{hw_A}(I, a_{hw_A,min}, a)$ ) must be greater or equal than  $\Delta(I, \langle a_{hw_A,min}, b' \rangle, \langle a, b \rangle)$  (see Safeness of Delta Composition). **The delta composition is used to analyse TA-P-I timing anomalies.**

#### Max Composition

In the previous section a composition technique was presented to compute a WCET bound for TA-P-I timing anomalies. In this chapter the max composition technique for analysing TA-P-A timing anomalies is shown. This can be done with the following steps (see Figure 2.9):

- 1.  $A_{max} = \{a \in A | \forall a' \in A.T_{hw_A}(I, a') \leq T_{hw_A}(I, a)\}$ : The set of initial states for hardware component  $hw_A$ , where execution times  $T_{hw_A}(I, a)$  are maximal is computed.

- 2.  $T(I, \langle a_{hw_A,max}, b \rangle)$ : For all states, of  $A_{max}$ , the entire execution times  $T(I, \langle a_{hw_A,max}, b \rangle)$  with fixed initial states  $a_{hw_A,max}$  are derived.

- 3.  $b_{mc,max} \in B_{A,max}(a_{hw_A,max}) = \{b \in B | \forall b' \in B.T(I, \langle a_{hw_A,max}, b \rangle) \geq T(I, \langle a_{hw_A,max}, b' \rangle)\}$ : One element *b* from the set  $B_{A,max}(a_{hw_A,max})$ , in which are initial states of set *B* to produce maximum overall execution times for the initial states  $a_{hw_A,max}$  of set *A*, is selected.

The max composition offers a precise WCET bound and is specified with the following definition.

**Definition 2.10.8**

$$T_{mc}(I) = \max_{a \in A_{max}, b \in B} T(I, \langle a, b \rangle)$$

It seems that the worst-case for the calculation of  $T_{mc}$  is that all initial states  $a \in A_{max}$ . But in this case there are no differences in the timing behaviour (like in the explanation of  $T_{dc}$ ) and hence it is not part of the TRDCS. Therefore  $|A_{max}| = |A| - 1$  is the worst-case for the calculation and it requires  $O((|A| + |A_{max}| * |B|) * |I|)$ . This computational cost is calculated as stated above by the search of all states from A to get  $A_{max}$  and then derive the overall execution times with the states from B multiplied with the number of instructions. CHAPTER 2. BASIC CONCEPTS AND RELATED WORK ON TIMING ANOMALIES

Figure 2.9: Max Composition principle

#### Theorem 2.10.9 Safeness of Max Composition

Assume the same definitions from def:TAW-P-I and an execution of I with a partitioned TRDCS, then the following expression is necessary and sufficient for the safeness of the max composition technique:

$\begin{array}{l} \forall a \in A, \forall b \in B, \exists a' \in A_{max}, \exists b' \in B_{A,max}(a'). \\ \Delta_{hw_A}(I, a, a') > 0 \rightarrow \Delta(I, \langle a, b \rangle, \langle a', b' \rangle) \geq 0 \ ( \ \textit{[6] Theorem 5.3 and Proof A.2)} \end{array}$

That means, if the execution time of an instruction I for  $a' (= a_{hw_A,max})$  is greater than for an arbitrary initial state a, then the difference of the overall execution time between  $\langle a', b' \rangle$  $(b' \in B_{A,max}(a'))$  and a pair of random initial states  $\langle a, b \rangle$  must be greater or equal to zero. One can observe, that this is the opposite of the definition of *TAW-P-I*.

Thus the max composition technique calculates the maximum execution time for the combina-

tion of the sets A and B, the following statement is obvious. The max composition is used to analyse TA-P-A timing anomalies.

With each of the introduced techniques it is possible to give a WCET bound without analysing the whole state space  $A \times B$ . If the two parallel anomaly types (TA-P-I and TA-P-A) occur in one execution for different initial states  $b_1, b_2 \in B$ , then also a WCET bound can be computed, even without searching the whole state space.

#### Definiton 2.10.10 TA-P-E

Assume an instruction sequence I and a TRDCS initial state space, which is partitioned in two non-empty sets  $A \cup B$  with the component latency  $T_{hw_A}(I, a)$  of hardware component  $hw_A$  and the overall execution time  $T(I, \langle a, b \rangle)$ , with  $a \in A, b \in B$ . Then an exclusive parallel timing anomaly is a situation, where the next three properties are fulfilled:  $\exists a_1, a_2, a_3, a_4 \in A, \exists b_1, b_2 \in B.$  $(b_1 \neq b_2) \land (\Delta t = (I, a_1, a_2) > 0 \land \land (I, \langle a_1, b_1 \rangle, \langle a_2, b_1 \rangle) < 0) \land$

$\begin{array}{l} (b_1 \neq b_2) \ \land \ (\Delta_{hw_A}(I, a_1, a_2) > 0 \ \land \ \Delta(I, \langle a_1, b_1 \rangle, \langle a_2, b_1 \rangle) < 0) \ \land \\ (0 < \Delta_{hw_A}(I, a_3, a_4) < \Delta(I, \langle a_3, b_2 \rangle, \langle a_4, b_2 \rangle)), \end{array}$

$\begin{aligned} \forall a_1, a_2, a_3, a_4 \in A, \forall b \in B. \\ (\Delta_{hw_A}(I, a_1, a_2) > 0 \land \Delta(I, \langle a_1, b \rangle, \langle a_2, b \rangle) < 0 \land \Delta_{hw_A}(I, a_3, a_4) > 0) \rightarrow \\ (\Delta_{hw_A}(I, a_3, a_4) \ge \Delta(I, \langle a_3, b \rangle, \langle a_4, b \rangle)), \end{aligned}$

$\begin{aligned} \forall a_1, a_2, a_3, a_4 \in A, \forall b \in B. \\ (0 < \Delta_{hw_A}(I, a_1, a_2) < \Delta(I, \langle a_1, b \rangle, \langle a_2, b \rangle) \land \Delta_{hw_A}(I, a_3, a_4) > 0) \rightarrow \\ (\Delta_{hw_A}(I, \langle a_3, b \rangle, \langle a_4, b \rangle) \geq 0). \end{aligned}$

The first expression shows, that a *TA-P-I* anomaly for state  $b_1$  and a *TA-P-A* anomaly for the state  $b_2$  occur. And if there is a *TA-P-I* for one state b (in that case  $b_1$ ), then it is excluded, that a *TA-P-A* can emerge for the same state b (second expression). In the third term the opposite case is displayed; if a *TA-P-A* occur for b, then for this state a *TA-P-I* anomaly is precluded. In this case it is possible to provide a WCET bound, because with the delta composition TA-P-I and with the max composition TA-P-A timing anomalies could be analysed. If both techniques

are used concurrently and the maximum of the results is taken  $(T_{dmc})$ , then a precise bound can be given. Observe that  $T_{dmc}(I)$  overestimates the WCET, resulting from the delta composition.

**Definition 2.10.11**  $T_{dmc}(I) = max(T_{dc}(I), T_{mc}(I))$

If both types of timing anomalies can occur for the same state  $b \in B$ . Then an efficient calculation of a safe WCET bound is not possible and the whole state space  $A \times B$  must be analysed (proof is shown in [6]). This is named a coupled parallel timing anomaly (*TA-P-C*).

#### Definition 2.10.12 TA-P-C

Assume an instruction sequence I and a TRDCS initial state space, which is partitioned in two

non-empty sets  $A \cup B$  with the component latency  $T_{hw_A}(I, a)$  of hardware component  $hw_A$ and the overall execution time  $T(I, \langle a, b \rangle)$ , with  $a \in A, b \in B$ . Then coupled parallel timing anomaly occurs whene:

$\begin{aligned} \exists a_1, a_2, a_3, a_4 \in A, \exists b \in B. \\ (\Delta_{hw_A}(I, a_1, a_2) > 0 \land \Delta(I, \langle a_1, b \rangle, \langle a_2, b \rangle) < 0) \land \\ (0 < \Delta_{hw_A}(I, a_3, a_4) < \Delta(I, \langle a_3, b \rangle, \langle a_4, b \rangle)) \end{aligned}$

Parallel timing anomalies are studied between related hardware components, in this thesis the interaction between different pipeline and cache architectures are analysed in Chapter 7 of this thesis, where the effects of the execution of the cache influence the behaviour and timing of the pipeline timing.

# CHAPTER 3

# **Pipeline Architectures**

## 3.1 Overview

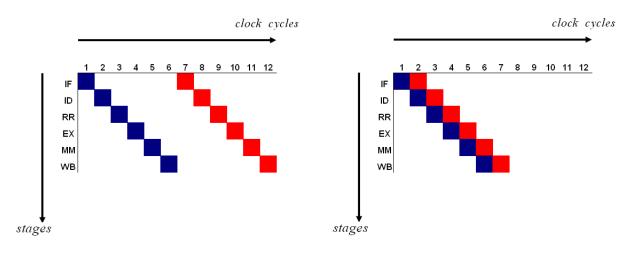

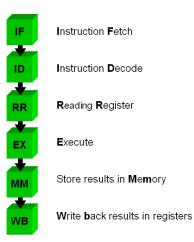

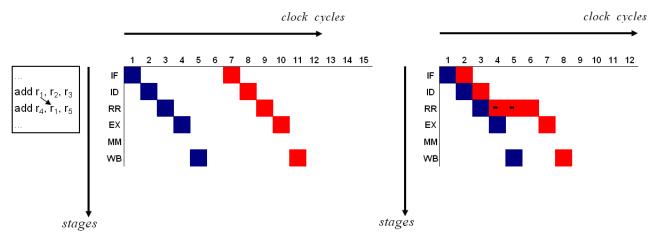

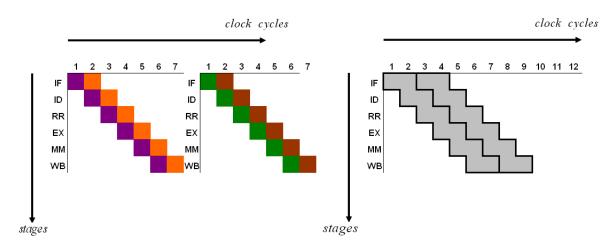

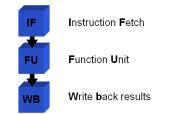

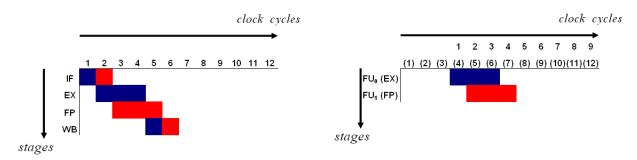

In early years computer processors commonly executed instructions successively usually in the following sense: fetching the instruction from the memory (IF), decoding it (ID), reading the operands for the instructions from the registers and memory (RR), executing the instruction (EX) and writing the results to the memory (MM) or the registers (WB). This strictly sequential execution is not very fast and it was improved in the way, that several instructions can now overlap. That means, the first instruction reads its operands, the second instruction can be decoded and the third instruction can be fetched in parallel. This concept increases the efficiency immense (see Figure 3.1).

The instructions pass through a number of stages. Naturally an instruction must not go through all pipeline stages. Additional there are several ways which stage an instruction can take. A stage can be occupied by only one instruction, and after a stage is entered by an instruction the appropriate step is processed and the instruction leaves the stage. However an instruction can occupy a stage for more than one clock cycle. The flow of instructions is from the upper left to the lower right corner, where the time scale is horizontal (divided in clock cycles) and the stages are displayed vertically.

## **3.2 Simple Scalar Pipelines**

A simple scalar pipeline is the simplest form of the presented pipelines. All stages are performed in an in-order manner. The number of stages in modern processors varies between three and ten, but in general there are five to seven stages. An example of a simple scalar pipeline is shown in Figure 3.2.

An execution of an instruction can be delayed in a pipeline stage by some reasons. In case of a *structural hazard* [16] a pipeline stage is blocked by an instruction and the next instruction is stalled during this time. On the left side of Figure 3.3 two instructions are shown, where the first

#### 3.2. SIMPLE SCALAR PIPELINES

Figure 3.1: Concept of Pipelines

instruction needs two clock cycles for the decode-stage and three clock cycles for reading the registers. The instructions are executed successively. On the right side the instructions overlap and thus the first instruction stalls the second instruction, which must pause in the *IF*- and *ID*-stage.

Another kind of delay can result from data dependencies. More precisely, when a preceding instruction generates some data, which is needed by the subsequent instruction and the generation is not complete until the next instruction is in the processing stage, then this next instruction is stalled. In the Figure 3.4 an example shows an execution of two instructions within a program, whereas on the left side the instructions are executed successively and on the right side the maximal overlap is shown.

The first instruction adds the content from registers  $r_2$  and  $r_3$  and writes the result to register  $r_1$ .

Figure 3.2: Simple Scalar Pipeline

#### CHAPTER 3. PIPELINE ARCHITECTURES

Figure 3.3: Structural Hazard

Thus this result in  $r_1$  is only available until termination in the *WB-stage*. The second instruction needs the content of the register  $r_1$  for a further addition, the second instruction is stalled in the RR-stage and waits until  $r_1$  can be read. Note that the *MM-stage* is not needed, because there is no memory access.

Figure 3.4: Data Hazard

In the following context of this thesis instructions can be combined into blocks. This is illustrated in Figure 3.5. Note that a single instruction could be also a block.

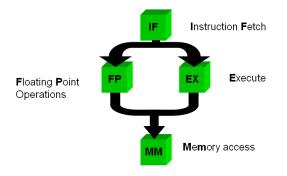

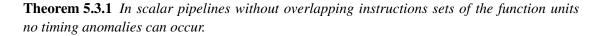

# 3.3 Scalar Pipelines

Within these pipelines the execution of an instruction can take different paths through the execution units of the processor. The decision which pipeline stages an instruction has to pass

#### 3.4. SUPERSCALAR IN-ORDER PIPELINES

Figure 3.5: Merged Instructions illustrated as Blocks

through depends on the type of the instruction. This concept is used to increase to efficiency of the pipeline. A well known case of application is the segregation of integer and floating-point operations. In Figure 3.6 an example of a scalar pipeline is illustrated. All instructions are executed in in-order.

Figure 3.6: Scalar Pipeline

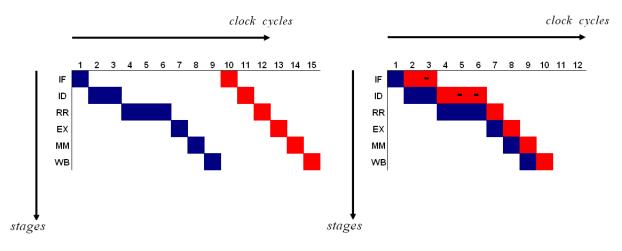

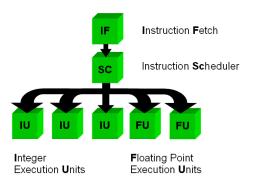

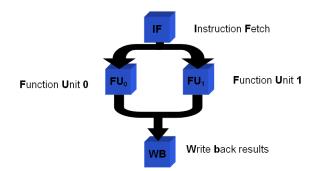

## 3.4 Superscalar In-Order Pipelines

Another more efficient pipeline is illustrated in Figure 3.7. In the *IF-stage* a number of instructions can be fetched within a clock cycle. The maximum number of instructions which are fetched in one clock cycle corresponds to the number of stages that can be executed in parallel. The *SC-stage* groups the previously fetched instructions and associates them with the subsequent stages, where the instructions are executed in-order. It is essential, that the instructions are scheduled statically, not dynamical, in the *SC-stage*.

#### CHAPTER 3. PIPELINE ARCHITECTURES

Figure 3.7: Superscalar In-Order Pipeline

#### 3.5 Superscalar Out-Of-Order Pipelines

In a superscalar out-of-order pipeline the selection of the processing instruction is done dynamically. This makes the pipeline more efficient, because the instructions can be scheduled so that delays by data dependencies and resource conflicts are reduced. In parallel the complexity of the pipeline and the function units increase. These pipelines are used for applications, where a high average-case performance is necessary, but the performance in the worst case is very hard to predict.

There exists also a distinction for superscalar out-of-order pipelines; instructions can be fetched and results written back in-order or out-of-order. If we consider in-order issue and in-order completion (IOI/IOC) pipelines, then we can observe that these pipelines are working in the same manner as superscalar in-order pipelines. In-order issue with out-of-order completion (IOI/OOC) pipelines are able to process the in-order fetched instructions and wrote back the results out-of-order.

To fetch and execute the instructions in an out-of-order manner an instruction buffer has to be added. This ensures the selection of instructions in a way, that the available resources are optimally occupied. Also this must procure, that the program behaviour and data dependencies are not affected. Thus the superscalar pipeline is perfectly utilised. The concept of processing instructions in OOI/OOC pipelines is shown in the a resource allocation Table 3.1.

#### 3.5. SUPERSCALAR OUT-OF-ORDER PIPELINES

| Instruction    | Unit | Cycles | Data Dep.             |

|----------------|------|--------|-----------------------|

| I <sub>0</sub> | IU   | 1      |                       |

| I <sub>1</sub> | IU   | 2      |                       |

| <b>I</b> 2     | IU   | 3      | before I <sub>3</sub> |

| 3              | FU   | 1      | after I <sub>2</sub>  |

| I4             | FU   | 2      | before I <sub>5</sub> |

| 5              | FU   | 2      | after I4              |

| I <sub>6</sub> | FU   | 1      |                       |

| I <sub>7</sub> | IU   | 2      |                       |

| I <sub>8</sub> | IU   | 2      |                       |

| <b>I</b> 9     | FU   | 2      |                       |

| Clock Cycle | Dispa          | tcher          |                | Bu             | ffer           |                | IU             | IU             | FU             | FU             | FU             | WB             | WB             | WB             |

|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1           | I <sub>0</sub> | l <sub>1</sub> |                |                |                |                |                |                |                |                |                |                |                |                |

| 2           | 2              | I <sub>3</sub> | l <sub>0</sub> | l <sub>1</sub> |                |                | I <sub>0</sub> | I <sub>1</sub> |                |                |                |                |                |                |

| 3           | 4              | <b>I</b> 5     | 2              | <b>I</b> 3     |                |                | l <sub>2</sub> | I <sub>1</sub> |                |                |                | I <sub>0</sub> |                |                |

| 4           | 6              | <b>I</b> 7     | <b>I</b> 3     | I4             | <b>I</b> 5     |                | <b>I</b> 2     |                | 4              |                |                | I <sub>1</sub> |                |                |

| 5           | <b>I</b> 8     | l <sub>9</sub> | <b>I</b> 3     | <b>I</b> 5     | I <sub>6</sub> | I <sub>7</sub> | l <sub>2</sub> | I <sub>7</sub> | 4              | 6              |                |                |                |                |

| 6           |                |                | <b>I</b> 3     | <b>I</b> 5     | <b>I</b> 8     | l <sub>9</sub> | I <sub>8</sub> | I <sub>7</sub> | I <sub>3</sub> | I <sub>5</sub> | l <sub>9</sub> | <b>1</b> 2     | I4             | <b>I</b> 6     |

| 7           |                |                |                |                |                |                | I <sub>8</sub> |                |                | I <sub>5</sub> | l <sub>9</sub> | I <sub>7</sub> | I <sub>3</sub> |                |

| 8           |                |                |                |                |                |                |                |                |                |                |                | I <sub>5</sub> | <b>I</b> 8     | l <sub>9</sub> |

Table 3.1: Superscalar Out-Of-Order Pipeline: Resource Allocation Table

## CHAPTER 4

### **Cache Architectures**

#### 4.1 Overview

Because storage elements have a large access times, buffer elements (caches) are placed between the main storage elements and the CPU. Caches contain copies of required data, therewith it is possible to provide that data faster for future requests. If some data is needed, then an enquiry on the caches is raised. If the cache contains the requested data, then this situation is called a *cache hit* and the data is provided. If the requested data is not part of the cache storage, this situation is called a *cache miss*. The required data is fetched from the main storage element (which takes some time) and it is saved for future requests. The *cache replacement strategy* decides which cache block is being replaced if new data must be stored in the cache. In the next sections several strategies are presented and discussed. With the may and must analysis [10] [7] the knowledge of the contained cache blocks can be done. Some cache replacement policies, which are responsible for the appearance of timing anomalies, are explored in [11] by Reineke et al. For serious WCET calculations we need a prediction if a cache hit or cache miss causes timing anomalies (and which timing anomalies) or not. This issue and an analysis of different replacement strategies are explored in detail in the next chapters.

#### 4.2 Structure of Caches

Caches are segmented into rows and each row consists of a cache line, which includes the required data memory blocks with *b* bytes. A *valid bit* indicates if a row contains valid data. The address is split into an index (with length of  $\lceil log_2(numberofcacherows) \rceil$ ), which indicates the row of the main memory, an offset (with length of  $\lceil log_2(numberofdatablocks) \rceil$ ), which shows the especially block in the cache line and an tag (with length of totaladdresslength - indexlength - offsetlength) and comprises the MSBs of the main memory address. The length of a data block with *b* bytes times the total number of cache lines *l* indicates the cache size *s*.

#### 4.3 Associativity

The associativity (number of cache lines within one set) k can be computed by the number of cache lines l divided by the number of sets. In *fully-associative* caches (k = l) there is only one set with all l cache lines in it [15]. Each data block can contain each data from the main memory. In case of a cache request it is necessary to check all tags; this makes only sense if small caches are used.

In case of *direct-mapped* caches (k = 1) every cache line represents a set. Thereby every cache block is directly mapped to data of the main memory and only this line has to be checked in case of a request. Thus this is the best choice if large cache sizes are available.

If k > 1, then a replacement strategy selects the cache line in the set, which should be updated. This should be done with the focus on decreasing the number of cache misses.

#### 4.4 Cache Replacement Policies

#### FIFO

With the first-in first-out replacement strategy the cache uses only one pointer, which increases its value sequentially modulo the sum of cache pages to select a cache line for updating. The entries are saved in the order they were loaded. Thus this strategy is relative simple and easy to understand. If some data is added to the last cache line, then afterwards the pointer has the value zero and points to the first cache line. This strategy has a constant access time regardless of the cache size.

#### Least Recently Used

This strategy updates the least recently used cache line, if the cache is full and a cache miss appears. It requires a tracking of the *age* of cache lines. This can be done by several implementations. To abstract the cache as a linked list is one realization. A referenced page is put to the head of the list. If a new element has to be saved, this element is added on the new head of the list and the oldest page (tail of the list) is ejected.

In another method the *ages* of cache lines are tracked. In a k-way associative LRU cache the most recently used line has the age 0 and the least recently used the age k - 1. In a cache miss situation the line with the age k - 1 is ejected and then the line, which contains the new data, gets the age 0 and all other increase their ages by 1. If a line of age a is accessed, then the age of the this page is set to 0 and the lines of age 0 to a - 1 increase their ages by 1. An example is shown in Table 4.1 for a 4-way LRU cache. Note that least recently used caches with greater than 4-way associativity are uncommon.

#### **Pseudo Least Recently Used**

The pseudo least recently used cache replacement strategy is using a tree-based approach for the replacing within a cache set. The average-case performance is comparable with LRU, nevertheless the worst-case performance is worse. It needs a less complex update logic. The constructed

#### CHAPTER 4. CACHE ARCHITECTURES

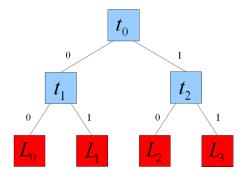

tree in 4-way PLRU caches consists of inner nodes, which contain state bits  $t_0$  to  $t_{k-2}$  (for a k-way PLRU cache). The content of the leafs  $L_0$  to  $L_k$  of the constructed tree include the data. The content of the inner nodes are state bits  $t_0$  to  $t_{k-2}$  (for a k-way PLRU cache), which point to the subtrees of them (in our case 0 to the left and 1 to the right subtree). Thereby it is possible to build a path from the root to every leaf. In case of a cache miss the content of the leaf, with the state bits of the tree pointing to it, is updated with the new one and this state bits are flipped. In case of a cache hit, the state bits to the accessed content are changed in that way that they are pointing away from this most recently used content. In practice 8-way PLRU is common (same update logic, but 7 state bits) and a 2-way PRLU equals a 2-way LRU. In Figure 4.1 the tree-based approach for the PLRU strategy for a 4-way PRLU is shown. An update example is shown in Table 4.2.

Figure 4.1: 4-way PLRU Tree

|                |          | Ages           |                |                |                |  |

|----------------|----------|----------------|----------------|----------------|----------------|--|

| Accesses       | hit/miss | 0              | 1              | 2              | 3              |  |

| Mo             | miss     | Mo             |                |                |                |  |

| M <sub>1</sub> | miss     | M <sub>1</sub> | Mo             |                |                |  |

| M <sub>2</sub> | miss     | M <sub>2</sub> | M <sub>1</sub> | Mo             |                |  |

| M <sub>3</sub> | miss     | M <sub>3</sub> | M <sub>2</sub> | M <sub>1</sub> | Mo             |  |

| $M_2$          | hit      | M <sub>2</sub> | M <sub>3</sub> | M <sub>1</sub> | Mo             |  |

| $M_4$          | miss     | M4             | M <sub>2</sub> | M <sub>3</sub> | M <sub>1</sub> |  |

| M <sub>1</sub> | hit      | M <sub>1</sub> | M <sub>4</sub> | M <sub>2</sub> | M <sub>3</sub> |  |

| $M_2$          | hit      | M <sub>2</sub> | M <sub>1</sub> | M <sub>4</sub> | M <sub>3</sub> |  |

| $M_5$          | miss     | M <sub>5</sub> | M <sub>2</sub> | M <sub>1</sub> | M <sub>4</sub> |  |

| M <sub>6</sub> | miss     | M <sub>6</sub> | M <sub>5</sub> | M <sub>2</sub> | M <sub>1</sub> |  |

| M <sub>7</sub> | miss     | M <sub>7</sub> | M <sub>6</sub> | M <sub>5</sub> | M <sub>2</sub> |  |

| M <sub>2</sub> | hit      | M <sub>2</sub> | M7             | M <sub>6</sub> | M <sub>5</sub> |  |

Table 4.1: 4-way LRU cache: Filling with Age Update

#### 4.4. CACHE REPLACEMENT POLICIES

|                |          | State Bits     |                |                | Content        |                |                |                |

|----------------|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Accesses       | hit/miss | t <sub>0</sub> | t <sub>1</sub> | t <sub>2</sub> | Lo             | L <sub>1</sub> | L <sub>2</sub> | L <sub>3</sub> |

|                |          | 0              | 0              | 0              |                |                |                |                |

| Mo             | miss     | 1              | 1              | 0              | Mo             |                |                |                |

| M <sub>1</sub> | miss     | 0              | 1              | 1              | Mo             |                | M <sub>1</sub> |                |

| M <sub>2</sub> | miss     | 1              | 0              | 1              | Mo             | M <sub>2</sub> | M <sub>1</sub> |                |

| M <sub>3</sub> | miss     | 0              | 0              | 0              | Mo             | M <sub>2</sub> | M <sub>1</sub> | M <sub>3</sub> |

| M <sub>2</sub> | hit      | 1              | 0              | 0              | Mo             | M <sub>2</sub> | M <sub>1</sub> | M <sub>3</sub> |

| $M_4$          | miss     | 0              | 0              | 1              | Mo             | M <sub>2</sub> | M4             | M <sub>3</sub> |

| M <sub>1</sub> | miss     | 1              | 1              | 1              | M <sub>1</sub> | M <sub>2</sub> | M4             | M <sub>3</sub> |