# DIPLOMARBEIT

# Aufbau, Test und Automatisierung einer Kontrollelektronik für magnetische Wanderwellenresonatoren zur Manipulation polarisierter Neutronenstrahlen

ausgeführt unter der Leitung von

Em. Univ.-Prof. Dipl.-Ing. Dr.techn. Gerald Badurek Ass. Prof. Dipl.-Ing. Dr.techn. Erwin Jericha Atominstitut, e141

eingereicht an der Technischen Universität Wien Fakultät für Physik

von

Patrick Reisinger, BSc Matrikelnummer 01607394 patrick.reisinger@gmx.at

Wien, am 20. Februar 2023

| (Unterschrift Verfasser) | (Unterschrift Betreuer) |

|--------------------------|-------------------------|

# Kurzfassung

Polarisierte Neutronenstrahlen können durch spezielle räumliche Magnetfeldverteilungen nach ihren spektralen Eigenschaften manipuliert und in ihrer zeitlichen Struktur beeinflusst werden. Auf dieser Tatsache beruht das Konzept von magnetischen Spinresonatoren für Neutronen, in denen für eine Resonanzwellenlänge eine Inversion der Neutronenpolarisation erreicht werden kann. Durch die Verwendung von individuell steuerbaren Resonatorelementen kann dabei eine größtmögliche Flexibilität in der Formung von Neutronenstrahlen erreicht werden. Eine aktuelle Entwicklung ist eng in das Neutronenzerfallsprojekt PERC integriert, das sich zur Zeit an der Forschungsneutronenquelle FRM II, in Garching bei München, in Entwicklung befindet.

Das Kernstück des Neutronenresonators ist eine eigens am Atominstitut entwickelte, schnell schaltbare Hochstromquelle, die für jedes Resonatorelement den erforderlichen Strom für die Erzeugung des Magnetfeldes im erforderlichen Zeitraum, der von Mikrosekunden bis zu Tagen dauern kann, zur Verfügung stellt. In dieser Diplomarbeit wurden solche Stromquellen in ein Gesamtsystem für bis zu 48 Resonatorelemente integriert. Dies beinhaltete, neben der Beseitigung bestehender Hardwareprobleme, die Entwicklung einer Software zur individuellen Kommunikation mit jeder Stromquelle, wodurch der Resonator automatisiert und flexibel kontrolliert werden kann.

Mittelfristiges Ziel, über diese Arbeit hinaus, sind Experimente mit dem Resonator an einem weißen thermischen Neutronenstrahl am TRIGA-Reaktor des Atominstituts der TU Wien in seinen verschiedenen Betriebsarten, wie stationärem Betrieb oder Wanderwellenmodus. Die experimentellen Parameter werden sich dabei an den Charakteristika thermischer Neutronenstrahlen sowie an den speziellen Anforderungen des PERC-Projekts mit kalten Neutronenstrahlen orientieren.

# Abstract

Polarized neutron beams can be manipulated and influenced in their temporal structure based on their spectral properties using spatial magnetic field distributions. This concept is the basis for magnetic spin resonators for neutrons, in which an inversion of the neutron polarization can be achieved for a certain resonance wavelength. The use of individually controllable resonator elements allows for maximum flexibility in shaping the neutron beams. A current development is closely integrated into the neutron decay project PERC, which is currently under development at the Research Neutron Source FRM II in Garching near Munich.

The core of the neutron resonator is a high-current source developed specifically at the Atominstitut of the TU Wien, which can quickly switch and provide the necessary current for generating the magnetic fields. The achievable time frame of the source can vary between microseconds up to days for each resonator element. In this thesis, such current sources were integrated into a system for up to 48 resonator elements. This included resolving existing hardware problems as well as developing a software for individual communication with each current source, allowing the resonator to be controlled flexibly.

The medium-term goal beyond this work is to conduct experiments with the resonator on a white thermal neutron beam at the TRIGA reactor of the Atominstitut in its various operating modes, such as stationary operation or traveling wave mode. The experimental parameters will be based on the characteristics of thermal neutron beams and the specific requirements of the PERC project with cold neutron beams.

# TU Sibliothek, Die approbierte gedruckte Originalversion dieser Diplomarbeit ist an der TU Wien Bibliothek verfügbar werk vour knowledge hub The approved original version of this thesis is available in print at TU Wien Bibliothek.

# Inhaltsverzeichnis

| Κι | ırzta       | ssung                                         |                                         | 11  |  |  |  |  |  |  |  |

|----|-------------|-----------------------------------------------|-----------------------------------------|-----|--|--|--|--|--|--|--|

| Al | ostra       | $\mathbf{ct}$                                 |                                         | iii |  |  |  |  |  |  |  |

| 1  | Einl<br>1.1 | nleitung<br>Aufbau- und Funktionsbeschreibung |                                         |     |  |  |  |  |  |  |  |

| 2  | Gru         | rundlagen                                     |                                         |     |  |  |  |  |  |  |  |

|    | 2.1         | Überti                                        | ragungsprotokolle                       | 5   |  |  |  |  |  |  |  |

|    |             | 2.1.1                                         | $	ext{I}^2	ext{C-Bus}$                  | 5   |  |  |  |  |  |  |  |

|    |             | 2.1.2                                         | UART                                    | 7   |  |  |  |  |  |  |  |

|    | 2.2         | Signal                                        | verarbeitung und -übertragung           | 8   |  |  |  |  |  |  |  |

|    |             | 2.2.1                                         | A/D- und D/A-Wandler                    | 8   |  |  |  |  |  |  |  |

|    |             | 2.2.2                                         | Hall-Sensor                             | 9   |  |  |  |  |  |  |  |

|    |             | 2.2.3                                         | Vierleitermessmethode                   | 9   |  |  |  |  |  |  |  |

|    |             | 2.2.4                                         | Koaxialkabel                            | 11  |  |  |  |  |  |  |  |

|    | 2.3         | Elektr                                        | onische Schaltwerke                     | 13  |  |  |  |  |  |  |  |

|    |             | 2.3.1                                         | Schieberegister (SR)                    | 13  |  |  |  |  |  |  |  |

| 3  | Har         | dware                                         |                                         | 14  |  |  |  |  |  |  |  |

|    | 3.1         | Platin                                        | en                                      | 14  |  |  |  |  |  |  |  |

|    |             | 3.1.1                                         | Steuerplatinen (SP)                     | 15  |  |  |  |  |  |  |  |

|    |             | 3.1.2                                         | Backplane (BP)                          | 16  |  |  |  |  |  |  |  |

|    |             | 3.1.3                                         | Stromquellen-Segmente                   | 16  |  |  |  |  |  |  |  |

|    |             | 3.1.4                                         | Platinen der Artificial- und Real-Last  | 18  |  |  |  |  |  |  |  |

|    |             | 3.1.5                                         | Trigger-Platine                         | 19  |  |  |  |  |  |  |  |

|    | 3.2         | Mikro                                         | controller ( $\mu$ C)                   | 19  |  |  |  |  |  |  |  |

|    | 3.3         | CPLD                                          |                                         | 22  |  |  |  |  |  |  |  |

|    |             | 3.3.1                                         | CPLDs im MONOPOL                        | 23  |  |  |  |  |  |  |  |

|    | 3.4         | $I^2C$ -Ba                                    | austeine                                | 25  |  |  |  |  |  |  |  |

|    |             | 3.4.1                                         | FRAM                                    | 26  |  |  |  |  |  |  |  |

|    |             | 3.4.2                                         | Temperatursensor (TMP101)               | 26  |  |  |  |  |  |  |  |

|    |             | 3.4.3                                         | Digital-Analog Konverter (LTH2631-LM12) | 26  |  |  |  |  |  |  |  |

|    |             | 3.4.4                                         | ADCs                                    | 28  |  |  |  |  |  |  |  |

|    |             | 3.4.5                                         | I/O-Extender                            | 32  |  |  |  |  |  |  |  |

|    |             |                                               |                                         |     |  |  |  |  |  |  |  |

|                        | 3.5   |                                                     | 33         |

|------------------------|-------|-----------------------------------------------------|------------|

|                        |       |                                                     | 33         |

|                        |       |                                                     | 34         |

|                        |       |                                                     | 35         |

|                        |       | 3.5.4 DC/DC-Konverter (5V)                          | 36         |

| 4                      | Soft  | wareübersicht 3                                     | 37         |

|                        | 4.1   | User-Interface                                      | 37         |

|                        | 4.2   |                                                     | 37         |

|                        | 4.3   | Mikrocontroller-Toolchain                           | 38         |

| 5                      | Soft  | ware der Ablaufsteuerung                            | 39         |

|                        | 5.1   | <u>e</u>                                            | 39         |

|                        |       | O v                                                 | 11         |

|                        |       |                                                     | <br>13     |

|                        |       |                                                     | 13         |

|                        | 5.2   |                                                     | $15 \\ 15$ |

|                        | 0.2   | 1                                                   | 17         |

|                        |       |                                                     | ±ι<br>51   |

|                        | E 9   |                                                     | 51<br>52   |

|                        | 5.3   |                                                     | 52<br>52   |

|                        |       |                                                     |            |

|                        |       |                                                     | 54         |

|                        |       | 0 /                                                 | 56         |

|                        | ٠.    | 00                                                  | 59         |

|                        | 5.4   | Software zur Überprüfung der Stromquellen-Segmente  | 60         |

| 6                      | Tes   | , r                                                 | 3          |

|                        | 6.1   | 1 0                                                 | 33         |

|                        | 6.2   | 1 0                                                 | 33         |

|                        |       | 6.2.1 Charakterisierung der $z/I$ -Kurve der DACs 6 | 33         |

|                        |       | 6.2.2 Minimale Schiebeperiode                       | 71         |

|                        | 6.3   | Gesamtsystemtests                                   | 73         |

|                        | 6.4   | TWM-Parameter für eine Wellenlänge von $5\text{Å}$  | 74         |

| 7                      | Zus   | ammenfassung und Ausblick 7                         | <b>7</b> 6 |

|                        | 7.1   | Durchgeführte Arbeiten                              | 76         |

|                        | 7.2   | Geplante Erweiterungen und Arbeiten                 | 77         |

|                        | 7.3   | -                                                   | 78         |

| A۱                     | bbild | ungsverzeichnis 8                                   | 30         |

| Та                     | belle | enverzeichnis 8                                     | 32         |

|                        |       |                                                     |            |

| $\mathbf{L}\mathbf{l}$ | terat | urverzeichnis                                       | 33         |

# Einleitung

Diese Arbeit beschäftigt sich mit der Steuerungselektronik des MONOPOLs, ein magnetischer Badurek-Wanderwellenresonator zur Erzeugung monochromatischer Neutronenstrahlen. Strahlen dieser Art kommen in vielen physikalischen Experimenten zum Einsatz, zum Beispiel dem PERC-Experiment (Proton Electron Radiation Channel) [1–3].Der Wanderwellenresonator bietet im Vergleich zu herkömmlichen Methoden viele Vorteile. So kann die Wellenlängenselektion im Vergleich zu Choppern und kristallinen Monochromatoren, welche kurz vorgestellt werden, ohne jegliche mechanischen Eingriffe rein durch Ändern von Magnetfeldern vorgenommen werden.

Ein Chopper besteht aus einer rotierenden Scheibe, welche aus einem Neutronenabsorber gefertigt ist und eine oder mehrere Öffnungen aufweist. Diese Öffnungen führen dazu, dass ein auf den Chopper gerichteter Neutronenstrahl durch periodisches Unterbrechen in Pakete unterteilt wird. Ein inhärenter Nachteil von Choppern ist der Neutronenverlust, da die meiste Zeit der absorbierende Teil der Scheibe im Strahl steht.

Die Wellenlängenselektion mittels Chopper kann auf zwei verschiedene Arten realisiert werden. Einerseits kann man statt der Scheibe eine rotierende Walze verwenden. Die zuvor beschriebenen Offnungen sind nun ein in die Walze eingebrachter Kanal, welcher im Ruhesystem der Neutronen mit gewünschter Geschwindigkeit (Selektion durch Rotationsfrequenz) ein passierbarer Tunnel ist. Andererseits können zwei drehzahlidente Scheiben-Chopper mit einem definierten Abstand hintereinander platziert werden, wodurch ebenfalls nach Geschwindigkeit gefiltert werden kann [4, Abschnitt 13.3].

Kristalline Monochromatore nutzen die Bragg-Bedingung aus, um eine Wellenlängenselektion zu erreichen. Will man die Wellenlänge ändern muss jedoch der gesamte Aufbau gedreht und gegebenenfalls der verwendete Kristall getauscht werden [5, Abschnitt 11.3].

Erstmals wurde die Wellenlängenselektion mittels magnetischer Felder von Drabkin [6] im Jahre 1963 vorgeschlagen und von Badurek und Jericha [7] in das im MONOPOL zur Anwendung kommende Konzept ausgereift.

Der MONOPOL-Resonator bietet drei unterschiedliche Betriebsmodi, welche individuell konfiguriert werden können. Dabei kann neben der Wellenlänge auch die Pulsdauer angepasst werden. Ihr unteres Limit ist durch die Schaltzeiten der Resonatorspulen begrenzt.

Die vorliegende Diplomarbeit beschäftigt sich mit der softwareseitigen Implementierung der drei Betriebsmodi, welche durch die Neutronengeschwindigkeiten strenge zeitkritische Anforderungen erfüllen muss. Zusätzlich zur physikalischen Funktionalität wird ein Interface zur Verfügung gestellt, um mit der Resonator-Ablaufsteuerung über einen PC zu kommunizieren. Neben der Softwareerstellung wurden diverse Hardwareprobleme detektiert und weitestgehend auch behoben. Details dazu sind in Kapitel 6 ausgeführt.

# Aufbau- und Funktionsbeschreibung

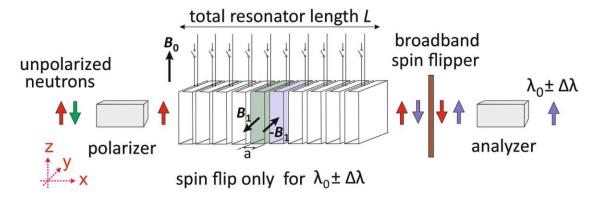

Der Badurek-Wanderwellenresonator nutzt zur Wellenlängenselektion das anomale magnetische Moment der Neutronen. Der prinzipielle Aufbau ist in Abb. 1.1 zu

Ein unpolarisierter polychromatischer Neutronenstrahl wird zunächst durch einen Superspiegel polarisiert. Anschließend durchqueren die Neutronen den Resonator, bestehend aus 48 Aluminium-Spulen. In diesem Resonator herrscht einerseits das Führungs-Magnetfeld  $B_0$ , auch Selektorfeld genannt, andererseits erzeugen die Spulen ein Magnetfeld  $B_1(x)$ . Beide Felder stehen üblicherweise normal aufeinander und es gilt  $B_0 >> B_1$ . Die Neutronen führen aufgrund des resultierenden Magnetfelds, welches wie  $B_0$  und  $B_1$  transversal zur Strahlrichtung steht (Abb. 1.1), eine Larmorpräzession durch. Wird  $B_1(x)$  so gewählt, dass die Frequenz des Magnetfelds im Ruhesystem der Neutronen mit der Larmorfrequenz übereinstimmt und die Amplitudenbedingung

$$\frac{B_1}{B_0} \cdot \frac{L}{2a} = (2k+1)\frac{\pi}{4}, \qquad k = 0, 1, 2, ...$$

(1.1)

erfüllt ist  $(2k+1 \dots \text{Anzahl der Spinflips})$ , kann die Spinflipwahrscheinlichkeit

$$W(\lambda) = \frac{\xi^2}{(\Delta \lambda/\lambda)^2 + \xi^2} \cdot \sin^2 \left[ \frac{\pi L \lambda}{2a\lambda_0} \sqrt{(\Delta \lambda/\lambda)^2 + \xi^2} \right], \tag{1.2}$$

mit

$$\xi = \frac{2B_1}{\pi B_0},\tag{1.3}$$

$$\Delta \lambda = \lambda - \lambda_0. \tag{1.4}$$

angegeben werden  $(L \dots L"ange, 2a \dots Periode des Resonators)$  [8].

$$\lambda_0 = \frac{\pi h}{am|\gamma|B_0} \tag{1.5}$$

ist dabei die Resonanzwellenlänge, welche von Naturkonstanten (h ... Plank'sches Wirkungsquantum, m ... Neutronenmasse,  $\gamma$  ... gyromagnetisches Verhältnis), dem Selektorfeld  $B_0$  und via a von der Geometrie des Resonators abhängt.

Die maximale Wellenlängenauflösung erhält man, wenn k=0 gilt und die Anzahl der Resonatorperioden  $N = \frac{L}{2a}$  maximiert wird

$$\frac{\Delta \lambda_{1/2}}{\lambda_0} \simeq \frac{0.8}{N} \tag{1.6}$$

mit der Halbwertsbreite (FWHM)  $\Delta\lambda_{1/2}$  des globalen Maximums der Spinflipwahrscheinlichkeit Gl. (1.2).

Nach Durchquerung des Resonators werden die Neutronenspins durch einen breitbandigen Stromblatt-Flipper umgekehrt. Ein darauffolgender Analyzer lässt nur jene Neutronen passieren, welche zuvor im Resonator einen Spinflip erfahren haben, also jene Neutronen im Bereich der Resonanzwellenlänge  $\lambda_0$  [9].

Abbildung 1.1: Schematische Darstellung eines Badurek-Wanderwellenresonators (Bild aus [9])

## Betriebsmodi

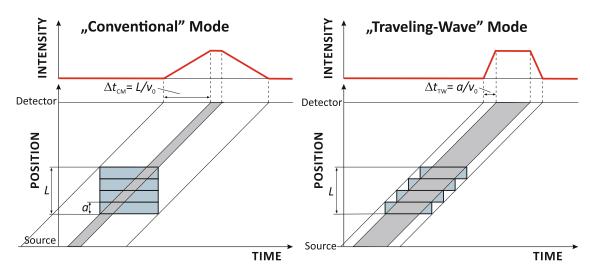

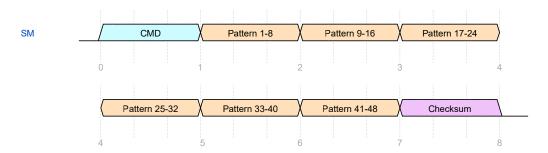

Die drei unterschiedlichen Betriebsmodi des Wanderwellenresonators sind der Static Mode (SM), der Conventional Mode (CM) und der Traveling Wave Mode (TWM). Im Vergleich zum SM können die beiden anderen Modi zusätzlich zur Wellenlängenselektion auch zur Pulsgenerierung verwendet werden. Dies wird durch gezieltes Ein- und Ausschalten der Resonatorspulen erreicht. Der Unterschied zwischen CM und TWM besteht darin, dass im TWM alle 48 im MONOPOL vorkommenden Spulen individuell geschaltet werden können. Die Neutronen werden quasi von den Magnetfeldern durch den Resonator "begleitet". Diese technische Erweiterung erlaubt dem Badurek-Resonator im optimalen Fall die Reduzierung der minimalen Puls-Anstiegs- und -Fallzeit von  $\Delta t_{CM,min} = L/v_0$  auf  $\Delta t_{TWM,min} = a/v_0$  (veranschaulicht in Abb. 1.2), also in diesem Fall  $\frac{1}{48}$ -stel eines herkömmlichen Drabkin-Resonators.

Abbildung 1.2: Vergleich des Zeitverhaltens von CM und TWM (Bild aus [9])

# Ansteuerungskonzept

Die elektronische Steuerung hat zwei Hauptaufgaben zu erfüllen. Einerseits muss die Stromstärke der einzelnen Resonatorspulen und damit die Amplitude der Magnetfelder eingestellt werden. Andererseits müssen die Ströme gezielt ein- und ausgeschaltet werden.

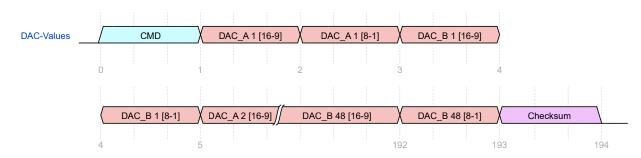

Um diese Aufgaben zu erfüllen, wurde in [10] ein Konzept entwickelt, welches hier kurz beschrieben wird. Der Benutzer stellt über eine GUI die gewünschte Wellenlänge, die Pulsdauer sowie weitere Parameter ein. Die PC-Software ermittelt daraus die Betriebsparameter der Ablaufsteuerung und übermittelt diese an einen Mikrocontroller via UART (Abschnitt 2.1.2). Der Controller konfiguriert daraufhin die Stromquellen mit den gewünschten Stromstärken über DACs.

Nun kann der Einschaltvorgang begonnen werden. Um Spannungsspitzen zu vermeiden, wurde das Konzept einer Artificial- und Real-Last eingeführt, welche beide in etwa den gleichen ohmschen Widerstand aufweisen und pro Stromquelle ausgeführt sind. Dabei wird zuerst der Strom über die Artificial-Last geführt bis sich Stabilität einstellt. Anschließend wird der Strom über die Real-Last geleitet, wobei kurzzeitig beide Lasten aktiv sind (=Glitch). Der Ausschaltvorgang erfolgt analog in umgekehrter Reihenfolge. Die Schaltvorgänge werden über Schieberegister so definiert, dass sich das vom Benutzer gewünschte Zeitverhalten einstellt und der Neutronenstrahl dadurch monochromatisiert und gegebenenfalls gepulst wird.

# Grundlagen

In diesem Kapitel werden die notwendigen Grundlagen der MONOPOL-Elektronik dargelegt. Dies beinhaltet sowohl technische Details wie Übertragungsprotokolle, als auch relevante physikalische und messtechnische Grundlagen und Konzepte.

# 2.1 Übertragungsprotokolle

# $2.1.1 I^2C$ -Bus

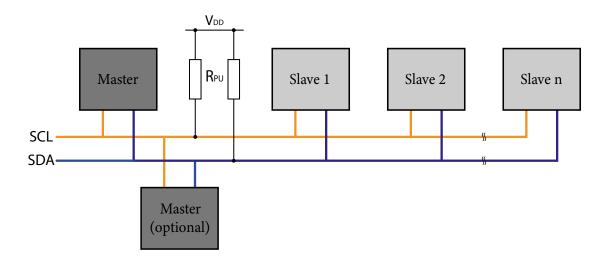

Der I<sup>2</sup>C-Bus (Inter-Integrated Circuit) [11] wurde von Philips entwickelt und ist ein serieller Bus. Er basiert auf dem Master-Slave Prinzip und kann von einem oder mehreren Mastern gesteuert werden.

Jedem Gerät im Busnetzwerk, beziehungsweise Slave in Singlemaster-Systemen, muss eine eindeutige Adresse zugeordnet sein. Sie kann entweder aus 8 bit (7 bit + R/W) oder 10 bit bestehen. Meist setzt sich die Adresse aus einem vom Chiphersteller und einem über Pins konfigurierbaren Teil zusammen. So wird sichergestellt, dass mehrere baugleiche ICs (=Integrated Circuit) in einem Netzwerk adressiert werden können.

Die theoretische Obergrenze für die Anzahl der angeschlossenen Bausteine ergibt sich durch die limitierte Anzahl an Adressen, in der Praxis muss jedoch auf die kapazitive Last geachtet werden. Spezielle I<sup>2</sup>C-Erweiterungen (Repeater, Hubs, Multiplexer und Switches) können das Netzwerk in mehrere Subnetze unterteilen und gezielt ansprechen. Dies verhindert einerseits die kapazitive Überbelastung, andererseits können so auch Adresskonflikte aufgelöst werden. Die Busteilnehmer merken von dieser Unterteilung nichts, die Adressierung erfolgt wie gehabt.

Der I<sup>2</sup>C-Bus kann je nach angeschlossener Peripherie mit unterschiedlichen Übertragungsraten betrieben werden. Eine Zusammenfassung ist in Tab. 2.1 zu finden, wobei die jeweiligen Obergrenzen angegeben sind. Sollte die Taktfrequenz zu hoch für die adressierten Bausteine sein, können diese den Takt verlangsamen und dadurch eine korrekte Übertragung sicherstellen.

| Bezeichnung         | $\mid \ddot{U}bertragungsrate$ |

|---------------------|--------------------------------|

| Standard Mode       | $< 100\mathrm{kbit/s}$         |

| Fast Mode           | $< 400\mathrm{kbit/s}$         |

| Fast Mode Plus      | $< 1  \mathrm{Mbit/s}$         |

| High Speed Mode     | $< 3.4\mathrm{Mbit/s}$         |

| $Ultra Fast Mode^1$ | m < 5Mbit/s                    |

<sup>&</sup>lt;sup>1</sup> nur unidirektional verwendbar

Tabelle 2.1: I<sup>2</sup>C-Bus Übertragungsmodi [11]

# Aufbau und Übertragungsablauf

Der physikalische Aufbau des Bussystems besteht aus zwei Leitungen, der Taktleitung SCL und der Datenleitung SDA. Alle Teilnehmer, sowohl alle Master als auch alle Slaves müssen an diese angeschlossen werden (Abb. 2.1).

Abbildung 2.1: Schematische Darstellung eines l<sup>2</sup>C-Bussystems mit R<sub>PU</sub> ... Pull-Up Widerstände, V<sub>DD</sub> ... Versorgungsspannung

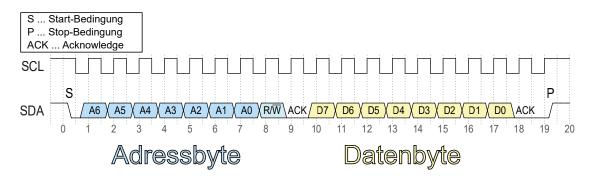

In Abb. 2.2 ist eine Veranschaulichung des I<sup>2</sup>C-Übertragungsprotokolls zu sehen. Findet keine Übertragung statt ist der Bus frei und befindet sich im Idle-Zustand (SCL = SDA = High). Dieser besteht bis ein Master den Beginn einer Übertragung durch das Einleiten einer Start-Bedingung signalisiert.

Die Start-Bedingung besteht aus einem High-Low-Ubergang der Datenleitung SDA während die Taktleitung SCL auf High bleibt. Nun legt der Master das Adressbyte auf den Bus, wobei das Least Significant Bit (LSB) angibt, ob der Master Daten empfangen ( $R/\overline{W} = Low$ ) oder senden ( $R/\overline{W} = High$ ) will. Das Adressbyte wird von allen Teilnehmern mit ihrer individuellen Adresse abgeglichen und der Adressat bestätigt im 9. Taktzyklus, indem er die Datenleitung SDA auf Low zieht  $(= ACK \dots Acknowledge).$

Jetzt kann der eigentliche Datenaustausch stattfinden. Der Master gibt den Takt auf SCL vor, der Slave kann den Low-Pegel des Takts verlängern und dadurch die Ubertragungsrate anpassen [12, Abschnitt 8.6]. Auf der Datenleitung überträgt je nach zuvor adressiertem Modus entweder der Master oder der Slave. Der Empfänger bestätigt nach Erhalt des Bytes mit einem ACK. Byteweises Senden inklusive anschließender Bestätigung wiederholt sich nun, bis die gesamte Nachricht übermittelt wurde.

Das Ende der laufenden Kommunikation wird durch die Stop-Bedingung eingeleitet, welche der Start-Bedingung gleicht und den Bus wieder frei gibt. Die Start/Stop-Bedingungen zeichnen sich insofern aus, dass hier eine Anderung des Datensignals auftritt, während die Taktleitung auf High ist. Bis auf diese Ausnahmen darf der Pegel auf SDA nur im Low-Zustand von SCL geändert werden [13, Abschnitt 15.3.2].

Abbildung 2.2: Datenübertragung mittels I<sup>2</sup>C-Bus

## 2.1.2 UART

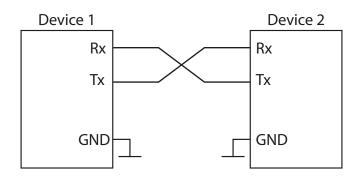

UART steht für Universal Asynchronous Receiver / Transmitter und stellt eine Schnittstelle zum Peer-to-Peer Datenaustausch dar. Die Übermittlung erfolgt dem Namen nach asynchron, es gibt also kein gemeinsames Taktsignal. Stattdessen wird auf die Baudrate zurückgegriffen, um die einzelnen Bits zu differenzieren. Sie muss für eine korrekte Übertragung bei Sender und Empfänger übereinstimmen und kann entweder fest eingestellt oder aber aus der Nachricht ermittelt werden. Weiters bietet UART die Möglichkeit unterschiedliche Frames (= Ubertragungsrahmen) zu verwenden. So kann die Anzahl der Daten- (5-9 bit) und Stopbits (1 oder 2) sowie der Paritätsbitmodus (gleich oder ungleich) eingestellt werden.

Abbildung 2.3: Schematische Darstellung der UART-Beschaltung

Der Aufbau eines UART-Systems besteht im Normalfall aus zwei Datenleitungen (Tx und Rx, Abb. 2.3). Zusätzlich wird oftmals auf zwei weitere Leitungen zwecks Handshake-Verfahren zurückgegriffen (RTS... Request to Send und CTS... Clear to Send). Die UART-Schnittstelle selbst trifft aber noch keinerlei Aussagen über die physikalische Schicht und unterstützt so die unterschiedlichsten Protokolle. Dabei können sowohl vollduplex (= gleichzeitiges Senden und Empfangen, Beispiel: RS232) als auch halbduplex (= kein gleichzeitiges Senden und Empfangen, Beispiel: RS485) Protokolle gewählt werden [14, Abschnitt 7.1].

# 2.2 Signalverarbeitung und -übertragung

# 2.2.1 A/D- und D/A-Wandler

Analog-Digital Konverter (ADC) wandeln ein kontinuierliches analoges in ein diskretes digitales Signal um. Dabei werden abhängig von der Bandbreite (je größer, desto genauer) bestimmten Spannungspegelbereichen Zahlenwerte zugewiesen. Durch die limitierte Auflösung entsteht bei der Konversion der sogenannte Quantisierungsfehler.

Digital-Analog Konverter (DAC) sind das Gegenstück zum ADC und machen die Quantisierungsprozedur rückgängig. Sie erzeugen aus dem digitalen Zahlenwert eine analoge physikalische Größe. Meist werden Spannungen erzeugt, welche wiederum über einen Aktor in die gewünschte physikalische Größe umgewandelt werden können.

Beispiel: 12-Bit ADC (0 V bis 12 V) mit analoger Eingangsspannung von 3.3 V

0 V bis 12 V Analoger Wertebereich: 0 bis  $2^{12} - 1$ Digitaler Wertebereich (12-Bit):

Volt pro Stufe:

$x = \frac{12}{2^{12}} = 2.93 \frac{\text{mV}}{\text{bit}}$ :  $\rightarrow$  max. Quantisierungsfehler von  $\pm 2.93 \,\text{mV}$

Analoge Eingangsspannung:  $3.3\,\mathrm{V}$

$\frac{3.3 \,\mathrm{V}}{z} = 1126.40 \approx 1126 = z$ Digitalisierter Wert:

Fehler der analogen Ausgangs- $3.3 \,\mathrm{V} - z \cdot x = 1.17 \,\mathrm{mV}$

spannung:

Heutzutage werden Datenwandler (ADC und DAC) meist seriell an die verarbeitende Elektronik gekoppelt [13, Abschnitt 9.2]. Beim MONOPOL-Aufbau findet die Kommunikation zwischen ADC/DAC und Mikrocontroller über den I<sup>2</sup>C-Bus statt.

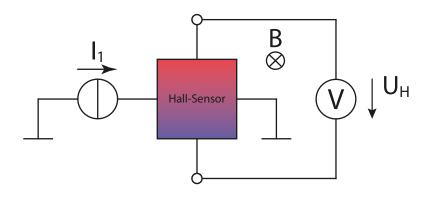

## 2.2.2 Hall-Sensor

Der Hall-Sensor ist ein mit Strom durchflossenes Plättchen, welches den Hall-Effekt zur Messung des magnetischen Feldes nutzt.

Durch das Plättchen fließt der Strom  $I_1$ , der durch eine Stromquelle eingespeist wird (Abb. 2.4). Auf die Elektronen wirkt bei äußeren Feldern die Lorentzkraft

$$\vec{F_L} = q \cdot (\vec{E} + \vec{v} \times \vec{B}). \tag{2.1}$$

Liegt kein elektrisches Feld vor  $(\vec{E}=0)$  verbleibt lediglich der magnetische Anteil. Dieser bewirkt eine Kraft auf die Elektronen, wodurch die direkt zum gemessenen Feld proportionale Hall-Spannung

$$U_H = \frac{R_H}{d} \cdot B \cdot I_1. \tag{2.2}$$

entsteht. Bei bekannten Hallkoeffizient  $R_H$  und Dicke der Hall-Platte d lässt sich so der Betrag des magnetischen Feldes ermitteln [15, Abschnitt 3.3.5].

In der vorliegenden Arbeit wird je ein Hall-Sensor pro Resonatorelement zwecks Strommessung verbaut. Genauere Details der realisierten Stromermittlung werden in den Abschnitten 3.4.4 und 6.2.1 beschrieben.

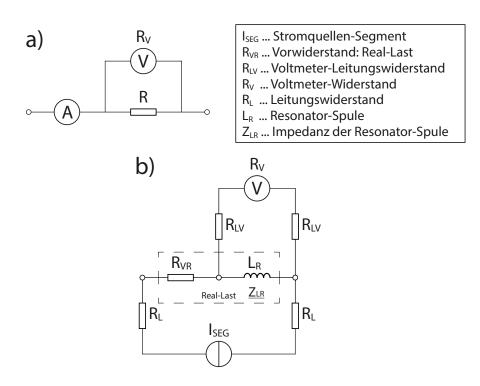

# 2.2.3 Vierleitermessmethode

Die Vierleitermessmethode entspricht näherungsweise der idealen spannungsrichtigen Messschaltung (Abb. 2.5.a) und kann zur Widerstands-, sowie Leistungsermittlung herangezogen werden. Der große Vorteil dieser Art von Messschaltung im Vergleich zur Zweileitermessmethode ist die hohe Genauigkeit, da der systematische Fehler durch Leitungs- und Kontaktierungswiderstände praktisch keinerlei

Abbildung 2.4: Funktionsprinzip eines Hall-Sensors mit I<sub>1</sub> ... Sensorstrom,  $B\ ...\ magnetisches\ Feld\ in\ die\ Zeichenebene,\ U_{H}\ ...\ Hall-Spannung$

Einfluss auf die Messung hat [16]. Erreicht wird dies, indem für Stromquelle und Voltmeter jeweils separate Leitungen zum zu messenden Verbraucher geführt werden. Dadurch ist es möglich die Spannung direkt am Widerstand abzugreifen und etwaige Spannungsabfälle der Strom-Zuleitung auszublenden.

Abbildung 2.5: Zum Vergleich: a Ideale spannungsrichtige Messschaltung; b Vierleitermessmethode im MONOPOL

Die Kabelwiderstände der Spannungsmessung sind prinzipiell von geringer Bedeutung. Der vergleichsweise große Innenwiderstand des Voltmeters  $(R_{LV} \ll R_V)$  bewirkt, dass der Messstrom durch das Spannungsmessgerät und die Messleitungen vernachlässigbar gering ist:

$$R_P = (2R_{LV} + R_V) \parallel \underline{Z_{LR}} \approx \frac{R_V \cdot Z_{LR}}{R_V + Z_{LR}} \approx Z_{LR}$$

(2.3)

$$U_{LR} = I_{SEG} \cdot R_P \approx I_{SEG} \cdot Z_{LR} \tag{2.4}$$

Nach Einstellen der Stromquelle und Ablesen der resultierenden Spannung muss man nur, je nach zu bestimmender Größe, eine entsprechende Gleichung anwenden. Im Falle einer Leistungsermittlung kommt folgende Gleichung zur Anwendung:

$$P = U \cdot I. \tag{2.5}$$

Soll der Widerstandswert errechnet werden, so greift man auf das Ohmsche Gesetz zurück:

$$R = \frac{U}{I}. (2.6)$$

Letzteres wird im MONOPOL verwendet (siehe Abschnitt 3.4.4), um den ordnungsgemäßen Zustand der einzelnen Resonatorspulen sicherzustellen. Sollte eine Spule beschädigt sein, so steigt ihr Widerstand  $Z_{LR}$  (Abb. 2.5.b).

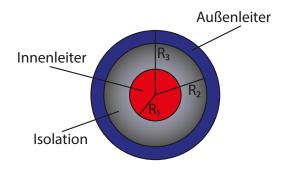

# 2.2.4 Koaxialkabel

Koaxialkabel (Abb. 2.6) werden in der Mess- und Übertragungstechnik verwendet, um Signale möglichst störungsfrei zu übermitteln. Im vorliegenden Projekt wird in Abschnitt 3.5.3 ein Aufbau zur Stromversorgung, der auf dem Koaxialkabel-Prinzip beruht, vorgestellt. Dieser soll mögliche Einflüsse auf den Neutronenstrahl minimieren.

Koaxialkabel bestehen aus einem Innenleiter mit Radius  $R_1$ , welcher von einem konzentrischen Außenleiter  $(R_3)$  durch eine Isolation getrennt ist. Dieser Aufbau erzeugt keinerlei elektrische und magnetische Felder außerhalb des Kabels, falls beide Leiter gegengleiche Ströme führen.

Für das elektrische Feld ist dies offensichtlich, da die Feldlinien alle innerhalb des Kabels verlaufen. Die Feldfreiheit für das magnetische Feld kann ausgehend vom Ampèreschen Gesetz gezeigt werden

$$\oint_{S} \vec{B} \cdot d\vec{s} = \mu_0 I, \tag{2.7}$$

wobei S eine Schleife um den stromführenden Leiter ist. Im dargestellten Fall bietet sich ein Kreis an, dessen Fläche normal auf die Stromrichtung und somit auf die Feldlinien des entstehenden B-Feldes steht.

Betrachtet man zuerst nur das Feld des Innenleiters mit Strom  $I_I$ , so ergibt sich nach Integration von Gl. (2.7)

$$2\pi r B = \mu_0 I_I, \tag{2.8}$$

$$\to B = \frac{\mu_0 I_I}{2\pi r}.\tag{2.9}$$

Für das Feld des Außenleiters mit Strom  $I_A$  erhält man analog

$$B = \frac{\mu_0 I_A}{2\pi r}. (2.10)$$

Durch Superposition beider Ergebnisse erhält man das magnetische Feld außerhalb eines Koaxialkabels

$$B = \frac{\mu_0(I_I + I_A)}{2\pi r},\tag{2.11}$$

wobei für  $I_I = -I_A$  das B-Feld 0 wird.

Abbildung 2.6: Querschnitt eines Koaxialkabels

Die Kapazität C und die Induktion L des Koaxialkabels hängen neben den Kabeldimensionen (Länge l) vom Dielektrikum ( $\varepsilon_r$ ) und der Permeabilität ( $\mu_r$ ) ab

$$C = 0, 2 \cdot \mu_r \cdot l \cdot \ln \frac{R_3}{R_1},\tag{2.12}$$

$$L = \frac{55, 3 \cdot \varepsilon_r \cdot l}{\ln \frac{R_3}{R_1}}. (2.13)$$

Der Wellenwiderstand  $Z_L$ , welcher auch als Abschlusswiderstand zur Vermeidung von Reflexionen verwendet wird, kann durch

$$Z_L = \frac{60}{\sqrt{\varepsilon_r}} \cdot \ln \frac{R_3}{R_1} \tag{2.14}$$

berechnet werden. In der Praxis übliche Werte des Wellenwiderstands von Koaxialkabeln sind  $50\,\Omega$  beziehungsweise  $75\,\Omega$ , je nach Anwendungsfall können aber auch andere Werte verwendet werden [17].

# Elektronische Schaltwerke

letztere Funktion angewendet. [18, Abschnitt 8.5]

# 2.3.1 Schieberegister (SR)

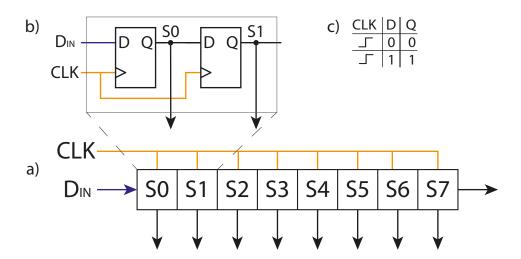

Ein Schieberegister ist ein taktgesteuerter Baustein, der aus mehreren Speicherzellen (D-Flip-Flops) besteht. Es besitzt je nach Ausführung zwei Eingänge, einen Daten- (D<sub>IN</sub>) und einen Takt-Eingang (CLK). Die Taktung erfolgt meist über die positive Taktflanke.

In Abb. 2.7.a ist der schematische Aufbau eines Schieberegisters zu sehen. Erfolgt eine positive Taktflanke auf der CLK-Leitung wird der logische Pegel des Eingangs D<sub>IN</sub> im D-Flip-Flop der Zelle S0 (2.7.b) gespeichert. Mit jedem weiteren Takt wird der Wert von jeder Zelle in die nächste weitergereicht (S $0\rightarrow$ S1, S $1\rightarrow$ S2, etc.). Der Wert, der in der Zelle S7 gespeichert war, wird aus dem Register geschoben. Je nach Realisierung des Registers können alle Zellen parallel ausgelesen werden. Schieberegister können anwendungsspezifisch mehrere verschiedene Aufgaben erfüllen. Sie können einerseits als FIFO-Speicher (First-In-First-Out), andererseits zur Parallelisierung serieller Daten verwendet werden. Im Wanderwellenresonator wird

Abbildung 2.7: Schematische Darstellung eines 8 bit-Schieberegisters, a Darstellung mit Speicherzellen; b Detailansicht der Zellen; c Wahrheitstabelle eines D-Flip-Flops

# Hardware

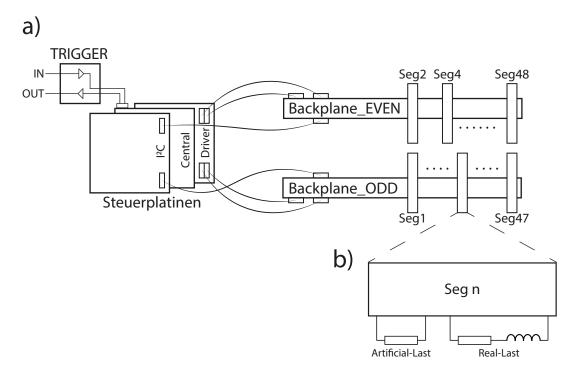

In diesem Kapitel werden alle beteiligten Hardware-Komponenten, sowie die Stromversorgung beschrieben. In Abb. 3.1.a ist eine schematische Darstellung des Aufbaus zu sehen. Auf die einzelnen Komponenten und Subkomponenten wird in den entsprechenden Unterkapiteln detailliert eingegangen.

Abbildung 3.1: Skizzierter Plan der beteiligten Hardwarekomponenten. a Übersicht; b Anschlussplan von Artificial- und Real-Last

# 3.1 Platinen

Die Automatisierung des MONOPOL-Projekts besteht neben anderen Komponenten aus mehreren Platinen, welche von Andrzej Pelczar entwickelt wurden. Die so entstandene Hardware wurde im Laufe mehrerer Projekte [10, 19–22] in den bestehenden Aufbau eingebunden und getestet.

3.1 Platinen 15

# 3.1.1 Steuerplatinen (SP)

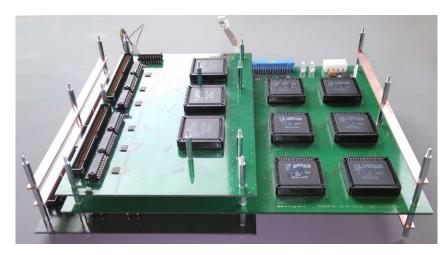

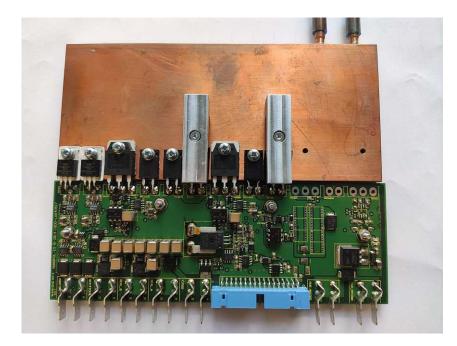

Die Steuerplatinen sind das Herzstück der Automatisierung. Sie bestehen aus drei miteinander verdrahteten und übereinander gestapelten Platinen (Abb. 3.2).

Abbildung 3.2: Foto der übereinander gestapelten Steuerplatinen (Bild aus [10])

## I<sup>2</sup>C-Steuerplatine

Ganz oben befindet sich die I<sup>2</sup>C-Steuerplatine. Auf ihr befindet sich das Schieberegister zur Auswahl der Stromquelle, mit der über I<sup>2</sup>C-Bus kommuniziert werden kann. Zu beachten ist, dass immer nur ein einziges High-Bit im gesamten Schieberegister vorhanden sein darf, da andererseits mehrere Bausteine gleichzeitig adressiert werden. Dies würde den Bus überlasten und die Kommunikation fehlschlagen lassen. Die I<sup>2</sup>C-Steuerplatine ist mit der Zentralen-Steuerplatine (Schieberegister-Steuerpins), sowie mit den Backplanes (SDA, SCL und Schieberegister-Ausgangpins) verbunden.

## Zentrale-Steuerplatine (CP)

In der Mitte ist die eigentliche Steuerplatine. Auf ihr befindet sich neben den Schieberegistern (Artificial-, Real-Last und Glitch) zur Spulenansteuerung auch der Mikrocontroller (µC) der den gesamten Ablauf steuert.

Neben der zuvor oben erwähnten Verbindung mit der I<sup>2</sup>C-Steuerplatine, bestehen auch noch Verdrahtungen zur Treiber-Platine sowie zu einem PC über RS485 (UART).

## **Treiber-Platine**

Die Treiber-Platine verstärkt die Ausgangspins der Artificial-Last-, Real-Last- und Glitch-Register und stellt die Konnektoren für die Verbindung zu den Backplanes zur Verfügung.

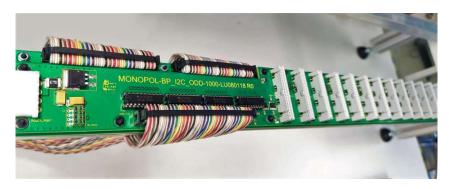

# 3.1.2 Backplane (BP)

Die Backplane (Abb. 3.3) besteht aus zwei miteinander verschraubten Platinen und ist das Verbindungsstück zwischen Steuerplatinen und Stromquellen-Segmenten. Alle Schieberegister-Ausgänge sowie, I<sup>2</sup>C-Busleitungen werden hier zu den jeweiligen Segmenten entflechtet. Weiters stellt die Backplane ein I<sup>2</sup>C-Erweiterungsinterface für zusätzliche Sensorik und Aktorik bereit.

Abbildung 3.3: Foto der Backplane-Platinen

# 3.1.3 Stromquellen-Segmente

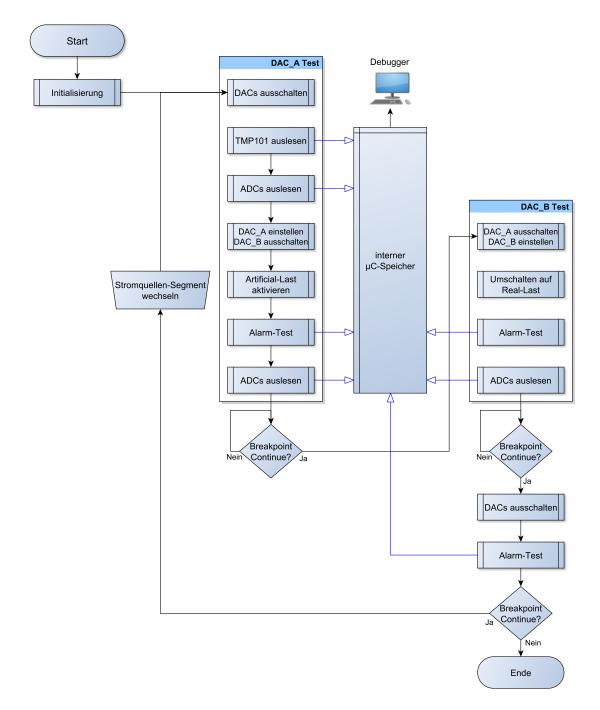

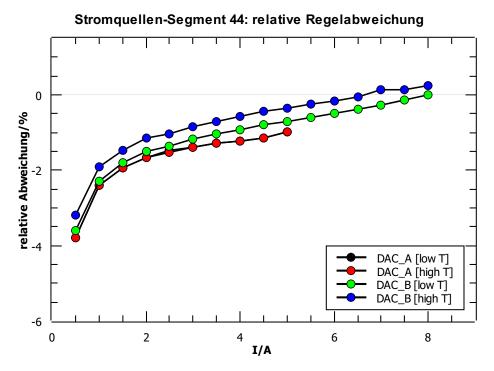

Das Stromquellen-Segment (Abb. 3.4) ist eine über I<sup>2</sup>C-Kommunikation steuerbare und auslesbare Stromquelle (siehe Abschnitt 3.4), welche in 48-facher Ausführung im MONOPOL-Projekt zum Einsatz kommt. Sie kann Ausgangsströme bis zu 25 A liefern. Dazu besitzt die Platine zwei DACs (DAC A: 0A - 5A und DAC B: 0 A - 25 A), die jeweils einen Feldeffekt-Transistor ansteuern. Diese Transistoren erhitzen sich abhängig vom eingestellten Strom und müssen über Temperatursensoren (TMP101) überwacht werden.

Weiters kann die Funktion des Segmentes sowie der angeschlossenen Peripherie über zwei ADCs kontrolliert werden. Dabei wird der Strom über einen Hall-Sensor in eine direkt proportionale Spannung umgesetzt und gemeinsam mit der Spannung an der Spule digitalisiert (Details in Abschnitt 3.4.4). So kann festgestellt werden, ob die zum Segment dazugehörige Spule intakt ist und die festgelegten Ströme eingehalten werden.

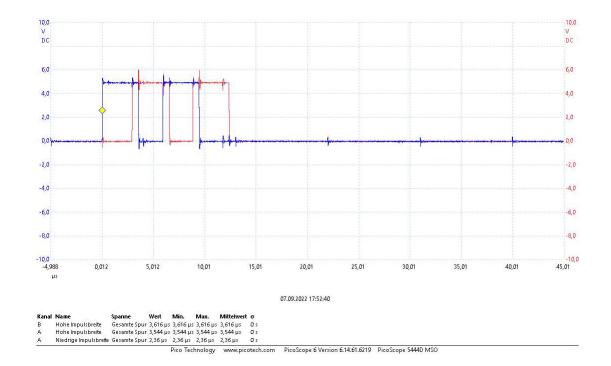

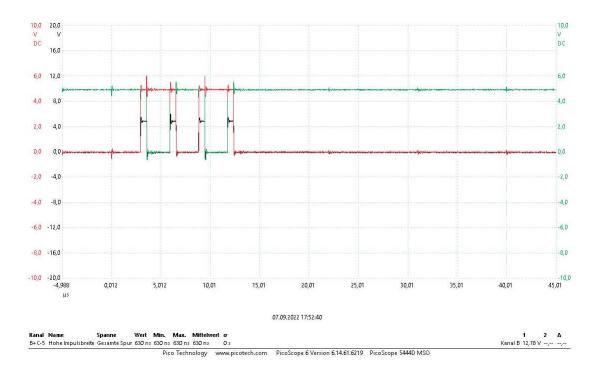

Neben der Bereitstellung des Spulenstromes ist das Segment auch für das Umschalten zwischen Artificial- und Real-Last, durch Steuerung über die entsprechenden Schieberegister, verantwortlich. Dieser Vorgang muss möglichst schnell (etwa 4 µs) vonstattengehen, darf aber gleichzeitig nur geringe Überschwinger produzieren. Um das zu gewährleisten wird der Strom für etwa 600 ns über beide Lasten geleitet (= Glitch) [10]. Die stromführende Last ist durch LEDs ersichtlich, was zur Schnellüberprüfung dient. Die grüne LED steht für die Artificial- die rote LED für die Real-Last.

Abbildung 3.4: Stromquellen-Segment

# Pinbelegung

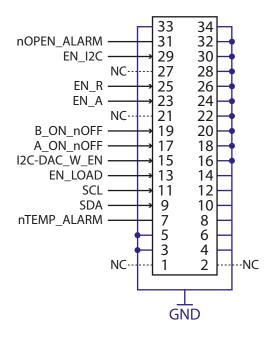

In Abb. 3.5 ist der Anschlussplan eines Segmentes zu sehen, die dazugehörige Erklärung liefert Tab. 3.1.

Abbildung 3.5: Anschlussplan eines Stromquellen-Segmentes

| Pin# | ig  Bezeichnung | $\mid Beschreibung$                                                                                                 | $ig  Verbindung\ zu$         |

|------|-----------------|---------------------------------------------------------------------------------------------------------------------|------------------------------|

| 7    | nTEMP_ALARM     | LOW: Temperatur-Alarm von                                                                                           | μC,                          |

| 1    | HIEMF_ALARM     | TMP101 liegt vor                                                                                                    | I/O-Extender                 |

| 9    | SDA             | I <sup>2</sup> C-Datenleitung                                                                                       | μC                           |

| 11   | SCL             | I <sup>2</sup> C-Clockleitung                                                                                       | μС                           |

| 13   | EN_LOAD         | Ermöglicht das Ein- und Ausschalten der Stromquelle; Oder-Verknüpfung zwischen EN_I_SRC und IO_EN_LOAD (invertiert) | μC,<br>I/O-Extender          |

| 15   | I2C-DAC_W_EN    | Ermöglicht die Kommunikation<br>mit den DACs                                                                        | μС                           |

| 17   | A_ON_nOFF       | Aktiviert den DAC für den niederen Strombereich                                                                     | I/O-Extender (invertiert)    |

| 19   | B_ON_nOFF       | Aktiviert den DAC für den<br>höheren Strombereich                                                                   | I/O-Extender<br>(invertiert) |

| 23   | EN_A            | Schaltet den Strom über die<br>Artificial-Last                                                                      | SR_A                         |

| 25   | EN_R            | Schaltet den Strom über die<br>Real-Last                                                                            | SR_R                         |

| 29   | EN_I2C          | Ermöglicht die<br>I <sup>2</sup> C-Kommunikation mit dem<br>jeweiligen Segment                                      | SR_I2C                       |

| 31   | nOPEN_ALARM     | LOW: Spule ist nicht korrekt angeschlossen                                                                          | μC,<br>I/O-Extender          |

Tabelle 3.1: Pinbeschreibung der Stromquellen-Segmente mit μC ... Mikrocontroller (Abschnitt 3.2), SR ... Schieberegister (Abschnitt 3.3.1) und I/O-Extender (Abschnitt 3.4.5)

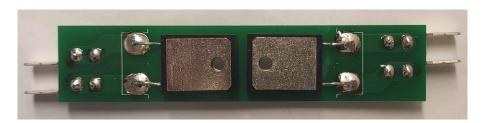

# 3.1.4 Platinen der Artificial- und Real-Last

Diese Platinen werden pro Stromquellen-Segment einmal benötigt und bestehen lediglich aus zwei Widerständen. Einer fungiert als Artificial-Last und der andere als Vorwiderstand für eine Resonatorspule. Die Serienschaltung aus Resonatorspule und Vorwiderstand ergeben die Real-Last.

Um die beim Umschaltvorgang zwischen den Lasten auftretenden Spannungsspitzen so klein wie möglich zu halten, sollten die Real- und die Artificial-Last in etwa den gleichen elektrischen Widerstand aufweisen. In |10| wurde gezeigt, dass  $0.22\,\Omega$ Widerstände ein guter Kompromiss zwischen Leistungsaufnahme und Stabilität sind.

Abbildung 3.6: Platine der Artificial- und Real-Last

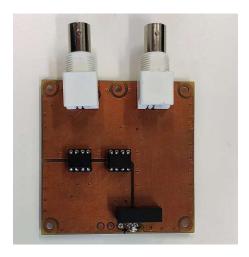

# 3.1.5 Trigger-Platine

Der MONOPOL-Wanderwellenresonator soll im Zusammenspiel mit externen Geräten verwendbar sein. Dazu besitzt er ein Trigger-Interface in Form der Trigger-Platine (Abb. 3.7). Auf ihr befindet sich jeweils ein Signal-Eingang und -Ausgang, beide direkt mit dem Mikrocontroller verbunden. Befindet sich der Mikrocontroller im Trigger-Mode und detektiert ein Signal am dazugehörigen Eingang, wird ein Interrupt ausgelöst und ein Neutronenpaket mit der definierten Geschwindigkeit gefiltert. Sobald der Schiebevorgang abgeschlossen ist und das Paket den Resonator verlässt, wird ein Signal am Trigger-Ausgang zur Synchronisation der nachfolgenden Instrumente ausgegeben. Zum Zeitpunkt dieser Arbeit wurde die Trigger-Platine noch nicht installiert.

Abbildung 3.7: Trigger-Platine

# 3.2 Mikrocontroller (μC)

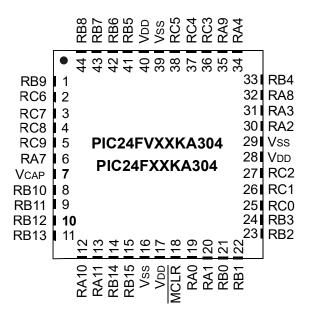

Im MONOPOL-Projekt kommt ein Mikrocontroller des Typs PIC24FV32KA304 (Anschlussplan in Abb. 3.8, Pinbeschreibung in Tab. 3.2) der Firma Microchip als zentrales Steuergerät zum Einsatz.

Der Speicher des Controllers ist gemäß Harvard-Architektur in Programm- (bis zu 4 M Instruktionen) und Daten-Speicher (64 kB) aufgeteilt. Die Adressierung erfolgt

individuell für beide Speicher. Der Programm-Speicher wird über einen 24 bit-Wert, meist abgeleitet vom 23 bit Program Counter (PC), angesteuert und beheimatet das erstellte Programm, bestehend aus den Befehlen der Instruktionen-Liste (zu finden in [23, Kapitel 28]). Der Daten-Speicher, in dem sich auch alle Working-Registers befinden, ist 16 bit breit, kann aber byteweise angesprochen werden. Die Adressierung erfolgt dabei über eine 16 bit-Adressleitung.

Weiters stellt der Mikrocontroller einen internen Takt von 8 MHz zur Verfügung, lässt sich aber über einen externen Oszillator auf bis zu 32 MHz takten. Im MONO-POL-Projekt kommt ein 29.4912 MHz Quarz als Taktquelle zum Einsatz, wodurch sich eine Periodendauer von 33.91 ns ergibt. Da der μC zwei solcher Perioden zur Abarbeitung einer Instruktion benötigt, ergibt sich die effektive Instruktionen-Periode  $T_I = 67.82 \,\mathrm{ns}$ . Dieser Wert ist maßgeblich für die Berechnung der Schiebeperiode und ermöglicht somit die Ermittlung der oberen Neutronen-Grenzgeschwindigkeit des Resonators (siehe Abschnitt 6.2.2).

Neben der Verwendung eines externen Clock-Signals bietet der Controller auch benutzerfreundliche Module für unterschiedliche geläufige Schnittstellen. Im MO-NOPOL werden davon ein UART- und beide I<sup>2</sup>C-Module eingesetzt.

Die Versorgung des Mikrocontrollers wird, wie bei der restlichen 5V-Hardware, über einen durch 12 V gespeisten DC/DC-Konverter sichergestellt.

Abbildung 3.8: Anschlussplan des Mikrocontrollers

| Funktion    | Port# | Pin# | Beschreibung                                         | Gruppe |

|-------------|-------|------|------------------------------------------------------|--------|

| DIN_A       | A1    | 20   | Artificial-SR: Dateneingang                          | SR_A   |

| CLK_A       | A0    | 19   | Artificial-SR: Takteingang                           | SR_A   |

| LAT_A       | C1    | 26   | Artificial-SR: Eingang um<br>Muster zu latchen       | SR_A   |

| EN_A        | С0    | 25   | Artificial-SR: Aktiviere<br>transparenten Modus      | SR_A   |

| DLB_A       | B10   | 8    | Artificial-SR: Feedback (letztes Bit im SR)          | SR_A   |

| DIN_R       | A9    | 35   | Real-SR: Dateneingang                                | SR_R   |

| CLK_R       | A8    | 32   | Real-SR: Takteingang                                 | SR_R   |

| LAT_R       | C3    | 36   | Real-SR: Eingang um Muster zu latchen                | SR_R   |

| EN_R        | C2    | 27   | Real-SR: Aktiviere<br>transparenten Modus            | SR_R   |

| DLB_R       | A4    | 34   | Real-SR: Feedback (letztes Bit im SR)                | SR_R   |

| DIN_G       | A11   | 13   | Glitch-SR: Dateneingang                              | SR_G   |

| CLK_G       | A10   | 12   | Glitch-SR: Takteingang                               | SR_G   |

| LAT_G       | C5    | 38   | Glitch-SR: Eingang um Muster<br>zu latchen           | SR_G   |

| CLR_OUT_G   | C4    | 37   | Glitch-SR: Muster am Ausgang<br>wird auf LOW gesetzt | SR_G   |

| DLB_G       | A7    | 6    | Glitch-SR: Feedback (letztes Bit im SR)              | SR_G   |

| DIN_I2C     | С9    | 5    | I2C-SR: Dateneingang                                 | SR_I2C |

| CLK_I2C     | B13   | 11   | I2C-SR: Takteingang                                  | SR_I2C |

| LAT_I2C     | С8    | 4    | I2C-SR: Eingang um Muster zu latchen                 | SR_I2C |

| EN_I2C      | B12   | 10   | I2C-SR: Aktiviere transparenten<br>Modus             | SR_I2C |

| DLB_I2C     | A3    | 31   | I2C-SR: Feedback (letztes Bit im SR)                 | SR_I2C |

| ITR_I2C_CLK | В8    | 44   | I2C-Modul 1: Taktleitung                             | I2C1   |

Fortsetzung auf der nächsten Seite

Tabelle 3.2: Pinbeschreibung des Mikrocontrollers

| Funktion     | Port # | Pin# | Beschreibung                              | Gruppe  |

|--------------|--------|------|-------------------------------------------|---------|

| ITR_I2C_DTA  | В9     | 1    | I2C-Modul 1: Datenleitung                 | I2C1    |

| EXT_I2C_CLK  | В3     | 24   | I2C-Modul 2: Taktleitung                  | I2C2    |

| EXT_I2C_DTA  | B2     | 23   | I2C-Modul 2: Datenleitung                 | I2C2    |

| I2C-DAC_W_EN | В7     | 43   | High: Aktiviere Kommunikation<br>mit DACs | I2C2    |

| RS_nRD       | В5     | 41   | LOW: Empfang möglich                      | UART    |

| RS_pDE       | В6     | 42   | HIGH: Senden möglich                      | UART    |

| RS_MRX       | C6     | 2    | Empfangsleitung                           | UART    |

| RS_MTX       | C7     | 3    | Sendeleitung                              | UART    |

| EN_I_SRC     | B14    | 14   | Aktiviert die Stromquellen                | Control |

| ALARM_IN     | B11    | 9    | Empfangspin der Alarmfunktion             | Control |

| PS_RTS       | B4     | 33   | LOW: Aktiviert den Drucksensor            | Control |

| MCLR         | -      | 18   | Masterclear                               | Control |

| SYSCLK       | -      | 30   | Anschluss des externen<br>Oszillators     | Control |

| Reserved     | В0     | 21   | -                                         | -       |

| Reserved     | B1     | 22   | Zur Programmierung des μC                 | Control |

| AIN_2V048    | B15    | 15   | Referenzspannung                          | Control |

Tabelle 3.2: Pinbeschreibung des Mikrocontrollers (Fortsetzung)

### CPLD3.3

CPLD steht für Complex Programmable Logic Device und beschreibt programmierbare Digitaltechnikbausteine. Einmal programmiert, bleibt das Verhalten auch nach Aus- und wieder Einschalten erhalten, ist also nicht flüchtig. Ein weiterer Vorteil gegenüber FPGAs (Field Programmable Gate Array) ist ihre Einfachheit und Benutzerfreundlichkeit. So bieten einige Hersteller die Möglichkeit digitale Schaltungen in einer grafischen Oberfläche nachzubilden und daraus das Programm des CPLD zu generieren. Das zeitliche Verhalten lässt sich dabei oft direkt aus dem Datenblatt der CPLDs und der programmierten Schaltung abschätzen.

Nachteil von CPLDs ist, dass sie aufgrund ihrer begrenzten Hardware-Ressourcen Anwendungen nur bis zu einem gewissen Komplexitätsmaß abdecken können. Ab dann überwiegen die Vorteile des FPGA, vor allem falls ein Produkt in die Massenfertigung gehen soll. Aus dem Code der bei FPGAs verwendeten Hardwarebeschreibungssprachen (VHDL, Verilog) kann direkt eine Chip-Maske abgeleitet werden. Im folgenden Teil wird kurz auf die Anwendungsgebiete und die Besonderheiten 3.3 CPLD 23

der CPLDs im Projekt eingegangen. Für detaillierte Ausführungen ist [10] hinzuzuziehen.

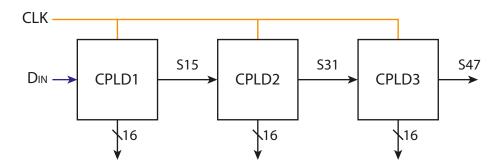

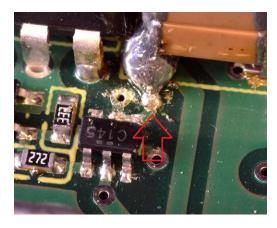

## 3.3.1 CPLDs im MONOPOL

Die im MONOPOL zum Einsatz kommenden CPLDs des Modells ISP LSI2064 CPLD stammen von der Firma Lattice Semiconductor Corporation und werden alle als 16 bit-Schieberegister eingesetzt. Sie werden in Gruppen von jeweils drei Chips verdrahtet, um ein resultierendes 48 bit-Schieberegister zu erhalten (Abb. 3.9). In Summe werden vier solcher Register verwendet, es werden also 12 CPLDs benötigt. Um Beschädigungen vorzubeugen, ist bei der Handhabung dieser Chips unbedingt auf elektrostatische Aufladung zu achten.

Abbildung 3.9: 48 bit-Schieberegister durch Zusammenschaltung von drei CPLDs; Sxx ... letztes Bit des jeweiligen Registers

Der Anspruch an die Register ist, möglichst schnell zu sein, die entsprechenden Setup-  $(t_{SU})$ , Clock-to-Output-Delay-  $(t_{CO})$  und Hold-Zeiten  $(t_H)$  sollten also so kurz wie möglich sein. Mithilfe des Datenblatts [24] lassen sich dazu die Werte aus Tab. 3.3 ermitteln. Es zeigt sich, dass zwischen zwei Schaltvorgängen mindestens  $93 \text{ ns} (= 3 \cdot 31 \text{ ns}; \text{ drei CPLDs ergeben ein Register}) liegen sollten.$

Anmerkung: Durch Vergleich mit der Periodendauer eines Instruktionen-Zyklus des Mikrocontrollers (67.82 ns) erkennt man, dass zwischen aufeinanderfolgenden Schaltvorgängen zwei Zyklen vergehen sollten. In der Software wurde dies durch Einfügen zweier NOP-Befehle nach jedem Schaltvorgang sichergestellt.

| $\mathrm{t_{SU}}\colon$ | $4.6\mathrm{ns}$ |

|-------------------------|------------------|

| $\mathrm{t_{CO}}\colon$ | $19\mathrm{ns}$  |

| $\mathrm{t_{H}}\colon$  | $7.4\mathrm{ns}$ |

| $\overline{GESAMT}$ :   | $31\mathrm{ns}$  |

Tabelle 3.3: Schaltzeiten der verwendeten CPLDs

Die Schieberegister werden im MONOPOL-Projekt verwendet, um die begrenzte Anzahl an Mikrocontroller-Pins zu erweitern. So kann mit wenigen Steuerleitungen auf 48 parallele Leitungen skaliert werden.

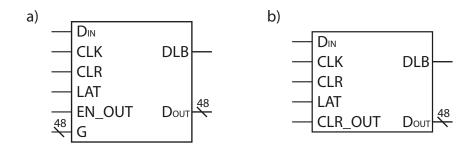

Wie vorhergehend erwähnt, werden vier dieser Register benötigt, welche in zwei unterschiedlichen Ausführungen realisiert werden (Abb. 3.10). Die Beschreibung der einzelnen Ein- und Ausgänge befindet sich in Tab. 3.4.

Abbildung 3.10: Varianten der eingesetzten 48 bit-Schieberegister. a Artificial-Lastregister b 12C-Control- und Glitch-Register

| Bezeichnung                            | Beschreibung                                     | Variante |  |

|----------------------------------------|--------------------------------------------------|----------|--|

| $\overline{\mathrm{D_{IN}}}$           | Daten-Eingangsbit                                | beide    |  |

| CLK                                    | Clock-Eingang                                    | beide    |  |

| CLR                                    | Clear: Reset aller D-Flip-Flops                  | beide    |  |

| LAT                                    | Latch: Übernehmen der in den D-FF                | beide    |  |

| LAI                                    | gespeicherten Werte an den Ausgang               | beide    |  |

| DLB                                    | Bit des letzten D-FF (muss nicht gelatched sein) | beide    |  |

| $\overline{\mathrm{D}_{\mathrm{OUT}}}$ | 48 bit-Parallelausgang des Registers             | beide    |  |

| EN OUT                                 | Aktiviert den transparenten Modus:               |          |  |

| EN_001                                 | eingeschobene Bits werden sofort gelatched       | a        |  |

|                                        | Glitch: High-Pegel von G werden sofort an die    |          |  |

| G                                      | Ausgänge weitergegeben, der Wert im D-FF a       |          |  |

|                                        | bleibt unverändert                               |          |  |

| CLR OUT                                | Alle Ausgänge werden auf LOW gesetzt, der        |          |  |

|                                        | Wert im D-FF bleibt unverändert                  | D        |  |

Tabelle 3.4: Ein- und Ausgänge der Schieberegister

Wird bei den Registern zur Steuerung des Stroms über die Real-(SR R) und Artificial-Last (SR A) verwendet. Die 48 G-Eingänge sind mit den 48 Pins von D<sub>OUT</sub> des Glitch-Registers verbunden. Diese Variante kommt außerdem beim I2C-Control-Register (SR I2C) zum Einsatz, wobei die G-Eingänge nicht verbunden sind.

3.4 I<sup>2</sup>C-Bausteine 25

Variante b: Wird beim Glitch-Register (SR G) verwendet.

Die Control-Pins (1 bit-Eingänge) aller vier Schieberegister sind genau wie die jeweiligen DLB-Pins direkt mit dem Mikrocontroller verbunden. Einzige Ausnahme sind die CLR-Eingänge, sie sind fest mit GND (0 V) verdrahtet und somit auch nicht verwendbar.

# 3.4 I<sup>2</sup>C-Bausteine

In diesem Abschnitt werden die I<sup>2</sup>C-fähigen Chips des MONOPOL-Projektes behandelt. In Tab. 3.5 findet sich eine Auflistung aller vorhandenen Bausteine samt dazugehöriger Adresse und verbautem Ort. Zusätzlich ist das zuständige I<sup>2</sup>C-Modul des Mikrocontrollers gelistet.

| Bezeichnung                                     | $\mid I^2C	ext{-}Modul \mid$ | Adresse    | Platine                |

|-------------------------------------------------|------------------------------|------------|------------------------|

| PIC24FV32KA304<br>(μC)                          | I2C1, I2C2                   | Master     | Zentrale-Steuerplatine |

| FM24W256-G<br>(FRAM)                            | I2C1                         | 0b10100000 | Zentrale-Steuerplatine |

| TMP101<br>(Temperatursensor)                    | I2C1                         | 0b10010000 | Zentrale-Steuerplatine |

| $\frac{\text{TCA9554A}}{\text{(I/O-Extender)}}$ | I2C2                         | 0b01110000 | Backplane ODD          |

| TCA9554A (I/O-Extender)                         | I2C2                         | 0b01111000 | Backplane EVEN         |

| FM24W256-G<br>(FRAM)                            | I2C2                         | 0b10100000 | Stromquellen-Segmente  |

| TMP101 (Temperatursensor)                       | I2C2                         | 0b10010000 | Stromquellen-Segmente  |

| TMP101 (Temperatursensor)                       | I2C2                         | 0b10010100 | Stromquellen-Segmente  |

| MCP3421<br>(Spannungs-ADC)                      | I2C2                         | 0b11010010 | Stromquellen-Segmente  |

| LTC2461<br>(Strom-ADC)                          | I2C2                         | 0b00101000 | Stromquellen-Segmente  |

| LTC2631-LM12<br>(DAC A)                         | I2C2                         | 0b00100100 | Stromquellen-Segmente  |

| LTC2631-LM12<br>(DAC B)                         | I2C2                         | 0b00100000 | Stromquellen-Segmente  |

Tabelle 3.5: Übersicht der l<sup>2</sup>C-Adressen

## 3.4.1 FRAM

Der FRAM-Chip FM24W256- $G(\underline{F}erroelectric \underline{R}andom \underline{A}ccess \underline{M}emory)$  der Firma Infineon ist ein nichtflüchtiger 256 kbit Speicher, der über I<sup>2</sup>C beschrieben und ausgelesen werden kann.

Der Baustein ist auf der Zentralen-Steuerplatine verbaut und ermöglicht das Speichern verschiedenster Parameter. So könnte der MONOPOL, nach vorheriger Konfiguration, auch ohne direkt verbundenen PC betrieben werden.

Weiters ist der Baustein auf allen Stromquellen-Segmenten verbaut. Hier können PCB-spezifische Parameter gespeichert werden, um etwa die verschiedenen Bauteiltoleranzen auszugleichen und höhere Präzisionen zu erzielen. Eine weitere Anwendung wäre die Hinterlegung der jeweiligen Segment-ID.

# 3.4.2 Temperatursensor (TMP101)

Der Temperatursensor TMP101 der Firma Texas Instruments Incorporated ist ein über I<sup>2</sup>C konfigurierbarer und auslesbarer Chip, der eine Temperaturüberwachungsfunktion bereitstellt. Der Sensor bietet eine einstellbare Auflösung von 9 bit bis 12 bit und deckt einen Temperaturbereich von -55 °C bis 125 °C ab.

Im MONOPOL-Projekt sind 97 Stück der TMP101 verbaut, einer auf der Zentralen-Steuerplatine zum Messen der Umgebungstemperatur, die anderen auf den Stromquellen-Segmenten zur MOSFET-Überwachung.

Die Konfiguration wird nach dem Einschalten des Systems vom Mikrocontroller durchgeführt. Dabei wird der 12 bit Modus für maximale Genauigkeit gewählt. Weiters wird die Alarmtemperatur, soweit nicht anders vom Benutzer festgelegt, auf 90°C eingestellt. Der Alarm wird ausgelöst, sobald vier aufeinanderfolgende Messwerte den Grenzwert überschreiten und besteht solange bis ebenfalls vier Werte wieder darunter liegen. Genaue Informationen zu Betrieb und Konfiguration finden sich in [25].

# 3.4.3 Digital-Analog Konverter (LTH2631-LM12)

Der Baustein LTH2631-LM12 der Firma LINEAR TECHNOLOGY CORPORA-TION ist ein 12 bit DAC und wandelt einen digitalen Zahlenwert in eine analoge Spannung um. Details zur Handhabung sind dem entsprechenden Datenblatt [26] zu entnehmen.

Im MONOPOL kommen zwei dieser Komponenten pro Stromquellen-Segment vor. Jeweils einmal für den Strombereich von 0 A bis 5 A (DAC A) und den Bereich von 0 A bis 25 A (DAC B). Geplant war, dass durch diese Unterteilung der Stromwert genauer geregelt werden kann.

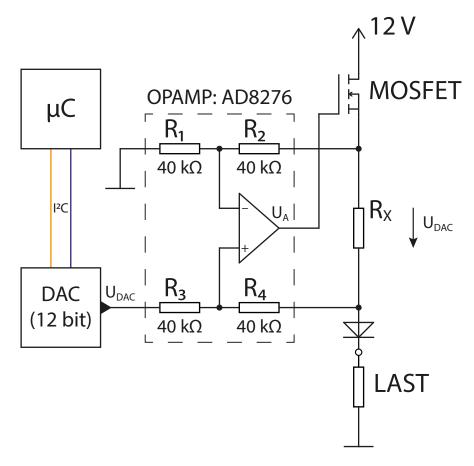

Die Übersetzung von Spannung zu Strom erfolgt mittels in Abb. 3.11 zu sehender

3.4 I<sup>2</sup>C-Bausteine 27

Beschaltung. Die Ausgangsspannung  $U_{DAC}$  kann von  $0 \,\mathrm{V}$  bis  $2.5 \,\mathrm{V}$  variiert werden und wird über einen OPV (AD8276) direkt an den Widerstand  $R_X$  angelegt. Gemäß dem ohmschen Gesetz ergibt sich der resultierende Strom zu

$$I_X = \frac{U_{DAC}}{R_X}. (3.1)$$

Da die Eingangswiderstände des OPV sehr groß sind, fließt praktisch der gesamte Strom  $I_X$  über die niederohmige Last. Verwendet man (aus dem Datenblatt)

$$U_{DAC} = U_{REF} \cdot \frac{z}{2^{12}},\tag{3.2}$$

mit  $U_{REF} = 2.5 \,\mathrm{V}$  ergibt sich der Zusammenhang zwischen übertragenen digitalen Zahlenwert z und dem resultierenden Strom  $I_X$  mit

$$I_X(z) = \frac{U_{REF}}{R_X} \cdot \frac{z}{2^{12}}.$$

(3.3)

Da pro Stromquellen-Segment zwei DACs verbaut sind, ist die in der Abb. 3.11 gezeigte Schaltung ebenfalls in doppelter Ausführung vorhanden. Der Unterschied besteht in den jeweiligen Widerstandswerten von  $R_X$ . Für DAC\_A gilt

$$R_{X,DAC} = R_A = 0.5 \,\Omega, \tag{3.4}$$

und für DAC B

$$R_{X,DAC} B = R_B = 0.1 \Omega.$$

(3.5)

Durch Division von  $U_{REF}$  mit den jeweiligen Widerstandswerten erhält man die maximal einstellbare Stromstärke:

$$I_{A,max} = \frac{U_{REF}}{R_A} = 5 \,\text{A},$$

(3.6)

$$I_{B,max} = \frac{U_{REF}}{R_B} = 25 \,\text{A}.$$

(3.7)

Anmerkung: Da sich im Falle unterschiedlicher Ströme die Ausgangsspannungen der beiden DAC-Stromquellen voneinander unterscheiden, können die Ströme nicht einfach aufaddiert werden, um die resultierende Stromstärke zu ermitteln. Will man dennoch die beiden Stromquellen simultan betreiben, kann der resultierende Strom mittels Thévenin-Theorem beziehungsweise zuvor bestimmter Übersetzungstabelle bestimmt werden.

Abbildung 3.11: Stromquellensteuerung über Digital-Analog Konverter

# 3.4.4 ADCs

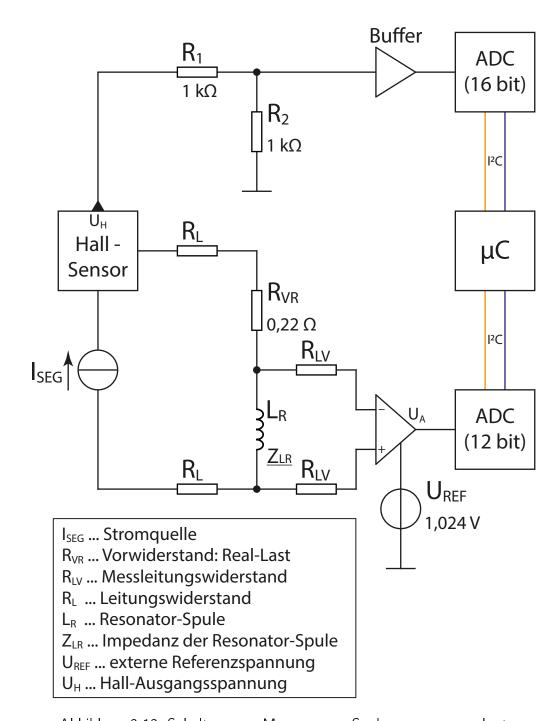

Um die Funktion des Resonator-Systems zu überprüfen, sind je Stromquellen-Segment zwei ADCs, jeweils einer zur Digitalisierung von Spulenspannung (MCP3421) und Spulenstrom (LTC2461), verbaut. In Abb. 3.12 sind alle relevanten Teile der Spannungs- und Stromwertdigitalisierung einsehbar.

# Spulenspannung: MCP3421 (12 bit ADC)

Der ADC MCP3421 [27] wird von Microchip Technology Inc. hergestellt und bietet Auflösungen bis zu 18 bit. Im MONOPOL-Projekt wird jedoch die Standardeinstellung von 12 bit verwendet, wodurch der Chip sofort nach einem Power-on-Reset einsatzbereit ist und nicht extra konfiguriert werden muss. Die zu dieser Einstellung dazugehörige Konversionszeit beträgt 4.2 ms. Das Eingangssignal des ADC ist die aufbereitete Spulenspannung  $U_{LR}$ . Sie wird mittels Vierleitermessmethode abgegriffen und anschließend durch einen Differenzverstäker-OPV [28] verstärkt. So kann festgestellt werden, ob die jeweiligen Spulen intakt sind und ausreichenden elektrischen Kontakt zur Ablaufsteuerung haben. Ist dies nicht der Fall, ist der

3.4 I<sup>2</sup>C-Bausteine

Abbildung 3.12: Schaltung zur Messung von Spulenspannung und -strom

Spannungsabfall  $U_{LR}$  über der Norm und somit detektierbar.

Durch die sehr großen Eingangswiderstände des Verstärkers wird die Spule praktisch nicht belastet und es gilt näherungsweise für die Ausgangsspannung  $U_A$  des Verstärkers

$U_A = \frac{U_+ - U_-}{10} + U_{REF} \approx \frac{U_{LR}}{10} + U_{REF}.$ (3.8)

Da der ADC im 12 bit Modus betrieben wird, ergibt sich der digitalisierte Spannungswert  $z_U$  (ganzzahlig gerundet) zu

$$z_U \approx 2^{11} \cdot \frac{U_A}{V_{REF}},\tag{3.9}$$

wobei die interne Referenzspannung  $V_{REF}$  des Chips 2.048 V beträgt. Durch Umformen und Einsetzen von Gl. (3.8) erhält man

$$U_{LR}(z_U) \approx 10 \cdot (\frac{z_U}{2^{11}} \cdot V_{REF} - U_{REF}).$$

(3.10)

Setzt man nun die Grenzwerte von  $z_U$  ein erhält man den abgedeckten Spulenspannungsbereich

$$U_{LR}(0) = -10.24 \,\mathrm{V},\tag{3.11}$$

$$U_{LR}(2^{11}) = 10.24 \,\text{V}.$$

(3.12)

## Spulenstrom: LTC2461 (16 bit ADC)

Der zweite ADC ist der Chip LTC2461 [29] von LINEAR TECHNOLOGY COR-PORATION. Er misst den eingestellten Strom eines Segmentes, der über einen Hall-Sensor in eine direkt proportionale Spannung übersetzt wird. So kann durch Vergleich von Soll- und Ist-Wert die Funktionstüchtigkeit der DAC-Stromquellen sichergestellt werden.

Dieser ADC kann nicht kontinuierlich betrieben werden und beginnt erst nach Lesen des alten Wertes eine neue Konversion, was bis zu 23 ms in Anspruch nehmen kann.

Aus dem Datenblatt des Hall-Sensors ACS756SCA-050B-PFF-T [30] ist folgende Relation zwischen Eingangsstrom  $I_{SEG}$  und Ausgangsspannung  $U_H$  zu entnehmen

$$U_H(I_{SEG}) = U_H(0) - 0.04 \frac{V}{A} \cdot I_{SEG},$$

(3.13)

wobei  $U_H(0) \approx \frac{3.3 \,\mathrm{V}}{2} = 1.65 \,\mathrm{V}$ , die von der Versorgungsspannung (3.3 V) abhängige Ausgangsspannung im stromlosen Zustand ist. Der ADC greift  $U_H$  über einen 3.4 I<sup>2</sup>C-Bausteine 31

Spannungsteiler mit darauffolgenden Buffer ab

$$U_{ADC} = \frac{1 \,\mathrm{k}\Omega}{2 \,\mathrm{k}\Omega} \cdot U_H. \tag{3.14}$$

Die Konversion von  $U_{ADC}$  erfolgt relativ zur ADC-internen Referenzspannung  $V_{REF}$  $1.25\,\mathrm{V}$  und liefert den digitalen Zahlenwert  $z_I$  (ganzzahlig gerundet)

$$z_I \approx (2^{16} - 1) \cdot \frac{U_{ADC}}{V_{REF}}$$

(3.15)

Durch Einsetzen und Umformen der Gl. (3.13) und (3.14) ergibt sich der gemessene Strom  $I_{SEG}$  zu

$$I_{SEG}(z_I) \approx 25 \cdot (U_H(0) - \frac{2 \,\mathrm{k}}{1 \,\mathrm{k}} \cdot \frac{z_I}{2^{16} - 1} \cdot V_{REF}).$$

(3.16)

Da der Hall-Sensor in negativer Zählrichtung verbaut ist, muss die gesamte Gleichung noch mit "-1" multipliziert werden

$$I_{SEG}(z_I) \approx -25 \cdot (U_H(0) - \frac{2 \,\mathrm{k}}{1 \,\mathrm{k}} \cdot \frac{z_I}{2^{16} - 1} \cdot V_{REF}).$$

(3.17)

Zusätzliche Anpassungen, welche im Abschnitt 6.2.1 "Anpassung der Strommessung über ADC" diskutiert werden führen zur finalen Gleichung der Spulenstrommessung mittels ADC

$$I_{SEG}(z_I) \approx -25 \cdot (U_H(0) - \frac{2 \,\mathrm{k}}{1 \,\mathrm{k}} \cdot \frac{z_I}{2^{16} - 1} \cdot V_{REF}) \cdot \frac{5}{3.18} - 0.7.$$

(6.5)

Den abgedeckten Strombereich kann man durch Einsetzen der  $z_I$ -Grenzwerte bestimmen

$$I_{SEG}(0) = -65.56 \,\mathrm{A},$$

(3.18)

$$I_{SEG}(2^{16} - 1) = 32.71 \,\text{A}.$$

(3.19)

Da die Ströme der Quellen nur in positive Zählrichtung eingestellt werden können, gilt

$$I_{SEG} \in [0, 32.71] A$$

(3.20)

**Anmerkungen:** Der Wert  $z_I$  ist indirekt proportional zum Strom  $I_{SEG}$ . Der gemessene Wert ist durch diverse Bauteiltoleranzen ungenau und sollte deswegen nur zur groben Bestimmung der Funktionstüchtigkeit herangezogen werden. Die Messung des Hall-Sensors kann möglicherweise durch die magnetischen Felder im Resonator beeinflusst werden.

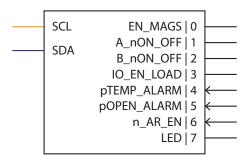

### 3.4.5 I/O-Extender

Der I/O-Extender TCA9554A der Firma Texas Instruments Incorporated ist, wie der Temperatursensor TMP101, ein über I<sup>2</sup>C konfigurierbarer und auslesbarer Chip. Seine Hauptfunktion ist das Erweitern der GPIO-Pins.

Der Bauteil ist in Summe zweimal verbaut und befindet sich auf den Backplanes. In Abb. 3.13 ist der logische Anschlussplan der TCA9554A zu sehen, die dazugehörigen Erklärungen finden sich in Tab. 3.6. Genaue Informationen zu Betrieb und Konfiguration können [31] entnommen werden.

Abbildung 3.13: Anschlussplan des TCA9554A

| Port # | Bezeichnung | $\mid Beschreibung$                                                    | Modus         |

|--------|-------------|------------------------------------------------------------------------|---------------|

| 0      | EN_MAGS     | LOW: Aktiviert den Magnetsensor                                        | Output<br>(O) |

| 1      | A_nON_OFF   | LOW: Aktiviert den DAC für den niederen Strombereich                   | О             |

| 2      | B_nON_OFF   | LOW: Aktiviert den DAC für den<br>höheren Strombereich                 | О             |

| 3      | IO_EN_LOAD  | HIGH: Aktiviert die Stromquellen, wenn $IO\_EN\_LOAD$ ( $\mu$ C) aktiv | О             |

| 4      | pTEMP_ALARM | HIGH: Einer der Temperatursensoren<br>schlägt Alarm                    | Input<br>(I)  |

| 5      | pOPEN_ALARM | HIGH: Eine der Resonatorspulen hat<br>keinen geschlossenen Kontakt     | I             |

| 6      | n_AR_EN     | LOW: Die Backplanes sind korrekt<br>miteinander verbunden              | I             |

| 7      | LED         | HIGH: Die LED auf der jeweiligen<br>Backplane leuchtet                 | О             |

| -      | SCL         | I <sup>2</sup> C-Clockleitung                                          | I/O           |

| -      | SDA         | I <sup>2</sup> C-Datenleitung                                          | I/O           |

Tabelle 3.6: Pinbeschreibung des TCA9554A

### 3.5 Stromversorgung

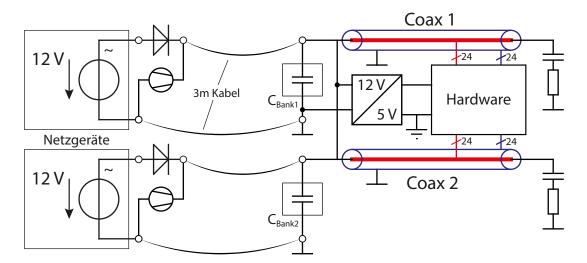

Die Ablaufsteuerung des Resonators wird mit 12 V Gleichspannung betrieben und benötigt unter Volllast einen Gesamtstrom von bis zu 1200 A. Um diesen Energiebedarf sicherzustellen, wurde das Konzept aus Abb. 3.14 entwickelt.

Da die Ausgangsspannung der Netzgeräte nicht den Anforderungen entsprach, wird ein Einweggleichrichter mit Glättungskondensatoren dazwischengeschaltet.

Abbildung 3.14: Übersicht der Stromversorgung

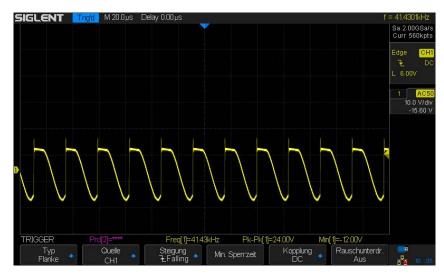

### 3.5.1 Netzgeräte (12V)

Insgesamt wurden drei Netzgeräte mit einer Nennleistung von je 18 kW angeschafft. Ursprünglich sollten die 12 V Netzgeräte direkt an die koaxialen Versorgungsleitungen angeschlossen werden. Leider zeigte sich nach Messungen von Andrzej Pelczar und Arno Frank [32], dass die Qualität der Ausgangsspannung der Netzgeräte, entgegen der Herstellerangaben, keinesfalls ausreichend für den geplanten Einsatz war (siehe Abb. 3.15). Um die erworbenen Netzgeräte dennoch verwenden zu können, wurde der Einsatz eines Einweggleichrichters beschlossen.

Abbildung 3.15: Ausgangsspannung der 12 V Netzgeräte ohne Last (Bild aus [32])

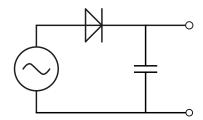

### 3.5.2 Einweggleichrichter

Der Einweggleichrichter mit angeschlossenem Kondensator wird verwendet, um eine Wechselspannung in eine möglichst konstante Gleichspannung umzuwandeln. Dabei blockt die Diode die negative Halbwelle und lässt nur die positive Spannung (abzüglich der Flussspannung) passieren. Letztere lädt einen Kondensator, welcher den Zeitraum der negativen Halbwelle überbrückt. Will man beide Halbwellen nutzen, so ist eine Brückengleichrichter zu verwenden.

Abbildung 3.16: Schaltung eines Einweggleichrichters mit Glättungskondensator

#### Schutzdiode

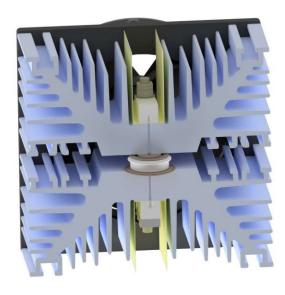

Ursprünglich sollte eine Schottkydiode verwendet werden, da diese eine niedrigere Flussspannung und somit auch eine deutlich geringere Hitzeentwicklung mit sich bringt. Nach langer Recherche stellte sich jedoch heraus, dass keine Schottkydiode mit ausreichenden Spezifikationen lieferbar war, weswegen die Wahl auf das Modell W0944WC150 von IXYS UK Westcode fiel. Hierbei handelt es sich um eine Gleichrichterdiode, welche unter der erwarteten maximalen Last von 600 A eine Verlustleistung von 650 W aufweist. Um diese Diode zu befestigen und zu kühlen wurde gemeinsam mit dem Hersteller eine Lösung erarbeitet, die bis zu 800 A betreibbar ist (zu sehen in Abb. 3.17).

Abbildung 3.17: Rendering der Diode inklusive Halterung und Kühlkörper (Maße in mm:  $200 \times 211 \times 190$ , Bild von Roman Gergen)

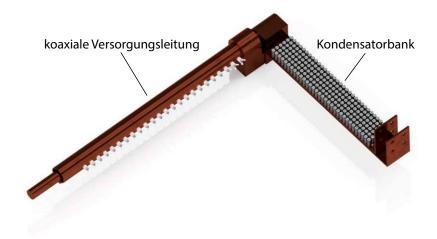

#### Kondensatorbank

Der Glättungskondensator besteht nicht aus einem einzigen Kondensator, sondern aus einer Kondensatorbank, welche 192 parallel geschaltete und individuell tauschbare Kondensatoren (je 680 μF) beheimatet. Die Gesamtkapazität beläuft sich auf 130.56 mF. Diese Anzahl ist notwendig, um Beschädigungen durch hohe Einschaltströme zu verhindern.

Hauptaufgabe der Kondensatoren ist das Stützen der Betriebsspannung gegen Schwankungen, ausgelöst durch die Netzgeräte oder aber auch die plötzliche Laständerung.

### 3.5.3 Koaxial-Versorgungsleitung

Die parallelen Versorgungsleitungen des Resonators (Abb. 3.18) führen unter Volllast Ströme bis zu 600 A, was gemäß dem Ampèreschen Gesetz (Gl. (2.7)) ein korrespondierendes magnetisches Feld verursacht. Dieses würde mit dem Führungsfeld des Resonators interferieren und die Funktion beeinträchtigen. Um dem entgegenzuwirken, wurden Hin- und Rückleiter in Form eines Koaxialkabels realisiert. Aufgrund der hohen Ströme benötigen die Leiter in koaxialer Bauform entsprechende Querschnitte, weswegen sie aus einem Kupferstab und einem Kupferrohr gefertigt

Wie in Abschnitt 2.2.4 beschrieben, müssen Koaxialkabel immer über einen Widerstand, der Reflexionen verhindert, abgeschlossen werden. In der vorliegenden Anordnung besteht dieser aus einer Reihenschaltung eines Kondensators mit einem Widerstand.

Abbildung 3.18: Rendering der koaxialen Versorgungsleitung (Länge:  $\sim \! 890\,\mathrm{mm}$ ) inklusive Kondensatorbank (Länge:  ${\sim}515\,\mathrm{mm}$ , Bild und Design von Roman Gergen)

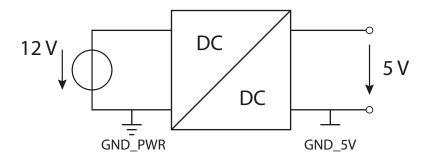

### 3.5.4 DC/DC-Konverter (5V)

Um den MONOPOL zu betreiben, benötigt man neben der 12 V Versorgungsspannung auch noch eine 5 V Spannung. Diese wird durch einen DC/DC-Konverter (RSD-30) bereitgestellt, der bis zu 6 A Ausgangsstrom liefern kann.

Wichtig ist, dass der Konverter keine interne Verbindung zwischen Eingangs- und Ausgangsspannung GND aufweist. Dadurch wird die 5 V-Elektronik von den großen Strömen der Stromquellen-Segmente isoliert und geschützt.

Abbildung 3.19: Eingang- und Ausgangsspannung des DC/DC-Konverters

# 4 Softwareübersicht

Die Software des MONOPOL-Projekts unterteilt sich in zwei miteinander kommunizierende Teile. Einmal die grafische Oberfläche, über die der Benutzer mit der Ablaufsteuerung interagiert, und einmal die Ablaufsteuerung selbst.

Der Softwareanteil der vorliegenden Arbeit befasst sich lediglich mit der Ablaufsteuerung, weswegen nur kurz auf das User-Interface eingegangen wird.

### 4.1 User-Interface

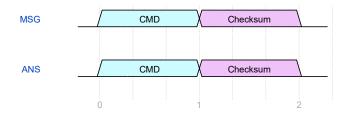

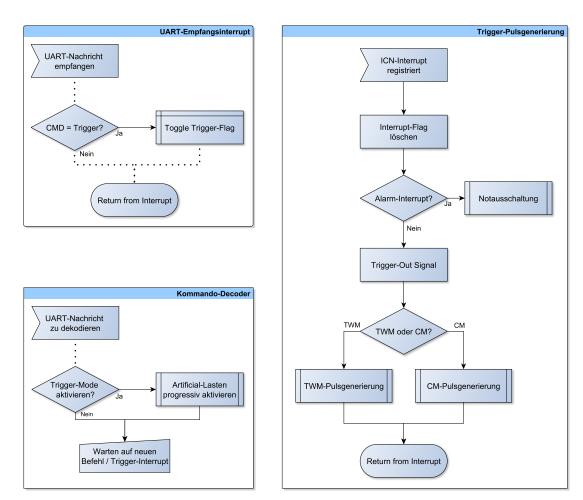

Das grafische User-Interface (GUI) ist die Schnittstelle zwischen Benutzer und Ablaufsteuerung. Über sie werden alle relevanten Einstellungen und Auswertungen getätigt und mittels UART über ein definiertes Protokoll (siehe Abschnitt 5.2.1) an den Mikrocontroller übermittelt.

Bisher existiert eine erste Version der GUI, welche von Maya Sajatovic [33] erstellt wurde. Diese wird derzeit im Zuge einer Bachelorarbeit überarbeitet, um weitere Funktionalitäten zu integrieren.

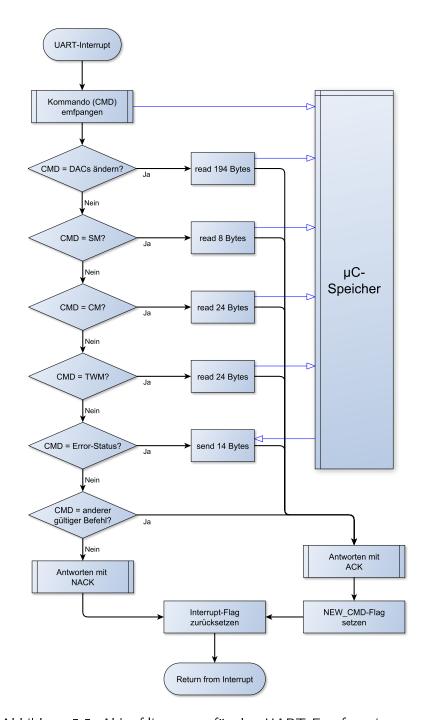

## Ablaufsteuerung

Die Software der Ablaufsteuerung muss eine ganze Reihe von Aufgaben bewältigen. Sie muss mit der angeschlossenen Peripherie kommunizieren, sei es über logische Pegel oder Kommunikationsprotokolle wie UART beziehungsweise I<sup>2</sup>C. Befehle, welche so vom Nutzer an die Steuerung übermittelt werden, müssen weiters dekodiert, interpretiert und ausgeführt werden.

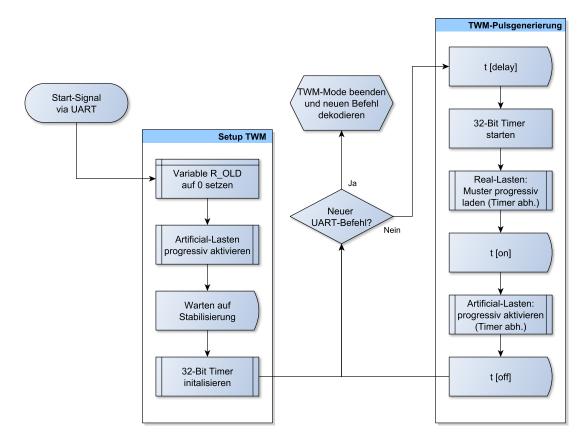

Die Ablaufsteuerung soll in drei verschiedenen Modi betrieben werden können. Den Static Mode (SM), den Conventional Mode (CM) und den Traveling Wave Mode (TWM). Die anfallenden Schiebezeiten sind dabei so gering wie möglich zu halten. So kann die einstellbare Geschwindigkeit des erhaltenen Neutronenpakets maximiert werden.

Zusätzlich dazu, sollen CM und TWM im Trigger-Modus betrieben werden können. Bei diesem wird erst dann ein Neutronenpaket erzeugt, wenn ein externes Signal registriert wird.

Um Fehlern und infolgedessen Beschädigungen vorzubeugen, soll das System eine Selbstüberprüfung vornehmen und deren Ergebnisse an den Benutzer kommunizieren. Sollten überwachte Parameter wie die Temperatur oder der Spulenkontakt

außerhalb definierter Normen liegen, so muss die Software in der Lage sein, das System herunterzufahren.

### Mikrocontroller-Toolchain

Wie in Abschnitt 3.2 Mikrocontroller beschrieben, wird ein Prozessor vom Typ PIC24FV32KA304 von Microchip zur Kontrolle der Ablaufsteuerung verwendet. Die Erstellung des Quelltexts erfolgt über die vom Hersteller bereitgestellte Entwicklungsumgebung MPLAB X IDE v3.50. Die Übersetzung wird mit dem ebenfalls von Microchip stammenden Compiler XC16 durchgeführt. Dieses Toolchain-Setup ermöglicht Programmierungen in C und Assembler und bietet für letzteres auch die Unterstützung von Makros und Präprozessoranweisungen. Zusätzlich kann der Code auch im Simulator oder durch einen In-Circuit Emulator getestet werden. Da die hier beschriebene Anwendung höchst zeitkritisch ist, wird die Programmierung in der programmiertechnisch aufwendigeren Assemblersprache abgewickelt. Sie bietet, durch den Minimalismus und die vordefinierte Abarbeitungsdauer der einzelnen Befehle, entscheidende Vorteile gegenüber höheren Sprachen und ist so-

Ein Nachteil von Assemblersprachen ist, dass sie sich je nach verwendetem Compiler und programmierten Prozessor unterscheiden, wodurch je nach Anwendungsfall auf die entsprechende Dokumentation zurückgegriffen werden muss. Für dieses Projekt wurden folgende vier Dokumente herangezogen:

- PIC24FV32KA304 FAMILY-Datasheet [23]

- PIC24F Family Reference Manual [34]

mit schneller sowie zeitlich determiniert.

- 16-bit MCU and DSC Programmer's Reference Manual [35]

- MPLAB® XC16 ASSEMBLER, LINKER AND UTILITIES User's Guide [36]

# Software der Ablaufsteuerung

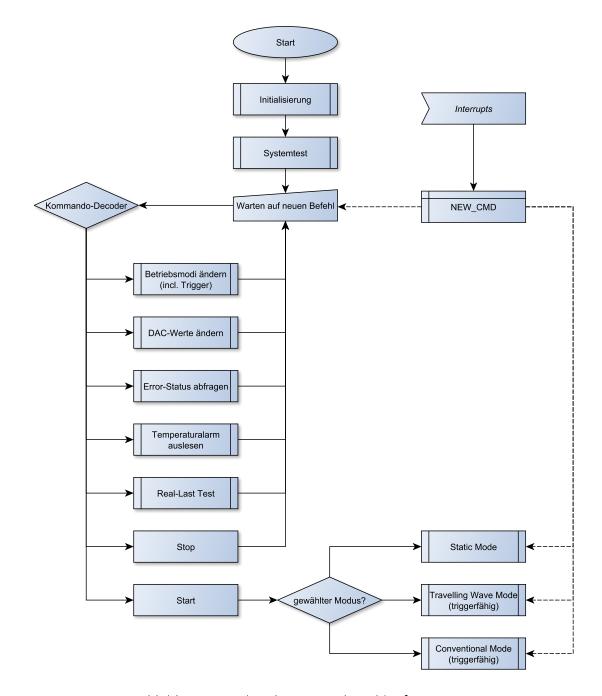

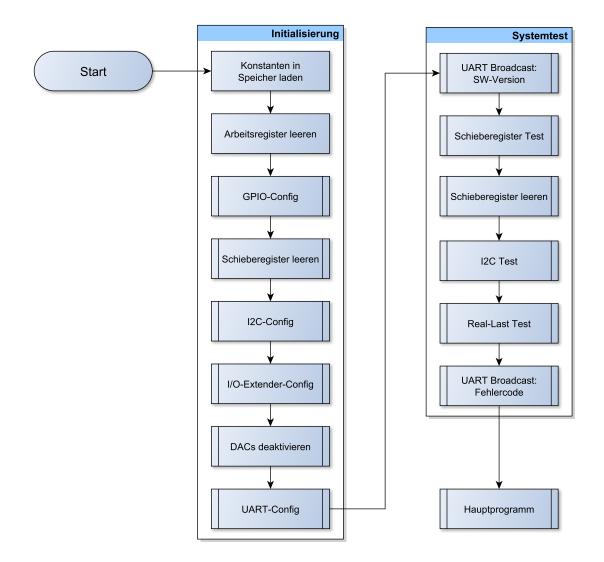

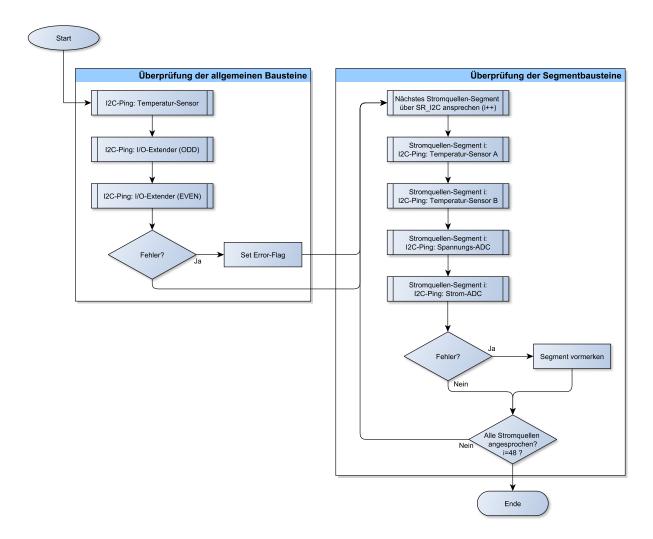

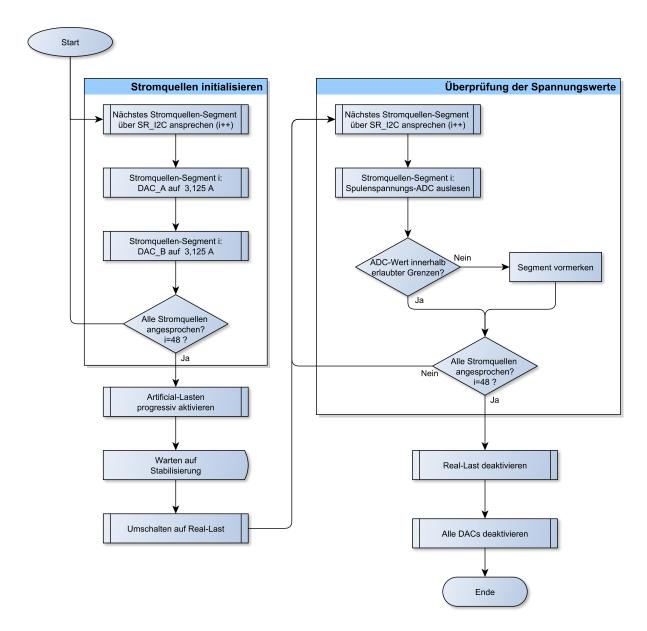

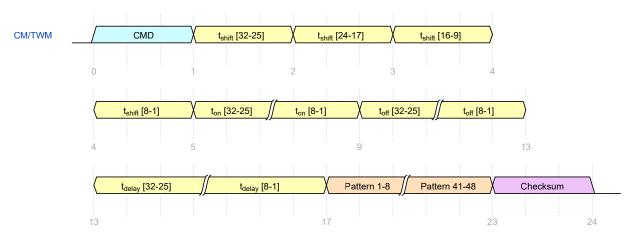

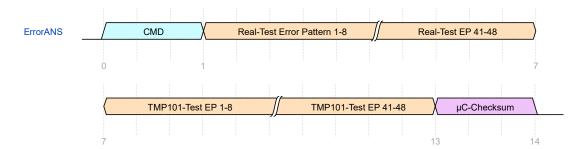

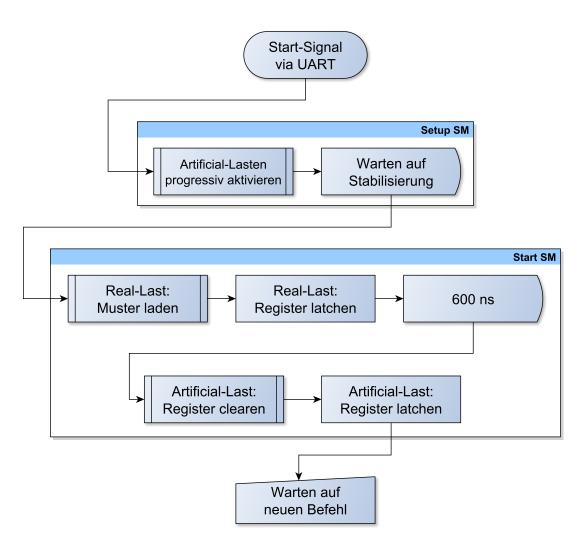

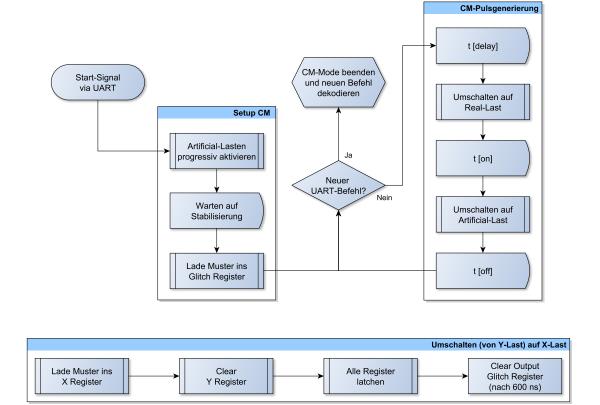

Die Ablaufsteuerungssoftware (Abb. 5.1) des Mikrocontrollers startet, wenn die Spannungsversorgung eingeschaltet ist. Bevor das System betriebsfähig ist, muss die Initialisierung mit anschließendem Systemtest (Abschnitt 5.1) erfolgen. Über weite Teile dieser Phase kann der Controller keine Daten mit dem PC austauschen und ist somit auch nicht steuerbar.