## DISSERTATION

# Predictive and Efficient Modeling of Hot Carrier Degradation with Drift-Diffusion Based Carrier Transport Models

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik von

### Prateek Sharma

8818 Travis Hills Drive, Austin, USA geboren am 14. Okt 1985 in Kota, Rajasthan. India

## ABSTRACT

Reliability in metal oxide semicondcutor (MOS) transistors is an important concern due to their use in crucial fields like space, military, medical, and several consumer products. As the electric fields in MOS devices increase, so does the probability of failure due to high energy carriers. Thus, simulation of these semiconductor devices before production is vital for optimizing the device designs and assessing their lifetimes. Simulation of degradation due to high energy carriers is challenging as carrier transport needs to be addressed to obtain the carrier energy distribution function (DF) via solution of the Boltzmann transport equation (BTE). This is a complicated and computationally demanding task. In laterally diffused metal-oxide semiconductor (LDMOS) transistors, for example, their large dimensions, peculiar architecture and high operating voltages make the solution of the BTE challenging. In scaled devices, on the other hand, scattering effects become dominant which makes the estimation of the DF difficult.

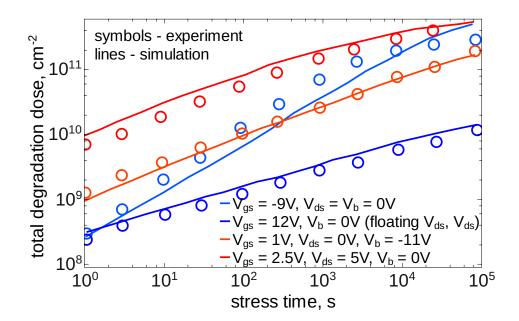

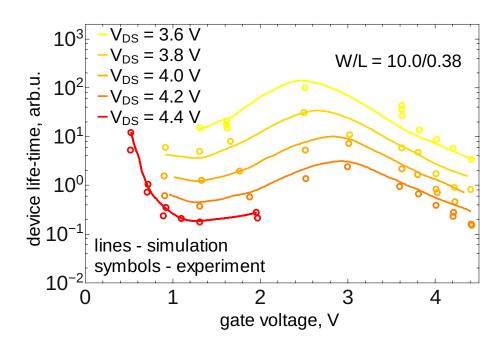

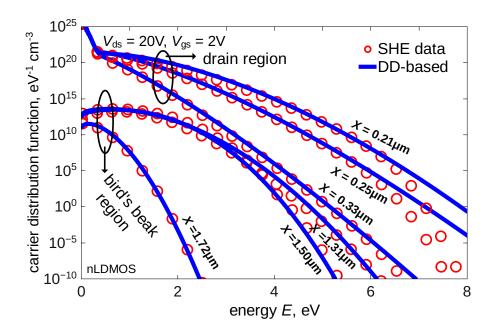

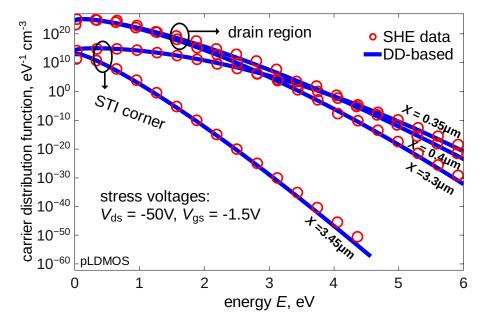

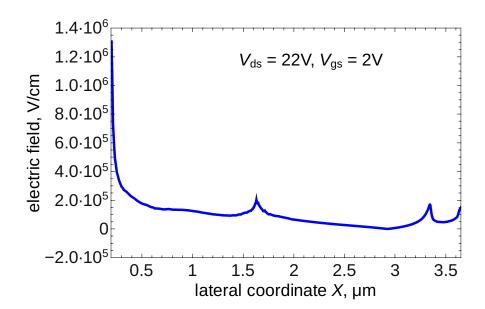

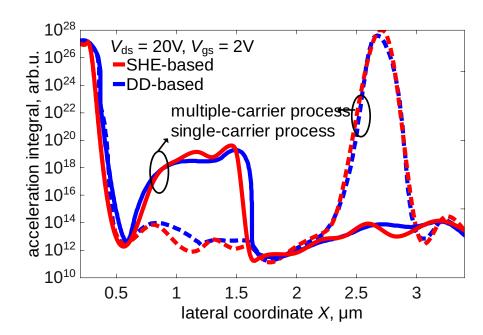

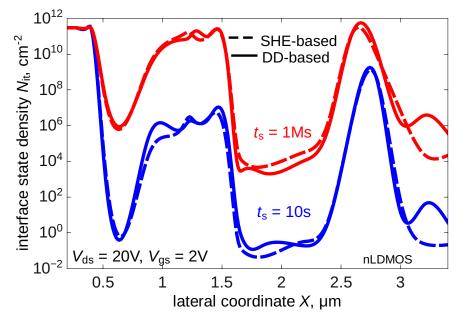

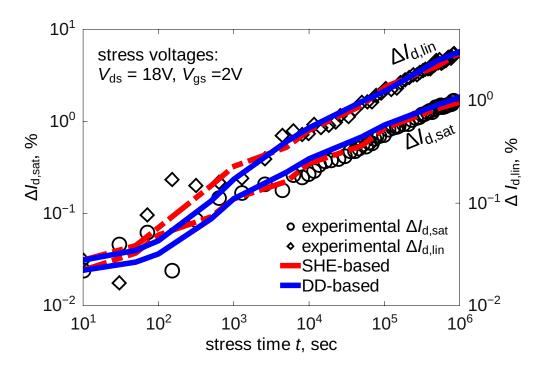

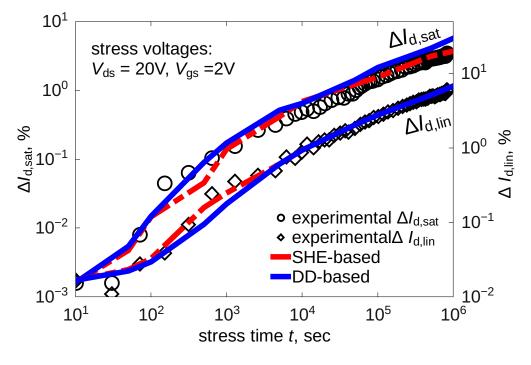

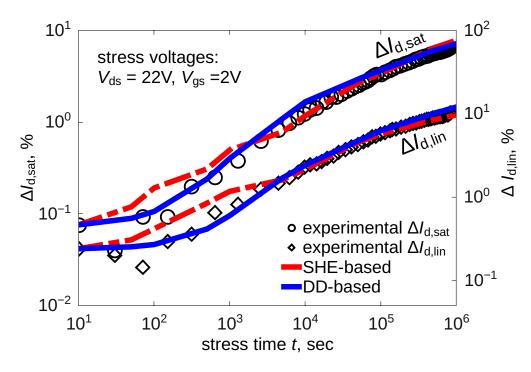

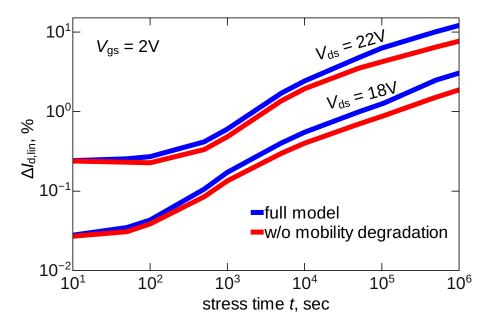

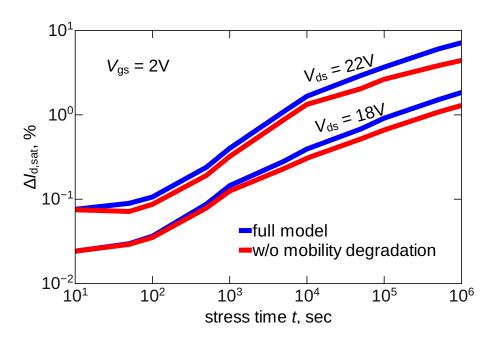

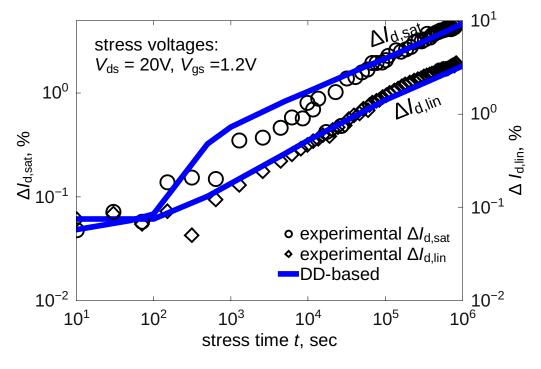

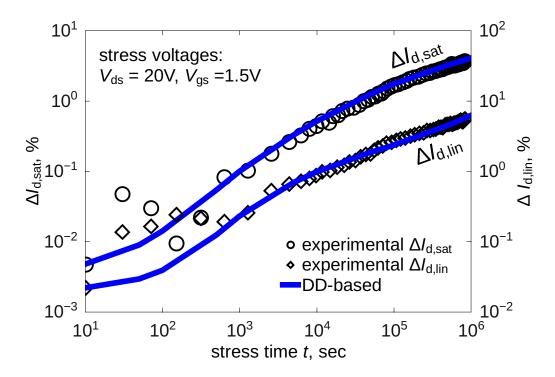

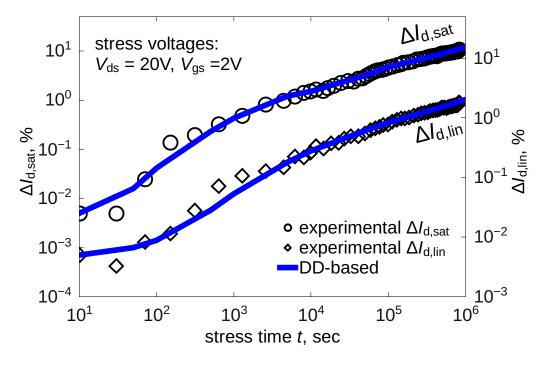

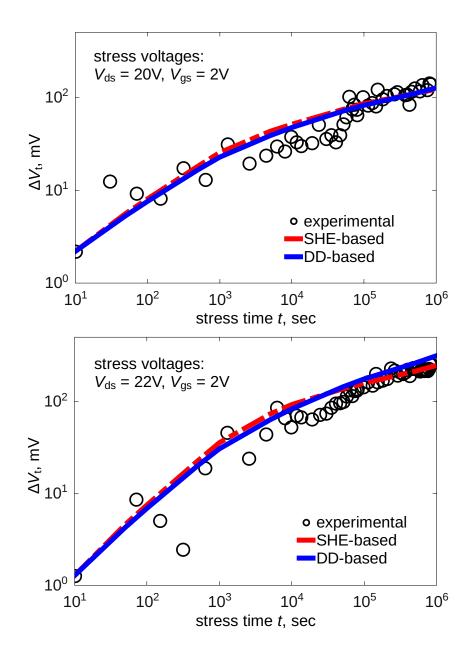

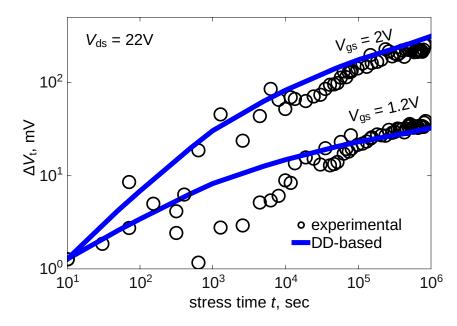

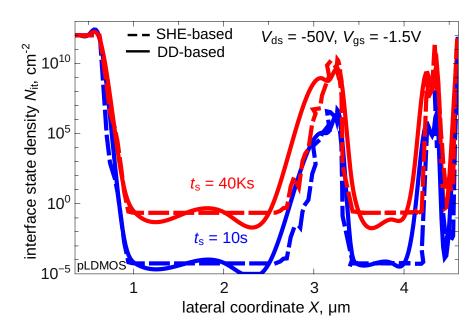

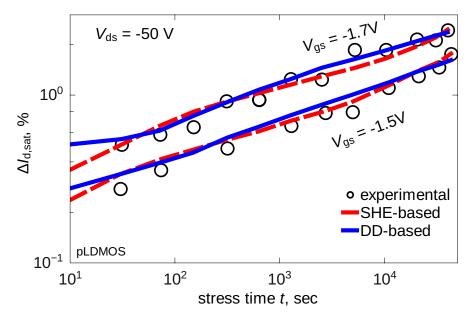

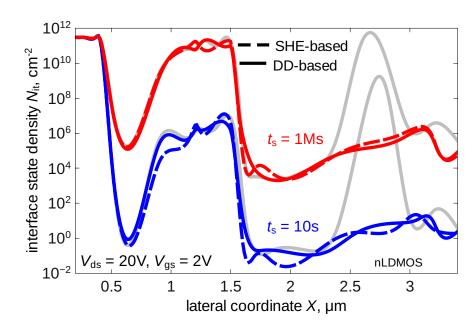

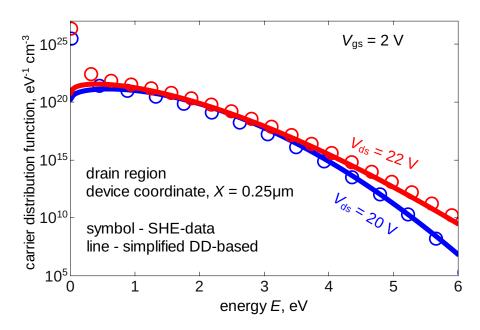

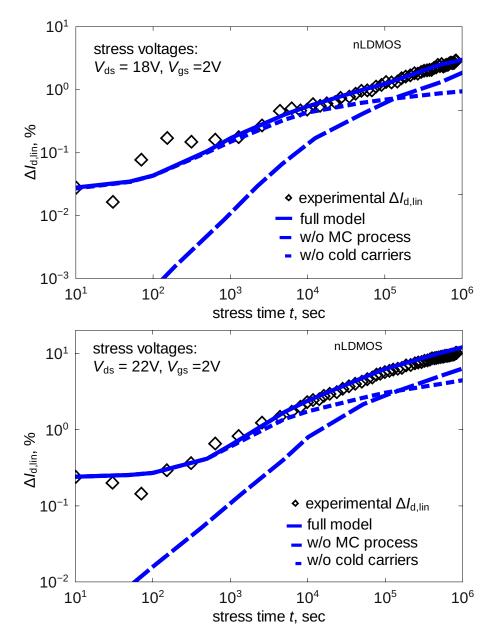

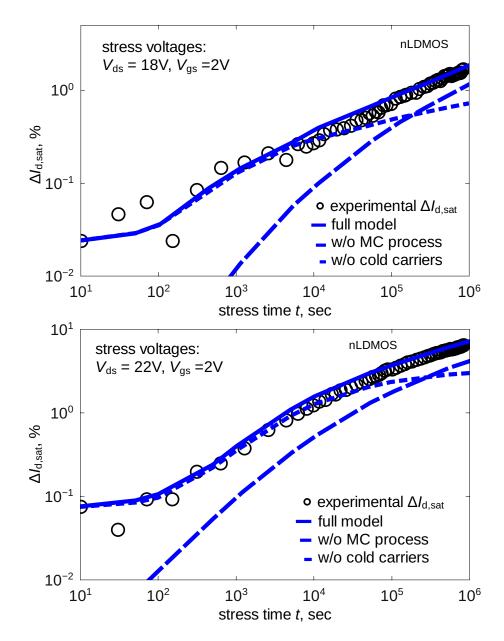

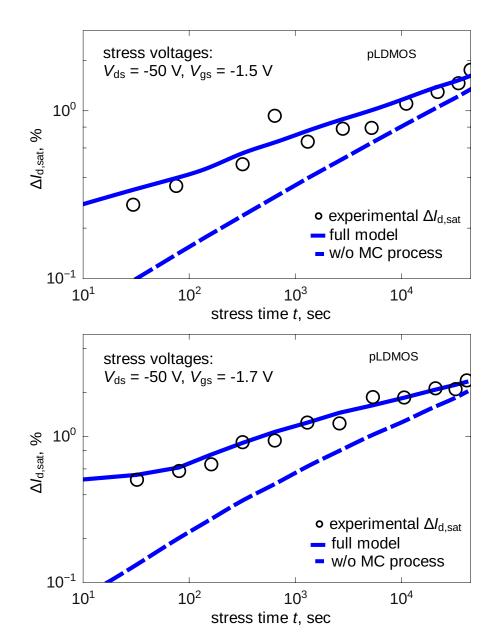

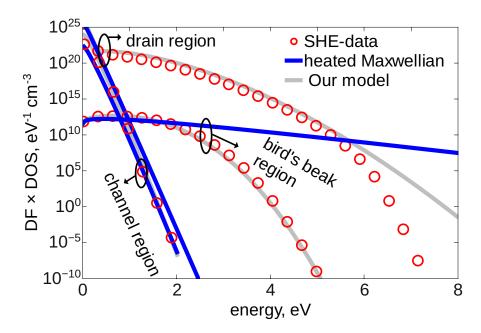

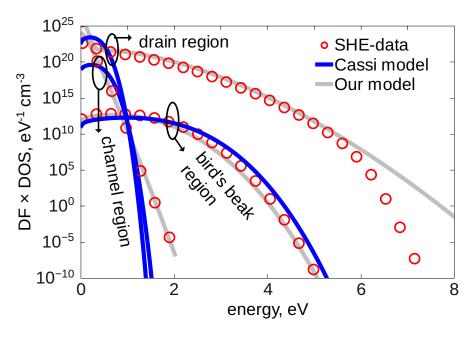

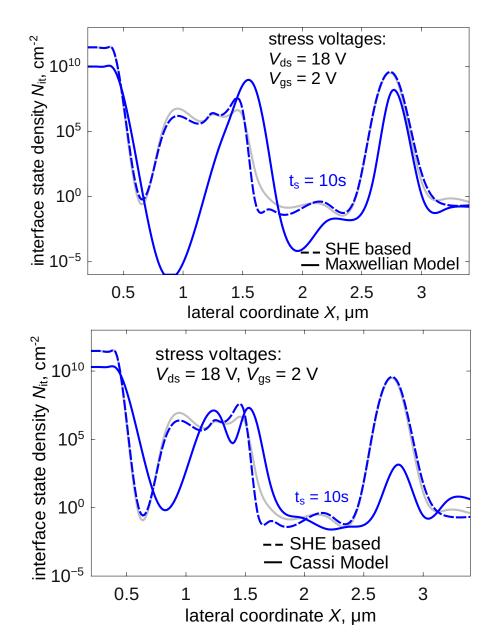

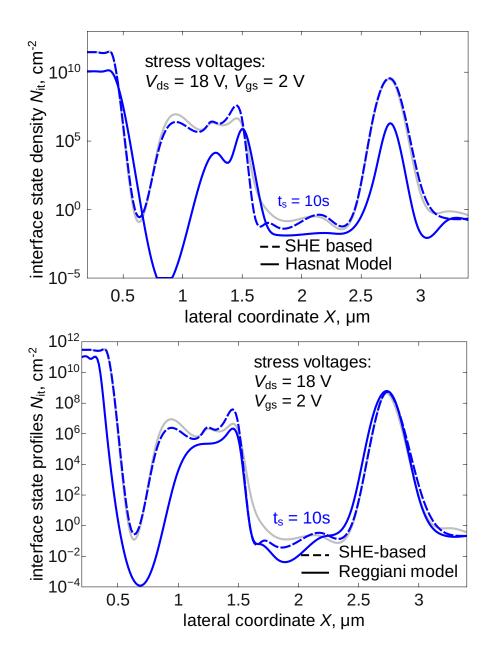

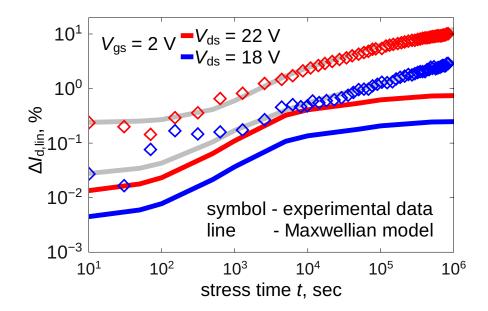

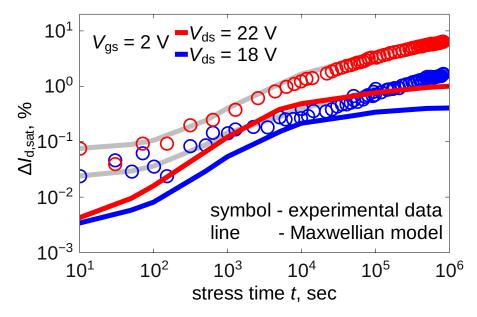

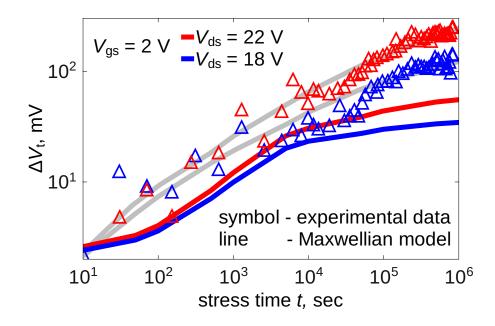

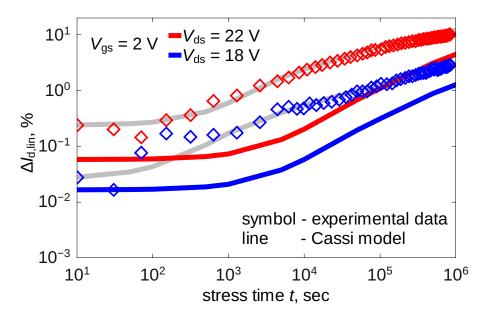

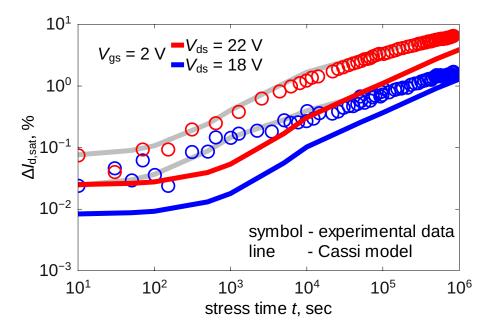

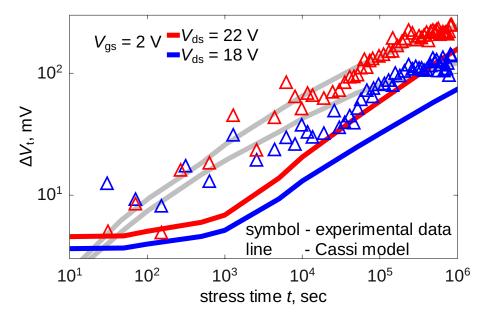

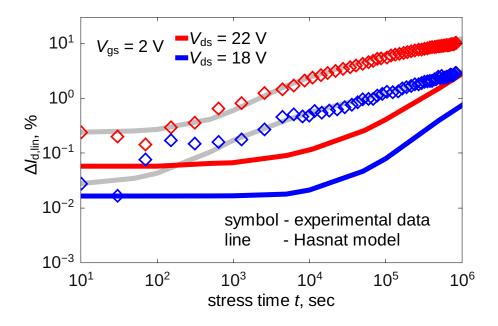

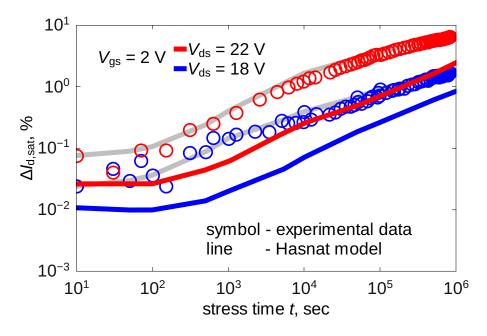

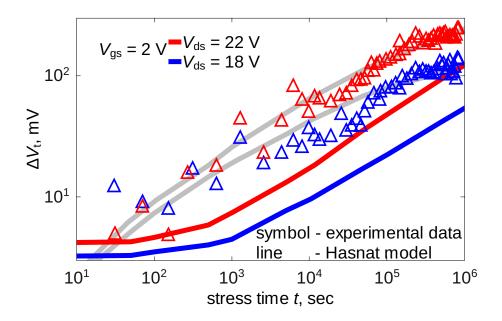

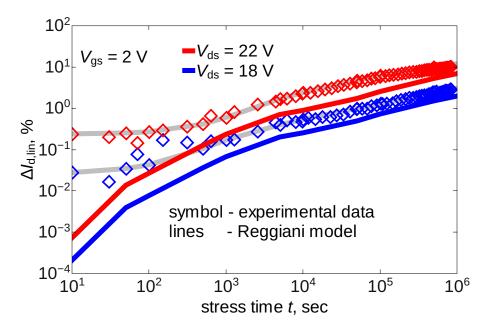

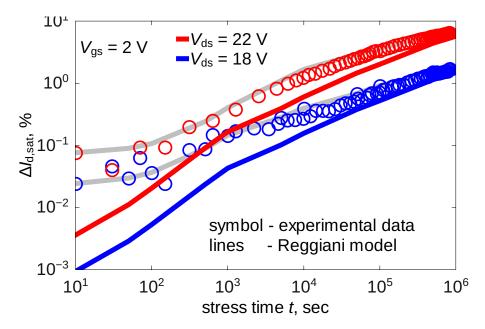

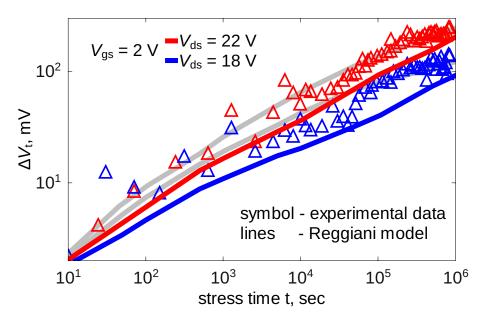

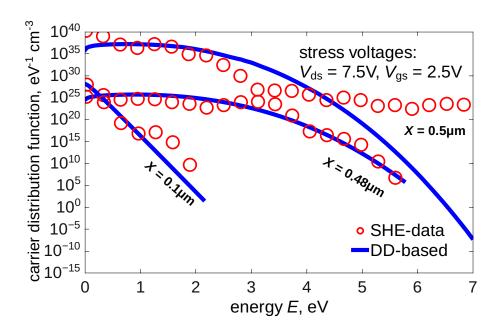

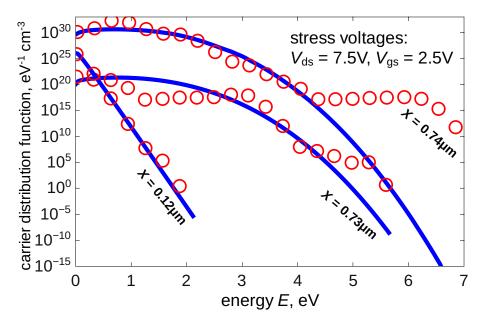

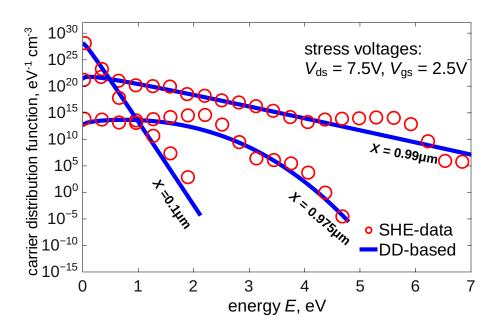

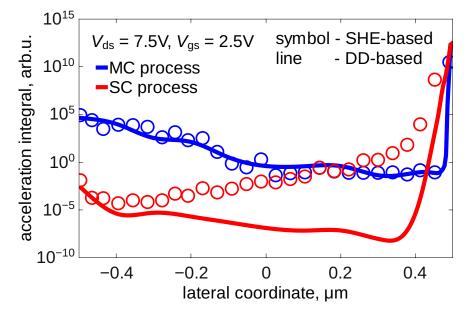

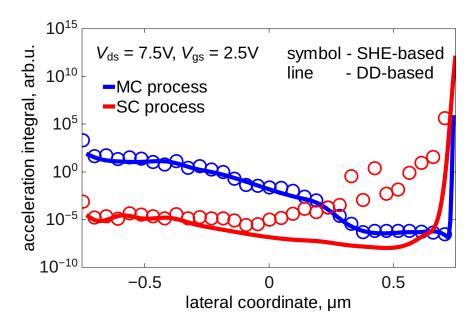

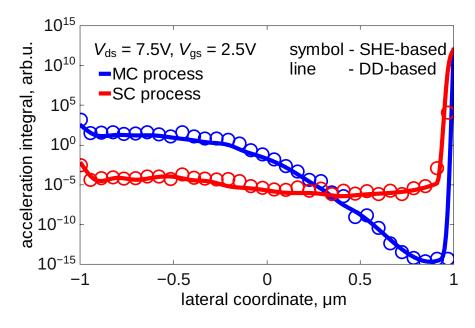

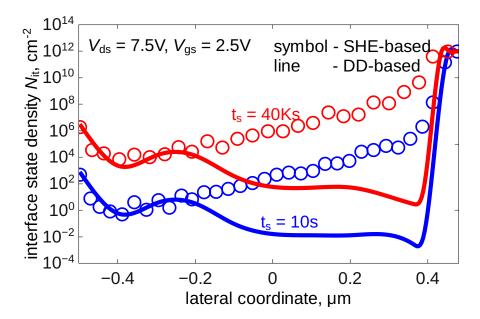

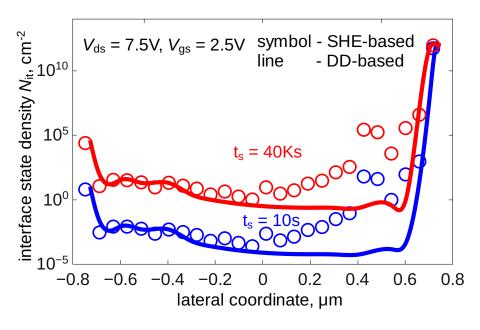

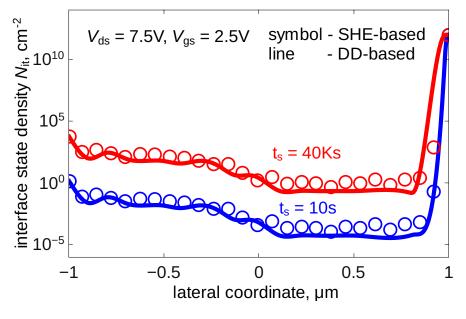

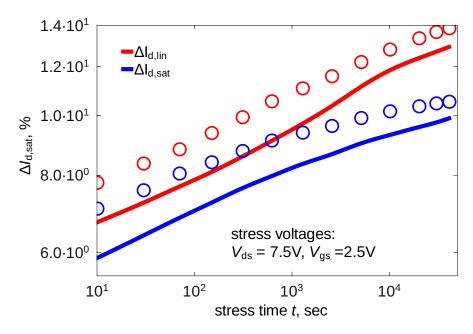

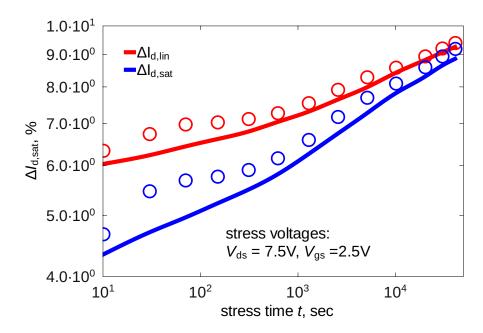

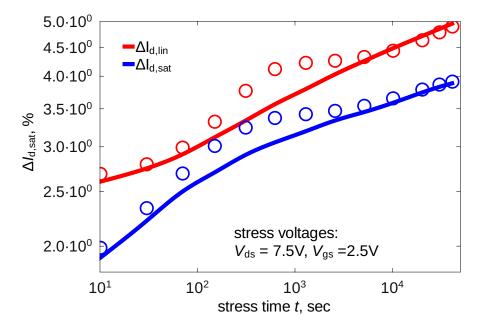

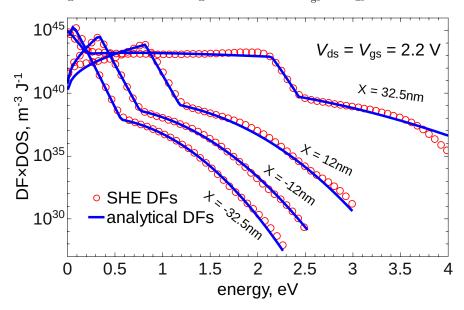

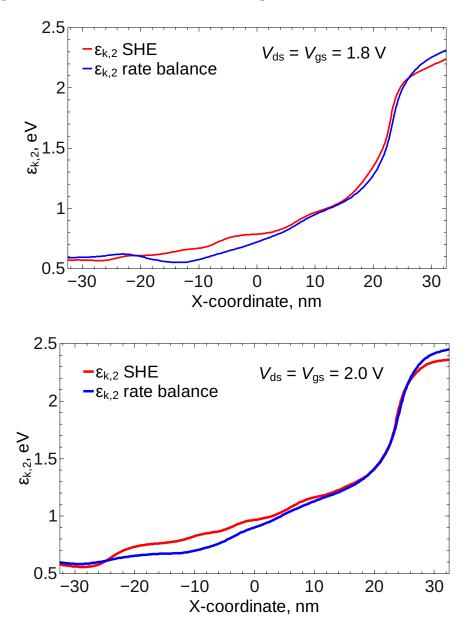

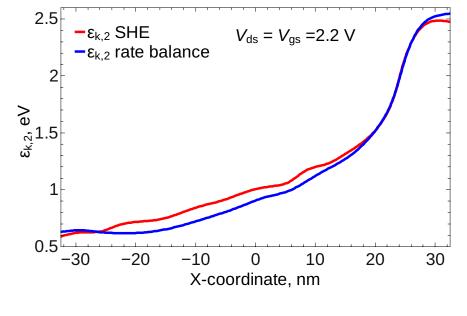

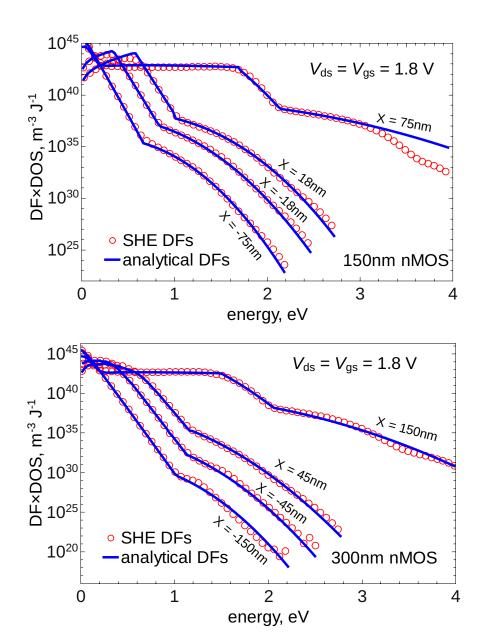

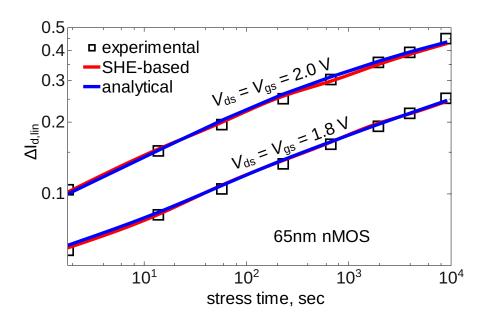

For this purpose, a drift-diffusion based approach is suggested which captures both the hot and cold carriers in the device. As a reference, a solution of the Boltzmann transport equation is performed using the spherical harmonics expansion method. The validity of the DD based approach is tested on LDMOS transistors by simulating the degradation characteristics like the interface state generation rates, the interface state density profiles, and changes of the linear and saturation drain currents as well as the threshold voltage shift and comparing with the spherical harmonics expansion (SHE) based approach as well as measurements. The applicability of different available analytic models for the DF has also been analyzed, namely the heated Maxwellian, the Cassi model, the Hasnat approach, as well as the Reggiani model. The DFs obtained from the different approaches are used as input for the physical HCD model and device degradation characteristics are determined. It is shown that the heated Maxwellian approach leads to an underestimation of HCD at long stress times. This trend is also typically observed for the Cassi and Hasnat models but in these models HCD is underestimated in the entire stress time window. While the Reggiani model gives good results in the channel and drift regions, it cannot properly represent the high-energy tails of the DF near the drain, and thus leads to a weaker curvature of the degradation traces. The analytical model for the carrier DF used in this work is capable of capturing DFs with very good accuracy and, as a result, the change of the device characteristics with stress time. Since the expression for the DF considers the contribution of both the hot and equilibrium carriers, it is well suited for the HCD model used which takes into account the single-carrier and multiple-carrier processes. The comparison of different realizations of the model shows that HCD captured by the DD based approach suggested in this work is very similar to the SHE based approach and matches the experiments quite well.

Particular attention is paid to study the role of the colder fraction of the carrier en-

semble. The role of cold carriers is checked by neglecting their effect in HCD modeling in LDMOS devices stressed at high voltages. In the proposed model, cold carriers are represented by the corresponding term in the analytic formula for the carrier distribution function as well as by the multiple-carrier process of the Si-H bond dissociation. It is shown that even in high-voltage devices stressed at high drain voltages the thermalized carriers still have a substantial contribution to HCD. These results contradict the previous conception that cold carriers are not important for HCD in power MOSFETs.

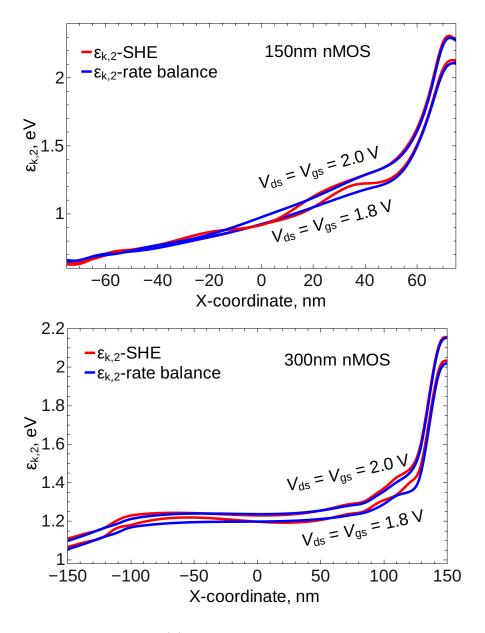

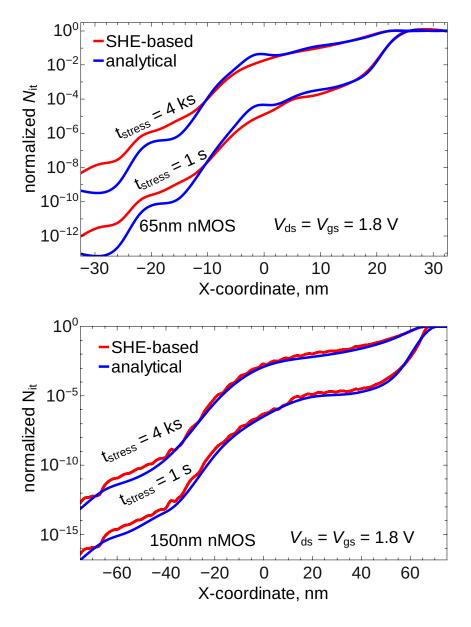

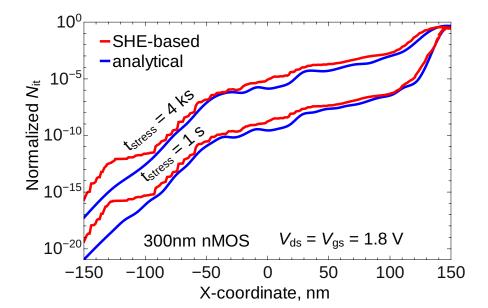

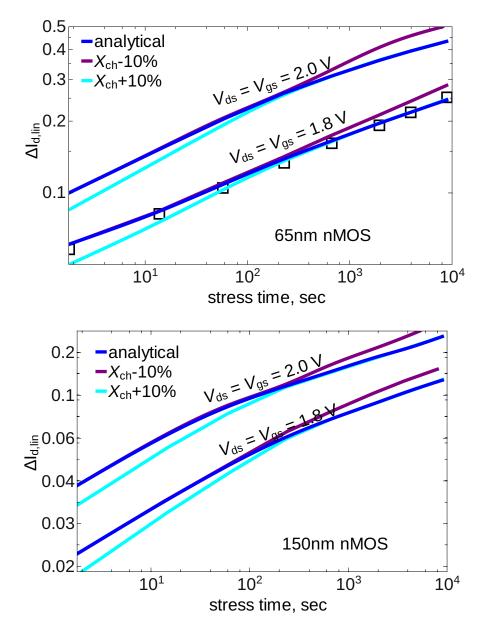

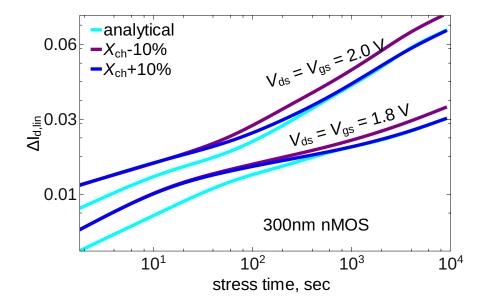

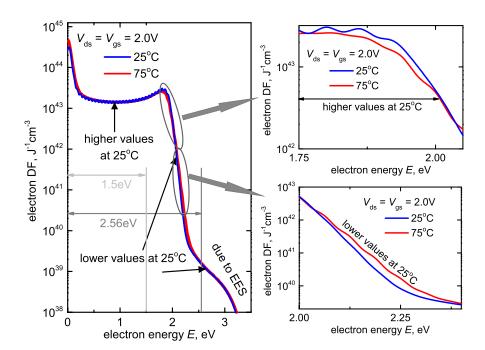

The limits of the DD based HCD scheme is determined using devices of different dimensions. A comparison of carrier distribution functions, bond breakage rates, interface state density profiles, and changes of device characteristics such as the saturation and drain currents obtained from SHE and DD based approaches for MOSFETs with different channel lengths suggests that this DD based approach is not suited for channel lengths less than  $1.5\,\mu\mathrm{m}$ . Also, in scaled devices mechanisms like electron-electron scattering start to affect the DF which cannot be captured with a simplistic approach. Thus, the simplistic DDbased HCD model is extended to the case of decananometer transistors. Special attention is paid to the effect of electron-electron scattering, which populates the high energy tail of the carrier distribution function, by using a rate balance equation. Finally, the accuracy and limits of applicability of the DD-based model are discussed concluding that the model is able to capture hot-carrier degradation in MOSFETs over a range of gate lengths with excellent accuracy.

## Acknowledgments

First and foremost, I am thankful to my wife who always believes in me. She supported me in my decision to pursue a PhD and kept my spirits high along the way. Special thanks to her for bringing our beautiful and cheerful daughter Aira into this world.

Many thanks to Prof. Tibor Grasser for granting me a PhD position and accepting in his prestigious group at the Institute for Microelectronics. His professional and personal guidance has been very valuable. During the course of my studies, he ensured of an ideal environment for high quality research and gave me the opportunity to attend several conferences where I met with highly ranked scientists from all over the globe. Most importantly, his attitude to attain perfection is very inspiring and I hope this inspiration stays with me through the life.

This thesis work would not have been possible without the contributions from Stanislav Tyaginov. He always helped me with his expertise in hot-carrier degradation and gave me invaluable suggestions on my research. I am highly grateful for his patience and understanding and for helping me become a better researcher.

I would like to thank my colleague and dear friend Paul Ellinghaus for all the interesting discussions and rants during our lunch at Mensa. I thank him for keeping me sharp with dosage of challenging puzzles (which he knew I was addicted to and could not get on with my day without solving). I am thankful to the colleagues at the institute Lado, Alex, Yannick, Gerhard, Wolfhard, Santo, Markus, Raffaele, Marco, Cerv for making it a great place to work and have fun. The parties and gatherings at the institute were real stress busters and my only means of social interaction.

Outside of the institute, I am thankful to my friends: Rahul and Neeti for always being loving and caring friends and welcoming me back home, Shubham and Megha for sharing numerous trips and memorable times, Sameer for his advice and support.

I am eternally grateful to my parents who always encourage me to do better and challenge myself. They inspire me to be hardworking and persistent.

Dedicated to my grandmother.

Prateek Sharma

Vienna, May 2016.

# Contents

| 1 | Intr<br>1.1<br>1.2<br>1.3              | Bias Temperature Instability                                                                                                                                                                                                                                                                                          | 1<br>4<br>6<br>9                                         |

|---|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2 | Hot 2.1                                | Measurement Techniques                                                                                                                                                                                                                                                                                                | 1 <b>2</b><br>1 3<br>1 4<br>1 9<br>2 0                   |

| 3 | A R<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | The Hess Model                                                                                                                                                                                                                                                                                                        | 22<br>23<br>25<br>27<br>29                               |

| 4 | The 4.1 4.2 4.3 4.4                    | Carrier Transport  Semi-Classical Transport  4.2.1 Monte-Carlo Approach  4.2.2 Boltzmann Transport Equation  4.2.2.1 Spherical Harmonics Expansion  4.2.2.2 The Moments Method  4.2.2.3 Drift-diffusion  4.2.2.4 Hydrodynamic/Energy Transport Model  4.2.2.5 Six Moments Model  Carrier Energy Distribution Function | 33<br>34<br>35<br>36<br>37<br>37<br>38<br>40<br>40<br>42 |

| 5 | 5.1<br>5.2<br>5.3<br>5.4<br>5.5        | Experiments Simulation Framework Spherical Harmonics Expansion Solution Drift-Diffusion Based Model                                                                                                                                                                                                                   | 47<br>47<br>48<br>49<br>50                               |

|              | Modeling the Degradation in pLDMOS Transistor                                        |           |

|--------------|--------------------------------------------------------------------------------------|-----------|

| 6            | B Hasnat Model                                                                       | 71        |

| 7            | n the Limits of Drift-Diffusion Based HCD Modeling  Model Results for Scaled Devices | <b>81</b> |

| 8            | ole of Electron-Electron Scattering  Extended DD-Based Distribution Function Model   | 97        |

| 9            | onclusions 1                                                                         | .03       |

| A            | ne Basic Semiconductor Equations 1                                                   | 05        |

| В            | alculating the Moments of the Maxwell Distribution 1                                 | 07        |

| $\mathbf{C}$ | nalytical Expression for the Moments                                                 | .08       |

## Chapter 1

## Introduction

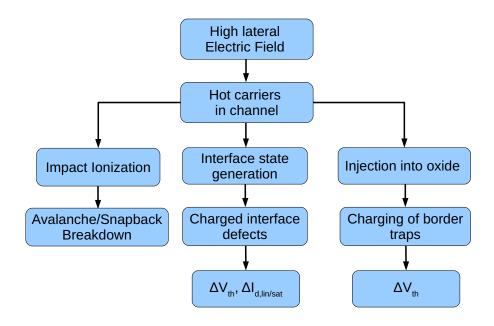

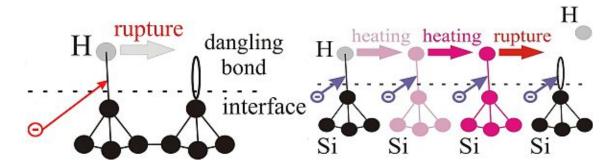

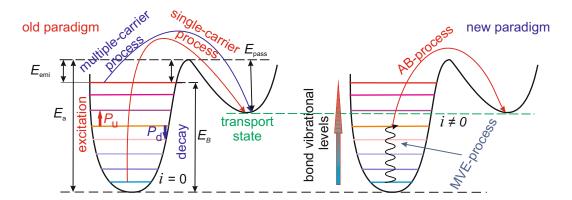

One of the main concerns limiting the lifetime of semiconductor devices is hot-carrier degradation (HCD) [1, 2, 3, 4, 5, 6]. HCD is often assumed to be dominated by the interaction of carriers with the Si-H bonds which are formed at the Si-insulator interface during hydrogen annealing of the unpassivated Si bonds. The rupture of interfacial Si-H bonds leads to the creation of traps which then can capture charges and affect normal device operation. The charged traps perturb the electrostatics of the device, leading to a change in the threshold voltage ( $\triangle V_{\rm th}$ ). The interface defects can also act as additional scattering centers and lead to changes in the mobility  $(\mu)$  and consequently to the degradation of linear and saturation drain currents  $(I_{\rm d,lin}/I_{\rm d,sat})$ , transconductance  $(g_{\rm m})$ , etc. Although the first observation of this detrimental phenomenon dates back over four decades, the full physical picture is complicated and not yet completely understood, making predictive modeling of HCD difficult. As a result, quite often simplified empirical/phenomenological approaches are used [7, 8]. The successful among them are based on the so-called "energy driven paradigm" proposed by Rauch and La Rosa [9, 10, 11, 12]. These approaches introduce three main modes of HCD: (i) governed by the single-carrier (SC-process) mechanism of Si-H bond dissociation, (ii) driven by the multiple-carrier (MC-process) bond breakage process, and (iii) dominated by electron-electron scattering (EES). In the SC-process, a high energy carrier ruptures the Si-H bond in a single interaction. This process is assumed to be the dominant HCD mechanism in metal oxide semiconductor field effect transistors (MOSFET) stressed at high voltages (also referred to as classical HCD). The MC-process involves interaction of the Si-H bonds with multiple low energy carriers which is more typical for scaled devices subjected to HCD at lower voltages. However, it has recently been shown that the MC degradation mode can result in a significant contribution also in high-voltage devices with channel lengths up to  $2 \mu m$  [12, 13, 14], while the SC-process can be important even in decananometer MOSFETs [14, 13, 15].

Therefore, in order to properly represent the contributions of SC- and MC-processes one needs to be able to distinguish between hot and cold carriers. This information is contained in the carrier energy distribution function (DF) which can be obtained from the solution of the Boltzmann transport equation (BTE). There are two main strategies to obtain such a solution: the stochastic Monte-Carlo method [16, 17] and deterministic methods which are based on a representation of the carrier DF by a spherical harmonics expansion [18, 19, 20]. Both methods are numerically quite challenging even for ultra-scaled planar MOSFETs and especially in transistors with 3D architectures. Thereby, the computationally demanding simulations of the carrier energy distribution function are often avoided and the rates of

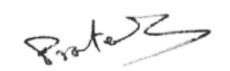

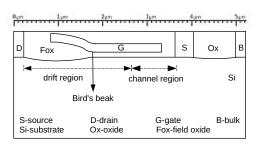

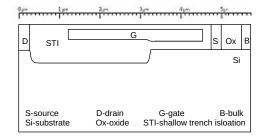

Figure 1.1: Schematic of an nLDMOS transistor showing its complex geometry which makes the transport simulations and HCD modeling challenging.

the aforementioned processes are described by empirical formulas which are related to the macroscopic transistor characteristics [21, 22, 23, 12]. Note that these models are derived and calibrated using accelerated stress conditions. Therefore, it is possible that at real operating conditions the physical picture behind HCD is different, thereby making the models based on empirical expressions not predictive.

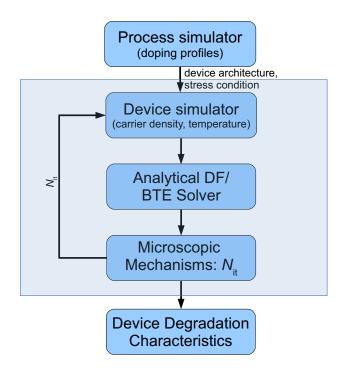

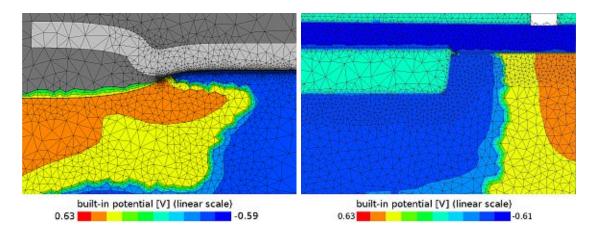

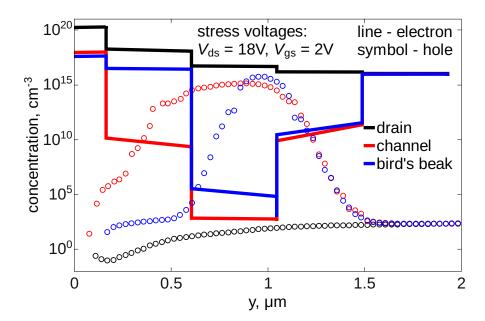

A remedy can be a physical HCD model which covers and links the whole hierarchy of the aspects related to HCD, namely (i) thorough carrier transport treatment which provides the information about the carrier energy distribution needed to (ii) model the microscopic mechanisms of trap generation and the corresponding rates, and to (iii) simulate the characteristics of the degraded devices [15, 24]. The most computationally expensive among these sub-tasks is the carrier transport treatment which requires a solution of the Boltzmann transport equation (BTE). This becomes even more challenging for large devices like laterally diffused metal oxide semiconductor (LDMOS) transistors. First of all, this is related to the typical dimensions of these devices, as compared to nanoscale complementary metal oxide semiconductor (CMOS) transistors, and thus to a mesh which contains a large number of cells. Second, complex transistor architectures with features like a bird's beak, shallow trench isolation (STI) corners and non-planar interfaces, see Figure 1.1, as well as high doping gradients in different regions make the situation worse. Whereas in scaled devices the complexity increases due to increasingly important scattering mechanisms and complex 3D geometries such as those of finFETs. Furthermore, as we have shown [25, 26, 27], both single- and multiple-carrier mechanisms of bond dissociation provide substantial contributions to HCD in these devices.

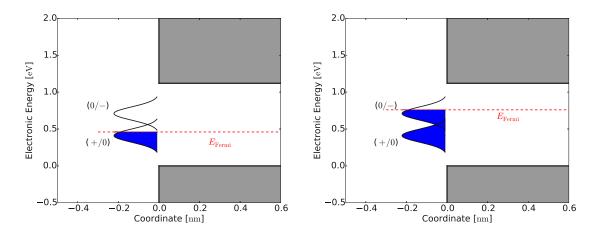

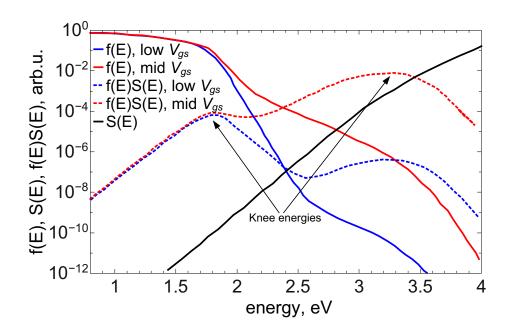

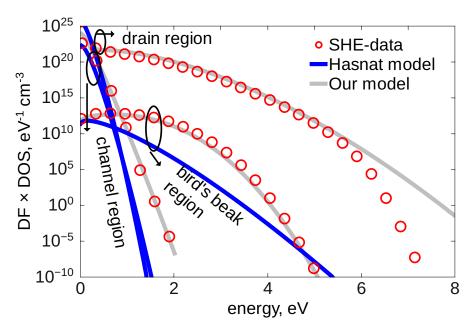

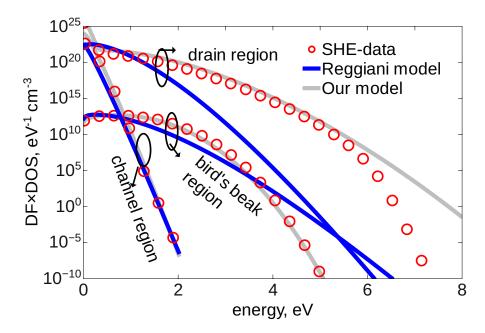

In this context, simplified approaches to the solution of the Boltzmann transport equation such as the drift-diffusion (DD) and energy transport schemes appear to be very attractive [28, 29, 30, 31]. However, these approaches only provide some moments of the BTE rather than the full DF, which then has to be estimated using approximate analytical expressions. The most popular variant is the heated Maxwellian distribution and its modifications like a polynomial in the exponential [32], models developed by Cassi et al. [33], Hasnat and co-authors [34], Reggiani [35], etc. These carrier DFs are based on quantities such as the electric field or the carrier temperature obtained from a simplified moment-based BTE solution. Among them, the most successful model has been developed by Reggiani et al. which is suitable for the analytic description of DFs in LDMOS devices with a shallow trench isolation [35, 36]. The Reggiani model is able to represent the degradation of the device quite well when applied to HCD. Recently, the model has

been demonstrated to work for LOCOS and STI-based LDMOS devices [37, 38]. However, the model has some difficulties in capturing the high-energy tail of the DF in the drain region and leads, therefore, to a less accurate description of the degradation in the drain area of the LDMOS. The inherent simplifications in all the above mentioned models limits their applicability and, thus, they cannot always substitute the solution obtained from the BTE. In this work, an analytical approach based on the physical mechanism is developed for DFs and HCD prediction.

The structure of the thesis is as follows: In order to precisely model the device degradation due to HCD, it is important to understand the difference between different reliability issues in semiconductor devices. Thus, the different degradation mechanisms and available carrier transport models in microelectronic devices are discussed in Chapter 1. The three main reliability issues discussed are: bias temperature instability (BTI), hot-carrier degradation (HCD) and time dependent dielectric breakdown (TDDB). BTI is mainly attributed to the creation of oxide defects and interface traps due to applied bias at elevated temperatures while the carriers are in equilibrium [39, 40, 41]. HCD, on the other hand, occurs due to the generation of defects at the oxide-semiconductor interface by the impinging high energy carriers [1, 7]. TDDB is a result of a percolation path in the dielectric which develops due to an applied field across the insulator [42, 43].

Chapter 2 is focused on HCD which is of most relevance for this work. This chapter also discusses the different experimental techniques used to extract interface state density profiles which are an important metric of degradation. Chapter 3 gives an overview of the existing HCD models, while Chapter 4 deals with the hot-carrier degradation model derived by our group [13, 25, 44]. Since the accurate description of HCD requires evaluating the carrier distribution function via a solution of the Boltzmann transport equation, special emphasis is given to the spherical harmonics expansion and the drift-diffusion methods. Thus, two versions of the HCD model have been used in this work, one based on carrier transport treatment by means of deterministic solution of the Boltzmann transport equation and another uses the simplified drift-diffusion scheme. In the latter implementation of our model an analytical expression is employed to approximate the carrier energy distribution function for the entire device. In Chapter 5, the results of both versions of the model are compared against experimental data for the n-and p-channel LDMOS transistors and a conclusion on the validity of the DD-based approach is drawn. The results suggest the efficiency of the DD-based method for predictive HCD simulations of LDMOS devices. The contribution of cold carriers to hot-carrier degradation is also analysed. The effect of cold carriers in our HCD model is twofold: firstly, a cold carrier term is used in the energy distribution function to account for low energy carriers, and secondly, the cold carriers determine the multiple-carrier process of Si-H bond dissociation.

Chapter 6 compares the different models for calculating the carrier DFs. The DFs obtained from the different approaches are used in our HCD simulations to predict the degradation in nLDMOS devices [45]. The simulated changes in device characteristics are compared to experimental data and conclusions on the validity of each model are drawn. Since all models use the same parameter set, the differences in the results can be directly traced back to inaccuracies in the approximation of the DF. Chapter 7 explores the limits of the DD-based method for obtaining the carrier energy DF. The analytical approach is used on planar devices with different dimensions and the HCD predicted by the SHE- and DD-based approaches are compared. The results suggest that the DD method to obtain the carrier DF looses its validity for devices scaled beyond 1.5  $\mu$ m. Chapter 8 deals with an

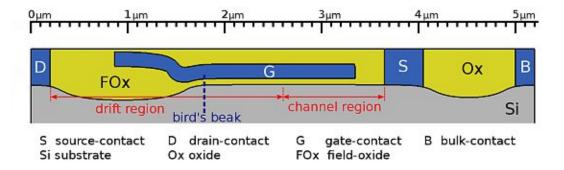

Figure 1.2: The threshold voltage shifts during NBTI stress  $(t_s)$  and recovery  $(t_r)$  in a pMOSFET with a 2.2 nm thick SiON oxide [46]. Dotted, dashed and solid lines represent the recoverable, permanent and the total degradation, respectively, obtained from simulations using the NMP model, while the symbols represent the experimental data. The measurements and simulations were performed with a subsequent increase in stress duration. The recovery curves suggest that the device does not fully recover within the given experimental window.

extension of our DD-based model to decananometer MOSFETs by incorporating the effects of electron-electron scattering on the carrier distribution. In Chapter 9, some conclusions are drawn, while Chapter 10 discusses future refinements and an outlook towards predictive HCD modeling.

### 1.1 Bias Temperature Instability

Bias temperature instability refers to the time-dependent instability in transistors which accelerates when bias and temperature are increased. It is particularly observed when a high voltage is applied to the gate contact of a transistor at elevated temperature, while the other contacts remain grounded. Previously BTI was considerable only in p-channel MOSFETs, especially with SiON gate dielectrics, due to hole trapping and interface state generation, but negligible electron trapping [1, 47, 48]. However, with the use of high-K dielectrics, both n- and p-channel MOSFETs can exhibit considerable BTI due to electron and hole trapping in the high-K and interfacial oxide layer [49, 50]. Another factor leading to pronounced BTI in modern devices is the aggressive down-scaling giving rise to high electric fields to maintain a reasonable subthreshold leakage. Increase in the density of integrated circuits for ultra large scale integrated systems on chips also leads to an increase in the power dissipation and self heating.

The BTI in n- and p-MOS transistors is observed when a positive or a negative voltage is applied at the gate and thus the phenomenon is referred to as positive bias temperature instability (PBTI) or negative bias temperature instability (NBTI), respectively. The consequence of BTI is a change in the threshold voltage in the inversion mode, thus, leading to a change in the drain current. BTI also affects other device parameters such as transconductance and gate-drain capacitance. In CMOS circuits this would mean performance degradation such as reduction of the switching speed. This degradation is usually attributed to chargeable defects, for instance the hydrogen bridge and the hydroxyl E'centers [51, 52, 53]. The other contributors to BTI are interface traps. These defects are present directly at the interface (represented with a density  $N_{\rm it}$ ) of the substrate and gate insulator in MOS devices [39, 40]. The capture and emission of charge carriers by these defects causes changes in the electrostatics of the device which disturb its functionality. For example, the threshold voltage in a p-MOSFET is given by [39]

$$V_{\rm t} = \Phi_{\rm MS} - \frac{Q_{\rm ox}}{C_{\rm ox}} - \frac{Q_{\rm it}(2\Phi_{\rm F})}{C_{\rm ox}} - 2\Phi_{\rm F} - \frac{Q_{\rm S}}{C_{\rm ox}},$$

(1.1)

where  $\Phi_{\rm MS}$  is the work function difference between the gate and the substrate,  $\Phi_{\rm F}$  the Fermi potential,  $Q_{\rm ox}~(=qN_{\rm ot})$  the oxide charge density,  $Q_{\rm it}~(=qN_{\rm it})$  the interface charge density,  $Q_{\rm S}$  the semiconductor charge density, and  $C_{\rm ox}$  the oxide capacitance per unit area. The oxide and interface charges denote the charges trapped by corresponding defects and, thus, Equation 1.1 approximates the relation between the threshold voltage and the change in the oxide and interface charge densities. It should be noted that Equation 1.1 assumes that the oxide capacitance  $C_{\text{ox}}$  remains unchanged during stress [54]. A characteristic feature of BTI is recovery, meaning that upon the removal of stress the device parameters tend to attain their original values as shown in Figure 1.2. The difference between the original and recovered values of the parameters is often called the permanent component of BTI. In the past, the recovery of BTI was largely attributed to  $N_{\rm ot}$  recovery on removal of stress, while the  $N_{

m it}$  were considered to remain unchanged during the recovery phase [55]. However, this differentiation is often debated and it was shown that  $N_{\text{ot}}$  also contributes to the permanent component of BTI [57], thereby making the characterization of BTI much

A majority of the modeling attempts focus on NBTI as it is a severe problem in  $Si/SiO_2$ based devices. In this respect, the Reaction-Diffusion (RD) model and its extensions have been widely used [58, 59, 60, 61]. Within the framework of the RD model, the reaction phase consists of interface trap generation and release of hydrogen as a consequence. The reaction is diffusion-limited. The released hydrogen is then assumed to diffuse into the oxide during the stress. This diffusion is dependent on the stress time. During the stress phase the degradation, i.e. interface state generation, predicted by the RD model typically depends on stress time as  $t^n$  [39]. However, the relaxation or recovery has not been adequately explained by any extension of the RD model.

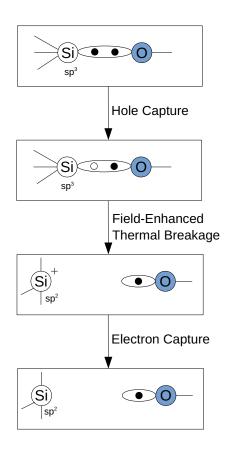

The RD models have proven to be inaccurate and later studies have linked NBTI to reaction-limited processes like charge trapping and interface state generation [55, 62, 63, 64. Some better descriptions were given by the double and triple well models where the diffusion of hydrogen is replaced by dispersive bond-breaking [59, 65, 66]. A more advanced model which was devised to explain the more complex experimental data was the two stage model [67]. This model suggested hole capture to occur in the gate oxide due to the presence of border traps instead of the Si/insulator interface. The introduction

Figure 1.3: Description of the neutral and charged states of an example oxide defect within the four state model framework. A hole capture event in the equilibrium state creates the metastable state 2' which can relax to a positive stable state 2 and an E' center is created. Upon electron capture, the E' center is neutralized into the metastable state 1'. Now hole capture can cause a transition back to state 2 or a structural relaxation can lead to the original equilibrium state 1. From [56].

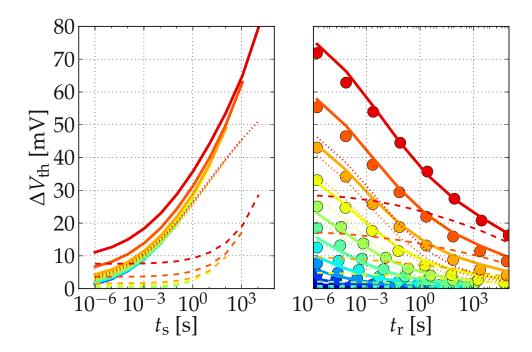

of time dependent defect spectroscopy (TDDS) has enabled detailed investigations of the charging and discharging of single defects. These investigations have led to the formulation of the four state model based on the non-radiative multiphonon (NMP) theory [68]. This model suggests the existence of two metastable states along with the conventional charged and neutral states. Within the NMP framework, the capture and emission time maps are derived using the carrier capture and emission time constants for the transitions between different states, shown in Figure 1.3. The distribution in the capture and emission time maps is mainly governed by the equilibrium occupancy difference which also describes the average contribution of a defect to the threshold voltage [69, 46]. The four state model not only explained the observations in BTI and TDDS experiments but also random telegraph noise (RTN) and flicker noise. These have been attributed to random exchange of charges between defects and the substrate during stationary conditions [70, 56]. The NMP model is highly effective in representing many more BTI characteristics when combined with a two well model for interface state generation.

### 1.2**Hot-Carrier Degradation**

Similar to BTI, HCD is also related to the build-up of defects at/near the Si/SiO<sub>2</sub> interface. However, during BTI stress, the electric field component along the channel is usually constant as the source and drain contacts are grounded. Thus, only the perpendicular component of the oxide field plays a role in defect creation. Hot carrier degradation, on the other hand, occurs when a voltage between source and drain is applied, leading to

Figure 1.4: The high energy carriers in the conduction band break the Si-H bonds at the interface leading to the creation of interface defects. From [71].

the increase in the carrier flux along the channel. This makes HCD even more complex due to the simultaneous action of the two electric field components. Therefore, one can conclude that HCD has one more degree of freedom than BTI. For example, in a MOSFET, when the drain to source voltage becomes comparable or greater than the gate voltage, the inversion layer is no longer homogeneous along the channel and the carrier concentration is higher near the source. In the saturation region pinch-off occurs at the drain side. This results in a high field region near the drain leading to an increased energy of the carriers travelling from the source to the drain. These high energy carriers strike the interface breaking the Si-H bonds [72]. Additionally, the energetic carriers may lead to generation of electrons and holes by impact ionization which further facilitate Si-H bond breakage [1]. This leads to the creation of interface defects and/or charging of the already present defects, see Figure 1.4. Some of the carriers with sufficient energy to overcome the energy barrier might get injected in the oxide and create or charge oxide defects.

The high electric field near the drain region causes strong localization of the HCD near the drain or the pinch-off region as has been reported in various studies [73, 1, 5, 7]. This localization of damage is another factor that distinguishes HCD from BTI. In modern scaled devices as well as in high voltage devices, the channel hot-carrier degradation is the main regime among the many regimes of HCD identified in literature. Other HCD mechanisms are drain avalanche, secondary generated hot-carrier, substrate hot-carrier, Fowler-Nordheim and direct tunneling [1, 74]. Drain avalanche and secondary generated hot-carrier mechanisms occur due to electron-hole pair generation from impact ionization, see Figure 1.5. Substrate hot-carrier degradation originates from injection from the channel-substrate p-n junction [75]. In Fowler-Nordheim emission, the carriers overcome the triangular potential barrier and are injected into the SiO<sub>2</sub> conduction band, while in direct tunneling carriers tunnel to the channel overcoming the trapezoidal potential barrier. Both Fowler-Nordheim and direct tunneling are quantum mechanical effects and are observed in scaled devices. Note that direct tunneling is observed in very thin oxides while

Figure 1.5: Steps involved in hot-carrier degradation

Fowler-Nordheim tunneling can occur in thicker oxides but requires a higher applied potential. Although HCD is a more general term, in this work it will be used to refer to the channel hot-carrier degradation mechanism.

The dominance of interface trap generation in hot-carrier degradation has been universally accepted for almost all technologies [76, 77, 1, 25]. Several stress and recovery measurements, see [78], show the absence of a recoverable component in HCD which leads to a controversy regarding the contribution of oxide traps as discussed in Section 1.1. The recovery in device degradation measurements is attributed to  $N_{\rm ot}$  traps, whereas no recovery indicates pure  $N_{\rm it}$ . Moreover, many studies suggest an absence of oxide trap contribution to HCD [79, 80, 81]. NBTI and HCD also differ in their response to elevated temperatures. While NBTI is found to worsen with a rise in temperature for all devices [68], HCD becomes less pronounced in long-channel/high-voltage devices with increase in temperature [82, 83, 84]. For scaled devices, on the other hand, HCD aggravates at high temperature as electron-electron scattering populates the high energy fraction of the ensemble [85, 86]. Alternatively, the importance of electron-electron scattering in HCD has been disputed by others [87] and the cause for the increase in HCD is attributed to a mixed-mode process [87]. Recently, HCD was found to decrease at elevated temperatures in MOSFETs with SiON gate dielectric [88]. At low stress voltages, the degradation was observed to be less severe with increasing temperature, while at higher voltages no change in degradation was observed with increase in temperature. This behavior was explained as being due to different thermal responses of the two bond breakage mechanisms. The rate of the multiple-carrier process was found to decrease and the rate of the single-carrier process increased with increasing temperature [88]. In a few other investigations, HCD accelerated by self-heating has been suggested to be an important reliability concern in modern devices [89, 90]. Thus, there are a number of complex factors that collectively

Figure 1.6: Development of a percolation path in a dielectric resulting in its breakdown.

contribute to HCD

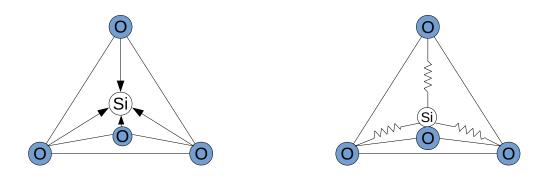

Figure 1.7: The tetrahedral SiO<sub>2</sub> structure with the arrows indicating the direction of the Si-O bond dipole moment. The strained bond is also shown where the distortions in the bond are induced by the electric field.

and need to be considered in modeling. The situation becomes even more complex when BTI mixes with HCD [91].

A comprehensive summary of widely used HCD models is presented in Chapter 3. A majority of these models are empirical while a few are physics based. However, a common feature among all modeling attempts is the interface state creation process which is controlled by the manner how the carriers are distributed over energy. Thus, the carrier energy distribution is the most important ingredient in modeling of HCD.

### Time Dependent Dielectric Breakdown 1.3

Silicon dioxide, the native oxide of Si, has been traditionally used as dielectric in Si based devices due to its large bandgap and its high breakdown field. However, application of

Figure 1.8: The hole-catalyzed, field-enhanced bond breakage process. A hole-capture event weakens the bond which can then be broken thermally or by a high electric field, thus, creating a defect. From [93].

stress, such as high electric field, for long stress times can cause the dielectric to loose its insulating property. Moreover, the continuous down-scaling of transistors causes high electric fields across the dielectric which further increase the risk of failure. Dielectric breakdown can be intrinsic or extrinsic. Intrinsic breakdown occurs due to the structure of the dielectric material like crystal defects, dielectric thickness, etc. Extrinsic breakdown, on the other hand, can be caused by introduction of defects during the technological steps to manufacture the device.

Time dependent dielectric breakdown (TDDB) is observed in devices which use silicon dioxide or high-K materials. TDDB refers to the transition of the insulator from its insulating phase to a conductive phase with time when a constant electric field, smaller than the breakdown field, is applied. While the complete molecular picture is still speculative, the phenomenon is often attributed to the polar nature of the dielectric [92]. In  $SiO_2$ , local electric fields cause distortion in the silicon-oxygen bond leading to the possible creation of an oxygen vacancy (dangling bond) via bond breakage or coordination breakage. The coordination breakage refers to displacement of the Si ion from the fourfold coordination to a threefold coordination in the tetrahedral SiO<sub>2</sub>. The coordination breakage requires

much less energy than bond breakage and is considered the primary mechanism behind TDDB [93]. TDDB stress leads to generation of traps which create a percolation path, as shown in Figure 1.6, which triggers the breakdown of the insulator [94]. Time dependent dielectric breakdown can only be described statistically as nominally identical devices subjected to the same stress break down at different times. This is also the case for BTI and HCD in scaled devices. Thus, the failure probability has to be described statistically. This description allows to extract the device lifetime [95].

Breakdown in oxides thicker than 5 nm occurs abruptly after a certain electric field. Thus, a large jump in the voltage/current vs. stress time curve is observed. This effect is known as hard breakdown. In thinner oxides, on the other hand, soft breakdown occurs where the change in voltage/current with stress time is not very abrupt and the magnitude of change is many orders lower than in hard breakdown [43, 96].

Various TDDB models which consider field-induced degradation, current-induced degradation or a combination of both have been suggested [93, 97, 98, 99]. The field dependent models suggest the logarithm of time to breakdown to be proportional to the oxide electric field. One of these models is the thermochemical E-model. Within this model, bond breakage is triggered by the interaction of the Si-O bond, which is strained due to the local field (see Figure 1.7), with the lattice [97]. Thus, the bond breakage is considered to be a phonon driven process. The time to breakdown is given as  $t_{\rm BD}=A_0\exp\left[\gamma E_{\rm ox}\right]\exp\left[E_{\rm a}/k_{\rm B}T\right]$ . However, the E-model was unable to explain the polarity dependence of TDDB [100].

The current driven model is the so-called 1/E model (the logarithm of time to breakdown is inversely proportional to the oxide electric field) where the damage is associated with the current flowing through the dielectric [93]. According to the 1/E model, the electrons tunneling through the dielectric from the cathode to the anode excite an electron from the valence band to the conduction, and leave a hole behind [101, 102]. On gaining energy, the holes can tunnel back into the oxide and create oxide traps. Thus, this model is also called Anode Hole Injection model (AHI). Emission of carriers through  $SiO_2$  is due to Fowler-Nordheim (FN) tunneling which requires high fields (>6 MV/cm) [103]. The 1/Edependence of time to breakdown is given as  $t_{\rm BD} = \tau_0 \exp[G/E_{\rm ox}]$ . If deep traps exist, trap assisted tunneling can lead to pre FN conduction. Since FN conduction is temperature independent, the current model was unable to explain the temperature dependence of TDDB [104]. Moreover, according to this model, breakdown occurs when a critical hole fluence is reached which has no physical explanation [105].

Other models for specific devices, such as the power-law voltage model [106, 107, 108] for thin dielectrics with transport in the ballistic regime and the exponential model [109, 110] for low-k dielectrics, have also been proposed. It has been suggested that TDDB can be better explained by a combination of field and current driven approaches [42, 111]. This combination suggests that the field strains the Si-O bonds which can then be excited by the carriers constituting the current flow. Figure 1.8 shows one of these scenarios where the bond breakage process is hole-catalyzed and enhanced by the field. Thus, the activation energy is reduced and the bond can be easily broken by phonon interactions. The combination of both field- and current-based models seems the most practical solution for modeling TDDB.

## Chapter 2

# Hot-Carrier Degradation

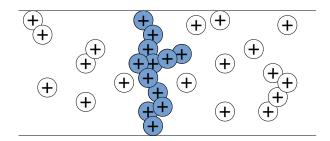

The semiconductor device fabrication process requires the growth of a dielectric, such as amorphous silicon gate oxide  $(SiO_2)$  or high-k dielectric such as  $HfO_2$ , on the crystalline silicon bulk/substrate (Si). The lattice mismatch at the interface of the dielectric and the substrate induces mechanical stress, leaving some of the Si atoms unsaturated. In other words, some Si atoms do not form four bonds with neighboring atoms to complete the octet. As a result, they carry up to two unpaired electrons, thereby creating two trap levels in the Si bandgap. This corresponds to electrically active Si dangling bonds which are visible in paramagnetic spin-resonance experiments [112, 113]. A large number of the unsaturated Si bonds are passivated with H gas during post-grow anneal. This creates electrically inactive Si-H bonds at the interface and shifts the corresponding energy levels out of the Si bandgap [114, 115]. However, during stress/operation of the device at high electric fields, carriers with high energies (as shown in Figure 1.4) can break the Si-H bonds, thereby creating interface traps. These defects at the interface are characterized by a density called the interface state density  $N_{

m it}$  (cm $^{-2}$ ), which represents the number of interface traps per unit area or  $D_{\rm it}$  (cm<sup>-2</sup> eV<sup>-1</sup>), the number of interface traps per unit area distributed across the energy bandgap [39]. The electrically active interface defects lead to

Figure 2.1: Interface trapped charge depending on the Fermi level. The traps between  $E_i$ and  $E_{\rm F}$  are occupied, while others are neutral. Traps are negatively charged if the Fermi level is above  $E_i$ , and positively charged if the Fermi level is below  $E_i$ .

Figure 2.2: Charge pumping measurement setup. The source to substrate and drain to substrate diodes are typically slightly reverse biased while the gate is pulsed between inversion and accumulation conditions. The substrate current is typically measured as the charge pumping current.

a threshold voltage shift  $(\Delta V_t)$  and the degradation of the drain current  $(\Delta I_{\rm d,lin}, \Delta I_{\rm d,sat})$ , thus, limiting the lifetime of the device. The traps also contribute to the leakage current and low frequency noise, thereby further disrupting the device functionality.

The charge stored in the traps depends on their position with respect to the Fermi level and thus on the bulk material, bias and temperature conditions, see Figure 2.1. The states between the intrinsic level  $(E_i)$  and the valence band  $(E_V)$  are filled with electrons and are donor-like as in a p-type substrate. On the other hand, the states between conduction band edge  $(E_{\rm C})$  and  $E_{\rm i}$  are acceptor-like as in a n-type substrate [116]. For instance, in the case of flatband conditions, if the Fermi level  $(E_{\rm F})$  is between  $E_{\rm C}$  and  $E_{\rm i}$ , the traps below  $E_{

m F}$  accept an electron to complete the octet and thus are negatively charged similar to occupied acceptors. Other states carry one unpaired electron and are neutral. On the other hand, if the Fermi level shifts below  $E_i$ , the traps between  $E_i$  and  $E_F$  loose an electron and are positively charged (unoccupied donors) while other states stay neutral being populated by electrons [39].

To sum up, interface traps are charged when they are donor-like and donate electrons (positively charged traps) or if they are acceptors and accept electrons (negatively charged traps). Otherwise the traps are neutral and benign. The traps that are charged create fields which interfere with the electrical properties of the devices. As the trap density increases during the course of device operation, the number of charged traps also increase ultimately leading to the device breakdown.

### 2.1Measurement Techniques

Since success of a technology node depends on the quality of the material and interface, determining the spatial distribution of the defects is vital. Modeling a degradation phe-

Figure 2.3: Generation of charge pumping current on application of a rectangular gate pulse. Arrows represent the carrier flow during inversion (black) and accumulation (red).

nomenon in semiconductor devices to evaluate their performance and lifetime requires the quality of the interface to be precisely characterized. Several signatures of the interfacial Si-H bond can help determine the interface state density. These include the  ${

m SiO_2/Si}$  interface charges through their distortion of the electrostatics, drain-source currents originating due to interface trap states and hopping of the carriers, and the recombination current. Several techniques are used for spatially locating the interface states and tracking their evolution during stress conditions. [117, 118, 119, 120, 121]. Some widely used methods, namely the charge pumping, capacitance-voltage characteristics, and the conductance technique are explained below.

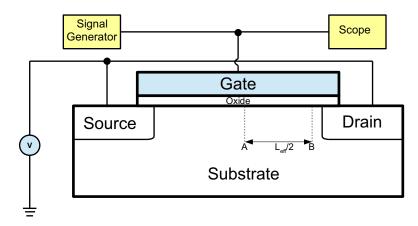

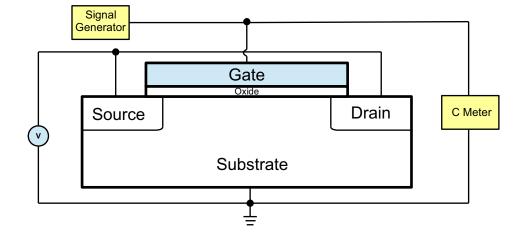

### 2.1.1Charge Pumping

When periodic pulses are applied to the gate of a metal-oxide-semiconductor transistor, the recombination of carriers trapped by the interface states present in the channel region of the device produces the charge pumping current [118, 119]. A simple setup for the charge pumping method is shown in Figure 2.2. The gate is pulsed between accumulation and inversion conditions with the reverse biased substrate-source and substrate-drain p-n junctions. The charge pumping current produced from recombination is measured at the substrate. Alternatively, the current can be measured at the source/drain connection or at source and drain separately.

The recombination takes place in the  $L_{\text{eff}}$  region, see Figure 2.2. Thus, the experimental

Figure 2.4: Evolution of the occupancy of interface states during one gate pulse cycle,  $T_{\rm p}$ . Traps lie in the band-gap between the valence band  $E_{\rm v}$  and conduction band  $E_{\rm c}$ . Only the traps between the energy levels  $E_{\text{em,e}}$  and  $E_{\text{em,h}}$  contribute to the charge pumping current.

charge pumping current is the average recombination current originating from the  $L_{

m eff}$ region in the channel. The generation of charge pumping current is described in Figure 2.3. When the gate voltage approaches inversion, the interface is flooded, up to a certain distance, with minority carriers from the drain and source regions. Considering the drain side in Figure 2.2, the interface is flooded with minority carriers up to some distance A(measured from the drain) during inversion. The majority carriers are swept into the substrate. Consequently, the interface states in this region capture minority carriers and are devoid of majority carriers. When the gate voltage approaches accumulation, the minority carriers travel back to the drain and majority carriers move from the substrate to the interface and reach point B (measured from drain) with B < A. In the region  $L_{\rm eff}/2$ (A-B), recombination takes place, which leads to the charge pumping current. Outside this region, the supply of either electrons or holes is insufficient for recombination to take place.

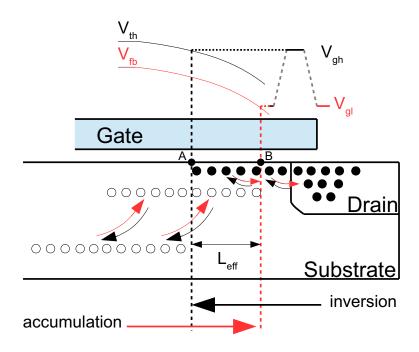

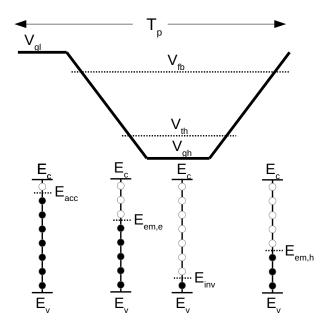

It is worth mentioning that not all the electrons/holes captured by interface states in the  $L_{\rm eff}$  region contribute to the recombination current [118, 119]. This is explained in the following example of constant high level charge pumping in a pMOSFET, Figure 2.4. During accumulation (positive  $V_{\rm gl}$ ), most of the interface states are filled with electrons up to the accumulation energy level  $E_{\rm acc}$ . As the interface moves from accumulation into weak inversion (from flatband voltage  $V_{

m fb}$  to threshold voltage  $V_{

m th}$ ) via depletion, electrons are emitted from the traps back into the substrate due to thermal emission. When the threshold voltage is reached, all the states with energy greater than  $E_{\rm em,e}$  are devoid of electrons. As the interface turns into inversion mode (negative  $V_{

m gh}$ ), holes flood in from

Figure 2.5: The maximum charge pumping current for nMOS devices with different channel lengths for a 65nm CMOS process.

the source and drain leading to emptying of traps via hole capture up to an energy level  $E_{\rm inv}$ . As the gate voltage increases back towards accumulation, holes move back to source and drain and the traps below a certain energy level,  $E_{\rm em,h}$ , are filled with electrons via hole emission. The interface states above this energy level are filled by electrons captured during accumulation. Thus, only the fast traps between  $E_{\rm em,e}$  and  $E_{\rm em,h}$  in the Si bandgap contribute to the charge pumping current. These energy levels can be calculated as [118]:

$$E_{\text{em,e}} = E_{\text{i}} - k_{\text{B}}T \ln \left( v_{\text{th}} \sigma_{\text{e}} n_{\text{i}} t_{\text{em,e}} + \exp \left( \frac{E_{\text{i}} - E_{\text{F,inv}}}{k_{\text{B}}T} \right) \right)$$

$$= E_{\text{i}} - k_{\text{B}}T \ln \left( v_{\text{th}} \sigma_{\text{e}} n_{\text{i}} \left| \frac{V_{\text{th}} - V_{\text{fb}}}{\Delta V_{\text{g}}} \right| t_{\text{r}} \right),$$

$$E_{\text{em,h}} = E_{\text{i}} + k_{\text{B}}T \ln \left( v_{\text{th}} \sigma_{\text{h}} n_{\text{i}} t_{\text{em,h}} + \exp \left( \frac{E_{\text{F,acc}} - E_{\text{i}}}{k_{\text{B}}T} \right) \right)$$

$$= E_{\text{i}} + k_{\text{B}}T \ln \left( v_{\text{th}} \sigma_{\text{e}} n_{\text{i}} \left| \frac{V_{\text{th}} - V_{\text{fb}}}{\Delta V_{\text{g}}} \right| t_{\text{f}} \right),$$

$$(2.1)$$

where,  $E_{\rm i}$  is the intrinsic energy level,  $E_{\rm F,inv}$  and  $E_{\rm F,acc}$  are Fermi energies in inversion and accumulation,  $v_{\rm th}$  is the thermal velocity,  $\sigma_{\rm e/h}$  the capture cross section of the traps, and  $n_i$  the intrinsic carrier concentration. Outside this band, thermal emission is the most prominent source of de-trapping.

Once the charge pumping currents are measured,  $N_{it}$  can be extracted using the steps described below. As an example, sample measurement data for a 65 nm nMOS transistor at temperature of 25 °C is used. For this temperature, the device was stressed for eight different times and the charge pumping current was measured using the constant base level and fixed high level techniques.

As a first step in the  $N_{\rm it}$  extraction procedure, it is important to determine whether the initial interface state distribution is uniform, non-uniform or locally uniform. The charge

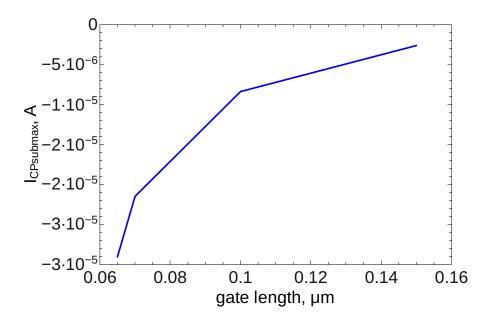

0

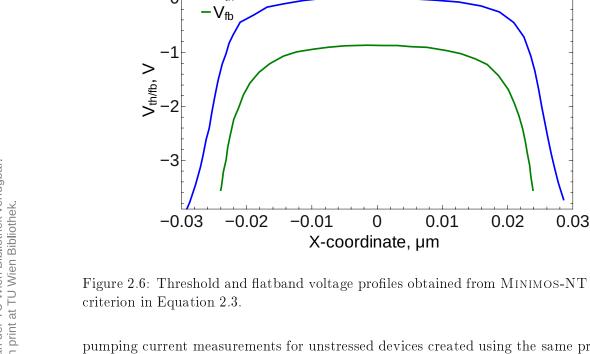

Figure 2.6: Threshold and flatband voltage profiles obtained from MINIMOS-NT using the

pumping current measurements for unstressed devices created using the same process but having different gate lengths can provide information on the nature of the  $N_{it}$  distribution. The maximum charge pumping current versus the gate length curve for 65 nm nMOS devices used in this example and longer gate length transistors created on the same process are shown in Figure 2.5. Figure 2.5 suggests that the interface state profile for a fresh transistor considered here is non-uniform as the increase in the interface state density is not proportional to the increase in the channel length [122]. However, the pre-stressed  $N_{\rm it}(x)$  profiles are significant only when HCD is not very strong, i.e., for low stress times and biases. Due to the high interface state density after severe stresses, the contribution of the pre-stress  $N_{\rm it}(x)$  profile to the total interface state density becomes negligible.

Second, the local threshold and flatband voltages are calculated for the unstressed device, see Figure 2.6. For an nMOS device, the local threshold voltage at a certain coordinate of the interface is defined as the gate voltage at which the traps can capture the minority carriers during inversion. On the other hand, the local flatband voltage at a certain coordinate of the interface is defined as the gate voltage at which the traps can capture the majority carriers during accumulation [123]. Hence, these voltages are derived using the dynamics of the capture and emission process at the interface. For the sample device, our device and circuit simulator MINIMOS-NT [124, 125] was used to obtain the threshold and flatband voltages. MINIMOS-NT employs a comprehensive set of physical models to provide steady-state, transient, and small-signal analysis of the devices. The required electron/hole concentration for the interface states to capture electrons/holes can be estimated by:

$$n_{\rm e/h} = \frac{1}{v_{\rm th}\sigma_{\rm e/h}\tau_{\rm e/h}},\tag{2.3}$$

where  $v_{\rm th}$  is the thermal carrier velocity,  $\tau_{\rm e/h}$  the time constant for electron/hole trapping,

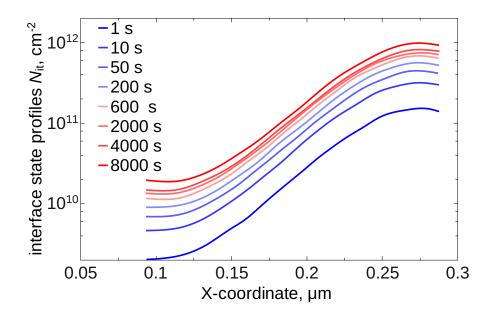

Figure 2.7: Lateral interface state profiles for eight stress times obtained using Equation 2.6 for a 65 nm nMOS stressed at  $V_{\rm ds}=V_{\rm gs}=2.2\,{

m V}$ . The origin (X=0) is at the center of the channel.

and  $\sigma_{\rm e/h}$  the capture cross section for electrons/holes.

Once the threshold voltage profile is obtained, the interface state profiles can be deduced using the expression:

$$I_{\rm CP} = \frac{qW}{T_{\rm P}} \int_{L_{\rm eff}} N_{\rm it}(x) \cdot \mathrm{d}x \tag{2.4}$$

where  $I_{\text{CP}}$  is the time averaged recombination (charge pumping) current, W the width of the interface, and  $T_{\rm P}$  the time period. Through this method, the  $N_{\rm it}(x)$  profiles over a certain distance  $L_{\rm eff}$  can be extracted as already discussed. So for Equation 2.4, the  $I_{

m CP}$  corresponding to the maximum  $L_{

m eff}$   $/V_{

m gh}$  is used to obtain the  $N_{

m it}$  over a maximum distance along the interface. Calculating  $N_{\rm it}(x)$  from equation Equation 2.4 proceeds by differentiating the equation on both sides. Thus,

$$\frac{\mathrm{d}I_{\mathrm{CP}}}{dx} = \frac{qW}{T_{\mathrm{P}}} N_{\mathrm{it}}(x),\tag{2.5}$$

rewritten as

$$\frac{\mathrm{d}I_{\mathrm{CP}}}{\mathrm{d}V_{\mathrm{gh}}}\frac{\mathrm{d}V_{\mathrm{gh}}}{\mathrm{d}x} = \frac{qW}{T_{\mathrm{P}}}N_{\mathrm{it}}(x),\tag{2.6}$$

or

$$\frac{\mathrm{d}I_{\mathrm{CP}}}{\mathrm{d}V_{\mathrm{gh}}}\frac{\mathrm{d}V_{\mathrm{th}}}{\mathrm{d}x} = \frac{qW}{T_{\mathrm{P}}}N_{\mathrm{it}}(x). \tag{2.7}$$

Here  $dV_{\rm th}/dx$  can be considered similar to  $dV_{\rm gh}/dx$  as the condition for the threshold voltage. In Equation 2.3, the threshold voltage is reached at  $V_{\rm gh}$ .

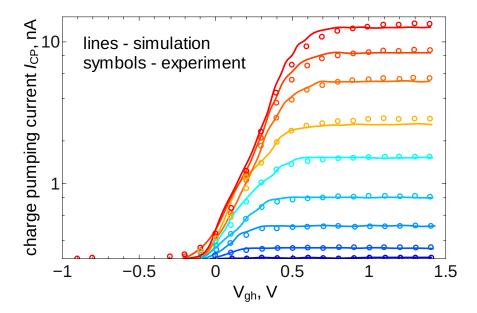

The interface state profiles obtained using this procedure (Equation 2.6) for different stress times are shown in Figure 2.7. The extracted  $N_{\rm it}(x)$  profiles were used to simulate

Figure 2.8: Comparison of simulated and experimental charge pumping currents after different stress conditions.

a degraded device and calculate the charge pumping currents in MINIMOS-NT. The comparison of charge pumping currents obtained from simulation with those from experiments are shown in Figure 2.8 for several stress conditions.

### 2.1.2Capacitance-Voltage Characteristics

The Capacitance-Voltage (CV) method is another widely used technique to evaluate new processes, materials, and devices [126, 120]. The measurement setup is shown in Figure 2.9. In this method, the interface is swept through different regimes, i.e., accumulation, depletion and inversion, successively and the small signal capacitance is measured. In the accumulation regime, there are a large number of majority carriers at the interface. During depletion, the majority carriers move inside the bulk and only fixed charges remain at the surface which build up the depletion layer. This results in a decrease of the total capacitance. When the semiconductor-insulator interface reaches the inversion mode, the minority carriers populate the surface and balance the gate charge. The total capacitance of the device is a combination of the depletion layer and inversion layer capacitance. The total space charge density can be expressed as  $Q_{\rm SC}=Q_{\rm d}+Q_{\rm n}$ , where  $Q_{\rm d}$  and  $Q_{\rm n}$  are the deletion and inversion layer charge density, respectively [120]. An increase in the interface trap density  $N_{\rm it}$  is followed by a deformation of the characteristics as the traps can dynamically be charged and discharged, while the fixed oxide charges shift the flat-band voltage. Therefore, the capacitance (C) is calculated as:

$$C = \frac{\Delta Q_{\rm it} + \Delta Q_{\rm OX}}{\Delta V_{\rm th}}.$$

(2.8)

where  $Q_{it}$  is the interface charge density and  $Q_{OX}$  the oxide charge density.

The frequency of the signal applied is very important to consider the contribution due to different regimes. For example, in a MOSCAP, if the signal has a high frequency, only

Figure 2.9: C-V measurement setup for a MOSFET.

the majority carrier response can be measured as the recombination-generation rates of the minority carriers cannot keep up with small signal variations at high frequencies. In the high frequency limit, the inversion layer charges cannot follow the AC signal. In this regime, the capacitance of the device will be determined by the depletion layer charge density alone [120]:

$$C = \frac{q\epsilon_{\rm Si}N_{\rm A}}{2\phi_{\rm S}}\frac{\mathrm{d}\phi_{\rm S}}{\mathrm{d}t}.$$

(2.9)

This capacitance calculated from Equation 2.9, using the doping concentration  $(N_{\rm A})$ , surface potential  $(\phi_S)$ , and permittivity of silicon  $(\epsilon_{Si})$ , is used to evaluate the density of charges stored in interface traps. The interface charge density enters Equation 2.9 via the rate of change of the surface potential  $d\phi_S/dt$  calculated from  $E_g/q + \chi - \phi_S - v_n + V =$  $-\frac{\delta}{\epsilon_{\rm i}}[Q_{\rm d}+Q_{\rm n}+Q_{\rm it}+qN_{\rm f}]$ , where  $E_{\rm g}$  is the band gap,  $\chi$  the electron affinity,  $v_{\rm n}$  the carrier velocity, V the applied bias,  $Q_{\rm it}$  the interface charge density, and  $N_{

m f}$  the fixed charge density [120].

### 2.1.3Conductance method

The conductance method is one the most sensitive methods to determine the interface trap density. This method depends on the analysis of the change in the charge state of the traps when a small AC voltage is superimposed on the DC gate bias. The modulated signal causes the position of the Fermi level to change with respect to the position of the interface states in energy. Thus, the occupancy of the interface states changes, leading to charge release which can be measured as a parallel conductance G. This conductance is measured as a function of frequency  $\omega$ . The conductance due to interface traps  $G_{\rm it}$  is calculated using the measured capacitance C and conductance G as:

$$\frac{G_{\rm it}}{\omega} = \frac{\omega^2 C_{\rm ox}^2 G}{G^2 + \omega^2 (C_{\rm ox} - C)^2},$$

(2.10)

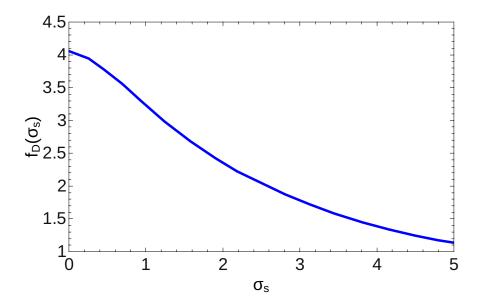

Figure 2.10: The universal function  $f_D(\sigma_s)$  used to calculate  $D_{it}$ , plotted as a function of  $\sigma_{\rm s}$  [128].

where  $C_{\rm ox}$  is the oxide capacitance and  $\omega$  is the angular frequency. The angular frequency  $\omega$  is related to the characteristic trap response time  $\tau = \exp\left[\Delta E/k_{\rm B}T\right]/\sigma v_{\rm th}D_{\rm dos} = 2\pi/\omega$ with  $\sigma$ ,  $v_{\rm th}$ ,  $D_{\rm dos}$  being the trap capture cross section, carrier thermal energy, and density of states, respectively [127]. A plot of the normalized interface trap conductance  $G_{

m it}/\omega$ versus frequency has a maximum value corresponding to a peak frequency  $f_p$ , implying maximum change in interface state occupancy which occurs when the interface traps are in resonance with the applied ac signal.

To calculate the interface trap density, the admittance is first measured at a fixed gate bias in the depletion region from any of the two regions of the curve, i.e., above or below  $f_{\rm p}$ . The value of the universal function  $f_{\rm D}$  is then determined using the standard deviation of band-bending  $(\sigma_s)$  obtained from the curve [128, 129]. The interface state density is then calculated as [121]:

$$D_{\rm it} \approx \left[ f_{\rm D}(\sigma_{\rm s}) q \right]^{-1} \left( \frac{G_{\rm it}}{\omega} \right)_{\rm max}.$$

(2.11)

Although the interface trap density can be directly deduced from measurements, the conductance method is not applicable to interfaces with a high interface state density such as in devices with high-k dielectrics. If the interface state capacitance  $qD_{

m it}$  becomes larger than the oxide capacitance, the measured impedance will be dominated by the oxide capacitance and  $D_{\rm it}$  would be underestimated [130]. Another drawback of the conductance method arises during weak inversion, when the increase in conductance due to minority carrier generation-recombination may lead to overestimation of the interface trap density.

## Chapter 3

# A Review of Existing HCD Models

As already discussed, HCD is a major reliability concern in power MOSFETs, but deeply scaled devices are also susceptible to hot-carrier effects [131]. Modeling this phenomenon is difficult as the physical effects are not completely clear and involve many mechanisms occurring simultaneously. Moreover, modeling of HCD requires solving the carrier transport problem from the full-band Boltzmann transport equation which is computationally challenging and often leads to convergence issues in large area and high voltage devices. The models also have to cope with the ever changing semiconductor industry. For example, in the eighties, the focus was on shrinking the device dimensions, while the operating voltages were not significantly reduced. This development has led to devices with high electric fields in which the carriers were energetic enough to break the Si-H bonds in a single interaction [132, 133]. Thus, the supply voltages were scaled to reduce the electric fields in the devices [134]. Due to the low source-drain voltage in extremely scaled devices, HCD was expected to be drastically suppressed as described in [135, 136, 137]. Such a trend, however, was not observed [138] and even ultra-scaled MOSFETs were found to exhibit HCD [139, 137, 140]. This peculiarity was attributed to energy exchange mechanisms, such as the multiple-carrier process and electron-electron scattering [86, 10].

Particularly for ultra scaled devices, HCD becomes complicated due to the dominance of the multiple-carrier process of Si-H bond breakage [136, 135, 139]. However, the singleand multiple-carrier mechanisms are limiting cases and commonly a superposition of the two is present [141, 25]. The interplay between the two bond breakage mechanisms causes a shift in the worst-case conditions for HCD. Typically, the worst-case HCD was observed at  $V_{\rm gs} \approx 0.5 V_{\rm ds}$  which corresponded to the maximum substrate current [85, 142]. This is no longer valid even for long-channel devices where the worst-case damage is observed at maximum average carrier energy, i.e. conditions corresponding to the maximum gate current [143]. In scaled devices, on the other hand, the dominance of the multiple-carrier process requires the maximum carrier flux instead of the carrier energy for most severe HCD, which is obtained at  $V_{\rm gs} \approx V_{\rm ds}$  [144, 145, 146]. It should be noted that high energy carriers exist also in ultra scaled devices due to processes like electron-electron scattering, so the single-carrier process cannot be ignored [11, 137]. Similarly, in long-channel devices the multiple-carrier process is important especially at higher stress times [147]. Apart from these characteristics, the temperature behavior of HCD is another important aspect to be understood. On the one hand, in long-channel devices hot-carrier damage decreases as the temperature increases. On the other hand, scaled devices show the opposite trend, exhibiting an increase in HCD with temperature. This trend in scaled devices is observed by

increased electron-electron scattering which populates the high energy tail of the carrier distribution function [148, 137, 149, 88]. Thus, a comprehensive model should capture these features of HCD and must be necessarily based on the carrier distribution function. The carrier distribution function is the key aspect as it provides the information on the interaction of carriers with the bonds. In this respect, several attempts have been made to simplify the HCD modeling problem as discussed in the following.

The first attempt for HCD modeling was the lucky electron model [150] which introduced the field-driven approach [151, 152, 77, 153]. According to this model, a defect is produced by an electron having high enough energy to overcome the potential barrier at the interface and enter the SiO<sub>2</sub> conduction band without being emitted back into the oxide. This simple model predicted that carriers with energy greater than 3.7 eV lead to interface state generation. This was deemed incorrect by measurements where the degradation was found to occur even at lower stress voltages [85]. Although the application of the lucky electron model is limited to long channel devices, it is still a popular model due to its simplicity. Takeda et al. proposed an extension to the lucky electron model whereby the degradation, i.e. transconductance and threshold voltage shifts with time are represented by a power law  $t^n$ . Using this empirical approach, the device lifetime could be easily extrapolated from accelerated hot-carrier stress measurements to real operating conditions. However, the model is of limited applicability and inaccurate to represent HCD in devices where a saturation in degradation is observed [154]. Some other extensions of the lucky electron model are: the Goo model which can capture the saturation of degradation [154], the Dreesen concept which was proposed for lightly doped drain transistors [155, 153], the Woltjer approach which incorporates a field-driven correction in the lucky electron model [76, 77]. In the Woltjer model, consideration of the electric field within the oxide allowed the description of degradation due to interface states in devices with varied dimensions and oxide thicknesses.

Mistry et al. introduced three different modes of degradation, i.e., generation of interface and neutral oxide traps at low gate voltages, interface state generation at mid voltage range, and oxide electron trap build-up at high voltages [156, 152]. Although this model was unable to predict the device lifetime correctly and was of limited use, it led to the idea of multiple competing mechanisms for constituting the overall degradation [152]. An important model by Moens et al. considers two competing mechanisms for representing degradation in LDMOS transistors and used different time exponents to characterize these mechanisms [4].

A majority of these models were empirical or at the best phenomenological and usually had time exponents to fit the experimentally obtained degradation characteristics. Another shortcoming of these models was the consideration of the electric field as the driving mechanism, which is valid only for large devices. Thus, models describing the physical picture behind HCD which were based on energy driven approaches were required [85, 86, 10].

### 3.1 The Hess Model

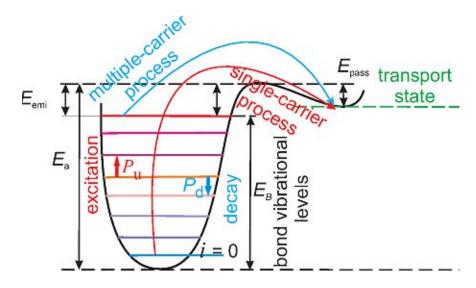

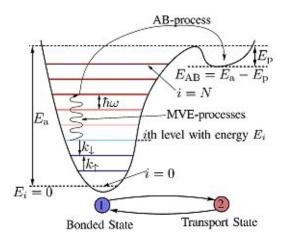

The first physics-based model for HCD was proposed by Hess et al. who suggested the existence of two mechanisms for Si-H bond breakage, i.e. the single- and multiple-carrier processes sketched in Figure 3.1 [21, 135, 157]. The single-carrier mechanism leads to breakage of a Si-H bond when a solitary hot carrier interacts with the bond, transferring its energy and leading to an excitation of one of the bonding electrons to an antibonding

Figure 3.1: The Si-H bond as a truncated harmonic oscillator.  $P_{\rm u}$  and  $P_{\rm d}$  are the bond excitation and de-excitation rates, respectively, while  $E_{\rm a}$  is the activation energy for bond dissociation. The hydrogen atom can be excited from the bonded state to the transport state via single- and multiple-carrier processes.  $E_{\rm emi}$ , and  $E_{\rm pass}$  are the energy barriers for the transition from the highest bonded level to the transport state and for the passivation process, respectively [27].

state. Thus, a repulsive force is induced on the hydrogen atom and leads to hydrogen release. The bond breakage rate with the single-carrier process is given by [157]:

$$R_{\rm SP} = \int_{\varepsilon_{\rm th}}^{\infty} I(\varepsilon) P(\varepsilon) \sigma(\varepsilon) d\varepsilon, \tag{3.1}$$

where  $I(\varepsilon)$  is the carrier flux in the energy range  $[\varepsilon; \varepsilon + d\varepsilon]$ ,  $P(\varepsilon)$  the probability of bond breakage,  $\sigma(\varepsilon)$  the reaction cross section, and  $\varepsilon_{\rm th}$  is the threshold energy the hot carrier should possess in order to initiate the bond breakage process.

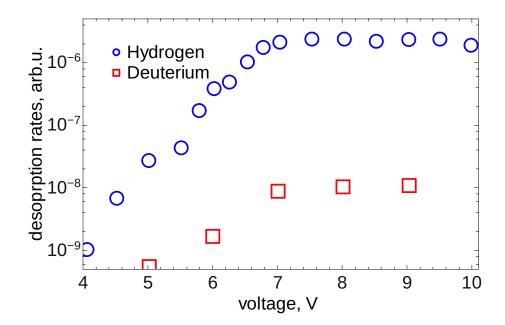

The Hess formalism was successful in explaining the giant-isotope effect, i.e. different desorption rates of the hydrogen and deuterium from Si surfaces, observed experimentally [158, 159, 160]: In experiments with scanning tunneling microscopes (STM), hydrogenand deuterium-passivated Si surfaces were bombarded by cold carriers from the tip of an STM. It was observed that much higher carrier current densities were required to break the Si-D bond as compared to Si-H. The bond breakage rates for the latter were found to be two orders of magnitude larger than the former at high voltages as shown in Figure 3.2. This effect was termed giant isotope effect and was explained by the multiple-carrier process.

Within this concept, the Si-H bond was modeled as a truncated harmonic oscillator comprising of an energy ladder, i.e. a system of eigenstates in the potential well. While interacting with colder carriers the bond can gain or loose energy, leading to its excitation or de-excitation, respectively, within the energetic states of the ladder. Such subsequent interactions with the carriers were linked to the excitation of the phonon modes. The bond is ruptured when the hydrogen leaves the highest energy level and overcomes the potential barrier  $E_{\text{emi}}$ , thereby ending up in the transport mode, see Figure 3.1. The passivation process is defined as hydrogen jumping in the opposite direction over the barrier  $E_{\text{pass}}$ .

The emission and passivation processes, characterized by the energies  $E_{\rm emi}$  and  $E_{\rm pass}$ , respectively, are assumed to obey an Arrhenius law with corresponding rates  $P_{

m emi}$  and  $P_{\rm pass}$ . The excitation and decay rates of the bond  $(P_{\rm u},\,P_{\rm d},\,{

m respectively})$  in the potential well are obtained by considering all combinations of phonon absorption (bond heating) and phonon emission (related to decay resulting from multiple-carrier process) which can be induced by the carrier flux [21, 157]

$$P_{\rm u} = \int_{\varepsilon_{\rm th}}^{\infty} I(\varepsilon) \sigma_{\rm ab}(\varepsilon) \left[ 1 - f_{\rm ph} \left( \varepsilon - \hbar \omega \right) \right] d\varepsilon,$$

$$P_{\rm d} = \int_{\varepsilon_{\rm th}}^{\infty} I(\varepsilon) \sigma_{\rm emi}(\varepsilon) \left[ 1 - f_{\rm ph} \left( \varepsilon + \hbar \omega \right) \right] d\varepsilon,$$

(3.2)

with  $I(\varepsilon)$  being the carrier flux,  $\sigma_{\rm ab/emi}(\varepsilon)$  the reaction cross section for absorption/emission of phonons,  $f_{\rm ph}$  the phonon occupation numbers, and  $\hbar\omega$  the distance between energy levels. The bond breakage rate for the multiple-carrier process can then be estimated as:

$$R_{\rm MC} = \left(\frac{E_{\rm B}}{\hbar\omega} + 1\right) \left[P_{\rm d} + \exp\left(\frac{-\hbar\omega}{k_{\rm B}T_{\rm L}}\right)\right] \left[\frac{P_{\rm u} + \omega_{\rm e}}{P_{\rm d} + \exp\left(-\hbar\omega/k_{\rm B}T_{\rm L}\right)}\right]^{-E_{\rm B}/\hbar\omega},\tag{3.3}$$

where  $E_{\rm B}=E_{\rm a}-E_{\rm emi}$  is the energy of the last bonded state in the potential well,  $\omega_{\rm e}$  the reciprocal phonon lifetime,  $k_{\rm B}$  the Boltzmann constant, and  $T_{\rm L}$  the lattice temperature.

The most important contribution of the Hess model was the consideration of the bond breakage process as a contribution of different carriers in the ensemble. Thus, the carrier distribution function was considered a major ingredient for a proper description of HCD. The DF enters the rate equations, Equations 3.1 and 3.2, via the carrier flux  $I(\varepsilon)$  (see Section 4.4). The isotope effect was explained from the difference in energetics of the Si-H and Si-D bonds which led to different parameters (like phonon lifetime) of the quantum well for the two kind of bonds. The Hess model also considers the statistical distribution of the activation energy,  $E_{\rm a}$ , which was supported by density functional theory calculations [21, 161] and by experiments reporting a double power law of interface state generation as:

$$N_{\rm it} = \frac{p_1}{1 + (t/\tau_1)^{\alpha_1}} + \frac{p_2}{1 + (t/\tau_2)^{\alpha_2}}.$$

(3.4)

Here  $\tau_1$ ,  $\tau_2$  are the characteristic times,  $\alpha_1$ ,  $\alpha_2$  are the different time slopes, while  $p_1$ ,  $p_2$ are the probabilities related to the traps.

However, the microscopic Hess model was not translated to the macroscopic or device level and thus, prediction of the device lifetime and degradation characteristics such as transconductance, linear drain current, etc. was not addressed.

### 3.2 The Penzin Model

Penzin et al. tried to link the microscopic mechanisms suggested by the Hess model with the degradation characteristics of the device [22]. Within this model, the Si/SiO<sub>2</sub> interface is considered as a capacitor. Thus, Si-H bond dissociation leaving behind a depassivated bond and a charged hydrogen atom leads to an increased electric field in the capacitor. Due to this, the potential barrier between bonded and transport states increases. The bond-dissociation process is described by the kinetic equation:

Figure 3.2: The giant-isotope effect: the desorption rates of hydrogen and deuterium atoms from passivated Si surfaces, as measured by an STM [158].

$$\frac{\mathrm{d}n}{\mathrm{d}t} = -kn + \gamma(N_0 - n),\tag{3.5}$$

with n being the concentration of passivated Si-H bonds, k the bond breakage rate,  $\gamma$  the bond passivation rate, and  $N_0$  the total concentration of Si-H bonds in the fresh device. The bond breakage rate k is given by  $k = k_0 \exp(-E_a/k_BT_L) k_{HC}$  where  $k_0$  is the attempt frequency. The hot-carrier acceleration factor  $k_{

m HC}$  is defined as  $k_{

m HC}=1+\delta_{

m HC}\left|I_{

m HC}\right|^{

ho_{

m HC}}$ where  $\rho_{\rm HC}$  and  $\delta_{\rm HC}$  are fitting parameters, and  $I_{\rm HC}$  is the local hot-carrier current [22]. With such a formalism for the defect generation kinetics, the Penzin model could be used for TCAD device simulations.

As per the Penzin model, the activation energy increases with depassivation of the interfacial Si-H bonds and is given as:

$$E_{a=}E_{a}^{0} + \delta |E|^{\rho} + \beta k_{B}T_{L} \ln \frac{N_{0} - n}{N_{0} - n^{0}}$$

$$\beta = 1 + \beta_{\perp}E_{\perp}$$

(3.6)

where  $E_a^0$  is the activation energy when there are no mobile hydrogen atoms, and  $n^0$  the concentration of pre-existing mobile hydrogen atoms. The increase in the capacitor electric field normal to the interface, due to bond dissociation is denoted as  $E_{\perp}$ . The activation energy can also change due to stretching or squeezing the bond by an external electric field. This is represented by the term  $\delta |E|^{\rho}$  in the expression for the activation energy, Equation 3.6.

The  $N_{\rm it}$  concentrations simulated using the Penzin approach are shown in Figure 3.3. The simulated results compare quite well with the experimental ones. Similar to the Hess

Figure 3.3: The cumulative interface state density  $N_{\rm it}$  obtained with the Penzin model vs experimental ones for a hot-carrier stressed n-MOSFET. The gate length is  $0.35\,\mu\mathrm{m}$  while the oxide thickness is 6.5 nm.

approach, the Penzin model considers the activation energy distribution which results in the sublinear slope seen in Figure 3.3. However, within this model, the carrier transport was not properly addressed and the  $N_{\rm it}(x)$  profiles were not determined, except for some cumulative  $N_{\rm it}$  shown in Figure 3.3. Also, the characteristics of the degraded device cannot be simulated with this approach.

### 3.3 The Reaction-Diffusion Model

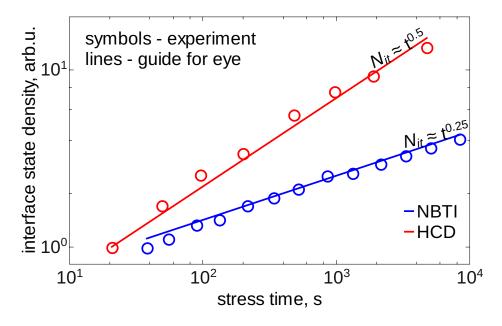

Another attempt to model the physical process behind HCD was the application of the reaction-diffusion model developed for NBTI to HCD by Alam et al. [162, 163]. They assumed both NBTI and HCD to be involved in Si-H bond breakage with different driving forces, and tried to model the two phenomena using the same framework. However, the experimental  $N_{\rm it}$  obtained from NBTI and HCD were found to have different times slopes as shown in Figure 3.4. The different stages in the reaction-diffusion model are summarized in Tab. 3.1. The degradation process starts with the reaction limited phase of Si-H bond breakage. In this phase,  $N_{\rm it}$  increases linearly with time. During the second stage, no more interface states are generated and hydrogen diffusion begins. The third step comprises of a diffusion limited phase with  $N_{\rm it}$  generation time slope of 1/4. In the next stage, hydrogen diffuses away with unlimited velocity and  $N_{\rm it}$  depending on time as  $t^{1/2}$ . In the final phase, all the Si-H bonds are depassivated thus leading to saturation of interface states.

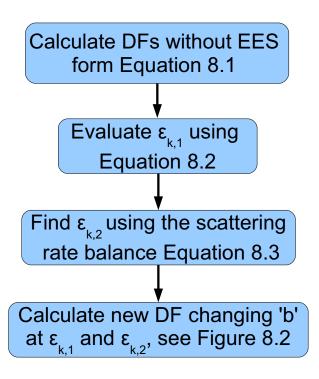

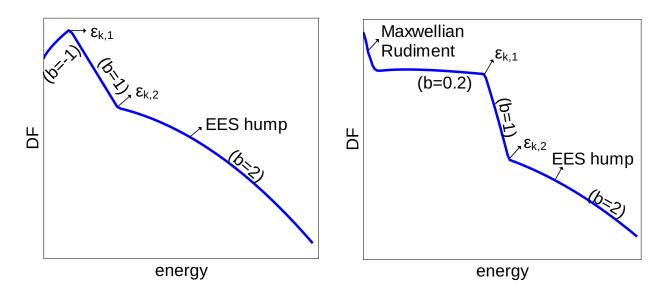

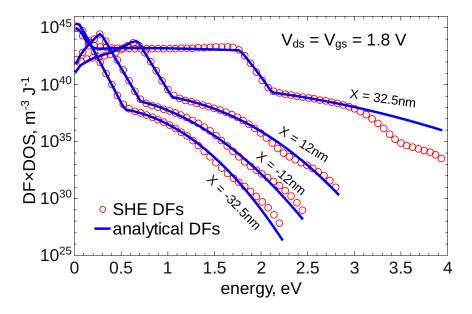

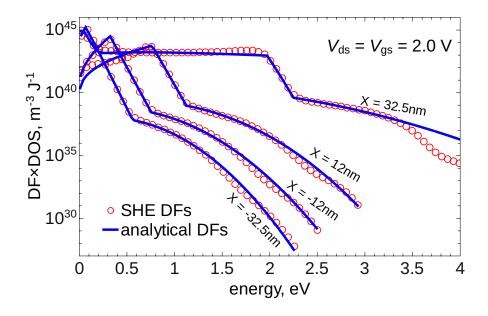

From Tab. 3.1 and Figure 3.4, it was inferred that NBTI is diffusion-limited while HCD is dominated by stage 4. The different slopes discussed above were explained by the RD model by considering the interface state density modeled as  $N_{\rm it} = \int N_{\rm H}(r,t) {\rm d}^3 r$ with  $N_{\rm H}(r,t)$  being the coordinate-dependent density of H-atoms. Using the hydrogen