# **Diplomarbeit**

# Untersuchung kapazitiver Transimpedanzverstärker für optische **Empfänger**

ausgeführt zum Zwecke der Erlangung des akademischen Grades

# **Diplom-Ingenieurs**

im Rahmen des Masterstudiums

# **Embedded Systems**

unter der Leitung von

# Univ.Prof. Mag.rer.nat. Dr.techn. Horst Zimmermann

(E354 - Institute of Electrodynamics, Microwave and Circuit Engineering, Integrated Circuits)

# Senior Scientist Dipl.-Ing. Dr.techn. Bernhard Goll

(E354 - Institute of Electrodynamics, Microwave and Circuit Engineering, Integrated Circuits) eingereicht an der Technischen Universität Wien

Fakultät für Elektrotechnik und Informationstechnik

von

# Christoph Ribisch

01326135

| Wien,  | im  | September | 2021 |      |

|--------|-----|-----------|------|------|

|        |     |           |      | <br> |

| Christ | oph | Ribisch   |      |      |

# **Abstract**

In this work, a highly sensitive optical data receiver implemented as an optoelectronic integrated circuit (OEIC) is designed. The used transimpedance amplifier (TIA) necessary to convert the photocurrent into a voltage has a capacitive feedback to avoid additional noise compared to a feedback resistor. The TIA therefore behaves like an integrator for the photocurrent. For integration the smallest possible capacitances are used for feedback. The circuit does not require a reset mechanism or parallel structures since the average photocurrent is compensated with a transistor at the input node to avoid overdriving of the receiver. This compensation is realized by a control loop which sets the operating point of the circuit after power-up and subsequently compensates the actual average received photocurrent continuously. Due to this control loop, there is also some insensitivity to background light. A subsequent differentiator is added to reconvert the integrating behavior of the TIA to finally get the bit sequence again. At the output, a digital signal is available at a 50  $\Omega$  port. An integrated PIN diode with low capacitance is used as a photodiode. The bandwidth of the receiver is designed for 100 Mbit/s signals with a minimum average photocurrent down into the nA range. The OEIC is designed in a 0.35 µm BiCMOS process with a nominal supply voltage of 3.3 V by X-FAB Silicon Foundries.

# Kurzfassung

Die vorliegende Arbeit befasst sich mit der Entwicklung eines hochempfindlichen optischen Datenempfängers in Form einer optoelektronischen integrierten Schaltung (OEIC). Der dabei eingesetzte Transimpedanzverstärker (TIA), der zur Umwandlung des Photostroms in eine Spannung erforderlich ist, hat eine kapazitive Rückkopplung, um im Vergleich zu einem Rückkopplungswiderstand zusätzliches Rauschen zu vermeiden. Der TIA verhält sich daher wie ein Integrator für den Photostrom. Für die Integration werden die kleinsten möglichen Kapazitäten zur Rückkopplung verwendet. Die Schaltung benötigt auch keinen Reset-Mechanismus oder Parallelstrukturen, da der mittlere Photostrom mit einem Transistor am Eingangsknoten kompensiert wird, um eine Übersteuerung des Empfängers zu vermeiden. Diese Kompensation wird durch eine Regelschleife realisiert, die den Arbeitspunkt der Schaltung nach dem Einschalten vorgibt und anschließend den tatsächlich empfangenen mittleren Photostrom kontinuierlich kompensiert. Aufgrund dieses Regelkreises besteht auch eine gewisse Unempfindlichkeit gegenüber Hintergrundlicht. Ein nachgeschalteter Differenzierer kehrt das integrierende Verhalten des TIA um, um schließlich wieder die Bitfolge zu erhalten. Am Ausgang steht ein digitales Signal an einem 50 Ω-Port zur Verfügung. Als Photodiode wird eine integrierte PIN-Photodiode mit kleiner Kapazität verwendet. Die Bandbreite des Empfängers ist für 100 Mbit/s Signale mit einem minimalen mittleren Photostrom bis hinunter in den nA-Bereich ausgelegt. Der OEIC wird in einem 0,35 µm BiCMOS-Prozess mit einer nominalen Versorgungsspannung von 3,3 V von X-FAB Silicon Foundries entworfen.

# **Danksagung**

Ich möchte meinen Kollegen Simon Laube, Dipl.-Ing. Christoph Gasser, Dipl.-Ing. Michael Hauser, Dipl.-Ing. Alexander Kuttner und Senior Scientist Dipl.-Ing. Dr.techn. Kerstin Schneider-Hornstein vom Institute of Electrodynamics, Microwave and Circuit Engineering an der Technischen Universität Wien für die wertvollen Diskussionen danken.

Ganz besonderer Dank gilt Univ.Prof. Mag.rer.nat. Dr.techn. Horst Zimmermann für seine Unterstützung und die Ermöglichung dieser Diplomarbeit und Senior Scientist Dipl.-Ing. Dr.techn. Bernhard Goll für die hervorragende Betreuung und die vielen Inputs.

Natürlich möchte ich mich auch bei meiner Familie bedanken, meiner Mutter Brigitte und meiner Schwester Petra für ihre großartige Unterstützung.

# TU **Sibliothek**, Die approbierte gedruckte Originalversion dieser Diplomarbeit ist an der TU Wien Bibliothek verfügbar vourknowledgehub vourknowledgehub

# Inhaltsverzeichnis

| 1. | Einle | eitungen                                            | .13 |  |  |  |

|----|-------|-----------------------------------------------------|-----|--|--|--|

|    | 1.1.  | Motivation                                          | .13 |  |  |  |

|    | 1.2.  | PIN-Photodiode                                      | .14 |  |  |  |

|    | 1.3.  | TIA-Typen                                           | .15 |  |  |  |

|    | 1.4.  | Rauschen                                            | .20 |  |  |  |

|    | 1.5.  | Sensitivität von optischen Empfängern               | .24 |  |  |  |

|    | 1.6.  | Grundlagen Inverter                                 | .26 |  |  |  |

|    | 1.7.  | Grundlagen Integratoren                             | .29 |  |  |  |

|    | 1.8.  | Grundlagen Differentiator                           | .30 |  |  |  |

| 2. | Scha  | altungsdesign                                       | .33 |  |  |  |

|    | 2.1.  | Prozesstechnologie                                  | .33 |  |  |  |

|    | 2.2.  | Schaltungskonzept                                   | .33 |  |  |  |

|    | 2.3.  | PIN-Photodiode                                      | .40 |  |  |  |

|    | 2.4.  | Stromregelung                                       | .41 |  |  |  |

|    | 2.5.  | Integrierender TIA                                  | .45 |  |  |  |

|    | 2.6.  | Differentiator                                      | .46 |  |  |  |

|    | 2.7.  | Ausgangsverstärkerstufen                            | .49 |  |  |  |

| 3. | Erge  | ebnisse                                             | .51 |  |  |  |

|    | 3.1.  | Verhalten im Zeitbereich                            | .51 |  |  |  |

|    | 3.2.  | Frequenzübertragungseigenschaften                   | .56 |  |  |  |

|    | 3.3.  | Rauschverhalten und elektrische Sensitivität        | .59 |  |  |  |

|    | 3.4.  | Stabilität und Veränderung über Prozessschwankungen | .66 |  |  |  |

|    | 3.5.  | Zusammenfassung                                     | .69 |  |  |  |

| 4. | Abb   | ildungsliste                                        | .72 |  |  |  |

| 5. | Lite  | iteratur76                                          |     |  |  |  |

## Verzeichnis der Abkürzungen

**VDD** positive Versorgungsspannung von MOS-Schaltkreisen

In den vorgeschlagenen Schaltungen dieser Arbeit 3,3V.

**PMOS** p-Kanal Metall-Oxid-Halbleiter-Feldeffekttransistor

n-Kanal Metall-Oxid-Halbleiter-Feldeffekttransistor **NMOS**

Megabit pro Sekunde Mb/s

OPV Operationsverstärker

Transkonduktanzverstärker (Operational-Transconductance-Amplifier) OTA

**HDMI** High Definition Multimedia Interface

**USB** Universal Serial Bus

**MOSFET** Metall-Oxid-Halbleiter-Feldeffekttransistor

BER Bitfehlerrate (BFR) (Bit Error Rate)

**PRBS** Pseudorandom Binary Sequence

NRZ Non-Return-to-Zero; Wechselschrift

# 1. Einleitungen

### 1.1. Motivation

Optische Datenübertragung spielt eine immer größere Rolle in den verschiedensten Bereichen, da sie viele Vorteile gegenüber elektrischen Verbindungen bietet. Die Anforderungen an Übertragungsstrecken bezüglich deren Datenrate und deren elektromagnetischen Verträglichkeit (EMV) steigen stetig. Optische Verbindungen können sehr hohe Datenraten ermöglichen, beeinflussen selbst andere Leitungen nicht und werden durch naheliegende Leitungen oder elektromagnetische Wellen nicht gestört. Wegen der geringen Dämpfung können außerdem sehr große Distanzen überbrückt werden. Am Ende einer Glasfaserleitung muss das Licht zur weiteren Datenverarbeitung allerdings wieder in ein elektrisches Signal gewandelt werden. Dazu sind optische Empfänger nötig, welche Lichtimpulse empfangen und in elektrische Signale umwandeln können. Für optische Empfänger gibt es bereits viele Ansätze in kostengünstiger CMOS-Halbleitertechnik. Die dazu oft Transimpedanzverstärker (TIAs), welche den Strom der Photodiode in eine Spannung wandeln, nutzen oftmals als Feedback einen ohmschen Widerstand, welcher zusätzliches Rauschen verursacht und damit die Empfindlichkeit des Empfängers stark senkt, sodass sehr kleine Photoströme nicht mehr mit einer ausreichenden kleinen Bitfehlerrate (BER) empfangen werden können. Um das Rauschen des Widerstandes zu eliminieren, muss dieser entfernt und durch ein anderes Feedback ersetzt werden. Einen Ansatz stellt hier der Einsatz einer Kapazität als rauschfreie Alternative zu dem ohmschen Widerstand dar, welche allerdings ein integrierendes Verhalten verursacht. Daher müssen Gegenmaßnahmen getroffen werden, um eine Übersteuerung zu verhindern.[1] Der in [1], [2] und [3] genutzte Reset-Ansatz (integrate and dump), bei dem nach einer bestimmten Zeit der Eingang zurückgesetzt wird, hat den großen Nachteil, dass der Vorgang Zeit kostet, in welcher keine Bits empfangen werden könnten, und dass durch die notwendige Schaltung zusätzliches  $k_BT/C$  Rauschen eingebracht wird.

Diese Arbeit fokussiert sich auf die Entwicklung eines rauscharmen integrierten optischen Empfängers, welcher einen TIA mit einer prinzipiell rauschfreien Kapazität fürs Feedback nutzt und trotz des integrierenden Verhaltens vollständig ohne Reset auskommen soll, indem der mittlere Photostrom am Eingang bei der Photodiode kontinuierlich abgezogen wird. Die Vorteile eines kapazitiven Feedbacks sollen genutzt werden, ohne die Nachteile eines Resets zu erhalten. Die Feedback-Kapazität soll sich ausschließlich aus den parasitären Kapazitäten der Transistoren zusammensetzen. Dabei soll kein zusätzlicher dezidierter Kondensator genutzt werden, um eine möglichst kleine Kapazität und damit eine sehr große Verstärkung zu erhalten. Die Bandbreite soll für eine Datenrate von 100 Mb/s und für mittlere Photoströme ab 2 nA ausgelegt werden. Als Ausgang soll eine digitale Schnittstelle, die eine  $50 \Omega$  Last treiben kann, bereitgestellt werden.

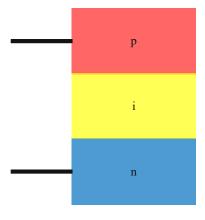

#### 1.2. PIN-Photodiode

In den vorgeschlagenen Schaltungen wird eine PIN-Photodiode genutzt, deren Funktionsweise nachfolgend kurz erläutert wird.

Im Allgemeinen ermöglicht die Photodiode den Übergang von optischen in elektrische Signale. Die eintreffenden Photonen verursachen einen entsprechenden elektrischen Strom, welcher mit herkömmlicher elektronischer (integrierter) Schaltungstechnik weiterverarbeitet werden kann. Die PIN-Photodiode besteht aus drei unterschiedlichen dotierten Halbleiterteilen. Neben der p- und n-Schicht verfügt sie zwischen diesen über eine intrinsische Schicht (undotiert oder leicht dotiert). Zusätzlich ist oft eine Antireflexionsschicht an der Öffnung, an der das Licht eintritt, angebracht, sie reduziert den Anteil der Photonen, die reflektiert werden, und schützt gleichzeitig die darunterliegende Schicht. Der schematische Aufbau ist in Abbildung 1-1 dargestellt, dieser weicht allerdings je nach Prozess vom tatsächlichen physischem Aufbau ab.

Abbildung 1-1 - Schematischer Aufbau einer PIN-Photodiode [1]

Die intrinsische Schicht erhöht die Größe der Raumladungszone und damit die Effizienz der Photodiode.[1] Wird eine Sperrvorspannung (reverse bias) angelegt, entsteht ein elektrisches Feld in der Raumladungszone. Bei der Absorption eines Photons im intrinsischen Bereich wird mit hoher Wahrscheinlichkeit ein Elektron vom dem Valenzin das Leitungsband gehoben und somit ein Elektronen-Loch Paar erzeugt. Dieses Paar wird durch das anliegende elektrische Feld getrennt, wobei sich das Elektron zum positiven Anschluss und das Loch zum negativen Anschluss bewegt. Dadurch entsteht ein Photostrom durch die Diode, welcher mittels elektronischer Beschaltung weiterverarbeitet werden kann. [4] Die Quanteneffizienz  $\eta$  gibt dabei an, wie viele der einfallenden Photonen ein Elektronen-Loch Paar erzeugen und damit zum Photostrom beitragen. Eine Quanteneffizienz von eins  $(\eta = 1)$  entspricht dabei einer idealen Photodiode. Die Quanteneffizienz ist u. a. abhängig von der Wellenlänge des eintreffenden Lichts, der Reflexion an der Oberfläche oder der Wahrscheinlichkeit einer Rekombination.[4]

# 1.3. TIA-Typen

Für die Weiterverarbeitung des empfangenen Photostroms der Photodiode ist oft ein Signal mit definierten Spannungen gefordert. Dazu ist ein Strom-Spannungs-Wandler nötig, welcher auch als Transimpedanzverstärker (transimpedance amplifier; TIA) bezeichnet wird.[5] Dieses Kapitel soll einen kurzen Überblick über wichtige TIA-Typen sowie deren Vor- und Nachteile geben. Für diese Arbeit muss der TIA ein sehr kleines Rauschen aufweisen, um für die geforderten sehr geringen Photoströme ausreichend sensitiv zu sein.

Der TIA wandelt einen Eingangsstrom in eine dazu proportionale Spannung. Die Bezeichnung Transimpedanz kommt von dem englischen Term "transfer impedance" und indiziert, dass die Spannung und der Strom, welche die Impedanz definieren, an zwei verschiedenen Ports gemessen werden. Für niedrige Frequenzen ergibt sich die Transimpedanz  $Z_T$  aus dem Verhältnis der Änderung des Eingangsstroms  $\Delta i_{in}$  und der Veränderung der Ausgangspannung  $\Delta u_{out}$  zu

$$Z_T = \frac{\Delta u_{out}}{\Delta i_{in}} \ . \tag{1}$$

Die Transimpedanz ist ein zentraler Kennwert des TIAs und im allgemeinen frequenzabhängig.[4]

Es gibt mehrere unterschiedliche Typen von TIAs. Die Realisierungsmöglichkeiten reichen allerdings von sehr einfachen Varianten bis hin zu sehr komplexen Schaltungen. Viele Varianten können in die folgenden vier Typen eingeteilt werden.

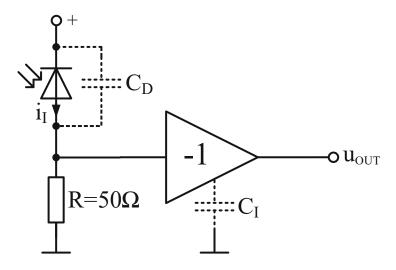

#### Low-Impedance Front-End [4]

Eine einfache Variante eines Low-Impedance Front-End ist in Abbildung 1-2 dargestellt. Ein niederohmiger Widerstand R wird genutzt, um den Photostrom in eine Spannung, entsprechend dem Ohm'schen-Gesetz, zu wandeln. Ein gebräuchlicher Wert für den Widerstand R ist  $50 \Omega$ . Die Spannung wird mit einem Puffer-Verstärker (Eingangsspannung ist gleich Ausgangsspannung) mit einem hohen Eingangswiderstand abgegriffen, um die Belastung des Eingangsknotens möglichst gering zu halten und um die Spannung am Widerstand mit keinem zusätzlichen Strom zu verfälschen. Durch den ohmschen Widerstand und den sehr hohen Eingangswiderstand des Puffers in Kombination mit einer möglichst geringen Eingangskapazität ergibt sich eine große Übertragungsbandbreite. Mehrere Gigahertz sind hier einfach möglich. Transimpedanz wird maßgeblich durch den Widerstand selbst bestimmt und ist daher sehr klein. Ein weiterer Nachteil ist, dass der kleine Widerstand R ein starkes thermisches Rauschen

$$\overline{i_{n,res}^2} = \frac{4k_B T \,\Delta f}{R} \tag{2}$$

am Eingang hinzufügt und damit das äquivalente Eingangsrauschen deutlich erhöht. Der in Abbildung 1-2 aus [4] dargestellte 50  $\Omega$ -Widerstand R würde (bei 20  $^{\circ}C$ ) alleine eine spektrale Rauschstromdichte  $\overline{i_n^2}/\Delta f$  von

$$\sqrt{\frac{41,380649*10^{-23} \frac{J}{K}*293,15 K}{50 \Omega}} = 18,00 \ pA/\sqrt{Hz}$$

(3)

an dem Eingang hinzufügen. Für Anwendungen, bei denen sehr hohe Bandbreiten erforderlich sind und das Rauschen keine zentrale Rolle spielt, eignet sich diese Variante gut.[4] Für diese Arbeit ist sie allerdings vollkommen ungeeignet, da das Rauschen bei den genutzten kleinen Photoströmen von hoher Bedeutung ist. Das Rauschen des  $50~\Omega$ Widerstandes würde für die 67 MHz-Bandbreite breites einen 147 nA-Rauschstrom verursachen und damit den Photostrom um ein Vielfaches übertreffen.

Abbildung 1-2 -Beispiel für einen Low-Impedance Front-End Transimpedanzverstärker; [4]

#### **High-Impedance Front-Ends**

Eine weitere Variante stellt der High-Impedance TIA dar, welcher wie der Low-Impedance TIA aufgebaut ist, allerdings mit einem hochohmigen Widerstand zur Konvertierung des Photostroms in eine proportionale Spannung. Eine einfache Variante des High-Impedance Front-Ends kann daher genauso, wie in Abbildung 1-2, veranschaulicht, aufgebaut werden, allerdings mit einem größeren Widerstand. Der abgebildete 50  $\Omega$ -Widerstand könnte zum Beispiel durch einen 5  $k\Omega$ -Widerstand ersetzt werden. Mit dieser Änderung werden die zwei großen Nachteile des Low-Impedance Front-End, das Wärmerauschen und die geringe Transimpedanz, verbessert. Wird der Widerstand um den Faktor 100 erhöht, vergrößert sich idealerweise auch die Transimpedanz um den Faktor 100. Das Rauschen des Widerstandes nimmt dabei um den Faktor  $\frac{1}{\sqrt{100}}=10$  ab. Diese Verbesserungen gehen auf Kosten der Bandbreite, welche (bei sonst gleichen Bedingungen) um den Faktor 100 reduziert wird. Die spektrale Rauschstromdichte  $\overline{i_n^2}\,/\Delta f$  des 5  $k\Omega$ -Widerstandes ergibt sich bei 20 °C laut

Gleichung (2) zu 1,8  $pA/\sqrt{Hz}$ . Das Rauschen des 5  $k\Omega$ -Widerstandes würde für die 67 MHz-Bandbreite einen 14,7 nA-Rauschstrom verursachen. Troz des reduzierten Rauschens ist dieser Typ für die kleinen Photoströme dieser Arbeit nicht gegeignet, da das thermische Rauschen den Photostrom immer noch um ein Vielfaches übersteigen würde.[4]

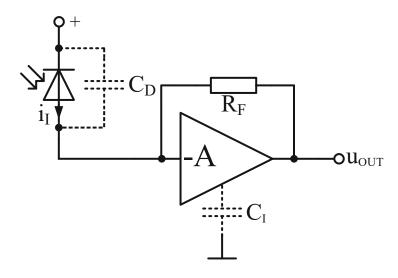

#### Shunt-Feedback TIA

Einen weiteren Transimpedanzverstärker-Typ stellt der Shunt-Feedback TIA dar. Eine Variante eines Shunt-Feedback TIAs ist in Abbildung 1-3 dargestellt. Dazu wird ein invertierender Verstärker genutzt, bei dem vom Ausgang auf den Eingang mit einem ohmschen Widerstand rückgekoppelt wird.

Abbildung 1-3 - Beispiel für einen Shunt-Feedback Transimpedanzverstärker, [4]

Idealisiert betrachtet hat der Verstärker eine unendliche Verstärkung, sodass am Eingang ein virtuelle Masse vorliegt.[6] Der Strom der Photodiode fließt über den Widerstand und ergibt, mit dem Ohm'schen-Gesetz, die Ausgangsspannung. Die Transimpedanz des TIAs  $Z_T$  ist für niedrige Frequenzen ungefähr mit dem Wert des Feedback-Widerstands  $R_F \ (Z_T = R_F)$  bestimmt. Da der Widerstand sehr groß gewählt werden kann, sind große Transimpedanzen möglich. Das Wärmerauschen eines beispielhaft angenommen Feedbackwiderstands von  $50\,k\Omega$  verursacht laut Gleichung (2) bei 20 °C eine spektrale Rauschstromdichte  $\overline{i_n^2}/\Delta f$  von 0,569  $pA/\sqrt{Hz}$ . Das Rauschen des  $50\,k\Omega$ -Widerstandes würde für die  $67\,MHz$ -Bandbreite breites einen 4,66nA-Rauschstrom verursachen. Trotz des hohen Wertes bewirkt der ohmsche Widerstand damit immer noch ein deutliches Wärmerauschen, welches in dieser Arbeit vermieden werden soll, und macht diesen Typ nicht geeignet für diese Arbeit.

#### Integrating TIA

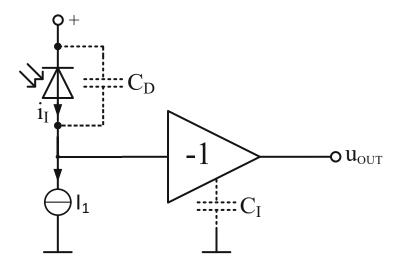

Der Integrating TIA ist der vierte Typ. Wie die Bezeichnung bereits erkennen lässt, integriert dieser den Photostrom und wirkt somit wie ein Integrator. Auch hier gibt es verschiedenste Optionen zur Realisierung.

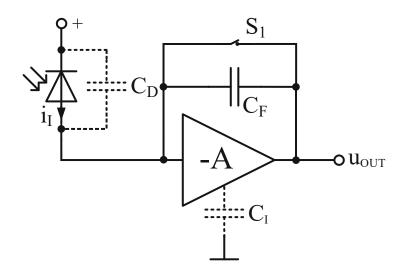

Wie in Abbildung 1-5 dargestellt, besteht eine Variante darin, den ohmschen Widerstand des Shunt-Feedback TIA durch eine rauschfreie Kapazität zu ersetzen und den Eingang nach einer bestimmten Zeit, (z. B. einem Bit oder einer Bit-Periode) zurückzusetzen. Dieser Ansatz wird auch als "integrate and dump" bezeichnet und beispielsweise in [1], [2] und [3] verwendet. Es ergibt sich eine sehr hohe Transimpedanz und das Rauschen wird deutlich reduziert, da der ohmsche Widerstand wegfällt. Ein Nachteil ist allerdings, dass der Reset-Vorgang Zeit benötigt, in der keine Daten empfangen werden können. Außerdem wird je nach Reset-Schaltung wieder mehr oder weniger Rauschen hinzugefügt.

Eine andere Version eines Integrating TIA ist in Abbildung 1-4 dargestellt. Hier wird der ohmsche Widerstand des high-impedance front-end durch eine Stromquelle ersetzt. Er kann als Grenzfall des high-impedance front-end TIAs, in dem der Widerstand gegen unendlich geht, angesehen werden.[4] Das Rauschen wird gegenüber dem des highimpedance front-end deutlich verbessert, da auch hier das thermische Rauschen des Widerstandes wegfällt. Nachteilig ist, dass der TIA schnell überladen werden kann, da mehrere gleiche Binär-Zeichen (Einsen oder Nullen) hintereinander integriert werden könnten, wobei die Ausgangsspannung gleichmäßig steigt oder fällt, ohne dass ein Reset den Eingang zurücksetzt, womit der TIA übersteuert wird. Dieser Nachteil kann jedoch durch das Nutzen von gleichanteilsfreien Signalen mit kurzen Perioden ausgeglichen werden.

Ein integrierender TIA scheint aufgrund des Wegfalls des rauschbehafteten ohmschen Widerstandes und des daraus resultierenden besseren Rauschverhaltens der Schaltung als am besten geeignet. Das Grundprinzip wird daher in den vorgeschlagenen Schaltungen dieser Arbeit genutzt.

Abbildung 1-4 - Beispiel für einen Integrating Front-End Transimpedanzverstärker [4]

Abbildung 1-5 - Beispiel für einen Integrating Front-End Transimpedanzverstärker als integrate and dump Ausführung; [1]

## 1.4. Rauschen

Rauschen ist ein wichtiger Faktor für die Beurteilung von optischen Empfängern. Es entsteht durch verschiedene unvermeidbare Effekte, welche bei fundamentalen Prozessen auftreten und statische Schwankungsvorgänge der Spannungen und Ströme verursachen, dem sogenannten Rauschen.[7] Rauschen verursacht Störungen, welche das eigentliche Nutzsignal überlagern. Wichtig ist hierbei das Signal-Rausch-Verhältnis S/N, das sich aus der Signalleistung S und der Rauschleistung N (noise) ergibt. Wird der Störabstand kleiner, steigt die Bitfehlerwahrscheinlichkeit und damit die Bitfehlerrate BER (bit error Rate) an, die für viele gängige Modulations- und Detektionsarten errechnet werden kann.[8]

Da Rauschen ein stochastisches Phänomen ist, werden der Rauschstrom und die Rauschspannung mit spektralen Dichten beschrieben. Die spektrale quadratische Rauschstromdichte  $|i(f)|^2$  und die spektrale Rauschspannungsdichte  $|u(f)|^2$ repräsentieren die spektrale Verteilung des korrespondierenden Effektivwerts RMS (root mean square).[6] Das jeweilige mittlere Rauschquadrat kann durch Integration über gewünschten Frequenzbereich ermittelt werden. Das einen gemittelte Rauschstromquadrat in dem betrachteten Frequenzbereich von  $f_0$  bis  $f_1$  ergibt sich damit zu

$$\overline{i_n^2} = \int_{f_0}^{f_1} |i_n(f)|^2 df \tag{4}$$

und das gemittelte Rauschspannungsquadrat zu

$$\overline{u_n^2} = \int_{f_0}^{f_1} |u_n(f)|^2 df.$$

(5)

Der Effektivwert (RMS) des Rauschstroms ergibt sich zu

$$i_n^{rms} = \sqrt{\overline{i_n^2}} \tag{6}$$

und der Effektivwert der Rauschspannung ergibt sich zu

$$u_n^{rms} = \sqrt{\overline{u_n^2}} \ . \tag{7}$$

[7] [6]

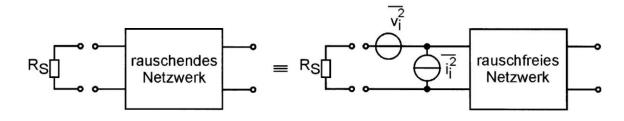

Abbildung 1-6 - Darstellung des Rauschens in einem Zweitornetzwerk durch Generatoren für äquivalente Eingangsrauschspannung und äquivalenten Eingangsrauschstrom; [7]

Zur Bewertung des Rauschens eines Zweitors, welches der TIA darstellt, kann dieses Netzwerk als rauschfrei angenommen werden und stattdessen können zwei äquivalente Rauschgeneratoren am Eingang platziert werden. Wie in Abbildung 1-6 dargestellt, wird dazu parallel zum Eingang des Zweitors eine äquivalente Rauschspannungsquelle und in Serie eine äquivalente Rauschstromquelle angenommen. Diese Vereinfachung ist möglich, solange für die beiden Rauschquellen eine Korrelation berücksichtig wird, da diese auf den gleichen ursprünglichen Rauschquellen basieren und somit nicht unabhängig sind.[7]

#### 1.4.1. Ursachen von Rauschen

Es gibt verschiedene Ursachen für das Entstehen von Rauschen. Je nach elektronischem Bauteil können unterschiedliche Rauschursachen eine dominante Rolle spielen. Die wichtigsten Formen für die in dieser Arbeit verwendeten Bauteile in dieser Arbeit werden im Folgenden erklärt.

#### Wärmerauschen (thermisches Rauschen)

Wärmerauschen entsteht durch die thermischen Bewegungen von Ladungsträgern bei Temperatur über dem absoluten Nullpunkt (0 K = -273.3 °C). Für einen ohmschen Widerstandswert R ergibt sich das gemittelte Rauschstromquadrat zu

$$\overline{i_n^2} = \frac{4k_B T \, \Delta f}{R} \tag{8}$$

und ist damit proportional zur Temperatur T und dem Frequenzbereich  $\Delta f$  sowie reziprok proportional zum Widerstandswert R.  $k_B$  stellt die Boltzmann-Konstante dar. Kleine Widerstände haben somit einen größeren Wärmerauschstrom zur Folge und sollten daher als Feedback bei TIAs vermieden werden. Thermisches Rauschen tritt in jedem passiven, linearen Widerstand auf und ist unabhängig vom Stromfluss. Die spektrale Rauschstromdichte  $\overline{i_n^2} / \Delta f$  des Wärmerauschens ist für Frequenzen kleiner 1 THz annähernd konstant über die Frequenz und kann daher als weißes Rauschen modelliert werden.[7]

#### Funkelrauschen (1/f Rauschen)

Funkelrauschen resultiert aus der zeitlich und statistisch verteilten Entstehung und Auslöschung einzelner Störstellen (Oberflächenladungen) in der Raumladungszone, aber auch durch Strombahnen in inhomogenen Widerstandsmaterialien. Die Umladung von Störstellen in Halbleitern verursacht eine mit höherer Frequenz abnehmende spektrale Rauschstromdichte. In MOSFETs, welche in den vorgeschlagenen Schaltungen verwendet werden, verursachen Si/SiO2-Interface-Zustände im Kanal unter den Gates das 1/f-Rauschen. Es ist hier deutlich ausgeprägter als in Bipolartransistoren und JFETs, tritt allerdings allgemein in allen aktiven Bauteilen und in Kohlewiderständen auf. Das gemittelte Rauschstromquadrat kann mit

$$\overline{i_n^2} = K_1 \frac{I^a}{f^b} \Delta f \tag{9}$$

modelliert werden, mit I als (Gleich-)Strom sowie a und  $K_1$  als bauteil- und prozessspezifische Konstanten. Es ist proportional zum Strom I und reziprok proportional zur Frequenz f, woher auch die Bezeichnung 1/f-Rauschen stammt.[7]

#### Schrot-Rauschen

Die Überwindung der Potentialbarriere am pn-Übergang ist für jeden Ladungsträger ein zufälliger Prozess. Der Strom am pn-Übergang setzt sich aus endlich großen Elementarladungen q zusammen und ist daher nicht konstant. Die Abweichung vom kann durch das Schrot-Rauschen beschrieben Mittelwert werden. Das Rauschstromquadrat ergibt sich für einen Strom  $I_D$  am pn-Übergang zu

$$\overline{i_p^2} = 2qI_D\Delta f \tag{10}$$

Elementarladung q. Die spektrale Rauschstromdichte  $\overline{i_n^2} / \Delta f$ Schrotrauschens ist ebenfalls konstant bezüglich der Frequenz (weißes Rauschen), daher kann das Rauschstromquadrat einfach durch Multiplikation mit der gewünschte Bandbreite berechnet werden.[7]

## 1.4.2. Rauschen des Systems

Das Rauschen des gesamten optoelektronischen Systems setzt sich aus dem optischen und dem elektrischen Teil zusammen. Der optische Teil umfasst den Photodetektor (hier: PIN-Photodiode) und den optischen Pfad, der elektrische Teil entspricht dem Bereiche Empfänger. Diese beiden verursachen, dargestellt Rauschgeneratoren, Rauschen. Der Rauschgenerator des optischen Teiles wird mit  $i_{n.opt}$ repräsentiert und der Rauschgenerator des elektrischen Systems (Empfänger) mit  $i_{n.el.}$ Der Effektivwert (RMS) der Ausgangsrauschspannung  $u_n^{rms}$  im Frequenzbereich von  $f_0$ bis  $f_1$  ergibt sich aus der spektralen Eingangsrauschdichte der beiden Rauschstromgeneratoren  $\left|i_{n,opt}(f)\right|^2$ ,  $\left|i_{n,el}(f)\right|^2$  und dem Betragsgang Übertragungssystems H(f) zu

$$u_n^{rms} = \sqrt{\int_{f_0}^{f_1} |H(f)|^2 * (|i_{n,opt}(f)|^2 + |i_{n,el}(f)|^2) df} .$$

(11)

Für digitale Kodierungen kann dieser Wert für eine logische Null und Eins unterschiedlich sein, daher ergeben sich zwei unterschiedliche Effektivwerte der Ausgangsrauschspannung  $u_{n,0}^{rms}$  bzw.  $u_{n,1}^{rms}$ . [6]

# 1.5. Sensitivität von optischen Empfängern

Die Sensitivität ist eine wichtige Eigenschaft jedes Empfängers. Sie ist definiert als die minimale Signalstärke, welche notwendig ist, um eine vorgegebene Bitfehlerrate BER zu erreichen, und kann im optischen und im elektrischen Bereich definiert werden. Die Bitfehlerrate gibt das Verhältnis der inkorrekt übertragenen Bits zu der gesamten Anzahl an Bits an. Erscheint durch das Rauschen eine logische Null als eine logische Eins am Ausgang oder umgekehrt, dann gilt das Bit als inkorrekt übertragen. Die Bitfehlerrate BER für NRZ-Signale kann zu

$$BER = \frac{1}{2} \operatorname{erfc}\left(\frac{Q}{\sqrt{2}}\right) \tag{12}$$

berechnet werden.[4] Die komplementäre Fehlerfunktion erfc ist durch das Integral

$$\operatorname{erfc}(x) = \frac{2}{\sqrt{\pi}} \int_{x}^{\infty} e^{-\tau^{2}} d\tau$$

(13)

definiert, kann aber für viele Werte von x direkt aus Tabellen übernommen werden.

Das Personick Q (Q-Faktor) ist ein Maß für das Signal-Rausch-Verhältnis, allerdings nicht direkt das allgemeingebräuchliche Signal-Rausch-Verhältnis SNR.[4] Es kann aus dem Verhältnis des Spitze-Spitze-Wertes der Ausgangspannung  $v_{out}^{pp}$  und dem Effektivwert der Ausgangsrauschspannung  $\boldsymbol{u}_n^{rms}$  mit

$$Q = \frac{v_{out}^{pp}}{2 * u_n^{rms}} \tag{14}$$

berechnet werden. Ist die Ausgangsrauschspannung, wie zuvor beschrieben, für die Binärsymbole unterschiedlich, ergibt sich Q näherungsweise zu

$$Q = \frac{v_{out}^{pp}}{u_{n.0}^{rms} + u_{n.1}^{rms}} \ . \tag{15}$$

[6] [4]

Die Sensitivität für den elektrischen Teil  $i^{pp}_{sens}$ , ist definiert als der kleinste Spitze-Spitze-Photostrom  $i_{s}^{pp}$ , welcher am Receivereingang notwendig ist, um eine vorgegebene Bitfehlerrate, beziehungsweise ein vorgegebenes Q, zu erreichen.[4] Wird die Gleichung umgeformt und das Ergebnis durch Übertragungsfunktion im Durchlassbereich des elektrischen Teils  $H_0$  dividiert, ergibt sich die elektrische Sensitivität zu

$$i_{sens}^{pp} = \frac{Q * 2 * u_n^{rms}}{H_0} = Q * 2 * i_n^{rms}$$

(16)

beziehungsweise bei unterschiedlichen Werten, je nach Binärsymbol, zu

$$i_{sens}^{pp} = \frac{Q\left(u_{n,0}^{rms} + u_{n,1}^{rms}\right)}{H_0} = Q\left(i_{n,0}^{rms} + i_{n,1}^{rms}\right). \tag{17}$$

Mit dem äquivalenten Eingangsrauschstrom, repräsentiert durch  $i_{n,0}^{rms}$  und  $i_{n,1}^{rms}$ , kann die Sensitivität für ein vorgegebenes Q berechnet werden.[4]

Die optische Sensitivität  $\overline{P}_{sens}$  ist definiert als die minimale optische Leistung, gemittelt über die Zeit, welche notwendig ist, um eine vorgegebene Bitfehlerrate BER, beziehungsweise ein vorgegebenes Q, zu erreichen. Für ein ideales NR- codiertes Signal ist die optische Sensitivität

$$\overline{P}_{sens} = \frac{Q * i_n^{rms}}{\mathcal{R}} \tag{18}$$

beziehungsweise

$$\overline{P}_{sens} = \frac{Q * \left(i_{n,0}^{rms} + i_{n,1}^{rms}\right)}{\mathcal{R}}$$

(19)

unterschiedliche Werte je Binärsymbol aufweist. Empfindlichkeit  $\mathcal{R}$  (responsivity) gibt an, wie groß der Photostrom  $I_{photo}$  für ein einfallendes Licht mit einer Leistung  $P_{opt}$  bei einer speziellen Wellenlänge ist. Sie ergibt sich zu

$$\mathcal{R} = \frac{I_{photo}}{P_{opt}} \tag{20}$$

und ist im allgemeinen frequenzabhängig.[5]

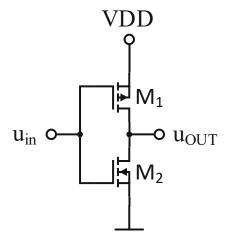

# 1.6. Grundlagen Inverter

In diesem Abschnitt wird ein CMOS-Inverter kurz beschrieben. Dieser besteht aus einem PMOS- und einem NMOS-Transistor, welche, wie in Abbildung 1-7 dargestellt, zusammengeschaltet sind. CMOS-Inverter stellen nicht nur für digitale Schaltungen eine sehr leistungsfähige Einsatzmöglichkeit dar, sondern sind auch für analoge Schaltungen bestens geeignet. [9] Während in digitalen Schaltungen der Übergang zwischen den zwei Spannungspegeln einen unerwünschten Zustand darstellt, arbeiten analoge Schaltungen genau in diesem Bereich.

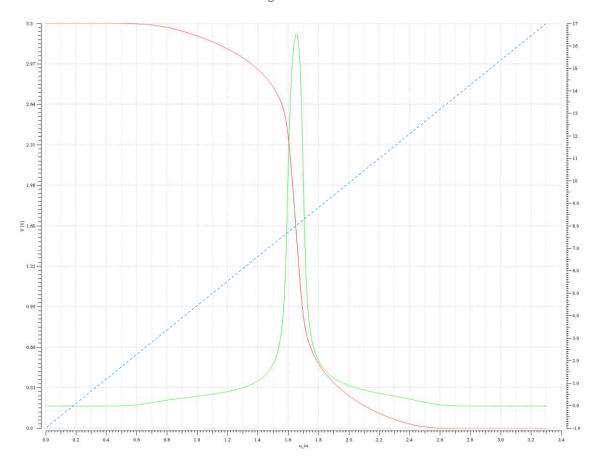

In Abbildung 1-8 ist die Übertragungskennlinie eines CMOS-Inverts rot dargestellt (Großsignalverhalten). Ohne Feedback ist die Übertragungskennlinie sehr steil und es ergibt sich in einem beschränkten Spannungsbereich eine sehr große Verstärkung, während sowohl PMOS- als auch NMOS-Transistor in Sättigung sind.[10] Je steiler die Kurve ist, desto größer ist die Verstärkung, gleichzeitig arbeitet der Inverter nur in einem kleineren Spannungsbereich als Verstärker. Die blaue Kurve in Abbildung 1-9 stellt die Ableitung der Übertragungskennlinie dar und entspricht damit der Gleichspannungsverstärkung (DC-Gain). Über einen großen Frequenzbereich ist die Verstärkung annähernd konstant.

Abbildung 1-7 - CMOS-Inverter

Abbildung 1-8 – rot: Übertragungskennlinie (Uout/Uin) eines CMOS-Inverters; grün: Ableitung der Übertragungskennlinie/ Gleichspannungsverstärkung; blau: U<sub>out</sub>=U<sub>in</sub> (V<sub>DD</sub>=3,3V)

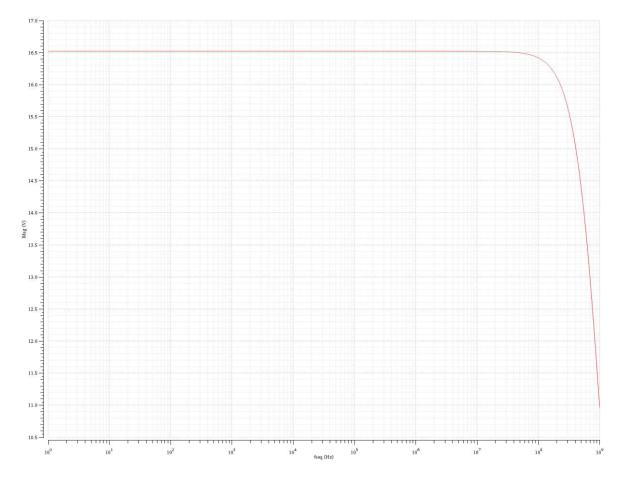

Der Betragsgang ist für den Arbeitspunkt von 1,65 V in Abbildung 1-9 dargestellt und entspricht für niedrige Frequenzen ungefähr der in Abbildung 1-8 gezeigten Gleichspannungsverstärkung bei eben diesen 1,65 V. Analytisch kann Spannungsverstärkung aus dem Kleinsignalersatzschaltbild der beiden Transistoren zu

$$A_{v} = \frac{v_{in}}{v_{out}} = -(r_{ds,p}//r_{ds,n}) * (g_{m,n} + g_{m,p})$$

(21)

hergeleitet werden, welcher abhängig vom Arbeitspunkt der Transistoren ist.[11]

CMOS-Inverter bieten einige Vorteile. Da sie nicht kaskodiert sind, reduziert sich der mögliche Spannungshub nicht, außerdem nutzen sie gleichzeitig die Transkonduktanz g<sub>m</sub> des PMOS und des NMOS und haben daher eine höhere Bandbreite verglichen mit einer Sourceschaltung mit aktiver Last (PMOS als Bias-Stromquelle).[9]

Abbildung 1-9 - Frequenzgansgang (Betrag) eines CMOS-Inverters im Arbeitspunkt von 1,65V (V<sub>DD</sub>=3,3V)

# 1.7. Grundlagen Integratoren

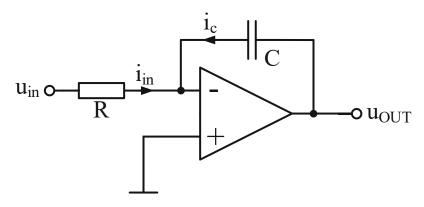

Dieses Kapitel gibt eine kurze Einführung in die Funktion eines Integrators. Dieser integriert das anliegende Signal an seinem Eingangstor und gibt es am Ausgang aus. Eine Prinzipschaltung eines Integrators ist in Abbildung 1-10 dargestellt. Der nichtinvertierende Eingang (+) des Operationsverstärkers (OPV) wird auf Masse gelegt. Wird der OPV als ideal angenommen, stellt sich am invertierenden Eingang (-) eine virtuelle Masse ein. Der Eingangsstrom  $i_{in}(t)$  ergibt sich damit aus dem Widerstand R und der Eingangsspannung  $u_{in}(t)$  zu

$$i_{in}(t) = \frac{u_{in}(t)}{R} \tag{22}$$

mit dem Ohm'schen Gesetz. Aufgrund der virtuellen Masse stellt sich der Strom durch die Kapazität C aus der Ausgangsspannung  $u_{out}(t)$  zu

$$i_c(t) = C * \frac{du_{out}(t)}{dt}$$

(23)

ein. Da in den invertierenden Eingang des OPV (-) idealerweise kein Strom fließt, sind die beiden Ströme  $i_{in}(t)$  und  $i_c(t)$  entgegengesetzt gleich groß. Aus Gleichung (22) und (23) erhält man durch Integration den Zusammenhang der Eingangs- und Ausgangsspannung

$$u_{out}(t) = u_{ou}(t=0) - \frac{1}{R*C} \int_0^T u_{out} dt$$

(24)

Für einen Anfangswert der Ausgangsspannung  $u_{out}(t=0)=0$  vereinfacht sich die Gleichung zu

$$u_{out}(t) = -\frac{1}{R*C} \int_0^T u_{out} \ dt \ . \tag{25}$$

Wird direkt der Strom  $i_{in}(t)$  als Eingangsgröße betrachtet, ergibt sich folgende Beziehung zwischen Eingangsstrom und Ausgangsspannung:

$$u_{out}(t) = -\frac{1}{C_{int}} \int_0^T i_{in} dt . {(26)}$$

Die Ausgangsspannung  $u_{out}$  ist damit proportional zum integrierten Eingangsstrom  $i_{in}$ . Fließt ein zeitlich konstanter Strom in den Integrator, fällt die Spannung am Ausgang linear ab, fließt ein konstanter Strom aus dem Eingang des Integrators, steigt die Spannung linear an. Im logarithmischen Betragsgang ergibt sich ein konstant abfallender Betrag. Dieses Verhalten weist der im Rahmen dieser Arbeit eingesetzte TIA auf.

Abbildung 1-10 - Prinzipschaltung eines Integrators mit Spannung als Eingangs- und Ausgangsgröße

Ein einfacher CMOS-Inverter, wie in Kapitel 1.6 beschrieben, erhält durch eine kapazitive Rückkopplung ebenfalls das beschriebene Verhalten. Der große Vorteil dieser Variante ist, dass lediglich zwei Transistoren (auch mit minimaler Weite) genutzt werden müssen und sich damit das Rauschen auf ein Minimum reduzieren lässt.

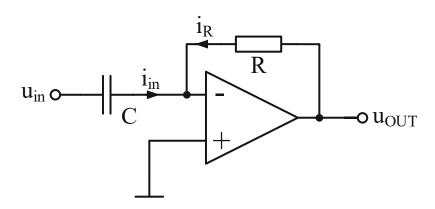

# 1.8. Grundlagen Differentiator

Dieses Kapitel gibt eine kurze Einführung in die Funktion eines Differentiators. Dieser gibt das Eingangssignal am Ausgang differenziert aus. Eine Prinzipschaltung eines Wird Differentiators ist in Abbildung 1-11 dargestellt. der abgebildete Operationsverstärker (OPV), wie in Kapitel 1.7 beschrieben, wieder als ideal angenommen, stellt sich mit der Eingangsspannung  $u_{in}(t)$  der Eingangsstrom  $i_{in}(t)$

$$i_{in}(t) = C * \frac{du_{in}(t)}{dt}$$

(27)

ein. Durch die virtuelle Masse stellt sich der Strom durch den Widerstand R mit der Ausgangsspannung  $u_{out}(t)$  zu

$$i_R(t) = \frac{u_{out}(t)}{R} \tag{28}$$

ein. Da in den invertierenden Eingang des OPVs (-) wieder kein Strom fließt, sind die beiden Ströme  $i_{in}(t)$  und  $i_c(t)$  entgegengesetzt gleich groß. Aus Gleichung (27) und (28) erhält man damit durch Integration den Zusammenhang zwischen der Eingangsspannung  $u_{in}(t)$  und Ausgangspannung  $u_{out}(t)$

$$u_{out}(t) = -R * C * \frac{du_{in}(t)}{dt}.$$

(29)

Die ist damit proportional der differenzierten Ausgangsspannung  $u_{out}$ Eingangsspannung  $u_{in}$ . Liegt am Eingang eine zeitlich konstant abfallende Spannung an, ergibt sich am Ausgang eine konstante Spannung, die dem Anstieg beziehungsweise Abfall der Eingangsspannung entspricht.

Abbildung 1-11 - Prinzipschaltung eines Differentiator mit Spannung als Eingangs- und Ausgangsgröße

Im Betragsgang weist der Differentiator für steigende Frequenzen einen konstanten Anstieg auf. Für die praktische Anwendung sollte daher noch ein Tiefpassverhalten ergänzt werden, damit die Schaltung nicht instabil und das Rauschen für höhere Frequenzen reduziert wird. Ein ohmscher Serienwiderstand am Eingang und ein Kondensator parallel zum Widerstand R fügen das gewünschte Tiefpassverhalten hinzu. Eine Prinzipschaltung ist in Abbildung 1-12 dargestellt. Mit der richtigen Wahl der Bauteilwerte verhält sich die Schaltung für niedrigere Frequenzen, welche differenziert

werden sollen, wie ein Differentiator und darüber hinaus wie eine zunehmende Abschwächung.

Abbildung 1-12 - Verbesserte Prinzipschaltung eines Differentiators mit Spannung als Eingangs- und Ausgangsgröße mit aktivem Tiefpass

# 2. Schaltungsdesign

#### Prozesstechnologie 2.1.

Für die integrierte Schaltung Rahmen dieser Arbeit wird die im Halbleiterprozesstechnologie XO035 des Halbleiterherstellers X-FAB Silicon Foundries genutzt. Der 0,35µm BiCMOS-Spezialprozess ist speziell für optoelektronische Anwendungen geeignet. Er lässt sich ebenfalls bestens für Anwendungen einsetzen, die empfindliche Photodioden mit hoher Bandbreite und hohem Dynamikbereich benötigen.[12] Daher kann die erforderliche PIN-Photodiode als Empfangsdiode auch direkt mit einem optischen Fenster auf dem Chip integriert werden. Die mögliche hochempfindliche PIN-Photodiode unterstützt Wellenlängen von 400 nm bis 900 nm. Der Prozess ermöglicht ebenfalls hochohmige Poly-Widerstände, die in der Schaltung benötigt werden. Es stehen Bauteile für 5 V und 3,3 V zur Verfügung.[13] In dieser Arbeit wird 3,3 V als Betriebsspannung genutzt.

# 2.2. Schaltungskonzept

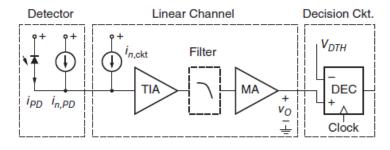

Ein optischer Empfänger kann im Allgemeinen laut [4] grob in drei funktionale Teile gesplittet werden. Wie in Abbildung 2-1 dargestellt, beinhaltet dieses Modell den Photodetektor, den linearen Kanal (linear Chanel) und den Entscheider (Decision Circuit) mit der Entscheiderschwelle V<sub>DTH</sub> (threshold voltage).

Abbildung 2-1 - Grundlegendes Empfängermodel laut [4]

An erster Stelle im linearen Kanal befindet sich der Vorverstärker, welcher meist als Transimpedanzverstärker (TIA, transimpedance amplifier) ausgeführt ist und aus dem Photostrom eine Spannung erzeugt. Nachgeschaltet werden Verstärkerstufen genutzt, um die Signalamplitude immer weiter zu vergrößern. Außerdem kann im linearen Kanal ein Tiefpassfilter (low-pass filter) eingesetzt werden, um Rauschen und Störungen bei Frequenzen über der Nutzbandbreite zu reduzieren. Zu beachten ist, dass das Frequenzübertragungsverhalten der Verstärkerstufen im Allgemeinen bereits selbst ein Tiefpassverhalten aufweist.

In den in dieser Arbeit vorgeschlagenen Schaltungen wird als optischer Detektor eine PIN-Photodiode mit einer Kapazität von 3,5 fF verwendet. Der Entscheider selbst befindet sich off-Chip und ist nicht Teil dieser Arbeit, wobei die Ausgangsstufe als limitierender Verstärker bereits wie ein Entscheider wirkt.

In den behandelten Schaltung weist der TIA ein integrierendes Verhalten auf und wirkt damit als Integrator für den Photostrom beziehungsweise das empfangene Signal. Die Tatsache, dass die eintreffenden Photonen immer einen Strom in die gleiche Richtung in der Photodiode verursachen, hat zur Folge, dass die Ausgangsspannung des Integrators immer stärker ansteigt und nach relativ kurzer Zeit den Integrator in den stark nichtlinearen Bereich bringt. Kurz darauf erreicht die Ausgangsspannung mit dem Wert der Versorgungsspannung ihr Maximum und das empfangene Nutzsignal ist unbrauchbar. Um dies zu verhindern, muss der Eingangsknoten im möglichst linearen Bereich, also nahe dem vorgesehen Arbeitspunkt, gehalten werden. Dieser optimale Arbeitspunkt entspricht beim ideal dimensionierten CMOS-Inverter der halben Versorgungsspannung  $V_{DD}/2$  mit 1,65 V. Um dies zu erreichen gibt, es mehrere Möglichkeiten.

Eine einfache Variante ist die Nutzung eines hochohmigen Widerstands, welcher den Eingangsknoten mit einer dem Arbeitspunkt entsprechenden Referenzspannung verbindet. Je stärker die Spannung am Eingangsknoten durch die Integration vom Arbeitspunkt abweicht, desto größer wird der Ausgleichsstrom über den Widerstand. Dies führt zu einem deutlichen Absinken des effektiven Anteils des Photostroms in den Integrator, da ein steigender Teil über den Widerstand ausgeglichen wird. Der sich in dieser Konfiguration ergebende Ausgleichsstrom über den Widerstand und die damit verbundene Verfälschung des Signals ist deutlich geringer, verglichen mit klassischen Pull-up- und Pull-down-Widerständen, welche auf VDD beziehungsweise Ground liegen (vlg. Low- and High-Impedance Front-Ends in [4]). Simulationen im Zuge dieser Arbeit haben allerdings gezeigt, dass diese Lösung in den vorgeschlagenen Schaltungen entweder eine zu starke Verfälschung, bei einem vergleichsweise kleinen Widerstand, oder einen zu geringen Effekt, bei einem größeren Widerstand, hat und damit nicht geeignet ist. Durch das thermische Rauschen des Widerstandes steigt außerdem das Rauschen am Eingangsknoten an.

Eine weitere Möglichkeit, um die Spannung im Arbeitsbereich zu halten, ist ein Reset des Eingangsknotens, welcher nach einer bestimmten Zeit erfolgt und damit den Integratoreingang wieder auf den Arbeitspunkt zurücksetzt (vgl. integrate and dump [1] [4]). Meist wird dazu ein Reset-Transistor als Schalter genutzt, welcher den Eingang zum Reset-Zeitpunkt (z. B. nach einer Bit-Periode oder nach einem Bit) auf die gewünschte Spannung legt. Nachteil ist hier, dass sich die mögliche Bitrate reduziert, da während des "Rest-Vorgangs" kein Bit empfangen werden kann. Die vorgeschlagene Aufteilung in [14] in drei parallele Strukturen, um die Phasen integrate, readout und dump parallel abzuarbeiten, kann diesen Nachteil ausgleichen, erhöht allerdings das Rauschen durch die benötigen Schalter zu stark, um die geforderte Sensitivität zu erreichen.

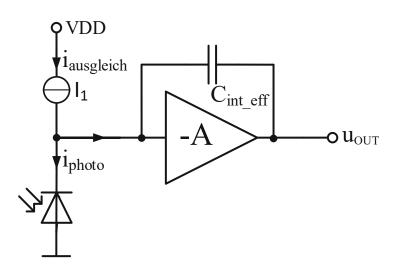

Abbildung 2-2 - Prinzip des Ausgleichens des mittleren Photostroms

Eine weitere Methode stellt das Ausgleichen des mittleren Photostroms dar (vgl. Integrating Front-End in [4] und Abschnitt 1.3). Durch den Ausgleichsstrom ändert sich die Stromrichtung am Eingang des Integrators, je nachdem, ob gerade ein Eins- oder ein Null-Bit empfangen wird. Der Photostrom kann damit außerdem variieren, wenn die Stromquelle dem mittleren Photostrom nachgeführt wird. Ist sichergestellt, dass kurze Folgen genutzt werden und das Signal einen konstanten Gleichanteil aufweist (DC balanced signal), löst sich das Problem der Überladung (overload) und die Ausgangsspannung  $u_{int\_out}$  wird beschränkt. In der Literatur finden unterschiedlichste Codierverfahren, welche diese Anforderungen sicherstellen. Die Nutzung solcher Codierverfahren ist keine Seltenheit, sondern weit verbreitet. Beispiele sind die 9B/10B-Codierung von Albert X.Widmer [15] oder der 8b/10b-Code [16], welche zum Beispiel bei Gigabit Ethernet [4], USB 3.0 [17] oder HDMI [18] verwendet werden. Es könnte daher auf diverse vorgefertigte Chips zur Signalerzeugung zurückgegriffen werden.

Das Prinzip des Ausgleichens des mittleren Photostroms wird in den vorgeschlagenen Schaltungen eingesetzt. Dieses Schaltungsprinzip sowie der Integrator sind in Abbildung 2-2 dargestellt. Der resultierende Strom  $i_{int}$  in den Integrator ergibt sich damit zu

$$i_{int}(t) = i_{ausgleich}(t) - i_{photo}(t)$$

(30)

Wird der Ausgleichsstrom  $i_{ausgleich}$  nun so gewählt, dass er dem mittleren Photostrom entspricht,

$$i_{ausgleich} = \overline{i_{photo}}$$

(31)

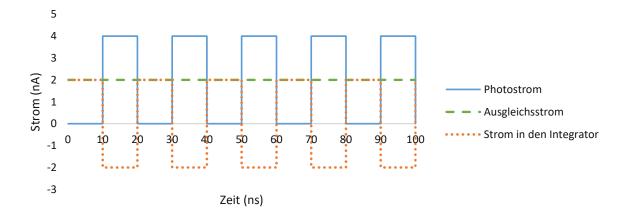

ist der Betrag des Stroms in den Integrator  $|i_{int}|$  für Eins- und Null-Bits gleich. Ein empfangenes Null-Bit unterscheidet sich von einem Eins-Bit am Integrator damit nur durch das Vorzeichen beziehungsweise durch die Stromrichtung. Das Prinzip ist schematisch für einen rechteckförmigen Photostrom in Abbildung 2-3 dargestellt.

Abbildung 2-3 - zeitlicher Verlauf des Prinzips des Ausgleichens des mittleren gleichanteilfreien Photostroms; rechteckförmigen Photostrom mit einer Pulsweite und Periodendauer von 10ns bei 4 nA Pulshöhe

Die in Abbildung 2-2 dargestellte Integrationskapazität  $C_{int\_eff}$  beinhaltet die parasitären Kapazitäten der Transistoren und die Kapazität der Photodiode selbst, welche einen nicht unwesentlichen Beitrag zur Integration leistet. Sie stellt damit die effektiv wirkende Integrationskapazität dar. Bei einer DC-freien Codierung, wie oben beschrieben, und einer beschränkten Folgen von Null- beziehungsweise Eins-Bits, ergibt sich eine beschränkte Ausgangsspannung am Integratorausgang  $u_{int\ out}$ .

Zum Hervorrufen des benötigten Ausgleichsstromes  $i_{ausgleich}$  und um dadurch den Eingang nahe des Arbeitspunktes zu halten, werden zwei verschiedene Möglichkeiten berücksichtigt, eine PMOS-Konstantstromquelle und ein NMOS-Sourcefolger. Beide Varianten ermöglichen die Kompensation des mittleren Photostroms. Mit der PMOS-Konstantstromquelle kann dieser Ausgleichsstrom prinzipiell über die Gate-Source-Spannung (negativ) vorgegeben werden, auch wenn das fehlende Konstantstromverhalten bei dem genutzten PMOS-Transistor bei sehr kleinen Strömen stärker von der Drain-Source-Spannung abhängt (vgl. Abschnitt 2.2.1). Bei der Variante mit dem NMOS-Sourcefolger wird über die Gate-Source-Spannung die Spannung am Eingangsknoten verändert, allerdings muss dies exakt den gesuchten Ausgleichstrom hervorrufen, um das Regelziel zu erreichen. Die Folge ist in beiden Fällen ein Ausgleichsstrom über den jeweiligen Transistor in den Eingangsknoten. In dieser Arbeit werden beide Möglichkeiten untersucht und verglichen. Um den Ausgleichsstrom  $i_{ausaleich}$  automatisch dem mittleren Photostrom nachzuführen, ist eine Regelung erforderlich.

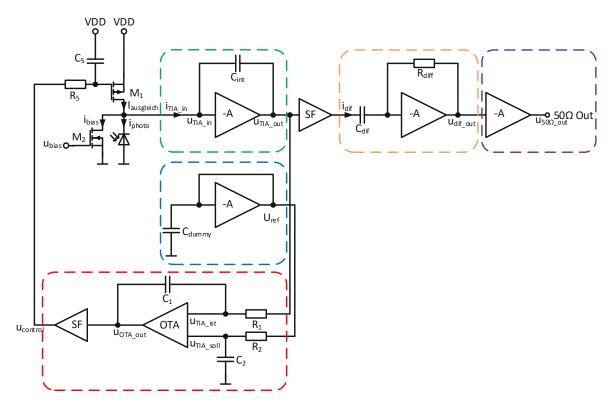

### 2.2.1. Schaltungskonzept mit PMOS-Konstantstromquelle

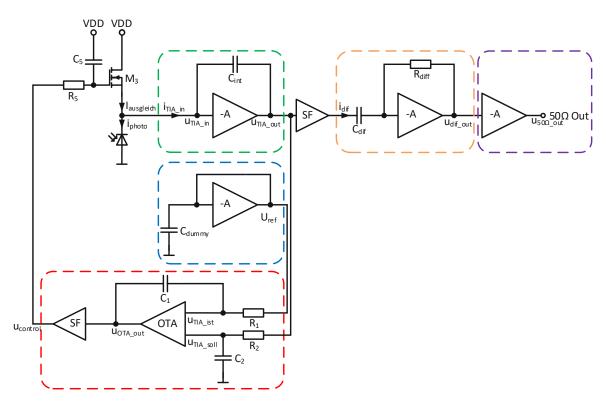

Das Schaltungskonzept mit der PMOS-Konstantstromquelle ist in Abbildung 2-4 dargestellt. In dieser Variante wird zum Ausgleich des mittleren Photostroms ein einziger P-Kanal MOS-Transistor als Konstantstromquelle verwendet. Der Drain-Source-Strom  $I_{DS}$  und damit der Ausgleichsstrom  $I_{ausgleich}$  kann in der Schaltung mithilfe des Gate-Potentials verändert werden. Die deutliche Abhängigkeit von der Drain-Source-Spannung und damit dem Potential des Eingangsknotens muss die Regelung bei der Ansteuerung des Gates ausgleichen.

Ein zusätzlicher NMOS (M<sub>2</sub>) dient als extern steuerbare Stromquelle. Mit dieser kann ein Bias-Strom parallel zur Photodiode eingeprägt werden, welcher auch bei sehr kleinen Photoströmen eine schnellere Einschwingzeit ermöglicht. Die damit erreichbare Einschwingzeit wird vergleichbar mit der Variante des NMOS-Sourcefolgers, welcher sonst deutlich schneller einschwingt. Durch die externe Ansteuerung kann ebenfalls Prozessschwankungen entgegengewirkt und der Empfänger optimiert werden.

Direkt nach dem Integrator wird das Signal für die weiteren Stufen im Signalpfad abgegriffen. Ein NMOS-Sourcefolger wird genutzt, um die Rückwirkung der folgenden Stufen, besonders der folgenden Kapazität, auf den TIA zu reduzieren. Farblich orange gekennzeichnet folgt der Differentiator, welcher aus dem ansteigenden und abfallenden Signal wieder ein rechteckiges Signal erzeugt und damit die empfangene Bitfolge herstellt. Die Kapazität am Eingang des Differentiators wirkt außerdem als Wechselstrom (AC) -Kopplung und hat zur Folge, dass der Gleichanteil gefiltert und unterdrückt wird. Der Arbeitspunkt am Ausgang des Sourcefolgers wirkt sich damit nicht auf den Arbeitspunkt des Differentiators aus. Design und Aufbau des Differentiators werden in Abschnitt 2.6 erläutert.

Abbildung 2-4 - Schaltungsstruktur des vorgeschlagenen optoelektronischen Empfängers mit PMOS-Konstantstromquelle

Der Ist-Wert für die Regelschleife wird ebenfalls direkt nach dem TIA abgegriffen. Um den TIA-Ausgang weniger zu belasten, wurde auch der Abgriff nach dem Sourcefolger getestet, was sich für die Stabilität der Regelschleife als nachteilig herausgestellt hat. Der direkte Abgriff des Ist-Wertes am TIA belastet diesen aufgrund des sehr großen Widerstand  $R_1$  mit 1  $M\Omega$  nur gering. Die Regelschleife, in Abbildung 2-4 rot dargestellt, vergleicht mithilfe eines OTAs den Ist-Wert am Inverter-Ausgang mit einer Referenzspannung und erzeugt daraus ein Spannungssignal, welches mithilfe eines

NMOS-Sourcefolgers auf das notwendige Spannungsniveau für die PMOS-Konstantstromquelle M<sub>1</sub> gebracht wird. Die Herausforderung besteht nun darin, den Ausgleichsstrom so zu regeln, dass er immer möglichst genau dem Mittelwert des Photostroms entspricht und damit die Eingangsspannung möglichst nahe im Arbeitspunkt gehalten werden kann. Außerdem muss die Regelschleife den Eingang nach dem Einschalten der Schaltung in den Arbeitspunkt führen. Die Regelung und damit die Ansteuerung der PMOS-Stromquelle wird im Abschnitt 2.4 beschrieben.

Nach dem Differentiator sorgt die Ausgangsstufe, eine Kette aus Invertern, dafür, dass das Signal von Inverter zu Inverter immer mehr verstärkt wird. In der Abbildung 2-4 ist diese Stufe violett gekennzeichnet. Der Signalhub wird immer größer und begrenzt, damit wird die Ausgangsstufe zum Begrenzungsverstärker (limiting amplifier). Der letzte Inverter ist so dimensioniert, dass er direkt einen  $50 \Omega$ -Ausgang darstellt und eine  $50 \Omega$ -Last treiben kann.

#### 2.2.2. Schaltungskonzept mit NMOS-Sourcefolger

Das Schaltungskonzept mit dem NMOS-Sourcefolger ist in Abbildung 2-5 dargestellt. Der grundlegende Aufbau ist identisch zu der Variante mit der PMOS-Konstantstromquelle. Die Schaltung ist allerdings dahingehend verändert wie der Ausgleich des mittleren Photostroms erfolgt. Es wird nun ein NMOS-Sourcefolger am Eingangsknoten genutzt, welcher diesen Ausgleich ermöglicht. Der Ausgleich des Stromes findet in dieser Variante nur indirekt über die Regelung der Spannung am Eingangsknoten durch den Sourcefolger statt.

Eine zusätzliche Bias-Stromquelle parallel zur Photodiode ist hier nicht vorgesehen, da die Einschwingzeit als ausreichend schnell betrachtet wird und der Bias-Strom-Transistor das Rauschen am Eingangsknoten deutlich erhöht hätte im Vergleich zum Schaltungskonzept mit der PMOS-Konstantstromquelle (dort bereits inklusive der Bias-Stromquelle).

In der Regelschleife muss berücksichtigt werden, dass der NMOS-Sourcefolger nicht invertiert. Um die erforderliche Invertierung zu erreichen, werden die Eingänge und die dazugehörige Beschaltung vertauscht. Der Sourcefolger, der sich in der Regelschleife nach dem OTA befindet, und die benötigte Spannungsverschiebung erreicht, muss an den Arbeitspunkt des NMOS-Sourcefolger angepasst werden. Die Ansteuerung des

NMOS-Sourcefolgers mit der dazu erforderlichen Regelschleife wird im Abschnitt 2.4 behandelt.

Abbildung 2-5 - Schaltungsstruktur des vorgeschlagenen optoelektronischen Empfängers mit dem NMOS-Sourcefolger

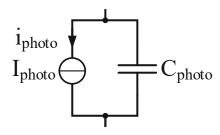

#### 2.3. PIN-Photodiode

Die in den vorgeschlagenen Schaltungen als optischer Detektor genutzte PIN-Photodiode hat eine vorgegebene fixe Kapazität von 3,5 fF. Diese kann in der genutzten XO035-Technologie direkt auf dem Chip integriert werden, ist aber nicht Teil dieser Arbeit. Als Modell der PIN-Photodiode wird eine ideale Stromquelle parallel zu einer Kapazität herangezogen, wie in Abbildung 2-6 dargestellt.[1] Alle Simulationen in Cadence wurden mit diesem Modell durchgeführt. Die Stromquelle ist eine Pulsquelle mit einer einstellbaren Anstiegs- und Abfallzeit sowie der einstellbaren Stromstärken für die Null- und Eins-Bits. Die Bitfolge selbst kann in einem File vorgegeben werden. Der Dunkelstrom  $i_{dark}$  muss in diese Werte integriert werden.

Abbildung 2-6 . PIN-Photodioden-Modell: ideale Stromquelle und Kapazität

#### 2.4. Stromregelung

Wie in Abschnitt 2.2 beschrieben, ist es notwendig, den Eingangsknoten des integrierenden TIAs in der Nähe des Arbeitspunktes zu halten, um diesen nicht zu überladen. Als Methode wurde hierfür der Ausgleich des mittleren Photostroms am Eingangsknoten mittels PMOS-Konstantstromquelle beziehungsweise NMOS-Sourcefolger gewählt. Die Herausforderung besteht nun darin, die Transistoren so anzusteuern, das der Ausgleichsstrom immer möglichst genau dem Mittelwert des Photostroms entspricht und folglich die Eingangsspannung möglichst nahe am Arbeitspunkt gehalten wird. Bei bekannter konstanten Empfangsleistung könnte dieser Ausgleichsstrom und damit die Gate-Spannung an M<sub>1</sub> und M<sub>3</sub> statisch vorgegeben werden. Da es aber in der Realität zu Schwankungen der Empfangsleistung kommt, ist dies nicht praktikabel. Es muss also eine Regelschleife genutzt werden, welche einen Ausgleich des tatsächlichen und veränderlichen mittleren Photostroms erreicht. Dies ist mit einer Regelschleife möglich, welche ein Tiefpassverhalten aufweist und damit nur niederfrequente Ströme am Eingangsknoten ausgleicht.

Die Regelschleife fügt damit dem Signalpfad ein Hochpassverhalten hinzu und macht den Empfänger zu einem Bandpass. Dies hat den weiteren Vorteil, dass ein möglicher Gleichanteil, der beispielsweise vom Hintergrundlicht stammt oder von leichten Abweichungen der gleichanteilsfreien Codierung (durch Beeinflussungen Übertragungskanal), zu einem gewissen Grad ausgeglichen wird. Es werden außerdem Rauschanteile, besonders die des Funkelrauschens (1/f Rauschen), welche in dem gefilterten Bereich liegen, im Signalpfad deutlich gedämpft. Hierüber wird das äquivalente Eingangsrauschen reduziert. Ohne das Tiefpassverhalten in Regelschleife würde diese praktisch das gesamte Nutzsignal auslöschen.

Tiefpassverhalten der Regelschleife mit der Grenzfrequenz  $f_{g\_fb}$  wird zu einem Hochpassverhalten des Signalpfades. Daher muss die Grenzfrequenz der Regelschleife sinnvoll gewählt werden, um das Datensignal nicht zu verfälschen. Auch wenn generell das übertragene Signal hochfrequenter ist, muss berücksichtig werden, dass Folgen gleicher Binärsymbole (Null- oder Eins-Bits) niederfrequentere Anteile im Datensignal verursachen, welche nicht gefiltert werden dürfen. Je höher diese Grenzfrequenz ist, desto unempfindlicher wird der Empfänger für niederfrequente Störeinflüsse und das Rauschen sinkt stärker, gleichzeitig wird allerdings die niedrigste mögliche Frequenz für das Datensignal reduziert und damit die Bandbreite gesenkt.

Da die vorgeschlagene Schaltung im ersten Schritt nicht auf eine konkrete Übertragungsanwendung begrenzt ist, kann keine reale Vorgabe für die kleinste vorkommende Signalfrequenz erfolgen. Die obere Grenzfrequenz des Empfängers wird so ausgelegt, dass ein 100 Mb/s NRZ-Signal (10 ns Bitdauer) empfangen wird. Für die Dimensionierung wird daher davon ausgegangen, dass maximal 64 bit mit 10 ns pro Bit hintereinander mit dem gleichen Binärsymbol (Null-Bit oder Eins-Bit) empfangen werden. Dies entspricht bereits einem Worstcase-Szenario, da hier der Ausgang des Integrators (je nach Empfangsleistung) sehr schnell überladen wird. Daraus ergibt sich eine untere Grenzfrequenz des Nutzsignals

$$f_{signal\_min} = \frac{1}{128bit * \frac{10ns}{bit} * 2} = 390,63 \text{ kHz}$$

(32)

die deutlich unter der eigentlichen Signalfrequenz liegt. Alle Frequenzen über  $f_{signal\_min}$ dürfen durch die Regelschleife nicht ausgelöscht werden. Die obere Grenzfrequenz der Regelschleife  $f_{g_{-}fb}$  ergibt sich daher zu

$$f_{afb} \ge f_{signal\ min}$$

(33)

Die Regelschleife hat zusätzlich eine weitere Funktion. Sie muss die Schaltung nach dem Einschalten in den Betriebspunkt bringen. Dazu muss die Spannung am Eingangsknoten in den Arbeitspunkt geführt werden.

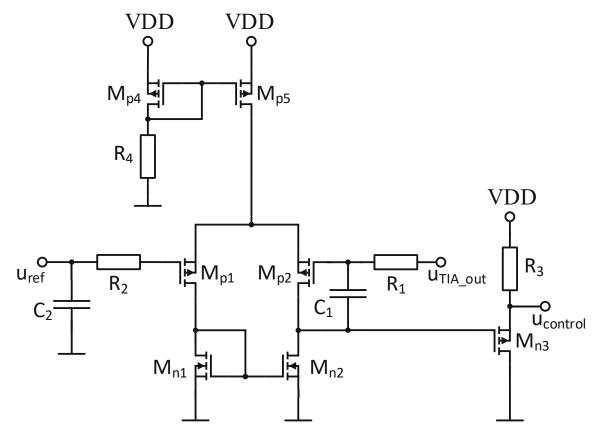

In den vorgeschlagenen Schaltungen besteht der erste Teil der Regelschleife aus einem OTA, welcher das Ausgangssignal des TIAs  $u_{TIA\_out}$  und die Referenzspannung  $U_{ref}$ vergleicht. Ergibt sich eine Abweichung der zwei Spannungen, führt dies zu einer

proportionalen Veränderung der OTA-Ausgangsspannung. Um die in Gleichung (33) beschriebene Grenzfrequenz einzuführen, werden die zwei OTA-Eingänge mit RC-Gliedern beschaltet. Für eine stabile Regelung wird der Kondensator am Ist-Signal-Eingang des OTAs  $u_{TIA\;ist}$  auf den OTA Ausgang  $u_{OTA\;out}$  gekoppelt. Die Rückkopplung fügt dem Zweig neben dem P-Anteil ein integrierendes Verhalten (I-Anteil) hinzu und ist notwendig, um eine bleibende Regelabweichung zu verhindern.[19]

Abbildung 2-7 - Schaltung der Regelschleife der PMOS-Schaltungsvariante

Für das Erreichen der sehr kleinen Ausgleichströme muss zum einen die Source-Gate-Spannung der PMOS-Konstantstromquelle klein und zum anderen das Gate-Source-Potential des NMOS-Sourcefolgers relativ groß sein. Das daher jeweils nötige Gate-Potential muss in seinem Arbeitspunkt verhältnismäßig weit über der mittleren Versorgungspannung liegen. Damit ergibt sich bei einem mittleren Photostrom von 2 nA ein Gate-Potential bei dem PMOS-Konstantstromquellen-Transistor im Bereich von 2,8V und bei dem NMOS-Sourcefolger-Transistor im Bereich von 2,6 V. Der linear mögliche Arbeitspunkt der Ausgangspannung des OTAs liegt damit deutlich zu niedrig, was eine direkte Ansteuerung unmöglich macht. Daher wird nach dem OTA ein PMOS-Sourcefolger eingesetzt, um die Spannung in den benötigten Arbeitspunkt zu verschieben. Der folgende Tiefpass nach dem PMOS Sourcefolger dient lediglich dazu, mögliches hochfrequentes Rauschen nochmals direkt vor der Einspeisung des Ausgleichsstromes abzuschwächen. Seine Grenzfrequenz liegt mit 127 MHz nahezu drei Dekaden über der Grenzfrequenz der Regelschleife und hat somit keinen direkten Einfluss auf das Datensignal.

Wie in Abschnitt 2.2.2 beschrieben, ist der NMOS-Sourcefolger nicht invertierend, im Vergleich mit der dargestellten Schaltung der Regelschleife der PMOS-Schaltungsvariante in Abbildung 2-7 müssen die Eingänge des OTAs und die dazugehörige Beschaltung vertauscht werden, um die Invertierung zu erreichen.

| Transistor                         | Weite  | Länge   |

|------------------------------------|--------|---------|

| $M_{P1}$                           | 24 μm  | 0.35 μm |

| $M_{N1}$                           | 30 μm  | 0.35 μm |

| $M_{P2}$                           | 24 μm  | 0.35 μm |

| $M_{N2}$                           | 30 μm  | 0.35 μm |

| M <sub>N3</sub><br>(PMOS-Variante) | 10,4μm | 0.35 μm |

| M <sub>N3</sub><br>(NMOS-Variante) | 14,6µm | 0.35 μm |

| $M_{P4}$                           | 50 μm  | 0.35 μm |

| $M_{P5}$                           | 50 μm  | 0.35 μm |

|                                    | 2      |         |

Wert Bauteil  $R_1$  $100 \text{ k}\Omega$  $R_2$  $100 \text{ k}\Omega$ R<sub>3</sub> (PMOS-Variante) 843,92 fF R<sub>3</sub> (NMOS-Variante) 843,92 fF  $R_4$ 7496,925  $\Omega$  $C_1$ 843,92 fF  $C_2$ 843,92 fF Ь,

Tabelle 2-1 - a, Gate-Weiten und -Längen der Transistoren b, Widerstands- und Kapazitätswerte der Regelschleife in Abbildung 2-7

Die Referenzspannung wird mithilfe eines CMOS-Inverters realisiert, wobei der Eingang und der Ausgang kurzgeschlossen werden und die Referenzspannung mit den entsprechenden Weiten der Transistoren erzeugt wird. Die Weiten und Längen der Transistoren entsprechen exakt denen des TIA-Inverts. Im Layout kann damit mit einem guten Matching die Sensitivität der Regelschleife gegenüber Prozessschwankungen und Temperaturen reduziert werden. Im Unterschied zu anderen Schaltungen wird hier statt

einer exakten TIA-Replika als Dummy-Pfad nur eine Referenzspannung erzeugt, die den Arbeitspunkt des Integrators vorgibt, da aufgrund des integrierenden Verhaltens eine exakte Replika nicht ohne weiteres möglich ist. Die Referenzspannung entspricht der halben Versorgungspannung und damit dem Sollwert der TIA-Ausgangsspannung  $u_{TIA~out}$ . Die Weiten und Längen der Gates sind in Tabelle 2-1 dargestellt.

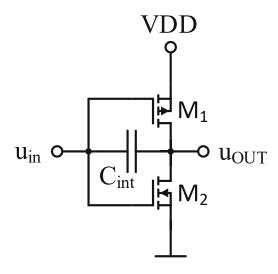

#### 2.5. Integrierender TIA

Der Integrator stellt in den vorgeschlagenen Schaltungen den Transimpedanzverstärker TIA dar und übernimmt damit die Funktion des Vorverstärkers. Er erzeugt aus seinem Eingangsstrom  $\emph{i}_{int}$  eine entsprechende Spannung am Ausgang. Der TIA bildet neben der Regelschleife den wichtigsten Teil der vorgeschlagenen Schaltungen. Durch die Position an erster Stelle der Empfängerkette und der im Verhältnis zu den nachfolgenden Verstärkerstufen größten Verstärkung wirkt sich sein Rauschen deutlich auf das Ausgangsrauschen aus. Das Ziel muss hier also eine möglichst große Verstärkung bei gleichzeitig möglichst geringem Ausgangsrauschen beziehungsweise dem sich daraus ergebenden äquivalenten Eingangsrauschen sein. Dieses bestimmt maßgeblich die Sensitivität des Empfängers und damit den kleinsten möglichen Photostrom.

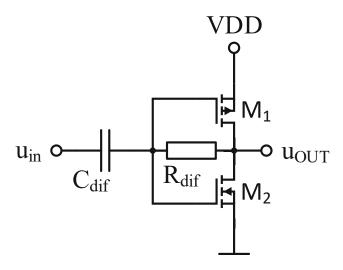

Abbildung 2-8 - Schaltungskonzept Transimpedanzverstärker TIA

Ein CMOS-Inverter mit sehr kleinen Weiten, wie in Abschnitt 1.6 behandelt, dient dem TIA als Verstärker, um das Rauschen am Eingangsknoten möglichst gering zu halten. Das Feedback wird kapazitiv realisiert, um das Rauschen des sonst oft üblichen ohmschen Feedbackwiderstandes zu eliminieren. Der TIA erhält damit ein integriertes Verhalten und wird zu einem Integrator für den eingehenden Strom. Der Eingangsstrom wird mit der effektiven Integrationskapazität in eine Spannung umgesetzt.

Die Veränderung der Ausgangsspannung des Integrators  $\Delta u_{TIA\_out}$  ergibt sich aus dem Eingangsstrom  $i_{TIA\_in}$  näherungsweise mit

$$\Delta u_{TIA_{out}}(t) \approx -\frac{A_V}{C_{int_{eff}}} \int i_{TIA_{in}}(t) dt$$

(34)

Damit sinkt die Ausgangsspannung konstant, wenn ein konstanter Eingangsstrom in den Integrator vorhanden ist. Die effektive Integrationskapazität  $\mathcal{C}_{int\_eff}$  ergibt sich maßgeblich aus der Kapazität der Photodiode und aus den parasitären Gate-Drain-Kapazitäten der Transistoren, welche durch den Millereffekt um den Faktor 1 + Agrößer wirken, wobei A die Spannungsverstärkung des Inverts aus Gleichung (21) ist. Eine dezidierte Integrationskapazität ist in Abbildung 2-4 beziehungsweise Abbildung 2-5 nur schematisch dargestellt und ist in den vorgeschlagenen Schaltungen nicht dezidiert vorhanden. Das kapazitive Feedback erfolgt in der realen Schaltung ausschließlich über die parasitären Kapazitäten der Inverter-Transistoren. Der Eingangsstrom summiert sich aus dem negativen Photostrom und dem Ausgleichsstrom. In der Variante mit der PMOS-Konstantstromquelle addiert sich noch der zusätzliche, extern einstellbare Bias-Strom  $i_{bias}$  hinzu.

#### 2.6. Differentiator

Um aus dem integrierten Signal wieder die empfangenen Pulse zu erhalten, wird ein Differentiator genutzt. Dieser erzeugt näherungsweise proportional der Änderungsrate der Eingangsspannung eine Ausgangsspannung zu

$$u_{dif\_out} \approx -k_2 \frac{du_e}{dt}$$

(35)

Wobei k ein Faktor ist, welcher sich aus der Beschaltung ergibt. Nachgeschaltet hinter dem Integrator erzeugt der Differentiator damit eine Ausgangsspannung von

$$u_{dif\_out} \approx -k_2 \frac{d\left(-\frac{k}{C_{int_{eff}}} \int i_{TIA\_in} \ dt\right)}{dt} = k_2 * i_{TIA\_in}$$

(36)

und stellt damit die empfangene Bit-Folge als Rechtecksignal wieder her. Die Bandpasscharakteristik, welche sich durch die oberen und unteren Grenzfrequenzen ergibt, ist in der Formel nicht berücksichtigt. Bei richtiger Wahl dieser Frequenzen ist die resultierende Verfälschung in Bezug auf den Photostrom beziehungsweise der sich mit dem Ausgleichsstrom ergebende Strom in den TIA  $i_{TIA\ in}$  vernachlässigbar.

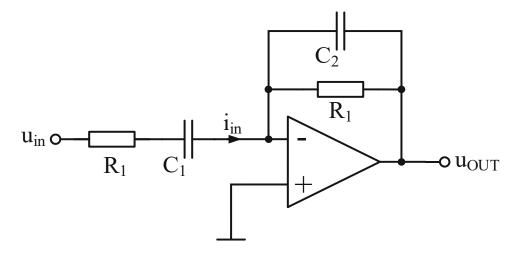

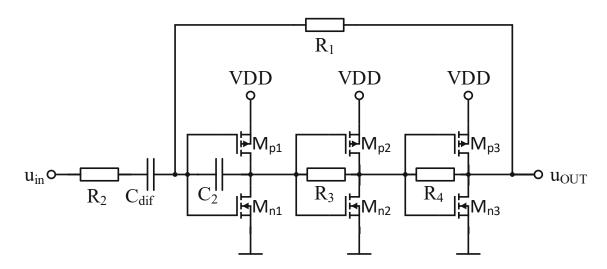

Abbildung 2-9 - Einfacher CMOS-Inverter als Differentiator

Der Differentiator besteht grundsätzlich aus einem Verstärker mit entsprechender Beschaltung, wie in Abschnitt 1.8 veranschaulicht. Als Verstärker wird in den vorgeschlagenen Schaltungen wieder ein CMOS-Inverter genutzt, da dieser in der Simulation ein geringeres Rauschen als aufwendigere Verstärkerschaltungen aufweist. In der nominalen Simulation funktioniert ein einfacher CMOS-Inverter mit der beschriebenen Beschaltung, wie in Abbildung 2-9 dargestellt, gemäß den gewünschten Spezifikationen, allerdings zeigt sich eine starke Sensitivität des Arbeitspunktes gegenüber Prozessschwankungen. Der Signalhub am Ausgang des Differentiators ist geringer als die Schwankung des Arbeitspunktes und verursacht damit in der Monte-Carlo-Analyse Bit-Fehler in den folgenden limitierenden Verstärkern.

Um dies zu verhindern, muss der Signalhub größer sein als der mögliche Einfluss statistischer Prozesstoleranzen inklusive Änderungen, die durch die Temperatur Die damit benötigte deutlich größere Verstärkung des verursacht werden. Differentiators wird durch mehrere CMOS-Inverter-Stufen mit mehreren Rückkoppelzweigen zum Erzeugen des gewünschten Frequenzganges erreicht. Die implementierte Schaltung ist in Abbildung 2-10 dargestellt. Der serielle Kondensator  $c_{dif} = 1,23 \ pF$  am Eingang schwächt das Signal immer stärker ab, je niedriger die Frequenz ist. Hieraus ergibt sich bereits der konstante Anstieg im Frequenzbereich und damit das differenzierende Verhalten.

Abbildung 2-10 - Implementierter Differentiator mit mehreren CMOS-Invertern

Das ohmsche Feedback mit  $R_1=100~k\Omega$  über alle Stufen begrenzt die Verstärkung der gesamten Kette und macht diese stabiler über Prozessschwankungen. Die ohmschen Feedbacks  $(R_3 = 5011,6 \,\Omega, R_4 = 2007,255 \,\Omega)$  der zweiten und dritten Stufe reduzieren jeweils deren Verstärkung und machen diese selbst ebenfalls unempfindlicher gegenüber Prozess- und Temperaturschwankungen. Die kapazitive Rückkopplung an der ersten Stufe  $C_2 = 66.9 \, fF$  reduziert die Verstärkung für größere Frequenzen und limitiert damit die Bandbreite gewollt nach oben, um Rauschen oberhalb der Signalfrequenzen möglichst zu unterdrücken. Die Kopplung könnte auch über alle Stufen (parallel zu  $R_1$ ) realisiert werden, hätte allerdings eine zu starke Reduktion der Bandbreite zur Folge. Der Metall-Kondensator  $\mathcal{C}_2$  befindet sich bereits am möglichen Minimum der Technologie (minimal mögliche Fläche) und könnte daher an dieser Stelle nicht mehr weiter verkleinert werden. Auf den expliziten seriellen Widerstand  $R_2$  am Eingang, welcher zusammen mit dem seriellen Kondensator  $\mathcal{C}_{dif} = 1.22936\,pF$  die obere

Knickfrequenz bestimmen würde, wird nach der Simulation verzichtet, da sich bereits ohne diesen eine ausreichend niedrige obere Grenzfrequenz ergibt.

| Transistor      | Weite    | Länge   |

|-----------------|----------|---------|

| M <sub>P1</sub> | 150 μm   | 0.35 μm |

| $M_{N1}$        | 48,4 μm  | 0.35 μm |

| $M_{P2}$        | 48,15 μm | 0.35 μm |

| $M_{N2}$        | 13,95 μm | 0.35 μm |

| $M_{P3}$        | 100 μm   | 0.35 μm |

| $M_{N3}$        | 32,4 μm  | 0.35 μm |

Tabelle 2-2 - Gate-Weiten und -längen der Transistoren des Differentiator in Abbildung 3-10

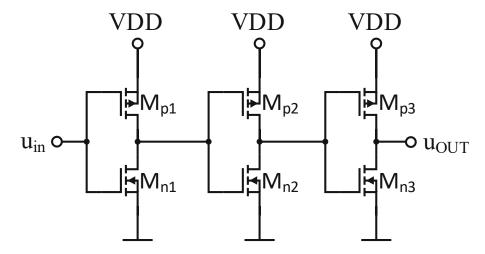

### 2.7. Ausgangsverstärkerstufen

Nach dem Differentiator muss das Signal noch weiter verstärkt werden, um am Ende einen  $50 \Omega$ -Ausgang zur Verfügung stellen zu können. Es soll möglich sein, direkt ein Messgerät, wie ein Oszilloskop, mit einem Eingangswiderstand von  $50~\Omega$  anzuschließen. Als notwendigen Signalhub an einer  $50 \Omega$ -Last wird 1,5 V als ausreichend vorgegeben. Außerdem soll der Empfängerausgang einen möglichst niedrigen Ausgangswiderstand aufweisen. Dies wird durch mehrere CMOS-Inverter-Stufen ohne weitere Beschaltung erreicht. Um die geforderten 1,5 V Signalhub an einer 50  $\Omega$ -Last zu erreichen, sind drei CMOS-Inverter notwendig, welche hintereinander geschaltet werden. Die Inverter verstärken das Signal nicht mehr linear, sondern limitieren den Hub und wirken somit als Begrenzungsverstärker (limiting amplifier).

Die Weite der Transistoren wird von Stufe zu Stufe größer, die Werte sind der Tabelle 2-3 zu entnehmen. Der letzte Inverter in der Kette ist so dimensioniert, dass der Ausgang der Stufe unbelastet bei 0 beziehungsweise 3,3 V limitiert. Mit einer 50  $\Omega$ -Last wird ein Signalhub von 1,5V erreicht. Damit ist der Ausgangswiderstand des Inverts ausreichend gut an die Last angepasst. Es wird auf einen exakten Ausgangswiderstand von  $50~\Omega$  verzichtet, da  $50~\Omega$  HF-Messgeräte am Ende einer  $50~\Omega$ -Leitung Reflexionen genügend unterdrücken.[20] Die genutzte Schaltung für die Ausgangsstufe ist in Abbildung 2-11 dargestellt.

Abbildung 2-11 – Ausgangsverstärkerstufen

|   | Transistor | Weite    | Länge   |

|---|------------|----------|---------|

| - | $M_{P1}$   | 48,25 μm | 0,35 µm |

|   | $M_{N1}$   | 15,95 μm | 0,35 µm |

|   | $M_{P2}$   | 100 μm   | 0,35 µm |

|   | $M_{N2}$   | 32,4 µm  | 0,35 µm |

|   | $M_{P3}$   | 140 µm   | 0,35 µm |

|   | $M_{N3}$   | 45,7µm   | 0,35 μm |

|   |            |          |         |

Tabelle 2-3 Gate-Weiten und -Längen der Transistoren der Ausgangsstufe in Abbildung 2-11

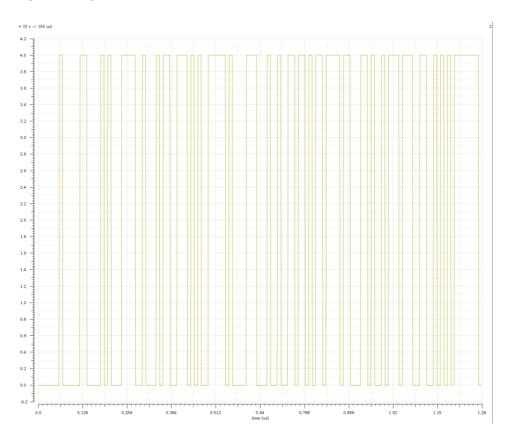

### 3. Ergebnisse

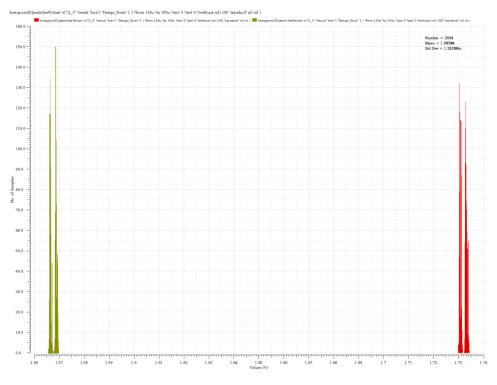

Alle Schaltungen sind mit der "Virtuoso Custom IC Design Environment XL" von Cadence designed und mit dieser ebenfalls simuliert, wobei die "ADE XL" verwendet wird. Als Simulator dient die "Spectre Simulation Engine", ebenfalls von Cadence. Alle Simulationen wurden Pre-Layout durchgeführt. Als Signal für den Photostrom wird eine  $100 \, Mb/s$  PRBS-Bitfolge mit der Länge  $2^7 - 1$  gewählt, um ein Bit ergänzt um vollständige Mittelwertfreiheit zu erreichen. Die Bitfolge wird einfach wiederholt und ist selbst gleichanteilsfrei, da in jeder Bitsequenz gleich viele logische Einsen und Nullen vorkommen. Das Signal ist NRZ (Non-Return-to-Zero)-codiert und hat eine Anstiegsund Abfallzeit von je 1 ns. Eine Sequenz des damit erzeugten Photostroms ist in Abbildung 3-1 dargestellt.

Abbildung 3-1 - eine Sequenz des erzeugten Photostroms: 128 Bitfolgen, NRZ, 100 Mb/s, 1ns Anstiegs- und Abfallzeit

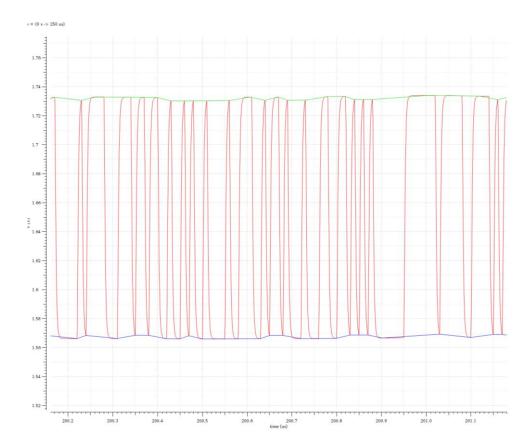

#### 3.1. Verhalten im Zeitbereich

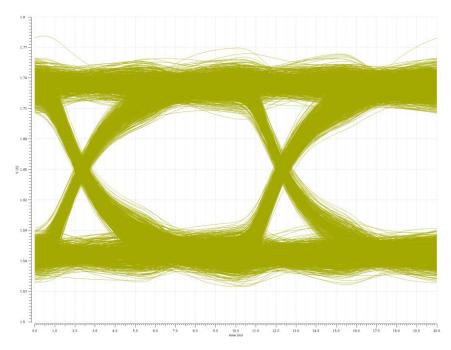

Das Verhalten der Schaltung im Zeitbereich stellt einen wichtigen Indikator für die Überprüfung der gewünschten Funktionen dar. Daher wird in diesem Teil das Zeitverhalten analysiert. Nachfolgende Beschreibungen beziehen sich auf einen Photostrom von 4 nA (= 2 nA mittlerer Photostrom).

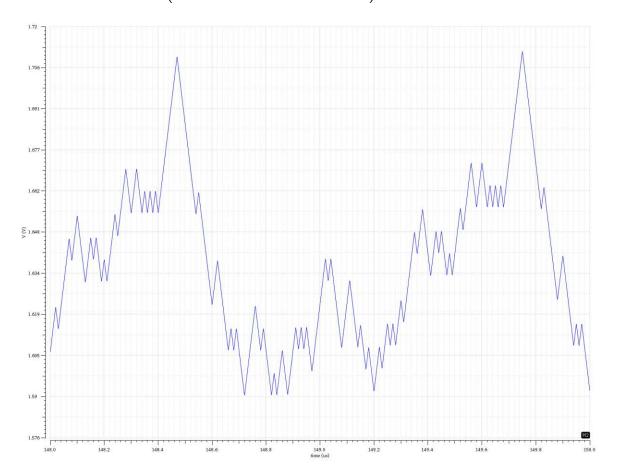

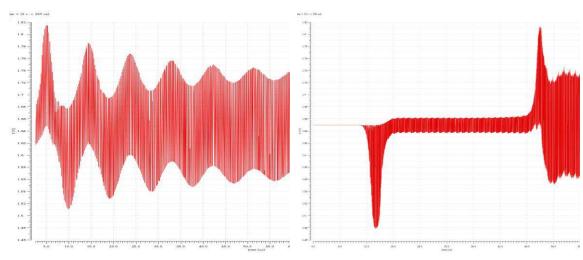

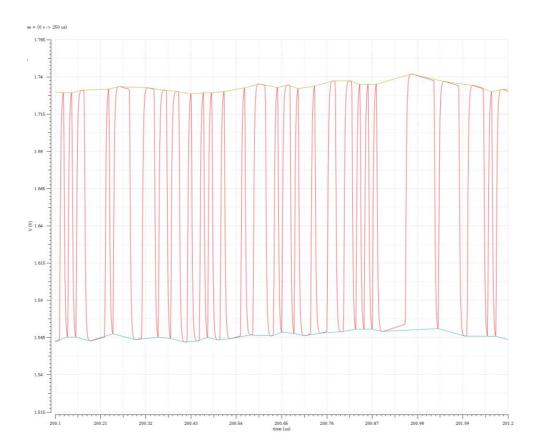

Abbildung 3-2 – Spannung am Ausgang des Integrators U<sub>TIA</sub> out im eingeschwungenen Zustand in der Schaltungsvariante mit der PMOS-Konstantstromquelle am bei 2 nA mittleren Photostrom mit einem Bias-Strom von 4 nA in M2

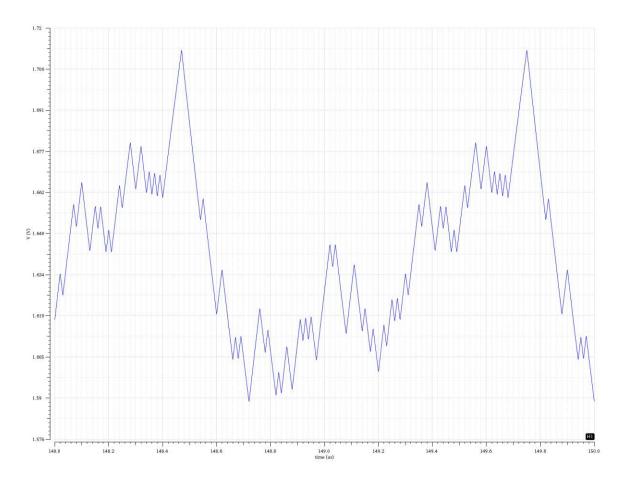

Die Spannung am Ausgang des Integrators  $U_{TIA\_out}$  ist für die Schaltungsvariante mit der PMOS-Konstantstromquelle in Abbildung 3-2 und für die Schaltungsvariante mit dem NMOS-Sourcefolger in Abbildung 3-3 dargestellt. Der erwartete lineare Anstieg beziehungsweise Abfall der Spannung pro empfangenem Bit ist deutlich zu erkennen. In der NMOS-Variante kann das Entgegenwirken der Regelung ebenfalls festgestellt werden, da nach zwei verschiedenen Binärsymbolen die Spannung nicht exakt auf den gleichen Spannungswert zurückkehrt. Je länger die Bitsequenz, in der sich die logischen Einsen und Nullen ausgleichen, dauert, desto stärker weicht die Spannung vom Arbeitspunkt ab. Größere Photoströme verursachen daher nach relativ kurzer Zeit, bei gleicher Frequenz und gleichem Bitmuster, eine Überladung des Ausgangsknotens.

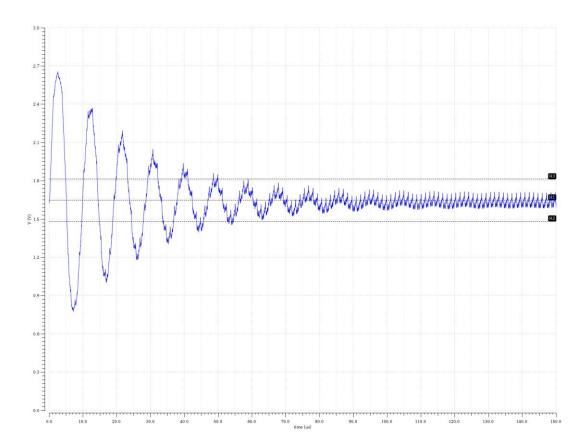

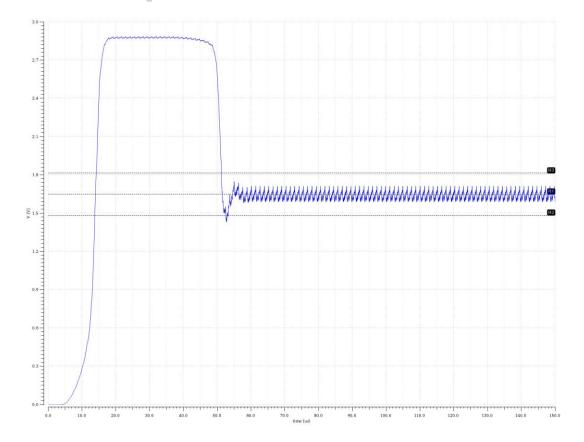

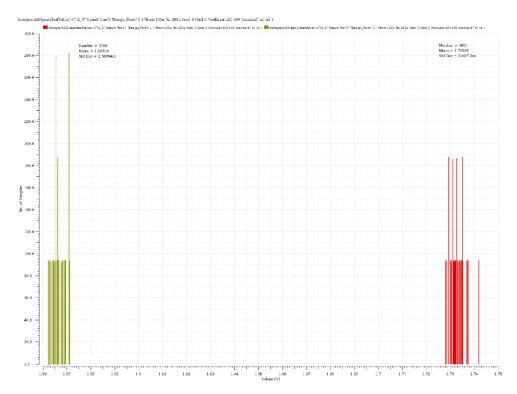

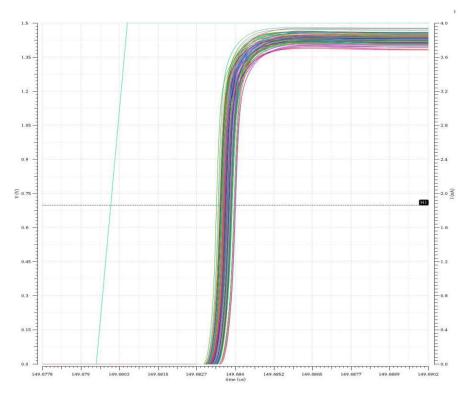

Beide Schaltungen benötigen nach dem Einschalten eine gewisse Zeit, bis der Arbeitspunkt stabil erreicht ist. Durch den Bias-Strom-Transistor M<sub>2</sub> in der PMOS-

Variante ist deren Geschwindigkeit mit jener der NMOS-Variante vergleichbar, wobei bei dieser sowohl Eingangs- als auch Ausgangsspannung des Integrators ungefähr im Arbeitspunkt bei t=0 s starten. Die Spannung am Ausgang des Integrators  $U_{TIA\ out}$ ist für die Variante mit der PMOS-Konstantstromquelle in Abbildung 3-4 und für die Variante mit dem NMOS-Sourcefolger in Abbildung 3-5 dargestellt. Die Einschwingzeit, nach der die Spannung nicht um mehr als  $\pm 10~\%$  des Unterschiedes zwischen Anfangsund Endwert (Arbeitspunkt) schwankt, kann für den Integrator Ausgang  $U_{TIA\_out}$  bei der NMOS-Variante angegeben werden, da diese von 0 V in den Arbeitspunkt (1,65 V) gebracht wird. Diese  $\pm 10 \,\%$  ergeben dann  $\pm 0,165 \,V$  vom Arbeitspunkt. Für eine bessere Vergleichbarkeit wird für die PMOS-Variante ebenfalls der Wert ±0,165 V um den Arbeitspunkt herangezogen. Für die PMOS-Variante (mit 4 nA Bias-Strom) beträgt diese Einschwingzeit 54,51 μs und für die NMOS-Variante 53,21 μs. Durch den Bias-Strom bei der PMOS-Variante ist die Einschwingzeit der beiden Varianten praktisch identisch.

Abbildung 3-3 - Spannung am Ausgang des Integrators UTIA out im eingeschwungenen Zustand in der Schaltungsvariante mit dem NMOS-Sourcefolger bei 2 nA mittlerem Photostrom

Abbildung 3-4 - 2 Einschwingen der Schaltungsvariante mit der PMOS-Konstantstromquelle am Ausgang des Integrators  $U_{TIA\_out}$  bei 2 nA mittlerem Photostrom mit einem Bias-Strom von 4 nA in  $M_2$

Abbildung 3-5 - Einschwingen der Schaltungsvariante mit dem NMOS-Sourcefolger am Ausgang des Integrators  $U_{TIA\_out}$  bei 2 nA mittlerem Photostrom

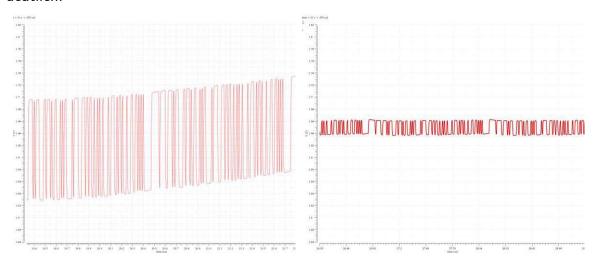

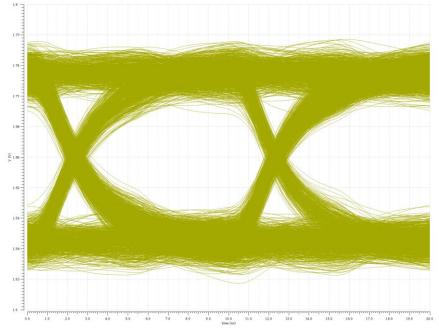

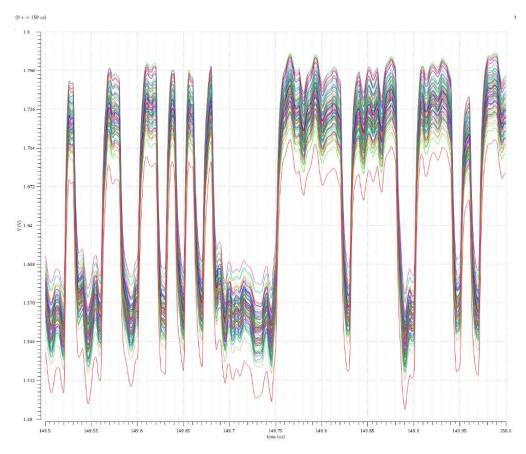

Das Einschwingverhalten am Ausgang des Differentiators bei einem mittleren Photostrom von 2nA ist für die Variante mit der PMOS-Konstantstromquelle in Abbildung 3-6 und für die Variante mit dem NMOS-Sourcefolger Abbildung 3-7 dargestellt. Bei der PMOS-Variante ist die korrekte Bitfolge am Ausgang allerdings schon vor der Einschwingzeit von 54,51 µs zu erkennen, da der Signalhub am Ausgang des Differentiators (zu sehen in der vergrößerten Darstellung des Einschwingens in Abbildung 3-7) trotz der Schwingung bereits groß genug ist für die Ausgangsstufe. Bei der NMOS-Variante liegt die korrekte Bitfolge auch bereits nach ungefähr 18ns nach dem Differentiator korrekt an, allerdings ist der Signalhub zu gering für ein Ausgangssignal mit ausreichend Hub für die nachfolgenden Stufen, wie der Abbildung 3-9 zu entnehmen ist. Bei der Schaltungsvariante mit dem NMOS-Sourcefolger bleibt die Bitfolge am Ausgang des Differentiators nach dem Einschwingen auch exakt im Arbeitspunkt. Die Variante mit dem PMOS schwingt minimalst um den Arbeitspunkt.

Abbildung 3-6 Einschwingen der Schaltungsvariante mit der PMOS-Konstantstromquelle am Ausgang des Differentiators U<sub>dif</sub> out bei 2 nA mittlerem Photostrom mit einem Bias-Strom von 4 nA

Abbildung 3-7 - Einschwingen der Schaltungsvariante mit dem NMOS-Sourcefolger am Ausgang des Differentiators U<sub>dif out</sub> bei 2 nA mittlerem Photostrom

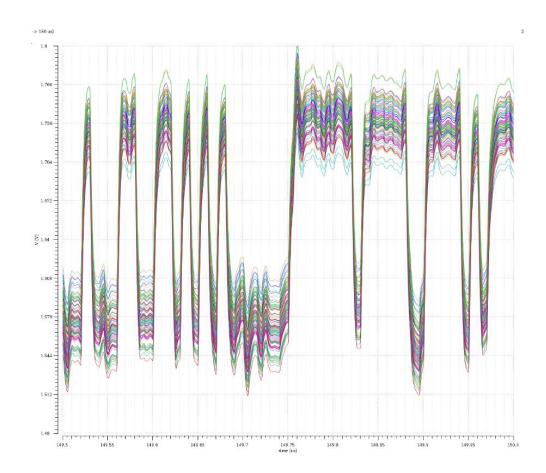

Ist die Schaltung eingeschwungen, liefern beide Schaltungsvarianten einen ähnlichen Signalpegel für logische Nullen und Einsen. Die Auswertung der Mittelwerte der Bitspannungen des Datenstroms ist im Abschnitt 3.3 dargelegt. Die Variante mit der PMOS-Konstantstromquelle ist, trotz der niedrigeren unteren Grenzfrequenz (siehe Kapitel 3.2), unempfindlicher gegenüber längeren Bit-Perioden (in welcher sich die logischen Nullen und Einsen ausgleichen). In der Variante mit dem NMOS-Sourcefolger ist die Bit-Periode deutlich zu erkennen und damit wird das Entgegenwirken der

Regelschleife auf die durch die Integration steigende Spannung am Integrator  $u_{\mathit{TIA\_out}}$ deutlich.

Abbildung 3-8 Einschwingen der Schaltungsvariante mit der PMOS-Konstantstromquelle am Ausgang des Differentiators U<sub>dif</sub> out, bei 2 nA Photostrom mit einem Bias-Strom von 4 nA; vergrößerte Darstellung von Abbildung 3-6

Abbildung 3-9 - Einschwingen der Schaltungsvariante mit dem NMOS-Sourcefolger am Ausgang des Differentiators U<sub>dif</sub> out, bei 2 nA mittlerem Photostrom; vergrößerte Darstellung von Abbildung

Abbildung 3-10 Zeitlicher Verlauf am Ausgang des Differentiators Udif out im eingeschwungenen Zustand der Schaltungsvariante mit der PMOS-Konstantstromguelle bei 2 nA mittlerem Photostroms mit einem Bias-Strom von 4 nA

Abbildung 3-11 - Zeitlicher Verlauf am Ausgang des Differentiators  $U_{dif\_out}$  im eingeschwungenen Zustand der Schaltungsvariante mit dem NMOS-Sourcefolger bei 2 nA mittlerem Photostroms

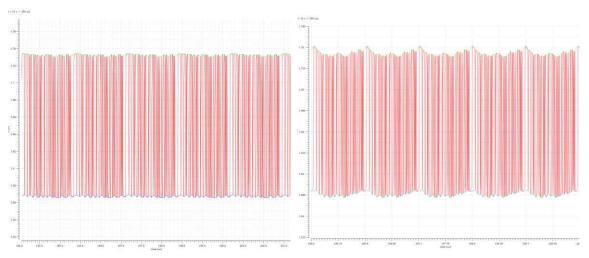

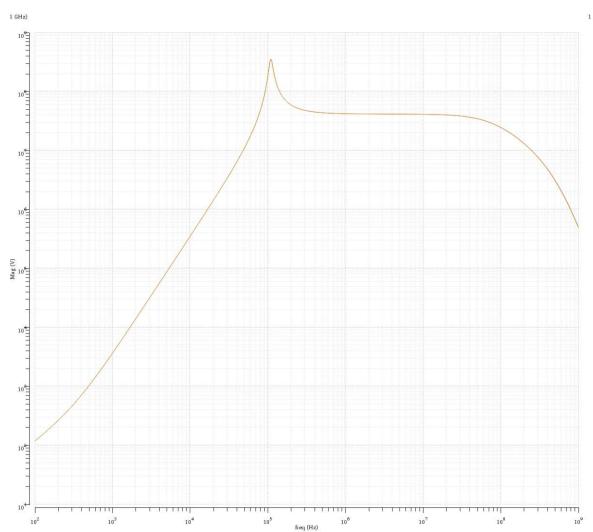

### 3.2. Frequenzübertragungseigenschaften

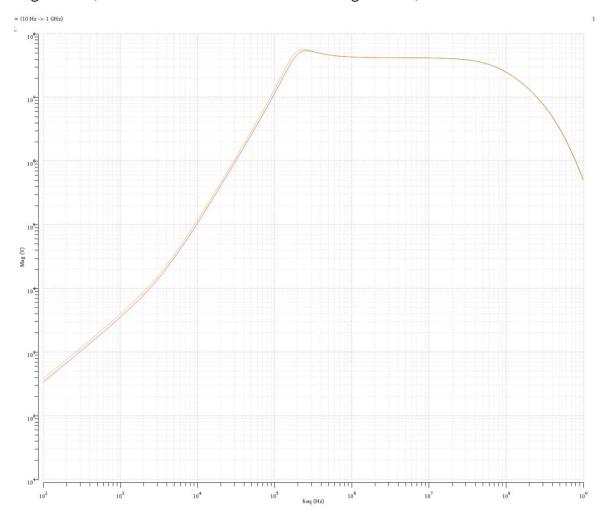

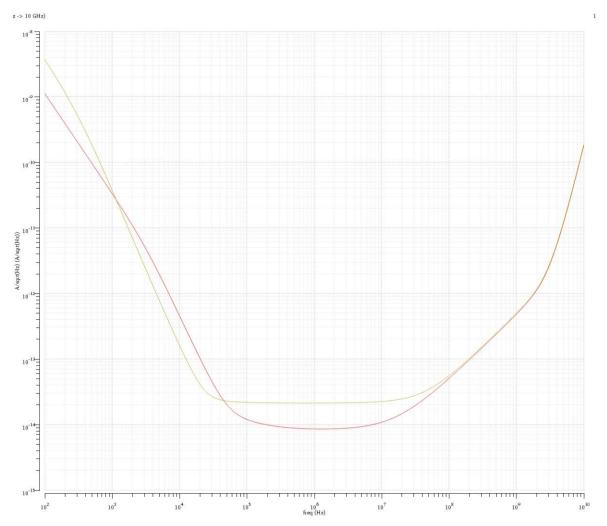

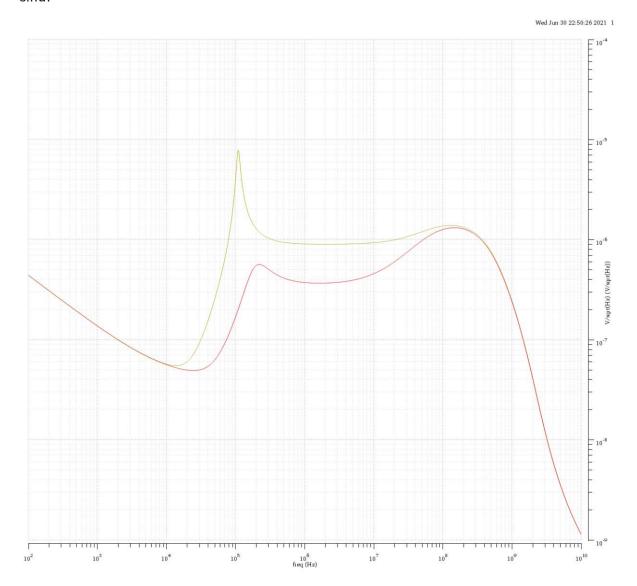

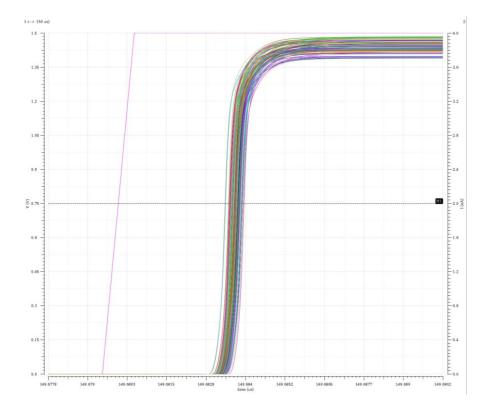

Die Frequenzübertragungseigenschaften des Photostroms auf den Ausgang des Differentiators sind essentiell zur Beurteilung der empfangbaren Bitfolgen. Am Ausgang des  $50 \Omega$ -Treibers ergibt sich aufgrund der Ausgangsverstärkerstufen aus Abschnitt 2.7 kein aussagekräftiger Frequenzgang, da die Verstärker limitierend wirken und Cadence