# Intelligentes Testen und Konfiguration von SoCs durch die Nutzung von IJTAG ergänzt durch on-chip Mikroprozessor-Zugriff

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## **Technische Informatik**

eingereicht von

### Clemens Pircher, BSc

Matrikelnummer 01525889

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Ao. Univ. Prof. Dipl.-Ing. Dr. techn. Andreas Steininger

Mitwirkung: Dipl.-Ing. Heimo Hartlieb

Univ.Ass. Dipl.-Ing. Florian Ferdinand Huemer, BSc

| Wien, 3. Februar 2022 |                 |                    |

|-----------------------|-----------------|--------------------|

|                       | Clemens Pircher | Andreas Steininger |

# Smart SoC testing and remote configuration facilitated by the use of IJTAG complemented with on-chip microprocessor access

## **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

## Computer Engineering

by

## Clemens Pircher, BSc

Registration Number 01525889

| to | the | Faculty of | of | Informatics |

|----|-----|------------|----|-------------|

| to | the | Faculty of | )t | Informatics |

at the TU Wien

Advisor: Ao. Univ. Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

Assistance: Dipl.-Ing. Heimo Hartlieb

Univ.Ass. Dipl.-Ing. Florian Ferdinand Huemer, BSc

| Vienna, 3 <sup>rd</sup> February, 2022 |                 |                    |

|----------------------------------------|-----------------|--------------------|

|                                        | Clemens Pircher | Andreas Steininger |

# Erklärung zur Verfassung der Arbeit

Clemens Pircher, BSc

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 3. Februar 2022

## Danksagung

Im Laufe dieser Arbeit habe ich viel fachliche und emotionale Unterstützung durch Personen in meinem Umfeld erfahren. Ich möchte allen von ihnen aus meinem tiefsten Herzen danken.

Zunächst möche ich Heimo Hartlieb und Wolfgang Ecker meinen Dank für die Möglichkeit an diesem spannenden Projekt zu arbeiten aussprechen. Insbesondere will ich euch auch für die erfrischenden und ergiebigen Diskussionen, sowie die ständige unbezahlbare Unterstützung danken. Ein weiteres großes Dankeschön gebührt Heimo auch dafür, dass er diese Arbeit über seine Feiertage korrekturgelesen hat.

Ich möchte mich auch bei meinem Betreuer Ao. Univ. Prof. Dipl.-Ing. Dr. techn. Andreas Steininger für seine Unterstützung, Flexibilität und Zuvorkommenheit im Fachlichen und Organisatorischen erkenntlich zeigen. Auch er war immer schnell zur Stelle und sehr engagiert mich in meinen Zeitplänen zu unterstützen.

Weiters möchte ich unserem Manager Gerald Derflinger dafür danken, dass er mir während einer globalen Pandemie immer den Rücken freigehalten hat.

Ich möchte auch allen Kollegen bei Infineon für ihre Hilfe, aber auch für den Teamgeist und die generell gute Zeit danken. Es hat mir viel Spaß gemacht mit euch allen zu arbeiten. Ein großes Dankeschön gebührt Keerthikumara Devarajegowda und Paritosh Sinha für ihre rasche Unterstützung bei allen Fragen und Problemen bezüglich Metagen und MetaRTL. Ich schulde auch Michael Werner meinen Dank und zumindest einen Abend voller Bier für seine Unterstützung bei allen MetaFirm-betreffenden Themen und für die schnelle Implementierung von Erweiterungen welche für diese Arbeit nötig waren. Ich möchte auch Zhao Han für unsere Diskussionen und seine Code Reviews danken. Spezieller Dank gebührt Timotei Muresan für die Verifikation meiner generierten Designs. Desweiteren möchte ich Thomas Grubelnik dafür danken, dass er bei der SoC Integration geholfen hat und mich während stundenlangen Debug-Sessions bei Laune gehalten hat. Ich danke auch Evren Kenanoglu für seine Hilfe beim Aufsetzen der Software Toolchain und der Modifikation der genutzten Linker Skripte.

Zu guter Letzt möchte ich meiner Freundin, meiner Familie und meinen Freunden meinen tiefsten Dank für ihre überwältigende Unterstützung und ständige Ermutigung während meines Studiums und dieser Arbeit aussprechen. Ohne euch hätte ich das alles nicht geschafft.

## Acknowledgements

Over the course of working on this thesis, a lot of people have provided me with technical and emotional support. I want to thank all of them from the bottom of my heart.

In particular, I would like to express my gratitude to Heimo Hartlieb and Wolfgang Ecker for the opportunity to work on this exciting project. I also want to thank both of you for the refreshing and fruitful discussions that we had in the process and the constant and invaluable support that I have received from you. Moreover, a very big thanks to Heimo for proofreading this thesis during his holidays.

I am also very grateful to my supervisor Ao. Univ. Prof. Dipl.-Ing. Dr. techn. Andreas Steininger for his support, flexibility and forthcomingness in technical and organizational matters. He was always promptly available and committed to supporting me in my schedule.

I must also thank our manager Gerald Derflinger for always having my back while working through a global pandemic.

Moreover, I want to thank all my colleagues at Infineon not only for the help they have offered but also for their good team spirit and in general the good times that we had. I had a blast working with you all. Big thanks go to Keerthikumara Devarajegowda and Paritosh Sinha for their prompt support with any Metagen- and MetaRTL-related questions and issues. I also owe gratitude and at least an evening's worth of beer to Michael Werner for his support with any MetaFirm-related topics and for providing the library extensions that were required for this thesis. I also want to thank Zhao Han for our discussion and his feedback during code reviews. Special thanks go to Timotei Muresan for spending the time to verify my generated designs. I also want to thank Thomas Grubelnik for his help with the SoC integration and for humoring me during seemingly endless hours of debugging. Furthermore, I want to thank Evren Kenanoglu for his help with the software toolchain setup and linker script modifications.

Last but not least, I want to express my deepest gratitude to my girlfriend, my family and my friends for their overwhelming support and words of encouragement throughout my studies and this thesis. I could not have done it without you.

## Kurzfassung

Die ständige Zunahme an integrierten Komponenten in modernen SoCs sorgt für einen enormen Anstieg der Komplexität. Dies wirkt sich nicht nur auf die digitalen Design- und Verifikationsprozesse aus, sondern auch auf die End of Line Tests der fabrizierten ICs deren Anteil an den Produktionskosten immer signifikanter wird. Gängige Design For Test Praktiken können unter Zuhilfenahme der CPU genutzt werden um den Parallelismus von End of Line Tests zu erhöhen und die Testzeit zu verkürzen. Diese Methode ermöglicht auch die Wiederverwendung von Scanketten wodurch mit minimalem Mehraufwand Selbsttests sowie das Trimmen und die Konfiguration von analogen Bauteilen zur Laufzeit genutzt werden kann. Die vorliegende Arbeit präsentiert ein Framework aus Hardwareund Softwaregeneratoren welches in der Lage ist eine modulare on-chip Testinfrastruktur auf der Basis der etablierten JTAG und IJTAG Standards zu generieren. Aus einer Spezifikation kann mittels der Generatoren ein systemspezifisches Reconfigurable Scan Network aus unabhängigen und wiederverwendebaren Subnetzwerkdefinitionen zusammengestellt werden. Durch ein eigens entwickeltes Modul welches Datenverkehr zwischen der CPU und dem Reconfigurable Scan Network ermöglicht können softwarebasierte Selbsttest-, Selbsttrim- und Konfigurationsabläufe zur Verfügung gestellt werden. Die Generierung von spezifischen Treiber aus high-level Definitionen von Scanoperationen nahe der standardisierten Procedural Description Language unterstützt die Entwicklung der entsprechenden Software. Dadurch fördert der beschriebene Ablauf nicht nur die Wiederverwendung von Intellectual Properties und Embedded Instruments sondern auch die Wiederverwendung der relevanten Software Routinen. Schlussendlich wird die Integration eines entsprechenden Designs in einen RISC-V-basierten SoC präsentiert. Die Entwicklung einer Komparator-basierten Selbsttrim-Applikation zeigt die Flexibilität, Modularität und Produktivitätssteigerung des vorgestellten Frameworks auf.

## Abstract

The ever-increasing number of embedded elements in modern SoCs is a major driver for growing design complexity. This affects not only the digital design and verification processes but also End of Line testing of manufactured ICs whose fraction of overall production cost is becoming more significant. Making Design For Test features accessible to the CPU can augment End of Line testing by increasing parallelism and reducing test time. Moreover, reusing scan chains in this way can provide valuable Built-In Self-Test, analog trimming and analog configuration mechanisms in the field with little to no additional hardware overhead. This thesis presents a hardware and firmware generator framework that is capable of generating a modular on-chip testing infrastructure based on the established JTAG and IJTAG standards. By providing a single source specification to the generators, a system-specific Reconfigurable Scan Network implementation is compiled from independent and reusable subnetwork definitions. A specially designed peripheral that manages traffic between the CPU and Reconfigurable Scan Network enables the provision of software-based self-testing, self-trimming and analog configuration. The generation of custom drivers from high-level scan operation descriptions close to the standardized Procedural Description Language further supports the development of the respective software. In doing so, the proposed flow does not only foster reuse of Intellectual Properties and Embedded Instruments but also reuse of test- and trim-related software routines. In the end, integration of a particular design in a RISC-V-based SoC is presented. The development of a comparator-based self-trim application is demonstrated to underline the flexibility, modularity and productivity that the proposed flow offers.

# Contents

xv

| Κι            | urzfassung                                                                                                                   | xi                         |

|---------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Αl            | bstract                                                                                                                      | xiii                       |

| Co            | ontents                                                                                                                      | $\mathbf{x}\mathbf{v}$     |

| 1             | Introduction  1.1 Motivation                                                                                                 | 1                          |

|               | 1.2 Objectives                                                                                                               | 2                          |

| 2             | Background 2.1 Scan Chain Architecture                                                                                       | 3<br>9<br>17               |

| 3             | Related Work  3.1 Self-Testing via Scan Chains                                                                               | 19<br>19<br>21             |

| 4             | Design Implementation4.1 Design Requirements and Structure4.2 Design Metamodel4.3 Hardware Generation4.4 Firmware Generation | 23<br>23<br>25<br>28<br>36 |

| 5             | Methodology Showcase                                                                                                         | 43                         |

| 6             | Discussion and Outlook                                                                                                       | 49                         |

| 7             | Summary                                                                                                                      | 55                         |

| $\mathbf{Li}$ | st of Figures                                                                                                                | 57                         |

| Li            | st of Tables                                                                                                                 | 59                         |

| Li           | List of Algorithms |                            |    |  |  |  |  |  |  |  |

|--------------|--------------------|----------------------------|----|--|--|--|--|--|--|--|

| A            | crony              | rms                        | 63 |  |  |  |  |  |  |  |

| Bi           | bliog              | raphy                      | 67 |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Source Code        |                            |    |  |  |  |  |  |  |  |

|              | A.1                | Hardware Abstraction Layer | 71 |  |  |  |  |  |  |  |

|              | A.2                | Basic Driver               | 75 |  |  |  |  |  |  |  |

|              | A.3                | Custom Driver              | 78 |  |  |  |  |  |  |  |

|              | A.4                | Trim Routine               | 80 |  |  |  |  |  |  |  |

CHAPTER \_

## Introduction

### 1.1 Motivation

Over the past decades, the complexity of Integrated Circuits (ICs) has been increasing rapidly while manufacturing costs and feature sizes have diminished [1]. Besides the enormous design and verification effort required to keep up with these fast-paced developments, the increased risk of manufacturing-induced defects necessitates thorough End of Line (EOL) testing [1, 2]. The use of Design For Test (DFT) techniques like scan chains and Built-In Self-Test (BIST) is inevitable to uphold or even improve upon product standards [3, 1, 4, 5].

With the complexity and number of embedded elements in modern Systems On Chips (SoCs) increasing, so do the number of Embedded Instruments (EIs) required to achieve acceptable test coverage. This further adds to the test time and test costs causing their share in overall production expenses to become more significant [2, 6]. Moreover, the time required to develop the tests should not be underestimated [1]. Integration of BIST engines can help to alleviate the demands and burden on Automated Test Equipment (ATE) during EOL testing while also offering valuable in-field tests but they come at the expense of increased area overhead [1, 6, 5]. In addition, to test requirements for digital and analog Intellectual Properties (IPs), analog blocks also require trimming which takes up a large portion of test time [7, 8] and cannot be parallelized on ATE easily [8]. Moreover, the required runtime configuration can be problematic because analog IPs usually do not feature bus interfaces.

The classical scan-inspired approach as described in the IEEE 1149.1 [9], while well supported by ATE and Electronic Design Automation (EDA) tools, is becoming unwieldy given the high number of EIs which complicates the test-related aspects of IP-reuse. This is even more relevant when targeting an entire product family range with a variety of feature sets among the individual SoCs. Moreover, the EOL test features add to

the overall chip area but usually do not serve any purpose for the rest of the product's lifetime.

Therefore, the (re-)use of scan chains with minimal per-IP overhead is of interest for the purpose of self-trimming, in-field testing and in-field configuration. The fact that an SoC already comes with a Central Processing Unit (CPU) suggests that enabling on-chip access to the scan chains can be of enormous help in reaching these goals in a flexible and future-proof way.

### 1.2 Objectives

The aim of this thesis is to develop an on-chip testing infrastructure to overcome the mentioned limitations. Specifically, it is essential to support conventional and transparent EOL testing as defined in IEEE 1149.1 combined with the additional benefits of smart software-driven self-testing, self-trimming and runtime configuration based on scan chain reuse. For this purpose, a strategy that allows interaction with scan chains via the CPU needs to be devised.

In order to ease IP and test-reuse and ensure future extensibility, recent developments with respect to flexible scan chain management [10] have to be taken into account. Moreover, the proposed architecture should be modular and flexible in its components to cover different on-chip testing requirements on a per-product basis.

Introducing an interface between the CPU and a set of scan chains also implies bridging the hardware/software boundary. Since dealing with scan chains directly is an intricate matter, having to work with a simple Hardware Abstraction Layer (HAL) is too tedious for software engineers. Therefore, productive development of the required test software must be ensured by provisioning reasonable high-level tool support.

As a demonstration of the achieved results, a practical example that illustrates the opportunities achieved by the integration of the described approach in an SoC shall be presented. Specifically, the aim is to showcase the reuse and flexibility made possible by design decisions at a hardware level as well as how a high level of abstraction in the firmware toolchain fosters software development.

# Background

Over the course of this thesis, it is essential to have a firm understanding of scan architectures. Another key requirement is a good understanding of metamodeling and how automated hardware generation is practiced at Infineon. Lastly, it is beneficial to understand the basic architecture of the targeted SoCs and how certain parts of the toolchain are involved during development. This chapter gives an overview of the necessary theoretical prerequisites for this thesis.

### 2.1 Scan Chain Architecture

Scan chains are without a doubt the most used concept when it comes to DFT. The key idea is to arrange Flip Flops (FFs) in a chain during testing so they act as a shift register. This can provide any level of observability and controllability of integrated circuits with a minimal interface. The goal of this section is to introduce standardized and time-proven (boundary) scan architecture concepts as well as recent developments for dealing with the ever-increasing complexity of SoCs.

#### 2.1.1 **Boundary Scan Architecture**

About three decades ago, the Joint Test Action Group (JTAG) finalized the original IEEE 1149.1 standard [9] focusing on the description of a Test Access Port (TAP) and boundary scan architecture. The primary purpose was to provide a standardized approach for the testing of IC to Printed Circuit Board (PCB) interconnect as well as the IC itself. Oftentimes, the 1149.1 standard is referred to as the JTAG standard.

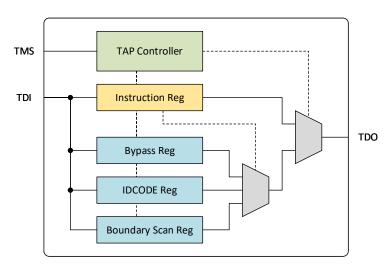

Figure 2.1 gives a basic overview of the scan architecture. The centerpiece is the so-called TAP controller which is driven via a TAP interface consisting of four digital signals:

Figure 2.1: Simple overview of the boundary scan architecture as outlined in the standard. Solid lines are data signals and dashed lines are control signals.

- The Test Clock (TCK) which is responsible for clocking of the TAP controller and the scan chains.

- The Test Mode Select (TMS) is used to change the state of the TAP controller at the rising edge of TCK.

- The Test Data Input (TDI) is the serial input clocked into the system at the rising edge of TCK.

- The Test Data Output (TDO) is the serial output clocked out of the system at the falling edge of TCK.

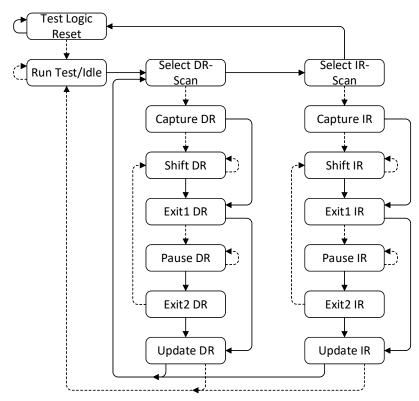

Figure 2.2 shows how the TMS signal controls the scan architecture. Essentially, when the TAP controller is not idle, it is either modifying the Instruction Register (IR) or a Test Data Register (TDR) (e.g. Bypass, IDCODE, Boundary Scan Register, ...).

The content of the IR determines which TDR is currently selected and would be operated on during a data scan operation. Moreover, multiple values of the IR may select the same TDR but cause a difference in the mode of operation. A single access to a TDR (called scan operation) consists of a *capture* operation (data is loaded into the register), a series of shift operations through the register and an update of the TDR (data shifted into the register takes effect).

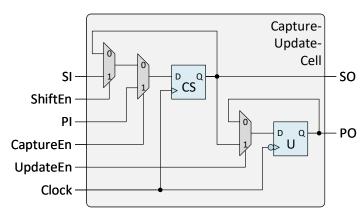

All TDRs are chains of so-called TDR cells. Figure 2.3 shows a schematic of a so-called capture-update cell which consists of a capture-shift register and an update-register. The former has two roles in this circuit. Firstly, it acts as a stage in a shift register chain during shift operations in that it fetches data from the serial input (SI) and provides its content to the serial output (SO). Moreover, during capture operations, it captures data

Figure 2.2: State diagram of the TAP controller as described in the standard. Solid lines are transitions taken when TMS=1 while dashed lines are transitions taken when TMS=0.

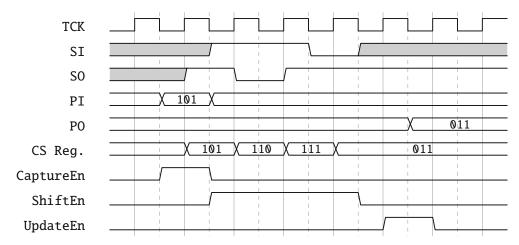

from the parallel input (i.e. observes a circuit or PCB signal via PI). In contrast, the update-register fetches the content of the capture-shift register during update operations and provides its state onto a parallel output (i.e. controls a circuit or PCB signal via PO). The control signals Capture En, Shift En and Update En are generated by the TAP controller in the respective states. It is worth noting that capture and shift operations take place on the rising edge of TCK while update operations take place on the falling edge.

Figure 2.4 illustrates a simple scan operation on a 3-bit TDR. As specified in the standard, the Least Significant Bit (LSB) is always shifted into the TDR first. This means that the cell that represents the Most Signigicant Bit (MSB) is closest to TDI and farthest from TDO.

In general, depending on the specific needs, TDR cells can have varying functionality. Leaving out the update register results in a capture cell while leaving out the capture logic (Capture En-driven multiplexer) results in an update cell. Waiving both results in a shift-only cell. Missing capture functionality means that observing signals via the cell is not possible anymore. Notably, missing update functionality does not imply a

Figure 2.3: Schematic of a capture-update cell as described by the standard.

Figure 2.4: Timing diagram demonstrating a scan operation on a TDR via the signals generated by the TAP controller. In this case, 101 is captured from the parallel input and **011** is shifted in and updated to the parallel output.

loss of controllability. However, without the update register, there is no way of ensuring consistent updates and *shift* operations cause rapid signal changes at cell outputs.

The idea of boundary scan is to provide a TDR of so-called boundary scan cells around the input and output pins of an IC. This TDR which is often referred to as Boundary Scan Chain (BSC) allows the application of stimuli and observation of signals at the IC's border. A boundary scan cell is essentially a TDR cell whose parallel output is not connected directly to the circuit or PCB but instead multiplexed with a default signal, usually its parallel input, based on a mode select signal. This makes it possible to control the operation mode (i.e. test or normal operation) independently of scan operations on the BSC. Controlling the output cells and observing the input cells enables testing of interconnect. In contrast, controlling input cells and observing output cells allows testing of the IC's functionality.

The IEEE 1149.1 standard requires implementation of at least the bypass register, a simple 1-stage shift register for when no operation is required, and the Boundary Scan Register for boundary scans. There are further standardized TDRs like IDCODE which provides a device identification. Further, it is possible to implement custom TDRs as needed (e.g. for operation of an On Chip Debug System (OCDS)).

For operation of the TDRs, the standard enforces provision of four instructions:

- A BYPASS instruction to select the bypass register.

- A PRELOAD instruction which can be used to load data into the BSC's update stage without asserting the test mode.

- A SAMPLE instruction which can be used to fetch data into the BSC's capture stage without asserting the test mode.

- An EXTEST instruction which asserts the test mode and also allows scan operations to be performed on the BSC. This is inteded for testing PCB connectivity.

It is permitted to combine instructions that do not conflict with one another meaning that implementation of a SAMPLE\_PRELOAD instruction is also allowed. Moreover, there are several other standardized instructions like INTEST which is similar to EXTEST but targets testing of the IC itself. For that purpose, it also has to support single stepping in the TAP controller's *idle* state.

The JTAG architecture has been used for decades and is supported by practically every relevant EDA tool. Nevertheless, it does come with some problems. Making a design scannable by replacing FFs with Scannable Flip Flops (SFFs) is possible by implementing a custom TDR and making it selectable with a custom instruction. However, in modern SoCs where multiple embedded elements require a TDR each, one has to decide whether they should be arranged in series or in parallel. In the first case, accessing a part of the TDR sequence means that data has to traverse the entire scan chain which causes a noticeable increase in test time. Moreover, special care has to be taken to avoid corrupting the state of other parts of the scan chain. Putting the TDRs in parallel does solve both of the problems but also does not allow any patterns where the TDRs of multiple EIs are accessed at the same time which is another cause of increased test time. Moreover, it would require introducing a lot of instructions which ultimately causes strong coupling between the TAP controller and the feature set of a system. In a way, the described scan chain architecture is too rigid for the purposes of modern SoCs. Furthermore, retargeting of tests due to product variety and IP reuse is very tedious if not impossible. While the newest revision of the standard introduced some improvements regarding these aspects, an entirely new standard has evolved with the goal of extending IEEE 1149.1 to fix those exact problems.

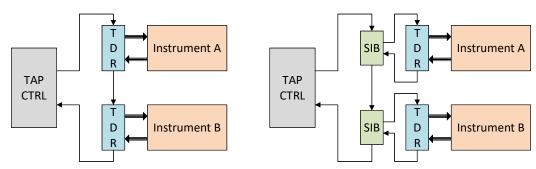

- (a) Scan chain of two TDRs in series.

- (b) Scan chain of two TDRs guarded by SIBs.

Figure 2.5: Example of how SIBs are used in the IJTAG network to make it configurable.

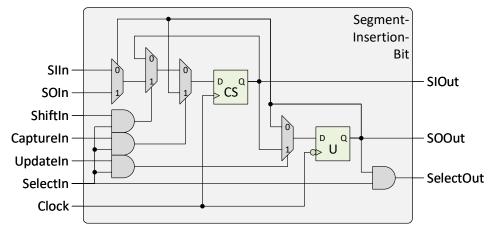

Figure 2.6: Schematic of a possible implementation of an SIB as specified in the standard.

#### 2.1.2A flexible and reconfigurable Scan Network

The Integrated Joint Test Action Group (IJTAG) has recognized that the TAP is used for many more purposes than just boundary scan and identified the need for an Reconfigurable Scan Network (RSN) based on scan chains for increased flexibility when accessing EIs as well as retargeting capabilities. This caused the emergence of the IEEE 1687 standard [10].

The basic idea is to allow flexible inclusion and exclusion of parts of a scan chain. An elementary building block to achieve this is the Segment Insertion Bit (SIB). It can be thought of as a single bit update cell that acts as a kind of TDR-guard. When it is active, the TDR is included in the scan chain right before the SIB's internal shift stage. Deasserting the SIB causes the TDR to be excluded from the scan chain. In this case, it essentially acts as a bypass register. Figure 2.5 outlines how SIBs can be used to guard subnetworks. Of course, a subnetwork guarded by an SIB may contain SIBs of its own which enables the construction of multi-level hierarchies.

A possible implementation of the SIB is visualized in Figure 2.6. It can be seen as a modified capture-update cell that multiplexes the input of its shift stage between the

serial input of its predecessor (SIIn) and the serial output of the TDR it is guarding (SOIn). Moreover, it generates a SelectOut signal for the subnetwork it is guarding which can be used to mask the control signals of the subnetwork to freeze it when the SIB is de-asserted.

The SIB is an example of an in-line scan chain multiplexer meaning that the control signal is generated from the same TDR as the SIB is configuring. An alternative would be a remotely controlled multiplexer whose control signal is being generated from a different register (e.g. another TDR or a decoded instruction). The main difference between the two approaches is that the SIB allows updating the configuration for the next scan operation during the current scan operation while remotely controlled scan multiplexers may require changing the IR.

Besides providing methods to allow more efficient and flexible operation on scan chains, the standard also provides definitions for two description languages. The first one is the Instrument Connectivity Language (ICL) which makes it possible to define the structure of the RSN for a given product. This allows efficient retargeting of operations on TDRs written in the second language called Procedural Description Language (PDL). The advantage is that sequences of operations can be developed at the level of Els. Given the ICL definition of a system (e.g. an SoC) a toolchain can then retarget a set of PDL definitions to the system level which significantly improves test development time. Moreover, the development of the operation procedures does not depend in any way on the final feature set of the system itself and can thus take place rather early or also entirely independent of the final system (e.g. third-party IP).

### 2.2Automated Code Generation

The concept of automated code generation is a major driver for productivity and a valuable tool for the purpose of closing the design productivity gap [11]. When practiced correctly, it can also offer the same conveniences as IP reuse with the addition of significantly increased flexibility. For this reason, many processes at Infineon build upon a metamodeling-based code generation framework. In conjunction with the concepts of Model Driven Architecture (MDA), this has also opened up opportunities for user-friendly Register Transfer Level (RTL) generation. This section provides an introduction to the concepts of this toolchain which is used throughout this thesis.

### 2.2.1 Metamodeling

The MDA methodology makes use of models to capture properties of systems at different levels of abstraction. It is therefore clear that a model has to consist of a set of objects. However, a model is essentially worthless without knowledge of its respective domain. Moreover, depending on the domain, a model may have to fulfill certain constraints.

This is where the concept of metamodels comes into play. A metamodel is essentially a structural and relational description of a class of models. One could say that a metamodel

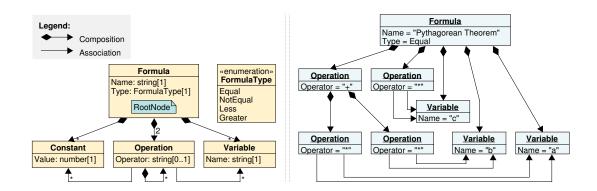

Figure 2.7: Example of a Formula metamodel (left) and a specific Formula model (right).

is itself a model of an underlying model; in a sense, it is "beyond" this described model, hence the name metamodel. A metamodel defines a set of models (i.e. a design space) by establishing certain constraints. The models in this set are said to be instances of the metamodel or conform to the metamodel. A model, in turn, characterizes a system at some level of abstraction.

Figure 2.7 illustrates a metamodel of simple mathematical formulas described in Unified Modeling Language (UML) as well as a concrete instance of the metamodel. The metamodel contains a root node which describes the attributes of a Formula, a Name and a Type which denotes whether the Formula is an equation or an inequality of some sort. Moreover, a Formula has multiple constituents. On the one hand, it can have an arbitrary number of Constants with assigned Values and Variables with assigned Name. In addition, it is also composed of exactly two *Operations* which basically describe the left- and right-hand sides of the formula. Each Operation can<sup>1</sup> have an Operator and an arbitrary number of associated Constants and Variables. Also an Operation can have an arbitrary number of "child"-Operations. As an example, a Formula instance representing the Pythagorean theorem  $a^2 + b^2 = c^2$  is visualized.

It is apparent that the exemplary model fulfills all restrictions of the metamodel in that it has a valid structure and valid attributes. Moreover, it is certainly a valid model of the Pythagorean theorem. However, it is also noteworthy that the metamodel itself allows the construction of models that no mathematician would ever accept as valid formulas. For example, it is possible to describe an operation without any operands, a unary operation with more than one operand or a non-unary operation with just a single operand. In a practical scenario, this would have to be forbidden by either introducing proper constraints in the metamodel (e.g. via Object Constraint language (OCL) for UML 2 and above) or implementing proper constraint checking in tools that take instances of the metamodel as input.

<sup>&</sup>lt;sup>1</sup>It does not have to have an Operator since it would be acceptable for it to just be a Variable or a Constant.

Figure 2.8: Visualization of the Metagen framework.

The goal of metamodeling is to identify and capture application-specific requirements in an abstract metamodel. This results in a formalized description of the models of interest which can be used to guide automation.

### 2.2.2Metamodel-based Code Generation

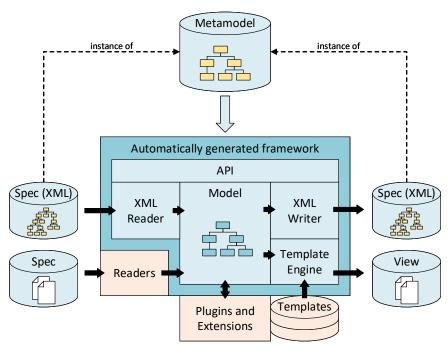

Metagen is a metamodel-based code generation framework that was developed at Infineon. Given a metamodel described in UML by the user, a Python-based framework is generated (see Figure 2.8). This framework consists of the following parts:

- An Application Programming Interface (API) for construction of and interaction with models as defined by the metamodel provided by the user including respective documentation.

- A set of readers and writers for de-/serialization of models from/to predefined formats (e.g. XML).

- A Graphical User Interface (GUI) for the purpose of creation, inspection and modification of model instances.

When a model is loaded into the framework through a reader, a Python representation of the model is constructed. In addition to the automatically generated readers, the user also has the option to provide their own readers. A custom reader implementation

may be useful to map data in an arbitrary input format to the Python-based model representation using the generated API. Essentially, the input data is interpreted as a specification for the resulting model.

After a model has been loaded into the framework, extensions provided by the user can be employed for model modifications. This may not always be useful or required but drastically increases the flexibility of the entire approach.

Finally, given a model representation, a default or custom writer can be invoked. The most relevant use case is the employment of custom write routines by providing so-called templates to a powerful template engine called Mako. Templates are basically a skeleton of the output format including placeholders and Python code. By combining a template with a model, a model-specific view is generated by the template engine. Multiple templates can be provided to generate multiple views from a single model (e.g. code, documentation, ...).

Simply put, Metagen is used to drastically speed up the development of code generators accepting models conforming to a metamodel. An interesting aspect of this flow is that, at a higher level, Metagen itself is a code generator accepting metamodels conforming to a meta-metamodel. This is in line with the concept of Meta-Object Facility (MOF) as defined by Object Management Group (OMG).

Metagen is used very extensively and has a high potential for reducing Non-Recurring Engineering (NRE) costs via automation and reuse. Specifically, productivity gains of up to 95% for particular tasks and effort reductions of up to 70% have been observed [12, 13].

While the advantages of the flow are evident as soon as a generator is usable, there is still one problem to be addressed during the development. When faced with the task of generating a specific type of view from a specific type of specification, it is often the case that there is a significant difference between source and target structure. Essentially, the metamodel has to lie somewhere in between the interval of input and output structure. If the metamodel is close to the specification, it is trivial to develop a custom reader, however, the development of the templates becomes a very complex task. This is especially apparent when considering the generation of Hardware Description Language (HDL) code from a specification of a digital filter, let alone more complex and irregular structures. On the other hand, when the metamodel is close to the view, developing the respective template is simple but transforming a specification into the respective model becomes increasingly tedious. Moreover, this choice would defeat the purpose of being able to transform a specification into many different views. Therefore, a flow for e.g. HDL generation needs to allow the metamodel to be close to the specification while also providing a sufficiently high-level API.

#### 2.2.3 Model Driven Architecture

The concept of MDA has been adopted by the OMG for the purposes of reducing complexity and cost and increasing interoperability and reuse about two decades ago [15,

Figure 2.9: Y-chart of the MDA approach [14].

16, 17]. In principle, MDA makes use of models as formal descriptions of systems at different levels of abstraction. These levels of abstraction are often called viewpoints. The key idea is that well-defined model transformations between adjacent viewpoints (i.e. relatively close levels of abstraction) are more straightforward to develop, reusable and allow for clearer semantics at higher levels of abstraction.

MDA defines three models whose relation can be seen in Figure 2.9:

- The Computation Independent Model (CIM) captures the requirements of a system without going into any detail regarding implementation. It is very close to the specification and serves as a high-level representation of the system. Essentially, it delivers an answer to the question: "What is our goal?".

- The Platform Independent Model (PIM) is more detailed in that it describes the required behavior of the system. Yet, it is still somewhat coarse in its level of abstraction in that it is not bound to a specific platform (i.e. a certain framework or environment). It basically answers the question: "With what strategy can we achieve our goal?".

- The Platform Specific Model (PSM) is a more refined description of the system's behavior and takes highly platform-specific details into account. It can be seen as an answer regarding the question: "How can we implement our strategy under given circumstances?"

As the Y-chart depicts, a more abstract model of a system is transformed in a step-wise fashion to a less abstract model of the system. From a higher point of view, a specification is translated to a respective view via a series of model-to-model transformations. This multi-level process allows bridging the gap of enormous differences in abstraction while sticking to a model (CIM) that is close to the specification.

In the step from PIM to PSM, a Platform Model (PM) is required which describes the capabilities and restrictions of the target platform. Depending on the use case, the platform may be for example a programming language (code generator) or an instruction set (compiler).

It is noteworthy that multiple classes of CIMs (i.e. conforming to different metamodels) can be mapped to the same class of PIMs, provided that the PIM's metamodel is powerful enough. In other words, the platform-independent metamodel defines what kinds of computation-independent metamodels are supported.

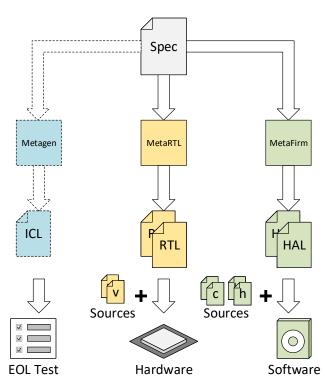

### RTL Code Generation 2.2.4

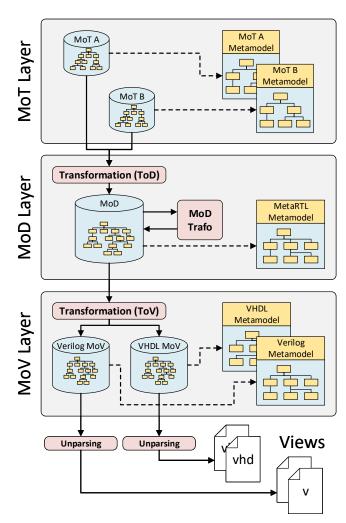

MetaRTL is an adaptation of the fundamental principles of MDA to the Metagen framework with the goal of allowing efficient development of RTL generators [18, 19, 20, 21] This is achieved by introducing three types of models analogous to the CIM, PIM and PSM:

- The Model-of-Things (MoT) defines components (things) of the design, their attributes and how they are related. The defining metamodel is close to the specification (and hence use-case-specific) so mapping informal requirements to an MoT is very straightforward. A simple example of an MoT could be the definition of a digital Finite Impulse Response (FIR) filter in terms of its coefficients.

- The Model-of-Design (MoD) defines the design in terms of an RTL schematic. Its metamodel offers a rich set of digital primitives to support the construction of a wide range of digital circuits. In the exemplary case of a digital FIR filter, the MoD would be a chain of registers whose outputs are connected to multipliers (according to the coefficients) and then summed up by an adder.

- The Model-of-View (MoV) is close to the desired view which is HDL code. There is a separate metamodel for each target backend (e.g. VHDL, Verilog, ...).

Figure 2.10 visualizes how MoTs are passed through several model transformations to generate a low-level MoV which can then be unparsed into the desired HDL code.

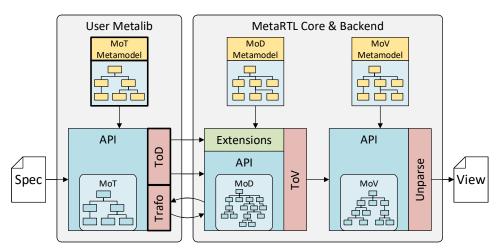

This structure has significant advantages over a Metagen-only approach when it comes to implementing a generator for a specific class of circuits. Figure 2.11 highlights the responsibilities of the developer. First, an appropriate metamodel is defined and the respective framework is generated using Metagen. Afterwards, the transformation between a specific MoT and its respective MoD has to be developed. For this purpose, a template called Template-of-Design (ToD) is written in Python. To accomplish this, the developer

Figure 2.10: An MDA-oriented approach to RTL generation called MetaRTL.

can use the MoD-specific API (generated by Metagen) as well as domain-specific high-level extensions to ease the process of constructing the digital design.

The rest is handled by the MetaRTL core and the HDL-specific backends. Notably, the developer does not require knowledge of the MoD to MoV transformation via the Template-of-View (ToV) much like implementing compiler optimizations at the level of abstract syntax trees does not require knowledge of the microarchitecture backends. Overall, the reduction in code required by the MetaRTL flow compared to a Metagen-only flow is a factor of 5x to 10x[21].

The power, flexibility and reusability of a generator grow with the freedom of the defining metamodel. However, there are certain concepts in digital design that are orthogonal to the specification of a circuit and may be applied frequently. For example, regardless of the functionality of a circuit, there is always the option of replacing registers with

Figure 2.11: Display of the boundary between user-defined code and the MetaRTL environment.

hardened registers for functional safety. Of course, this only makes sense if the use case really requires it. Since implementing this feature in ToDs would quickly lead to code duplication and incidental complexity, this can be solved with MoD transformations. Essentially, the extended API provides features to apply transformations to an already existing MoD regardless of how it was originally constructed. Therefore, given an arbitrary MoD and a set of transformations, an altered variant of the MoD can be produced in a transparent and flexible fashion.

### 2.2.5Firmware Generation

With the help of MetaRTL, a rich variety of similar hardware designs can be generated. However, some hardware components are at the hardware/software boundary and therefore require an appropriate HAL and driver. It follows that variations in the generated design are likely to cause variations in the required software stack.

For this reason, an MDA-inspired flow for firmware generation called MetaFirm is provided to complement MetaRTL. MetaFirm is relatively similar to MetaRTL in that it is also a MDA-based three-layer flow. The idea is to use the same MoT (i.e. a single source with abstract concepts concerning hardware and software) as a basis for both, MetaRTL and MetaFirm.

An essential part connecting MetaRTL and MetaFirm is the Control Status Configuration (CSC) metamodel whose models serve as hardware/software interfaces. Every MoT at the hardware/software boundary also contains a CSC MoT. On the hardware side, the CSC MoT is transformed into a register interface that can be connected to a data bus. The software side is the HAL of said register interface in the C programming language.

Since the same MoT is used by MetaFirm and MetaRTL, the first layer in the MDAinspired structure is essentially identical. The second model in MetaFirm is called

Figure 2.12: Overview of the RiVal 2 test chip.

Model-of-Firmware (MoF) and it is created by transforming the MoT via a Templateof-Firmware (ToF). It captures programming concepts like functions, loops, conditions and variables and can make use of the HAL. The model at the third layer is again called MoV but is concerned with representing the firmware in the C programming language and should not be confused with its MetaRTL counterpart. Unparsing yields a view in the form of C source and header files.

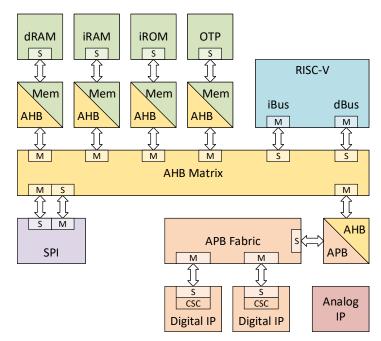

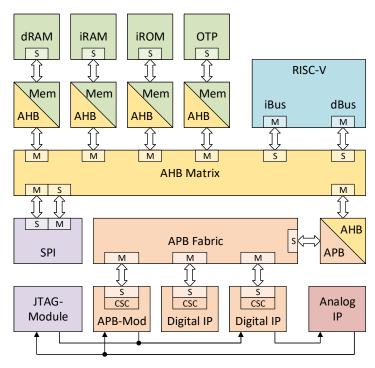

### 2.3 SoC Architecture

Infine is developing an SoC called RiVal 2 on the basis of a RISC-V [22] implementation based on MetaRTL. Besides the CPU, several other parts of the architecture are generated via MetaRTL like the multi-layer Advanced High-Performance Bus (AHB) matrix. A Serial Peripheral Interface (SPI) module makes it possible to program the SoC. Figure 2.12 gives a high-level overview of the architecture.

As already outlined in Section 2.2.5, peripherals at the hardware/software boundary require a register interface. This can be generated via the MetaRTL-based CSC metalib. It offers a simple data bus interface that is very easy to bridge to other peripheral interfaces. In the case of the RiVal 2, an Advanced Peripheral Bus (APB) bridge allows the peripheral to be connected to the APB fabric of the SoC. This APB fabric then connects to the bus matrix via an AHB-to-APB bridge. The data widths of the AHB and APB buses are 32 bit and 16 bit respectively.

Any functional access to the digital peripherals can be handled via the bus. This is in

contrast to any analog peripherals which do not have a bus interface. Of course, both digital and analog IPs still need to be scannable for EOL testing. Additionally, analog IPs must be trimmed at least once after the manufacturing process. Moreover, configurability of the analog peripherals based on the found trim values is necessary for operation in the field.

CHAPTER 3

## Related Work

The subject of this thesis is related to the possibilities that scan architectures open up during EOL testing as well as in the field with respect to BIST and analog IP trimming and configuration. Another corner stone is the addressing of design productivity by means of harmonizing these aspects with the concept of automated firmware generation. This chapter provides an overview of state-of-the-art proposals to tackle self-testing, trimming and configuration via scan chains and RSNs as well as the possibilities that EDA tools already offer.

## 3.1 Self-Testing via Scan Chains

Using (and reusing) scan chains for BISTs is attractive because the hardware interface is very simplistic and lightweight and the introduction of scan chains may be a requirement for EOL testing anyways. Therefore, there are multiple proposals targeting the opportunities especially in combination with the recent IJTAG standard. Moreover, processor-driven self-test opens up a lot of flexibility on its own.

In larger systems, one possibility is the employment of a dedicated service processor acting as a JTAG master [23]. This way, BISTs can be performed in the field via the use of software-based test routines. While this opens many possibilities, it is not exactly a resource-saving approach and therefore not feasible for integration on an SoC.

A more lightweight approach is described in [24] where blocks of memory are connected as alternative drivers of the TAP controller. This memory is used to store the signal transitions required for the application of test vectors. The TAP interface is multiplexed to allow switching between off-chip and on-chip operation. In the paper, an IJTAG network is used to allow access to sensors for temperature monitoring but the system can be used for virtually any monitoring or test-related task. It is, however, worth noting

that the design is relatively static with respect to test data and test flow since they are essentially programmed into the memory.

An example of an EDA tool that offers the compilation of IJTAG networks for the purpose of testing is Tessent IJTAG [25]. It supports inclusion of Tessent MemoryBIST [26] and LogicBIST [27] components as well as any other IJTAG-compatible IPs. With the help of Tessent MissionMode [28], a so-called In-System Controller can be generated which enables on-chip operation of the RSN. MissionMode offers memory-based and CPU-based implementations. The former option is similar to the approach described in [24] in that test data is stored in memory and access to the TAP controller is multiplexed. Another possibility is to embed a controller that allows the CPU to operate on the RSN by mapping CPU signals to the TAP controller. As of June 2021 [29], another CPU-driven option is available where the detour via the TAP controller is bypassed and an APB-slave device is employed to map memory transactions to scan operations. The software required for the CPU-targeted can be generated from Verilog test benches which only supports limited functionality. Alternatively, it can also be written by hand to enable more dynamic control flow but this quickly becomes a tedious task especially due to arbitrary bit widths and the dynamic nature of RSNs.

On a sidenote, the interest in using alternative interfaces (like Inter-Integrated Circuit (I<sup>2</sup>C), SPI or in the above example APB) to access RSNs has generally been picking up in the last years. Consequently, an entirely new standard, currently known as P1687.1 [30], is expected to evolve from the ongoing research. A strong focus of this work is enabling highly dynamic accesses to the IJTAG network for the use in BISTs where the use of static predefined test vectors is not sufficient.

In [31, 32] an on-chip RSN controller is presented that is supported by a cross compiler flow for efficient development and retargeting of test procedures in high-level programming languages. This allows software developers to use PDL-derived operations on parts of the IJTAG network without having to care about the network's hierarchy, TDR definitions or the required scan operations. The proposal also features a dynamic on-line retargeting engine which provides a great deal of flexibility with respect to control flow in access routines and is especially valuable for access in interrupt service routines.

Making use of the structural information of an RSN and retargetable scan operations during the test software development is certainly an important aspect in terms of usability and productivity. The PDL and ICL are the IEEE 1687 conforming methods of capturing this information. For this purpose, the software layer, especially PDL and ICL parsers, provided in the open IEEE 1687 ecosystem in [33] can be extremely valuable.

IJTAG networks have also been used in [34] for the purpose of efficient fault monitoring. Specifically, a slightly modified SIB is introduced which is capable of opening its respective subnetwork based on some events. This allows the RSN to reconfigure itself and provide scan-chain-based fault monitoring and fault localization.

#### 3.2 Trimming and Configuration via Scan Chains

The usual way of performing digital trimming would be to use ATE for the application of digital trim stimulus and also measurement of the produced analog signal. In [35, 36] the concept of self-trimming is outlined where the ATE is instead concerned with the provision of an analog reference signal. The analog signal produced by the IP is then compared against this reference using an on-chip Analog Digital Converter (ADC) or analog comparator. This (digital) result can then be used to systematically adjust the trim value which can effectively be carried out on-chip by a respective state machine.

As outline in [8], going with an ADC instead of just a comparator does allow to implement a so called full BIST approach instead of just a partial BIST (i.e. no reference from ATE needed) but also increases the required area. Moreover, this freedom comes at the cost of initial ADC trimming requirements. The authors describe a BIST trim controller which is capable of adaptively switching between linear, binary and hybrid search including early response analysis.

In [7] an IJTAG based approach is introduced to integrate the mentioned concepts within a digital core which can be operated transparently via I<sup>2</sup>C. Specifically, for each analog block, a digital island consisting of the required test and trim logic as well as a TDR for the operation thereof is introduced. The islands are then combined into an RSN and augmented with a TAP controller as well as an I<sup>2</sup>C-to-TAP mapper. Their self-trim logic and configuration registers can therefore be accessed via both interfaces.

Interestingly, the authors chose to use the TDRs as an addressing mechanism to operate on the digital islands' register banks instead of using it as a direct access mechanism. While this promotes transparent operation via I<sup>2</sup>C and simplifies the software aspect for programmers by a great deal, it also means that the flexible and in some sense parallel nature of RSNs can not be used to its full potential. This also means that the maximum number of analog blocks and their registers is fixed which again results in a relatively limited and rigid approach.

In general, configuration is not any different from testing in that it greatly benefits from a suitable software abstraction layer and reuse through retargeting. Therefore, software ecosystems and ICL- and PDL-specific parsers like in [33] are also relevant to this task.

# Design Implementation

The aim of this chapter is to give an overview of the hardware and firmware generators implemented in the course of this thesis. To that end, it provides insights into how the requirements outlined in Section 1.2 affect design decisions with respect to the overall design structure. Based on these considerations, the metamodel that is employed in the generation flow is presented. This chapter also goes into detail on how the generated hardware architecture is structured, what possibilities the firmware generation flow offers and how specification parameters and design transformations can be employed to influence code generation. In the end, it should become clear how various aspects of the implemented flow empower reuse, flexibility and extensibility on a hardware level and further support software development for self-test, self-trim and configuration routines.

#### 4.1 Design Requirements and Structure

One of the basic requirements identified in Section 1.2 is compatibility with existing ATE. For this reason, an IEEE 1149.1 conforming JTAG-Module is required including a TAP controller and the TDRs and instructions mandated by the standard. The designspecific aspects like the content of the IDCODE register or instruction indices shall be configurable. Moreover, it is essential to offer straightforward extensions with other standardized instructions as well as custom instructions. Ideally, both can be achieved by simply adapting the specification from which the hardware is generated. This would allow putting together varying feature sets based on the actual product requirements with minimal effort. Of course, some instructions (standardized or custom) may require very specific logic even within the JTAG-Module which means that changes to the code generator may be required from time to time which is fine as long as it enhances the generator in a modular and reusable way. Section 4.3.1 gives an overview of how these requirements can be met with the presented design.

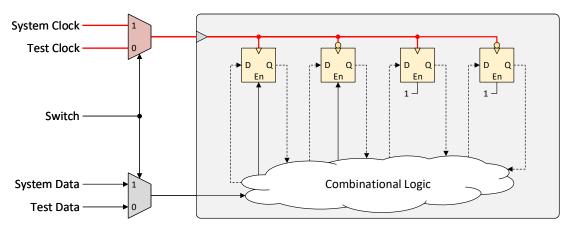

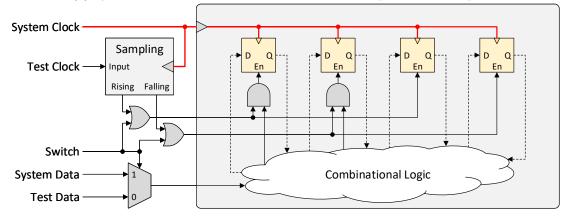

Arguably, the most important aspect of the entire design is the interaction of the CPU with scan chains which enables self-testing, self-trimming and runtime configuration. For this purpose, a module that is capable of performing scan operations on TDRs via the serialization of input data and deserialization of output data is required. As mentioned in Section 2.3, the RiVal 2 SoC offers an AHB matrix with a data width of 32 bits as well as an APB bus with a data width of 16 bits. Since serialization is slower than the memory transactions, the high performance of the AHB interface is certainly not necessary. Therefore it makes sense to opt for an APB-driven CPU-to-TDR interface which will be referred to as APB-Module. This thesis will focus on the specific choice of an APB interface with a data width of 16 bits.

From a functional point of view, the APB-Module must support the selection of instructions and TDR registers similar to the JTAG-Module. Since there may be TDRs that are accessible via the JTAG-Module but not via the APB-Module and concurrent operation on disjunct TDRs may be necessary in the future (e.g. a JTAG-driven OCDS), the APB-Module must have its own IR. Moreover, one must be able to trigger capture and update operations as well as a series of shift operations. Since the APB bus of the RiVal 2 has a data width of 16 bits, in theory, up to 16 shifts can be carried out per transaction. However, TDRs can have arbitrary lengths. Therefore, it must also be possible to shift only a fraction of the 16 data bits. While shift operations supply data to TDRs via the serial input, they also produce data at the serial output. Consequently, the APB-Module must deserialize this data and provide it to the CPU as necessary.

All in all, the register interface of the APB-Module must map sequences of memory transactions to scan operations according to the discussed requirements in a transparent way. Section 4.3.2 goes into detail on how this is achieved in the presented design.

Since strong support for the reuse of IPs and related test routines is another key requirement, it is natural to employ an IJTAG network for the scan chains which shall be accessible via the JTAG-Module and the APB-Module. Most importantly, it shall be possible to define IP-specific and reusable subnetworks on a per-IP basis. Within a subnetwork, the common types of standardized TDR cells and custom configuration cells shall be supported. The generation of an IJTAG-Module which combines these subnetworks into a corresponding RSN shall be driven by the system's specification. For maximum flexibility, reconfigurability of the RSN shall be possible at the network- and subnetwork-level. Therefore, scan multiplexers (e.g. SIBs) must be employed within the subnetworks and the IJTAG-Module. To enable operation via the JTAG-Module or the APB-Module, the IJTAG-Module must define a set of instructions and TDRs. Signals towards the IJTAG-Module must be multiplexed depending on the mode of operation (off-chip vs on-chip). The details on how the related requirements are achieved are presented in Section 4.3.3 and Section 4.3.4.

Finally, since TDRs can have arbitrary widths and the state of the RSN affects the total scan chain length, operating the IJTAG-Module via the APB-Module is inherently complex and can easily lead to convoluted code. This negatively impacts productivity and increases the probability of bugs. Moreover, this is not in line with the idea of fostering

Figure 4.1: UML description of the extended CSC metamodel. Hardware-related aspects are displayed in yellow while firmware-related aspects are displayed in blue. All changes are highlighted in red.

code reuse since the source code would have to change whenever the IJTAG network structure defined in the system specification or a subnetwork specification changes. Therefore, the generation of source code from high-level descriptions of RSN interactions is necessary to support software developers. The primary purpose is to handle TDR interactions for testing, trimming and configuration in the generated driver while the developers can focus on the algorithmic aspects of the software. Ideally, the high-level description of these RSN procedures shall be close to PDL so that a combination with existing workflows and tools is possible later on. Section 4.4 outlines the possibilities and inner workings of the firmware generation.

#### 4.2 Design Metamodel

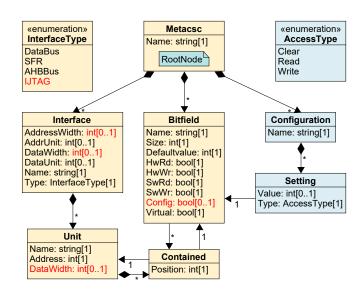

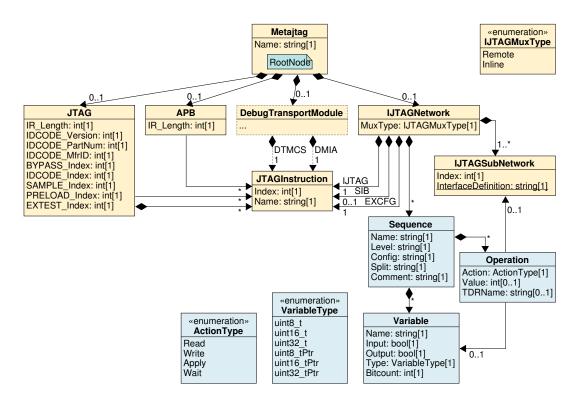

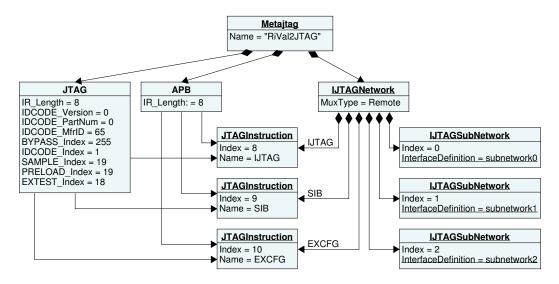

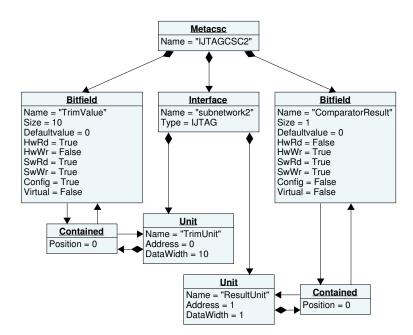

For the full specification of a design as presented in this thesis, two types of metamodels are needed. The first metamodel is an extension of the existing CSC metamodel mentioned in Section 2.2.5 which is concerned with the generation of register interfaces. Figure 4.1 illustrates the parts of the CSC metamodel relevant for this thesis. The second metamodel is the JTAG metamodel and can be seen as the main metamodel in the context of this thesis. It is depicted in Figure 4.2.

The CSC metamodel serves two purposes in the presented design. On the one hand, the APB-Module contains an instance of the CSC since it must be controlled via a register interface. On the other hand, the CSC metalib was adapted to also handle the generation of the IJTAG subnetworks.

Figure 4.2: UML description of the extended CSC metamodel. Hardware-related aspects are displayed in yellow while firmware-related aspects are displayed in blue. The DebugTransportModule represents a future addition. The underlined attribute InterfaceDefinition is an external reference to a CSC Interface (i.e. a JTAG MoT can reference multiple CSC MoTs).

A CSC instance contains a set of Bitfields, which can be seen as the actual physical registers. They have a Name and Size and can be readable and writable from the hardware and the software side (HwRd, HwWr, SwRd, SwWr). The CSC also contains a set of *Interfaces* that can be of various *Types* like the *DataBus* which is a single-cycle bus with data\_in, address, rd\_en, wr\_en inputs and data\_out, error outputs. Moreover, Interfaces are assigned specific data and address widths and unit definitions. They can be used to access the Bitfields via their respective Units which are essentially logical registers with a defined Address. Generally, Bitfields and Units have a many-to-many relationship which is defined by the *Contained* relation and the translation from logical to physical registers is handled by the CSC circuit accordingly.

The CSC metamodel also captures some firmware-related information in the form of Configurations that describe sequences of operations on Bitfields. These can be seen as an addition to the basic HAL generated for the register interface via MetaFirm.

The new option that is required for the design presented in this thesis are interfaces of

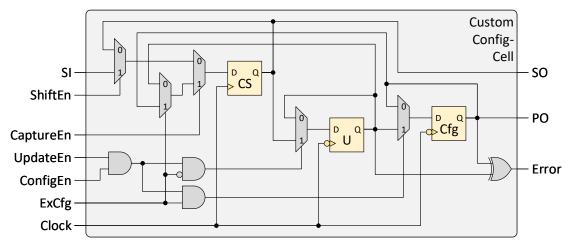

Type IJTAG. In this case, the address and data information does not serve any purpose since the described subnetwork always has a serial input and a serial output and the JTAG control signals. Moreover, the notion of a *Unit's* address is a bit different. Essentially, a *Unit* is still equivalent to an addressable unit in that its design analogue is an SIB at a specific position in the described subnetwork. This SIB guards its related Bitfields which are realized as TDRs. The HwRd and HwWr flags denote whether the respective TDR has update and capture functionality while the new Config flag is used to state that a configuration cell (see Section 4.3.4) shall be generated instead. Since the testtrim- and configuration-procedures for the presented design must be able to work across multiple subnetworks, the firmware-related information in the CSC metamodel is of no direct use in this case.

The JTAG metamodel describes the composition of the presented architecture as well as the system-specific details of the individual modules. Therefore, it can have a JTAG-Module, an APB-Module and an IJTAG-Module which are configured by the respective child objects of an MoT.

In the case of the JTAG-Module, the length of the IR, the contents of the IDCODE register and the indices of the mandatory IDCODE, SAMPLE, PRELOAD and EXTEST instructions can be configured. While the IDCODE register is strictly speaking not mandatory according to the JTAG standard, it is definitely considered good practice to include one and is therefore enforced by the metamodel. The JTAG-Module can also have additional JTAGInstructions which could be any optional standardized instructions or also custom instructions. Moreover, other modules may require their own JTAGInstructions to which the JTAG-Module can have a reference to model the fact that it can interact with them.

The APB-Module is similar to the JTAG. However, it cannot have its own JTAGInstructions. The only way for the APB to interact with TDRs is to have a reference to other modules' JTAGInstructions.

The most complex part of the metamodel is the IJTAG-Module. It has a set of IJTAGSub-Networks that correspond to CSC interfaces of Type IJTAG. Each of these subnetworks has a unique Index to define its position in the network. The module also has a set of JTAGInstructions for the purpose of accessing the RSN (IJTAG and EXCFG) and an optional SIB instruction which may be required depending on the MuxType. The MuxType is there to give control over the type of scan multiplexer that is generated between the subnetworks. While the Inline setting corresponds to SIBs, the Remote setting uses the TDR of the SIB instruction for the control of the scan multiplexers.

On the firmware side, the model can have a set of Sequences. Each Sequence has a set of Variables and Operations. A Variable has a Name, a Type that corresponds to the data type in the code and a Bitcount which defines the usable bits within the Variable to provide some form of documentation and additional safety. Moreover, the Input and Output flags denote whether a Variable is local, a return variable or some kind of function parameter. The Operations can describe Reads from TDRs into Variables and Writes of

| <b>Bibliothek</b> , Your knowledge hub |  |

|----------------------------------------|--|

| <b>2</b> m - N                         |  |

| Name | Width | Direction | Description    |

|------|-------|-----------|----------------|

| TCK  | 1     | Input     | The TCK signal |

| TMS  | 1     | Input     | The TMS signal |

| TDI  | 1     | Input     | The TDI signal |

| TDO  | 1     | Output    | The TDO signal |

Table 4.1: Overview of the JTAG-Interface from the perspective of the SoC.

| Name                | Width | Master | Slave | Description               |

|---------------------|-------|--------|-------|---------------------------|

| Clock               | 1     | Output | Input | The clock signal          |

| Capture             | 1     | Output | Input | The capture enable signal |

| Shift               | 1     | Output | Input | The shift enable signal   |

| Update              | 1     | Output | Input | The update enable signal  |

| $\operatorname{SI}$ | 1     | Output | Input | The serial input signal   |

Table 4.2: Overview of the *JTAG-TAP-Interface* which provides shared control and data signals between the TAP controller and the TDRs. The control signals are not masked yet.

Values or Variables to TDRs. The respective TDR is identified by the reference to the IJTAGSubNetwork and the Name of the Bitfields. Similar to PDL, the Apply is required to define when a scan operation is complete and shall be executed (i.e. all formerly issued Reads and Writes take effect with the Apply). For time-sensitive procedures, Wait can be used to wait at least the specified number of cycles.

Each Sequence has a Name and a Comment which are used for code generation. Moreover, it has a Level that can be used to define driver feature subsets. The Config flag is required to specify whether the Sequence targets normal TDRs or configuration cells. The latter needs to be handled slightly differently in that an additional update with the EXCFG instruction is required. In this case, the Split flag defines whether the two configuration phases should be split into two functions in the generated driver.

## 4.3 Hardware Generation

Instances of the metamodel presented in Section 4.2 serve as a specification for the implemented hardware generators. Therefore, they directly affect the features of the generated hardware description. This section goes into detail on the capabilities of the individual modules, how they are generated and how they are combined to form the presented design.

### 4.3.1 JTAG-Module

The generator of the JTAG-Module expects an instance of the JTAG child object of the JTAG metamodel illustrated in Figure 4.2. It instantiates a finite state machine in

| Name  | Width | Master | Slave | Description                          |

|-------|-------|--------|-------|--------------------------------------|

| Idle  | 1     | Output | Input | Active in the <i>Idle</i> state      |

| Reset | 1     | Output | Input | Active in the Test Logic Reset state |

| Pause | 1     | Output | Input | Active in the $Pause DR$ state       |

Table 4.3: Overview of the JTAG-TAP-EXT-Interface which provides extension signals from the TAP controller.

| Name   | Width | Master | Slave  | Description              |

|--------|-------|--------|--------|--------------------------|

| Select | 1     | Output | Input  | The TDRs select signal   |

| SO     | 1     | Input  | Output | The serial output signal |

Table 4.4: Overview of the JTAG-TDR-Interface which provides the TDR-specific control and data signals. The Select signal is required to mask the control signals of the JTAG-TAP-Interface.

the form of a MetaRTL FSM primitive, which models the TAP controller depicted in Figure 2.2. Moreover, it creates shift registers for the IR as well as for the IDCODE and BYPASS instructions. These are described as MetaRTL Register primitives with Mux primitives at their input and SLICE and CONCAT primitives to describe the shift operations. As the IR requires consistent updates, a separate update register is placed after the shift register. The clock sensitivity of all generated registers is in line with the IEEE 1149.1 standard and also the TAP signals generated by the state machine are delayed accordingly.

In contrast to the BYPASS and IDCODE TDRs, the BSC and any custom instructions are external scan chains. They must therefore be connected to the JTAG-Module via appropriate interfaces. For this purpose, a shared JTAG-TAP-Interface (see Table 4.2) and per-TDR JTAG-TDR-Interfaces (see Table 4.4) are provided.

Since the BSC is a special TDR in that it must be selected by multiple standardized instructions, the generator has an internal record of the implemented instructions which target the BSC. The Select signals are merged and only one JTAG-TDR-Interface is provided for the BSC. However, the individual Select signals are also provided as sideband signals. Another specialty of the BSC is that a Mode signal, which is required to control the multiplexers of boundary scan cells to switch between normal operation and test mode, is also provided as a sideband signal.

Apart from the peculiarities of the standardized instructions and registers, the selection logic and interfaces of any extension instructions are embedded fully automatically. This drastically eases the integration of future extensions without the need to change the generator of the JTAG-Module. The generator also checks the instructions' indices against any IEEE 1149.1 requirements or suggestions to warn the user about violations of the standard or questionable design choices.

| Name        | Address | Width        | Readable | Writable | Description              |

|-------------|---------|--------------|----------|----------|--------------------------|

| Instruction | 0       | $IR\_Length$ | yes      | yes      | The internal IR          |

| Action      | 1       | 2            | no       | yes      | Trigger capture/update   |

| WriteF      | 2       | 16           | no       | yes      | Full 16 bit shift        |

| WriteP      | 3       | 16           | no       | yes      | Partial <16 bit shift    |

| Read        | 4       | 16           | yes      | no       | Read output data         |

| Control     | 5       | 0            | yes      | yes      | Reserved for future      |

| Status      | 6       | 1            | yes      | no       | Poll state of the module |

Table 4.5: Overview of the APB-Module's register interface.

Figure 4.3: State machine of the APB module. Transitions are labelled with their input conditions and their outputs. If none of the conditions of incident transitions are met, the state machine stays in its current state.

#### 4.3.2 **APB-Module**

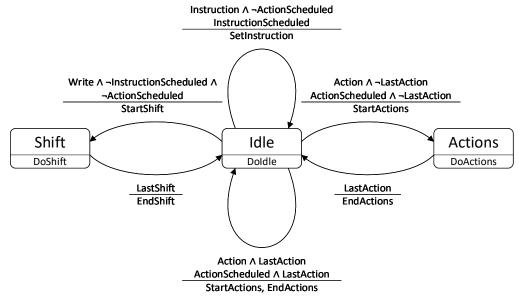

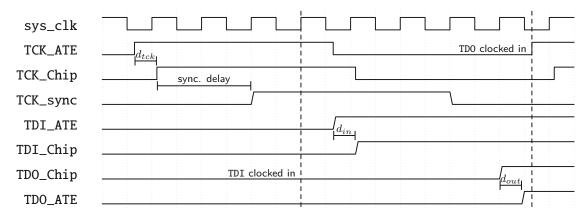

While the APB-Module's metamodel object is very simple, the respective hardware implementation is a bit more complex. As already outlined in Section 4.1, the APB-Module must expose quite a bit of functionality via a register interface. The register interface (see Table 4.5) consists of seven addresses that provide controllability and observability of scan chains. Similarly to the JTAG-Module, the APB-Module provides a single shared JTAG-TAP-Interface as well as one JTAG-TDR-Interface per implemented instruction.

As the APB-Module must serialize and deserialize data and enforce a strict sequence while mostly operating concurrently to the CPU, it contains a state machine as described in Figure 4.3. The transitions' input signals are based on transactions via the register interface (Write, Instruction, Action), the data serialization circuit (LastShift), the instruction circuit (InstructionScheduled) and the action circuit (LastAction, Action-Scheduled). Transition and state output signals directly control the data serialization circuit (StartShift, DoShift, EndShift), the instruction circuit (SetInstruction) and the action circuit (StartActions, DoActions, EndActions).

The first register is the *Instruction* register which can be used to select a TDR in a JTAGstyle. However, in contrast to JTAG the register's bits are written and read in parallel without any need for serialization or deserialization. It is implemented by the generator as two simple MetaRTL Register primitives whose widths depend on the definition in the MoT. If the state machine is not in its idle state, writing to the logical *Instruction* register causes the data to be cached in the secondary register and InstructionScheduled is asserted. The physical register is only updated when SetInstruction is asserted by the state machine (i.e. after any serialization or actions on the selected TDR are finished).

The Action register is only two bits wide and cannot be written to in the conventional sense. Instead, writing to this register causes the currently set bits to be merged with the written bits. The 0-bit (LSB) and 1-bit correspond to a scheduled capture and update operation respectively. When setting any bits in this register, Action is asserted. If any bits are already set, ActionScheduled is asserted. Moreover, if only one bit is set LastAction is asserted. When StartActions or DoActions is asserted by the state machine, the bits in the register are cleared from the MSB to the LSB on successive cycles while performing the assigned actions on the selected TDR (i.e. asserting the respective TDR enable signals). At first, it may seem counterintuitive that a scheduled update action is processed before a scheduled capture action since the state machine in Figure 2.2 does it the other way around. However, in the APB-driven flow, this choice is much more appropriate because it allows to schedule the end and start of back-to-back scan operations.

Shift operations can be started by writing the data to be shifted to the WriteF or the WriteP register. Data supplied during the write is cached and Write is asserted. The cached data is serialized from LSB to MSB to the shared SI on successive cycles as soon as StartShift or DoShift are asserted. During serialization of the 16th bit, LastShift is asserted to leave the shift state. The difference between the two registers is that the Write F is used to shift the full 16 bits while the Write P only performs a partial shift of the supplied data. Partial shifts require a special format to clearly encode the number of bits to be shifted which will be called first-zero-encoding. This is achieved by MSB-aligning the partial data and then padding it with a single zero and as many one bits as are necessary to reach the full 16 bits. For example, padding the data 1101101 to 16 bits would result in 11011010111111111. Hence, when the serialization circuit encounters a WriteP, the only difference to a WriteF is that the shift enable signal must be kept low until the first zero bit (in the example the 8-bit) has been serialized. This is achieved by a register within the serialization circuit which is only set during a WriteP operation.

Reading the data shifted out of the selected TDR during a WriteF or WriteP operation can be accomplished by reading the Read register. During serialization to the SI, the

| Name       | Width | Master       | Slave | Description                   |

|------------|-------|--------------|-------|-------------------------------|

| Clock      | 1     | Output Input |       | The clock signal              |