# Atomic Instruction und Cache-Unterstützung in VADL

# DIPLOMARBEIT

zur Erlangung des akademischen Grades

# **Diplom-Ingenieur**

im Rahmen des Studiums

## Software Engineering und Internet Computing

eingereicht von

Simon Himmelbauer Matrikelnummer 12044925

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall

Wien, 29. Oktober 2024

Simon Himmelbauer

Andreas Krall

# Atomic Instruction and Cache-Support for VADL

## **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

## Software Engineering and Internet Computing

by

Simon Himmelbauer Registration Number 12044925

to the Faculty of Informatics

at the TU Wien

Advisor: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Krall

Vienna, October 29, 2024

Simon Himmelbauer

Andreas Krall

# Erklärung zur Verfassung der Arbeit

Simon Himmelbauer

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 29. Oktober 2024

Simon Himmelbauer

# Acknowledgements

First and foremost, I would like to thank my parents and my brother for their unconditional mental and financial support as well as always being available when I needed them.

Furthermore, thank you to all my friends and library companions who cheered me up when work or other things in life were simply too much. I want to specifically thank my friends Johanna and Jeff as well as especially my girlfriend Emma for holding through with me during these turbulent times.

Special thanks go to my supervisor Prof. Andreas Krall for providing me the opportunity to work on this project and always being available for feedback and further advice. Last but not least, I want to thank the entire VADL team for providing assistance, particularly in the beginning of the project.

# Kurzfassung

Die Entwicklung von neuen Prozessoren für domän-spezifische Anwendungen stellen eine herausfordernde Aufgabe dar, die mit vielen Komplexitäten und Kosten verbunden ist. Prozessorbeschreibungssprachen wie die Vienna Architecture Description Language (VADL) ermöglichen schnelle "design space exploration", da AnwenderInnen die Struktur und das Verhalten ihrer Architektur beschreiben und die VADL Generatoren automatisch Compiler, Linker, Assembler, Simulatoren und sogar synthetisierbare Hardware in einer Hardwarebeschreibungssprache erzeugen können.

Allerdings ist VADL noch weit entfernt, um alle Funktionen moderner Prozessoren ab zu bilden. Erstens unterstützt es keine Übersetzung von virtuellen zu physischen Adressen, was zum Starten aktueller Betriebssysteme benötigt wird. Zweitens kann VADL atomare Instruktionen nicht modellieren. Allerdings sind diese fundamental für Mehrkernprozessoren, insbesondere für die Implementierung von parallelen Algorithmen für den Befehlssatz einer bestimmten Architektur. Letztlich besitzen fast alle gängigen CPUs in PCs, Handys und Einplatinencomputer mehrere Cacheebenen, um Speicher-Latenzzeiten zu verkürzen und dadurch die Ausführung zu beschleunigen. VADL bietet jedoch keine Möglichkeit zur Modellierung von Caches und Cache-Hierarchien. In dieser Arbeit erweitern wir VADL und die generierten Simulatoren, um all die vorhin genannten Aspekte zu integrieren.

Um die genannten Funktionalitäten zu demonstrieren, implementierten wir atomare Instruktionen für unsere RISC-V RV32 und AArch64 VADL Spezifikationen. Außerdem erweiterten wir VADL, sodass Caches und beliebige Cache-Hierarchien definiert werden können. Für diesen Zweck präsentieren wir einen neuen Cachesimulator, welchen wir von Grund auf an die Anwendungsfälle von VADL angepasst haben. Um den Einfluss von Caches besser verstehen zu können, kann der Simulator sowohl funktionale als auch hardwarespezifische Aspekte, wie zum Beispiel Kohärenzzustände und Nachrichten, welche über den Interconnect gesendet werden, simulieren. Wir validierten die Genauigkeit des Cachesimulators durch einen Vergleich mit gem5, ein im Forschungsumfeld etablierter Allzwecksimulator. Zu guter Letzt implementierten wir den Sv32 Adressübersetzungsalgorithmus der RISC-V Architektur in VADL.

# Abstract

Designing new processors for domain-specific applications can be a cumbersome task due to the high complexity and costs involved. Hence, processor description languages, such as the Vienna Architecture Description Language (VADL), enable rapid design space exploration because users may describe the structure and behavior of their architecture and the VADL generators automatically produce compilers, linkers, assemblers, simulators and even synthesizable hardware in a hardware description language.

However, VADL is still away from allowing to design all features modern processors provide. Firstly, it does not support translation from virtual to physical addresses necessary for properly booting modern operating systems. Secondly, VADL cannot model atomic instructions. However, they are fundamental for multi-core processors, particularly when implementing parallel algorithms on the given instruction set architecture. Finally, almost all CPUs, found in PCs, phones and even single-board computers, employ multiple levels of caches in order to reduce memory latencies and hence, speed up execution. However, VADL does not offer a way to model caches and cache hierarchies. In this work, we extend VADL and its generated simulators to integrate all these aforementioned aspects.

To showcase our proposed features, we implemented atomic instructions for our RISC-V RV32 and AArch64 VADL specifications. Furthermore, we extended VADL to allow defining caches and arbitrary cache hierarchies. For this purpose, we present a new cache simulator designed from scratch tailored towards the use cases of VADL. In order to understand the impact of caching, the simulator is capable of simulating high-level functionality and low-level aspects such as coherence states and messages sent via the interconnect. We validated parts of its accuracy by comparing it to gem5, which is a general purpose simulator well-established in academia. Finally, we implemented the Sv32 address translation scheme of the RISC-V ISA in VADL.

# Contents

| $\mathbf{K}$ | urzfassung                                          | ix   |

|--------------|-----------------------------------------------------|------|

| A            | bstract                                             | xi   |

| Co           | ontents                                             | xiii |

| 1            | Introduction                                        | 1    |

|              | 1.1 Problem Statement and Motivation                | 1    |

|              | 1.2 Aim of the Thesis and Expected Results          | 3    |

|              | 1.3 Research Questions                              | 4    |

|              | 1.4 Methodology                                     | 5    |

|              | 1.5 Structure of this Thesis                        | 5    |

| <b>2</b>     | Background                                          | 7    |

|              | 2.1 Vienna Architecture Description Language (VADL) | 7    |

|              | 2.2 Caches and Cache Coherence                      | 13   |

|              | 2.3 Memory Consistency Model                        | 19   |

|              | 2.4 Atomic Instructions                             | 23   |

|              | 2.5 Virtual Address Space and Address Translation   | 25   |

| 3            | Related Work                                        | 29   |

|              | 3.1 Cache Simulation                                | 29   |

|              | 3.2 Processor Description Languages                 | 33   |

| 4            | Implementation                                      | 35   |

| -            | 4.1 Atomic Instruction Support                      | 35   |

|              | 4.2 Address Translation                             | 46   |

|              | 4.3 Cache                                           | 48   |

|              | 4.4 Write Buffers                                   | 63   |

| 5            | Evaluation                                          | 69   |

| 9            | 5.1 Benchmark Setup                                 | 69   |

|              | 5.2 Results                                         | 71   |

|              |                                                     |      |

xiii

| 6 Future Work                             | 77  |

|-------------------------------------------|-----|

| 7 Conclusion                              | 81  |

| A Common Atomic Primitives                | 83  |

| <b>B</b> Sv32 Memory Translation          | 87  |

| C VADL Implementation of RV32 A-Extension | 91  |

| D VADL Benchmark Configuration            | 93  |

| E Additional Results                      | 95  |

| List of Figures                           | 99  |

| List of Tables                            | 101 |

| List of Algorithms                        | 103 |

| Listings                                  | 105 |

| Acronyms                                  | 107 |

| Bibliography                              | 109 |

# CHAPTER

# Introduction

#### 1.1 Problem Statement and Motivation

In a world where Moore's Law slowly converges toward its limit, manufactures follow the trend of packing more and more cores onto the same die. When designing an out-of-order multi-scalar and/or multicore architecture, additional aspects become relevant:

- 1. What memory model do architects want to implement?

- 2. What instructions do they require in order to provide stronger guarantees than given by the memory model?

- 3. How does all of this affect the cache coherency between cores?

We explain the relevance of these questions in the following paragraphs. We begin with why a CPU even needs a memory model? Modern processors implement a variety of techniques to keep their pipeline busy and therefore, increase its performance. Examples are multiple layers of caches as well as out-of-order and speculative execution. For instance, a CPU might prefetch certain memory loads in order to hide their latency as much as possible. In addition, CPUs commonly have multiple layers of caches in order to avoid costly accesses to main memory. These caches are often tied to a specific set of cores (e.g. Level 1 caches are usually tied to a single core, while the level 2 cache is shared). This means that a store to a certain memory location is not necessarily visible to other threads because they might access an older value in their local cache. These tricks work fine in single-threaded use cases because they are designed to be transparent to the underlying process. However, when working with parallel algorithms, the effects of these techniques become apparent. So how can a software engineer implement a parallel algorithm correctly? This is where the memory/concurrency model comes into action: The memory model of an architecture describes how memory accesses can be reordered (e.g. the memory model might guarantee that the CPU keeps all stores in the same order). The concurrency model often relates to the underlying microarchitecture. For instance, x86 implements the total store order (TSO) model which originates from the fact that each core has a FIFO write-buffer to hide the latency of commencing a write directly to memory  $[NSH^+20]$ , p. 3]. This is why the memory model and the underlying caching architecture are closely related which answers why question one and three matter to a CPU architecture designer.

To answer the second question, consider our software engineer who now has a memory model explaining how the underlying microarchitecture affects the correctness of a parallel algorithm. What if it turns out that the provided guarantees are too weak? Modern architectures provide so-called memory fences or barriers to handle this problem. A fence instruction prevents the CPU from ordering a memory access across its location, just like an actual fence. Weaker architectures (weak refers to the memory model) often provide different types of fences, varying in strength but also in performance costs. Thus, it is again up to the architecture designer to define what fences are necessary which again largely depends on the memory model as well as underlying caching mechanism. We observe that these three concepts closely interact with each other.

Last but not least, concurrent languages and multicore machines additionally require support for atomic operations. For instance, take two threads A and B which each increment a value stored at some memory location n number of times. The expected result is 2n. Each increment operation consists of three steps: Loading the value (read), incrementing it (modify) and storing the result back (write). Now take thread A that loads the initial value 0 and then stops. Next, thread B executes the increment operation ntimes. Now A continues, increments 0 and stores the result (one) back to memory. Hence, the final value (n) of thread B is not considered and simply overwritten. We observe that the final result does not equal to 2n. Note that the strength of the memory model does not impact the correctness here because even in case our CPU executes the program in program order and has no caches, which in consequences means every store is visible in a total order, the execution previously described may still occur. Instead, engineers require a certain class of atomic operations that combine all three steps (read, modify and write) into a single observable step. The most common classes are fetch-and-modify (-Add, -Sub, etc.) and compare-and-swap (CAS).

Following these design considerations, we focus on the job of a CPU architect. The Vienna Architecture Description Language (VADL) is a processor description language (PDL) that allows developers to design a CPU on all levels, from the instruction set and ABI down to the underlying microarchitecture. Currently, VADL misses support for the following aspects:

• Atomic instructions: As mentioned above, some concurrent and parallel algorithms require certain synchronization primitives to function correctly. This requires the architecture to provide certain instructions such as memory fences/barriers or read-modify-write (RMW) instructions. Thus, VADL must support a way to

prevent reorderings in case of memory barriers as well as a way to define atomic operations.

- Caches and Memory Hierarchy: VADL currently does not support any type of CPU cache. However, they are imperative for fast CPUs, even in the case of single-threaded processors. Furthermore, when designing atomic instructions on a microarchitectural level, their effect becomes more interesting in combination with caches. A flexible mechanism to define caches could also allow VADL developers to more easily experiment with different hierarchies, sizes and coherence protocols. Furthermore, simulation facilitates design space exploration (DSE) [BKP20].

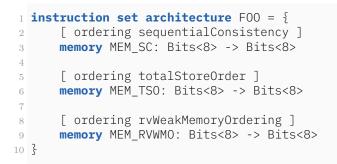

- Memory Model A memory model is required in order to properly define what kind of synchronization instructions are necessary. For instance, a sequentially consistent architecture does not require any form of fence instructions, while a more relaxed model might want to provide different types of barriers, each with different strengths and guarantees.

## 1.2 Aim of the Thesis and Expected Results

The goal is to lay a foundation for defining out-of-order multi-scalar and multicore processors in VADL. This means VADL must support the following aspects:

- Definition of caches and declaration of memory hierarchy: The goal is to declare the total and line size, associativity, replacement policy and coherence protocol of a cache. As part of this thesis, one idea is to configure caches via annotations, a syntactical mechanism provided by VADL.

- **Definition of address translation**: While not strictly necessary for multicore processors, we want to add support for defining address translation from virtual to physical addresses. Since memory management units (MMUs) themselves utilize caches such as the translation lookaside buffer (TLB), this topic conveniently matches the task of implementing a caching subsystem.

- Definition of atomic instructions: This specifically includes fetch-and-modify, compare-and-swap and load-reserved/store-conditional. The goal is to support all atomic operations provided by ARMv8 AArch64 [Arm21, C3.2.6, C3.2.12.1 C3.2.12.4] and RISC-V RV32 (Standard Extension for Atomic Instructions, Version 2.1) [RIS19].

- **Declaration of memory model**: The architect must specify what memory model is desired for the instruction set architecture. It is important that this model is then fully respected by both the instruction set and underlying microarchitecture. Ultimately, a developer should be able to define an arbitrary axiomatic or operational model. However, this thesis focuses on a set of specific models.

In order to meaningfully test these features, the instruction set simulator (ISS) and cycle accurate simulator (CAS) will be extended to support these language features. For the ISS, it is sufficient to handle atomic instructions and address translation because microarchitectural details such as caching are not relevant here. On the other side, the CAS must support all aspects of the hardware.

Needless to say, the effects of caching behavior and atomic instructions become more apparent in multicore scenarios. However, both simulators currently do not support multithreading and adding multithreading support is specifically not in the scope of this thesis. However, we can measure how emulating the cache hierarchy affects the throughput of the CAS. In addition, the simulator should be capable of tracking cache-specific information such as miss rate.

## **1.3** Research Questions

**RQ1:** How can we extend VADL to enable developers to fully model and implement atomic instructions such as Fetch-And-Modify, CAS and memory fences (as provided by ARMv8 and RISC-V)?

As mentioned above, we want to offer VADL developers the possibility to specify arbitrary atomic instructions. Our idea is to study the set of operations provided by common ISAs, such as x86, ARM, RISC-V and Power, to help us derive what features are necessary to cover their use cases.

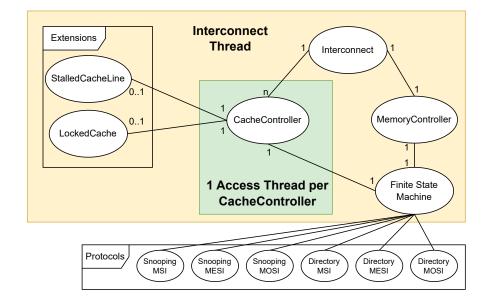

**RQ2:** How can memory models and cache coherence be efficiently and correctly implemented in a simulator?

This question primarily concerns the cache and write buffer simulation. Correctness is particularly important for design space exploration because developing hardware prototypes for a new chip design is costly. Needless to say, accuracy is a broad term. In the context of this thesis, we decided to implement a functional cache simulator, based on the definition from Brais et al. [BKP20]. Hence, we want to simulate behavioral events such as cache misses, coherence state changes and interconnect topographies. Some simulators go into more detail and consider detailed timings such as how long a message needs to traverse the interconnect. However, we think this has a significant impact on the performance of the simulation and hence, believe that this additional overhead is not worth for the purposes of VADL.

**RQ3**: What performance impact does cache emulation have on the cycle accurate simulation?

A cache simulator might have a considerable influence on the overall performance of the simulator. Consider a simple system with just an instruction cache: The CAS requires constant interaction with the cache simulator because the cache must be consulted for every single instruction fetch. Hence, we want to evaluate how the cache simulation impacts the overall runtime of our CAS.

4

## 1.4 Methodology

We begin with an onboarding phase in order to become familiar with the current state of the project which includes VADL itself, the VADL frontend, VADL intermediate representation (VIR) and the instruction set simulator (ISS) as well as cycle accurate simulator (CAS). Next, we design two to three proof-of-concept specifications in VADL to support address translation, caches and atomic instructions so that they comply with the goals described in section 1.2. Regarding RQ1, deciding on the most concise and intuitive version should be based on an empirical study, as conducted by [PSZ21]. However, this is not in the scope of this thesis. Instead we compare our design to existing solutions and base our preference on personal opinions. This version will be integrated into VADL in addition to both the ISS and CAS receiving the necessary support to simulate caching, address translation and atomic instructions (RQ2).

As mentioned in section 1.2, one of the stated goals is the ability to implement all atomic instructions of ARMv8 and RISC-V in VADL. The latter can be validated using the official RISC-V test suite<sup>1</sup>. While ARM provides a validation framework as well, it is unfortunately not publicly available MRSM16. Hence, we verify their correctness by hand. Next, we evaluate the impact of simulating the caching subsystem by comparing its throughput to a version without caching (RQ3). Furthermore, we verify the functionality of the cache hierarchy by measuring cache-specific data such as hit and miss rate and comparing them to a state-of-the-art simulator such as gem5 [BBB+11], [LAA+20] (RQ2).

## 1.5 Structure of this Thesis

Chapter 2 introduces the reader to theoretical concepts of caches, memory translation and atomic instructions. In addition, we present an overview of VADL. Chapter 3 summarizes current research on the topics of PDLs and cache simulation. In Chapter 4, we state our language design choices for defining caches, write buffers, memory hierarchies, atomic instructions as well as address translation in VADL. We also present our cache and write buffer simulator. Next, we discuss our VADL specifications of atomic instructions and performance findings in terms of cache simulation and address translation in Chapter 5. Finally, we propose further improvements and extension to VADL in Chapter 6 and conclude our thesis in Chapter 7.

# $_{\rm CHAPTER} 2$

# Background

This section introduces the reader to several concepts fundamental to understanding the goal of this thesis. Note that many sections talk about memory accesses. We use the terms 'reads' and 'loads' as well as 'writes' and 'stores' interchangeably.

## 2.1 Vienna Architecture Description Language (VADL)

The Vienna Architecture Description Language (VADL) is a PDL for designing all aspects of a processor, ranging from the instruction set architecture (ISA), application binary interface (ABI) to the microarchitecture (MiA). It was developed at the Technical University of Vienna as part of a research project [Sch20, Mih23, Sch22, Gra21, HHH<sup>+</sup>24, HK23]. The following Listing provides an overview of some of the features part of VADL

```

constant MLen = 32

using BitsM = Bits<MLen>

using SIntM = SInt<MLen>

using UIntM = UInt<MLen>

function lessthan (a: SIntM, b: SIntM) -> Bool = a < b

import rv32i::RV32I

instruction set architecture RV32IM extending RV32I = {}

application binary interface ABI for RV32IM = {}

user mode emulation UME for CPU = {}

assembly description Assemble for RV32IM = {}

micro processor CPU implements RV32IM with ABI = {}

micro architecture FiveStage implements CPU = {}

```

Listing 2.1: Overview of the Vienna Architecture Description Language

2

4

6

7 8

9

11

13

14 15

16

Lines 11-16 define the different aspects of a CPU architecture. Note that depending on the use case, not all definitions are required. For instance, an ISS does not require a MiA specification, while the compiler generator may optionally use the additional information to improve instruction scheduling for instance. Needless to say, meaningful cycle-accurate simulation relies on a MiA\_Lines 1-9 in Listing 2.1 present some structural features of VADL. For instance, constant definitions can be used to easily switch between 32- and 64-bit address width while keeping the same ISA definition. The using keyword can be compared to C's **typedef**. VADL also provides functions as seen on Line 7. Here, the function lessthan takes two arguments a and b both of type SIntM and returns a value of type bool. Note that functions must be pure in VADL. Hence, any side effects are forbidden, such as reading or writing from/to memory. We additionally want to highlight the strict separation of ISA and MiA\_All instructions, registers and memory are defined generically in an ISA definition, while the MiA is only concerned with execution of said instruction set. This enables CPU engineers to write multiple MiAs for the same ISA.

The VADL frontend then takes a VADL specification and allows to generate a compiler backend, simulators as well as a hardware description language, which can be synthesized on an FPGA. To be more precise, the VADL frontend currently supports generating an LLVM compiler backend, instruction set simulator (ISS), a cycle accurate simulator (CAS) as well as Chisel for hardware description. However, the general design goal of VADL and its frontend is to support arbitrary backends. Hence, the VADL generators accommodate a common intermediate language called the VADL intermediate representation (VIR) which conceptually follows static single assignment (SSA) form. This section introduces some of the core features of VADL

#### 2.1.1 Instruction Set Architecture

An **ISA** definition fundamentally consists of the following construction:

```

instruction set architecture SYS = {

using Byte = Bits<8>

using Index = Bits<5>

using Address = Bits<32>

program counter PC : Address

memory MEM : Address -> Byte

register file X : Index -> Byte

// ...

```

Listing 2.2: Basic instruction set architecture (ISA).

The example above defines an ISA with the name SYS and showcases some general aspects of VADL. Bits<N> is a primitive type representing a bit vector of size N. VADL also provides specialized integer types UInt<N> and SInt<N> to represent unsigned integer

(with modulo arithmetic) as well as signed integers using the two's complement. The **using** directive allows to alias a type with a more relevant identifier in the given context. For example, in Listing 2.2, Line 4 defines a specific Address type. Thus, using this new type provides more semantical information than using the primitive Bits<32> directly. Furthermore, this allows developers to more easily reuse the ISA definition. For instance, if users want to support an address width of 64, they will need to change only one line of code. Having to alter the size only at one location additionally tends to be less error-prone. Line 6 defines a program counter named PC having the type Address (Bits<32>). Next, the architecture needs some memory, which is called MEM and defined on Line 7. Observe that MEM is actually a function mapping an address to a single Byte (defined as Bits<8> on Line 2). Register definitions are similar, however, the argument describes an index *i* to access the *i*th register. Thus, the size of the argument also implies the amount of registers of the given register file. In our case, index is a bit vector of size five and thus, the architecture has  $2^5 = 32$  registers.

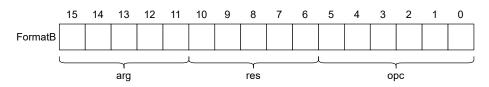

Next, in order to complement the ISA with an instruction, the specification first requires information about the structure of an instruction. Consider the following example of a format definition:

```

instruction set architecture RV32I extending SYS = {

format FormatB : Byte = {

arg : Index,

res : Index,

opc : Bits<6>

}

// ...

}

```

Listing 2.3: Format definition in VADL

The **format** keyword defines a format with the name FormatB and the type Byte. Hence, this type of instruction consists of 16 bits. These bits are separated into three fields: arg, res and opc. Recall that Index is defined as a bit vector of size five. Thus, all fields summed up result in 16 bits. Note that the order of the fields matters in how they are layed out in memory, as seen in Figure 2.1. We also want to highlight another feature of VADL: An ISA can be based on another ISA specification using the **extending** keyword. Compare this to the approach of RISC-V which is separated into several extensions **RIS19**. VADL allows to define the base architecture as RV32I and an implementation including integer multiplication and division (M-extension) can be provided separately by defining a new **ISA** via **instruction set architecture** RV32IM **extending** RV32I. Next follows a definition of our first instruction:

Figure 2.1: Memory layout of our example format definition FormatB.

```

instruction LOAD : FormatB = {

let addr = (0x1000'0000 as UInt<32>) + (X(arg) as UInt<32>) in {

2

X( res ) := MEM( addr )

3

3

4

5

}

6

encoding LOAD = {

7

opc = 0b0010

}

8

assembly LOAD = (mnemonic, " ", register( res ), ",", register( arg ))

9

```

Listing 2.4: Instruction definition in VADL.

Lines 1-5 define the semantics of an instruction called LOAD using the previously defined FormatB as a structure. All fields of the format are directly accessible within the definition. The Listing 2.4 shows how the address is calculated from a fixed base address and an offset stored in register X(arg). On line 3, the value stored at the address is loaded and saved in register X(res). Observe how the arg and res fields are used as parameters within the definition. Recall that our format definition also contains the field opc. Needless to say, the CPU instruction decoder must be able to uniquely identify the appropriate instruction. Generally, instructions have a fixed structure (defined via a format in VADL) and a part of it, called the *opcode*, identifies what instruction to execute [PH17, p. 198]. Hence, we added an opc field in Listing 2.3. Line 7 establishes the static structure of an instruction in the encoding. In theory, these steps are sufficient for a simulator or hardware generator. However, the compiler generator also requires information about the structure of the assembly language, defined on Line 9. A VADL developer simply specifies the syntax and the VADL generators automatically produce the appropriate grammar. However, many instructions share a similar structure in practice and hence, manually defining the assembly string for each instruction leads to a lot of boilerplate code. VADL provides additional helper functions to avoid this situation: The mnemonic builtin uses the identifier of the instruction for matching. For instance, assume our ISA also had two instructions named ADD and STORE. We could write the following code:

assembly ADD, LOAD, STORE =

(mnemonic, " ", register(res), ",", register(arg))

Listing 2.5: Handling multiple instructions with a single assembly definition.

10

The **register** builtin matches the field of a format to a register. The VADL frontend includes a semantical analysis to check on what register file the field is used Sch22. For instance, consider an architecture with a separate set of address and data registers, called A and D respectively. Next, assume an instruction LOAD D1, A2 that loads the value stored at address A2 in memory and saves the data to register D1. Without the aforementioned analysis, the assembler would need to assume that any register file is valid. Hence, it would accept LOAD D1, D2 for example. The analysis ensures that the VADL frontend only generates rules for registers that are actually used by the specific instruction.

#### 2.1.2 Application Binary Interface

This section presents how CPU engineers may specify an application binary interface (ABI) in VADL. We continue with the example introduced in Section 2.1.1.

```

application binary interface ABI for RV32I = {

1

alias register a0 = X(0)

2

alias register a1 = X(1)

alias register a2 = X(2)

4

alias register a3 = X(3)

alias register sp = X(31)

6

7

[ alignment : Bits<8> ]

8

stack pointer = sp

9

return address = X(29)

11

frame pointer = X(30)

return value = [ a0 ]

function argument = [a{0..3}]

13

caller saved = [ a{0..3}, X(4), X(5), X(6), X(7) ]

14

callee saved = [ X(8), X(9), X(10), sp ]

15

16 }

```

Listing 2.6: ABI definition in VADL

First, we introduce another VADL concept on Line 7 called *annotations*. They equip the subsequent element with additional attributes. What type of annotations are supported depends on the specific object. In our example, the stack pointer definition has the annotation alignment, specifying that the stack pointer must always be aligned to eight bits. Listing 2.6 also shows definitions of several typical elements of an ABI which should mostly be self-explanatory. Observe that VADL also supports aliasing registers commonly used by architectures [RIS19], p. 137]. For instance, a0 and sp map to the registers X(0) and X(31) respectively. Aliases additionally help save some boilerplate code, for instance, when defining function arguments on Line 13. Here, a{0..3} expands into a0, a1, a2, a3.

2

```

micro processor CPU implements RV32I with ABI = {

1

start = 0 \times 8000'0000

2

stop = PC = 0xeeee'eeee

3

4

exception invalid = {

6

startup = {

8

3

9

}

```

Listing 2.7: Microprocessor definition in VADL.

#### 2.1.3Microprocessor and Microarchitecture

The idea of the micro processor section is to describe general behavior that are independent from a MiA. As seen in Listing 2.7, this includes defining the start address of execution, a stop condition (mostly relevant for simulation), exception handling as well as including startup code to execute before the user-supplied binary. Last but not least, we can specify a MiA for our micro processor CPU, as seen in Listing 2.8.

```

1 micro architecture P3 implements CPU = {

stage FETCH -> ( fr : FetchResult ) = {

3

// ...

7

4

stage DECODE -> ( ir : Instruction ) = {

6

// Previous stage result accessible via FETCH.fr

7

}

8

9

stage EXECUTE = {

// Previous stage result accessible via DECODE.ir

7

13

}

```

Listing 2.8: Microarchitecture definition in VADL

This definition only presents a small subset of the MiA features. Our example implements the CPU micro processor in a three-stage pipeline MiA called P3. The pipeline is separated into three stages named FETCH, DECODE and EXECUTE where each stage can access the output of the previous one.

**TU Bibliothek** Die approbierte gedruckte Originalversion dieser Diplomarbeit ist an der TU Wien Bibliothek verfügbar WIEN Vourknowledge hub The approved original version of this thesis is available in print at TU Wien Bibliothek.

12

## 2.2 Caches and Cache Coherence

In a modern processor, reading or writing to main memory usually belongs to the slowest aspects in the pipeline of a CPU. Thus, modern compilers try to generate code which minimizes the amount of accesses to main memory by keeping values in registers. However, accessing main memory becomes unavoidable at some point and in order to bridge the gap, CPUs provide multiple levels of caches that contain a subset of main memory. The size of a cache is considerably smaller than main memory (e.g. the Cortex-X1 has an L1 data cache of size 64 kB [Arm20, p. A6-74]). How does a system determine what data to store in the cache? The concept of caching is based on **temporal** and **spatial** locality [PH17], p. 738]. The former assumes that a value that has recently been accessed is likely to be accessed again, while the latter assumes that data closely located has a high probability to be accessed as well. For example, consider an array A in the programming language C and the common case of iterating through all elements in A. Recall that an array always represents a continuous part in memory. Instead of loading each element individually from main memory, a cache may fetch a larger region surrounding the first element and thus, accessing subsequent elements in A will be much faster because they are already contained in the cache. This block of data, fetched from memory at once, is called the **cache line**. Its size can vary among microarchitectures, but many, such as the Cortex X1, have a cache line size of 64 bytes Arm20.

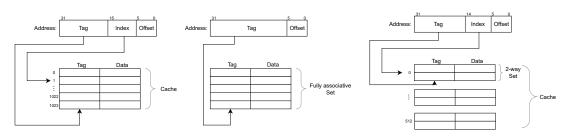

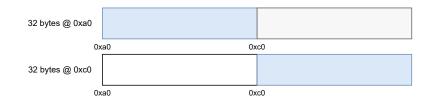

There exist several approaches for managing cache lines. One is to store them in an array-like manner as seen in 2.2 which is called a **direct-mapped** cache. To determine the location of a cache line, the controller considers the index of an address which directly maps to an entry in the cache. The size of the index depends on the amount of cache lines. For instance, a cache with 1024 entries requires  $\log_2(1024) = 10$  bits. However, the mapping from address to index is surjective. In other words, multiple addresses map to the same index. The tag in combination with the index uniquely identifies a memory region and thus, the controller must store the tag in addition to the data in order to check whether the cache line corresponds to the requested memory region. If the tag does not match, the cache line needs to be evicted and the requested data must be fetched from main memory. Next, as mentioned above, a cache line contains several bytes. The offset precisely determines a specific element within the cache line. The size of the offset directly correlates with the size of the cache line. For instance, a cache line of size 64 bytes requires  $\log_2(64) = 6$  bits. Finally, the size of the tag consists of the remaining parts of the address: Size of address  $-\log_2(\text{Number of cache entries}) - \log_2(\text{Size of cache line})$ . To continue with our example, this corresponds to 32 - 10 - 6 = 16 bits. PH17, p. 754-764]

The advantage of a direct-mapped cache is its constant lookup time and thus, it scales well with the size of the cache. However, consider a program which accesses different memory regions but all addresses map to the same index. Then the single cache line in the cache needs to be constantly evicted, while other indices of the cache remain completely unused. An alternative approach is to manage its cache lines in a set instead of an array. Thus, the index becomes irrelevant and only the tags are considered. This

Figure 2.2: Basic examples for a cache of size 64 KiB in three different variations from left to right: Direct-mapped, fully associative and 2-way set associative. An address is separated into a tag, index and offset. Sizes of each parameter depend on the configuration of the cache. Index maps to the entry in the cache, tag determines whether cache line corresponds to the same memory region. Offset corresponds to offset within cache line. Figure inspired by [PH17], p. 762]

type of cache is called **fully associative** and allows full utilization of the entire cache because the controller only needs to evict a cache line if the set is full. This adds more complexity though: The decision on what cache line the cache controller decides to evict (called the **replacement policy**) might impact the performance of the system. For example, consider a worst-case situation where the CPU alternatingly accesses two memory regions (mapping to two different cache lines) and the controller always replaces one with the other. Here, this scenario completely eliminates the benefits of a cache. CPU vendors have come up with several schemes. Basic ones include round-robin, random, least-frequently used (LFU) or least-recently used (LRU). For instance, the Cortex X1 uses pseudo-LRU for its L1 data and instruction caches Arm20, p. A6-74. Since **LRU** is difficult to implement in hardware and particularly does not scale with the amount of cache lines, this replacement policy is often approximated, hence the name pseudo-LRU [PH17, p. 861]. There exist also more thorough and complex schemes, such as Static and Dynamic Re-reference Interval Prediction (SRRIP/DRRIP) JTSE10, Sampling Dead Block Prediction (SDBP) [KTJ10] and Signature-based Hit Predictor (SHiP) [WJH<sup>+</sup>11].

A fully-associative cache might seem clearly superior to its direct-mapped counterpart because it is able to fully utilize the entire cache. However, implementing a fully associative cache requires comparing the tags of all cache lines which incurs additional overhead and might be infeasible to achieve in hardware. However, there exists a way to combine both ideas: Instead of having one large set, the cache can be divided into several sets and each set corresponds to a certain index. Each set can then hold multiple cache lines with the same index. This is called a **set associative** cache. For instance, a cache with sets of size 4 is called a 4-way set associative cache. Which configuration is most desirable highly depends on several factors. For instance, a fully associative cache might be feasible if the cache is not very big and/or a cache miss induces a high penalty [PH17, S. 860].

Last but not least, caches can be distinguished in terms of how they handle writes.

| Thread 1 | Thread 2      |

|----------|---------------|

| A = 1    | while(A == 0) |

Figure 2.3: Example execution for cache coherency. A is initialized with 0. Inspired by  $[NSH^+20]$ .

A write through cache forwards all writes directly to memory, while a write back configuration writes a value to the cache and thus, the modified data will be written back to memory once the cache line is evicted. [PH17], S. 862]

#### 2.2.1 Cache Coherence

Modern CPUs usually have several layers of caches where each layer tends to be bigger but also slower to access. For instance, the Intel Ice Lake Client Microarchitecture has a L1 access latency of five cycles, while L2 already needs 13 cycles Int24, p. 2-21. This is called the cache or memory hierarchy because if a requested memory region does not exist in the level 1 cache, then it has to be fetched from the second level. If it also does not exist there, it needs to be loaded from the third level and so forth. Next, consider multi-core CPUs where another property of a cache becomes relevant: A cache may be shared by multiple cores or is local to a core. For instance, modern CPU cores usually have their own L1 data and instruction caches but the L2 cache could be shared by all cores. Observe that this introduces another problem: Consider the example program in Figure 2.3. Thread 2 begins execution and since A is initialized to 0, the loop will be continuously executed. Thread 1 then stores A = 1. In a system that only consists of main memory, thread 2 will see the value written by 1 and exit the loop. Next, consider a system where each core has a local cache. Thread 2 remains stuck in the loop. Why? Both threads have a copy of A in their local caches. Since 2 executes first, A == 0. Once thread 1 stores A = 1, this value is only updated in its local cache and thus, not visible by 2. Even if thread 1 decides to evict the cache line at some point and writes A = 1 back to memory, thread 2 will not realize that the value has been modified. This example shows the necessity for the system to provide additional guarantees, which are called **coherence invariants**. There exist different variations of these properties, such as token coherence MHW03. However, they are conceptually similar and we stick to the definition from [NSH<sup>+</sup>20, p. 13]: The authors describe two safety invariants called Single-Writer, Multiple-Read (SWMR) and Data-Value invariant. The former describes that at any point of time either one core may exclusively read and write to a location or multiple entities may only read from the same location. This concept allows us to separate memory accesses into single-writer and multiple-reader epochs. The Data-Value invariant states that the value of a memory location at the end of an epoch is equal to the value at the beginning of the succeeding epoch. Both invariants solve our previous example: The first epoch starts when thread 2 acquires read-only access to A where A == 0. Once thread 1 attempts to write A = 1, thread 2 loses access to A and thus, a new single-writer epoch begins. Finally, thread 2 tries to read from A again, leading

to a new read-only epoch. Due to our Data-Value invariant, the value of A must be 1 because the write epoch ended with A == 1. Thus, thread 2 exits the loop. This results in so-called **cache coherence** and both the SWMR and Data-Value property comprise the safety invariants of **cache coherence**.

In order to provide cache coherence, cache and memory controllers implement a finite state-machine (FSM) associated with each cache line. One of the simplest protocols is the **MSI** protocol. The name corresponds to the three main states that a cache line can be associated with. This protocol closely matches the SWMR invariant where the *modified* state describes that the cache controller is allowed to read and write, while the *shared* state denotes read-only access. All caches are connected via a bus to the memory. If a cache requires access to a memory region, they send a request on the bus, including the access type (read-only or read-write) as well as the address. The other cache entities monitor the bus to react accordingly. For instance, if some caches have a certain memory location in the *shared* state and some cache then requests read-write access, the other caches will see those messages and evict their copies of the same location. Thus, these type of protocols are called snooping cache coherence protocols. Another common protocol family are directory coherence protocols [LLG<sup>+</sup>90]. The main problem with a snooping-based system is that all messages are broadcasted to all entities and every cache controller has to process these messages, limiting scaling. Directory coherence protocols follow the idea that there exists a global view on the state of a memory location (the directory) and thus, requests are sent directly to the directory. The directory then forwards the message accordingly. For instance, if a cache A requests read-write access, while another cache B currently owns the location, the directory will forward the message from A to B, which then evicts the cache line and sends it to A directly.

#### 2.2.2 Common Cache Coherence protocols

The design of the cache coherence protocol heavily depends on the structure of the cache hierarchy. Relevant aspects include the amount of levels, whether the cache should be write through or write back, inclusive-or-exclusive and whether the protocol must support non-uniform memory access (NUMA) configurations. All these properties particularly determine what transitional states are required. Note that there are usually two sets of states: One for the cache and another for the memory controller. To keep this section easier to understand, we want to stick to the states of the former. We begin by introducing some of the more common protocols in their base configuration:

**MSI**: This protocol consists of three states *Modified*, *Shared* and *Invalid*. The first allows read and write access, while the second one is restricted to read-only access. Note that among all caches only one controller can be in the *Modified* state for the same cache line. However, multiple readers may access the same data in a read-only manner and therefore, the *Shared* state can be obtained by multiple entities at the same time. Note that the cache lines in the *Shared* state are always clean, which means a cache controller may simply evict the cache line without needing to write it back to memory. Needless to

say, a cache holding a line in a *Modified* state needs to write the data back to memory before eviction.

**MESI**: Another common protocol (e.g. implemented by the Cortex X1 [Arm20]), which adds an *Exclusive* state, is called **MESI**. To understand the motivation for this version, consider the following case: Assume the CPU first reads from a memory region and then writes to the same location. Hence, a cache using only MSI first asks for read-only access on the bus, which puts the cache line in the Shared state. However, then a write is performed and thus, the controller must ask for write permissions on the bus. Observe that this adds additional latency to the write instruction even though the cache technically already contains the cache line which causes needless traffic on the bus. The goal of the *Exclusive* state is to resolve this issue. The memory controller explicitly keeps track of whether some cache currently has read-only-access to a specific cache line, which is not relevant in the MSI protocol (it must only know whether a cache has write permissions). Hence, once a cache requests read-only permission and the controller knows that no other cache currently has access to the same line, the controller explicitly informs the requester that it is currently the only user of this cache line. Thus, the cache may put the line in the *Exclusive* state. The advantage now is that once the CPU writes to the location, it may silently upgrade the cache to the *Modified* state without consulting the bus. However, this also means that if a cache evicts a line in the *Exclusive* state, it must explicitly notify the memory controller on the bus. The reason is that the latter cannot distinguish between whether a cache line is in an *Exclusive* or *Modified* state due to the cache having the ability to silently upgrade the line.

**MOSI**: This protocol adds the *Owned* state to the FSM. We briefly explain the motivation: When a cache has a cache line in the *Modified* state and another core requests read-only access, the cache downgrades the state to *Shared* and has to send the data to both the requester as well as to the memory controller. The reason is that the *Modified* state implies ownership of the data. By downgrading its own state to *Shared*, the ownership gets lost and thus, it is vital to explicitly transfer the data to the memory controller. Observe the following potential issues: The cache might need to send the data twice, depending on whether caches and memory controller are connected to the same bus  $[NSH^+20]$ , p. 128]. Furthermore, the memory must be frequently accessed. These disadvantages are avoidable by keeping the ownership information: Recall that the *Modified* state implies ownership. Thus, if another cache requests read-only access, the cache line downgrades to the *Owned* state. It is now also read-only but dirty. This means our cache keeps ownership information and only if eviction of this cache line is required, the cache controller needs to explicitly write the data back to the memory controller.

**MOESDIF**: This is the protocol mentioned in the amd64 programmer reference Adv24a p. 192]. The additional letters **D** and **F** refer to *Dirty* and *Forward* respectively. The former is similar to the *Exclusive* state as the cache line is also read-only and can be upgraded to *Modified* without consulting the interconnection first. However, the cache line in the *Exclusive* state is clean, while this is not the case for *Dirty*. In case of an

eviction, both states mandate the cache to notify the other entities but the *Dirty* state additionally requires the cache line to be sent back to memory. The *Forward* state is a microarchitectural optimization. Considering a simple **MSI** protocol, a read request must be handled by the directory or memory controller. Thus, data is fetched from memory, even though another cache might already have the same cache line which could provide the data much faster. The *Forward* state allows a cache to respond to a read request from another entity.

#### 2.2.3 Write/Store Buffers

In the previous section, we discussed how caches reduce latency of memory accesses while keeping coherence. We want to highlight another hardware technique that is relevant for the topics discussed in this thesis. As described in the previous sections, writing to memory can be quite costly, even when using a write-back cache. Recall that in order to write data the cache needs to request write permissions from the memory controller. This state is exclusive unlike read-only access, where multiple threads may share the same memory region at the same time. Thus, if multiple writers need to write to the same location, they need to constantly take each other's permissions to access the line. The AMD64 Programmer's manual mentions that writes may also stall memory reads, presumably due to limited ports to the memory, which can potentially stall the entire execution pipeline Adv24a, p. 202]. The system can reduce the impact of said situations using a write or store buffer. When executing a store, the value is not sent to the cache directly, but instead stored in the write buffer. In fact, the cache does not even require to contain the affected memory region. The actual store occurs at a later point for several reasons, such as when the store buffer is full. This might raise the question whether a store buffer simply defers the problem to a later time because the system has to commit to memory at some point anyway. In essence, the question is valid but deferring to a later point may have several advantages: For example, the system can commit all stores at the same time which can be more efficient, especially when there are several stores affecting the same cache line. In addition, the system might write back values step-by-step if it observes that memory/cache contention is low at the moment. Hence, as long as the CPU generates less writes than the write buffer can commit to memory, the latency of a store can be completely eliminated [PH17, p. 769]. In addition, consider a thread writing to the same location as a previous store that is still contained in the buffer. The write buffer can simply overwrite the value of a previous store to the same location, reducing the amount of writes that actually have to be committed to the cache and memory. This optimization is called **write coalescing**.

An important question to consider is how write buffers affect the correctness of a multicore system. Recall that a cache coherence protocol is actually necessary to maintain assumptions of a memory-only system. Take a system where each core has a private store buffer. In a single-threaded context and for true dependencies (read-after-write), if the write has not yet been committed to memory, the read returns the value from the buffer. This mechanism is called **store forwarding** [TA13]. For a multi-threaded environment,

|    | Thread 1 |    | Thread 2 |  |  |

|----|----------|----|----------|--|--|

| 1: | x = 1    | 1: | r1 = y   |  |  |

| 2: | y = 1    | 2: | r2 = x   |  |  |

Figure 2.4: Litmus test,  $\times$  and  $\gamma$  are initialized to 0. [MHAM11]

|    | Thread 1    |    | Thread 2                               |

|----|-------------|----|----------------------------------------|

| 1: | x = 1       | 1: | <pre>while(flag == false) goto 1</pre> |

| 2: | flag = true | 2: | r1 = x                                 |

Figure 2.5: Litmus test, × and flag are initialized to 0 and false respectively. [MHAM11]

| Cycle | Thread 1    | Thread 2                        | Coherence State of $x$ | Coherence State of flag |

|-------|-------------|---------------------------------|------------------------|-------------------------|

| 1     | flag = true |                                 | Read-only for 2        | Read-Write for 1        |

| 2     |             | <pre>while(flag == false)</pre> | Read-only for 2        | Read-only for 2         |

| 3     |             | r1 = x                          | Read-only for 2        | Read-only for 2         |

| 4     | x = 1       |                                 | Read-Write for 1       | Read-only for 2         |

Figure 2.6: Possible cache coherent execution of litmus test 2.5. Thread 2 reads flag = true at cycle 2 and x = 0 at cycle 3. Taken from [NSH<sup>+</sup>20].

consider the example in Figure 2.3, which we used to explain the motivation behind cache coherence protocols. Thread 2 may only continue if it sees  $A \neq 0$ . When thread 1 stores A = 1 to its private write buffer, the value is not yet visible to 2. Nevertheless, the value must be committed to cache or memory eventually, making it visible to all threads. However, Section 2.2.1 explains how cache coherence protocols are an abstraction over a memory-only system and hence, cache coherence still preserves a total order over all memory accesses. But since write buffers are private to each core, a core observes its own writes before other hardware threads in the system. Therefore, each core might observe a different order of loads and stores. Whether a certain order is allowed depends on the memory consistency model specified by the ISA. Refer to Section 2.3 for more information.

#### 2.3 Memory Consistency Model

It might seem that cache coherence is sufficient to model multi-threaded programs. Consider the example in Figure 2.4: We are interested in the possible values of r1 and r2. Needless to say, the result depends on the order of execution which is non-deterministic in a parallel environment. The obvious cases are r1 = r2 = 0 and r1 = r2 = 1 where thread 2 has executed its code before thread 1 and vice versa respectively. Another possible execution is that thread 1 runs Line 1, then thread 2 executes its program and then thread 1 continues to execute Line 2 which yields  $r1 = 0 \wedge r2 = 1$ . What might come as a surprise is that  $r1 = 1 \wedge r2 = 0$  is also a possible result. The reason is that modern hardware, thanks to out-of-order execution, can decide to reorder the store at Line 1

of thread 1 after Line 2 which is valid from an isolated single-threaded perspective. Of course, one might argue that this example is impractical because the program relies on non-deterministic behavior even when assuming every line is executed in-order. Consider a more practical example in Figure 2.5. Thread 2 loops endlessly while a flag is equal to *false*. This flag could represent several practical scenarios such as a mutex to a resource or notifying another thread that new data is available for further processing. Taking the latter case, thread 2 is supposed to see the newly available data once it gets notified via the flag. However, Figure 2.6 shows a valid cache-coherent execution which yields r1 = 0.

Observe that a cache coherence protocol is a way to hide the abstraction over the memory subsystem in order for the caches to behave like a cacheless system [NSH<sup>+</sup>20] p. 21]. However, it does not specify how memory accesses to different locations are related to each other. This is where the **memory consistency model** or just **memory model** comes into affect. A memory model describes all possible values for a certain input that reading from memory can yield. These results are called MC executions [NSH<sup>+</sup>20]. Unlike in a deterministic single-threaded environment, there can be multiple options, similarly to the example given in Figure 2.4. Example models are sequential consistency (SC), total store order (TSO), the C11 Memory Model or Linux Kernel Memory Model (LKMM). Observe that a memory consistency model exists for both hardware and software. When translating from one model to another, the compiler or tool must ensure that the target model disallows all executions forbidden by the source model. The target model might be stronger in the sense that it disallows more executions than the source model. Consider an example of compiling C code using C11 atomics to the RISC-V architecture. First of all, the compiler must ensure to reorder reads and writes only as long as it does not violate the C11 memory model. However, this might not be sufficient because the hardware's weaker model allow it to reorder these operations during execution. Therefore, the compiler needs to insert special fence or barrier instructions at certain points. We introduce these instructions in Section 2.3.4.

Memory models can be formally defined. There exist several methods which can be divided into operational or axiomatic models [AMT14]. Some [ISAs] use these tools to model their architecture's memory behavior such as RISC-V [RIS19] p. 191]. However, a lot of formalism can be hard to understand and hence, vendors often also supply so-called **litmus tests**. These are small multithreaded code snippets that explain what outcomes are allowed and what are not [NSH+20], p. 262]. Figures 2.4 and 2.5 show simple examples for litmus tests.

#### 2.3.1 Sequential Consistency

Sequential consistency (SC) was originally defined by Lamport [Lam79] and consists of two properties:

1. Each read and write must be committed in the order defined by the program (also called program order).

#### 2. All memory operations are serviced via a single FIFO-queue.

The second property implies an interesting observation: There exists a single global view on memory and hence, all threads see all memory operations in the same order. In other words, consider every pair of loads-loads, loads-store, store-load and store-store occurring in the program (program order). SC ensures that all threads observe these pairs in the same order. While being very strict, it is also the most intuitive to understand. The result of these properties is that sequential consistency only allows executions which are formed by some combined sequential execution. Considering our litmus test from Figure 2.4, the result  $r1 = 1 \land r2 = 0$  is disallowed by SC. The load from y must happen before the load from x by property (1). r1 = 1 and r2 = 0 implies that y = 1 happens before x = 1, considering that both variables are initialized with 0. However, this yields a contradiction because y = 1 before x = 1 does not respect the program order of thread 1.

#### 2.3.2 Total Store Order

Another common memory model is total store order (TSO), provided by x86 for example. In general, TSO is quite similar to SC with one notable exception: A load may be reordered before a store unless the store-load pair accesses the same memory location because TSO must still preserve read-after-write dependencies. Thus, threads can observe their own write operations before other threads. However, once a write becomes globally visible, all other threads observe the same order [NSH<sup>+</sup>20, p. 39-44]. One might ask what benefits does TSO have over SC since the differences are rather subtle. The important aspect is that allowing loads to be reordered before a store enables the use of a FIFO write buffer, explained in Section 2.2.3. Thus, writes do not need to be committed to cache/memory immediately which can improve throughput. Note that the buffer may not use write-coalescing as TSO still needs to preserve store-store order unless the implementation can guarantee the preservation via some other mechanism.

#### 2.3.3 Weak/Relaxed Memory Model

There exists no general notion of a weak memory model, but more like a family of weak memory models. SC and TSO are often called 'strong' memory models because they still preserve per-thread memory operations [NSH+20], p. 55]. Weaker or relaxed memory models allow both the hardware and the compiler to more aggressively optimize code execution. However, when certain orderings are required, additional fence instructions must be inserted which might not be necessary on an architecture such as x86. RISC-V, ARMv8 and IBM Power are prominent examples for having variations of more relaxed memory models. Even among them, the strength of their respective memory model varies. For instance, RISC-V provides multi-copy atomicity, ARMv8 defines its architecture as 'other-multi-copy atomic' and IBM Power does neither [RIS19],[Arm21],[Ope21]. Multi-copy atomicity and other-multi-copy atomicity describe that all writes, once they are globally visible, are observed in the same order by all threads. However, threads may see their own writes in a different order in order to preserve program order [Arm21], [RIS19], p.

(1) li t1, 1

(2) sw t1, 0(s0)

(3) fence

(4) sw t1, 0(s1)

Figure 2.7: Example of a memory fence in the RISC-V ISA. Code snippet from the "PPOCA" store buffer forwarding litmus test [RIS19, p. 166].

B2-224, p. 185]. This property is inherently fulfilled by TSO (see Section 2.3.2) but for instance, the memory model of RISC-V still allows write coalescing or write reorderings which would be forbidden under TSO.

The Power ISA is an interesting case which does not enforce multi-copy atomicity. Thus, different threads may observe reads and writes in different orders and hence, there exists no global order of memory operations. On the one side, this makes writing parallel software more difficult because developers and compilers need to be more explicit about when synchronization is required. On the other side, microarchitecture designers have more freedom to speed up execution. For instance, multi-copy atomicity essentially enforces that a write buffer must be private to each thread (at least from a behavioral perspective). However, a Power core is allowed to read a value from another core's write buffer before it is committed to global cache/memory. This leads to a situation where a thread may observe memory operations in a different order than other cores.

#### 2.3.4 Memory Fences

In the previous section, we introduced several common memory models used by more popular ISAs. This helps us understand how a core may reorder loads and stores as well as how they are observed by other threads. But what if the memory model of the hardware does not provide sufficient guarantees for a particular algorithm? In order to enforce stronger constraints, ISAs provide so-called **memory fences**. As the name might imply, a fence instruction ensures that all memory-related operations occurring before the fence in program order are observed before the ones occurring after the fence in program order. For instance, consider the code snippet in Figure 2.7. (3) shows the use of a fence instruction as provided by RISC-V. Assume that 0(s0) and 0(s1) are both initialized to 0 and correspond to different memory locations. Without a fence, the memory model of RISC-V would allow another core to observe the store of (4) before (2). The fence ensures that (2) is always observed before (4). On a side note, an analogous example for x86 does not require a memory fence because TSO implicitly preserves store-store ordering.

Depending on the strength of the consistency model of an **ISA**, different types of fences might be provided. This is particularly the case for architectures with weaker memory models because depending on the situation, a full memory fence might not be necessary. For instance, the RISC-V instruction fence w, w prevents any write after the fence to be observed before a write before the fence. However, loads may still be reordered freely across the fence. This might reduce the performance impact of an explicit synchronization when a complete order preservation is not actually required.

#### 2.4 Atomic Instructions

A multicore CPU requires synchronization primitives in order to allow software developers to implement parallel algorithms. The most common family of instructions are readmodify-write (RMW) operations, such as fetch-and-add (FAA) or compare-and-swap (CAS). While these instructions consist of multiple steps, atomicity guarantees that all these steps appear to other threads as if they were executed in a single step. The question is what instructions are sufficient to implement parallel algorithms? This requires a formal way to assess the power of an atomic operation. The consensus problem states that multiple threads propose a value each and then, need to agree on one of those values. An algorithm solving the consensus problem is called a consensus protocol. We specifically focus on wait-free protocols because implementing a parallel wait-free algorithm requires that the atomic primitives of the CPU are wait-free themselves. An algorithm is wait-free if all threads finish execution in a finite number of steps. Next, the consensus number assesses the strength of a consensus protocol. This number corresponds to how many threads are able to agree on one of their proposed values. For instance, a consensus number of two states that the algorithm can only agree on a value for at most two threads. Three or more threads are not supported. Note that the consensus number can be infinite in which case there is no limit for how many threads the consensus protocol can decide upon at most [HSLS20].

Most interestingly, atomic registers are proven to have a consensus number of one. Informally, consider two threads A and B deciding on the value. The question is how can the system determine which thread accessed the register first? Consider the case where A reads from the register and B also executes an operation (either a read or write). There exist two possibilities: In the first one, B executes its operation first and hence, it won the consensus. In the other one, A reads first, then B applies its operation and thus, A won the consensus. However, both scenarios are indistinguishable to B because the side effect of A reading from the shared register is not visible to B. There are also other cases which need to be formally considered, however, the argument is similar, namely that neither thread cannot differentiate the outcome. Therefore, atomic registers have consensus number of one. Thus, even if one was to built a CPU with shared registers between cores, simple loads and stores to those registers would not suffice for implementing parallel algorithms. This shows the need for dedicated atomic instructions. Let us consider the family of RMW operations, such as a FAA operation. This operation has a consensus number of exactly two. Very informally, consider a protocol where each thread stores its proposed value in an array where the id of the thread corresponds to the index in the array. Next, a decision variable is initialized to zero and each thread increments the value via a FAA, Recall that a FAA returns the current value and atomically increments the value by one in the memory. The thread loading the value zero has won the consensus, while all other threads, which must receive a non-zero value by definition of a FAA, have

```

cas:

#Load value from memory

lr.w t0, (a0)

bne t0, a1, fail

# a1 contains expected value

sc.w t0, a2, (a0)

# Try to update. a2 contains new value

bne t0, cas

# Retry if store-conditional failed

# Indicate success as return value

li a0, 0

# Return

jr ra

fail:

li a0, 1

# Indicate failure as return value

# Return

jr ra

```

Figure 2.8: Example for a CAS function using LR/SC instructions provided by RISC-V ISA. Code snippet from [RIS19, p. 50].

lost and thus, the winning thread's value will be chosen. In case of two threads, the losing thread clearly knows who the winning thread is because the array has size two and one element belongs to the losing thread and thus, the other remaining element must contain the decided value. However, in the case of more than two threads, the losing threads cannot determine which thread won the consensus. Thus, FAA only has consensus number two.

Finally, let us consider a CAS operation. A CAS has three operands, an address, an expected value and an updated value. First, the currently stored value is loaded from the given address and compared to the expected value. Next, if they match, the CPU stores the updated value at the same address. All of this happens atomically. We construct a consensus protocol based on a CAS A decision variable x is initialized to zero. Next, each thread proposes its value in an array where the thread id corresponds to the index in the array. Each thread tries to exchange the value stored at x with its own thread id. Note that we assume that there cannot be a thread with an id zero. Only one thread will be able to replace the initial value stored at x, which is the winning thread. All other threads see the winning thread's id so they also know which thread won the consensus. Thus, the consensus number is infinite, assuming that integers are unbounded.

Finally, we want to introduce universality: A primitive is universal if and only if it is powerful enough to support arbitrary wait-free algorithms. An operation with consensus number n is universal for a system with at most n processes [Her91], p. 125]. Thus, we can conclude that a compare-and-swap operation is sufficient to implement parallel algorithms for any system. ARMv8 and amd64 provide dedicated instructions called CAS and CMPXCHG respectively. The former is atomic by default, while the latter requires a LOCK prefix [Adv24b], Arm21]. While these instructions would be sufficient in theory and thus, can be used to implement other [RMW] operations such as [FAA], most [ISAs still provide dedicated fetch-and-add, fetch-and-and, etc. instructions, presumably for performance reasons as they are often required in practice.

Some architectures, most notably RISC-V, Power and ARMv8, support even more

powerful primitives called load-reserve (other names include load-exclusive or load-link) and store-conditional (also named store-exclusive) [Arm21, RIS19, Ope21]. We continue with load-reserved (LR) and store-conditional (SC) but the other names can be used interchangeably. An LR instruction loads a value from memory and additionally creates a reservation. A store-conditional stores a value to memory if and only if such a reservation to the specified address exists. This reservation is cleared by stores from the same or other threads but may also be cleared spuriously e.g. due to a context switch. Observe that this functionality can be used to implement a compare-and-swap and other RMW operations such as for RISC-V in Figure 2.8. The question might arise why such a more verbose construction is required if a CAS already provides an infinite consensus number? LR/SC is popular for RISC architectures because they might not have an instruction format for three source operands such as RISC-V [RIS19, p. 48]. Another reason is that, albeit being the same consensus class, LR/SC is slightly more powerful than a CAS because it does not suffer from the ABA-problem [HSLS20, p. 244]. An ABA-problem occurs in the following situation: Suppose thread 1 loads value A from location a and then, pauses before applying a CAS to exchange it for some other value. In the meantime, thread 2 runs and applies the CAS to exchange A for B at location a. Next, it runs another CAS to exchange B back to A. Next, thread 1 continues with its [CAS] which succeeds because the stored value is still A as expected for thread 1, even though the stored value A does not correlate with the value A that was originally loaded by thread 1. However, if the code used a LR/SC pair to conduct the exchange, thread 1's operation will fail because another store was executed between its load and the store-conditional. ABA-issues commonly occur in memory management scenarios where internal data structures are recycled for reuse [HSLS20, p. 241].

Recall that when an LR-like instruction is executed, the core makes a reservation of the given address. Note that the hardware usually does not remember the entire address but ignores some least-significant bits. Thus, a single reservation covers an entire memory region and the size is defined by the reservation granule [Ope21], p. 1049]. Thus, as long as the address of a subsequent conditional store translates to the same reservation region, the store will succeed albeit the address not being equal. The reservation granule can vary between MiAs [Arm21], p. B2-312] [Ope21], p. 1049].

#### 2.5 Virtual Address Space and Address Translation

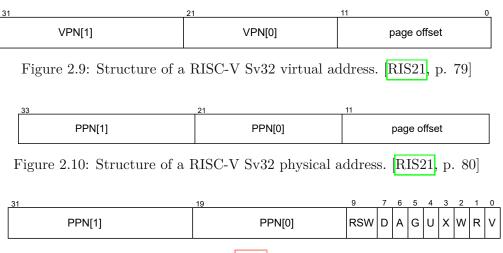

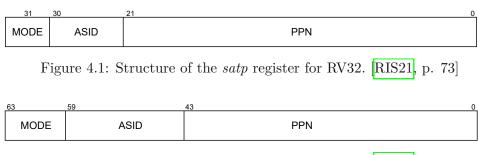

When user space programs access memory on modern systems, the addresses do not correspond to physical addresses of the real memory. Instead, they work with virtual addresses which get translated into physical addresses on access. Similarly to how a cache is organized in cache lines, physical addresses are separated into pages. The mapping is defined by a page table which is usually unique for each user space process. Usually, a dedicated register holds the address to the beginning of the current page table. The upper bits of a virtual address are then mapped to a physical address while the remaining bits designate the offset within the page [RIS21], p. 79]. Using a virtual address space has many advantages:

Figure 2.11: Structure of a RISC-V Sv32 PTE. The field RSW is reserved for software. Flags are dirty D, accessed A, global G, accessible to user mode U, execute X, write W, read R and valid V. [RIS21, p. 80]

- Address space separation: The virtual address space differs for each process, providing some degree of isolation between multi processes. For instance, this prevents one process to maliciously or unintentionally modify the memory of another process, potentially corrupting it. [PH17, p. 819]

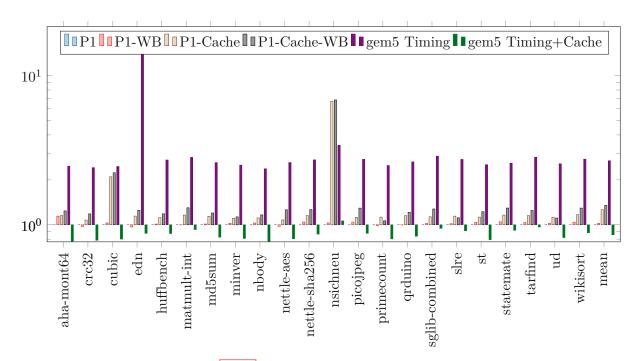

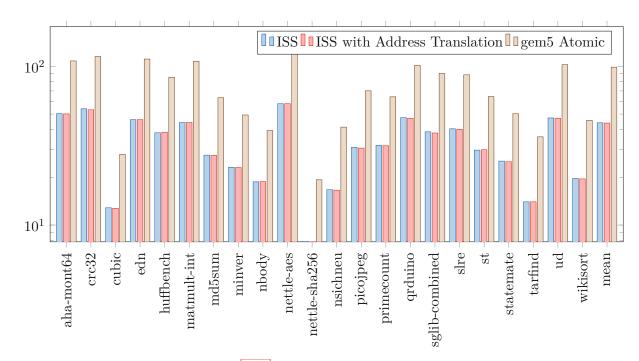

- Physical memory management: Since the mapping can be freely configured by the operating system, pages in the physical memory can be freely moved around. Furthermore, operating systems employ a technique called 'swapping', allowing to store less frequently used pages on the hard disk in order to use the memory for other purposes. [PH17, p. 829]