Contents lists available at ScienceDirect

# Nonlinear Analysis: Hybrid Systems

journal homepage: www.elsevier.com/locate/nahs

#

Arman Ferdowsi <sup>a</sup>,<sup>\*</sup>, Matthias Függer<sup>b</sup>, Thomas Nowak<sup>b,c</sup>, Ulrich Schmid<sup>a</sup>, Michael Drmota<sup>d</sup>

<sup>a</sup> TU Wien, Embedded Computing Systems Group, Austria

<sup>b</sup> LMF, Université Paris-Saclay, CNRS, ENS Paris-Saclay, France

<sup>c</sup> Institut Universitaire de France, France

<sup>d</sup> TU Wien, Institute of Discrete Mathematics and Geometry, Austria

# ARTICLE INFO

Keywords: Thresholded hybrid systems Circuit verification Continuity Composition Dynamic timing analysis Faithfulness

# ABSTRACT

Thresholded hybrid systems are restricted dynamical systems, where the current mode, and hence the ODE system describing its behavior, is solely determined by externally supplied digital input signals and where the only output signals are digital ones generated by comparing an internal state variable to a threshold value. An attractive feature of such systems is easy composition, which is facilitated by their purely digital interface. A particularly promising application domain of thresholded hybrid systems is digital integrated circuits: Modern digital circuit design considers them as a composition of Millions and even Billions of elementary logic gates, like inverters, OR and AND. Since every such logic gate is eventually implemented as an electronic circuit, however, which exhibits a behavior that is governed by some ODE system, thresholded hybrid systems are ideally suited for making the transition from the analog to the digital world rigorous.

In this paper, we prove that the mapping from digital input signals to digital output signals is continuous for a large class of thresholded hybrid systems. Moreover, we show that, under some mild conditions regarding causality, this continuity also continues to hold for arbitrary compositions, which in turn guarantees that the composition faithfully captures the analog reality. By applying our generic results to some recently developed thresholded hybrid gate models, both for single-input single-output gates like inverters and for a two-input CMOS NOR gate, we show that they are continuous. Moreover, we provide a novel thresholded hybrid model for the two-input NOR gate, which is not only continuous but also, unlike the existing one, faithfully models all multi-input switching effects.

# 1. Introduction

The behavior of *thresholded hybrid systems* is governed by the dynamics of a continuous process, described by some system of *ordinary differential equations* (ODEs), which is selected according to externally supplied digital mode switch signals from a set of

# https://doi.org/10.1016/j.nahs.2024.101572

Available online 6 January 2025

$<sup>\</sup>stackrel{i}{\sim}$  This research has been supported by the Austrian Science Fund (FWF) project DMAC (10.55776/P32431) and the French National Research Agency (ANR) projects DREAMY (ANR-21-CE48-0003) and COSTXPRESS (ANR-23-CE45-0013). For open access purposes, the author has applied a CC BY public copyright license to any author accepted manuscript version arising from this submission.

<sup>\*</sup> Corresponding author.

*E-mail addresses:* aferdowsi@ecs.tuwien.ac.at (A. Ferdowsi), mfuegger@lmf.cnrs.fr (M. Függer), thomas@thomasnowak.net (T. Nowak), s@ecs.tuwien.ac.at (U. Schmid), michael.drmota@tuwien.ac.at (M. Drmota).

Received 24 February 2024; Received in revised form 8 December 2024; Accepted 19 December 2024

<sup>1751-570</sup>X/© 2025 The Authors. Published by Elsevier Ltd. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/).

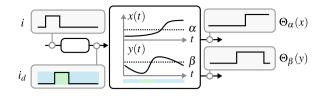

**Fig. 1.** Thresholded mode-switched ODE with a single mode input *i*, the delayed input  $i_d$ , two continuous states *x*, *y*, and two thresholded outputs  $\Theta_a(x)$  and  $\Theta_\beta(y)$ .

candidates, and controls some digital outputs based on whether some internal signals are above or below a threshold, see Fig. 1 for an illustration. Thresholded hybrid systems can be found in various application areas, including digitally controlled thermodynamic processes, hydrodynamic systems, and, in particular, digital integrated circuits. Consider a simple digitally controlled heating system, for example: The continuous dynamics of the room temperature would be governed by some ODE for the case when the heating is switched on, and another ODE for the case where the heating is switched off. A binary mode switch input signal tells whether the heating is switched on or off. Two binary output signal, low resp. high, report on whether the current room temperature is below 20 degrees resp. above 23 degrees. A simple digital bang–bang controller could be used to switch the heating on when low makes a transition from 0 to 1, and to switch it off when high makes such a transition.

In this paper, we will study properties of such thresholded hybrid systems, and systems built from those via arbitrary composition, i.e., where the digital output signal of one component drives a mode switch signal of one or more other components, possibly forming some feedback loops. First and foremost, we will give conditions that ensure the continuity of the outputs of such systems with respect to their external inputs. This continuity property guarantees that small timing variations of the digital input signals lead to small variations of the digital output signals only. Moreover, we will show that, under some mild constraints regarding causality, any finite composition of continuous thresholded hybrid systems is continuous, and faithfully models the analog reality.

Whereas our continuity results are independent of the particular application area, we will tailor our presentation primary to digital integrated circuits. Indeed, digital circuits are a particularly important class of systems composed of thresholded hybrid systems, modeling elementary logic gates like inverters, OR, and AND, which will be called *digitized hybrid gates* in the sequel. The application of our generic results will reveal that thresholded hybrid systems are indeed ideally suited for making the transition from the analog implementation to the digital abstraction in modern digital circuit design rigorous.

*Digital circuit modeling basics.* Modern digital integrated circuits consist of Millions and sometimes Billions of transistors, which are analog electronic devices and thus process and generate analog signals. Modern digital circuit design, on the other hand, considers a circuit as a composition of elementary digital logic gates, and leaves it to (quite complex) tools to compile a design down to its analog implementation.

In view of the very short design cycles nowadays, developers cannot afford to repeatedly downcompile a design to verify its correctness and performance. Fast *digital* functional verification and timing analysis techniques and tools are hence key elements of modern circuit design. In particular, thanks to the elaborate static timing analysis techniques available today, like CCSM [1] and ECSM [2], worst-case critical path delays can be determined very accurately and very quickly, even for very large circuits. Whereas such corner-case delay estimates are sufficient for synchronous circuit designs, which are still the vast majority nowadays, analyzing the behavior of specific asynchronous circuits, like the one described in [3], or inter-neuron links using time-based encoding in hardware-implemented spiking neural networks [4], require more elaborate timing analysis techniques.

More specifically, consider the token-passing ring studied by Winstanley et al. in [3], which is composed of stages consisting of a 2-input Muller C gate with its inputs connected to the preceding and succeeding stages. The authors demonstrated that this ring implements an oscillator, which exhibits two distinct modes of operation: burst behavior and evenly spaced output transitions, which can alternate over time in an unpredictable (chaotic) fashion. In order to predict the actual behavior of this circuit, it is essential to track the timing relationships of *individual* transitions across the entire ring. Since static timing analysis techniques cannot accomplish this, *dynamic* timing analysis techniques need to be resorted to.

The golden standard for dynamic timing analysis are analog simulations, e.g., using SPICE [5], applied to a (usually manufacturersupplied) ODE model of the entire circuit. Since such numerical analog simulations are prohibitively time-consuming even for small circuits and short signal traces, *digital* dynamic timing analysis techniques have been invented as a less accurate but much faster alternative. They rest on fast and efficiently computable *gate delay models* like pure or inertial delays [6], which provide input-tooutput delay estimations for every gate. The resulting dynamic timing analysis techniques enable efficient correctness validation of large circuits, as well as precise performance and power estimations, even during early design stages [7].

The simplest non-trivial<sup>1</sup> digital delay models suitable for accurate dynamic timing analysis are *single-history delay models*. In fact, since the delay for a given signal transition of a real gate is also dependent on the previous transition(s), in particular, when they are close, single-history delay models like [8–10] assume that the input-to-output delay  $\delta(T)$  of a gate also depends on the previous-output-to-input delay *T*.

<sup>&</sup>lt;sup>1</sup> In our context, the widely known pure and inertial delay models [6], which exhibit little to no history dependency, must be considered trivial.

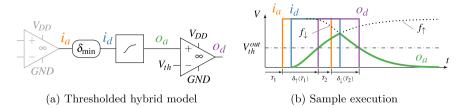

Fig. 2. A digitized hybrid gate model (for a non-inverting buffer) satisfying the involution property and a sample execution. Source: Adapted from [10].

It has been proved by Függer et al. [8,10] that *continuity* is mandatory for any single-history model of a gate to faithfully represent the analog reality. Continuity ensures, for example, that a constant-low input signal and an arbitrarily short low-high-low pulse lead to very similar gate output signals. Note that this continuity property also implies continuity of the output signal power w.r.t. the input signal power, since the square of a signal is proportional to its power. Consequently, continuous delay models are the most promising candidates for the timing and power-accurate simulation of digital circuits [7].

So far, the only delay model that is known to ensure continuity is the *involution delay model* (IDM) [10], which consists of zero-time Boolean gates interconnected by single-input single-output involution delay channels. An IDM channel is characterized by a delay function  $\delta$  that is a negative involution, i.e.,  $-\delta(-\delta(T)) = T$ . In its generalized version, different delay functions  $\delta_{\uparrow}$  resp.  $\delta_{\downarrow}$  are assumed for rising resp. falling transitions, requiring  $-\delta_{\uparrow}(-\delta_{\downarrow}(T)) = T$ .

It has been shown already in [10] that involution delay functions arise naturally in the 2-state thresholded hybrid model illustrated in Fig. 2, which consists of a pure delay component, a slew-rate limiter with a rising and falling switching waveform, and an ideal comparator: The binary-valued input  $i_a$  is delayed by some  $\delta_{\min} > 0$ , which assures causality, i.e.,  $\delta_{1/4}(0) > 0$ . At every transition of  $i_d$ , the slew-rate limiter switches to the corresponding waveform ( $f_4/f_1$  for a falling/rising transition), thereby ensuring that the resulting analog output voltage  $o_a$  is a *continuous* (but not necessarily smooth) function of time. Finally, the comparator generates the output  $o_d$  by digitizing  $o_a$  w.r.t. the discretization threshold voltage  $V_{th}$ .

It is hence probably not too surprising that the involution property itself guarantees continuity also at the level of digital signals, which in turn is the key to proving that the IDM allows to solve the canonical *short-pulse filtration problem* (see Section 4.2) exactly as it is possible with real circuits. Note that the IDM also allows to incorporate substantial delay noise, PVT variations, and aging without compromising faithfulness [11,12].

The IDM also comes with a publicly available simulation framework, the *Involution Tool* [13], which allows to simulate circuits composed of gates for with an IDM model has been provided. It also facilitates the evaluation of the accuracy of IDM delay predictions against SPICE-generated data and other delay models. Whereas the accuracy of IDM predictions for single-input, single-output circuits like inverter chains or clock trees turned out to be very good [13], this is less so for circuits involving multi-input gates. It has been revealed by Ferdowsi et al. [14] that this is primarily due to the IDM's inherent inability to properly cover output delay variations caused by *multiple input switching* (MIS) effects, also known as *Charlie effects*, where different inputs switch in close temporal proximity [15]: compared to the *single input switching* (SIS) case, output transitions may be sped up/slowed down with decreasing transition separation time on different inputs. Since circuit models based on single-input, single-output delay channels like IDM inherently cannot model MIS effects, generalized delay models like the ones presented in Section 5 are needed for the accurate digital modeling of multi-input gates.

#### Detailed contributions.

- (1) We show that any thresholded hybrid model, where mode *m* is governed by a system of first-order ODEs  $\frac{dx}{dt} = F_m(t, x)$ , leads to a continuous digital delay model, provided all the  $F_m$  are continuous in *t* and Lipschitz continuous in *x*, with a common Lipschitz constant for every t > 0 and *m*.

- (2) We carry over our general continuity property to digitized hybrid gates.

- (3) We prove that the parallel composition of finitely many digitized hybrid gates in a circuit result in a unique and Zeno-free execution, under some mild conditions regarding causality. Moreover, we prove that the resulting model is faithful w.r.t. solving the canonical short-pulse filtration problem, provided all involved digitized hybrid gates are continuous.

- (4) We introduce the intricacies caused by MIS effects in multi-input gates, and show that the digitized hybrid model for CMOS NOR gates proposed in [14] is continuous.

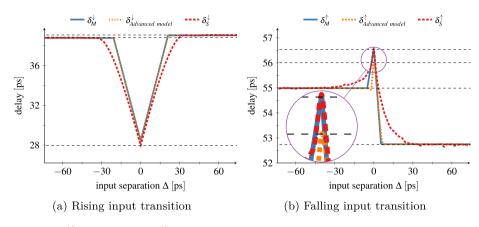

- (5) We revisit the advanced digitized hybrid model for CMOS NOR gates presented in [16], which covers all MIS effects. We prove that it is continuous, and derive an accurate approximation of its delay function based on explicit solutions of the underlying ODEs.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup> Note that the present paper actually combines and extends both the HSCC'23 paper [17] (where we presented our continuity proof) and the ICCAD'23 paper [16] (where we presented our advanced model for the NOR gate), with the important difference that we replace the complicated approximation of the ODE solutions used in [16] by the recently found explicit solutions, which results in much simpler and more accurate delay formulas and an explicit model parametrization procedure that avoids any fitting.

(1)

*Paper organization.* In Section 2, we instantiate our general continuity result (Theorem 6). Section 3 presents our main continuity results for digitized hybrid gates (Theorems 7 and 8), and Section 4 deals with circuit composition and faithfulness of composed models. In Section 5, we introduce MIS effects in multi-input gates and apply our continuity and faithfulness results to existing digitized hybrid models [10,14]. In Section 6, we provide our novel analysis of the advanced model introduced in [16]. Some conclusions are provided in Section 7.

# 2. Thresholded mode-switched ODEs

In this section, we provide a generic proof that every hybrid model that adheres to some mild conditions on its ODEs leads to a continuous digital delay model. We start with proving continuity in the analog domain and then establish continuity of the digitized signal obtained by feeding a continuous real-valued signal into a threshold voltage comparator. Combining those results will allow us to assert the continuity of digital delay channels like the one shown in Fig. 2.

# 2.1. Continuity of ODE mode switching

For a vector  $x \in \mathbb{R}^n$ , denote by ||x|| its Euclidean norm. For a piecewise continuous function  $f : [a, b] \to \mathbb{R}^n$ , we write  $||f||_1 = \int_a^b ||f(t)|| dt$  for its 1-norm and  $||f||_{\infty} = \sup_{t \in [a,b]} ||f(t)||$  for its supremum norm. The projection function of a vector in  $\mathbb{R}^n$  onto its *k*th component, for  $1 \le k \le n$ , is denoted by  $\pi_k : \mathbb{R}^n \to \mathbb{R}$ .

In this section, we will consider non-autonomous first-order ODEs of the form  $\frac{d}{dt}x(t) = f(t, x(t))$ , where the non-negative  $t \in \mathbb{R}_+$  represents the time parameter,  $x(t) \in U$  for some arbitrary open set  $U \subseteq \mathbb{R}^n$ ,  $x_0 \in U$  is some initial value, and  $f : \mathbb{R}_+ \times U \to \mathbb{R}^n$  is chosen from a set F of bounded functions that are continuous for  $(t, x) \in [0, T] \times U$ , where  $0 < T < \infty$ , and Lipschitz continuous in U with a common Lipschitz constant for all  $t \in [0, T]$  and all choices of  $f \in F$ . It is well-known that every such ODE has a unique solution x(t) with  $x(0) = x_0$  that satisfies  $x(t) \in U$  for  $t \in [0, T]$ , is continuous in [0, T], and differentiable in (0, T).

The following lemma shows the continuous dependence of the solutions of such ODEs on their initial values. To be more explicit, the exponential dependence of the Lipschitz constant on the time parameter allows temporal composition of the bound. The proof can be found in standard textbooks on ODEs [18, Theorem 2.8].

**Lemma 1.** Let  $U \subseteq \mathbb{R}^n$  be an open set and let  $f : \mathbb{R} \times U \to \mathbb{R}^n$  be Lipschitz continuous with Lipschitz constant K for  $t \in [0, T]$  with T > 0, and let  $x, y : [0, T] \to U$  be continuous functions that are differentiable on (0, T) such that  $\frac{d}{dt}x(t) = f(t, x(t))$  and  $\frac{d}{dt}y(t) = f(t, y(t))$  for all  $t \in (0, T)$ . Then,  $||x(t) - y(t)|| \le e^{tK} ||x(0) - y(0)||$  for all  $t \in [0, T]$ .

A step function  $s : \mathbb{R}_+ \to \{0, 1\}$  is a right-continuous function with left limits, i.e.,  $\lim_{t \to t_0^+} s(t) = s(t_0)$  and  $\lim_{t \to t_0^-} s(t)$  exists for all  $t_0 \in \mathbb{R}_+$ . A binary signal s is a step function  $s : [0, T] \to \{0, 1\}$ , a mode-switch signal a is a step function  $a : [0, T] \to F$ ,  $t \mapsto a_t$ . Given a mode-switch signal a, a matching output signal for a is a function  $x_a : [0, T] \to U$  that satisfies

(i)  $x_a(0) = x_0$ ,

(ii) the function  $x_a$  is continuous,

(iii) for all  $t \in (0, T)$ , if a is continuous at t, then  $x_a$  is differentiable at t and  $\frac{d}{dt} x_a(t) = a_t(t, x_a(t))$ .

For (iii), recall that the codomain of *a* is *F*.

Using an inductive argument, the following lemma establishes that, for any given mode-switch signal, there is a unique matching output signal, given as a continuous and differentiable function.

**Lemma 2** (Existence and Uniqueness of Matching Output Signal). Given a mode-switch signal a, the matching output signal  $x_a$  for a exists and is unique.

**Proof.**  $x_a$  can be constructed inductively, by pasting together the solutions  $x_{t_j}$  of  $\frac{d}{dt} x_{t_j}(t) = a_{t_j}(t, x_{t_j}(t))$ , where  $t_0 = 0$  and  $t_1 < t_2 < ...$  are *a*'s switching times in  $S_a$ : For the induction basis j = 0, we define  $x_a(t) := x_{t_0}(t)$  with initial value  $x_{t_0} = x_{t_0}(t_0) := x_0$  for  $t \in [0, t_1]$ . Obviously, (i) holds by construction, and the continuity and differentiability of  $x_{t_0}(t)$  at other times ensures (ii) and (iii).

For the induction step  $j \to j + 1$ , we assume that we have constructed  $x_a(t)$  already for  $0 \le t \le t_j$ . For  $t \in [t_j, t_{j+1}]$ , we define  $x_a(t) := x_{t_{j+1}}(t)$  with initial value  $x_{t_{j+1}} = x_{t_{j+1}} := x_a(t_j) = x_{t_j}(t_j)$ . Continuity of  $x_a(t)$  at  $t = t_j$  follows by construction, and the continuity and differentiability of  $x_{t_{j+1}}(t)$  again ensures (ii) and (iii).

Finally, the uniqueness of  $x_a$  follows directly from the uniqueness of the solution of the underlying first-order Lipschitz-continuous ODE system  $\frac{dx}{dt} = f(t, x)$  with the given initial condition.

Given two mode-switch signals a, b, we define their distance as

$$d_T(a,b) = \lambda \left( \{ t \in [0,T] \mid a_t \neq b_t \} \right)$$

where  $\lambda$  is the Lebesgue measure on  $\mathbb{R}$ . Obviously, the distance function  $d_T$  is a metric on the set of mode-switch signals.

The following Theorem 3 shows that the mapping  $a \mapsto x_a$  is continuous. Note that it requires all the functions in F to satisfy a common Lipschitz constant. Albeit this clearly limits the applicability of our theorem, the examples in Sections 5 and 6 reveal that it is not an overly conservative assumption.

**Theorem 3.** Let  $K \ge 1$  be a common Lipschitz constant for all functions in F and let M be a real number such that  $||f(t, x(t))|| \le M$  for all  $f \in F$ , all  $x \in U$ , and all  $t \in [0, T]$ . Then, for all mode-switch signals a and b, if  $x_a$  is the output signal for a and  $x_b$  is the output signal for b, then  $||x_a - x_b||_{\infty} \le 2Me^{TK}d_T(a, b)$ . Consequently, the mapping  $a \mapsto x_a$  is continuous.

**Proof.** Let  $S = \{t \in (0, T) \mid a \text{ or } b \text{ is discontinuous at } t\} \cup \{0, T\}$  be the set of switching times of *a* and *b*. The set *S* must be finite, since both *a* and *b* are right-continuous on a compact interval. Let  $0 = s_0 < s_1 < s_2 < \cdots < s_m = T$  be the increasing enumeration of *S*.

We show by induction on k that

$$\forall t \in [0, s_k]: \quad \|x_a(t) - x_b(t)\| \le 2M e^{tK} d_t(a, b) \tag{2}$$

for all  $k \in \{0, 1, 2, ..., m\}$ . The base case k = 0 is trivial. For the induction step  $k \mapsto k + 1$ , we distinguish the two cases  $a_{s_k} = b_{s_k}$  and  $a_{s_k} \neq b_{s_k}$ .

If  $a_{s_k} = b_{s_k}$ , then we have  $a_t = b_t$  for all  $t \in [s_k, s_{k+1})$  and hence  $d_t(a, b) = d_{s_k}(a, b)$  for all  $t \in [s_k, s_{k+1}]$ . Moreover, we can apply Lemma 1 and obtain

$$\forall t \in [s_k, s_{k+1}]: \quad \|x_a(t) - x_b(t)\| \le e^{(t-s_k)K} \|x_a(s_k) - x_b(s_k)\| \quad .$$

(3)

Plugging in (2) for  $t = s_k$  reveals that (2) holds for all  $t \in [s_k, s_{k+1}]$  as well.

If  $a_{s_k} \neq b_{s_k}$ , then  $x_a$  and  $x_b$  follow different differential equations in the interval  $t \in [s_k, s_{k+1}]$ . We can, however, use the mean-value theorem for vector-valued functions [19, Theorem 5.19] to obtain

$$\forall t \in [s_k, s_{k+1}]: \quad \|x_a(t) - x_a(s_k)\| \le M(t - s_k) \text{ and}$$

(4)

$$\forall t \in [s_k, s_{k+1}]: \quad \|x_b(t) - x_b(s_k)\| \le M(t - s_k). \tag{5}$$

This, combined with the induction hypothesis, the equality  $d_t(a, b) = d_{s_k}(a, b) + (t - s_k)$ , and the inequalities  $1 \le e^{tK}$  and  $e^{s_kK} \le e^{tK}$ , implies

$$\begin{aligned} \|x_a(t) - x_b(t)\| &\leq \|x_a(t) - x_a(s_k) + \|x_a(s_k) - x_b(s_k)\| + \|x_b(s_k) - x_b(t)\| \\ &\leq 2M(t - s_k) + 2Me^{s_kK}d_{s_k}(a, b) \\ &\leq 2Me^{tK}(t - s_k) + 2Me^{tK}d_{s_k}(a, b) \\ &= 2Me^{tK}\left(d_t(a, b) - d_{s_k}(a, b)\right) + 2Me^{tK}d_{s_k}(a, b) \\ &= 2Me^{tK}d_t(a, b) - d_{s_k}(a, b) \end{aligned}$$

for all  $t \in [s_k, s_{k+1}]$ . This concludes the proof.  $\Box$

We remark that the (proof of the) continuity property of Theorem 3 is very different from the standard (proof of the) continuity property of controlled variables in closed thresholded hybrid systems. Mode switches in such systems are caused by the time evolution of the system itself, e.g., when some controlled variable exceeds some value. Consequently, such systems can be described by means of a *single* ODE system with discontinuous righthand side [20].

By contrast, in our hybrid systems, the mode switches are solely caused by changes of digital inputs that are *externally* controlled: For every possible pattern of the digital inputs, there is a dedicated ODE system that controls the analog output. Consequently, the time evolution of the output now also depends on the time evolution of the inputs. Proving the continuity of the (discretized) output w.r.t. different (but close, w.r.t. some metric) digital input signals require relating the output of *different* ODE systems. Therefore, our setting *cannot* be modeled as a single ODE system with discontinuous righthand side.

#### 2.2. Continuity of thresholding

For a real number  $\xi \in \mathbb{R}$  and a function  $x : [a, b] \to \mathbb{R}$ , denote by  $\Theta_{\xi}(x)$  the thresholded version of x defined by

$$\Theta_{\xi}(x) : [a, b] \to \{0, 1\}, \quad \Theta_{\xi}(x)(t) = \begin{cases} 0 & \text{if } x(t) \le \xi, \\ 1 & \text{if } x(t) > \xi. \end{cases}$$

(6)

In what follows, we prove that, under some mild conditions, the mapping  $x \mapsto \Theta_{\varepsilon}(x)$  is continuous.

**Lemma 4.** Let  $\xi \in \mathbb{R}$  and let  $x : [a, b] \to \mathbb{R}$  be a continuous strictly monotonic function with  $x(b) = \xi$ . Then, for every  $\varepsilon > 0$ , there exists  $a \ \delta > 0$  such that, for every continuous function  $y : [a, b] \to \mathbb{R}$ , the condition  $||x - y||_{\infty} < \delta$  implies  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_1 < \epsilon$ .

**Proof.** We show the lemma for the case that x is strictly increasing. The proof for strictly decreasing x is analogous.

Set  $\chi = x(a)$ . Since x is bijective onto the interval  $[\chi, \xi]$ , it has an inverse function  $x^{-1} : [\chi, \xi] \to [a, b]$ . The inverse function  $x^{-1}$  is continuous because the domain [a, b] is compact [19, Theorem 4.17].

The relation  $t \le x^{-1}(\xi - \delta)$  implies  $x(t) + \delta \le \xi$ . Hence, if  $||x - y||_{\infty} < \delta$ , then  $y(t) \le x(t) + \delta \le \xi$  for all  $t \le x^{-1}(\xi - \delta)$ . This means that  $\Theta_{\xi}(y)(t) = 0$  for all  $t \le x^{-1}(\xi - \delta)$ , so  $t > x^{-1}(\xi - \delta)$  for every  $t \in [a, b]$  where  $\Theta_{\xi}(y)(t) = 1$ .

By assumption, we have  $\Theta_{\xi}(x)(t) = 0$  for all  $t \in [a, b]$ . Thus,

$$\|\theta_{\xi}(x) - \theta_{\xi}(y)\|_{1} = \lambda \left( \{t \in [0, T] \mid \theta_{\xi}(y) = 1\} \right) = \lambda \left( \{t \in [0, T] \mid y(t) > \xi\} \right) \le b - x^{-1} (\xi - \delta).$$

(7)

Note that continuity of y is sufficient to ensure that the set  $\{t \in [0,T] \mid y(t) > \xi\}$  in Eq. (7) is measurable. Since  $x^{-1}$  is continuous, we have  $x^{-1}(\xi - \delta) \to x^{-1}(\xi) = b$  as  $\delta \to 0$ . In particular, for every  $\varepsilon > 0$ , there exists a  $\delta > 0$  such that  $b - x^{-1}(\xi - \delta) < \varepsilon$ . This concludes the proof.  $\Box$

The following Lemma 5 shows that we can drop the assumption  $x(b) = \xi$  in Lemma 4:

**Lemma 5.** Let  $\xi \in \mathbb{R}$  and let  $x, y : [a, b] \to \mathbb{R}$  be two continuous functions where x is strictly monotonic. Then, for every  $\varepsilon > 0$ , there exists a  $\delta > 0$  such that  $||x - y||_{\infty} < \delta$  implies  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_1 < \varepsilon$ . Moreover, if  $\max\{x(a), x(b)\} \le \xi$  or  $\min\{x(a), x(b)\} > \xi$ , then  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_1 = 0$ .

**Proof.** We again show the lemma for the case that x is strictly increasing. The proof for strictly decreasing x is analogous. Let  $\varepsilon > 0$ . We distinguish three cases:

(i) If  $x(b) < \xi$ , then we have  $\Theta_{\xi}(x)(t) = 0$  for all  $t \in [a, b]$ . Choosing  $\delta = \xi - x(b)$ , we deduce  $y(t) < x(t) + \delta \le x(b) + \xi - x(b) = \xi$  for all  $t \in [a, b]$  whenever  $||x - y||_{\infty} < \delta$ . Hence, we get  $\Theta_{\xi}(y)(t) = 0$  for all  $t \in [a, b]$  and thus  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{1} = 0 < \varepsilon$ .

(ii) If  $x(a) > \xi$ , then we can choose  $\delta = x(a) - \xi$  and get  $\Theta_{\xi}(y)(t) = \Theta_{\xi}(x)(t) = 1$  for all  $t \in [a, b]$  whenever  $||x - y||_{\infty} < \delta$ . In particular,  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{1} = 0 < \varepsilon$ .

(iii) If  $x(a) \leq \xi \leq x(b)$ , then there exists a unique  $c \in [a, b]$  with  $x(c) = \xi$ . Applying Lemma 4 on the restriction of x on the interval [a, c], we get the existence of a  $\delta_1 > 0$  such that  $||x - y||_{[a,c],\infty} < \delta_1$  implies  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{[a,c],1} < \varepsilon/2$ ; herein,  $|| \cdot ||_{[a,c],\infty}$  and  $|| \cdot ||_{[a,c],1}$  denote the supremum-norm and the 1-norm on the interval [a, c], respectively. Applying Lemma 4 on the restriction of x on the interval [c, b] after the coordinate transformation  $t \mapsto -t$  yields the existence of a  $\delta_2 > 0$  such that  $||x - y||_{[c,b],\infty} < \delta_2$  implies  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{[a,b],1} < \varepsilon/2$ . Setting  $\delta = \min\{\delta_1, \delta_2\}$ , we thus get  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{[a,b],1} = ||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{[a,c],1} + ||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_{[c,b],1} < \varepsilon/2 + \varepsilon/2 = \varepsilon$  whenever  $||x - y||_{[a,b],\infty} < \delta$ .

The following Theorem 6 shows that the mapping  $x \mapsto \Theta_{\xi}(x)$  is continuous for a given function x, provided that x has only finitely many alternating critical points, i.e., local optima that alternate between lying above and below  $\xi$ . Formally, these are times  $t_0, t_1, \ldots, t_M$  where  $x'(t_j) = 0$  for all  $0 \le j \le M$  and  $\operatorname{sgn}(x(t_j) - \xi) = -\operatorname{sgn}(x(t_{i+1}) - \xi)$ , for all  $0 \le i \le M - 1$ . Note carefully that we require M to be fixed and hence, in particular, independent of the choice of T here.

**Theorem 6.** Let  $\xi \in \mathbb{R}$  and let  $x, y : [0,T] \to \mathbb{R}$  be two differentiable functions. Assume that x has at most  $M < \infty$  alternating critical points, where M is independent of T. Then, for every  $\varepsilon > 0$ , there exists a  $\delta > 0$  such that  $||x - y||_{\infty} < \delta$  implies  $||\Theta_{\xi}(x) - \Theta_{\xi}(y)||_1 < \varepsilon$ . Consequently, the mapping  $x \mapsto \Theta_{\xi}(x)$  is continuous.

**Proof.** Let  $\mathcal{N} = \{t \in [0, T] \mid x \text{ has a critical point at } t\} \cup \{0, T\}$ , which contains only  $m \le M$  alternating critical points by assumption, and  $t_0 < t_1 < t_2 < \cdots < t_m$  be the increasing enumeration of  $\mathcal{N}$ . By the mean-value theorem, the function x is strictly monotonic in every interval  $[t_k, t_{k+1}]$  for every  $k \in \{0, 1, 2, \dots, m\}$ .

Let  $\varepsilon > 0$ . Applying Lemma 5 to the restriction of x on each of the intervals  $[t_k, t_{k+1}]$ , we distinguish two cases: (i) if  $t_k, t_{k+1}$  are non-alternating critical points, then  $\|\Theta_{\xi}(x) - \Theta_{\xi}(y)\|_{[t_k, t_{k+1}], 1} = 0$ . Otherwise, we are assured of the existence of some  $\delta_k > 0$  such that  $\|x - y\|_{[t_k, t_{k+1}], \infty} < \delta_k$  implies  $\|\Theta_{\xi}(x) - \Theta_{\xi}(y)\|_{[t_k, t_{k+1}], 1} < \varepsilon/m$ . Setting  $\delta = \min\{\delta_{k_0}, \delta_{k_1}, \delta_{k_2}, \dots, \delta_{k_{m-1}}\}$ , we thus obtain

$$\|\Theta_{\xi}(x) - \Theta_{\xi}(y)\|_{[0,T],1} = \sum_{k=0}^{m-1} \|\Theta_{\xi}(x) - \Theta_{\xi}(y)\|_{[t_k, t_{k+1}],1} < \sum_{k=0}^{m-1} \varepsilon/m = \varepsilon,$$

(8)

whenever  $||x - y||_{[0,T],\infty} < \delta$ .

## 3. Continuity of digitized hybrid gates

To prepare for our general result about the continuity of hybrid gate models (Theorem 8), we will first (re)prove the continuity of IDM channels as shown in Fig. 2, which has been established by a (somewhat tedious) direct proof in [10]. In our notation, an IDM channel consists of:

• A nonnegative minimum delay  $\delta_{\min} \ge 0$  and a delay function  $\Delta_{\delta_{\min}}(s)$  that maps the binary input signal  $i_a$ , augmented with the left-sided limit  $i_a(0-)$  as the *initial value*<sup>3</sup> that can be different from  $i_a(0)$ , to the binary signal  $i_d = \Delta_{\delta_{\min}}(i_a)$ , defined by

$$\Delta_{\delta_{\min}}(i_a)(t) = \begin{cases} i_a(0-) & \text{if } t < \delta_{\min} \\ i_a(t-\delta_{\min}) & \text{if } t \ge \delta_{\min} \end{cases}$$

(9)

<sup>&</sup>lt;sup>3</sup> In [10], this initial value of a signal was encoded by extending the time domain to the whole  $\mathbb{R}$  and using  $i_a(-\infty)$ .

- An open set  $U \subseteq \mathbb{R}^n$ , where  $\pi_1[U]$  represents the analog output signal and  $\pi_k[U]$ ,  $k = \{2, 3, ..., n\}$ , specifies the internal state variables of the model. In this fashion,<sup>4</sup> we presume that  $\pi_1[U] = (0, 1)$ , i.e., the range of output signals is contained in the interval (0, 1).

- Two bounded functions  $F_{\uparrow}, F_{\downarrow} : \mathbb{R} \times U \to \mathbb{R}^n$  with the following properties:

- $F_{\uparrow}, F_{\downarrow}$  are continuous for  $(t, x) \in [0, T] \times U$ , for any  $0 < T < \infty$ , and Lipschitz continuous in *U*, which entails that every trajectory *x* of the ODEs  $\frac{d}{dt}x(t) = F_{\uparrow}(t, x(t))$  and  $\frac{d}{dt}x(t) = F_{\downarrow}(t, x(t))$  with any initial value  $x(0) \in U$  satisfies  $x(t) \in U$  for all  $t \in [0, T]$ , recall Section 2.1.

- for no trajectory x of the ODEs  $\frac{d}{dt}x(t) = F_{\uparrow}(t, x(t))$  and  $\frac{d}{dt}x(t) = F_{\downarrow}(t, x(t))$  with initial value  $x(0) \in U$  does  $\pi_1[x]$  have infinitely many alternating critical points  $t_0, t_1, \ldots$  with  $\pi_1[x]'(t) = 0$  and  $\operatorname{sgn}(\pi_1[x](t_i) \xi) = -\operatorname{sgn}(\pi_1[x](t_{i+1}) \xi)$ , for all  $i \ge 0$ .

- An initial value  $x_0 \in U$ , with  $x_0 = F_{\uparrow}$  if  $i_a(0-) = 1$  and  $x_0 = F_{\downarrow}$  if  $i_a(0-) = 0$ .

- A mode-switch signal  $b: [0,T] \to \{F_{\uparrow}, F_{\downarrow}\}$  defined by setting  $b(t) = F_{\uparrow}$  if  $i_d(t) = 1$  and  $b(t) = F_{\downarrow}$  if  $i_d(t) = 0$ .

- The analog output signal  $o_a = \pi_1[x_b]$ , i.e., the output signal for b and initial value  $x_0$ .

- A threshold voltage  $\xi = V_{th} \in (0, 1)$  for the comparator that finally produces the binary output signal  $o_d = \Theta_{\xi}(o_a)$ .

By combining the results from Sections 2.1 and 2.2, we obtain the continuity of the channel function in a hybrid system mapping input signals to output signals stated in Theorem 7. It implies that small changes in the input signal lead to proportionally small changes in the output signal.

**Theorem 7.** The channel function of an IDM channel, which maps from the input signal  $i_a$  to the output signal  $o_d$ , is continuous with respect to the 1-norm on the interval [0,T].

**Proof.** The mapping from  $i_a$  to  $o_d$  is continuous as the concatenation of continuous mappings:

- The mapping from  $i_a \mapsto i_d$  is continuous since  $\Delta_{\delta_{\min}}$  is trivially continuous for input and output binary signals with the 1-norm.

- The mapping  $i_d \mapsto b$  is a continuous mapping from the set of signals equipped with the 1-norm to the set of mode-switch signals equipped with the metric  $d_T$ , since the points of discontinuity of b are the points where  $i_d$  is discontinuous.

- By Theorem 3, the mapping  $b \mapsto x_b$  is a continuous mapping from the set of mode-switch signals equipped with the metric  $d_T$  to the set of piecewise differentiable functions  $[0, T] \rightarrow U$  equipped with the supremum-norm.

- The mapping  $x_b \mapsto \pi_1 \circ x_b$  is a continuous mapping from the set of piecewise differentiable functions  $[0, T] \to U$  equipped with the supremum-norm to the set of piecewise differentiable functions  $[0, T] \to (0, 1)$  equipped with the supremum-norm. Since  $\|(x_1, \dots, x_n)\|_1 = \|x_1\|_1 + \dots + \|x_n\|_1$  for every  $x \in U$ , this follows from  $\|\pi_1[x]\|_1 \le \|x\|_1$ .

- By Theorem 6, the mapping  $\pi_1 \circ x_b \mapsto \Theta_{\xi}(\pi_1 \circ x_b)$  is a continuous mapping from the set of piecewise differentiable functions  $[0, T] \to (0, 1)$  equipped with the supremum-norm to the set of binary signals equipped with the 1-norm.

Whereas the condition that no trajectory of any of the ODEs may have infinitely many alternating critical points is difficult to check in general, it is always guaranteed for every switching waveform f(t) typically found in elementary<sup>5</sup> digitized hybrid gates. More specifically, as any f is meant to represent a digital signal here, it must satisfy either  $\lim_{t\to\infty} f(t) = 0$  or  $\lim_{t\to\infty} f(t) = 1$ . Moreover, since real circuits cannot produce waveforms with arbitrary steep slopes, |f'(t)| must be bounded. From the former, it follows that, for every  $\varepsilon > 0$ , there is some  $t(\varepsilon)$  such that either  $f(t) < \varepsilon$  or else  $f(t) > 1 - \varepsilon$  for every  $t \ge t(\varepsilon)$ . Consequently, choosing  $\varepsilon = \min\{V_{th}, 1 - V_{th}\}$  reveals that no alternating critical point  $t \ge t(\varepsilon)$  can exist. Infinitely many alternating critical points for  $t < t(\varepsilon)$  are prohibited by |f'(t)| being bounded.

With these preparations, we can now deal with the general case: General digitized hybrid gates have  $c \ge 1$  binary input signals  $i_a = (i_a^1, \dots, i_a^c)$ , augmented with *initial values*  $(i_a^1(0-), \dots, i_a^c(0-))$ , and a single binary output signal  $o_d$ , and are specified as follows:

Definition 1 (Digitized Hybrid Gate). A digitized hybrid gate with c inputs consists of:

• *c* delay functions  $\Delta_{\delta_j}(s)$  with  $\delta_j \ge 0, 1 \le j \le c$ , that map the binary input signal  $i_a^j$  with initial value  $i_a^j(0-)$  to the binary signal  $i_a^j = \Delta_{\delta_i}(i_a^j)$ , defined by

$$\Delta_{\delta_j}(i_a^j)(t) = \begin{cases} i_a^j(0-) & \text{if } t < \delta_j \\ i_a^j(t-\delta_j) & \text{if } t \ge \delta_j \end{cases}$$

(10)

• An open set  $U \subseteq \mathbb{R}^n$ , where  $\pi_1[U]$  represents the analog output signal and  $\pi_k[U]$ ,  $k = \{2, 3, ..., n\}$ , specifies the internal state variables of the model.

<sup>&</sup>lt;sup>4</sup> In real circuits, the interval (0, 1) typically needs to be replaced by  $(0, V_{DD})$ .

<sup>&</sup>lt;sup>5</sup> This is true for all combinational gates like inverters, NOR, NAND etc. Excluded are gates with an internal state, like a storage element, which may exhibit *metastable behavior* [21,22].

- A set *F* of bounded functions  $F^{\ell} : \mathbb{R} \times U \to \mathbb{R}^n$ , with the following properties:

- $F^{\ell}$  is continuous for  $(t, x) \in [0, T] \times U$ , for any  $0 < T < \infty$ , and Lipschitz continuous in *U*, with a common Lipschitz constant, which entails that every trajectory *x* of the ODE  $\frac{d}{dt}x(t) = F^{\ell}(t, x(t))$  with any initial value  $x(0) \in U$  satisfies  $x(t) \in U$  for all  $t \in [0, T]$ .

- for no trajectory x of the ODEs  $\frac{d}{dt}x(t) = F^{\ell}(t, x(t))$  with initial value  $x(0) \in U$  does  $\pi_1[x]$  have infinitely many alternating critical points  $t_0, t_1, \ldots$  with  $\pi_1[x]'(t) = 0$  and  $\operatorname{sgn}(\pi_1[x](t_i) \xi) = -\operatorname{sgn}(\pi_1[x](t_{i+1}) \xi)$ , for all  $i \ge 0$ .

- A mode-switch signal  $b : [0,T] \to F$ , which obtained by a continuous choice function  $b_c$  acting on  $i_d^1(t), \dots, i_d^c(t)$ , i.e.,  $b(t) = b_c(i_d^1(t), \dots, i_d^c(t))$ .

- An initial value  $x_0 \in U$ , which must correspond to the mode selected by  $b_c(i_0^1(0-), \dots, i_c^r(0-))$ .

- The analog output signal  $o_a = \pi_1[x_b]$ , i.e., the output signal for *b* and initial value  $x_0$ .

- A threshold voltage  $\xi = V_{ih} \in (0, 1)$  for the comparator that finally produces the binary output signal  $o_d = \Theta_{\xi}(o_a)$ .

By essentially the same proof as for Theorem 7, we obtain:

**Theorem 8.** The gate function of a digitized hybrid gate with *c* inputs according to Definition 1, which maps from the vector of input signals  $i_a = (i_a^1, \dots, i_a^c)$  to the output signal  $o_d$ , is continuous with respect to the 1-norm on the interval [0, T].

# 4. Composing gates in circuits

In this section, we will first compose digital circuits from digitized hybrid gates and reason about their executions. More specifically, it will turn out that, under certain conditions ensuring the causality of every composed gate, the resulting circuit will exhibit a unique execution for any given execution of its inputs. This uniqueness is mandatory for building digital dynamic timing simulation tools.

Moreover, we will adapt the proof that no circuit with IDM channels can solve the bounded SPF problem utilized in [10] to our setting: Using the continuity result of Theorem 8, we prove that no circuit with digitized hybrid gates can solve bounded SPF. Since unbounded SPF can be solved with IDM channels, which are simple instances of digitized hybrid gate models, faithfulness w.r.t. solving the SPF problem follows.

## 4.1. Executions of circuits

**Circuits.** Circuits are obtained by interconnecting a set of input ports and a set of output ports, forming the external interface of a circuit, and a finite set of digitized hybrid gates. We constrain the way components are interconnected in a natural way, by requiring that any gate input, channel input and output port is attached to only one input port, gate output or channel output, respectively. Formally, a *circuit* is described by a directed graph where:

- (C1) A vertex  $\Gamma$  can be either a *circuit input port*, a *circuit output port*, or a digitized hybrid gate.

- (C2) The edge  $(\Gamma, I, \Gamma')$  represents a 0-delay connection from the output of  $\Gamma$  to a fixed input I of  $\Gamma'$ .

- (C3) Circuit input ports have no incoming edges.

- (C4) Circuit output ports have exactly one incoming edge and no outgoing one.

- (C5) A *c*-ary gate *G* has a single output and *c* inputs  $I_1, \ldots, I_c$ , in a fixed order, fed by incoming edges from exactly one gate output or input port.

**Executions.** An *execution* of a circuit *C* is a collection of binary signals  $s_{\Gamma}$  defined on  $[0, \infty)$  for all vertices  $\Gamma$  of *C* that respects all the gate functions and input port signals. Formally, the following properties must hold:

- (E1) If *i* is a circuit input port, there are no restrictions on  $s_i$ .

- (E2) If *o* is a circuit output port, then  $s_o = s_G$ , where *G* is the unique gate output connected to *o*.

- (E3) If vertex *G* is a gate with *c* inputs  $I_1, \ldots, I_c$ , ordered according to the fixed order condition C5), and gate function  $f_G$ , then  $s_G = f_G(s_{\Gamma_1}, \ldots, s_{\Gamma_c})$ , where  $\Gamma_1, \ldots, \Gamma_c$  are the vertices the inputs  $I_1, \ldots, I_c$  of *C* are connected to via edges  $(\Gamma_1, I_1, G), \cdots, (\Gamma_d, I_c, G)$ .

The above definition of an execution of a circuit is "existential", in the sense that it only allows checking for a given collection of signals whether it is an execution or not: For every hybrid gate in the circuit, it specifies the gate output signal, given a *fixed* vector of input signals, all defined on the time domain  $t \in [0, \infty)$ . A priori, this does not give an algorithm to construct executions of circuits, in particular, when they contain feedback loops. Indeed, the parallel composition of general hybrid automata may lead to non-unique executions and bizarre timing behaviors known as *Zeno*, where an infinite number of transitions may occur in finite time [23].

To avoid such behaviors in our setting, we require all digitized hybrid gates in a circuit to be strictly causal:

**Definition 2** (*Strict Causality*). A digitized hybrid gate *G* with *c* inputs is strictly causal, if the pure delays  $\delta_j$  for every  $1 \le j \le c$  are positive. Let  $\delta_{\min}^C > 0$  be the minimal pure delay of any input of any gate in circuit *C*.

We proceed with defining input–output causality for gates, which is based on signal transitions. Every binary signal can equivalently be described by a sequence of transitions: A *falling transition* at time t is the pair (t, 0), a *rising transition* at time t is the pair (t, 1).

**Definition 3** (*Input–output Causality*). The output transition  $(t, .) \in s_G$  of a gate G is *caused* by the transition  $(t', .) \in s_G^j$  on input  $I_j$  of G, if (t, .) occurs in the mode  $a_c(i_d^1(t^+), ..., i_d^c(t^+))$ , where  $i_d^j(t^+)$  is the pure-delay shifted input signal at input  $I_j$  at the last mode switching time  $t^+ \le t$  (see Eq. 1) and (t', .) is the last transition in  $s_G^j$  before or at time  $t^+ - \delta_j$ , i.e.,  $\nexists(t'', .) \in s_G^j$  for  $t' < t'' \le t^+ - \delta_j$ . We also assume that the output transition  $(t, .) \in s_G$  *causally depends* on every transition in  $s_G^j$  before or at time  $t^+ - \delta_j$ .

Strictly causal gates satisfy the following obvious property:

**Lemma 9.** If some output transition  $(t,.) \in s_G$  of a strictly causal digitized hybrid gate G in a circuit C causally depends on its input transition  $(t',.) \in s_{i,c}^{j}$ , then  $t - t' \ge \delta_{i}$ .

The following Theorem 4.1 shows that every circuit made up of strictly causal gates has a unique execution, defined for  $t \in [0, \infty)$ .

**Theorem 4.1** (Unique Execution). Every circuit C made up of finitely many strictly causal digitized hybrid gates has a unique execution, which either consists of finitely many transitions only or else requires  $[0, \infty)$  as its time domain.

**Proof.** We will inductively construct this unique execution by a sequence of iterations  $\ell \ge 1$  of a simple deterministic simulation algorithm, which determines the prefix of the sought execution up to time  $t_{\ell}$ . Iteration  $\ell$  deals with transitions occurring at time  $t_{\ell}$ , starting with  $t_1 = 0$ . To every transition *e* generated throughout its iterations, we also assign a *causal depth* d(e) that gives the maximum causal distance to an input port: d(e) = 0 if *e* is a transition at some input port, and d(e) is the maximum of  $1 + d(e^j)$ ,  $1 \le j \le c$ , for every transition added at the output of a *c*-ary gate caused by transitions  $e^j$  at its inputs.

Induction basis  $\ell = 1$ : At the beginning of iteration 1, which deals with all transitions occurring at time  $t_1 = 0$ , all gates are in their initial mode, which is determined by the initial values of their inputs. They are either connected to input ports, in which case  $s_i(0-)$  is used, or to the output port of some gate *G*, in which case  $s_G(0)$  (determined by the initial mode of *G*) is used. Depending on whether  $s_i(0-) = s_i(0)$  or not, there is also an input transition  $(0, s_i(0)) \in s_i$  or not. All transitions in the so generated execution prefix  $[0, t_1] = [0, 0]$  have a causal depth of 0.

Still, the transitions that have happened by time  $t_1$  may cause additional *potential future transitions*. They are called future transitions, because they occur only after  $t_1$ , and potential because they need not occur in the final execution. In particular, if there is an input transition  $(0, s_i(0)) \in s_i$ , it may cause a mode switch of every gate *G* that is connected to the input port *i*. Due to Lemma 9, however, such a mode switch, and hence each of the output transitions *e* that may occur during that new mode (which all are assigned a causal depth d(e) = 1), of *G* can only happen at or after time  $t_1 + \delta_{\min}^C$ . In addition, the initial mode of any gate *G* that is not mode switched may also cause output transitions *e* at arbitrary times t > 0, which are assigned a causal depth d(e) = 0. Since at most finitely many critical points may exist for every mode's trajectory, it follows that at most *finitely* many such future potential transitions could be generated in each of the finitely many gates in the circuit. Let  $t_2 > t_1$  denote the time of the closest transition among all input port transitions and all the potential future transitions just introduced.

Induction step  $\ell \to \ell + 1$ : Assume that the execution prefix for  $[0, t_{\ell}]$  has already been constructed in iterations  $1, \dots, \ell$ , with at most finitely many potential future transitions occurring after  $t_{\ell}$ . If the latter set is empty, then the execution of the circuit has already been determined completely. Otherwise, let  $t_{\ell+1} > t_{\ell}$  be the closest future transition time.

During iteration  $\ell + 1$ , all transitions occurring at time  $t_{\ell+1}$  are dealt with, exactly as in the base case: Any transition e, with causal depth d(e), happening at  $t_{\ell+1}$  at a gate output or at some input port may cause a mode switch of every gate G that is connected to it. Due to Lemma 9, such a mode switch, and hence each of the at most finitely many output transitions e' occurring during that new mode (which all are assigned a causal depth d(e') = d(e) + 1), of G can only happen at or after time  $t_{\ell+1} + \delta_{\min}^C$ . In addition, the at most finitely many potential future transitions w.r.t.  $t_{\ell}$  of all gates that have not been mode-switched and actually occur at times greater than  $t_{\ell+1}$  are retained, along with their assigned causal depth, as potential future transitions w.r.t.  $t_{\ell+1}$ . Overall, we again end up with at most finitely many potential future transitions, which completes the induction step.

To complete our proof, we only need to argue that  $\lim_{\ell \to \infty} t_{\ell} = \infty$  for the case where the iterations do not stop at some finite  $\ell$ . This follows immediately from the fact that, for every  $k \ge 1$ , there must be some iteration  $\ell \ge 1$  such that  $t_{\ell} \ge k \delta_{\min}^{C}$ . If this was not the case, there must be some iteration after which no further mode switch of any gate takes place. This would cause the set of potential future transitions to shrink in every subsequent iteration, however, and thus the simulation algorithm to stop, which provides the required contradiction.

From the execution construction, we also immediately get:

**Lemma 10.** For all  $\ell \ge 1$ , (a) the simulation algorithm never assigns a causal depth larger than  $\ell$  to a transition generated in iteration  $\ell$ , and (b) at the end of iteration  $\ell$  the sequence of causal depths of transitions in  $s_{\Gamma}$  for  $t \in [0, t_{\ell}]$  is nondecreasing for all components  $\Gamma$ .

# 4.2. Impossibility of short-pulse filtration

The results of the previous subsection allow us to adapt the impossibility proof of [10] to our setting. We start with the definition of the SPF problem:

**Short-Pulse Filtration.** A signal *contains a pulse* of length  $\Delta$  at time  $T_0$ , if it contains a rising transition at time  $T_0$ , a falling transition at time  $T_0 + \Delta$ , and no transition in between. The zero signal has the initial value 0 and does not contain any transition. A circuit solves Short-Pulse Filtration (SPF), if it fulfills all of:

- (F1) The circuit has exactly one input port and exactly one output port. (Well-formedness)

- (F2) If the input signal is the zero signal, then so is the output signal. (No generation)

- (F3) There exists an input pulse such that the output signal is not the zero signal. (Nontriviality)

- (F4) There exists an  $\epsilon > 0$  such that for every input pulse the output signal never contains a pulse of length less than or equal to  $\epsilon$ . (*No short pulses*)

We allow the circuit to behave arbitrarily if the input signal is not a single pulse or the zero signal.

- A circuit solves bounded SPF if additionally:

- (F5) There exists a K > 0 such that for every input pulse the last output transition is before time  $T_0 + \Delta + K$ , where  $T_0$  is the time of the first input transition. (Bounded stabilization time)

A circuit is called a *forward circuit* if its graph is acyclic. Forward circuits are exactly those circuits that do not contain feedback loops. Equipped with the continuity of digitized hybrid gates and the fact that the composition of continuous functions is continuous, it is not too difficult to prove that the inherently discontinuous SPF problem cannot be solved with forward circuits.

# Theorem 4.2. No forward circuit solves bounded SPF.

**Proof.** Suppose that there exists a forward circuit that solves bounded SPF with stabilization time bound *K*. Denote by  $s_A$  its output signal when feeding it a *A*-pulse at time 0 as the input. Because  $s_A$  in forward circuits is a finite composition of continuous functions by Theorem 8,  $\|s_A\|_{[0,T],1}$  depends continuously on *A*, for any *T*.

By the nontriviality condition (F3) of the SPF problem, there exists some  $\Delta_0$  such that  $s_{\Delta_0}$  is not the zero signal. Set  $T = 2\Delta_0 + K$ . Let  $\varepsilon > 0$  be smaller than both  $\Delta_0$  and  $\|s_{\Delta_0}\|_{[0,T],1}$ . We show a contradiction by finding some  $\Delta$  such that  $s_{\Delta}$  either contains a pulse of length less than  $\varepsilon$  (contradiction to the no short pulses condition (F4)) or contains a transition after time  $\Delta + K$  (contradicting the bounded stabilization time condition (F5)).

Since  $\|s_A\|_{[0,T],1} \to 0$  as  $\Delta \to 0$  by the no generation condition (F2) of SPF, there exists a  $\Delta_1 < \Delta_0$  such that  $\|s_{\Delta_1}\|_{[0,T],1} = \epsilon$  by the intermediate value property of continuity. By the bounded stabilization time condition (F5), there are no transitions in  $s_{\Delta_1}$  after time  $\Delta_1 + K$ . Hence,  $s_{\Delta_1}$  is 0 after this time because otherwise it is 1 for the remaining duration  $T - (\Delta_1 + K) > \Delta_0 > \epsilon$ , which would mean that  $\|s_{\Delta_1}\|_{[0,T],1} > \epsilon$ . Consequently, there exists a pulse in  $s_{\Delta_1}$  before time  $\Delta_1 + K$ . But any such pulse is of length at most  $\epsilon$  because  $\|s_{\Delta_1}\|_{[0,\Delta_1+K],1} \le \|s_{\Delta_1}\|_{[0,T],1} = \epsilon$ . This is a contradiction to the no short pulses condition (F4).

We next show how to simulate (part of) an execution of an arbitrary circuit C by a forward circuit C' generated from C by the unrolling of feedback loops. Intuitively, the deeper the unrolling, the longer the time C' behaves as C.

**Definition 4.** Let C be a circuit, V a vertex of C, and  $k \ge 0$ . We define the *k*-unrolling of C from V, denoted by  $C_k(V)$ , to be a directed acyclic graph with a single sink, constructed as follows:

The unrolling  $C_k(I)$  from input port I is just a copy of that input port. The unrolling  $C_k(O)$  from output port O with incoming channel C and predecessor V comprises a copy of the output port  $O^{(k)}$  and the unrolled circuit  $C_k(V)$  with its sink connected to  $O^{(k)}$  by an edge.

The 0-unrolling  $C_0(B)$  from hybrid gate *B* is a trivial Boolean gate  $X_v$  without inputs and the constant output value *v* equal to *B*'s initial digitized output value. For k > 0, the *k*-unrolling  $C_k(B)$  from gate *B* comprises an exact copy of that gate  $B^{(k)}$ . Additionally, for every incoming edge of *B* from *V* in *C*, it contains the circuit  $C_{k-1}(V)$  with its sink connected to  $B^{(k)}$ . Note that all copies of the same input port are considered to be the same.

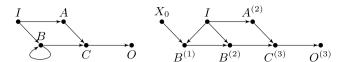

To each component  $\Gamma$  in  $C_k(V)$ , we assign a value  $z(\Gamma) \in \mathbb{N}_0 \cup \{\infty\}$  as follows:  $z(\Gamma) = \infty$  if  $\Gamma$  has no predecessor (in particular, is an input port) and  $\Gamma \notin \{X_0, X_1\}$ . Moreover,  $z(X_0) = z(X_1) = 0$ , z(V) = z(U) if V is an output port connected by an edge to U, and  $z(B) = \min_{c \in E^B} \{1 + z(c)\}$  if B is a gate with its inputs connected to the components in the set  $E^B$ . Fig. 3 shows an example of a circuit and an unrolled circuit with its z values.

Noting that, for every component  $\Gamma$  in  $C_k(V)$ ,  $z(\Gamma)$  is the number of gates on the shortest path from an  $X_v$  node to  $\Gamma$ , or  $z(\Gamma) = \infty$  if no such path exists, we immediately get:

# **Lemma 11.** The z-value assigned to the sink vertex $V^{(k)}$ of a k-unrolling $C_k(V)$ of C from V satisfies $z(V^{(k)}) \ge k$ .

Recalling the causal depths assigned to transitions during the execution construction in Theorem 4.1, we are now in the position to prove the result for a circuit simulated by an unrolled circuit.

Fig. 3. Circuit C (left) and  $C_3(O)$  (right) under the assumption that the gate B has initial value 0. It is  $z(X_0) = 0$ ,  $z(I) = z(A^{(2)}) = \infty$ ,  $z(B^{(1)}) = 1$ ,  $z(B^{(2)}) = 2$ ,  $z(C^{(3)}) = 3$ , and  $z(O^{(3)}) = 3$ .

**Theorem 4.3.** Let *C* be a circuit with input port *I* and output port *O* that solves bounded SPF. Let  $C_k(O)$  be an unrolling of *C*,  $\Gamma$  a component in *C*, and  $\Gamma'$  a copy of  $\Gamma$  in  $C_k(O)$ . For all input signals  $s_I$  on *I*, if a transition *e* is generated for  $\Gamma$  by the execution construction algorithm run on circuit *C* with input signal  $s_I$  and  $d(e) \leq z(\Gamma')$ , then *e* is also generated for  $\Gamma'$  by the algorithm run on circuit  $C_k(O)$  with input signal  $s_I$ ; and vice versa.

**Proof.** Assume that *e* is the first transition violating the theorem. The input signal is the same for both circuits, and the initial digitized values of gates in *C* and both their copies in  $C_k(O)$  and the  $X_v$  gates resulting from their 0-unrolling are equal as well. Hence, *e* cannot be any such transition (added in iteration 1 only).

If *e* was added to the output of a gate *B* in either circuit, the transition *e'* resp. *e''* at one of its inputs that caused *e* in *C* resp.  $C_k(V)$  must have been different. These transitions *e'* resp. *e''* must come from the output of some other gate  $B_1$ , and causally precede *e*. Hence, by Definition 3, d(e) = d(e')+1, and by Lemma 10,  $d(e) \ge d(e'')$ . Also by definition,  $z(B) = z(B_1)+1$  in  $C_k(O)$ . Since  $d(e) \le z(B)$  by assumption, we find  $d(e') \le z(B_1)$  and  $d(e'') \le z(B)$ , so applying our theorem to *e'* and *e''* yields a contradiction to *e* being the first violating transition.

We can finally prove that bounded SPF is not solvable, even with non-forward circuits.

Theorem 4.4. No circuit solves bounded SPF.

**Proof.** We first note that the impossibility of bounded SPF also implies the impossibility of bounded SPF when restricting pulse lengths to be at most some  $\Delta_0 > 0$ .

Since all transitions generated in the execution construction Theorem 4.1 up to any bounded time  $t_{\ell}$  have bounded causal depth, let  $\zeta$  be an upper bound on the causal depth of transitions up to the SPF stabilization time bound  $\Delta_0 + K$ . Then, by Theorem 4.3 and Lemma 11, the  $\zeta$ -unrolled circuit  $C_{\zeta}(O)$  has the same output transitions as the original circuit C up to time  $\Delta_0 + K$ , and hence, by definition of bounded SPF, the same transitions for all times. But since  $C_{\zeta}(O)$  is a forward circuit, it cannot solve bounded SPF by Theorem 4.2, i.e., neither can C.

# 5. Digitized hybrid models for multi-input gates

In this section, we will apply the results obtained in the previous section to circuits composed of digitized hybrid gates. For a warm-up, we will effortlessly re-prove the already known fact that every digitized hybrid gate model obtained by appending resp. prepending an IDM *exp-channel* with pure delay  $\delta_{\min} > 0$  at the output of resp. at every input of any zero-time Boolean gate is continuous and strictly causal. Consequently, according to Section 4, the resulting IDM circuit model is faithful w.r.t. solving the SPF problem.

An exp-channel, as introduced in [10], is just the two-state digitized hybrid model illustrated in Fig. 2 instantiated with exponential switching waveforms  $f_{\downarrow}(t) = 1 - f_{\uparrow}(t) = e^{-t/\tau}$  for some time constant  $\tau > 0$ . Obviously, these are the trajectories of a simple first-order RC low-pass filter. The ODEs governing  $y = f_{\downarrow}(t)$  resp.  $y = f_{\uparrow}$  are  $y' + y/\tau = 0$  resp.  $y' + y/\tau = 1/\tau$ , so  $F_{\downarrow}(t, y) = -y/\tau$  resp.  $F_{\uparrow}(t, y) = (1 - y)/\tau$  is of course Lipschitz-continuous. An exp-channel hence satisfies the conditions of Theorem 7 and is hence continuous and, due to the assumption  $\delta_{\min} > 0$ , also strictly causal according to Definition 2. Since zero-time Boolean gates that alternate with IDM channels can neither affect continuity nor causality of the latter, this completes our proof.

## 5.1. Modeling multi-input switching effects

As already mentioned in Section 1, experiments in [13] showed that the prediction accuracy of the above IDM circuit model for multi-input gates is below expectations. As revealed by Ferdowsi et al. [14], this is primarily due to the fact that a model of a multi-input gate that combines single-input single-output IDM channels with zero-time Boolean gates cannot properly capture output delay variations caused by *multiple input switching* (MIS) effects: output transitions may be sped up/slowed down when different inputs switch in close temporal proximity [15].

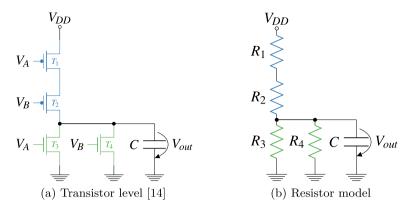

Consider the CMOS implementation of a NOR gate shown in Fig. 6(a), for example, which consists of two serial pMOS ( $T_1$  and  $T_2$ ) for charging the load capacitance *C* (producing a rising output transition), and two parallel nMOS transistors ( $T_3$  and  $T_4$ ) for discharging it (producing a falling one). When an input experiences a rising transition, the corresponding nMOS transistor closes while the corresponding pMOS transistor opens, so *C* will be discharged. If both inputs *A* and *B* experience a rising transition at

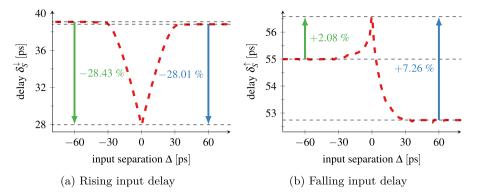

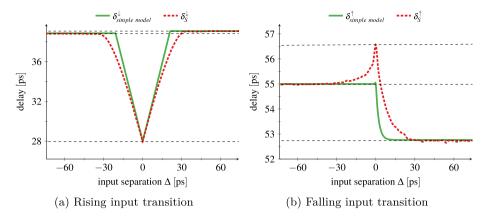

Fig. 4. MIS effects in the measured delay of a 15 nm technology CMOS NOR gate.

the same time, *C* is discharged twice as fast. Since the gate delay depends on the discharging speed, it follows that the delay  $\delta_{S}^{\downarrow}(\Delta)$  increases (by almost 30% in the example shown in Fig. 4(a)) when the *input separation time*  $\Delta = t_{B} - t_{A}$  increases from 0 to  $\infty$  or decreases from 0 to  $-\infty$ . For falling input transitions, the behavior of the NOR gate is quite different: Fig. 4(b) shows that the MIS effects lead to a moderate decrease of  $\delta_{S}^{\dagger}(\Delta)$  when  $|\Delta|$  goes from 0 to  $\infty$ , which is primarily caused by capacitive coupling.

MIS effects have of course been studied in the digital circuit modeling literature in the past, with approaches ranging from linear [24] or quadratic [25] fitting over higher-dimensional macromodels [26] and model representations [27] to recent machine learning methods [28]. However, the resulting models are either empirical or statistical and, hence, have not been analyzed w.r.t. continuity. Whether they admit a faithful digital circuit model or not is hence unknown.

### 5.2. A simple digitized hybrid model for a CMOS NOR gate

To the best of our knowledge, the first attempt to develop a delay model that captures MIS effects and can be analyzed w.r.t. continuity has been provided in [14]. It is a 4-state digitized hybrid model for a CMOS NOR gate, with one mode per possible digital state of the inputs  $(A, B) \in \{(0, 0), (0, 1), (1, 0), (1, 1)\}$ , which has been obtained by replacing the four transistors in Fig. 6(a) by ideal zero-time switches with non-zero resistance, and adding another capacitance  $C_N$  to the node N between the two pMOS transistors  $T_1$  and  $T_2$ . In each mode, the voltage of the output signal O and the internal node N are governed by a system of constant-coefficient first-order ODEs as follows:

• System (1, 1):  $V_A = 1$ ,  $V_B = 1$ : If inputs *A* and *B* are 1, both nMOS transistors are conducting and thus replaced by resistors, causing the output *O* to be discharged in parallel. By contrast, *N* is completely isolated and keeps its value. This leads to the following ODEs:

$$\begin{pmatrix} \frac{\mathrm{d}}{\mathrm{d}t} V_{int}(t) \\ \frac{\mathrm{d}}{\mathrm{d}t} V_{out}(t) \end{pmatrix} = \begin{pmatrix} F_1(V_{int}(t), V_{out}(t)) \\ F_2(V_{int}(t), V_{out}(t)) \end{pmatrix} = \begin{pmatrix} 0 \\ -\left(\frac{1}{CR_3} + \frac{1}{CR_4}\right) V_{out}(t) \end{pmatrix}$$

• System (1,0):  $V_A = 1$ ,  $V_B = 0$ : Since  $T_1$  and  $T_4$  are open, node N is connected to O, and O to GND. Both capacitors have to be discharged over resistor  $R_3$ , resulting in less current that is available for discharging C. One obtains:

$$\begin{pmatrix} \frac{\mathrm{d}}{\mathrm{d}t} V_{int}(t) \\ \frac{\mathrm{d}}{\mathrm{d}t} V_{out}(t) \end{pmatrix} = \begin{pmatrix} F_3(V_{int}(t), V_{out}(t)) \\ F_4(V_{int}(t), V_{out}(t)) \end{pmatrix} = \begin{pmatrix} -\frac{V_{int}(t)}{C_{int}R_2} + \frac{V_{out}(t)}{C_{int}R_2} \\ \frac{V_{int}(t)}{CR_2} - \left(\frac{1}{CR_2} + \frac{1}{CR_3}\right) V_{out}(t) \end{pmatrix}$$

• System (0, 1):  $V_A = 0$ ,  $V_B = 1$ : Opening transistors  $T_2$  and  $T_3$  again decouples the nodes N and O. We thus get

$$\begin{pmatrix} \frac{\mathrm{d}}{\mathrm{d}t} V_{int}(t) \\ \frac{\mathrm{d}}{\mathrm{d}t} V_{out}(t) \end{pmatrix} = \begin{pmatrix} F_5(V_{int}(t), V_{out}(t)) \\ F_6(V_{int}(t), V_{out}(t)) \end{pmatrix} = \begin{pmatrix} -\frac{V_{int}(t)}{C_{int}R_1} + \frac{V_{DD}}{C_{int}R_1} \\ -\frac{V_{out}(t)}{CR_4} \end{pmatrix}$$

• System (0,0):  $V_A = 0$ ,  $V_B = 0$ : Closing both pMOS transistors causes both capacitors to be charged over the same resistor  $R_1$ , similarly to system (1,0). Thus

$$\begin{pmatrix} \frac{\mathrm{d}}{\mathrm{d}t} V_{int}(t) \\ \frac{\mathrm{d}}{\mathrm{d}t} V_{out}(t) \end{pmatrix} = \begin{pmatrix} F_7(V_{int}(t), V_{out}(t)) \\ F_8(V_{int}(t), V_{out}(t)) \end{pmatrix} = \begin{pmatrix} -\left(\frac{1}{C_{int}(t)R_1} + \frac{1}{C_{int}(t)R_2}\right)V_{int} + \frac{V_{out}(t)}{C_{int}R_2} + \frac{V_{DD}}{C_{int}R_2} \\ \frac{V_{int}(t)}{CR_2} - \frac{V_{out}(t)}{CR_2} \end{pmatrix}$$

Every  $F_i$ ,  $i \in \{1, ..., 8\}$ , is a mapping from  $U = (0, 1)^2 \subseteq \mathbb{R}^2$  to  $\mathbb{R}$ , whereat U is the vector of the voltages at the nodes N and O. Solving the above ODEs provides analytic expressions for these voltage trajectories, which can even be inverted to obtain the relevant gate delays. As it turned out in [14], although the model perfectly covers the MIS effects in the case of rising input

Fig. 5. Comparison of the measured delay  $\delta_{r}^{1/4}(\Delta)$  of a real 15 nm CMOS NOR gate (red dashed line) and the delay prediction of the simple digitized hybrid model (green line) from [14]. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

transitions (Fig. 5(a)), it unfortunately fails to do so for falling input (= rising output) transitions (Fig. 5(b)). Nevertheless, using Theorem 8, we can show that the model of [14] is continuous:

**Theorem 5.1.** For any  $i \in \{1, ..., 8\}$ ,  $F_i$  of the simple digitized hybrid model is Lipschitz continuous.

**Proof.** Since the proof is straightforward, we elaborate it only for  $F_7$ ; similar arguments apply to the other cases. Let  $K = max\{(\frac{1}{C_{int}R_1} + \frac{1}{C_{int}R_2}), \frac{1}{C_{int}R_2}\}$ . For any voltages  $V_{int}^1, V_{int}^2, V_{out}^1$ , and  $V_{out}^2$  in (0,1), we find

$$\begin{aligned} \left| F_7(V_{int}^1, V_{out}^1) - F_7(V_{int}^2, V_{out}^2) \right| &= \left| -\left(\frac{1}{C_{int}R_1} + \frac{1}{C_{int}R_2}\right) (V_{int}^1 - V_{int}^2) + \frac{1}{C_{int}R_2} \left(V_{out}^1 - V_{out}^2\right) \right| \\ &\leq K \left| (V_{int}^1 - V_{int}^2) + (V_{out}^1 - V_{out}^2) \right|. \end{aligned}$$

$$\tag{11}$$

$$K\left| (V_{int}^{1} - V_{int}^{2}) + (V_{out}^{1} - V_{out}^{2}) \right|. \quad \Box$$

(12)

Consequently, we can instantiate Definition 1 with

ſ

$$b_{c}(i_{d}^{A}, i_{d}^{B}) = \begin{cases} \begin{pmatrix} F_{1}(V_{int}(t), V_{out}(t)) \\ F_{2}(V_{int}(t), V_{out}(t)) \end{pmatrix} & (i_{d}^{A}, i_{d}^{B}) = (1, 1) \\ \begin{pmatrix} F_{3}(V_{int}(t), V_{out}(t)) \\ F_{4}(V_{int}(t), V_{out}(t)) \end{pmatrix} & (i_{d}^{A}, i_{d}^{B}) = (1, 0) \\ \begin{pmatrix} F_{5}(V_{int}(t), V_{out}(t)) \\ F_{6}(V_{int}(t), V_{out}(t)) \end{pmatrix} & (i_{d}^{A}, i_{d}^{B}) = (0, 1) \\ \begin{pmatrix} F_{7}(V_{int}(t), V_{out}(t)) \\ F_{8}(V_{int}(t), V_{out}(t)) \end{pmatrix} & (i_{d}^{A}, i_{d}^{B}) = (0, 0) \end{cases} \end{cases}$$

such that the model is continuous by Theorem 8.

# 6. An advanced digitized hybrid model for a CMOS NOR gate

In an attempt to mitigate the inability of the simple digitized hybrid model for a CMOR NOR gate proposed in [14] to cover the MIS effect for falling input (= rising output) transitions (recall Fig. 5(b)), Ferdowsi, Schmid, and Salzmann developed an advanced model originally presented in [16]. Whereas this model indeed accomplishes its purpose, its analysis is based on a complicated piecewise approximation (in terms of  $\Delta$ ) of both the ODE solutions and, in particular, the corresponding delay formulas. This not only impairs the utility of the results for determining delays of compound circuits, both for simulation-based and analytical studies, but also caused the model parametrization, which is based on fitting, to partially compensate for the approximation error by obtaining inexact parameters.

In this section, we will provide an entirely novel analysis of the digitized hybrid model proposed in [16], which has been enabled by the recent discovery of an explicit expression for the ODE solution. It not only leads to more accurate delay formulas, but also to an explicit model parametrization procedure that avoids any fitting.

The advanced digitized hybrid model for a 2-input CMOS NOR gate introduced in [16] is built upon replacing the transistors in Fig. 6(a) by time-varying resistors: The values  $R_i(t)$ ,  $i \in \{1, ..., 4\}$  in the resulting Fig. 6(b) vary between some fixed on-resistance  $R_i$  and the off-resistance  $\infty$  according to some laws, which we will introduce below. The law to be used is determined by the state of the particular input signal that drives the gate of the corresponding transistor. This construction results in a hybrid model with Table 1

Fig. 6. Schematics and resistor model of a CMOS NOR gate.

| State transitions and modes. $\uparrow$ and $\uparrow\uparrow$ (resp. $\downarrow$ and $\downarrow\downarrow$ ) represent the first and the second rising (resp. falling) input transitions. $+$ and $-$ specify the sign of | the |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| switching time difference $\Delta = t_B - t_A$ .                                                                                                                                                                             |     |

| Mode                           | Transition                | $t_A$       | t <sub>B</sub> | $R_1$                 | $R_2$                 | $R_3$                 | $R_4$                 |

|--------------------------------|---------------------------|-------------|----------------|-----------------------|-----------------------|-----------------------|-----------------------|

| $T_{-}^{\uparrow}$             | $(0,0) \rightarrow (1,0)$ | 0           | -∞             | $on \rightarrow of f$ | on                    | $off \rightarrow on$  | off                   |

| $T_{+}^{\uparrow\uparrow}$     | $(1,0) \rightarrow (1,1)$ | $- \Delta $ | 0              | of f                  | $on \rightarrow of f$ | on                    | $off \rightarrow on$  |

| $T^{\uparrow}_{+}$             | $(0,0) \to (0,1)$         | -∞          | 0              | on                    | $on \rightarrow of f$ | off                   | $off \rightarrow on$  |

| $T_{-}^{\uparrow\uparrow}$     | $(0,1) \to (1,1)$         | 0           | $- \Delta $    | $on \rightarrow of f$ | off                   | $off \rightarrow on$  | on                    |

| $T_{-}^{\downarrow}$           | $(1,1) \rightarrow (0,1)$ | 0           | -∞             | $of f \rightarrow on$ | off                   | $on \rightarrow of f$ | on                    |

| $T_{+}^{\downarrow\downarrow}$ | $(0,1) \rightarrow (0,0)$ | $- \Delta $ | 0              | on                    | $of f \rightarrow on$ | off                   | $on \rightarrow of f$ |

| $T_{+}^{\downarrow}$           | $(1,1) \rightarrow (1,0)$ | -∞          | 0              | off                   | $of f \rightarrow on$ | on                    | $on \rightarrow of f$ |

| $T_{-}^{\downarrow\downarrow}$ | $(1,0) \rightarrow (0,0)$ | 0           | $- \Delta $    | $of f \rightarrow on$ | on                    | $on \rightarrow of f$ | off                   |

4 different modes, which correspond to the 4 possible input states  $(A, B) \in \{(0, 0), (0, 1), (1, 0), (1, 1)\}$ .

Table 1 shows all possible input state transitions and the corresponding resistor time evolution mode switches. Double arrows in the mode switch names indicate MIS-relevant modes, whereas + and - indicate whether input A switched before B or the other way round. For instance, assume the system is in state (0,0) initially, i.e., that both A and B were set to 0 at time  $t_A = t_B = -\infty$ . This causes  $R_1$  and  $R_2$  to be in the *on-mode*, whereas  $R_3$  and  $R_4$  are in the *off-mode*. Now assume that at time  $t_A = 0$ , A is switched to 1. This switches  $R_1$  resp.  $R_3$  to the *off-mode* resp. *on-mode* at time  $t_1^{Off} = t_3^{On} = t_A = 0$ . The corresponding mode switch is  $T_{-}^{\uparrow}$  and reaches state (1,0). Now assume that B is also switched to 1, at some time  $t_B = \Delta > 0$ . This causes  $R_2$  resp.  $R_4$  to switch to *off-mode* resp. *on-mode* at time  $t_2^{Off} = t_4^{On} = t_B = \Delta$ . The corresponding mode switch is  $T_{+}^{\uparrow\uparrow}$  and reaches state (1, 1); note carefully that the delay is  $\Delta$ -dependent and hence MIS-relevant.

Crucial for the model is choosing a suitable law for the time evolution of  $R_i(t)$  in the *on*- and *off-mode*, which should facilitate an analytic solution of the resulting ODE systems (15) while being reasonably close to the physical behavior of a transistor. The simple Shichman–Hodges transistor model [29] is used here, which states a quadratic dependence of the output current on the input voltage. Approximating the latter by  $d\sqrt{t-t_0}$  in the operation range close to the threshold voltage  $V_{th}$ , with *d* and  $t_0$  some fitting parameters, leads to the *continuous resistance model*

$$R_{j}^{0n}(t) = \frac{u_{j}}{t - t^{0n}} + R_{j}; \ t \ge t^{0n},$$

(13)

$$R_j^{off}(t) = \beta_j(t - t^{off}) + R_j; \ t \ge t^{off},$$

(14)

for some constant slope parameters  $\alpha_j$  [ $\Omega$ s],  $\beta_j$  [ $\Omega/s$ ], and on-resistance  $R_j$  [ $\Omega$ ].  $t^{on}$  resp.  $t^{off}$  represent the time when the respective transistor is switched on resp. off.

Actually, it was found in [16] that continuously changing resistors, according to (13), are only required for switching-on the pMOS transistors in Fig. 6(a). All other resistors can be immediately switched on/off (in zero-time), as already employed in [14]. Note that immediate switching is obtained by setting  $\alpha_j = 0$  and  $\beta_j = \infty$  in (13) and (14). Subsequently, we will use the notation  $R_1 = R_{p_A}$ ,  $R_2 = R_{p_B}$  with the abbreviation  $2R = R_{p_A} + R_{p_B}$  for the two pMOS transistors  $T_1$  and  $T_2$ , and  $R_3 = R_{n_A}$ ,  $R_4 = R_{n_B}$  for the two nMOS transistors  $T_3$  and  $T_4$ .

Another pivotal question is how to incorporate  $R_1(t), \ldots, R_4(t)$  in the ODEs of the modes. The arguably most intuitive idea is to incorporate those in the state of the ODE of every mode, and switch between them continuously upon a mode switch. This "full-state model" would lead to ODE systems with a 5-dimensional state (output voltage  $V_{out}$  and the 4 resistors), however, which rules out finding analytic solutions.

Therefore, in [16], these resistors were incorporated in the *coefficients* of a simple first-order ODE obtained by applying Kirchhoff's rules to Fig. 6(b). Doing this results in the non-autonomous, non-homogeneous ordinary differential equation (ODE)

(15)

| $F(t, V_{out}(t))$ for each state transition. |                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|