### A MASTER THESIS ON

# Fault-tolerant Design Techniques for Nano-Mechanical Circuits

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### Diplom-Ingenieur

(Equivalent to Master of Science)

in

Embedded Systems (066 504)

by

### **Dominik Rudolf**

1225777

### Supervisor(s):

Univ.Prof. Dipl.-Ing. Dr.techn. Axel Jantsch M.sc. Ardavan Elahi

Vienna, Austria

December 2024

### **Abstract**

The shift from conventional manufacturing and monitoring techniques to systems with decentralised, interconnected, and increasingly self-aware components has created a demand for edge-devices that are capable of operating under harsh environmental conditions, such as high temperatures or high radiation doses. Due to constrained resources and limited supply, these edge-devices also require efficient circuitry with low leakage current. Traditional complementary metal-oxide-semiconductor (CMOS) technology is not suitable for meeting these requirements.

The i-EDGE project aims to establish nanoelectromechanical (NEM) relays as substitutes for CMOS transistors to address the aforementioned challenges. However, at the current Technology Readiness Level (TRL) of the project, the yield of manufactured NEM circuits, as well as the reliability under operation, is significantly lower than in CMOS technology. To tackle this issue, it is necessary to explore fault-tolerant design techniques that can be applied to NEM circuits.

This thesis first derives fault models from the physical defects that can occur in NEM devices. Conventional fault-tolerant design techniques are then reviewed and assessed for their applicability to NEM circuits. The unique characteristics of NEM devices are leveraged to simplify or enhance established fault-tolerant circuit designs, as well as to propose new NEM circuit designs. A simulation environment is developed to simulate test circuits with fault-tolerant design techniques applied. The resulting data is used to explore the design space and to evaluate the achievable fault tolerance.

# Kurzfassung

Der Wandel von konventionellen Produktions- und Überwachungssystemen hin zu Systemen mit dezentralisierten, vernetzten und zunehmend intelligenten Geräten sowie Edge-Computing hat eine Nachfrage nach Komponenten geschaffen, die in der Lage sind, unter extremen Umweltbedingungen wie hohen Temperaturen oder hohen Strahlungsdosen zu arbeiten. Aufgrund begrenzter Hardware-Ressourcen und eingeschränkter Energieversorgung erfordern diese Edge-Geräte zudem häufig effiziente Schaltungen mit minimalem Leckstrom. Traditionelle Schaltungen auf Basis von CMOS sind daher oft nicht geeignet, diese Anforderungen zu erfüllen.

Das i-EDGE-Projekt hat zum Ziel, NEM-Relais als Ersatz für CMOS-Transistoren zu etablieren, um die oben genannten Herausforderungen zu bewältigen. Zum aktuellen Stand des TRLs dieses Projekts liegen sowohl der Ertrag der fabrizierten NEM-Schaltungen als auch die Zuverlässigkeit im Betrieb deutlich unter dem Niveau der CMOS-Technologie. Um dieses Problem zu lösen, ist es erforderlich, fehlertolerante Designtechniken auf ihre Eignung für NEM-Schaltungen zu prüfen.

Diese Masterarbeit leitet zunächst Fehlermodelle aus physischen Defekten ab, die in NEM-Relais auftreten können. Konventionelle fehlertolerante Designtechniken werden anschließend hinsichtlich ihrer Anwendbarkeit auf NEM-Schaltungen bewertet. Die einzigartige Funktionsweise von NEM-Relais wird genutzt, um etablierte fehlertolerante Schaltungsdesigns zu vereinfachen oder zu verbessern sowie um neue NEM-Schaltungsdesigns vorzuschlagen. Eine Simulationsumgebung wird entwickelt, um die fehlertoleranten Designtechniken mithilfe von Testschaltungen zu simulieren. Anhand der resultierenden Daten werden verschiedene Designs bewertet und die erreichbare Fehlertoleranz evaluiert.

### Erklärung

Hiermit erkläre ich, dass die vorliegende Arbeit ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt wurde. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet.

Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder in ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

### Copyright Statement

- I, Dominik Rudolf, hereby declare that this thesis is my own original work and, to the best of my knowledge and belief, it does not:

- Breach copyright or other intellectual property rights of a third party.

- · Contain material previously published or written by a third party, except where this is appropriately cited through full and accurate referencing.

- · Contain material which to a substantial extent has been accepted for the qualification of any other degree or diploma of a university or other institution of higher learning.

- Contain substantial portions of third party copyright material, including but not limited to charts, diagrams, graphs, photographs or maps, or in instances where it does, I have obtained permission to use such material and allow it to be made accessible worldwide via the Internet.

| Signature:                     |                |

|--------------------------------|----------------|

| Vienna, Austria, December 2024 | Dominik Rudolf |

# Acknowledgment

This thesis marks the final step of a long and eventful journey that I decided to go on many years ago. Like most ventures that seem overwhelming at first, this one wasn't accomplished alone. They become manageable only through the helping hands that prepare one's luggage both before and during the journey, are made more pleasant by the companionship of fellow travellers met along the way, and often involve unexpected losses that allow us to see the pathway we walk with sharper eyes. Similarly, this chapter of my personal journey, embodied in an academic career and culminating in this thesis, would not have been imaginable without such people. To them, I would like to express my heartfelt thanks in the following lines.

First and foremost, I would like to thank my colleagues at i-EDGE, who enabled me to carry out my thesis as part of this significant project. Not only were they always willing to answer technical questions of all kinds in great detail, but they also gave me the opportunity to travel to various parts of the world. I have always enjoyed the personal meetings we had. Looking back, I must say that participating in a multinational project has been an invaluable experience that I would not want to miss. I hope that with this thesis, I have been able to make a small contribution to its progress.

I owe special thanks to Prof. Dr. Axel Jantsch, who gave me the opportunity to work on this thesis and guided me throughout the process in a highly professional manner. His far-reaching perspective always enabled me to grasp what was essential in this work. Without his corrective hand, the scope of this thesis would have become far too extensive, making it nearly impossible to finish. Additionally, it is hard to put into words the immense patience my co-supervisor, M.Sc. Ardavan Elahi, showed with me and this thesis over several months. His expertise and encouraging words enabled me to overcome every obstacle, no matter how large, and even under significant time pressure, he never failed to provide me with the best possible support until the very end. Without the assistance of these two individuals, this work would not have reached its completed form. I therefore owe them my deepest gratitude.

This would not be a proper acknowledgment but an affront if I did not mention the colleagues who ended up sharing an office with me. Above all, I would like to thank Philipp, with whom I had countless conversations which led to fruitful thoughts, ideas, and impulses for my work. Thanks also goes to my Dutch colleagues Jan and Jasper, particularly for introducing me to the Dutch language to an extent sufficient for basic communication (Ik hou van Nederlandse vrouwen). Furthermore, I would like to thank Sofia, who always helped me with organizational matters and transformed my presentations into something reasonable by giving countless suggestions for improvement. I further extend my gratitude to all the other colleagues and staff at ICT for always being helpful and for various distractions that helped reduce the effective working hours to a bearable level.

I would also like to thank all my former fellow students who became my companions and friends during my studies, whose names are too numerous to mention. Without them, the challenging academic path I pursued would have been not only significantly more arduous but also lacking many memorable experiences. At this point, I would also like to thank my friends outside the academic sphere: Dominik, Martin, and Daniel, who have accompanied me since childhood and adolescence; René and Daniel, who reliably provided the necessary motivation during every training session to keep my muscles in a hypertrophic rather than atrophic state throughout my studies; and Patrick, who has passed away but always brought the right energy to our group and knew how to pleasantly challenge and surprise me with technical discussions during his lifetime.

Finally, I extend my deepest thanks to my parents, Gerhard and Monika, who made this journey possible through their continuous support, and to my deceased sister Sarah, who was a pillar of strength throughout my whole life. Without you, this journey would not have reached its conclusion.

# Danksagung

Die vorliegende Arbeit stellt den Schlussstein einer langen und ereignisreichen Reise dar, die ich vor etlichen Jahren beschloss, anzutreten. Wie bei solchen, anfangs unmöglich scheinenden Unternehmungen üblich, bewältigt man diese nicht im Alleingang. Sie werden gangbar gemacht durch eine Vielzahl unterstützender Hände, die einem vor und während der Reise das Weggepäck bereiten, werden erleichtert durch die Begleitung von Weggefährten, die man auf selbigem Wege trifft, und beherbergen oft auch unerwartete Verluste, die dem Weg erst eine schärfere Zeichnung verleihen. So ist auch jener Abschnitt meines persönlichen Lebensweges, der sich in Form einer akademischen Laufbahn ausgestaltete und mit dieser Arbeit seinen Abschluss findet, nicht ohne solche Menschen denkbar. Ihnen sei in den folgenden Zeilen mein Dank ausgesprochen.

Zuallererst möchte ich den Kollegen von i-EDGE danken, die es mir ermöglicht haben, meine Abschlussarbeit im Zuge dieses bemerkenswerten Projekts durchzuführen. Nicht nur waren sie stets bemüht, mir technische Fragestellungen aller Art in ausführlicher Weise zu beantworten, sie eröffneten mir auch die Möglichkeit, verschiedene Orte der Welt zu bereisen. Die persönlichen Zusammenkünfte in den Meetings habe ich stets genossen. Rückblickend möchte ich festhalten, dass die Mitarbeit an einem multinationalen Projekt eine wertvolle Erfahrung für mich darstellt, die ich keinesfalls missen möchte. Ich hoffe, dass ich mit dieser Arbeit einen kleinen Beitrag zu dessen Fortschritt beisteuern konnte.

Besondere Beachtung verdient in dieser Danksagung Prof. Dr. Axel Jantsch, der mir diese Abschlussarbeit ermöglichte und mich in weiterer Folge, im wahrsten Sinne des Wortes, professionell betreute. Sein richtender Blick half mir stets, das Wesentliche dieser Arbeit zu erfassen. Ohne seine korrigierende Hand wäre dieses, letztlich umfangreiche Werk, zudem vollends ausgeufert und hätte seinen Abschluss nur schwerlich gefunden. Zum Weiteren ist es nur schwer in Worte zu fassen, wie viel Geduld mein Mitbetreuer, M.sc. Ardavan Elahi, über mehrere Monate hinweg mit mir und dieser Arbeit aufgebracht hat. Seine Expertise und motivierenden Worte befähigten mich, jede noch so große Hürde zu meistern, und selbst unter großem Zeitdruck versäumte er es nicht, mich bis zuletzt bestmöglich zu unterstützen. Ohne die Hilfe jener beiden Personen würde diese Arbeit nicht in ihrer abgeschlossenen Form vorliegen. Ihnen gebührt deshalb mein ausdrücklicher Dank.

Dies wäre keine Danksagung, sondern ein Affront, wenn nicht auch jene Kollegen erwähnt würden, die das Schicksal mit mir in einem Institutsbüro zusammengeführt hat. Allen voran möchte ich deshalb Philipp danken, mit dem ich eine nicht unerhebliche Anzahl an Konversationen führte, aus denen fruchtbare Gedanken, Ideen und Anstöße für meine Arbeit erwuchsen. Dieser Dank gilt auch meinen niederländischen Kollegen Jan und Jasper, insbesondere aber dafür, mir die niederländische Sprache in einem Ausmaß näher gebracht zu haben, das zur Verständigung vollkommen ausreicht (Ik hou van Nederlandse vrouwen). Des Weiteren möchte ich mich bei Sofia bedanken, die mir stets bei organisatorischen Fragen weiterhalf und durch unzählige Verbesserungsvorschläge auch meine Präsentationen in eine zumutbare Form brachte. Außerdem danke ich allen übrigen Kollegen und Mitarbeitern des ICT für ihre Hilfsbereitschaft und allerlei sonstigen Ablenkungen, um die effektiven Arbeitsstunden auf ein erträgliches Maß zu reduzieren.

Ich danke zudem allen meinen ehemaligen Kommilitonen, die mir während meiner Studienzeit als Weggefährten und Freunde zuteilwurden und deren Namen zu zahlreich sind, um sie alle zu nennen. Ohne sie wäre die akademische Laufbahn, die ich einschlug und die von vielen Herausforderungen durchzogen war, nicht nur um ein Vielfaches mühseliger, sondern auch um das ein oder andere Gelage ärmer gewesen. An dieser Stelle möchte ich auch meinen Freunden außerhalb des universitären Bereichs Dank aussprechen: Dominik, Martin und Daniel, die mich schon seit Kindheits- und Jugendtagen begleiten, René und Daniel, die zuverlässig in jedem Training den nötigen Ansporn lieferten, um meine Muskulatur während meiner gesamten Studienzeit in den hypertrophen anstatt in den atrophen Zustand zu versetzen, sowie dem verstorbenen Patrick, der stets den nötigen Schwung in die Runde brachte und es verstand, mich mit fachspezifischen Gesprächen zu überraschen und angenehm herauszufordern.

Abschließend danke ich ganz besonders meinen Eltern Gerhard und Monika, die mir durch Unterstützung jeglicher Art diesen Lebensweg erst ermöglicht haben, sowie meiner verstorbenen Schwester Sarah, die mir zu allen Lebenszeiten eine Stütze war. Ohne euch hätte diese Reise keinen Abschluss gefunden.

# **Contents**

| AI | ostrac | et en       | 111 |

|----|--------|-------------------------------------------------|-----|

| Κι | ırzfa  | ssung                                           | iv  |

| 1  | Intr   | roduction                                       | 1   |

|    | 1.1    | NEM Devices in i-EDGE                           | 2   |

|    | 1.2    | Research Questions and Expected Results         | 3   |

| 2  | Phy    | sical Defects and Fault Models                  | 7   |

|    | 2.1    | Physical Defects in NEM Relays                  | 7   |

|    | 2.2    | Gate Level                                      | 8   |

|    | 2.3    | Device Level                                    | 10  |

| 3  | Fau    | lt-tolerant Design Techniques in CMOS           | 13  |

|    | 3.1    | Hardware Redundancy                             | 13  |

|    | 3.2    | Time Redundancy                                 | 28  |

|    | 3.3    | Information Redundancy                          | 30  |

|    | 3.4    | Summary                                         | 32  |

| 4  | Fau    | lt-tolerant Design Techniques in NEM Technology | 35  |

|    | 4.1    | Conventional TMR Voters with NEM Relays         | 35  |

|    | 4.2    | Proposed NEM Voters                             | 35  |

| 5  | Sim    | ulation Framework                               | 41  |

|    | 5.1    | Simulation Methods                              | 41  |

|    | 5.2    | Evaluation Metrics                              | 48  |

| 6  | Sim    | ulation Results                                 | 51  |

|    | 6.1    | Test Circuits                                   | 52  |

| Die appro         | The appr           |

|-------------------|--------------------|

| <b>3ibliothek</b> | Your knowledge hub |

| P                 | E N                |

| xii |        | Cont                     | ents |

|-----|--------|--------------------------|------|

|     | 6.2    | Gate Level Simulations   | 53   |

|     | 6.3    | Device Level Simulations | 59   |

| 7   | Con    | clusion                  | 83   |

| Bil | oliogi | raphy                    | 85   |

# **List of Tables**

| 2.1 | Truth table of Equation (2.1)                                                      | 10 |

|-----|------------------------------------------------------------------------------------|----|

| 3.1 | Overview of the conventional fault-tolerant design techniques discussed            | 33 |

| 3.2 | Overview of the implemented design techniques                                      | 33 |

| 5.1 | Mapping of Boolean operations to arithmetic operations of signal probabilities [1] | 44 |

# **List of Figures**

| 1.1  | 3-1 relay: (a) schematic, (b) truth table                                               | 2  |

|------|-----------------------------------------------------------------------------------------|----|

| 1.2  | 4-T relay: (a) schematic, (b) truth table                                               | 3  |

| 1.3  | 7-T relay: (a) schematic, (b) truth table                                               | 4  |

| 2.1  | Fault Injection Logic [2]                                                               | 9  |

| 2.2  | NAND gate: (a) implementation with 3-T devices, (b) fault free case (c) single stuck-on |    |

|      | fault, (d) single stuck-off fault.                                                      | 12 |

| 3.1  | Duplication with comparison [3]                                                         | 14 |

| 3.2  | Standby sparing [3]                                                                     | 15 |

| 3.3  | Pair-and-a-spare [3]                                                                    | 15 |

| 3.4  | TMR system                                                                              | 17 |

| 3.5  | Standard TMR voter [4]                                                                  | 18 |

| 3.6  | Voter with XORs, priority encoder, and a multiplexer [5]                                | 19 |

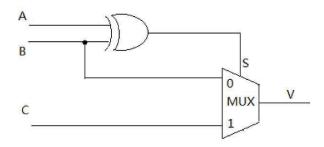

| 3.7  | Voter with multiplexer and XOR [6]                                                      | 19 |

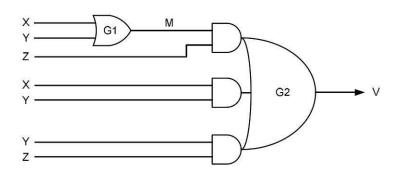

| 3.8  | Voter with OR gate and complex gate [7]                                                 | 20 |

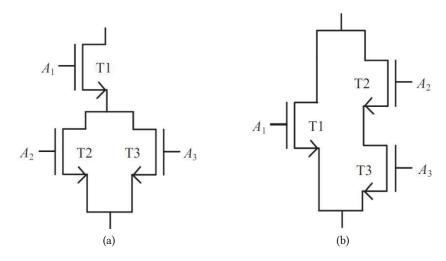

| 3.9  | Voter with triple transistor redundancy [4]                                             | 20 |

| 3.10 | Tripled design: (a) version 1, (b) version 2 [8]                                        | 21 |

| 3.11 | Quadded design: (a) version 1, (b) version 2 [8].                                       | 23 |

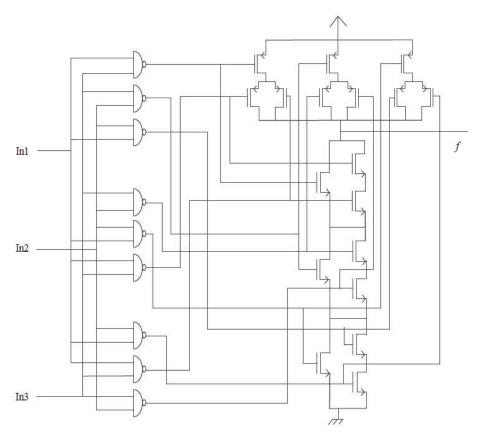

| 3.12 | C17 circuit (Section 6.1.1) implemented in QL + QD [9]                                  | 24 |

| 3.13 | C17 circuit (Section 6.1.1) implemented in TMR + TD [10]                                | 25 |

| 3.14 | Self-purging redundancy [3]                                                             | 26 |

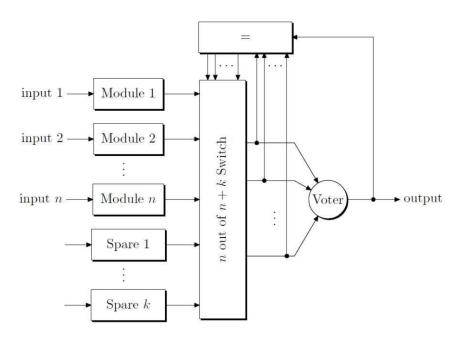

| 3.15 | N-modular redundancy with spares [3]                                                    | 27 |

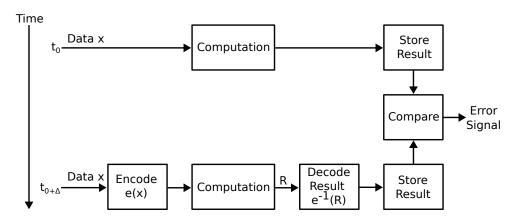

| 3.16 | Concept to detect permanent faults using time redundancy [11]                           | 29 |

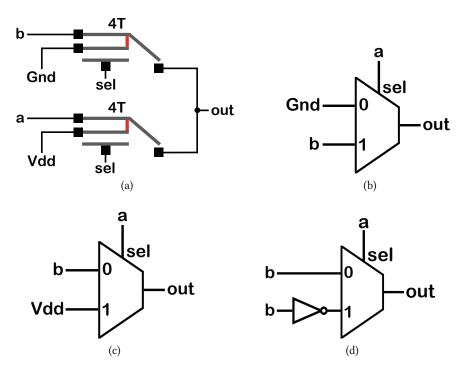

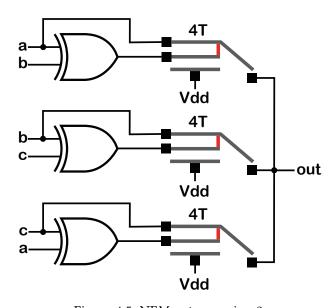

| 4.1  | (a) 2-to-1 multiplexer, (b) AND gate with multiplexer (c) OR gate with multiplexer,     |    |

|      | (d) XOR gate with multiplexer                                                           | 36 |

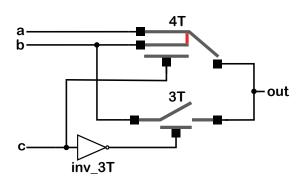

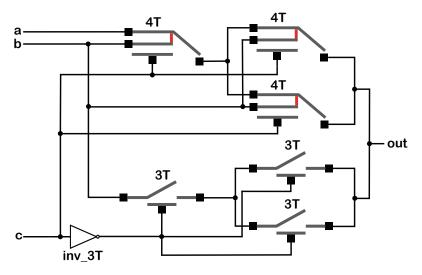

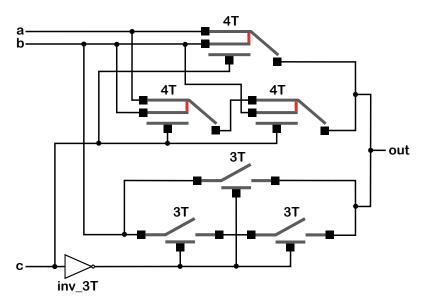

| 4.2  | NEM voter version 1                                                                          | 37 |

|------|----------------------------------------------------------------------------------------------|----|

| 4.3  | NEM voter in tripled design v1.                                                              | 37 |

| 4.4  | NEM voter in tripled design v2.                                                              | 38 |

| 4.5  | NEM voter version 2                                                                          | 39 |

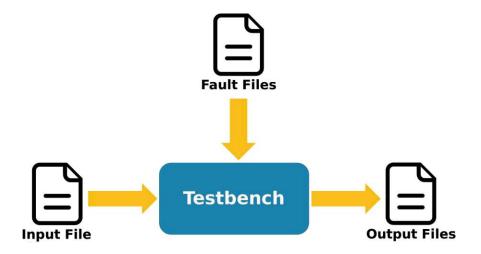

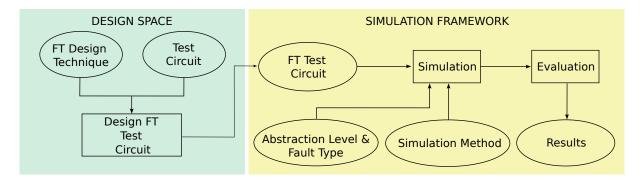

| 5.1  | Structure of the simulation framework                                                        | 42 |

| 5.2  | Inverter with stochastic encoding [1]                                                        | 44 |

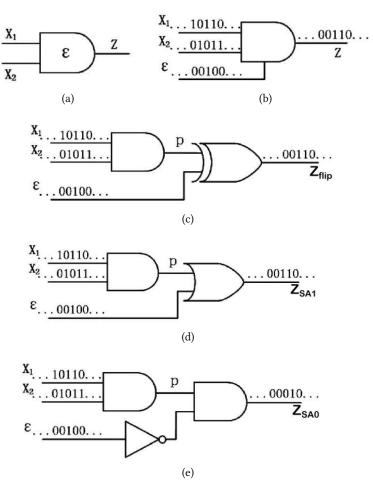

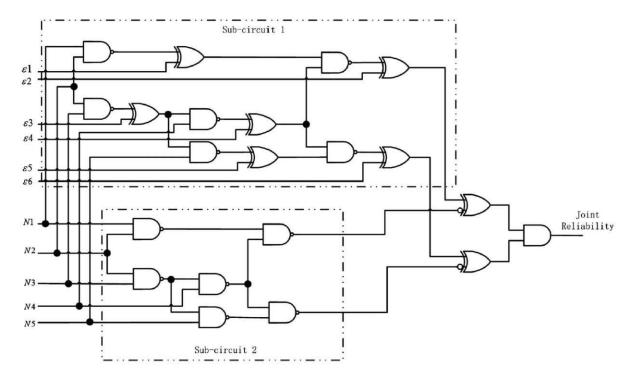

| 5.3  | AND gate: (a) unreliable gate, (b) stochastic logic implementation, (c) SCM for flipping     |    |

|      | error, (d) SCM for stuck-at-1 fault, (e) SCM for stuck-at-0 fault [1]                        | 45 |

| 5.4  | Stochastic transistor model for flipping error [12]                                          | 45 |

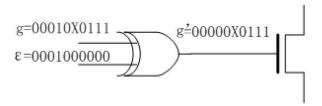

| 5.5  | Architecture utilizing SCMs to assess the reliability of the C17 circuit [1]                 | 47 |

| 6.1  | Workflow from design to evaluation.                                                          | 51 |

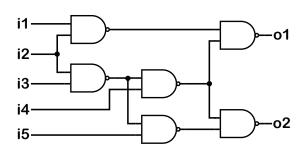

| 6.2  | C17 circuit                                                                                  | 52 |

| 6.3  | Full adder circuit.                                                                          | 52 |

| 6.4  | 74283 fast adder circuit [13]                                                                | 53 |

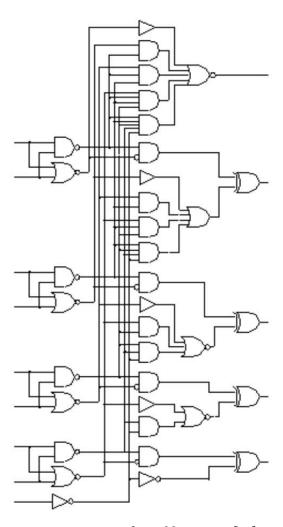

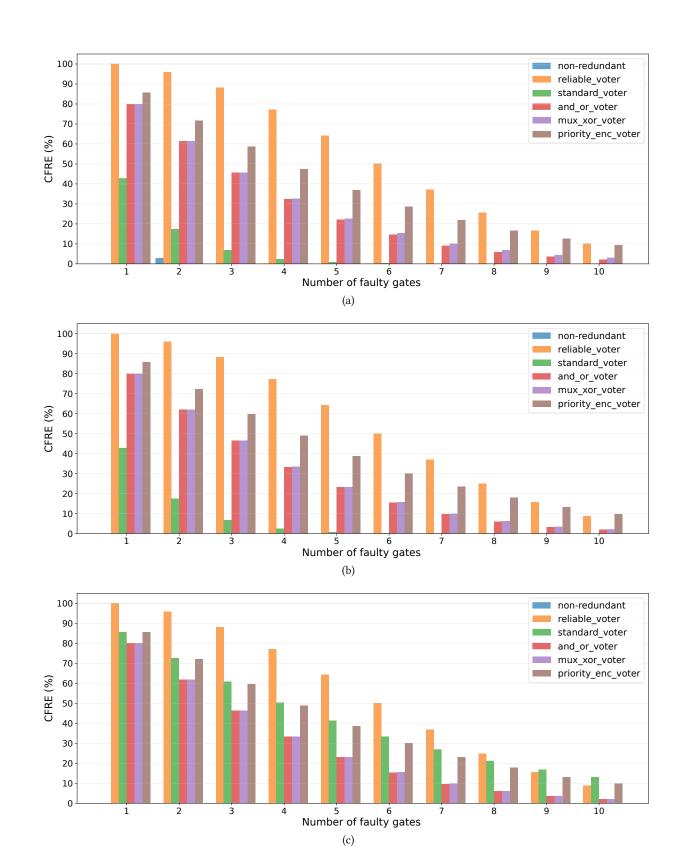

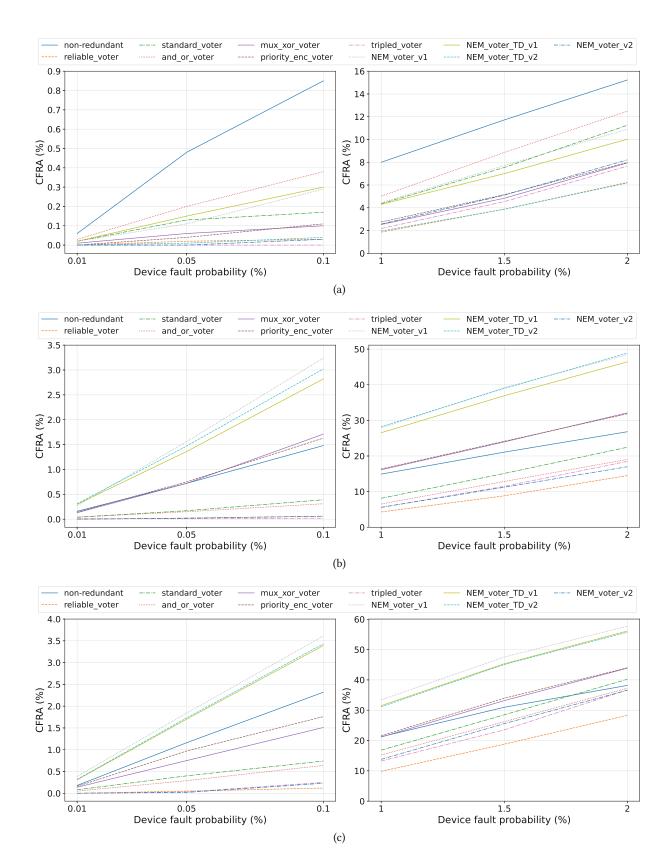

| 6.5  | CFRA for the full adder with TMR and different voter designs: (a) flipping error, (b) stuck- |    |

|      | at-0, (c) stuck-at-1                                                                         | 55 |

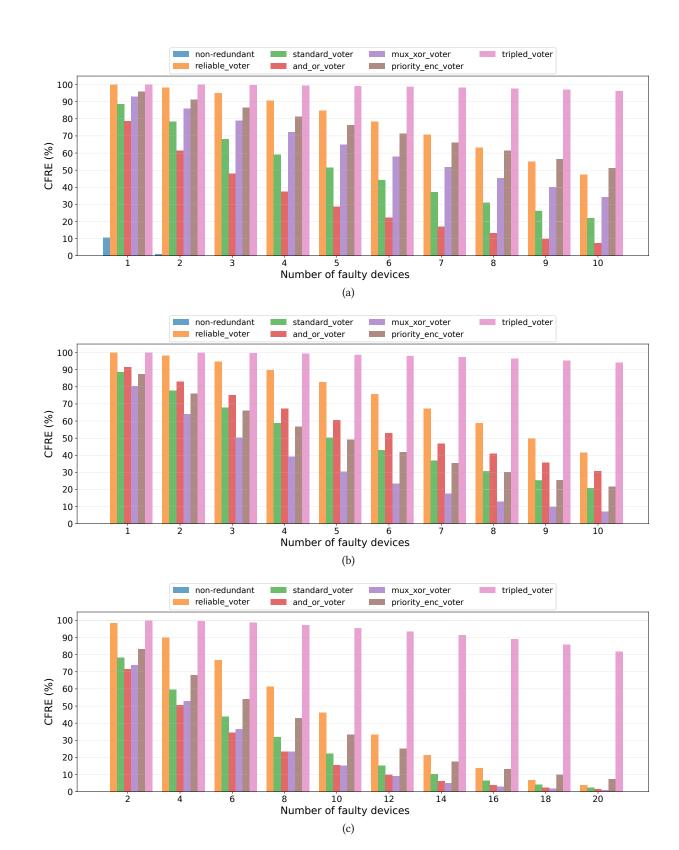

| 6.6  | CFRE for the full adder with TMR and different voter designs: (a) flipping error, (b) stuck- |    |

|      | at-0, (c) stuck-at-1                                                                         | 56 |

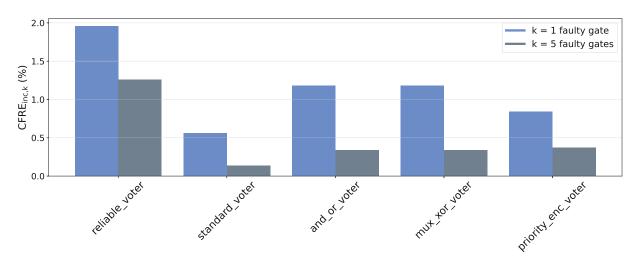

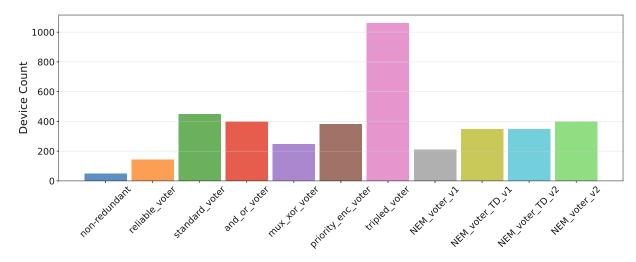

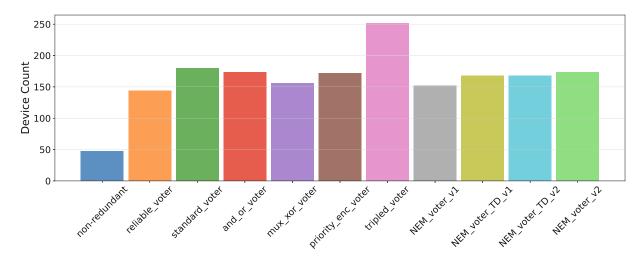

| 6.7  | Gate count of the full adder with TMR and different voter designs                            | 57 |

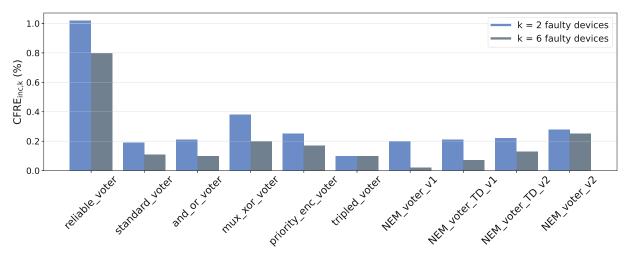

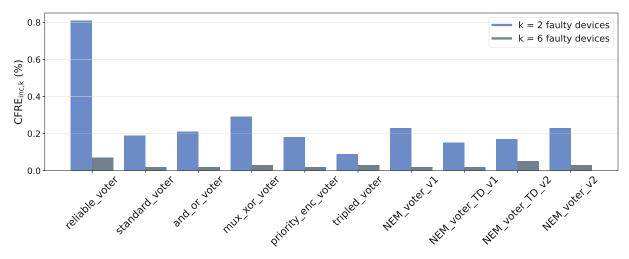

| 6.8  | Increase in CFRE per additional gate for the full adder with TMR averaged over all fault     |    |

|      | types                                                                                        | 58 |

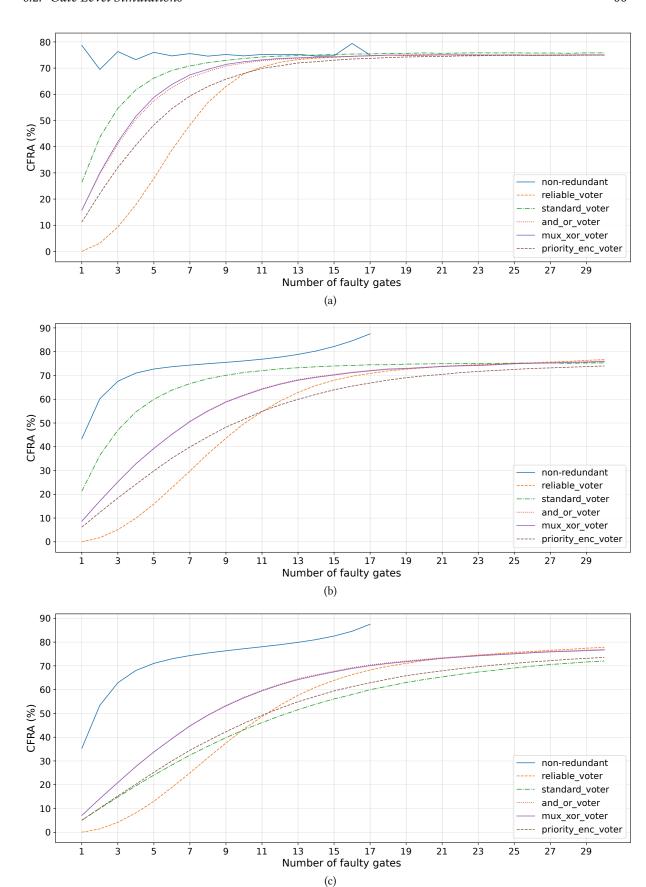

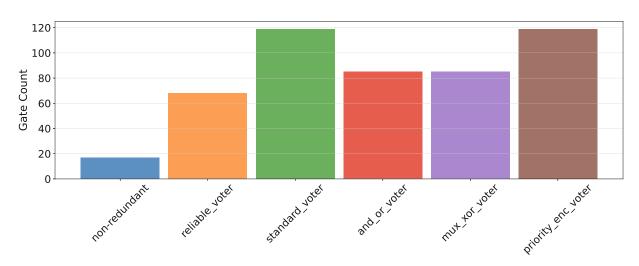

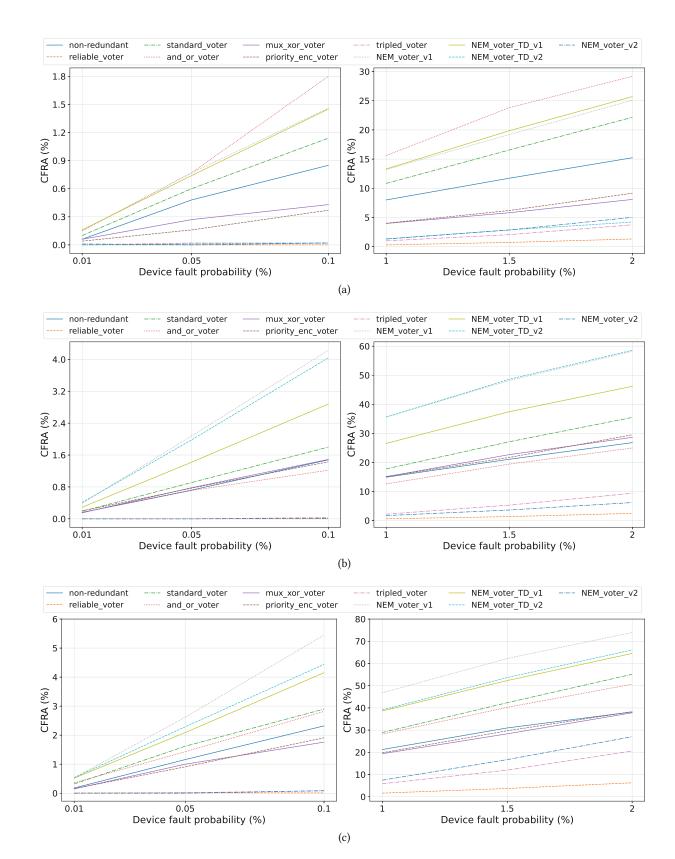

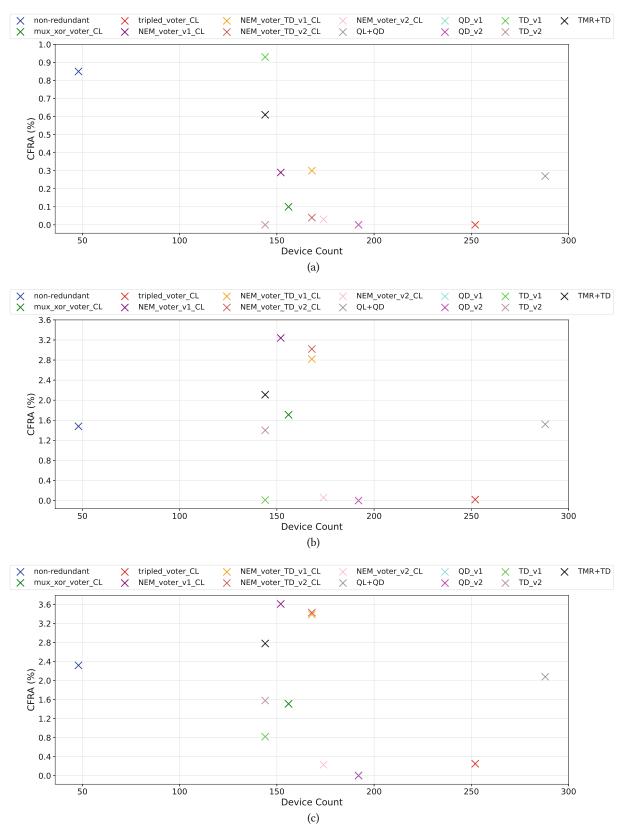

| 6.9  | CFRA for the full adder with TMR applied at gate level and different voter designs:          |    |

|      | (a) stuck-off, (b) stuck-on, (c) mixed faults (50%/50%)                                      | 60 |

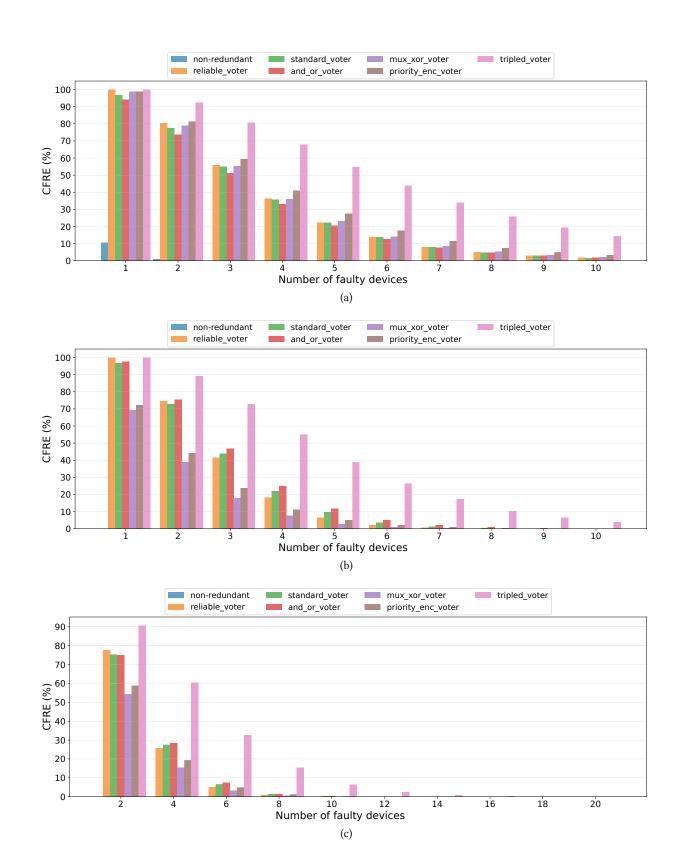

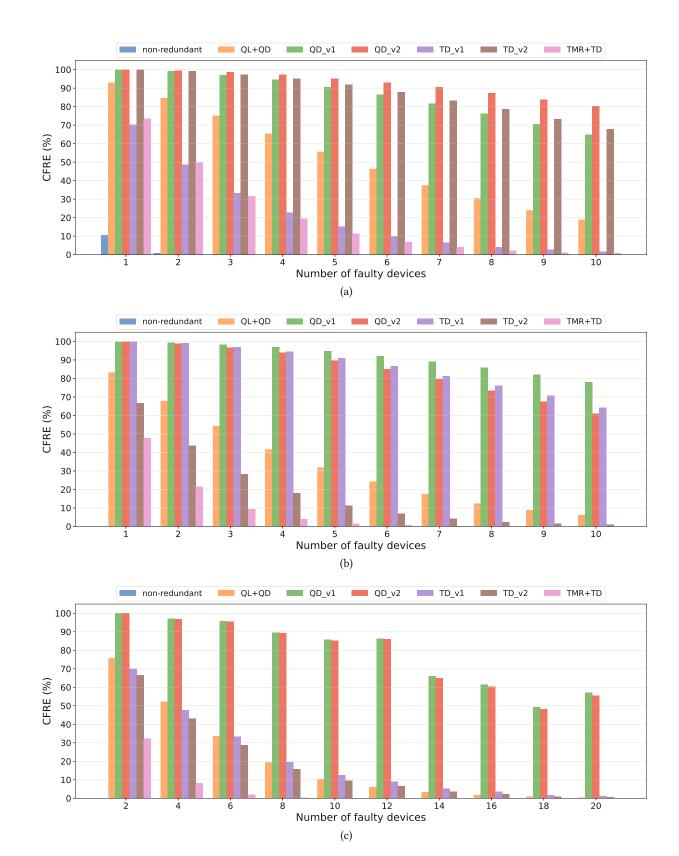

| 6.10 | CFRE for the full adder with TMR applied at gate level and conventional voter designs:       |    |

|      | (a) stuck-off, (b) stuck-on, (c) mixed faults (50%/50%)                                      | 62 |

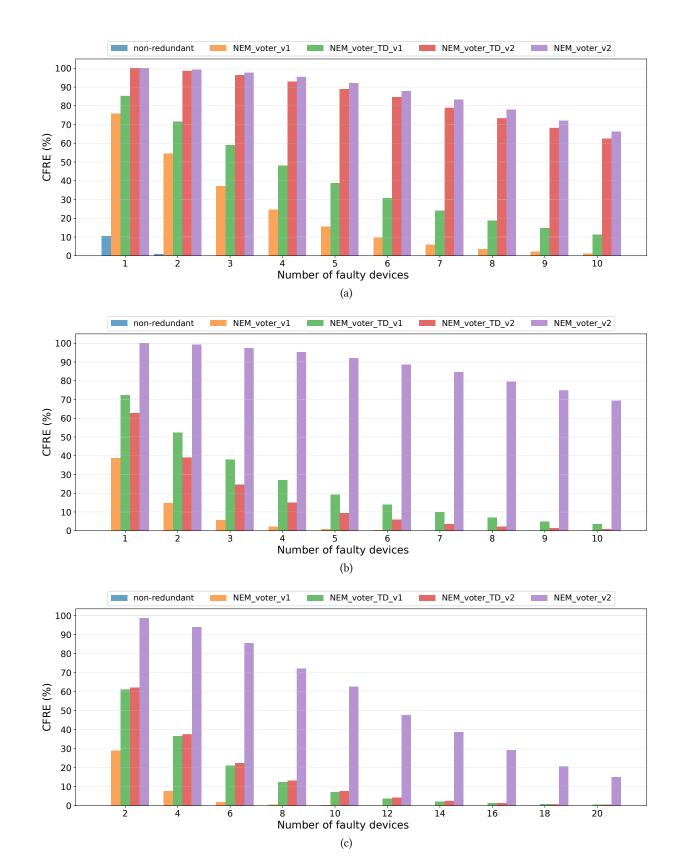

| 6.11 | CFRE for the full adder with TMR applied at gate level and NEM voter designs: (a) stuck-     |    |

|      | off, (b) stuck-on, (c) mixed faults (50%/50%)                                                | 63 |

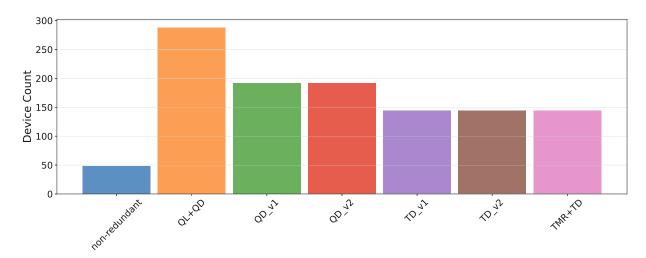

| 6.12 | Device counts of the full adder with TMR applied at gate level and different voter designs.  | 64 |

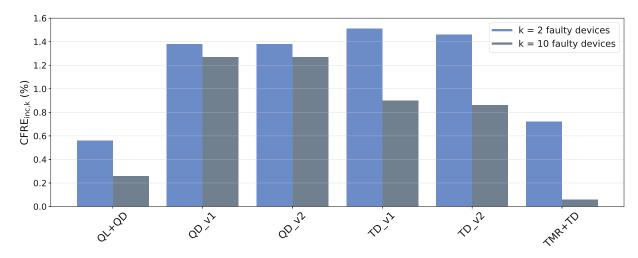

| 6.13 | Increase in CFRE per additional device for the full adder with TMR applied at gate level     |    |

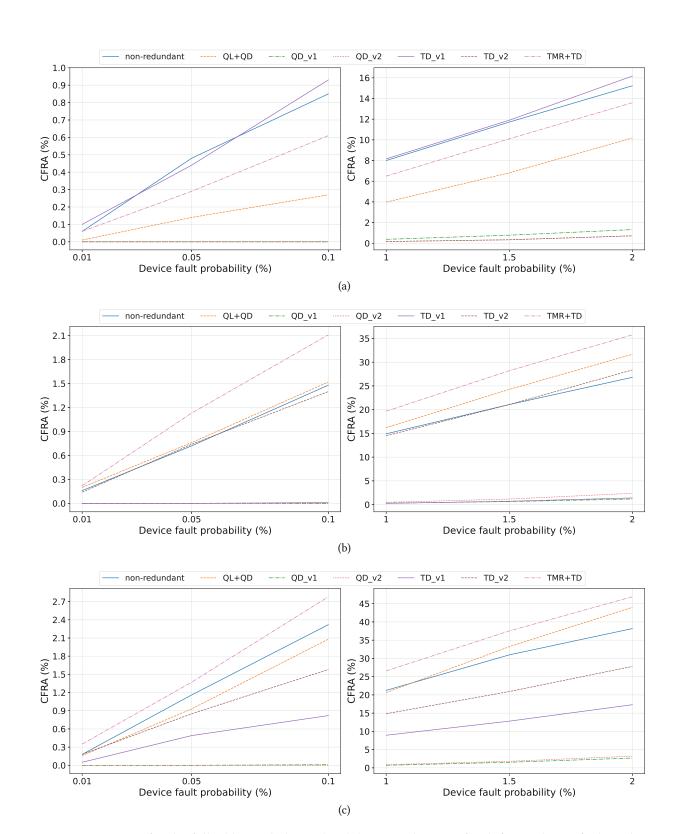

|      | averaged over all fault types                                                                | 64 |

| 6.14 | CFRA for the full adder with TMR applied at gate level for different device fault proba-     |    |

|      | bilities: (a) stuck-off, (b) stuck-on, (c) mixed faults (50%/50%)                            | 66 |

|      |                                                                                              |    |

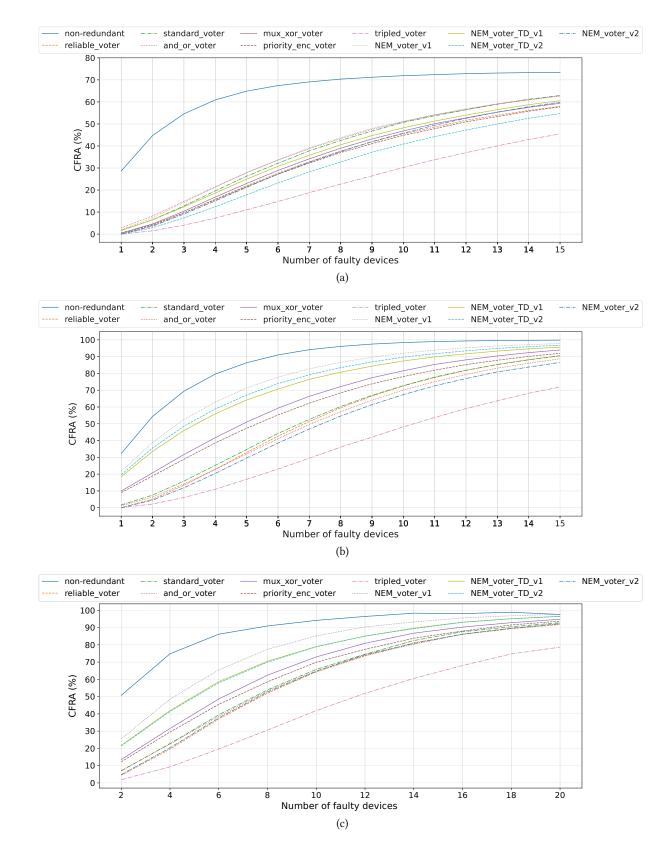

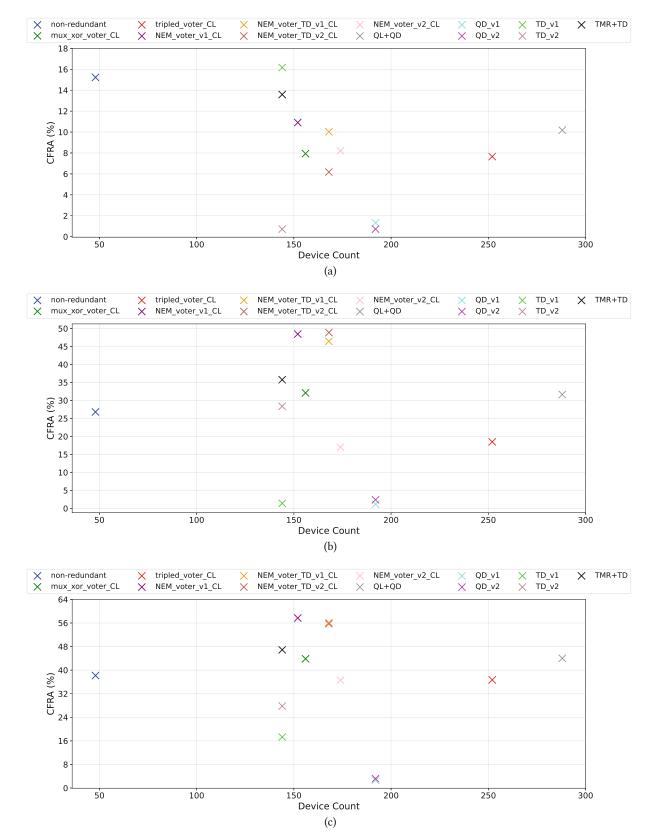

| 6.15 | CFRA for the full adder with TMR applied at circuit level and conventional voter de-               |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | signs: (a) stuck-off, (b) stuck-on, (c) mixed faults                                               | 68 |

| 6.16 | CFRE for the full adder with TMR applied at circuit level and conventional voter designs:          |    |

|      | (a) stuck-off, (b) stuck-on, (c) mixed faults.                                                     | 69 |

| 6.17 | CFRE for the full adder with TMR applied at circuit level and NEM voter designs:                   |    |

|      | (a) stuck-off, (b) stuck-on, (c) mixed faults.                                                     | 70 |

| 6.18 | Device counts of the full adder with TMR applied at circuit level and different voter              |    |

|      | designs                                                                                            | 72 |

| 6.19 | Increase in CFRE per additional device for the full adder with TMR applied at circuit              |    |

|      | level averaged over all fault types                                                                | 72 |

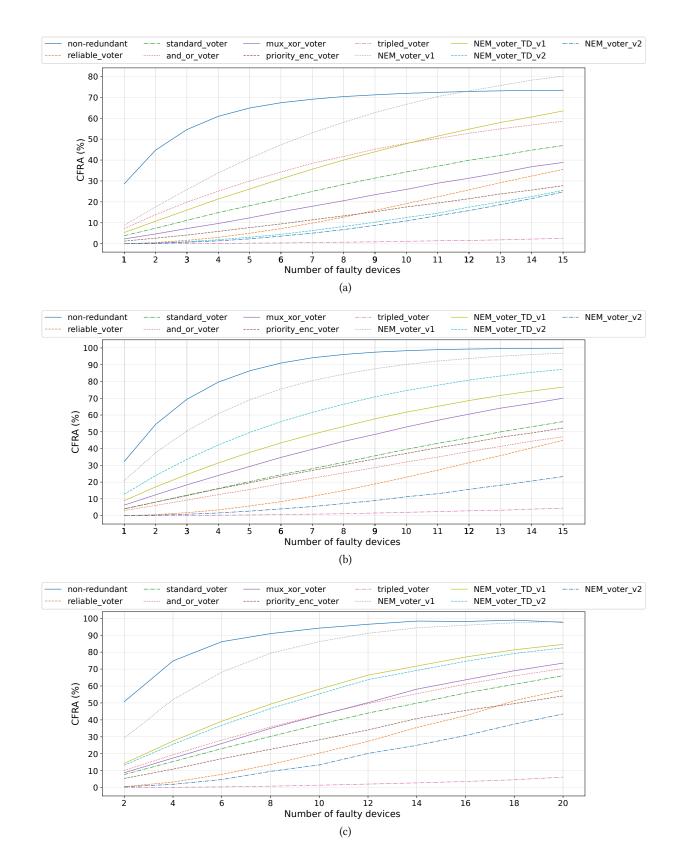

| 6.20 | CFRA for the full adder with TMR applied at circuit level for different device fault prob-         |    |

|      | abilities: (a) stuck-off, (b) stuck-on, (c) mixed faults (50%/50%)                                 | 73 |

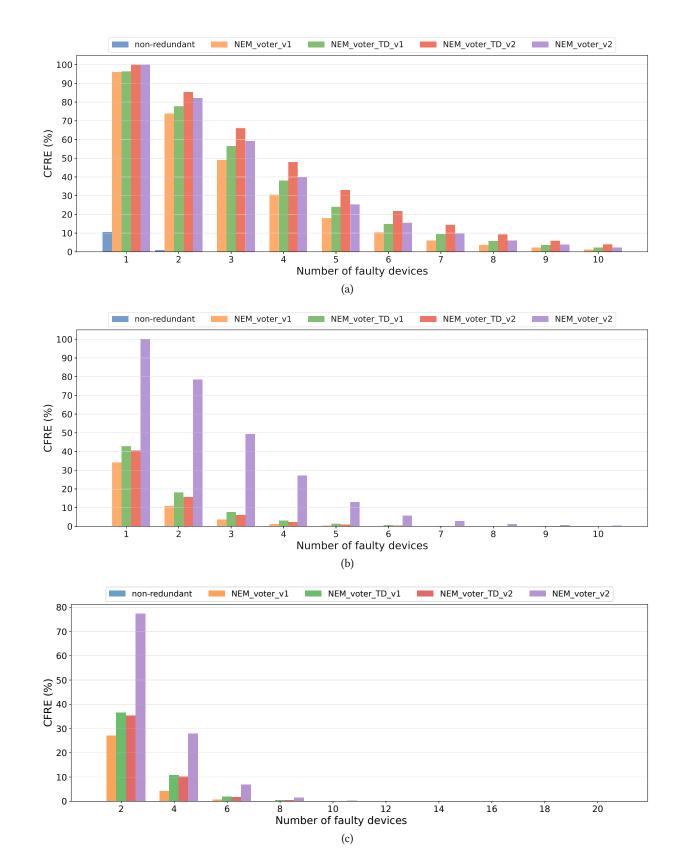

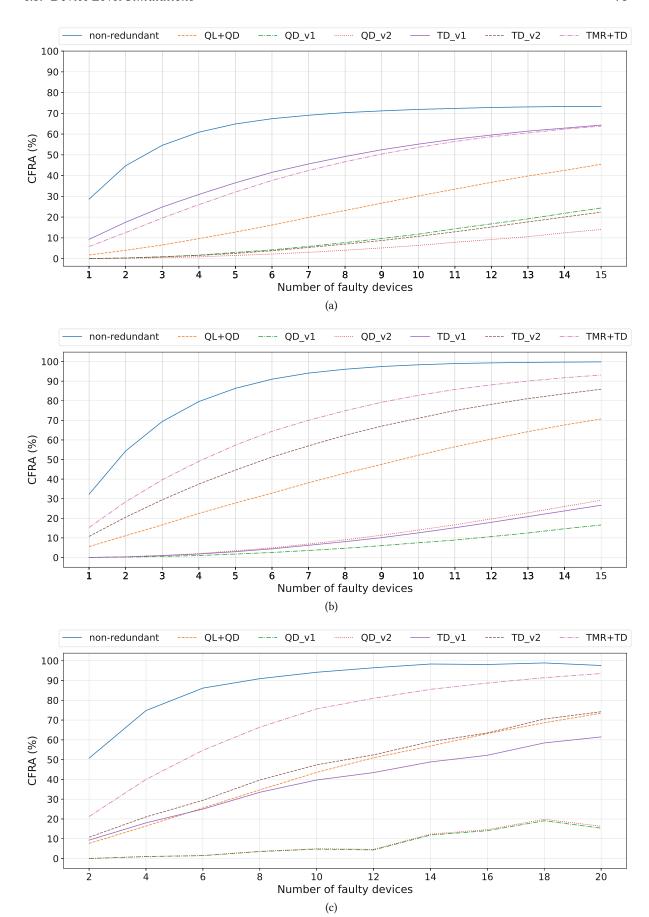

| 6.21 | CFRA for the full adder with device level design techniques: (a) stuck-off, (b) stuck-on,          |    |

|      | (c) mixed faults                                                                                   | 75 |

| 6.22 | CFRE for the full adder with device level design techniques: (a) stuck-off, (b) stuck-on,          |    |

|      | (c) mixed faults                                                                                   | 76 |

| 6.23 | Device counts of the full adder with device level design techniques                                | 77 |

| 6.24 | Increase in CFRE per additional device for the full adder with device level design tech-           |    |

|      | niques averaged over all fault types                                                               | 78 |

| 6.25 | CFRA for the full adder with device level design techniques for different device fault             |    |

|      | probabilities: (a) stuck-off, (b) stuck-on, (c) mixed faults (50%/50%)                             | 79 |

| 6.26 | CFRA and device count for the full adder with various fault-tolerant design techniques             |    |

|      | and $0.1\%$ device fault probability: (a) stuck-off, (b) stuck-on, (c) mixed faults (50%/50%).     | 81 |

| 6.27 | CFRA and device count for the full adder with various fault-tolerant design techniques             |    |

|      | and $2\%$ device fault probability: (a) stuck-off, (b) stuck-on, (c) mixed faults ( $50\%/50\%$ ). | 82 |

# Acronyms

**3-T** 3-terminal. xv, 2, 3, 10, 12, 35, 36, 37

**4-T** 4-terminal. xv, 3, 35, 36, 37, 38

7-T 7-terminal. xv, 3, 4

ALU arithmetic logic unit. 29

**CFRA** Circuit Failure Rate. xvi, xvii, 48, 49, 54, 55, 57, 59, 60, 65, 66, 67, 68, 71, 73, 74, 75, 77, 79, 80, 81, 82

CFRE Circuit Fault Resilience. xvi, xvii, 49, 54, 56, 57, 58, 61, 62, 63, 64, 67, 69, 70, 71, 72, 74, 76, 77, 78

**CMOS** complementary metal-oxide-semiconductor. iii, iv, xi, 1, 2, 7, 10, 13, 14, 16, 18, 20, 21, 22, 24, 26, 28, 30, 32, 34, 35

CRC Cyclic Redundancy Check. 31

**FD** Fault Detection. 14, 15, 16

FIL Fault Injection Logic. 9, 45

IC integrated circuit. 1

**IoT** Internet of Things. 1

NCG nano-crystalline graphite. 8

NEM nanoelectromechanical. iii, iv, xi, xvi, xvii, 1, 2, 3, 4, 7, 9, 10, 13, 16, 17, 21, 22, 25, 26, 28, 30, 32, 35, 36, 37, 38, 39, 40, 46, 59, 61, 63, 67, 70, 83, 84

NMR N-Modular Redundancy. 17, 26, 27

PGM Probabilistic Gate Model. 43, 44

**QD** Quadded Design. xv, 22, 23, 24, 26, 74, 77

QL Quadded Logic. xv, 22, 23, 24

SCM Stochastic Computation Model. xvi, 43, 44, 45, 46, 47

**SET** Single Event Transient. 7

**SEU** Single Event Upset. 7

**SOI** silicon-on-insulator. 2

**TD** Tripled Design. xv, 21, 22, 23, 25, 26, 74, 77, 80

TMR Triple Modular Redundancy. xi, xv, xvi, xvii, 16, 17, 18, 23, 25, 26, 35, 53, 54, 55, 56, 57, 58, 59, 60,  $61,\,62,\,63,\,64,\,65,\,66,\,67,\,68,\,69,\,70,\,71,\,72,\,73,\,74,\,77,\,80,\,83,\,84$

TRL Technology Readiness Level. iii, iv

VIV Vulnerable Input Vector. 49

### Chapter 1

### Introduction

The continuous advancements in integrated circuit (IC) technology and artificial intelligence have lead to a paradigm shift in the development and application of technological devices, especially within the industrial sector. Conventional manufacturing practices are gradually being replaced by automated processes that rely on smart, self-monitoring devices with high interconnectivity. To describe this evolution, the term Internet of Things (IoT) was coined, which refers to a system that integrates sensors, actuators, controllers, cloud applications, and data storage within a communication network. In this network, components that monitor or directly interact with physical processes often have to deal with harsh environmental conditions, such as high temperatures or high radiation doses. Additionally, realtime requirements often need to be considered, which makes it reasonable to design these components as edge devices. These edge devices have limited resources and power supply, so there is a need for light-weight algorithms and technology with low leakage current.

The use of complementary metal-oxide-semiconductor (CMOS) technology in extreme environment is usually not practicable, as CMOS suffers from inherent limitations. High temperatures reduce carrier mobility, leading to reduced transistor switching speed and overall degraded circuit performance. Additionally, increased leakage currents cause power consumption to rise and a shift of the threshold voltage in MOSFETS may affect the switching characteristics of the transistor. Moreover, radiation effects can cause transient or permanent errors in the circuit, such as bit flips, latch-ups etc. Due to these circumstances, several other technological alternatives have been proposed. However, alternative technologies often require complex manufacturing processes in specialist foundries and cannot be integrated into mainstream semiconductor factoring.

The i-EDGE project introduces nanoelectromechanical (NEM) relays as a promising solution. NEM relays can act as a substitute for complementary CMOS transistors when designing components for edge applications. It stays operational at temperatures up to 300 °C [14], has high radiation hard-

| Gate | Source | Drain |  |

|------|--------|-------|--|

| 0    | 0      | Z     |  |

| 0    | 1      | 1     |  |

| 1    | 0      | 0     |  |

| 1    | 1      | Z     |  |

| (b)  |        |       |  |

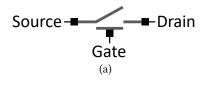

Figure 1.1: 3-T relay: (a) schematic, (b) truth table.

ness [15] and operates with zero standby power [16-18]. The NEM technology consists of different device primitives used for modelling logic circuits and non-volatile memory. The following section elaborates on the design and the functional behaviour of these NEM devices.

### **NEM Devices in i-EDGE** 1.1

The i-EDGE project introduces NEM switching technology to substitute or complement conventional CMOS technology. The basic set of NEM devices for modelling logic circuits and non-volatile memory consists of three different device types. These NEM relays are fabricated on a wafer using a standard silicon-on-insulator (SOI) CMOS foundry process. This wafer is then placed on top of a prefabricated metal interconnect stack, which can be shared with CMOS circuitry located on the bottom side. Thus, the fabrication of NEM circuits can be integrated into established mainstream foundries while maintaining compatibility with CMOS technology [19-21]. The modelling and fabrication of these devices are done by project partners and are not part of this thesis.

### 3-Terminal Relay 1.1.1

The 3-terminal (3-T) device is a simple relay with a gate, source, and drain terminal (Fig. 1.1a). Its geometry features two parallel beams that are connected via a mechanical coupler and act as a cantilever [22,23]. The relay can be actuated by applying a potential difference between the source and the gate. The voltage required to pull the beams in is called pull-in voltage. When the beams are actuated, an electrical contact between the source and the drain is established. The beams pull out and return to their original position when the voltage is removed. The functionality of the relay is depicted in the truth table shown in Fig. 1.1b. Digital logic gates in complementary CMOS technology are modelled using PMOS and NMOS transistors, which constitute the pull-up and pull-down networks. Since the pull-in voltage can be applied to either the gate or the source terminal to actuate the 3-T device, the switching characteristics of NMOS and PMOS transistors can be emulated. This allows for the modelling of logic gates using only 3-T devices.

| Gate | Body/Beam | Source | Drain |

|------|-----------|--------|-------|

| 0    | 0         | 0/1    | Z     |

| 1    | 0         | 0/1    | 0/1   |

| 0    | 1         | 0/1    | 0/1   |

| 1    | 1         | 0/1    | Z     |

| (b)  |           |        |       |

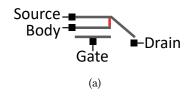

Figure 1.2: 4-T relay: (a) schematic, (b) truth table.

### 4-Terminal Relay 1.1.2

The 4-terminal (4-T) device is geometrically equivalent to the 3-T device [23]. However, in the 4-T device, the coupler connecting the two beams is electrically insulating (Fig. 1.2a). Thus, the data signal, applied at the source, is separated from the actuation voltage (Fig. 1.2b). To actuate the relay, a potential difference exceeding the pull-in voltage has to be established between the gate and the body. Therefore, this device extends the functionality of the 3-T device and its utilization allows for designs with lower device count. Applications include multiplexer and demultiplexer designs, as well as writing and reading circuitry for non-volatile memory, when used in conjunction with the other NEM relays.

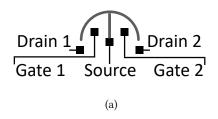

### 7-Terminal Relay 1.1.3

The 7-terminal (7-T) device is a non-volatile relay that can perform rotational movements and exerts non-volatile behaviour [24,25]. It has two gate terminals, two drain terminals, and one source terminal, which is connected to a semicircular beam (Fig. 1.3a). In its neutral position, the relay is actuated by applying a voltage to one of the gate terminals. When the applied voltage exceeds the actuation threshold, the potential difference between the driven gate and the beam is large enough to overcome the stiffness of the hinge to which the beam is anchored. The beam then rotates either clockwise or anti-clockwise, depending on which gate is driven, and establishes electrical contact with one of the drains. When the actuation voltage is removed or both gates have the same potential difference to the beam, it remains in its position, due to adhesive forces. To move the beam to the opposite direction, the other gate has to be driven, to overcome the adhesion force between the beam and the drain. The functionality of the relay is depicted in the truth table shown in Fig. 1.3b. The non-volatile behaviour of this relay allows it to store information, making it suitable for modelling non-volatile memory [26].

### **Research Questions and Expected Results** 1.2

Due to the novelty of this technology, the manufacturing of NEM devices is not mature enough to fabricate circuits with sufficient yield. Moreover, physical defects in NEM devices may occur during

| Gate 1 | Gate 2 | Source | Drain 1 | Drain 2 |

|--------|--------|--------|---------|---------|

| 0      | 0      | 0      | Z       | Z       |

| 0      | 1      | 0      | Z       | 0       |

| 0      | 1      | 1      | 1       | Z       |

| 1      | 0      | 0      | 0       | Z       |

| 1      | 0      | 1      | Z       | 1       |

| 1      | 1      | 1      | Z       | Z       |

| 0      | 0      | X      | Z       | Z       |

| 1      | 1      | X      | Z       | Z       |

|        |        | (b)    |         |         |

Figure 1.3: 7-T relay: (a) schematic, (b) truth table.

operation and affect their functionality, worsening the circuit's reliability. Therefore, it is necessary to make the circuit fault tolerant during the design phase by applying and evaluating various design techniques. Consequently, this thesis addresses the following research questions:

- What are suitable fault models for NEM circuits?

- Which established fault-tolerant circuit techniques can be utilized on NEM-based circuits?

- Can NEM devices be utilized to enhance existing fault-tolerant design techniques or to propose new designs?

- What fault tolerance can be obtained?

In the first step, a fault model is formulated. The physical defects that potentially occur in NEM devices are discussed. Based on this analysis, fault models are defined at different abstraction levels. The purpose of a fault model is to provide an abstract representation of how physical defects in NEM relays impact the circuit at the specified abstraction levels. Thus, it is expected that the fault models depict the real physical behaviour of defective components with sufficient accuracy and provide the necessary information on how to inject the corresponding faults into the modelled circuits during simulation.

In the next step, conventional fault-tolerant design techniques are reviewed and assessed for their applicability to NEM circuits. Fault-tolerant design techniques usually exploit some form of redundancy in the domains of hardware, time or information. Different concepts of design techniques are reviewed and elaborated upon. The chosen design techniques are expected to be suitable for NEM technology and will be applied to experimental circuits later on. Further, it is examined whether specific design techniques can be simplified or enhanced through the use of NEM devices. Additionally, new designs leveraging the unique functionalities of NEM devices are proposed.

To simulate the designs, a simulation framework has been developed. The framework can be expected to simulate NEM circuit models and inject faults according to the defined fault models during

TU **Bibliothek**, Die approbierte gedruckte Originalversion dieser Diplomarbeit ist an der TU Wien Bibliothek verfügbar wern vour knowledge hub The approved original version of this thesis is available in print at TU Wien Bibliothek.

simulation. The simulation setup can be modified via various parameters. Furthermore, the simulation process, as well as the evaluation process, was automated as much as possible.

Lastly, the outputs of the simulations are analysed. The results are expected to show that the implemented design techniques are effective against the identified faults. The design space is explored concerning fault tolerance and device count. The achievable fault tolerance for the specified fault types is determined, and trade-offs are discussed using different metrics.

### **Chapter 2**

# **Physical Defects and Fault Models**

This chapter elaborates on potential defects in NEM relays and further defines appropriate fault models. In the domain of hardware, a fault refers to the abnormal behaviour of a component or device and can further be classified into three types: transient, intermittent, and permanent faults. Transient faults usually persist temporarily and disappear without any intervention. In CMOS technology, transient faults are generally divided into Single Event Transients (SETs) and Single Event Upsets (SEUs). A SET refers to a sudden spike in a voltage signal within a circuit, which can be caused by the strike of a high-energy particle striking. A SEU, on the other hand, describes a change to an erroneous state in a memory cell. Intermittent faults occur and disappear sporadically. Permanent faults are consistent and require actions such as masking or repair to be removed. A fault can manifest as an error, which describes a deviation in a value or state within a system. If an error is not corrected, it may lead to system failure, meaning that the system is no longer capable of providing its intended service.

The purpose of a fault model is to provide an abstract view of the functional behaviour of a faulty device or component, making it possible to model and analyse a circuit's behaviour in the presence of defects. A fault model ideally covers numerous defects that would be impractical to model individually. Furthermore, a fault model can be defined at various levels of abstraction. Hardware faults are usually caused by physical defects that depend on the technology used. Therefore, a technology-specific investigation of the relevant components and devices is necessary.

### Physical Defects in NEM Relays 2.1

Since NEM relays are essentially physical switches, most defects that occur are mechanical in nature. These physical defects can appear either during manufacture, lowering the yield, or during operation, decreasing the circuit's reliability. During manufacture, any terminal of a NEM relay can be expected to short to any other or collapse down to the substrate. This collapse usually cannot be recovered from. Steady improvements in the fabrication process are expected to eventually lead to more mature manufacturing, narrowing this problem down to a satisfactory degree.

Under normal operation, regular use of the devices will wear down the conductive contact material at the tip of the beam, leading to increased resistance up to a point where sufficient electrical conductivity is no longer ensured. Additionally, oxidation might accelerate the increase of resistance. On the other hand, stiction might prevent the beam from returning to its neutral position, causing the relay to remain permanently closed. It is anticipated that further improvements in the fabrication process will mitigate this problems, making the relays more durable. Coating the contact surface with nanocrystalline graphite (NCG) has been tested as a solution and yielded promising results [22]. However, it must still be assumed that these defects may occur after a certain amount of switching cycles, so fault models need to take them into consideration. Lastly, overdriving the device causes the beam to make contact with the gate, shorting it to both the source and the drain. The beam is flexible enough to avoid breaking, but it cannot recover due to the surface adhesion being too large.

All the described defects can be classified as permanent faults. Transient faults, on the other hand, might occur when a device gets stuck and eventually resolves itself after some time without any intervention. Since only a small number of individual devices have been manufactured so far, there is no statistical data available to cover a device's fault probability over time or fault distribution across the chip area. Still, it is expected that devices will start to fail due to the on-resistance becoming too high after a certain number of switching cycles. At this point, a small number of devices might begin to fail, followed by an increasingly larger portion, meaning that the fault probability over time likely follows an exponential function. However, in this thesis, the focus is set on static permanent faults, as this approach is sufficient to investigate faults regardless of their temporal and spatial distribution. Aside from that, most fault-tolerant design techniques that address permanent faults are also applicable to correcting transient faults.

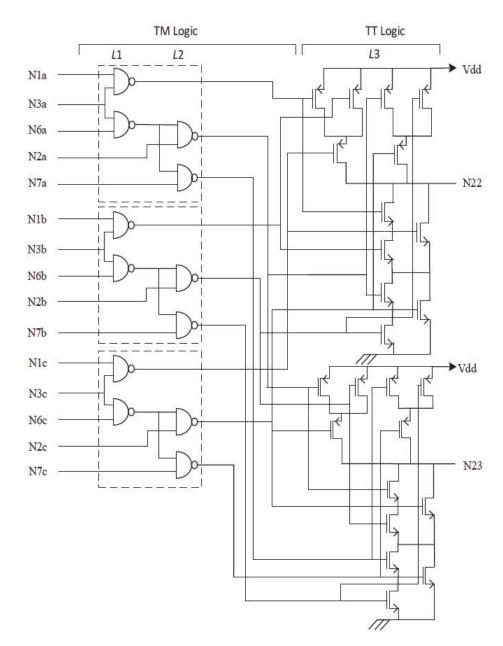

### **Gate Level** 2.2

First, the faulty behaviour is examined from a gate level perspective. At this level of abstraction, the experimental circuits are modelled in Verilog using a structural description of primitive gates, such as NAND, NOR, AND, OR, etc. In the case of a fault, it is assumed that the functional behaviour of the corresponding gate is affected, potentially manifesting as a stuck input or output node, or as a flipped output value. This means that the affected node is either permanently set to zero, set to one, or its value is flipped. The advantage of this fault model is its low complexity and its ability to cover a variety of defects. The terms used to describe this fault model are:

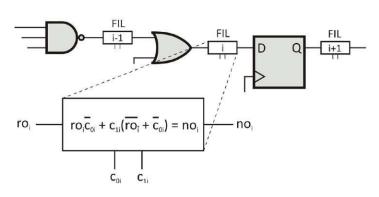

Figure 2.1: Fault Injection Logic [2].

- **stuck-at-0**: The affected node is permanently set to zero.

- **stuck-at-1**: The affected node is permanently set to one.

- **flipping error**: The value of the affected node is flipped.

To assess the circuit's fault tolerance, these faults need to be injected during the simulation according to the fault model. This is done using a Fault Injection Logic (FIL) [2]. The FIL is a Verilog module that is designed to inject faults of the desired type into the circuit. Each gate has a FIL module placed at its output, whereas the index i denotes the FIL module associated with the i-th gate (Figure 2.1). The input  $ro_i$  of the FIL module is connected to the output of the *i*-th gate, while its output  $no_i$  is connected to the node where the gate's output was previously connected. To determine the output of the FIL, the Boolean equation

$$no_i = ro_i \overline{c_{0i}} + c_{1i} (\overline{ro_i} + \overline{c_{0i}}) \tag{2.1}$$

is used. The result of this equation is primarily dependent on the control inputs  $c_{0i}$  and  $c_{1i}$ . Thus, the fault type can be selected by setting  $c_{0i}$  and  $c_{1i}$  accordingly. For example, a stuck-at-0 fault corresponds to  $c_{0i}$  set to 1 and  $c_{1i}$  set to 0, whereas a stuck-at-1 fault corresponds to  $c_{0i}$  set to 0 and  $c_{1i}$  set to 1. When both  $c_{0i}$  and  $c_{1i}$  are set to 1, the gate output is flipped, while setting  $c_{0i}$  and  $c_{1i}$  to 0 leaves the gate output unchanged (Table 2.1). The control inputs of the FIL are set in the simulation environment later to inject the different fault types.

Although the defined gate level fault models are widely used in fault simulations, they have their limitations due to their reduced complexity. Defects in NEM relays can impact the behaviour of the gates in various ways. That means that the occurrence of a defect does not always result in a flipped or stuck gate output. To obtain a more accurate understanding of a gate's behaviour under the influence of defects in one or more of its NEM relays, it is necessary to investigate the device level, which lies one abstraction layer deeper.

Table 2.1: Truth table of Equation (2.1).

| $c_{1i}$ | $c_{0i}$ | $no_i$            |

|----------|----------|-------------------|

| 0        | 0        | roi               |

| 0        | 1        | 0                 |

| 1        | 0        | 1                 |

| 1        | 1        | $\overline{ro_i}$ |

### **Device Level** 2.3

At this abstraction level, the faulty behaviour of the NEM devices is examined to define a fault model. With this approach, a more accurate view on the behaviour of the faulty circuit can be obtained. Based on the discussion of potential physical defects above, it can be concluded that many faults during manufacture or operation lead to terminals being shorted, causing the NEM relay to behave like a closed switch. On the other hand, wear during operation will cause a NEM relay to behave as if it were permanently open. Thus, a simple fault model with the following cases is assumed:

- **stuck-on**: The relay is permanently closed.

- **stuck-off**: The relay is permanently open.

At device level, the NEM relays are modelled as Verilog modules in behavioural description. The fault mechanism, which implements the defined fault model, is integrated into the modules and can be activated via a port. The logic gates are then modelled using these modules of the NEM relays, whereas the experimental circuits are modelled using a structural description of the different logic gates. When designing the logic gates, special care must be taken to ensure the correct computation of the gate's output when one of the aforementioned faults occurs in one of its NEM relays.

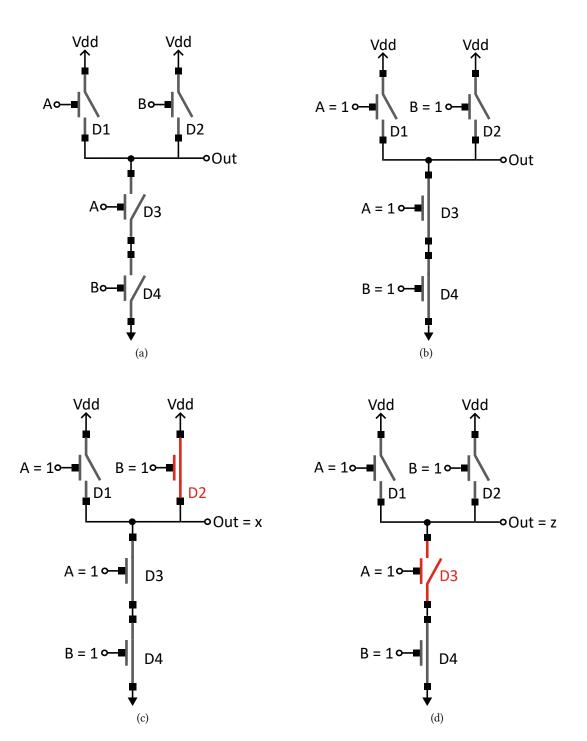

To better understand how the function of a gate can be affected by the presence of different faults, a simple NAND gate implemented with 3-T devices will serve as an example (Figure 2.2a). In this gate, the PMOS transistors, which constitute the pull-up network in a traditional CMOS implementation, are replaced by the 3-T devices D1 and D2. The source terminals of D1 and D2 are connected to  $V_{dd}$ , while their drain terminals are connected to the output node. Conversely, the NMOS transistors, which constitute the pull-down network in a CMOS implementation, are substituted with the 3-T devices D3 and D4. The drain terminal of D3 is connected to the output node, and its source terminal is connected to the drain terminal of D4, with the source terminal of D4 connected to ground. In a fault free case where the inputs A and B are both set to one, D1 and D2 are open, while D3 and D4 are closed, pulling the output node to ground (Figure 2.2b). The following analysis shows how the gate's output is affected when faults occur in this switching state:

• A single stuck-on fault occurs: If a stuck-on fault occurs in D3 or D4, the output of the gate

2.3. Device Level 11

remains unchanged (but may be incorrect for other inputs). However, if the fault occurs in D2 (or D1), the gate shorts from  $V_{dd}$  to ground (Figure 2.2c). This situation can also happen when a stuck-at-0 fault appears at the gate of D2 (or D1). Typically, this leads to a significant increase in power consumption due to continuous current flow, as well as increased heat dissipation, which may damage the devices. The output voltage is then indeterminate and can fluctuate between  $V_{dd}$  and ground. If the on-resistance of D1 and D2 is lower than that of D3 and D4, the output may be closer to  $V_{dd}$ . On the other hand, if D3 and D4 have a lower on-resistance, the output may be closer to ground. In a Verilog simulation, the value x is assigned to the output node, representing an unknown logic value. Experimental circuits are assessed later using digital behavioural simulations, which means that this x value could be either 1 or 0.

• A single stuck-off fault occurs: If a stuck-off fault occurs in D1 or D2, the output of the gate remains unchanged (but may be incorrect for other inputs). However, if the fault occurs in D3 or D4, the output node will be left in a floating state (Figure 2.2d). This can also be caused by a stuck-at-0 fault at the gate of D3 or D4. In a real implementation, this results in the output node being at high impedance, meaning that the node cannot discharge and thus retains the voltage level it had before. The device can hold its voltage level for several hours before discharging. In Verilog, the high-impedance state is denoted by the value z. To accurately depict this behaviour, the logic gates were modelled to retain the logic level of the previous clock cycle when a z value occurs at the output node.

Figure 2.2: NAND gate: (a) implementation with 3-T devices, (b) fault free case (c) single stuck-on fault, (d) single stuck-off fault.

### **Chapter 3**

# Fault-tolerant Design Techniques in **CMOS**

This chapter aims to review various established fault-tolerant design techniques frequently used in CMOS circuits. These techniques usually introduce redundancy in the form of hardware, time, or information to provide additional resources when a fault occurs. The benefits and drawbacks of these design techniques are discussed in detail. Furthermore, their suitability for NEM circuits is assessed to determine which design techniques are appropriate for simulation in the subsequent steps.

### **Hardware Redundancy**

Fault tolerance in the domain of hardware is one of the simplest and most widely used design techniques to increase the reliability of a circuit. The basic concept is to replicate hardware to provide backup resources when a component or device fails. Hardware redundancy can be implemented at different levels, including the entire system, individual components and modules, and even CMOS transistors or NEM relays at the nanometer scale. Moreover, it can be further divided into active, passive, and hybrid hardware redundancy.

Active hardware redundancy involves fault detection, fault location, and fault recovery to maintain the circuit's correct functionality. Fault detection determines whether a fault has occurred, while fault location identifies the specific location of the fault. In the fault recovery process, the system is reconfigured to remove the faulty component. During this procedure, the fault may propagate, putting the system into an erroneous state until the faulty component is removed. In passive hardware redundancy, fault propagation is prevented by masking the fault, meaning that the concept of fault masking does not require any further interaction to tolerate the fault. In hybrid hardware redundancy, characteris-

Figure 3.1: Duplication with comparison [3].

tics of both active and passive hardware redundancy are combined. Fault masking is used to prevent faults from manifesting in errors, while fault detection, location, and recovery is used to remove and replace the faulty components. The following sections elaborate on the different forms of hardware redundancy [3, 11].

### **Active Hardware Redundancy**

Active hardware redundancy techniques employ a fault detection mechanism to determine if a fault has occurred. When a fault is detected, the faulty component or device is located. Finally, the required actions are performed by an operator or the system itself to remove or replace the faulty component. Active hardware redundancy techniques do not apply fault masking, meaning the system must be able to tolerate erroneous results for a certain amount of time. Thus, this design technique is not suitable for highly reliable systems that rely on permanently correct outputs. The following examples demonstrate the core principles of active hardware redundancy.

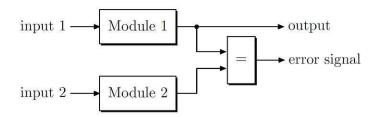

### 3.1.1.1 Duplication with Comparison

The simplest method of active hardware redundancy is duplication with comparison. In this technique, a module is duplicated, so the computation is performed by two identical modules (Figure 3.1). The outputs of these modules are then compared by a comparator. If the outputs do not match, the comparator generates an error signal, indicating that one of the modules has failed. After an error signal has been observed, the system has to be reconfigured, as this technique cannot mask or correct faults [3].

### **Standby Sparing** 3.1.1.2

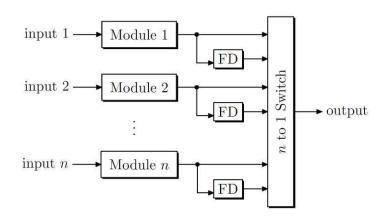

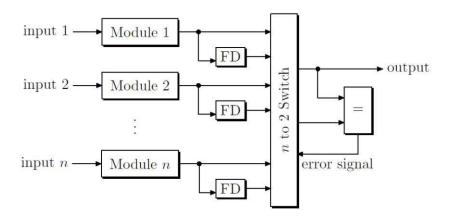

Another approach in active hardware redundancy is called *standby sparing*. In this design technique, the module is replicated into n identical modules (Figure 3.2). Out of these modules, only one is active, while the others serve as spares. A spare module can be seen as a backup module that is activated when the active module fails. The outputs of the modules are fed into a Fault Detection (FD) logic as well as into a n to 1 switch. The switch is responsible for directing the output of the active module to the

Figure 3.2: Standby sparing [3].

Figure 3.3: Pair-and-a-spare [3].

system's output. When the active module fails, the FD signals the switch to select the output from one of the spare modules. The spares can be held in either hot or cold standby. In hot standby sparing, the spare modules are on and work in parallel with the active module. When the active module fails, the spare modules can take over with minimal reconfiguration time. In cold standby all spare modules are powered off to reduce power consumption. Therefore, they need to be turned on when selected as active module, leading to higher reconfiguration time [3].

### 3.1.1.3 Pair-and-a-spare

The pair-and-a-spare technique is a combination of duplication with comparison and standby sparing (Figure 3.3). However, in this technique two modules are active at the same time. The outputs of all modules are fed into a n to 2 switch that directs the outputs of the two active modules into a comparator, with one of these outputs also being directed to the system's output. If a mismatch in the comparison occurs, the comparator generates an error signal. The switch then uses information from the FD logic to determine which module has failed and selects a spare module to replace the failed one. Thus, it is ensured that there are always two fault-free modules working [3].

### 3.1.1.4 Applicability to NEM Circuits

Since duplication with comparison is only capable of detecting faults but not correcting or masking them in the affected modules, it is not considered as an appropriate choice to address yield and reliability issues in NEM technology. The technique can be used to detect faulty modules, but there is no mechanism to determine which module has failed. Furthermore, the circuit must be reconfigured when a faulty module has been detected, which is impractical when faults occur during manufacture or while the device is in operation. Additionally, the high fault probability in NEM technology may cause both modules or even the comparator to fail.

In both standby sparing and pair-and-a-spare configurations, the system can reconfigure itself without requiring any intervention. Both systems are capable of tolerating n-1 faults, assuming they are comprised of n modules. Therefore, there must be enough replicated modules to achieve the desired fault tolerance. This can lead to a significant increase in hardware cost. Moreover, the additional hardware required for FD and switching logic has to be considered. It is also important to note that the circuitry implementing the FD and switching logic is susceptible to faults as well, so it is crucial to ensure that this part of the circuit functions correctly, otherwise, the active redundancy system may fail.

In general, active hardware redundancy techniques are applied at an abstraction level where modules and functional units serve as the basic building blocks of a circuit. However, at the current stage of the i-EDGE project, it is not yet possible to reliably manufacture complex modules in NEM technology. Due to this limitation and the reasons mentioned above, the active hardware redundancy approach is not pursued further in this thesis. Nevertheless, active redundancy techniques may become more attractive in a later stage of the project when manufacturing processes have matured sufficiently to fabricate NEM modules with higher reliability.

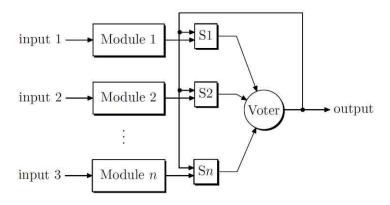

### **Passive Hardware Redundancy** 3.1.2

Passive hardware redundancy aims to mask faults, ensuring that the affected component continues to function correctly when a fault occurs. Thus, neither fault detection nor intervention by the system or the operator is needed to tolerate faults. Because of its low design complexity and versatility, it is a widely used approach to increase a system's fault tolerance. There are a multitude of passive hardware redundancy techniques, with the most prominent one being Triple Modular Redundancy (TMR). Therefore, the first part of the following section is dedicated to TMR, followed by a discussion of other design techniques.

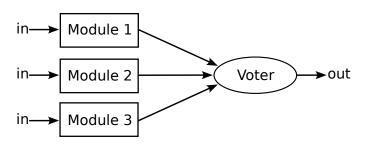

Figure 3.4: TMR system.

### Triple Modular Redundancy

In TMR, a module is replicated three times to have three identical modules working in parallel. The output of each module is fed into a voting circuit, which performs majority voting on the inputs and provides the result as the output. It is evident that the voting system can tolerate one faulty module, as the voting process will mask the fault. In this structure, the voter constitutes a single point of failure, as it is critical that the voting circuit operates fault-free to provide the correct result. Selective hardening is not possible with NEM technology, so the critical parts of the circuit cannot be made more reliable by modifying the manufacturing process. Several design techniques have been proposed to improve the reliability of the voting process, with R-fold modular redundancy and cascaded TMR being two of them [27]. In R-fold modular redundancy, the module is replicated not just three times, but R times, allowing correct voting even when more than one module fails. Often, the term N-Modular Redundancy (NMR) is used in literature to refer to this technique. In cascaded TMR, the TMR concept is repeated, meaning that the entire TMR structure is replicated, and an additional voter is introduced that performs the voting process for the triplicated structures. However, these design techniques significantly raise hardware costs and do not address the issue of the voter being a single point of failure. Thus, several voter designs have been proposed to improve the reliability of the voter itself. A selection of different designs is presented below.

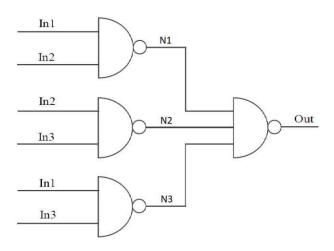

**Standard Voter** The standard majority voter can be implemented using four NAND gates (Figure 3.5). From a gate level perspective, this voter may fail if the output of the NAND gate in the second stage becomes stuck or flips. Additionally, the voting process fails if a fault in one of the NAND gates in the first stage causes one or more of the nodes N1, N2, or N3 to become stuck at 0, while the remaining nodes are set to 1 (which is assumed to be the correct value). On the other hand, the NAND gate in the last stage will still produce the correct output if one or more of the nodes N1, N2, or N3 are stuck at 1, while the other nodes are correctly set to 0. At the device level, a stuck-off fault can cause a gate's output to be stuck at either 0 or 1, leading to similar cases as those at the gate level. A stuck-on fault may cause a gate's output to remain at an undefined logic level. When an undefined logic level is fed

Figure 3.5: Standard TMR voter [4].

into a NAND gate, the output can only be determined when one of its other inputs is 0, as in this case, the output of the gate will always be 1. If an undefined logic level occurs at the output of the voter, it is considered a failure. In the simulations, this voter is labelled as standard voter.

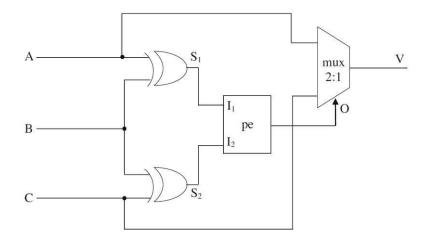

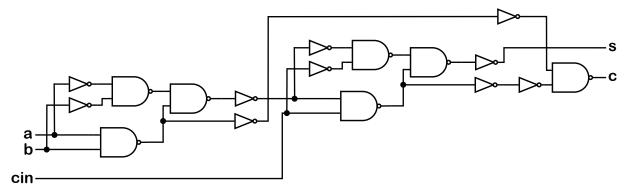

Voter with XORs, Multiplexer & Priority Encoder This voter design features two XOR gates, a priority encoder, and a multiplexer (Figure 3.6). The inputs A and C are compared to input B for inequality using XOR gates. The outputs of the XOR gates are fed into a priority encoder, which is designed to give priority to the input with the logic level 0 by implementing the Boolean equation  $O=I_1\wedge \overline{I_2}$ . The multiplexer then selects either A or C as the output, depending on which input is determined to be fault-free based on the comparison. If all inputs are equal, or if both A and C are not equal to B, then A is selected as the output. This voter can handle a single external fault at the inputs, as well as a single internal fault at node S1, S2 or O. This means that the voter remains operational when  $S_1$ ,  $S_2$  or O becomes stuck at 1 or stuck at 0, assuming all inputs are correct. If both internal and external faults occur, the voter may still function in specific cases. For example, when the inputs A and C are equal, and input B is faulty, the voter will still perform correctly, even in the presence of an internal fault. In this case, it will also provide the correct output when an undefined logic level appears at node O due to stuck-on faults [5]. In the simulations, this voter is labelled as priority enc voter.

Voter with Multiplexer & XOR This voter is designed using an XOR gate and a multiplexer (Figure 3.7). The inputs A and B are compared for inequality by the XOR gate, and its output is used as select line for the multiplexer. This means that if inputs A and B are equal, the multiplexer selects input B; otherwise, input C is selected as the output. Similar to the previous design, this voter can handle a single external, as well as a single internal fault. If both internal and external faults occur, the voter remains functional only in specific cases. When inputs B and C are correct, and input A is faulty, the

Figure 3.6: Voter with XORs, priority encoder, and a multiplexer [5].

Figure 3.7: Voter with multiplexer and XOR [6].

voter can also handle an internal fault at node S, including undefined logic levels [6]. In the simulations, this voter is labelled as *mux\_xor\_voter*.

**Voter with OR & Complex Gate** This voter design consists of an OR gate and a complex gate, which implements the Boolean function  $V = (M \land Z) \lor (X \land Y) \lor (Y \land Z)$  with  $M = X \lor Y$  (Figure 3.8). In addition to handling a single internal fault or a single external fault, this design is capable of tolerating more scenarios where both occur simultaneously, compared to the previous designs. The downside of this voter is that its behaviour largely relies on the correct functioning of the complex gate, which can be compromised by stuck-on and stuck-off faults [7]. Because the logic function of this voter uses only AND and OR operations, it is labelled as and\_or\_voter in the simulations.

Voter with Triple Transistor Redundancy In this design, gate level redundancy and device level redundancy are combined to improve the fault tolerance of the standard voter. The modification involves replicating each NAND gate in the first level three times. The 3-input NAND gate in the second level is then redesigned using tripled transistor design (Figure 3.9), where each transistor is replaced by a structure consisting of three transistors (Section 3.1.2.2). The outputs of the triplicated gates in the first level provide the inputs to the tripled transistor structures. The redundant transistor structure

Figure 3.8: Voter with OR gate and complex gate [7].

of the NAND gate in the second level allows to tolerate faulty outputs coming from the gates in the first level. Moreover, it makes the gate more resilient against stuck-on and stuck-off faults [4]. In the simulations, this voter is labelled as tripled\_voter.

Figure 3.9: Voter with triple transistor redundancy [4].

### 3.1.2.2 Tripled Design

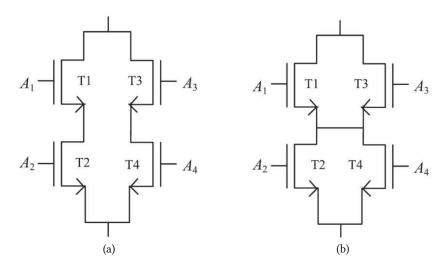

In this design technique, fault tolerance is achieved by introducing redundant transistors, which serve as backup devices [8, 28]. Each transistor is replaced by a structure of three transistors, which can be arranged in two different configurations. In the first version, a transistor is placed in series with

Figure 3.10: Tripled design: (a) version 1, (b) version 2 [8].

two parallel transistors (Figure 3.10a). In the second version, a transistor is placed in parallel with two transistors that are connected in series (Figure 3.10b). In a fault-free case, the gate inputs A<sub>1</sub>, A<sub>2</sub>, and A<sub>3</sub> are equal, causing the entire structure to behave like a single transistor. In the case of one or more faults, the following scenarios can occur:

- Version 1: This configuration can tolerate a single stuck-on fault in T1, T2, or T3 (or a stuck-at-1 fault at either  $A_1,\ A_2,\ or\ A_3).$  However, it can only tolerate a stuck-off fault in T2 or T3. If a stuck-off fault occurs in T1 (or A<sub>1</sub> gets stuck-at-0), the path remains open, resulting in incorrect behaviour of the circuit. Dual stuck-on faults can also be tolerated when they occur in T2 and T3, whereas the circuit always fails for dual stuck-off faults.

- Version 2: This configuration can tolerate a single stuck-off fault in T1, T2, or T3 (or a stuck-at-0 fault at either A<sub>1</sub>, A<sub>2</sub>, or A<sub>3</sub>). A single stuck-on fault can only be tolerated when it occurs in T2 or T3. A stuck-on fault in T1 (or a stuck-at-1 fault at A<sub>1</sub>) will cause a short circuit. Dual stuckoff faults are tolerated only when they occur in T2 and T3, whereas dual stuck-on faults always result in a short circuit.

From this analysis, it can be concluded that the first version is more resilient to stuck-on (or stuck-at-1) faults, whereas the second version is more resilient to stuck-off (or stuck-at-0) faults. Thus, the most suitable version depends on which type of fault is more likely to occur. This design technique can also be applied to NEM circuits by substituting the transistors in the structures with their NEM counterparts. In CMOS, this technique is usually referred to as triple-transistor redundancy, while in this work the term Tripled Design (TD) is used. In the simulations, the two design structures are labelled as TD\_v1 and TD\_v2.

### Quadded Design 3.1.2.3

This design technique makes use of the concept of replacing each transistor with a redundant structure to improve fault tolerance, similar to TD [29-32]. In this structure, four transistors are arranged in one of two possible configurations. In the first configuration, two pairs of transistors connected in series are arranged in parallel (Figure 3.11a). In the second configuration, two pairs of parallel transistors are connected in series (Figure 3.11b). In a fault-free case, the gate inputs A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub>, and A<sub>4</sub> are equal, so the behaviour of the entire structure is the same as that of a single transistor. In the presence of faults, the following scenarios can occur:

- Version 1: This configuration can tolerate both single stuck-on and stuck-off faults in T1, T2, T3, or T4 (or stuck-at-1 and stuck-at-0 faults at either A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub>, or A<sub>4</sub>). Dual stuck-off faults are tolerated as long as they don't occur in T1 & T3, T1 & T4, T3 & T2, or T2 & T4. Dual stuck-on faults are tolerated as long as they don't occur in T1 & T2 or T3 & T4.

- Version 2: This configuration can tolerate both single stuck-on and stuck-off faults in T1, T2, T3, or T4 (or stuck-at-1 and stuck-at-0 faults at either A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub>, or A<sub>4</sub>). Dual stuck-off faults are tolerated as long as they don't occur in T1 & T3 or T2 & T4. Dual stuck-on faults are tolerated as long as they don't occur in T1 & T4, T1 & T2, T3 & T2, or T3 & T4.

This analysis shows that the first version is more resilient against stuck-on faults (or stuck-at-1 faults), whereas the second version is more resilient against stuck-off faults (or stuck-at-0 faults). The term Quadded Design (QD) is used to refer to this design technique, and similar to TD, the transistors are replaced with their NEM counterparts. Furthermore, the concept of redundant transistor structures can also be generalized by introducing  $N^2$  transistor structures, where  $N \ge 2$  [33]. Each  $N^2$  structure consists of N serially connected blocks, where one block is comprised of N parallel transistors. It is evident that the number of tolerated faults can be increased by the use of redundant structures with a larger N. However, since QD already provides a significant improvement in fault tolerance, and N<sup>2</sup> structures with N > 2 come at the expense of a high hardware overhead, only QD was utilized. In the simulations, the two versions of QD are labelled as QD v1 and QD v2.

### 3.1.2.4 Quadded Logic + Quadded Design

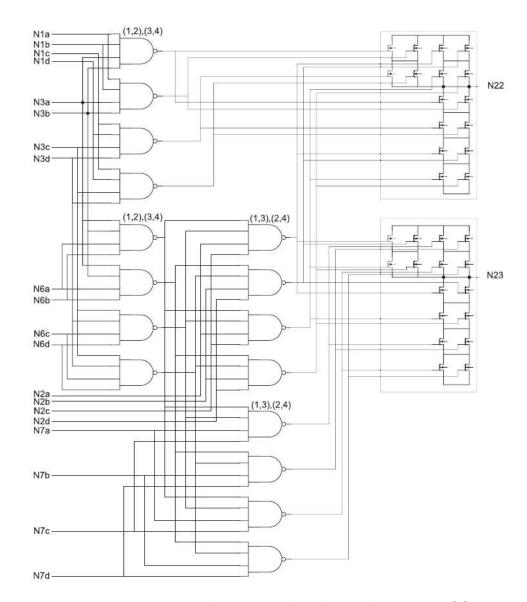

This design technique combines both Quadded Logic (QL) and QD to leverage the strengths of both approaches. The circuit is implemented in QL, with only the last level being realized in QD (Figure 3.12). In QL, each gate in the circuit is replicated four times. Additionally, the replicated gates have twice as many inputs as the original gates. The four outputs of the replicated gates are grouped into two pairs,

Figure 3.11: Quadded design: (a) version 1, (b) version 2 [8].

with each pair providing inputs to two gates at the next level. The outputs can be paired in three possible ways: (1,2) and (3,4); (1,3) and (2,4); and (1,4) and (2,3). These patterns determine which outputs provide the inputs to each gate at the next level. If the outputs are grouped into the pairs (1,2) and (3,4), the output pair (1,2) will be connected to gate 1 and 2 at the next level, while the output pair (3,4) will be connected to gate 3 and 4 at the next level. It is important that the interconnect pattern at the inputs of a group of gates at one level must be different from the interconnect pattern at the outputs of that group. To understand how faults are corrected in this design, the terms critical error and sub-critical error must be defined. A critical error at one of the gate's inputs always results in an incorrect output, regardless of the other inputs. An example of a critical error is an input of a NAND gate wrongly set to 0, which leads to the output always being 1. A sub-critical error at one of the gate's inputs does not always result in an incorrect output, as it depends on the other inputs. For example, if an input of a NAND gate is wrongly set to 1, the gate's output still depends on the the other inputs. A single sub-critical error is absorbed after passing one stage of gates, while a critical error is corrected after passing two stages. However, critical errors occurring in the last two stages, as well as sub-critical errors occurring in the last stage cannot be corrected. Combining the QL approach with QD addresses this issue by implementing the last stage in QD, which enables it to tolerate both faults coming from the previous stage, as well as faults occurring at the last stage [9, 34]. In the simulations, this design technique is labelled as QL+QD.

### Triple Modular Redundancy + Tripled Design

This approach combines TMR at the gate level with TD at the device level. Similar to TMR, redundancy is achieved by replicating the gates three times. However, in this design, the gates at the last level of the circuit are not replicated but instead implemented in TD (Figure 3.13). The outputs of the triplicated

Figure 3.12: C17 circuit (Section 6.1.1) implemented in QL + QD [9].

Figure 3.13: C17 circuit (Section 6.1.1) implemented in TMR + TD [10].

gates serve as inputs to the TD structure at the last level. The application of TD to the gates at the last level not only improves the fault tolerance of these gates but also implements a voting mechanism for the triplicated gates in the preceding stages, as TD structures can also tolerate faulty inputs. Therefore, voting circuits, which are susceptible to faults, are no longer required [10]. In the simulations, this design technique is labelled as TMR+TD.

### 3.1.2.6 Applicability to NEM Circuits

Passive hardware redundancy offers a wide range of design techniques for enhancing the fault tolerance of circuits. These techniques are capable of effectively masking faults that originate from defective

Figure 3.14: Self-purging redundancy [3].

NEM devices, whether they occur during manufacture or operation. This low level approach enables fault-tolerant circuits without requiring sophisticated additional circuitry or external intervention by an operator. Additionally, their versatility allows for various design choices, such as choosing the module size in TMR, selecting a specific design variation in TD or QD depending on the fault type, or determining a general trade-off between device overhead and device fault probabilities. Lastly, passive hardware redundancy techniques can not only easily be adapted to NEM circuits by replacing the conventional CMOS transistors with their NEM counterparts, but also enable designs that are only possible in NEM technology, such as NEM voting circuits in TMR (Chapter 4). Therefore, passive hardware redundancy is considered a viable option for increasing the yield and the reliability of NEM circuits.

### Hybrid Hardware Redundancy 3.1.3

Hybrid hardware redundancy is the most complex form of hardware redundancy, as it combines elements of both passive and active hardware redundancy. Passive hardware redundancy provides the ability to mask faults, preventing them from propagating through the system, while active hardware redundancy employs fault detection, fault location, and fault recovery to reconfigure the circuit. The following sections provide two examples to elaborate on the concept.

### 3.1.3.1 **Self-Purging Redundancy**

The concept of *self-purging redundancy* is based on NMR, meaning that a module is replicated n times, and a voter determines the correct output through majority voting. However, the output of a replicated module is not fed directly into the voter, but into a switch that compares the output of the voter to the output of the connected module (Figure 3.14). If the comparison fails, the switch opens, removing the connected module from the voting process. The voter is designed to be capable of adapting the number of its inputs. A system with n replicated modules can tolerate n-2 faulty modules [3].

Figure 3.15: N-modular redundancy with spares [3].

### N-Modular Redundancy with Spares 3.1.3.2

N-modular redundancy with spares is similar to self-purging redundancy in the sense that it utilizes NMR as its base technique. However, in addition to the n replicated modules, k spare modules are introduced (Figure 3.15). The outputs of the n + k modules are connected to a switch. A comparator compares the output of the n active modules to the output of the voter and feeds the results of the comparisons into the switch. If a module's output fails the comparison, the module is considered faulty, and the switch replaces it with a spare module. When there are no spare modules left, the system can operate in one of two possible ways. In the first option, the comparator is turned off, and the system continues working like a NMR system. In this case, the system can tolerate  $\lfloor n/2 \rfloor + k$  faulty modules. In the second option, the comparator continues working and the system operates like one with self-purging redundancy. In this case, the system can handle k + n - 2 faults [3].

### **Other Hybrid Architectures** 3.1.3.3

More sophisticated hybrid architectures combine not only different hardware redundancy techniques but also incorporate redundancy in the domains of information or time. Designs that use both hardware duplication and information redundancy, in the form of parity check codes, to perform fault diagnosis and correction have been proposed [35]. Other architectures aim to modify or extend N-modular redundancy with spares by utilizing information redundancy for error detection, time redundancy for correcting transient errors, and hardware redundancy for correcting permanent errors [36, 37]. To achieve this, finite state machines are implemented and integrated into the design to recompute the

result or change the hardware configuration in the case of a fault.