## Passivierung von n-Ge Nanostrukturen für neuartige Ge Nanotransistoren

## **MASTER THESIS**

Melisa Mustajbašić Alibegović Matrikelnummer e11733843

Institute of Solid-State Electronics, Technische Universität Wien

### Supervisor:

Univ. Prof. Dipl.-Ing. Univ. Dr.-Ing. Walter Michael Weber Univ. Ass. Dr.techn. Daniele Nazzari Univ. Ass. Dipl.-Ing. Dr. techn. Masiar Sistani

### **Statutory Declaration**

I declare that I have authored the present work independently according to the code of conduct, that I have not used other than the declared sources, and that I have explicitly marked all material quoted either literally or by content from the used sources. This work was not yet submitted to any examination procedure either in Austria or in any other country.

### Erklärung zur Verfassung der Arbeit

Erklärung zur Verfassung der Arbeit Hiermit erkläre ich, dass die vorliegende Arbeit gemäß dem Code of Conduct - Regeln zur Sicherung guter wissenschaftlicher Praxis - ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel, angefertigt wurde. Die aus anderen Quellen direkt oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder in ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

| Vienna, Januar 2025 |                               |

|---------------------|-------------------------------|

|                     | Melisa Mustajbašić Alibegović |

The continuous optimization of high-k dielectrics is crucial for enhancing the performance of modern MOSFETs, particularly in reducing leakage currents and improving charge carrier mobility. The objective of this work was to investigate the electrical properties of various highk materials and evaluate their suitability as gate dielectrics in Ge-based MOSFETs. This placed a particular focus on the interactions between the dielectrics and the substrate to evaluate the stability and efficiency of these materials for future applications.

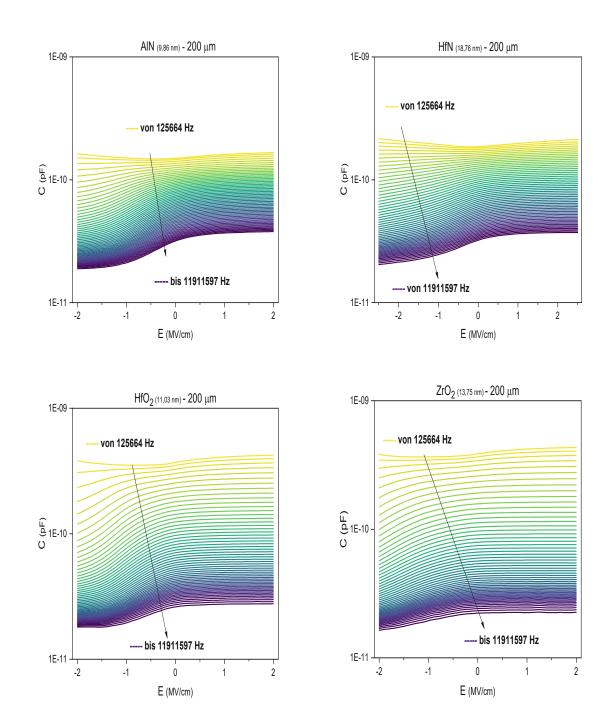

In the first part of the study, hafnium dioxide (HfO<sub>2</sub>), zirconium dioxide (ZrO<sub>2</sub>), hafnium nitride (HfN), and aluminum nitride (AlN) were analyzed with respect to their frequency dependence, defect density, and interface quality. The results indicate that HfO2 and ZrO2 exhibit higher frequency dependence and a greater number of interface charge traps, leading to more unstable electrical characteristics. Conversely, AlN and HfN demonstrated more stable performance due to lower defect densities, with AlN showing the best interface quality.

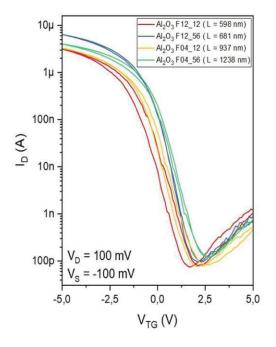

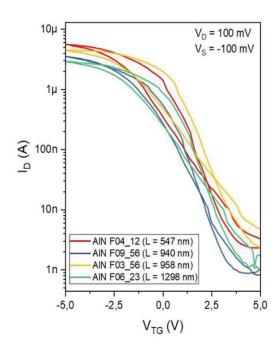

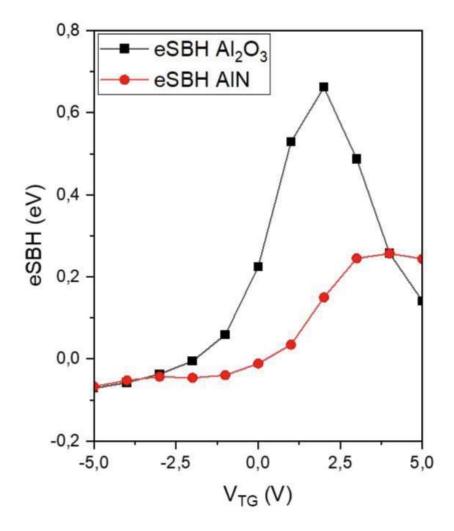

In the second part of the work, Al<sub>2</sub>O<sub>3</sub> and AlN are compared as a potential gate dielectric for Ge nanowire based Schottky barrier field-effect transistors (SBFETs). The use of Al<sub>2</sub>O<sub>3</sub> exhibited stronger modulation of the Schottky barrier height and width as well as higher current injection across the junction. AlN, on the other hand, offered more stable electrical performance, lower leakage currents, and better charge carrier mobility, making it well-suited for applications requiring high reliability and consistency.

This positions AlN as a promising candidate for use in future high-performance MOSFET applications and provides a solid foundation for further research on material optimization and process development. These findings offer valuable insights for the targeted selection of highk materials to optimize the efficiency and reliability of MOSFETs in future semiconductor technologies.

# Kurzfassung

Die kontinuierliche Verbesserung von High-k-Dielektrika ist von entscheidender Bedeutung für die Leistungsfähigkeit moderner MOSFETs, insbesondere im Hinblick auf die Reduktion von Leckströmen und die Verbesserung der Ladungsträgermobilität. Ziel dieser Arbeit war es, die elektrischen Eigenschaften verschiedener High-k-Materialien zu untersuchen und deren Eignung als Gate-Dielektrika in Ge-basierten MOSFETs auf Germanium-Substraten zu bewerten. Hierbei lag ein besonderer Fokus auf den Interaktionen zwischen den Dielektrika und dem Substrat, um die Stabilität und Effizienz dieser Materialien für künftige Anwendungen zu beurteilen.

Im ersten Teil der Arbeit wurden die Materialien Hafniumdioxid (HfO2), Zirkoniumdioxid Hafniumnitrid (HfN) und Aluminiumnitrid (AlN) hinsichtlich Frequenzabhängigkeit, Defektdichte und Grenzflächenqualität analysiert. Die Ergebnisse zeigen, dass HfO2 und ZrO2 eine höhere Frequenzabhängigkeit und eine größere Anzahl von Grenzflächen Ladungsfallen aufweisen, was zu instabileren elektrischen Eigenschaften führt. AlN und HfN hingegen bieten eine stabilere Performance aufgrund geringerer Defektdichten, wobei AlN die beste Grenzflächenqualität aufweist.

Im zweiten Teil der Arbeit wurde Al2O3 und AlN als potenzielles Gate-Dielektrikum für Ge Nanodraht Schottky-Barrieren Feld-Effekt Transistoren (SBFETs) verglichen. Die Anwendung von Al<sub>2</sub>O<sub>3</sub> zeigte eine höhere Leitfähigkeit und eine stärkere Modulation der Schottky-Barrierenhöhe und Weite, sowie eine sich daraus ergebene höhere Leitfähigkeit. AlN hingegen zeichnete sich durch eine stabilere elektrische Leistung, niedrigere Leckströme und eine bessere Ladungsträgermobilität aus, was es für Anwendungen mit hohen Anforderungen an Zuverlässigkeit und Konsistenz prädestiniert.

Dadurch hat sich AlN als vielversprechender Kandidat für den Einsatz in zukünftigen Hochleistungs-MOSFET-Anwendungen positioniert und bietet eine solide Grundlage für weitere Forschungsarbeiten zur Materialoptimierung und Prozessentwicklung. Diese Erkenntnisse bieten wertvolle Einsichten für die gezielte Auswahl von High-k-Materialien, um die Effizienz und Zuverlässigkeit von MOSFETs in zukünftigen Halbleitertechnologien zu optimieren.

# **Danksagung**

Univ. Prof. Dipl.-Ing. Univ. Dr.-Ing Walter Weber, ich möchte Ihnen von Herzen danken, dass Sie mir die Gelegenheit gegeben haben, Teil dieser großartigen Gruppe zu sein. Ihre Unterstützung und Ihr gleiches Vertrauen in jeden einzelnen Studenten haben mir sehr viel bedeutet.

Masiar Sistani, ich bin dir sehr dankbar, dass du mich in die Gruppe aufgenommen hast. Du hast mein Wissen und meine Perspektiven maßgeblich erweitert, und ich habe so viel von dir gelernt. Deine Geduld und dein Engagement sind inspirierend.

Daniele Nazzari, deine ständige Bereitschaft, mir zu helfen, hat mir unglaublich viel bedeutet. Egal, wie beschäftigt du warst, du hast immer Zeit gefunden. Deine Hilfe war ein großer Rückhalt für mich. Durch deine Unterstützung habe ich gelernt, wie wichtig es ist, anderen zu helfen und Wissen zu teilen.

Group Weber, ich möchte euch allen für die wunderbare Zeit danken, die ich mit euch verbringen durfte. Die Erlebnisse und Erinnerungen, die ich mit euch teilen durfte, werde ich für immer in meinem Herzen tragen. Eure Kameradschaft und Unterstützung waren einzigartig.

Fke Institut, ein herzliches Dankeschön an alle Mitarbeiter und Professoren. Ihr habt mir die Möglichkeit gegeben, mein Projekt und mein Studium auf eine Weise zu vertiefen, die ich mir nie hätte vorstellen können. Eure Förderung und euer Engagement haben dieses großartige Erlebnis ermöglicht.

Meinem Man Edvin, ich kann dir nicht genug danken für deine unermüdliche Unterstützung und dein bedingungsloses Verständnis, selbst in den stressigsten Zeiten. Deine Liebe und Geduld haben mir die Kraft gegeben, weiterzumachen. Mit dir an meiner Seite ist das Leben viel schöner, du mahlst mein Leben bunt. Ich liebe dich.

Meinen Eltern Sead und Hasiba und meine Schwester Dijana, ohne eure Unterstützung und euren Glauben an mich wäre ich nicht hier. Ihr habt mir immer zugehört, mich motiviert, nicht aufzugeben. Ihr seid meine Schutzengel, und ich liebe euch von ganzem Herzen.

Vielen Dank, meine liebe Oma Saha, dass du mich in all deinen Gebeten immer miteingeschlossen hast. Du bist und bleibst für mich ein unglaublicher Mensch.

Danke an meine wahren Freunde, ihr wart stets an meiner Seite und habt mich durch Höhen und Tiefen begleitet. Eure Freundschaft und euer Beistand bedeuten mir viel.

Und schließlich ein großes Dankeschön an das Klimt Team, für euer Verständnis und den Respekt, den ihr meinem Studium entgegengebracht habt. Eure Rücksichtnahme hat mir sehr geholfen, meine Ziele zu erreichen.

# Für meine Eltern ♡

## Inhaltsverzeichnis

| 1. | EIN   | FÜHRUNG                                                                             | 1  |

|----|-------|-------------------------------------------------------------------------------------|----|

| 2. | THE   | ORETISCHE GRUNDLAGEN                                                                | 4  |

|    | 2.1.  | GERMANIUM                                                                           | 4  |

|    | 2.2.  | "High-k" Dielektrika                                                                |    |

|    | 2.3.  | METALL-HALBLEITER HETERESTRUKTUREN                                                  |    |

|    | 2.4.  | OXID-HALBLEITER GRENZFLÄCHE                                                         |    |

|    | 2.5.  | SCHOTTKY BARRIERE                                                                   |    |

|    | 2.6.  | METALL-OXIDE-SEMICONDUCTOR (MOS)                                                    | 17 |

|    | 2.7.  | FELDEFFEKTTRANSISTOREN (FET)                                                        |    |

|    | 2.8.  | Nanodrähte                                                                          |    |

|    | 2.9.  | VLS WACHSTUM VON GE-NANODRÄHTEN                                                     | 21 |

| 3. | EXP   | ERIMENTELLE DURCHFÜHRUNG                                                            | 23 |

|    | 3.1.  | UHV ANNEALING UND UHV SPUTTERN                                                      | 23 |

|    | 3.2.  | ATOMLAGENABSCHEIDUNG (ALD)                                                          | 25 |

|    | 3.3.  | RAPID THERMAL ANNEALING (RTA)                                                       | 26 |

|    | 3.4.  | LASERLITOGRAPHIE UND ELEKTRONENSTRAHLVERDAMPFER (E-BEAM EVAPORATION)                |    |

|    | 3.5.  | HERSTELLUNG DES NANODRAHT-TRANSISTORS.                                              | 29 |

|    | 3.6.  | ELEKTRISCHE CHARAKTERIZIERUNG                                                       |    |

|    | 3.6.1 |                                                                                     |    |

|    | 3.6.2 |                                                                                     |    |

|    | 3.6.3 |                                                                                     |    |

|    | 3.6.4 | 5 "                                                                                 |    |

|    | 3.6.5 |                                                                                     |    |

|    | 3.6.6 |                                                                                     |    |

| 4. | ERG   | EBNISSE UND DISKUSSIONEN                                                            | 41 |

|    | 4.1.  | C-V MESSUNGEN (MOS-BAUTEILE)                                                        | 42 |

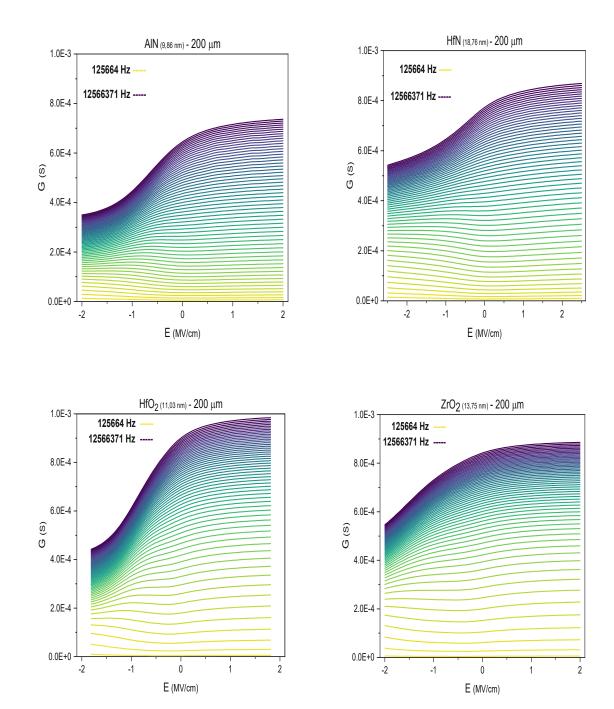

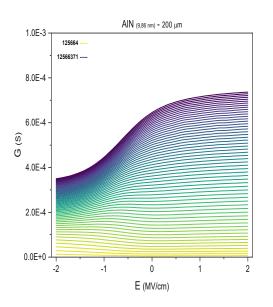

|    | 4.2.  | G-V Messungen (MOS Bauteile)                                                        |    |

|    | 4.2.1 |                                                                                     |    |

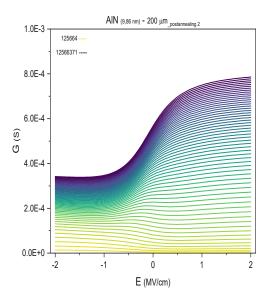

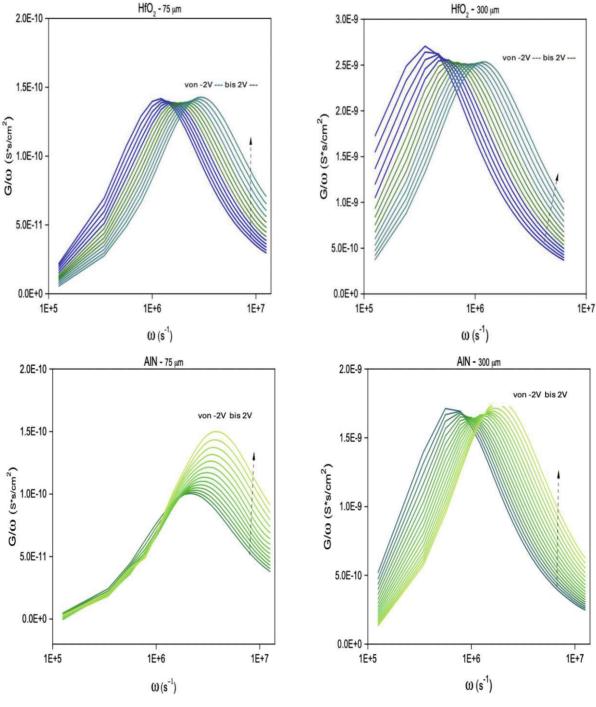

|    | 4.3.  | $G/\Omega$ VS. $\Omega$ (MOS BAUTEILE)                                              |    |

|    | 4.3.1 |                                                                                     |    |

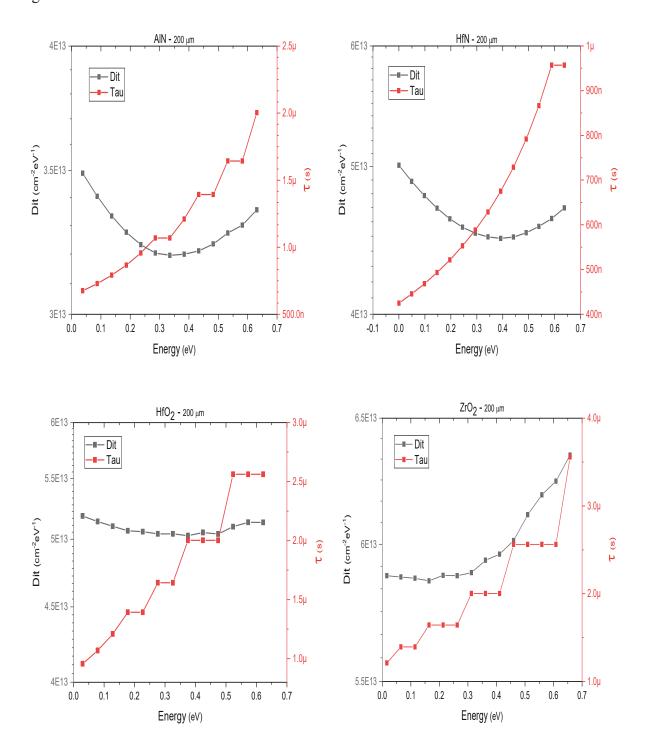

|    | 4.4.  | D <sub>IT</sub> (MOS BAUTEILE)                                                      |    |

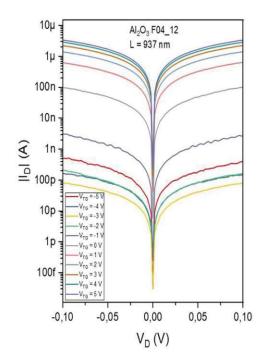

|    | 4.5.  | TRANSFERKENNLINIEN FÜR GE-ALN-NW UND GE-AL <sub>2</sub> O <sub>3</sub> -NW (MOSFET) |    |

|    | 4.6.  | AUSGANGSKENNLINIEN FÜR GE-ALN-NW UND GE-AL <sub>2</sub> O <sub>3</sub> -NW (MOSFET) |    |

|    | 4.7.  | EFFECTIVE SCHOTTKY BARRIER HEIGHT VS. GATE VOLTAGE                                  |    |

| 5. | ZUS   | AMMENFASSUNG                                                                        | 60 |

| 6. | LITI  | ERATURVERZEICHNIS                                                                   | 62 |

# 1. Einführung

In den vergangenen Jahrzehnten verzeichnete die Elektronikindustrie ein bemerkenswertes Wachstum. Das Wachstum und die Herstellung von Halbleitermaterialien haben zu diesem Erfolg beigetreten. Ein bedeutender Erfolg in der CMOS-Technologie war die Reduzierung des Energieverbrauchs und Erhöhung der Schaltgeschwindigkeit pro Funktionseinheit durch Verkleinerung. In den letzten Jahren hat sich die Forschung diversifiziert und neue Technologien, Architekturen und Materialien hervorgebracht. Reines Silizium wird schrittweise durch Silizium-Germanium (SiGe), Germanium (Ge) und III-V Materialien ersetzt, da diese eine höhere Mobilität aufweisen. [1] Dies hat ein erhebliches Forschungsinteresse geweckt, Materie auf Nanometerebene zu manipulieren, um Materialeigenschaften zu verbessern. Aufgrund der relativ hohen effektiven Massen, die die Anwendung von Tunneleffekte von Ladungsträgern und quantenballistischem Transport in Bauelementen der Gruppe IV auf sehr kleine Strukturen oder sehr niedrige Temperaturen beschränken, wurden III-V-Halbleiter intensiv untersucht. [2]

Forschungen haben gezeigt, dass das quantenmechanische Tunneln durch die immer dünner SiO<sub>2</sub>-Gate-Dielektrik zu einem exponentiellen Anstieg des Stromverbrauchs von Transistoren geführt hat. Gleichzeitig führten diese Erkenntnisse zu intensiven Bemühungen, ein Material mit einer höheren Dielektrizitätskonstante (K) als SiO<sub>2</sub> zu finden, um bei gleichbleibender Feldstärke die physikalische Dicke zu erhöhen und debei den Leckstrom durch das Gate zu reduzieren. [3] Um weitere Kurzkanaleffekte zu reduzieren wurde beträchtlicher Aufwand in die Herstellung von niederdimensionalen Nanostrukturen investiert, wie z. B. einwandigen Kohlenstoffnanoröhren (SWCNTs) und aus Vapor-Liquid-Solid (VLS) gewachsenen Nanodrähten (NWs). [2], [4] SWCNT-Basis hat sich als vielversprechende Plattform für die Untersuchung neuartiger Transportphänomene erwiesen, jedoch treten Probleme hinsichtlich der Reinheit, Gleichmäßigkeit und der Herstellung zuverlässiger Kontakte die Hauptfaktoren auf, die die Integration auf Wafer-Skala behindern. [2] Im Gegensatz dazu ist bei NWs keine Unterscheidung zwischen metallischen oder halbleitenden Materialien erforderlich, da deren Eigenschaften durch das verwendete Material bestimmt werden. Einer der bedeutendsten Vorteile von NWs ist die Möglichkeit, ihre Morphologie, Geometrie, Zusammensetzung, Kristallorientierung und Größe durch Anpassung der Wachstumsbedingungen zu optimieren. Darüber hinaus stehen eine Vielzahl von Halbleitermaterialien für das Wachstum von NWs zur Verfügung. [5][2]

Als Halbleiter werden feste Materialien bezeichnet, die aufgrund ihres Aufbaus, ihrer Gitterstruktur und in Abhängigkeit mit Temperatur eine mehr oder weniger große Zahl von beweglichen Elektronen bzw. Löcher (fehlende Elektronen) aufweisen. [6] Materialien, die keine beweglichen Ladungsträger aufweisen und damit höhere spezifische Widerstände haben, werden als Isolatoren bezeichnet [6], während Materialien, deren Leitfähigkeit auch bei tiefsten Temperaturen erhalten bleibt und normalerweise niedrige spezifische Widerstände zeigen, Leiter sind. [6]

Abbildung 1.1. Schematische Darstellung des elektrischen Widerstandes für die drei Materialkategorie

Elektrischer Widerstand (R) ist ein Widerstand gegen einen elektrischen Stromfluss durch ein Material. Er ist proportional zu seiner Länge (1) und umgekehrt proportional zu seiner Querschnittsfläche (A). [7] Jedes Material hat auch eine intrinsische Eigenschaft, die Resistivität (o), die angibt, wie gut ein bestimmtes Material den elektrischen Strom leitet. Je höher die Resistivität desto schlechter leitet es den elektrischen Strom. [7]

$$\mathbf{R} = \boldsymbol{\rho} * (\frac{1}{A}) \quad (1.1.)$$

Die Fähigkeit fast hochreine Halbleitermaterialien herzustellen, Dotierungsprofil und Typ steuern zu können und neue Materialkombinationen zu entwickeln, öffnete neue Türen zu höheren Leistungen. Einer der Hauptziele in der Elektronik ist die extreme Miniaturisierung von elektronischen Bauelementen. Nanotechnologie ist ein Gebiet, bei dem es um Kontrolle von Materie auf der Größenskala von Nanometern geht. [8] Die Idee ist, die Größe von Transistoren, Widerständen und Kondensatoren auf die Nanometer-Skala zu reduzieren. Dies ermöglicht, mehr Schaltungen auf einem einzigen Chip unterzubringen, was die Leistung und Effizienz elektronischen Bauelementen verbessert. von Durch die Miniaturisierung können Bauelemente schneller schalten und höhere Frequenzen erreichen. Dies führt zu leistungsstärkeren und schnelleren elektronischen Bauelementen, was insbesondere Bereichen wie Computern, Kommunikationstechnologie Signalverarbeitung von großem Nutzen ist. [9] Erwähnungswert sind auch die sinkenden Kosten, kleinere Transistoren erfordern weniger Leistung, um zwischen den Zuständen "Ein" und "Aus" zu wechseln. [10] Genau das hat der bekannter Wissenschaftler Gordon Moore in seine Arbeit in Jahr 1965 vorausgesagt. [11] Moores Gesetz sagt aus, dass sich die Anzahl der Transistoren pro Chip etwa alle 18 bis 24 Monate verdoppelt. [12]

Der erste experimentelle Transistor [13] wurde von drei Physiker W.Shockley, J.Bardeen und W.Brattain im Jahr 1948 entwickelt und das hatte einen großen Einfluss auf die Elektronikindustrie.

Die beobachteten, dass eine Änderung der Flussspannung an der ersten Diode<sup>1</sup> eine Änderung des Sperrstroms der zweiten Diode zur Folge hatte. Sie nannten diesen Effekt "Transistoreffekt", abgeleitet von "transit" (Übergang) und "resis tor" (Widerstand). [6]

<sup>&</sup>lt;sup>1</sup> Diode-lässt den elektrischen Strom in einer Richtung passieren und in anderen sperren

Shockley kam zur Idee, die Übergänge nicht durch Kontakte herzustellen, sondern diese in Kristall zu zerlegen durch "Verunreinigung" von IV-wertigen Germanium Kristall durch Dotierung<sup>2</sup> mit III-wertigen Indium. Somit wurde die Leitfähigkeit, sowie Kristalleigenschaften (Bandstruktur) verändert und diese Bauweise nennt man Legierungstransistor PNP Germanium-Transistor. [6] Seine Nachteile sind dagegen, dass es bei 80°C zerfällt und dass er über ein instabiles natürliches Oxid verfügt. Silizium verträgt auch Temperaturen bis 150°C und verfügt über ein stabiles Oxid, was einer der Gründe wurde, dass Germanium schnell von Silicium überholt wurde. [14][15] Um diese Nachteile zu überwinden und um die Betriebsgeschwindigkeit der Schaltungen zu erhöhen und gleichzeitig den Stromverbrauch zu senken, ist wichtig, wie oben erwähnt, die Transistoren zu verkleinern. Dabei stoßt man auf grundlegenden Skalierungsgrenzen, wie erhöhte Leckstromdichte, die die Leistungsfähigkeit elektronischer Bauelemente einschränken. [16] Germanium findet man heutzutage als SiGe Legierung in diversen Bauelementen, z.B Heterobipolartransistoren, Photodetektoren, wie auch in p-Kanal Mosfets

In dieser Arbeit wird n-dotiertes Germanium als Schlüsselmaterial verwendet, da mit einer hohen und nahezu symmetrischen Elektronen- und Lochmobilität, Germanium eines der relevantesten Halbleiter für zukünftige nanoelektronische Schaltungen ist. Trotzdem ist das Problem mit Grenzfläche zu Oxiden sowie der Einfluss der Ge/GeOx- und Ge/High-k-Grenzfläche, immer noch ein schwerwiegender limitierender Faktor für Anwendungen von Gebasierten nanoskaligen Bauelementen. [17] Dies führt zu einer höheren Dichte der Elektronen, Defekte durch unabgäsetigte Bindungen. Daher ist es eine wichtige Aufgabe, die Ge-Oberfläche richtig zu reinigen und eine Grenzfläche Oxid/Nitrid zwischen der Ge-Oberfläche und einem dielektrischen Material, mit einem niedrigen Grenzflächendefekt Dichte, zu finden.

<sup>&</sup>lt;sup>2</sup> Dotierung-einbringen von Fremdatomen in eine Schicht oder in das Grundmaterial eines integrierten Schaltkreises

# 2. Theoretische Grundlagen

diesem Kapitel werden die besonderen Eigenschaften von Germanium, Halbleitermaterial, das wir als Basissubstrat ausgewählt haben, detailliert dargestellt. Darüber hinaus werden die Unterschiede zu anderen Halbleitermaterialien, insbesondere Silizium, diskutiert, um zu verdeutlichen, warum Germanium bevorzugt wird und als Hauptmaterial für unsere angestrebte MosCap (Metall-Oxid-Semiconductore capacitor) Anwendung dient. Der Schwerpunkt liegt auf den wichtigsten Passivierungsmethoden zur Oberflächenbehandlung, um die Oxideinschlüsse, die bei Germanium auftreten, zu beseitigen und ein erfolgreiches Bauteil zu entwickeln. Im Anschluss wird auch die hervorragende Eignung von Germanium für nanoelektronische Anwendung angesprochen. Ziel dieser Arbeit ist die Herstellung von Metall-Oxid-Halbleiter-Kondensatoren (MOSCAPs), diese Struktur ist in wesentlichen ein elektronisches Bauelement und spielt eine bedeutende Rolle in der Halbleitertechnologie. Die Hauptkomponenten eines MOSCAP sind das Halbleitersubstrat, auf dem die gesamte Struktur aufgebaut ist, die Top Gate Elektrode aus einem leitfähigen metallischen Werkstoff und eine dazwischenliegende isolierende Oxid-oder Nitridschicht. Wirtschaftlich wird meist Metall für die zweite Elektrode (Top Gate) verwendet, wobei Materiallien wie Platin und Titan aufgrund ihrer guten Verbindungseigenschaften und Haftung zwischen den vershiedenen Schichten im MOS-Kondensator bevorzugt werden. Aufgrunddesen haben wir 1:1 Platin und Titanium auf unser Germanium -Oxid Probe aufgedampft. Titanium haftet sehr gut an Germanium, was sehr wichtig ist, weil eine gute Adhäsion unerwünschte Schichtenbildung oder Delamination verhindern kann.

### 2.1. Germanium

Meendelejew war "nahezu", um Germanium zu entdecken, da er einige Eigenschaften dieses Elements vorhergesagt hatte. Er nannte es jedoch Ekasilicon, weil er auf eine Lücke unterhalb des Siliciums stieß. [18] Das Element Germanium, das sich in der IV-Spalte des Periodensystems befindet, wurde aber von Winkler im Jahr 1886 entdeckt [19] als er das neu entdeckte Mineral Argyrodit analysierte. Nach Aufschlüsselung aller Bestandteilen, Großteil waren Silber und Schwefel, blieb ein Fehlbetrag von rund 7 % und daraus isolierte er das reine Halbmetall und nannte es Germanium (lat. Germania = Germanien, Deutschland). [20] In den späten Vierzigern Jahren wurde Germanium das Material der Wahl, da es die beste Kristallqualität aufwies und mehr als ein Jahrzehnt lang war Germanium die Arbeitsbasis für die Entwicklung von Bipolartransistoren, während die Fortschritte bei Feldeffektgeräten aufgrund ungünstiger Oberflächeneigenschaften von Ge, wie die geringe Qualität des GeO, nicht sehr erfolgreich waren. [21] Es wurden damals ganz viele Untersuchungen der Bauelemente Materialphysik Germanium und durchgeführt. an Eines der bekanntesten Beispiele ist die McWhorter Theorie für 1/f-Rauschen, das besagt, dass die Schwankungen im Ladungstransport durch ein Gerät mit dem Tunneln in dem sogenannten langsamen Oxid fallen. [22]

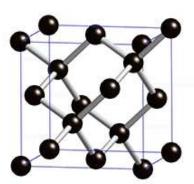

Germanium befindet sich in der 14. Gruppe mit einer Atommasse von 72,64. Er verfügt über vier Elektronen in seiner Valenzschale und kristallisiert bei Raumtemperatur genau wie Silizium in der Diamantstruktur (krz- kubisch raumzentriert, im Raumgitter einer kubisch raumzentrierten Elementarzelle befinden sich 9 Atome, 8 Eckatome und 1 Atom in der Würfelmitte, mit einer Gitterkonstante von 5,66 Å. [23] Jedes Ge-Atom ist von vier anderen Atomen umgeben, die an den Ecken eines Tetraeders positioniert und durch kovalente Bindungen verbunden sind. [24] In Diamantkristall befinden sich die Atome in einem sp3-Hybridisierten Zustand und alle verfügbaren Valenzelektronen können mit den Nachbarn geteilt werden, sodass nur die Bindungsorbitale besetzt wird. Dadurch erzeugen wir ein komplett aufgefülltes Valenzband und ein Leitungsband, die durch eine Energielücke getrennt sind. [25]

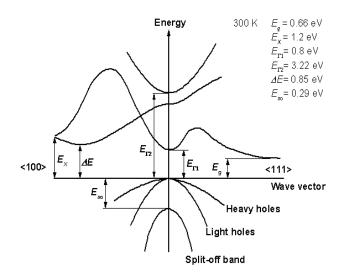

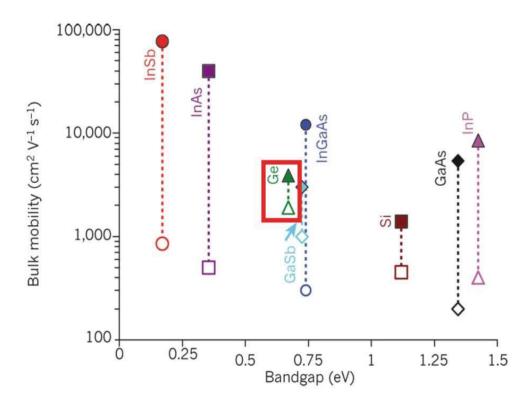

Germanium ist ein indirekter Halbleiter, womit eigentlich die Art der Rekombination gemeint ist, der Übergang von Elektronen aus dem Leitungsband in das Valenzband. Bei indirekten Bandübergang Mitwirkung eines ist die Phonons erforderlich. Bandlücke von Ge beträgt Eg = 0,66 eV wie in Abbildung 2.1.1. dargestellt, und ist somit 0,46 eV kleiner als die von Si [9], was zu sehen ist in Abbildung 2.1.2.. Die erleichterte Übertragung von Elektronen von Valenzband in das Leitungsband ist genau der geringen Bandlücke zur verdanken. Germanium hat einen Schmelzpunkt von 938,25°C und einen Siedepunkt von 2833°C. Die Elektronen- und Lochmobilität in Germanium sind wichtige physikalische Eigenschaften dieses Halbleitermaterials. Mobilität bezieht sich auf die Fähigkeit von Elektronen und Löchern, sich in einem Material zu bewegen, wenn sie von einem äußeren elektrischen Feld beeinflusst werden. Diese Mobilität ist ein entscheidender Parameter für die Leistung von Halbleiterbauelementen wie Transistoren und Dioden. Germanium weist mit 1800 cm<sup>2</sup>/Vs die höchste Löchermobilität aller Halbleiter und in Vergleich zu Silizium hat er bei Elektronen den doppelten und bei Löchern den vierfachen Wert von Silizium erreicht, wie sich aus Tabelle 2.1.1 sehen lässt. [27]

|           | Elektronen                     | Löcher                        |

|-----------|--------------------------------|-------------------------------|

| Silizium  | $1350 \text{ cm}^2/\text{V s}$ | $480 \text{cm}^2/\text{V s}$  |

| Germanium | $3600 \text{ cm}^2/\text{V s}$ | $1800 \text{cm}^2/\text{V s}$ |

|           |                                |                               |

Tabelle 2.1.1: Ladungsträgermobilität von Silizium und Germanium bei 300 K [27][28]

Germanium verfügt über leichte effektive Massen an Elektronen und Löchern, die zu einer deutlich höheren Ladungstragemobilität führen. [29] Die Löchermobilität ist die höchste in Vergleich mit allen bekannten Halbleitermaterialien und aus diesem Grund ist Germanium ein vielversprechendes Material für die Hochleistung-CMOS-Technologie, das bei sehr niedrigen Spannungen von etwa 0.5 V betrieben werden kann. [30]

Trotz der hohen Ladungsmobilität von Ge wird Si sehr häufiger in der Produktion eingesetzt. Grund dafür ist, dass sich Si-Oxid wie ein guter Isolator auch bei hoher Temperatur und Umgebungsdruck gezeigt hat. Im Gegensatz dazu bildet Germanium ein Oxid, das instabil, je nach Stöhiometrie sogar wasserlöslich und leicht in mehrere Ge-O-Suboxide zerfällt und somit die Morphologie und die elektrische Qualität der Grenzfläche stark beeinflusst. Die Zusammensetzung und die Qualität der Oxidschicht ist stark abhängig von der Temperatur sowie dem Druck. [31] Der bevorzugte Oxidation Zustand wäre GeO<sub>2</sub>, mit dem wir die Dichte der Fallenzustände an der Grenzfläche verringern könnten, leider reagiert GeO2 bei höheren Temperaturen (> 400°C) mit der Grenzfläche und zerfällt zur GeO, was wieder zur einer Zunahme der Fallenzustände führt. [31]

Aufgrund der höheren Qualität der GeO2/Ge-Grenzfläche ist also die Bildung von GeO2 bevorzugt, um Oberflächeneinschlüsse zu reduzieren, obwohl keiner dieser Oxide stabil bleibt. [31] Mit der Einführung von High-k-Dielektrika als Gate Oxide, wurde Germanium wieder einer der potenziellen Halbleitermaterialien für die zukünftigen Hochleistungsbauelemente. [32]

Abbildung 2.1.1.: Bandstruktur von Ge bei 300 K. Die indirekte Bandlücke mit E = 0.66 eV befindet sich bei k = 111 (L-Punkt). Die direkte Bandlücke E = 0.80 eV liegt am  $\Gamma$ -Punkt (k = 0) und ist nur 0.14 eV höher als die indirekte Bandlücke. (Ioffe Institute, Band structure and carrier concentration of Germanium.) Abbildung aus Ref. [28] und Kristallstruktur von Germanium-krz Diamantstruktur (fcc) (von: Brian0918 http://www.msm.cam.ac.uk/phase-trans/2003/MP1.crystals/MP1.crystals.html; English Wikipedia)

Abbildung 2.1.2. Vergleich der Banstrukturen einiger Halbleiter Materialien, Abbildung aus Ref [33]

Die Zugfestigkeit von Ge ist wesentlich geringer als die von Si, da die Dichte und damit auch die Probendicke von Germanium doppelt so hoch ist wie die von Si. Der E-Modul ist ein Maß für den Wiederstand eines Festkörpers gegen Verformung, wenn mechanische Kräfte auf ihn wirken. [34] Aufgrund der hohen Dichte von Germanium in Vergleich zur Si, führt es zu höheren Krümungswerten für Germanium. Die Härte von Germanium ist sehr gering und daher auch sehr leicht durch Partikel in der Anwendung zu zerkratzen. Studien der mechanischen Eigenschaften von Versetzungen in Germanium und ihres Zusammenhangs mit der Materialfestigkeit und den plastischen Fluss, zeigen eine viel höhere Versetzungsmobilität in Germanium als in Silizium. [21][35]

In Tabelle 2.1.2 sind die physikalischen und elektrischen Eigenschaften verschiedener Halbleitermaterialien zusammengefasst und einander gegenübergestellt, um ihre Eignung für unterschiedliche Anwendungen und Einsatzbedingungen zu veranschaulichen.

| Eigenschaften            | GaAs                                  | Ge                                         | Si                                    |

|--------------------------|---------------------------------------|--------------------------------------------|---------------------------------------|

| Kristallstruktur         | Zinkblende                            | Diamant                                    | Diamant                               |

| Dichte                   | $5.32 \text{ g cm}^{-3}$              | 5.323 g cm <sup>-3</sup>                   | 2.239 g cm <sup>-3</sup>              |

| Dielektrizitätskonstante | 12.9                                  | 16.2                                       | 11.7                                  |

| Energieband              | 1.12 eV                               | 0.661 eV                                   | 1.43 eV                               |

| Elektronenaffinität      | 4.07 eV                               | 4.0 eV                                     | 4.05 eV                               |

| Härte nach Mohs-         | 4-5                                   | 6                                          | 7                                     |

| Skala                    |                                       |                                            |                                       |

| Schmelzpunkt Tm          | 1240°C                                | 937 °C                                     | 1412°C                                |

| [100] Elastizitätsmodul  | $8.59 \cdot 10^{11} \text{dyn/cm}^2$  | 10.3·10 <sup>11</sup> dyn cm <sup>-2</sup> | $13.0 \cdot 10^{11} \text{ dyn/cm}^2$ |

| Schubmodul               | $3.285 \cdot 10^{11} \text{dyn/cm}^2$ | 4.1·10 <sup>11</sup> dyn cm <sup>-2</sup>  | $5.2 \cdot 10^{11}  \text{dyn/cm}^2$  |

| [100] Poissonzahl        | 0.31                                  | 0.26                                       | 0.28                                  |

| Diffusionskoeffizient    | $\leq 10 \text{ cm}2/\text{s}$        | $\leq 50 \text{ cm}^2 \text{ s}^{-1}$      | $\leq 12 \text{ cm}^2/\text{s}$       |

| Löcher                   |                                       |                                            |                                       |

| Diffusionskoeffizient    | $\leq 200 \text{ cm}^2/\text{s}$      | $\leq 100 \text{ cm}^2 \text{ s}^{-1}$     | $\leq$ 36 cm <sup>2</sup> /s          |

| Elektronen               |                                       |                                            |                                       |

Tabelle 2.1.2 Materialeigenschaften sowie einige mechanische und thermische Eigenschaften von Germanium und Silizium auf 300 K. [28]

Wie bereits in der Einführung erwähnt, wurde der erste Transistor aus Germanium gefertigt (siehe Abbildung 2.1.3), dss sich durch eine hohe elektrische Leitfähigkeit auszeichnet und somit besonders für Anwendungen bei hohen Frequenzen geeignet ist.

Abbildung 2.1.3. Erster Transistor aus Germanium, Abbildung aus Ref. [36]

## 2.2. "High-k" Dielektrika

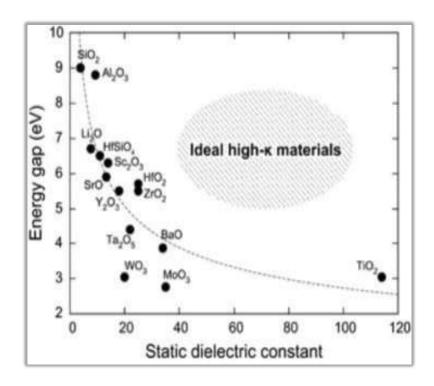

In einem Metall-Oxid-Halbleiter-Kondensator (MOSCAP) fungieren der Halbleiter und das Metall als die beiden leitenden Platten des Kondensators, während das Oxid oder Nitrid als Dielektrikum dient. Diese dielektrische Schicht ist entscheidend, da sie die elektrischen Ladungen voneinander trennt und isoliert. Das Dielektrikum muss ein nicht leitfähiges Material, also ein Isolator sein, das den Durchfluss von elektrischem Strom effektiv verhindert. In der Regel wird ein "lineares" Dielektrikum verwendet, um die Kapazität des Bauelements bei höher werdender Spannung linear zu erhöhen und elektrische Ladungen zu speichern. Die Dielektrizitätskonstante des verwendeten Oxids oder Nitrids beeinflusst direkt die Kapazität des MOSCAPs, da sie bestimmt, wie stark das Dielektrikum das elektrische Feld zwischen den Platten beeinflusst. [37] Je höher die Dielektrizitätskonstante, desto größer ist die Kapazität des Kondensators, was bedeutet, dass mehr Ladung gespeichert werden kann. [37] Die Funktion dieser Struktur besteht darin, elektrische Ladungen effizient zu speichern und bei Bedarf abzugeben. In der Halbleitertechnologie werden sogenannte High-k-Dielektrika verwendet, (wobei "k" der englische Begriff für relative Dielektrizitätskonstante ε<sub>r</sub> ist) um die Kapazität weiter zu steigern. Ein High-k-Dielektrikum ist ein Material mit einer höheren relativen Dielektrizitätskonstante als Siliziumdioxid ( $\varepsilon_r = 3.9$ ) oder Siliziumoxinitride ( $\varepsilon_r < 6$ ). [38]

Im Rahmen dieses Projekts wurden High-k-Filme auf einem Germanium-Substrat abgeschieden, um den Mobilitätsverlust, der bei Silizium-basierten Systemen auftreten kann, auszugleichen. Germanium hat im Vergleich zu Silizium eine höhere Ladungsträgermobilität, was zu einer besseren Leistung der MOS-Bauelemente führt. [39] Die richtige Auswahl des Dielektrikum-Materials ist von entscheidender Bedeutung. Aus diesem Grund wurden in dieser Arbeit verschiedene High-k-Materialien untersucht, darunter auch HfO<sub>2</sub> (siehe Tabelle 2.2.1). Es ist bekannt, dass MOS-Transistoren mit einem Si-Substrat und HfO2 als Gate-Dielektrikum inhärenten Beweglichkeitsverschlechterung leiden. bedingt durch Wechselwirkungen der Inversionsschichtladung mit Grenzflächendefekten und fester Oxidladung sowie durch die Fernwirkung von Phononen in HfO<sub>2</sub>. [39]

Um diese Nachteile zu minimieren, wurde das Si-Substrat durch ein Ge-Substrat ersetzt, das eine höhere Elektronen- und Löcher-Mobilität aufweist. [39] Ein weiterer Vorteil von High-k-Materialien ist die Reduzierung des Leckstroms, einem unerwünschten elektrischen Strom, der die Leistung von Bauelementen negativ beeinflusst, indem er zu einem höheren Energieverbrauch und einer stärkeren Erwärmung führt, was letztlich die Lebensdauer eines Bauteils verringern kann. [37], [38] Die technologische Entwicklung hat inzwischen einen Punkt erreicht, an dem SiO2 durch alternative Materialsysteme wie High-k-Filme ersetzt werden muss, um den steigenden Anforderungen an die Miniaturisierung und Leistungsfähigkeit gerecht werden.[40]  $\mathbf{z}\mathbf{u}$

Damit ein hochdielektrisches Material für die Integrierung an Germanium für Aufbau des MOSCap Bauteiles ausgewählt wird müssen viele Kriterien erfüllt sein. Wichtigste sind [41]:

- Hoher k-Wert: Der k-Wert des Oxids muss hoch genug sein, um eine langfristige Skalierbarkeit zu ermöglichen. Idealerweise sollte der k-Wert über 10 liegen, vorzugsweise bei 25-30, bei gleichzeitig ausreichendem Bandabstand.

- **Thermodynamische Stabilität:** Das Dielektrikum dem Halbleitermaterial reagieren, um die Integrität der Schicht zu gewährleisten.

- Kinetische Stabilität (Temperaturstabilität bis 1000°C): Das Dielektrikum muss den bestehenden Prozessbedingungen standhalten können, ohne zu degradieren.

- Reinheit des Oxids: Es sollten keine elektrisch aktiven Defekte vorhanden sein, um eine optimale Performance zu gewährleisten.

- Isolator-Funktion: Das Material muss als effektiver Isolator wirken, was erfordert, dass die Potenzialbarrieren an jedem Band über 1 eV liegen.

- Hohe Grenzschichtqualität: Das Dielektrikum muss eine gute elektrische Schnittstelle mit dem Halbleiter bilden und eine hohe Qualität der Grenzfläche sicherstellen.

Die elektrische Leitfähigkeit der dielektrischen High-k-Filme sowie der Grenzfläche zwischen High-k und Substrat hängt maßgeblich vom Abscheidungsprozess ab. Dabei spielen die genaue Auswahl der Abscheidungsparameter, die Oberflächenbehandlung vor der Abscheidung und die anschließenden Glühtemperaturen eine entscheidende Rolle. [39] In Tabelle 2.2.1 sind die wichtigsten High-k-Materialien mit ihren spezifischen Dielektrizitätskonstanten (k-Werten) sowie ihren Bandlücken (Eg-Werten) aufgeführt, um einen umfassenden Überblick über deren Eigenschaften zu geben.

| High-k Material  | k       | Eg[eV]                       |

|------------------|---------|------------------------------|

| $ m ZrO_2$       | 25      | 7.8                          |

| $HfO_2$          | 25      | 5.7                          |

| $Al_2O_3$        | 9       | 8.7                          |

| HfN              | 30 [42] | ~ 1.46 HfN <sub>2</sub> [43] |

| AIN              | 9.14    | 6.2                          |

| SiO <sub>2</sub> | 3.9     | 8.9                          |

| $\mathrm{GeO}_2$ | 5.2     | 5.7                          |

Tabelle 2.2.1 [40] Liste mit wichtigen High-k Materialien // Quelle: https://www.ioffe.ru

Abbildung 2.2.1.aus Ref. [44] Darstellung der Bandlücke und Dielektrizitätskonstanten für einige Oxide

### 2.3. Metall-Halbleiter Heterestrukturen

Für die Realisierung elektronischer Bauelemente ist es von großer Bedeutung zuverlässige Kontakte herzustellen, die idealweiße keine Grenzflächendefekte aufweisen und den Kontaktwiederstand reduzieren. Unbehandelte Metall-Halbleiter Kontakte zeigen große Schottky-Barrieren, die berücksichtigt werden müssen, da die Barrieren Höhe einen starken Einfluss auf die elektrischen Eigenschaften der Heterostruktur aufweist. [45]

Silizide und Germanide spielen eine zentrale Rolle in der Entwicklung von Metall-Halbleiter-Heterostrukturen. Diese Verbindungen werden aufgrund ihrer hervorragenden elektrischen Eigenschaften und ihrer Fähigkeit, stabile, gut definierte Schichten zu bilden, intensiv erforscht. Silizide, wie Nickel- und Kobaltsilizid, sind besonders wichtig in der CMOS-Technologie, da sie eine geringe Schottky-Barriere und exzellente Leitfähigkeit bieten. [46] Silizide, die intermetallischen Phasen, die oft durch eine Festkörperreaktion zwischen Silizium und einer Metallschicht gebildet werden, finden in der Silizium-basierten Technologie breite Anwendung als Kontaktmaterialien. Ihre Beliebtheit verdanken sie ihrer Eignung für den selbstjustierenden Silizid- (Salicide-Prozess). Dabei wird besonders NiSi als Kontakt verwendet, da es eine geringe elektrische Resistivität, gute thermische Stabilität und die Fähigkeit besitzt, auch in sehr kleinen Dimensionen gebildet zu werden. [47]

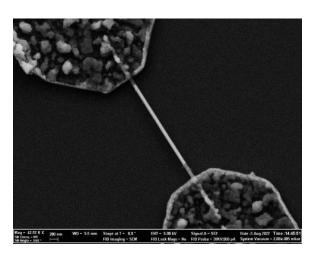

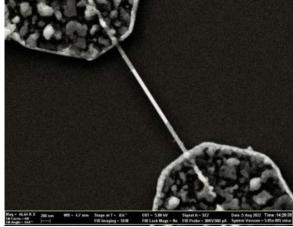

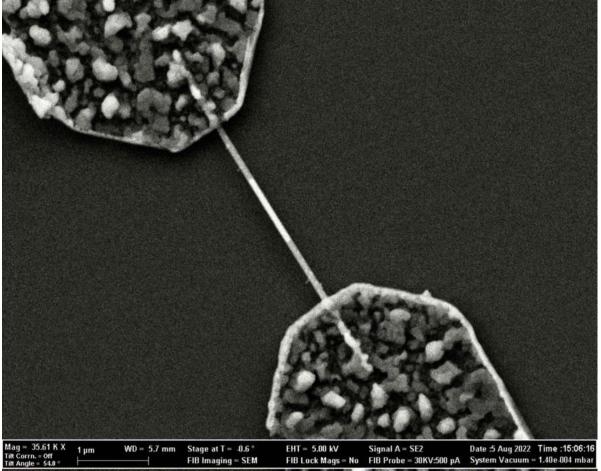

Germanium-Nanodrähte sind besonders interessant, da Germanium im Vergleich zu Silizium eine höhere Ladungsträgermobilität aufweist. [48] Dies erfordert aber die Integration von Germaniumoxiden mit höherer Dielektrizitätskonstante in das Gerätedesign. [49]

Darüber hinaus hat Germanium einen größeren Bohr-Radius für Exzitonen als Silizium, wodurch das Quantenconfinement auch in Nanodrähten mit größerem Durchmesser besser beobachtet werden kann. Allerdings könnten die elektrischen Kontakte die Leistung von Halbleiter-Nanodraht-Bauelementen beeinträchtigen, da die Schottky-Barriere an der Metall-Halbleiter-Grenzfläche eine Herausforderung darstellt. [47]

Nickelgermanid-Kontakte werden voraussichtlich eine wichtige Rolle in der auf Germanium basierenden Elektronik spielen, ähnlich wie ihre Nickel-Silizid-Gegenstücke in Siliziumbasierten Bauelementen. [47], [50] Diese Prozesse erfordern jedoch ein hohes thermisches Budget, was das Germaniumsubstrat und die Germanium/Dielektrikum-Schnittstellen in der MOSFET-Herstellung beeinträchtigen kann. [50] Die Kurzschlussprobleme bei NiGe/Ge-Bauelementen sind in erster Linie auf die thermisch getriebene Diffusion von Nickel (Ni) in das Germanium (Ge)-Substrat zurückzuführen. Bei der Herstellung von Bauelementen mit Nickelgermanid (NiGe) als Kontaktmaterial wird das Nickel auf das Germanium aufgebracht und bei hohen Temperaturen erhitzt, um die Reaktion zwischen Nickel und Germanium zu initiieren, wodurch eine dünne NiGe-Schicht entsteht. [51] Allerdings treten bei höheren Temperaturen thermisch bedingte Diffusionsprozesse auf, bei denen Nickel-Atome in das Germanium eindringen. Dadurch können sich Bereiche im Bauelement bilden, in denen es lokal zu Kurzschlüssen kommt (Spiking), die die Funktion des Bauelements erheblich beeinträchtigen können. Sie können dazu führen, dass das Bauelement nicht mehr als Transistor arbeitet, sondern dauerhaft im leitenden Zustand verbleibt. [51] Zur Lösung dieses Problems wird oft versucht, die Temperatur während des Herstellungsprozesses zu senken, um die Nickel-Diffusion zu minimieren. Es wird ein Verfahren mit niedrigerer Temperatur, basierend auf einer schnellen thermischen Behandlung (Rapid Thermal Annealing, RTA), für Nickelgermanid-Kontakte vorgeschlagen. [50]

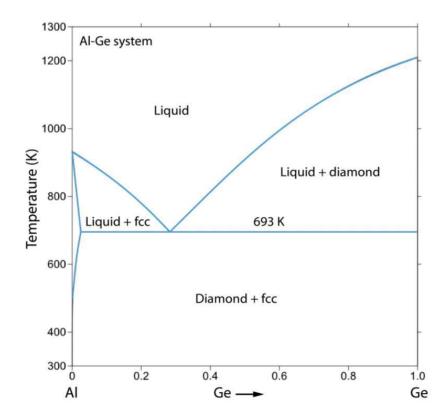

Aluminium (Al) zeigte bemerkenswerte Ergebnisse ohne die Bildung von intermetallischen Phasen, wodurch Al-Atome, Ge-Atome ersetzen und somit eine Metall-Halbleiter-Heterostruktur mit einer bis hin zu atomar scharfen Grenzfläche schaffen kann. Dies wird durch den hohen Diffusionskoeffizienten von Ge in Al ermöglicht, im Vergleich zur Diffusion von Al in Ge. Dadurch kommt es zu einer Austauschreaktion, bei der Ge ausdiffundiert und Al den Platz einnimmt. [52] Zudem weist Al gute elektrische und mechanische Eigenschaften auf und keine hohe Variabilität, was auf einen zuverlässigen und ausgefeilten Diffusionsprozess hinweist. [53] Al ist ein Metall, das in der 3. Gruppe des Periodensystems der Elemente zu finden ist. Es hat die Ordnungszahl 13 und eine relative Atommasse von 26,98. Die Schmelzund Siedepunkte liegen bei 933 K bzw. 2790 K. Al kristallisiert in einer kubischflächenzentrierten Struktur mit einer Gitterkonstante von a = 0,405 nm. Aluminium kommt in der Natur nur in Verbindungen wie Feldspat, Granit und Bauxit vor und wird hauptsächlich aus dem Erz Bauxit durch eine äußerst energieintensive Elektrolyse gewonnen, wobei Al von ungefähr 99,99 % Reinheit erreicht wird. [54] In Bezug auf die Klassifikation ist Al ein dreiwertiges und Ge ein vierwertiges Element. Es gibt keine stabile stöchiometrische Verbindung von Al und Ge. Das binäre Phasendiagramm das Al-Ge Materialsystem, das in Abbildung 2.3.1 dargestellt ist, zeigt die Schmelzpunkte von Al und Ge bei 933 K bzw. 1211 K. [55] Der eutektische Punkt des Materialsystems liegt bei einer Ge-Zusammensetzung von 29,5 % mit einem Fest-Flüssig-Übergang bei 693 K. Da die Löslichkeit von Ge in Al unterhalb der eutektischen Temperatur sehr gering ist, können nur etwa 2 % Ge in Al eingebaut werden. Die Löslichkeit von Al in Ge beträgt weniger als 1% und ist daher noch geringer. Das bedeutet das die Bildung von nur lokalen Kristalliten viel wahrscheinlicher ist als die Bildung von intermetallischen Phasen. [55]

Abbildung 2.3.1. Phasendiagramm des Al-Ge Materialsystems: Der eutektische Punkt zeigt einen Fest-Flüssigen-Übergang bei 693 K für eine Ge- Zusammensetzung von 29,5 %. Abbildung aus Ref. [55], [2]

### 2.4. Oxid-Halbleiter Grenzfläche

Die Oxid-Halbleiter-Grenzfläche spielt eine entscheidende Rolle bei der Bestimmung der elektrischen Eigenschaften und des Verhaltens eines Halbleiterbauteils. Diese Grenzfläche erfüllt mehrere wesentliche Funktionen [56], [57]:

- Isolation: Das Oxid wirkt als Isolator zwischen dem Metall und dem Halbleitermaterial und verhindert so unerwünschte Leckströme. Diese Isolation ist entscheidend, um die Integrität des elektrischen Signals zu bewahren und Energieverluste zu minimieren.

- Gate-Steuerbarkeit: Die Grenzfläche bildet den Bereich, der durch die an das Gate angelegte Spannung gesteuert wird. Durch die Anpassung dieser Spannung kann der Kanal im MOSFET geöffnet oder geschlossen werden, wodurch der Stromfluss gezielt gesteuert wird.

- Ladungstransfer: An der Grenzfläche werden Elektronen oder Löcher in den Halbleiter injiziert oder gesammelt, um den Stromfluss zu kontrollieren. Diese Funktion ist zentral für die Leistungsfähigkeit und Effizienz des Bauteils.

Trotz dieser wichtigen Funktionen sind bestimmte Phänomene an der Grenzfläche, wie gefangene Ladungen und Defekte, besonders kritisch. Diese fallen und Ladungen beeinflussen die elektrische Leistung erheblich, die an Beispiel der Si-SiO2-Grenzfläche, im Folgenden näher erläutert werden [57]:

- 1. Grenzflächengefangene Ladungen: Diese können positive oder negative Ladungen sein, die an der Si-SiO2-Grenzfläche auftreten. Sie entstehen durch ungesättigte Bindungen, Strukturfehler, Fehler bei der Oxidation oder Metallverunreinigungen, die durch Strahlung oder Bindungsbruchprozesse verursacht werden. Diese offene Bindungen können durch einen Annealing-Prozess bei niedrigen Temperaturen (etwa 450°C) in einem Wasserstoff- oder Formiergas gesättigt werden.

- 2. Feste Oxidladungen: Diese positiven Ladungen befinden sich in der Nähe der Si-SiO<sub>2</sub>-Grenzfläche. Sie sind, wie der Name andeutet, fest und ihre Dichte bleibt unabhängig vom elektrischen Potential konstant. Die Dichte dieser Ladungen wird nicht durch die Dicke des Oxids oder Verunreinigungen im Silizium beeinflusst, sondern hängt von der Oxidationsqualität und anderen Faktoren wie den Annealing-Bedingungen und der Kristallorientierung des Siliziums ab.

- 3. Oxid-eingefangene Ladungen: Diese Ladungen entstehen durch Defekte im SiO2 und können sowohl positiv als auch negativ sein. Sie resultieren aus Löchern oder Elektronen, die im Oxid gefangen werden. Diese Ladungen können eine Verschiebung der Hochfrequenz-C-V-Kurve entlang der Spannungsachse verursachen, was die elektrische Charakteristik des Bauelements beeinflusst.

- 4. Mobile Ionische Ladungen: Diese Ladungen entstehen durch Verunreinigungen, hauptsächlich durch Alkali-Metallionen wie Natrium und Lithium oder durch negative Ionen und Schwermetalle. Solche Ladungen sind in Halbleiterbauelementen unerwünscht, da sie bereits bei moderaten Temperaturen oder Spannungen Zuverlässigkeitsprobleme verursachen können.

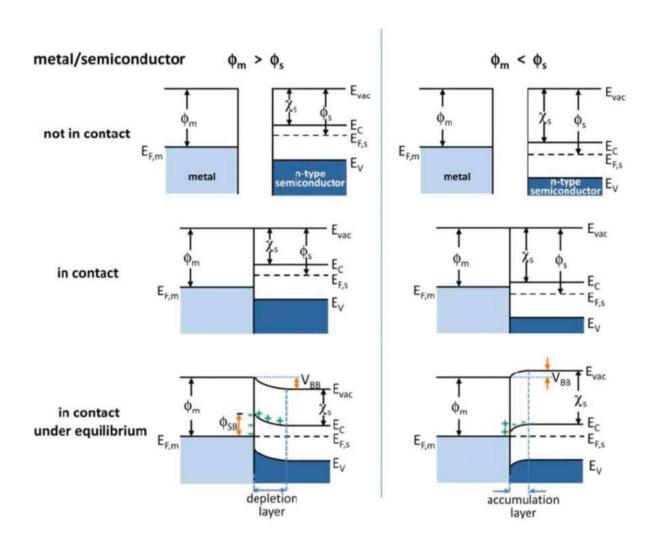

## 2.5. Schottky Barriere

Die früheste systematische Untersuchung von Metall-Halbleiter-Gleichrichtersystemen wird gemeinhin Karl Ferdinand Braun zugeschrieben. Bereits im Jahr 1874 erkannte Braun eine Abhängigkeit des Gesamtwiderstands eines Punktkontakts von der Polarität der angelegten Spannung sowie von den spezifischen Oberflächenbedingungen des Kontakts. [9] Im Jahr 1931 legte Wilson mit der Formulierung der Transporttheorie von Halbleitern auf Basis der Bändertheorie der Festkörper die theoretischen Grundlagen, die später auf Metall-Halbleiter-Kontakte angewandt wurden. [9] Ein bedeutender Fortschritt erfolgte 1938, als der Physiker Walter Schottky vorschlug, dass die Potentialbarriere an einem Metall-Halbleiter-Kontakt ausschließlich durch stabile Raumladungen im Halbleiter entstehen könnte, ohne dass eine chemische Zwischenschicht erforderlich wäre. [9] Die Schottky-Barriere stellt ein fundamentales Konzept in der Halbleitertechnologie dar und ist entscheidend für das Verständnis und die Kontrolle der Eigenschaften von Halbleiterbauelementen. Sie beschreibt eine physikalische Barriere, die an der Grenzfläche zwischen einem Metall und einem Halbleiter entsteht. Die Bildung der Schottky-Barriere wird primär durch die unterschiedlichen Austrittsarbeiten von Metallen und Halbleitern bestimmt, die aufgrund der unterschiedlichen elektronischen Eigenschaften auf verschiedenen Energiehöhen liegen. Beim Kontakt zwischen einem Metall und einem Halbleiter fließen Elektronen vom Metall mit dem höheren Fermi-Niveau in den Halbleiter mit dem niedrigeren Fermi-Niveau, um ein thermodynamisches Dieser Elektronenfluss Gleichgewicht herzustellen.[27] führt zur Bildung Raumladungszone in der Nähe der Grenzfläche, in der positive und negative Ladungen durch den Elektronenfluss räumlich getrennt werden. In dieser Raumladungszone diffundieren Elektronen aus dem Metall in den Halbleiter, wobei sie im Metall positiv geladene Ionen und im Halbleiter negative Ladungen (Elektronen) hinterlassen. Dies führt zur Entstehung der Schottky-Barriere, die von den Elektronen nur überwunden werden kann, wenn sie eine ausreichende Energie aufweisen. [27] Die Höhe der Schottky-Barriere hat einen entscheidenden Einfluss auf die Leistung und Funktionalität der entsprechenden Bauelemente und kann durch verschiedene experimentelle und theoretische Methoden bestimmt werden. Zu den wichtigsten Methoden zur Charakterisierung der Schottky-Barriere gehören [48], [57]:

- I-V-Charakterisierung: Diese Methode misst den Strom, der durch eine Schottky-Diode fließt, in Abhängigkeit von der angelegten Spannung. Sie ermöglicht eine direkte Bestimmung der Strom-Spannungs-Beziehung und damit der Schottky-Barriere-Höhe.

- C-V-Charakterisierung: Die Kapazitäts-Spannungs-Messung analysiert die Kapazität einer Schottky-Diode in Abhängigkeit von der angelegten Spannung und liefert Informationen über die Raumladungszone und die Verteilung der Ladungsträger.

- Photoelektronen Spektroskopie (PES): Diese Technik erlaubt die direkte Untersuchung der Elektronenenergien an der Grenzfläche zwischen Metall und Halbleiter. Die kinetische Energie der emittierten Photoelektronen gibt Aufschluss über die Schottky-Barriere-Höhe.

- Strom-Temperatur-Kennlinie (Richardson-Plot): Diese Analyse untersucht den Zusammenhang zwischen Strom und Temperatur, um die Schottky-Barriere-Höhe und die Temperaturabhängigkeit des Schottky-Kontakts ermitteln. zu

Theoretische Modellierung und Simulation: Diese Methoden ermöglichen es, die physikalischen Mechanismen der Schottky-Barriere auf atomarer Ebene zu verstehen und Vorhersagen über ihr Verhalten unter verschiedenen Bedingungen zu treffen

Die Schottky-Barriere an der Metall-Halbleiter-Grenzfläche Beziehung qφSB=q(φm-γs) beschrieben, wobei φm das Metallaustrittsarbeit und γs die Elektronenaffinität des Halbleiters darstellt. [58] Die Elektronenaffinität ist die Energie, die benötigt wird, um ein Elektron vom unteren Rand des Leitungsbandes bis zur Vakuumenergie zu bringen. Wenn φm>χs ist, bildet sich eine Schottky-Barriere; ist jedoch φm<χs entsteht kein Schottky-Kontakt, sondern ein ohmscher Kontakt, bei dem die Grenzfläche keinen nennenswerten Einfluss auf den Stromfluss hat. [58] Dies wird anschaulich in Abbildung 2.5.1 dargestellt. Ein ohmscher Kontakt ist ein Metall-Halbleiter-Kontakt, der einen im Verhältnis zum Gesamtwiderstand des Halbleiterbauelements vernachlässigbaren Übergangswiderstand aufweist. [9] Ein idealer ohmscher Kontakt beeinträchtigt die Leistung des Bauelements nicht und kann den erforderlichen Strom mit einem internen Spannungsabfall bereitstellen, der im Vergleich zum Spannungsabfall über den aktiven Bereich des Bauelements gering ist. [9]

Abbildung 2.5.1. Darstellung von Schottky Kontakt (links) und Ohm'scher Kontakt (rechts. Abbildung aus Ref. [59], [60]

## 2.6. Metall-Oxide-Semiconductor (MOS)

MOS steht für "Metall-Oxide-Semiconductor" (Metall-Oxid-Halbleiter) und bezeichnet eine Technologie, die in der Elektronikindustrie von zentraler Bedeutung ist. Diese Technologie bietet zahlreiche Vorteile, weshalb sie weitverbreitet in der Herstellung von Transistoren und integrierten Schaltkreisen (ICs) zum Einsatz kommt. [9] Ein MOS-Transistor besteht aus einem Halbleitersubstrat und einer Metall-Elektrode, die durch eine dünne Schicht aus Oxid voneinander getrennt sind (siehe Abbildung 2.6.1). Diese Struktur bildet die Grundlage für die Funktionalität von MOS-Transistoren, die als Schaltelemente in digitalen und analogen Schaltungen fungieren. Das Oxid, spielt eine entscheidende Rolle, da es als Isolator wirkt und die Steuerung des Stromflusses durch das elektrische Feld der Metall-Elektrode ermöglicht. Die MOS-Technologie ist daher nicht nur für die Entwicklung leistungsfähiger Transistoren, sondern auch für die Miniaturisierung und Effizienzsteigerung moderner integrierter Schaltkreise unerlässlich.

Abbildung 2.6.1. Schematische Darstellung MOSCAP-Bauteiles

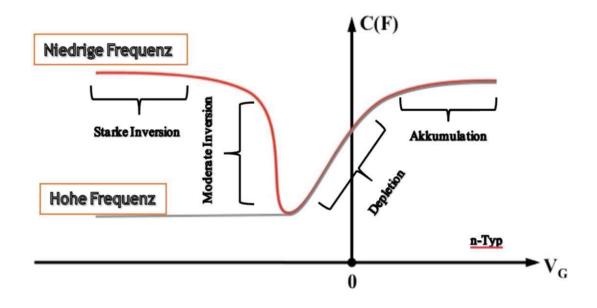

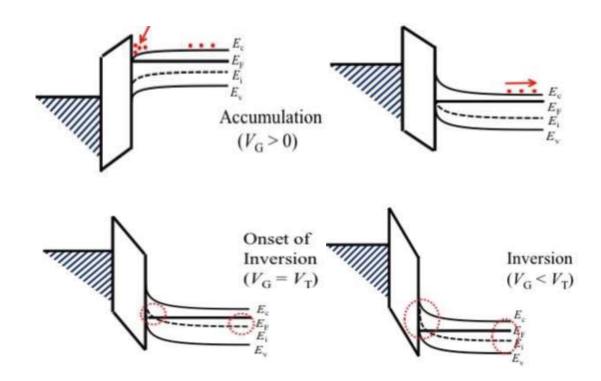

Struktur sowie die Verteilung von Ladungsträgern können durch Kapazitätsspannungsmessungen (C-V) detailliert charakterisiert werden. Abhängig von der angelegten Vorspannung lassen sich in einer C-V-Kurve drei wesentliche Bereiche unterscheiden [57],[61] im Beispiel eines n-dortierten Halbleiter:

- Akkumulation tritt auf, wenn eine positive Spannung an das Gate eines MOS-Transistors angelegt wird. Diese Spannung zieht Elektronen an die Grenzfläche zwischen Halbleiter und Oxid, wodurch eine stark dotierte Schicht entsteht. In diesem Zustand sammelt sich eine hohe Konzentration von Elektronen in der Nähe der Grenzfläche, was zu einer erhöhten Leitfähigkeit führt, da Elektronen leicht zwischen Source und Drain fließen können. Dies verbessert die Leistung des Transistors erheblich.

- Depletion (Verarmung) erfolgt, wenn eine negative oder keine Spannung an das Gate angelegt wird. In diesem Fall werden die freien Ladungsträger in der Nähe der Halbleiteroberfläche reduziert, wodurch eine Verarmungszone entsteht. Diese Zone ist arm an freien Ladungsträgern und dadurch nicht leitfähig, was den Stromfluss zwischen Source und Drain stark einschränkt.

- **Inversion (Umkehrung)** wird erreicht, wenn eine ausreichend hohe positive Spannung an das Gate angelegt wird. Diese Spannung zieht eine ausreichende Menge an Elektronen an die Halbleiter-Oxid-Grenzfläche. Es bildet sich eine Inversionsschicht. Wenn die Minioritäten > Majoritäten haben wir schwache Inversion, wenn die Minioritäten < Dotierungskonzentration, sprechen wir über strake Inversion. Diese Schicht bildet einen Kanal, der den Stromfluss zwischen Source und Drain ermöglicht und den MOS-Transistor in den "Ein"-Zustand versetzt.

Der Hauptunterschied zwischen Akkumulation und Inversion liegt in der Intensität des Effekts: Während die Akkumulation zu einer moderaten Erhöhung der Leitfähigkeit führt, bewirkt die Inversion einen starken, vollständig leitfähigen Zustand, der den Transistor in einen stabilen "Ein"-Zustand versetzt. Diese Zustände sind in Abbildung 2.6.2. dargestellt und verdeutlichen die unterschiedlichen Betriebsmodi eines MOS-Transistors.

Abbildung 2.6.2. C-V Kurve von CMOS für n-Typ Halbleiter

Abbildung 2.6.3. Drei Zustände von n-Typ MOS Gerät (oben links: Akkumulation oben rechts: Depletion VG < 0; unten links(VG=VT) und rechts starke Inversion). Abbildung aus Ref. [62]

## 2.7. Feldeffekttransistoren (FET)

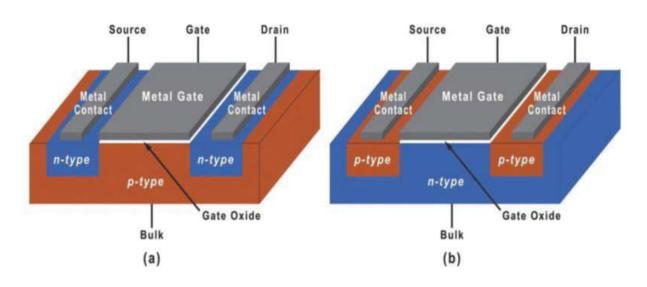

Feldeffekttransistoren (FETs) sind wesentliche Komponenten in Halbleitertechnologie und spielen eine zentrale Rolle in einer Vielzahl von elektronischen Schaltungen. Im Gegensatz zu bipolaren Transistoren (BJT), die den Stromfluss durch Steuerung eines elektrischen Stroms regulieren, ermöglichen FETs die Steuerung des Stroms über ein elektrisches Feld. Diese Eigenschaft macht FETs besonders attraktiv für Anwendungen, bei denen eine hohe Eingangsimpedanz und eine geringe Leistungsaufnahme erforderlich sind. [56] FETs wurden in den 1920er und 1930er Jahren erstmals konzipiert, etwa 20 Jahre bevor die bipolaren Transistoren entwickelt wurden. Zwei Wissenschaftler, J. E. Lilienfeld und O. Heil, entwarfen unabhängig voneinander die Grundstruktur von Transistoren, die später als FETs bekannt wurden. [56] Trotz dieser frühen Konzepte musste die praktische Umsetzung bis zur erfolgreichen Entwicklung anderer Festkörperelemente in den späten 1940er und frühen 1950er Jahren warten. Der erste moderne Feldeffekttransistor, der Junction Field-Effect Transistor (JFET), wurde von William Shockley, einem der Mitbegründer des Transistors, vorgeschlagen und theoretisch analysiert. [56] In dieser Masterarbeit liegt der Schwerpunkt auf der MOSFET-Struktur, da sie die am weitesten verbreitete Art von FET ist und in zahlreichen Anwendungen von Mikroprozessoren bis hin zu Leistungselektronik eingesetzt wird. Physikalisch gesehen kann der MOSFET als ein weiterentwickelter MOS-Kondensator betrachtet werden, bei dem zwei Übergänge (Source und Drain) unmittelbar neben dem vom Gate gesteuerten Bereich des Halbleiters platziert sind.

Das Substrat kann je nach Anwendung entweder negativ oder positiv dotiert sein. Bei n-Kanal-MOSFETs (n-MOSFETs) besteht das Halbleitermaterial aus einem negativ dotierten Substrat (n-Typ), auf dem Source, Drain und Gate angeordnet sind.

Das Gate ist über eine dünne isolierende Schicht aus einem Dielektrikum vom Kanalmaterial getrennt. Wenn eine positive Spannung am Gate (gegenüber der Source) angelegt wird, entsteht

ein elektrisches Feld, das Elektronen im Substrat anzieht und einen leitfähigen Kanal zwischen Source und Drain bildet. Dieser Kanal ermöglicht den Stromfluss zwischen Source und Drain, wobei die Höhe des Drain-Stroms ID direkt durch die Gate-Source-Spannung VGS beeinflusst wird.

Im ausgeschalteten Zustand, wenn VGS=0 oder VGS<Vth (Schwellspannung), ist der Kanal gesperrt und es fließt kein Strom. Erst wenn die angelegte Gate-Spannung die Schwellspannung Vth überschreitet, öffnet sich der Kanal und der Strom kann zwischen Source und Drain fließen. Die Steuerung des Drain-Stroms erfolgt durch die Variation der Gate-Spannung, wodurch der MOSFET als Schalter oder Verstärker in elektronischen Schaltungen eingesetzt werden kann. Die Vielseitigkeit und Effizienz des MOSFETs machen ihn zu einem unverzichtbaren Bestandteil moderner Elektronik. Seine Fähigkeit, schnell zwischen Ein- und Aus-Zuständen zu wechseln, sowie die hohe Skalierbarkeit ermöglichen die Integration von Milliarden von Transistoren auf einem einzigen Chip, was die Grundlage für die heutige Mikroelektronik darstellt. Darüber hinaus bietet die geringe Verlustleistung bei der Steuerung des Stroms durch das elektrische Feld erhebliche Vorteile in Anwendungen, bei denen Energieeffizienz von größter Bedeutung ist. Die Motivation für diesen Teil der Masterarbeit stammt großen Teils aus dem Buch "Semiconductor Device Fundamentals" von Robert F. Pierret. In Abbildung 2.5.1. werden Elemente eines typischen MOSFET gezeigt, die entweder als PMOS oder NMOS-Transistoren gebaut werden können, abhängig von der Polarität, der Bulk-, Source-, und Drain-Regionen.[63]

Abbildung 2.5.1. a) P-Typ und b) n-Typ MOSFETS. Abbildung aus Ref. [63]

### 2.8. Nanodrähte

Nanodrähte sind stäbchenförmige Nanostrukturen mit Durchmessern unter 100 nm, die ein bemerkenswert hohes Größenverhältnis von Länge zu Durchmesser aufweisen können, dass weit über 1:1000 liegt. [64] Dieses inhärent hohe Oberflächen-zu-Volumen-Verhältnis führt dazu, dass die Eigenschaften von Nanodrähten stark von ihrer Oberfläche und nicht nur vom verwendeten Material abhängen.

Daher bieten Nanodrähte eine einzigartige Plattform, um den Einfluss von Oberflächeneffekten auf elektronische Transportphänomene und optische Effekte zu untersuchen. sehr Gruppe-IV-Nanodrähten Insbesondere bei dünnen und niedrigen Dotierungskonzentrationen spielen Oberflächeneffekte eine entscheidende Rolle. Fallen an der Grenzfläche und im Oxid führen dazu, dass das Oberflächenpotenzial positiv ist und sich die Bänder nach oben biegen. Obwohl diese Nanodrähte intrinsisch oder n-dotiert sein können, wird dieser Effekt als "Oberflächendotierung" bezeichnet. Dieser Effekt kann eine Verschiebung der Energiebandstruktur über den gesamten Querschnitt des Nanodrahts (Nanowire, NW) bewirken, was zu einem Typischen p-Typ-Verhalten führt. [66], [67] Ein bedeutender Vorteil von Nanodrähten ist die Möglichkeit, eine Vielzahl von Materialien, einschließlich Halbleitermaterialien und Halbleiterverbindungen wie Silizium (Si), Germanium (Ge), Galliumarsenid (GaAs) und Galliumnitrid (GaN), für das Wachstum von Nanodrähten zu nutzen. Diese Materialvielfalt ermöglicht die Integration unterschiedlicher Funktionalitäten in CMOS-Schaltkreise, was deren Leistungsfähigkeit erheblich steigert. [68] Aufgrund ihrer geringen Durchmesser ist die Bewegung der Ladungsträger in sehr dünnen Nanodrähten häufig auf eine Dimension beschränkt, was sie zu sogenannten Quasi-1D-Nanostrukturen macht. Die Dimensionalität spielt eine entscheidende Rolle bei der Bestimmung der Materialeigenschaften, sodass elektrische, chemische und mechanische Eigenschaften von Nanodrähten angepasst werden können. [69], [70] Diese Anpassungsfähigkeit eröffnet innovative Anwendungen in einer Vielzahl von Bereichen, unterstützt durch vielseitige Herstellungsmethoden wie die Elektronenstrahllithografie und die VLS-Methode (Vapor-Liquid-Solid). [4] Die Erforschung und Entwicklung von Nanodrähten tragen wesentlich zur Schaffung fortschrittlicher Materialien und Geräte bei. Aufgrund ihrer äußerst geringen Abmessungen eignen sich Nanodrähte ideal für die Skalierung und Miniaturisierung elektronischer Bauelemente. In der CMOS-Technologie ist die kontinuierliche Verkleinerung von Transistoren und Schaltkreisen ein Schlüsselfaktor zur Steigerung der Leistungsfähigkeit und Effizienz. [71] Insgesamt bieten Nanodrähte durch ihre einzigartigen physikalischen Eigenschaften und die Vielzahl an verfügbaren Herstellungsmethoden eine vielversprechende Grundlage für zukünftige technologische Innovationen.[72]

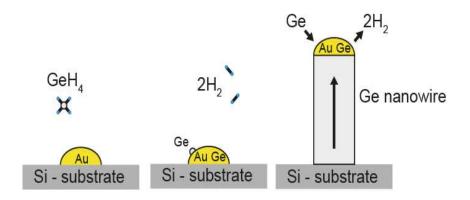

### 2.9. VLS Wachstum von Ge-Nanodrähten

Der Name VLS (Vapor-Liquid-Solid) leitete sich von den Aggregatzuständen ab, die das von Vorläufergas gelieferte Halbleitermaterial durchlaufen muss, bevor es in den NW eingebaut wird. Das Substrat sollte aus katalytischen Materialien bestehen, die die Kristallisation und das Wachstum der Nanodrähte unterstützen. Metalle wie Gold, Silber, Eisen oder Nickel werden häufig als Katalysatoren verwendet, da sie eine hohe Affinität zur Wachstumsspezies haben und die Bildung von Liquid-Droplets auf der Oberfläche ermöglichen. Die Nanodrähte (fest), die aus dem gasförmigen Vorläufermaterial auf der Oberfläche des Katalysators wachsen. [73] VLS-Wachstumsverfahren ermöglicht es, Nanodrähte mit maßgeschneiderten Eigenschaften für die Nanotechnologie und die Materialwissenschaft zu produzieren.

Zuerst wird ein Substrat vorbereitet, auf dem der Katalysator abgeschieden werden kann. Das Substrat kann aus vielen Materialien bestehen, wie Silizium, Quarz oder Saphir, oder wie in unserem Fall aus Germanium. Der Katalysator in Form von Nanopartikeln eines geeigneten Metalls wie Gold, Silber oder Kupfer wird auf die Oberfläche des Substrats abgelagert. Man kann das durch verschiedene Techniken machen. Zum Beispiel durch Wärmebehandlung, Sputtern oder chemische Reinigung. Das Substrat mit dem Katalysator wird in eine Reaktionskammer gebracht, wo gasförmige Präkursoren entstehen. Diese Moleküle disozieren sich in der Verbindung mit Nanopartikeln. [74] Die eindiffundierten Atome bilden mit den Nanopartikel einen Flüssigkeitströpfehen. Die Moleküle lösen sich bei geeigneter Temperatur und Druck aus dem Katalysator heraus. [74] So werden die Materialien gesättigt, sie beginnen zu kristallisieren und wachsen in Nanodrähten. Nanodrähte wachsen senkrecht oder verwinkelt Oberfläche des Katalysatortropfens und wachsen zur kontinuierlich. Vorläufermoleküle vorhanden sind. In konkreten Fall berührt das VLS-Verfahren für Germanium Nanodrähte auf der Übersättigung von Gold durch Germanium aus der Gasphase. Für diesen Zweck wird eine dünne Schicht Gold auf einem temperaturbeständigen Substrat abgeschieden. Gold Tröpfchen entstehen durch das Erhitzen in Heliumatmosphäre, deren Durchmesser von der Dicke der ursprünglichen Goldschicht abhängt wie in Abbildung 2.9.1. (links) zu sehen ist. Bei Erreichen der gewünschten Wachstumstemperatur (Substrat wird über die eutektische Temperatur des Au-Ge-Materialsystems, 539 K erhitzt) wird das Germanium durch Trägergase wie German (GeH<sub>4</sub>), Digerman (Ge<sub>2</sub>H<sub>6</sub>) oder Germaniumtetrachlorid (GeCl<sub>4</sub>) in die Prozesskammer eingelassen, in unserem Fall war GeH<sub>4</sub> eingeführt. [75] Diese dissoziieren nun mit dem Goldtropfen und Germanium wird gelöst (Abbildung 2.9.1.-mitte). Bei Übersättigung beginnt das Germanium an der Grenzfläche zum Substrat zu lagern und die in Germanium unlösliche Goldmenge wird kontinuierlich nach oben gedrückt (Abbildung 2.9.1.-rechts). Durch die Kontrolle von Parametern wie Temperatur, Druck, Gasflussrate und Art der Vorläufermoleküle kann die Länge, Dicke, Ausrichtung und Zusammensetzung des Nanodrahtes gezielt gesteuert werden.[76]

Abbildung 2.9.1. Darstellung des Nanodrahtwachstums mittels VLS- Verfahren: (links): Das Gold bildet beim Erhitzen feine Tröpfchen, (mitte): GeH4 dissoziiert am Goldtropfen, (rechts): Nukleation und Kristallisation der übersättigten Germanium-Gold-Legierung. Abbildung aus Ref. [77]

# 3. Experimentelle Durchführung

In diesem experimentellen Abschnitt werden die Methoden zur Herstellung und Charakterisierung von Passivierungsschichten, sowie MOS-Cap Bauteilen beschrieben. Diese Bauteile werden aus verschiedenen Materialien Hergestellt, wobei spezifische Muster und Herstellungsreihenfolge beachtet werden müssen, die von den Umgebungsbedingungen und Parameter abhängen. Zunächst wird auf die Herstellung von MOSFET (Metall-Oxid-Halbleiter-Feldeffekttransistoren) eingegangen und für diese Untersuchung wurden zahlreiche MOS-Bauteile mit High-k-Dielektrika hergestellt. In der weiteren Analyse konzentrieren wir uns jedoch auf den Vergleich zwischen zwei spezifischen Proben: einer AlN-Ge-NW (Aluminiumnitrid-Germanium-Nanodrähte) und einer Al<sub>2</sub>O<sub>3</sub>-Ge-NW (Aluminiumoxid-Germanium-Nanodrähte) Probe. Die Aluminiumoxid Probe wurde von Kollegen Dr. Daniele Nazzari hergestellt um einen direkten Vergleich der zwei Proben zu ermöglichen. Die Herstellung und Charakterisierung dieser Proben erfolgt durch präzise Verfahren, die es ermöglichen, die Leistungsfähigkeit der verschiedenen Materialien und Schichtstrukturen zu beobachten und zu bewerten. Dabei werde Methoden wie Abscheidung von Dünnschichten, litografische Verfahren und verschiedene Analyseverfahren zur Bewertung der elektrischen Eigenschaften und der strukturellen Integrität der Schichten angewendet. Vorgehensweise erlaubt es uns, Aussagen über die Eignung der verschiedenen Materialien und Technologien für die Anwendung in MOSFET zu treffen.

# Bauteil-Herstellung

## 3.1. UHV Annealing und UHV Sputtern

Die Herstellung sauberer Oberflächen ist eine der wichtigsten Herausforderungen in der Oberflächenforschung erfolgt unter **UHV** (Ultra High Vacum) UHV Annealing und UHV-Sputtern sind wesentliche Techniken in der Halbleiterfertigung und Materialforschung, um hochreine und präzise Schichtstrukturen zu erzeugen. Das UHV Annealing ist ein thermisches Verfahren, bei dem die Materialien in einer Umgebung mit extrem niedrigen Druck (meistens unter 10<sup>-9</sup> mbar) auf hohen Temperaturen erhitzt werden. [78] Dieses Verfahren dient dazu, Defekte in Kristallstrukturen zu beseitigen, Oberflächen zu reinigen und die chemische Stabilität der Materialien zu verbessern. Die Proben werden in eine UHV-Kammer eingeführt und diese Kammer wird auf ein Ultra-Hochvakuum evakuiert. Die Proben werden auf die gewünschte Temperatur erhitzt (in unserem Fall auf 650°C) und für eine bestimmte Zeit (20 min) gehalten. Die Proben werden anshließend langsam auf Raumtemperatur abgekühlt. UHV Sputtern wird in diesem Schritt auch zur Reinigung von Oberflächen verwendet, indem eine dünne Schicht der Oberfläche durch Sputtern entfernt wird. Diese Methode ist besonders effektiv, um Oberflächenverunreinigungen zu entfernen und eine saubere, atomar glatte von Oxiden befreite Oberfläche zu erzeugen. In unserem Prozess wird das Substrat auf 100°C erhitzt und das Sputtern erfolgt für 1 Minute.

Durch die Kombination dieser Schritte (sehe Tabele 3.1.1.) könnten wir hochreine und gut definierte Schichtstrukturen erzielen, die für unsere weitere Untersuchung und Anwendungen von nentscheindender Bedeutung sind.

| Prozess              | Temperatur | Zeit       |

|----------------------|------------|------------|

| Schritt 1.           | 650 °C     | 20 Minuten |

| <b>UHV Annealing</b> |            |            |

| Schritt 2.           | ~ 100 °C   | 1 Minute   |

| <b>UHV Sputtern</b>  |            |            |

| Schritt 3.           | 600 °C     | 20 Minuten |

| <b>UHV Annealing</b> |            |            |

Tabele 3.1.1. Schritte und Parameter für Ultahochvakuum Prozess

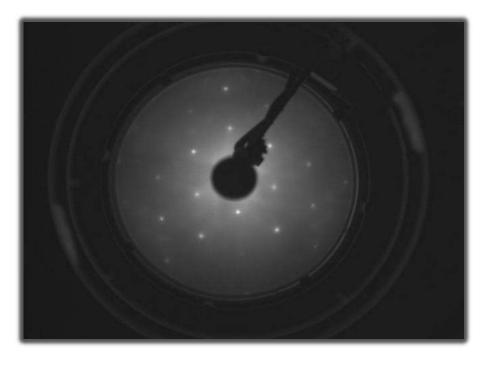

Abbildung 3.1.1. zeigt eine LEED-Aufnahme (Low-Energy Electron Diffraction) einer ndotierten Germanium-(111)-Oberfläche, die nach UHV-Sputtern und UHV-Glühen aufgenommen wurde. Die sichtbaren Beugungspunkte (helle Flecken) entstehen durch die Interaktion niederenergetischer Elektronen mit der Kristalloberfläche und repräsentieren die regelmäßige Anordnung von Atomen in der einkristallinen Struktur. Das symmetrische Beugungsmuster bestätigt die Rekonstruktion der Oberfläche und weist auf eine gut geordnete Kristallstruktur hin.

Abbildung 3.1.1. LEED Aufnahme von n-Ge (111) Struktur, 170 eV, nach UHV Annealing und UHV Sputtern

## 3.2. Atomlagenabscheidung (ALD)

Die Herstellung von Strukturen und Schichten für den Einsatz in Halbleitertechnologie erfordert die Fähigkeit, die Schichtdichte, Zusammensetzung und Struktur sorgfältig zu steuern. Das spielt eine große Rolle für die Leistungsfähigkeit der Schichten, hinsichtlich elektrischer, mechanischer und chemischer Eigenschaften. Insbesondere bei Halbleitern ist es sehr wichtig, dass es eine Tendenz hat, die Bauteile immer kleiner zu fertigen. Aus diesem Grund ist es von Vorteil bei einer Methode, die Fähigkeit, die Dicke der einzelnen Komponenten dünner werden lassen, und zu berücksichtigen, dass die Beziehung zwischen dem Film und Oberfläche, auf der er wächst, immer Qualität reicher und präziser sein sollte. Die Atomlagenabscheidung ist ein Filmwachstumsprozess, der auf wiederholten Halbreaktionen berührt, an denen an der Oberfläche adsorbierte chemische Spezies beteiligt sind, um dünne Schichten mit Präzision zu bilden. [79] Der ALD-Prozess bezieht sich auf eine binäre chemische Reaktionssequenz, bei der jeder chemischer Vorläufer (Präkursor) selbstlimitierend ist und zur Sättigung der Monolage führt. Diese Methode ist eine hervorragende Stufenabdeckung und ist optimal für Fertigung/Abscheidung sehr dünner und konformal abgeschiedene Schichten in dem konkreten Fall High-k Schichten. [80] Damit die Metallschicht und Halbleiterschicht des Transistors durch das Oxid elektrisch voneinander getrennt sind, muss die Oxidschicht sehr präzise gefertigt werden, das wird mittels ALD (Atomic Layer Deposition) erreicht. In der Tabele 3.2.1. sind die Processparameter die wir für Abscheidung unterschiedlicher Dielektrika benutzt haben aufgelistet. Beschäftigt haben wir uns jedoch am meisten mit HfO<sub>2</sub>, ZrO<sub>2</sub>, HfN und AlN.

|                        | HfO <sub>2</sub>                   | HfN                                 | ZrO <sub>2</sub>                  | ZrN                                 | AlN                            |

|------------------------|------------------------------------|-------------------------------------|-----------------------------------|-------------------------------------|--------------------------------|

| Anzahl der Umdrehungen | 95                                 | 165                                 | 85                                | 165                                 | 100                            |

| Reinigungszeit         | 15 s<br>Hf/12s<br>H <sub>2</sub> O | 15s<br>Hf/<br>10s<br>N <sub>2</sub> | 15s<br>Zr/12s<br>H <sub>2</sub> O | 15s<br>Zr/<br>10s<br>N <sub>2</sub> | 5s<br>Al/10s<br>N <sub>2</sub> |

| Temperatur             | 250°C                              | 250°C                               | 250°C                             | 250°C                               | 200°C                          |

| Materialdicke          | 11,03<br>nm                        | 18,76<br>nm                         | 13,76<br>nm                       | 18,54<br>nm                         | 9,86<br>nm                     |

Tabele 3.2.1. Processparameter für Abscheidung der Oxide/Nitride mittels ALD

## 3.3. Rapid thermal Annealing (RTA)

Die thermische Verarbeitung basiert auf der Wärmeübertragung, Glühen einschließlich Diffusion (Fiksches Gesetz) und Oxidation. Die thermische Verarbeitung von Materialien in einer inerten Umgebung wie Stickstoff oder Argon, manchmal unter Zusatz von Wasserstoff, wird als Glühprozess bezeichnet. Zwei Arten von Materialien sind bei diesem Prozess wichtig, Inertgase z. B. Stickstoff (N), die nicht mit anderen Materialien reagieren und Reaktionsgase, die sich in den gewünschten Film zersetzen. Glühen ist ein wichtiger Schritt für die Verbesserung der Oxideigenschaften. Es dient dazu, die Bindungen abzusättigen und dadurch dichter zu machen.[81] Ein typischer Batch-Ofenprozess dauert mehrere Stunden und ermöglicht dadurch eine höhere thermische Stabilität und Prozessstabilität und hat einen Vorteil mehrere Proben gleichzeitig zu verarbeiten, der Nachteil ist die Gesamtprozesszeit. Die Verarbeitung einzelner Proben hat aufgrund einer schnelleren Durchlaufzeit bei der Geräteentwicklung zugenommen, da die individuelle Bearbeitung einer Probe per RTA (Rapid Thermal annealing) in wenigen Minuten erledigt ist. [82] Die Prozessparameter sind in Tabele 3.3.1. dargestellt.

### Durchgeführt in einem UniTem Model UTP1100.

| 450°C | 3 min | Stickstoff (N <sub>2</sub> )/N <sub>2</sub> H <sub>2</sub> |

|-------|-------|------------------------------------------------------------|

Tabele 3.3.1. Prozessparameter für Rapid thermal annealing

# 3.4. Laserlitographie und **Elektronenstrahlverdampfer (e-beam evaporation)**

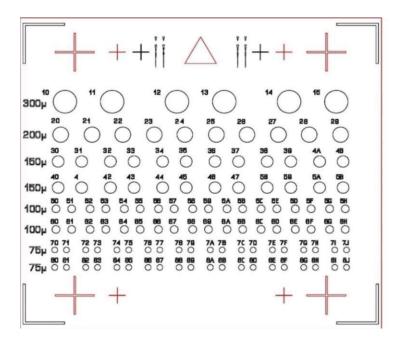

Die Laserlithographie und die Elektronenstrahlverdampfung (e-beam evaporation) sind zwei zentrale Techniken in der Mikro- und Nanofabrikation, die zur Herstellung von präzisen mikround nanoskaligen Strukturen auf unterschiedlichen Substraten verwendet werden. Beide Techniken sind essenziell für die Entwicklung von Halbleiterbauelementen, Sensoren, optischen Komponenten und anderen nanoskaligen Geräten. Die Laserlithographie ist eine Technik, die es ermöglicht, sehr feine Strukturen auf einem lichtempfindlichen Material (Resist) durch die direkte Bestrahlung und Rastera mit einem Laserstrahl zu erzeugen. Die Laserlithographie basiert auf dem Prinzip der Photolithographie, bei dem ein Laserstrahl verwendet wird, um ein Muster in einen auf einem Substrat aufgebrachten lichtempfindlichen Resist ohne Maske zu schreiben. Der Resist wird dabei durch den Laser belichtet und dadurch an den belichteten Stellen chemisch verändert. Dieser Prozess kann in zwei Haupttypen unterteilt werden: Direktes Schreiben mit einem fokussierten Laserstrahl (Direct Laser Writing, DLW) und Maskenprojektion, bei der ein Laserstrahl durch eine Maske geführt wird, um das gewünschte Muster auf das Substrat zu übertragen.[83], [84], [85] Um den Erfolg dieses Schrittes sicherzustellen, muss die Probe zunächst vorbereitet, gereinigt und mit Fotolack beschichtet werden. Die in der Lithografie eingesetzten Masken enthalten ein exakt definiertes Muster, das zur Strukturierung der jeweiligen Schicht auf dem Wafer verwendet wird. In Abbildung 3.4.1 ist das Muster der Maske dargestellt.

Abbildung. 3.4.1. Mustermaske für die Litografie

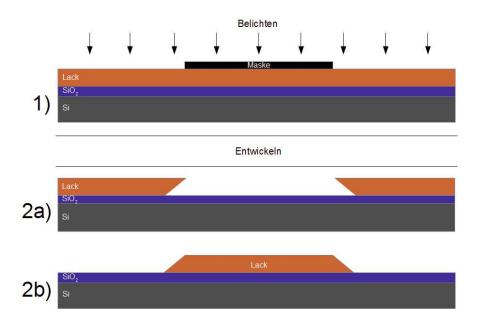

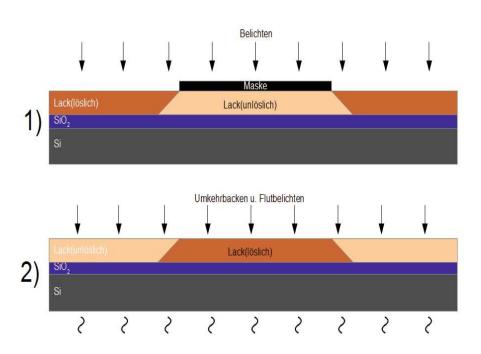

In diesem Projekt wurde der Belichtungsprozess mithilfe eines Laser-Lithographiesystems durchgeführt. Dabei wurde das Licht des Lasers durch ein Mikroskopobjektiv auf das mit positivem Fotolack beschichtete Substrat fokussiert. Positiver Fotolack bietet den Vorteil, dass er gegenüber äußeren Einflüssen wie Feuchtigkeit und Verunreinigungen weniger empfindlich ist, was seine Anwendung in der Laserlithographie erleichtert. Zudem ermöglicht der Einsatz von positivem Lack oft einen schnelleren Prozessablauf im Vergleich zu negativem Lack, was zu einer Verkürzung der Gesamtproduktionszeit führen kann. Nach der Belichtung durchläuft das Substrat einen Entwicklungsprozess, bei dem überschüssiger Fotolack entfernt wird und die belichteten Bereiche auf dem Substrat freigelegt werden. Dieser Entwicklungsschritt erfolgt häufig durch das Eintauchen des Substrats in ein geeignetes Lösungsmittel. In der Lithographie spielen Fotolacke eine zentrale Rolle bei der Musterbildung auf Substraten. Die Auswahl des richtigen Fotolacks ist entscheidend, da sie die Auflösung, Präzision und Effizienz des gesamten Herstellungsprozesses beeinflusst. Es gibt drei Hauptarten von Fotolacken: Positiv-, Negativ- und Reversal-Fotolacke, die jeweils spezifische Eigenschaften und Anwendungen aufweisen. [86] Positiv-Fotolacke zeichnen sich dadurch aus, dass die belichteten Bereiche während der Entwicklung löslich werden und entfernt werden. Das bedeutet, dass das ursprüngliche Muster der Maske direkt auf das Substrat übertragen wird. Im Gegensatz dazu härten bei Negativ-Fotolacken die belichteten Bereiche aus und bleiben auf dem Substrat haften, während die unbelichteten Bereiche beim Entwickeln entfernt werden. Negativlacke sind besonders nützlich, wenn dickere Schichten erforderlich sind oder wenn eine hohe chemische Beständigkeit nach dem Entwickeln notwendig ist. Reversal-Fotolacke kombinieren die Vorteile von Positiv- und Negativlacken und bieten eine erhöhte Flexibilität im Lithographieprozess. [87] Dieser Lacktyp wird zunächst wie ein Positivlack belichtet, aber durch einen anschließenden thermischen Schritt oder eine Nachbelichtung umgekehrt. Dadurch werden die ursprünglich unbelichteten Bereiche ausgehärtet, ähnlich wie bei einem Negativlack. Die Wahl des geeigneten Fotolacks – sei es ein Positiv-, Negativ- oder Reversal-Fotolack – hängt stark von den spezifischen Anforderungen des Lithographieprozesses ab.

Positivlacke bieten hohe Präzision und Effizienz, Negativlacke eignen sich für robuste Strukturen, und Reversal-Lacke bieten eine Kombination der Vorteile beider Typen. [88] Das Verständnis der Eigenschaften und Anwendungsbereiche dieser Fotolacke ist entscheidend für die erfolgreiche Umsetzung moderner Lithographieverfahren in der Mikro- und Nanotechnologie und die Unterschiede sind in Abbildungen 3.4.2. und 3.4.3. zu sehen.