Contents lists available at ScienceDirect

## Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# $Si/Ge_{1-x}Sn_x/Si$ transistors with highly transparent Al contacts

Lukas Wind alo, Stefan Preiß a, Daniele Nazzari alo, Johannes Aberl blo, Enrique Prado Navarrete blo, Moritz Brehm blo, Lilian Vogl alo, Andrew M. Minor blo, Masiar Sistani alo, Walter M. Weber alo,\*

- <sup>a</sup> Institute of Solid State Electronics, TU Wien, 1040 Vienna, Austria

- <sup>b</sup> Institute of Semiconductor and Solid State Physics, Johannes Kepler University, 4040 Linz, Austria

- <sup>c</sup> Department of Materials Science and Engineering, University of California, CA 94720, Berkeley, USA

## ARTICLE INFO

The review of this paper was arranged by Francisco F. Gamiz

Keywords: GeSn Transistor Transparent contacts Transport investigations Multi-gate architecture

#### ABSTRACT

We study the monolithic quasi-ohmic contact formation with single-elementary Al to  $Ge_{1-x}Sn_x$  channel devices with various Sn concentrations between 0.5% and 4%. Thereby we investigate the influence of increasing Sn content on the electrical transport properties in field-effect transistors for a wide temperature range between 77 K and 400 K. At low temperatures, the devices exhibit improved performance metrics, promising for cryo-CMOS applications. Compared to pure Ge control devices, the introduction of Sn into the channel leads to a 20 times increased on-current. In a multi-gate architecture, we analyze the decoupled influence of the carrier injection through the metal–semiconductor junction and the channel conduction.

## 1. Introduction

The introduction of GeSn as a channel material, with its modulated band structure and high carrier mobilities for both electrons and especially holes, is promising for optoelectronics, Beyond CMOS technologies with high on-state conductance as well as low power cryogenic applications [1–5]. Mobilities of up to 698 cm<sup>2</sup>/Vs for electrons [6] and 509 cm<sup>2</sup>/Vs for holes [7] have been recently reported. In fieldeffect transistors (FETs) the integration of Sn has already demonstrated performance enhancements, such as increased transconductance and operation frequencies, compared to equivalent Ge channel devices [1, 8]. Importantly, as a group-IV semiconductor material, GeSn retains high compatibility with current Si CMOS technology. Furthermore, with Sn concentrations higher than ~8%, GeSn exhibits direct band gap transitions [9,10], making it highly promising for direct integration of optoelectronic applications into CMOS platforms [11]. For any integration of GeSn devices, high-quality, nanoscaled ohmic contacts are of utmost importance. Especially for cryo-CMOS applications, doping-free metal contacts to GeSn devices are of high interest, as their resistivity is even reducing with lower temperatures, in contrast to doped semiconductor contacts that suffer from carrier freeze-out, leading to an exponential increase in material resistivity [12]. On the other hand, the reproducibility of stochiometry and crystal quality in metallic compound materials, such as NiGeSn [3], PtGeSn [2] or

Yb stanogermanide [13], can be challenging due to complex phase transitions, although providing good contact properties.

Recently, we have demonstrated monolithic and single elementary Al contact formation to top-down fabricated nanosheets composed of vertical  $\mathrm{Si}\text{-}\mathrm{Si}_{1-x}\mathrm{Ge}_x$ -Si heterostructures [14], providing a versatile platform for various emerging device concepts [15]. In this work, we now demonstrate the contact formation to heterostructures encompassing  $\mathrm{Ge}_{1-x}\mathrm{Sn}_x$  layers with Sn concentrations ranging from 0.5% to 4%. Thereby, we analyze the composition-dependent electrical transport properties in FET architectures.

## 2. Results and discussion

For GeSn device fabrication, we adapted recent growth strategies using ultra-low growth temperatures for the epitaxial deposition of  $Si/Ge_{1-x}Sn_x/Si$  heterostructures on SOI substrates [16], schematically shown in Fig. 1(a). The growth was carried out in a Riber SIVA 45 solid source molecular beam epitaxy (MBE) system on silicon on insulator (SOI) substrates, with a Si(001) device layer thickness of 20 nm on a 100 nm thick buried oxide (BOX). The samples underwent a standard Si substrate cleaning process [17], finalized by a dip in diluted hydrofluoric acid (HF 1 %) to remove the native oxide. All substrates were degassed at 923 K for 15 min, followed by a one-hour conditioning step at 723 K. In all cases, an 8 nm thick Si buffer was

https://doi.org/10.1016/j.sse.2025.109069

<sup>\*</sup> Corresponding author.

E-mail address: walter.weber@tuwien.ac.at (W.M. Weber).

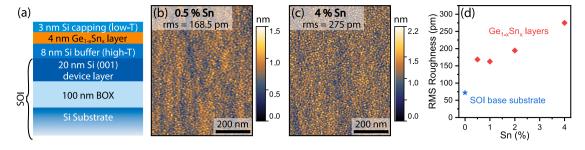

Fig. 1. (a) Schematic of the epitaxially grown  $Si/Ge_{1-x}Sn_x/Si$  heterostructure on SOI, with AFM surface topography of the substrate containing 0.5% (b) and 4% Sn (c). The rms surface roughness of four substrates with different Sn contents (0.5%, 1%, 2%, 4%) and the base SOI substrate are compared in (d).

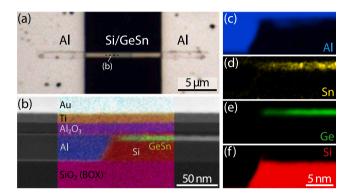

**Fig. 2.** (a) Microscope image of the formed Al-Si/Ge $_{0.99}$ Sn $_{0.01}$  heterostructure after the thermally induced exchange reaction. (b) HAADF-STEM image with EDX overlay of the axial cut at the Al-Si/Ge $_{1-x}$ Sn $_x$  interface, indicated in (a). (c)–(f) Single elementary EDX maps.

deposited at a growth temperature of 923 K and a rate of 0.7 Å/s. Hereafter, a 4 nm thick  $\mathrm{Ge}_{1-x}\mathrm{Sn}_x$  layer was deposited, followed by a 3 nm thick Si capping layer, both grown at 448 K. In total, four samples with different Sn contents x of 0.5 %, 1 %, 2 %, and 4 % were grown. In all cases, the low growth temperatures of the  $\mathrm{Ge}_{1-x}\mathrm{Sn}_x$  layers suppress elastic and plastic relaxation [17]. This results in a low root-mean-square (rms) surface roughness < 0.28 nm for all substrates, as shown in the atomic force microscopy images in Figs. 1(b,c) taken immediately after sample growth. With increasing the Sn content in the strained  $\mathrm{Ge}_{1-x}\mathrm{Sn}_x$  layer on Si, the strain energy in the film increases, promoting a strain relaxation-driven increase in the film's surface roughness (see Fig. 1(d)). However, the rms values are close to that of the pristine SOI substrate, indicating that the low growth temperature of the Si capping layers ensures efficient suppression of Ge [18] and Sn surface segregation.

From the vertical Si-Ge<sub>1-x</sub>Sn<sub>x</sub>-Si heterostructure sample,  $\sim$ 700 nm wide mesa structures are then patterned using laser lithography and SF<sub>6</sub>-O<sub>2</sub> based dry etching techniques. An approximately 10.8 nm thick Al<sub>2</sub>O<sub>3</sub> gate dielectric is grown by atomic layer deposition (ALD) and subsequently removed by BHF (7:1) etching at the drain (D) and source (S) contact areas of the nanosheets prior to sputtering 120 nm of Al. Using rapid thermal annealing (RTA) at 773 K in forming gas atmosphere a solid-state exchange reaction between Al and the Si/Ge<sub>1-x</sub>Sn<sub>x</sub> layers is induced, where Al supplied by the contact pads is exchanging the semiconducting channel material [14]. A microscope image of the monolithically formed metal-semiconductor-metal heterostructure is shown in Fig. 2(a). The high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) image of the axial cut of this heterostructure in Fig. 2(b) reveals the formed abrupt Al- $\operatorname{Ge}_{1-x}\operatorname{Sn}_x$  junction. Interestingly, a nanometer-thin Si agglomeration between the Al and the  $Ge_{1-x}Sn_x$  layer is evident, which is consistent with observations in exchange processes between Al and SiGe

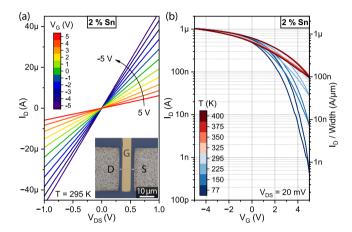

Fig. 3. (a) Linear gate-dependent I/V characteristic of a top-gated Al-Ge $_{0.98}$ Sn $_{0.02}$  heterostructure shown in the inset. (b) Temperature-dependent transfer characteristic at  $V_{DS}=20\,\mathrm{mV}$ .

in similar structures [14]. The single elementary energy-dispersive X-ray spectroscopy (EDX) images in Fig. 2(c-d) show that during the exchange process at 773 K the vertical  $Si/Ge_{1-x}Sn_x/Si$  heterostructure stays intact, without any evident intermixing of the epitaxially grown layers. Furthermore, the intruded Al leads seem to be crystalline and single elementary (within the Sn detection limit), with only small Sn residuals detected close to the metal–semiconductor junction and surface. As no intermetallic phases with complex phase transitions occur during the thermally induced exchange process, several consecutive annealing steps can be applied to precisely control the remaining  $Ge_{1-x}Sn_x$  channel length [14].

Integrated into a FET by adding a gate atop the whole Al-Ge<sub>1-x</sub>Sn<sub>x</sub>-Al heterostructure via laser lithography, Ti/Au (10 nm/100 nm) evaporation and lift-off, the electrical transport is investigated in Fig. 3 for a device with a Sn concentration of 2%. The gate-dependent I/V characteristic thereby reveals linear behavior, suggesting highly transparent quasi-ohmic contacts attributed to the high Sn content in the Si interlayer. By decreasing the gate voltage  $(V_G)$  from -5 V to 5 V, the current can be increased by a factor of ~20. The transfer characteristic in Fig. 3(b) at a bias voltage  $V_{DS}$  of 20 mV further shows very p-type dominant conduction, which can be attributed to strong Fermi-level pinning near the valance band edge. Furthermore, as the 4nm thin Ge<sub>1-x</sub>Sn<sub>x</sub> layer is sandwiched vertically between two Si layers, we speculate that this results in an abrupt discontinuity of the energy band structure at the interfaces, potentially leading to a hole gas formation [14,19]. Temperature-dependent measurements in Fig. 3(b) between 77 K and 400 K indicate that at cryogenic temperatures, the  $Ge_{1-x}Sn_x$  channel can be sufficiently depleted due to fewer thermally excited charge carriers at  $V_G > 0$  V. This results in a drain current modulation over six orders of magnitude while the on-currents remain mostly temperature-independent, making the system especially interesting for

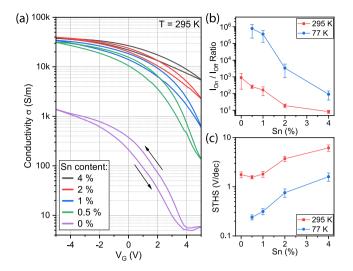

**Fig. 4.** (a) Comparison of the gate-dependent conductivity of samples with different Sn content, including a reference sample with a pure Ge layer, measured at  $V_{DS}=20\,\mathrm{mV}$ . The arrows indicate the sweeping direction. (b)  $I_{on}/I_{off}$  ratio and (c) subthreshold slope vs. Sn content, at 295 K and 77 K. The values are averaged over three comparable devices.

cryo-CMOS applications. At elevated temperatures above  $325\,\mathrm{K}$ , there are almost no changes in the transfer characteristic.

The comparison of nanosheets with four different GeSn stoichiometries in an FET architecture is shown in Fig. 4, compared to a control sample with a pure Ge layer. The gate-dependent conductivity, normalized to the geometry of the remaining  $Ge_{1-x}Sn_x$  channel, shows that an increased Sn content enhances the conductivity, over 20x higher compared to a pure Ge layer in agreement with an accumulation channel. However, the off-state is given by depletion implying a  $V_G$ -dependent overall gate capacitance accompanied by degraded  $I_{\it on}/I_{\it off}$  ratios and subthreshold slopes (STHS), as shown in Fig. 4(b,c). Scaling the width of the semiconducting channel down to the low nm range and improved gating architecture, such as FinFETs [20] or gate-all-around (GAA) FETs [2,5], should therefore significantly improve electrostatic gating, as a sufficient carrier depletion in the off-state cannot be achieved for such wide channels. At cryogenic temperatures, both the  $I_{\it on}/I_{\it off}$  ratio and the STHS for all Sn concentrations can be greatly improved, with a modulation up to 6 orders of magnitude and STHS of 240 mV/dec for 0.5 % Sn channel device at 77 K.

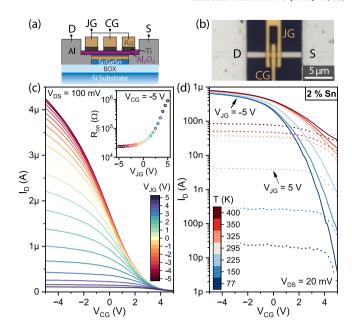

To decouple the influence of the carrier injection at the junction and the channel conduction, a multi-gate structure, featuring a dedicated junction gate (JG) atop the  $\mathrm{Al}\text{-}\mathrm{Ge}_{1-x}\mathrm{Sn}_x$  interfaces and a channel gate (CG) in the middle of the  $\mathrm{Ge}_{1-x}\mathrm{Sn}_x$  channel, is investigated. A schematic cross section of this multi-gate transistor is depicted in Fig. 5(a), with an optical microscope image in (b). The JG-dependent transfer characteristic in Fig. 5(c) shows that the on-state current can be lowered with increased  $V_{IG}$ , as this leads to an increased injection barrier for holes. This results in a modulation of the on-state resistance by a factor of  $\sim$ 40. In the transfer characteristic in Fig. 5(c), with  $V_{CG}$ swept from -5 V and 5 V, the on-state current can be modulated via the JG, as the injection barrier for holes is increased with increasing  $V_{IG}$ . Thereby, the on-state resistance can be tuned by a factor of ~40. The off-state current is barely influenced by the JG, as this is defined by the depletion of the charge carriers within the channel. With the JG set to 5 V, the current can then only be modulated by a factor of 4.8. Temperature-dependent measurements in 5(d) show that reduced temperatures lead to improved channel depletion due to less thermally active carriers, resulting in increased  $I_{\it on}/I_{\it off}$  ratio over more than 5 orders of magnitude at 77 K for  $V_{JG} = -5\,\mathrm{V}$ . Furthermore, this leads to an increased influence of the JG, with an on-state resistance change of up to  $2.5 \times 10^4$  at  $V_{CG} = -5$  V. It can, therefore, be assumed that

**Fig. 5.** (a) Schematic and (b) microscope image of a multi-gate structure with 2% Sn. Junction gate  $(V_{JG})$  dependent transfer characteristic, with the inset showing the change in on-state resistance  $(R_{on})$ . (b) Temperature dependent transfer characteristic for  $V_{JG} = -5 \, \text{V}$  (solid) and  $V_{JG} = 5 \, \text{V}$  (dotted line).

the main mechanism for controlling the device is modulation of the injection barrier, mainly by blocking the holes with positive  $V_{JG}$  by introducing an electrostatically tunable energy barrier at the junction.

## 3. Conclusion

We have systematically investigated the contact formation to nanosheets patterned from epitaxially grown vertical Si-Ge $_{1-x}$ Sn $_x$ -Si heterostructures with Sn contents between 0.5% and 4%. Using a thermally induced exchange reaction between Al and Si/GeSn at 773 K, single-elementary Al contacts with abrupt junctions to the Ge $_{1-x}$ Sn $_x$  channel are formed, showing highly transparent quasi-ohmic behavior for holes. In FETs, the introduced Sn leads to a more than 20-fold increase in on-state conductivity compared to a Ge control sample. Temperature measurements down to 77 K reveal improved electrostatic tunability for all samples, up to 6 orders of magnitude for 0.5% Sn, while on-state currents remain temperature invariant. In multi-gate structure, decoupling carrier injection and channel modulation, the on-state resistance can be modulated by a factor of ~40 via a junction gate by changing the injection barrier of holes into the channel. This finding supports the highly transparent contacts for holes.

## CRediT authorship contribution statement

Lukas Wind: Writing – original draft, Methodology, Investigation, Data curation. Stefan Preiß: Investigation, Data curation. Daniele Nazzari: Methodology, Investigation. Johannes Aberl: Resources, Methodology, Investigation. Enrique Prado Navarrete: Resources, Methodology, Investigation. Moritz Brehm: Writing – review & editing, Resources, Methodology, Funding acquisition. Lilian Vogl: Validation, Methodology, Investigation. Andrew M. Minor: Resources, Investigation. Masiar Sistani: Writing – review & editing, Supervision, Project administration, Investigation, Funding acquisition, Data curation, Conceptualization. Walter M. Weber: Writing – review & editing, Supervision, Resources, Project administration, Funding acquisition, Conceptualization.

#### Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Acknowledgments

This research was funded in part by the Austrian Science Fund (FWF): project No.: I5383-N, Y1238-N36. We further thank the Center for Micro- and Nanostructures (ZMNS) for providing the cleanroom facilities. This work was also supported by uAtoms, an Energy Frontier Research Center funded by the U.S. Department of Energy, Office of Science, USA, Basic Energy Sciences, USA. Work at the Molecular Foundry was supported by the Office of Science, Office of Basic Energy Sciences, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. For open access purposes, the author has applied a CC BY public copyright license to any author accepted manuscript version arising from this submission.

## Data availability

Data will be made available on request.

#### References

- [1] Liu M, Junk Y, Han Y, Yang D, Bae JH, Frauenrath M, et al. Vertical GeSn nanowire MOSFETs for CMOS beyond silicon. Commun Eng 2023;2(1):1–9. http://dx.doi.org/10.1038/s44172-023-00059-2.

- [2] Huang YS, Lu FL, Tsou YJ, Ye HY, Lin SY, Huang WH, et al. Vertically stacked strained 3-GeSn-Nanosheet pGAAFETs on Si Using GeSn/Ge CVD epitaxial growth and the optimum selective channel release process. IEEE Electron Device Lett 2018;39(9):1274–7. http://dx.doi.org/10.1109/LED.2018.2852775.

- [3] Sun J, Han Y, Junk Y, Concepción O, Bae JH, Grützmacher D, et al. Low contact resistance of NiGeSn on n-GeSn. Solid-State Electron 2024;211:108814. http://dx.doi.org/10.1016/j.sse.2023.108814.

- [4] Wang N, Xue C, Wan F, Zhao Y, Xu G, Liu Z, et al. High-performance GeSn photodetector covering all telecommunication bands. IEEE Photonics J 2021;13(2). http://dx.doi.org/10.1109/JPHOT.2021.3065223.

- [5] Junk Y, Frauenrath M, Han Y, Diaz OC, Bae JH, Hartmann JM, et al. GeSn Vertical Gate-all-around Nanowire n-type MOSFETs. Eur Solid-State Device Res Conf 2022;364–7. http://dx.doi.org/10.1109/ESSDERC55479.2022.9947133.

- [6] Chuang Y, Liu CY, Liu GL, Li JY. Electron mobility enhancement in GeSn nchannel MOSFETs by tensile strain. IEEE Electron Device Lett 2021;42(1):10–3. http://dx.doi.org/10.1109/LED.2020.3041051.

- [7] Huang YS, Tsou YJ, Huang CH, Huang CH, Lan HS, Liu CW, et al. High-mobility CVD-grown Ge/Strained Ge0.9Sn0.1/Ge quantum-well pMOSFETs on Si by optimizing Ge cap thickness. IEEE Trans Electron Devices 2017;64(6):2498–504. http://dx.doi.org/10.1109/TED.2017.2695664.

- [8] Mondal C, Biswas A. Performance analysis of nanoscale GeSn MOSFETs for mixed-mode circuit applications. Mater Sci Semicond Process 2017;66:109–16. http://dx.doi.org/10.1016/j.mssp.2017.04.014.

- [9] Lu Low K, Yang Y, Han G, Fan W, Yeo YC. Electronic band structure and effective mass parameters of Ge 1-xSnx alloys. J Appl Phys 2012;112(10). http://dx.doi.org/10.1063/1.4767381.

- [10] Gupta S, Magyari-Köpe B, Nishi Y, Saraswat KC. Achieving direct band gap in germanium through integration of Sn alloying and external strain. J Appl Phys 2013;113(7). http://dx.doi.org/10.1063/1.4792649.

- [11] Wirths S, Geiger R, Von Den Driesch N, Mussler G, Stoica T, Mantl S, et al. Lasing in direct-bandgap GeSn alloy grown on Si. Nat Photonics 2015;9(2):88–92. http://dx.doi.org/10.1038/nphoton.2014.321.

- [12] Ibach H, Lüth H. Solid-state physics. fourth ed. Berlin, Heidelberg: Springer Berlin Heidelberg; 2009, p. 1–533. http://dx.doi.org/10.1007/978-3-540-93804-0.

- [13] Teng SC, Su CC, Chen KY, Chou CP, Wu YH. Fermi level depinning on n-epitaxial GeSn by Yb stanogermanide formation with low-contact resistivity. IEEE Electron Device Lett 2016;37(9):1207–10. http://dx.doi.org/10.1109/LED.2016.2591620.

- [14] Wind L, Sistani M, Böckle R, Smoliner J, Vukušić L, Aberl J, et al. Composition dependent electrical transport in SiGe nanosheets with monolithic single-elementary Al contacts. Small 2022;18(44):2204178. http://dx.doi.org/10.1002/smll.202204178.

- [15] Fuchsberger A, Wind L, Nazzari D, Kühberger L, Popp D, Aberl J, et al. A Runtime Reconfigurable Ge Field-Effect Transistor With Symmetric On-States. IEEE J Electron Devices Soc 2024;12:83–7. http://dx.doi.org/10.1109/JEDS. 2024.3350209.

- [16] Salomon A, Aberl J, Vukušić L, Hauser M, Fromherz T, Brehm M. Relaxation delay of Ge-rich epitaxial SiGe films on Si(001). Phys Status Solidi (A) Appl Mater Sci 2022;219(17):2200154. http://dx.doi.org/10.1002/pssa.202200154.

- [17] Aberl J, Vukušić L, Fournel F, Hartmann JM, Brehm M. Epitaxial Growth of Planar Hutwires on Silicon-on-Insulator Substrates. Phys Status Solidi (A) 2022;219(17):2200145. http://dx.doi.org/10.1002/PSSA.202200145.

- [18] Brehm M, Grydlik M, Lichtenberger H, Fromherz T, Hrauda N, Jantsch W, et al. Quantitative determination of Ge profiles across SiGe wetting layers on Si (001). Appl Phys Lett 2008;93(12):121901. http://dx.doi.org/10.1063/1. 2988261/131737.

- [19] Fukata N, Yu M, Jevasuwan W, Takei T, Bando Y, Wu W, et al. Clear experimental demonstration of hole gas accumulation in Ge/Si core-shell nanowires. ACS Nano 2015;9(12):12182-8. http://dx.doi.org/10.1021/acsnano.5b05394.

- [20] Lei D, Lee KH, Bao S, Wang W, Masudy-Panah S, Yadav S, et al. The first GeSn FinFET on a novel GeSnOI substrate achieving lowest S of 79 mV/decade and record high Gm, int of 807 μs/μm for GeSn P-FETs. In: Symposium on VLSI technology. Kyoto, Japan: Institute of Electrical and Electronics Engineers Inc.; 2017, p. T198–9. http://dx.doi.org/10.23919/VLSIT.2017.7998170.