# Verifikation von nebenläufigen Programmen in schwachen Speicher-Modellen

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

### Software Engineering und Internet Computing

eingereicht von

### Hannes Dallinger

Matrikelnummer 11775789

| an | der | Fakı  | ıltät | fiïr | Inforn | natik |

|----|-----|-------|-------|------|--------|-------|

| ап | ucı | I and | шаі   | IUI  | ппоп   | ICHIN |

der Technischen Universität Wien

Betreuung: Ao. Univ. Prof. Dr. Johann Blieberger

Mitwirkung: Dr. techn. Dipl-Ing. (FH) MSc MBA Patrick Denzler

| Wien, 27. Jänner 2025 |                  |                   |

|-----------------------|------------------|-------------------|

|                       | Hannes Dallinger | Johann Blieberger |

# Verification of concurrent programs in weak memory models

### **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

### Software Engineering and Internet Computing

by

## Hannes Dallinger

Registration Number 11775789

| to | the | Faculty of | Informatics |

|----|-----|------------|-------------|

| at | the | TU Wien    |             |

Ao.Univ.Prof.Dr. Johann Blieberger

Assistance: Dr. techn. Dipl-Ing. (FH) MSc MBA Patrick Denzler

| Vienna, January 27, 2025 |                  |                   |

|--------------------------|------------------|-------------------|

|                          | Hannes Dallinger | Johann Blieberger |

## Erklärung zur Verfassung der Arbeit

### Hannes Dallinger

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Ich erkläre weiters, dass ich mich generativer KI-Tools lediglich als Hilfsmittel bedient habe und in der vorliegenden Arbeit mein gestalterischer Einfluss überwiegt. Im Anhang "Übersicht verwendeter Hilfsmittel" habe ich alle generativen KI-Tools gelistet, die verwendet wurden, und angegeben, wo und wie sie verwendet wurden. Für Textpassagen, die ohne substantielle Änderungen übernommen wurden, habe ich jeweils die von mir formulierten Eingaben (Prompts) und die verwendete IT-Anwendung mit ihrem Produktnamen und Versionsnummer/Datum angegeben.

| Wien, 27. Jänner 2025 |                  |

|-----------------------|------------------|

|                       | Hannes Dallinger |

## Danksagung

Ich möchte meine aufrichtige Dankbarkeit gegenüber meinen Betreuern, Ao. Univ. Prof. Dr. Johann Blieberger und Dr. techn. Dipl.-Ing. (FH) MSc MBA Patrick Denzler, für ihre Unterstützung und ihr Feedback während dieser Thesis zum Ausdruck bringen.

Weiters möchte ich auch meiner Familie für ihre ständige Ermutigung und ihr Verständnis danken. Ihre Unterstützung war von unschätzbarem Wert und hat mir während meines Studiums sehr geholfen.

# Acknowledgements

I would like to express my sincere gratitude to my supervisors, Ao.Univ.Prof.Dr. Johann Blieberger and Dr. techn. Dipl-Ing. (FH) MSc MBA Patrick Denzler, for their support, guidance, and feedback throughout this thesis.

I also want to thank my family for their constant encouragement and understanding. Their support has been invaluable and helped me during my studies.

## Kurzfassung

Moderne Processoren nutzen schwache Speichermodelle, um die Ausführung von Code zu optimieren. Im Vergleich zu sequentiell konsistenten Speichermodellen erlauben schwache Speichermodelle die Umordnung von Codeanweisungen. Während dies das Verhalten eines Single-Thread-Programmes nicht verändert, kann es in Multicore-Systemen Fehler verursachen indem Ausführungsreihenfolgen zwischen Threads ermöglicht werden, die ansonst nicht möglich wären. Diese Fehler sind für Entwickler oft schwer zu erkennen und zu verstehen.

Diese Thesis schlägt vor, mithilfe von Kronecker Algebra mögliche Ausführungsreihenfolgen von Multithread-Programmen innerhalb schwacher Speichermodelle zu modellieren. Dies kann dann verwendet werden, um Race Conditions im System zu erkennen. Der Fokus liegt dabei speziell auf schwachen Speichermodellen die Release-Acquire Semantiken nutzen.

Im Rahmen der Arbeit wird ein Prototyp entwickelt, der das System zur Erkennung von Race Conditions in Multithread-Programmen einzusetzen, die in LLVM-Bytecode kompiliert wurden, um zu zeigen, dass das System in der Lage ist, in Programmen Probleme zu identifizieren, die unter Verwendung von Release-Acquire Speichermodellen auftreten, obwohl das Programm unter sequentiellen Speichermodellen korrekt war.

Der Prototyp bewies die Korrektheit der sequentiellen Versionen von Petersons und Dekker's Algorithmus und erkannte auch die Fehler, die auftreten, wenn sie nahezu unverändert unter der Verwendung von Release-Acquire-Speichermodellen ausgeführt werden.

## Abstract

Modern Central Processing Units (CPUs) utilize weak memory models to optimize code execution. Compared to sequential consistent memory models, weak memory models allow the reordering of code instructions. While this does not alter the behavior of a single-thread program, it can cause bugs in multicore systems by allowing execution orders between threads that would otherwise not be possible. These errors are often problematic for the developer to detect and understand.

This thesis proposes to use Kronecker Algebra to model possible execution orders of multithreaded programs within weak memory models. The output of such a toolchain can then be used to detect race conditions within the system. It focuses explicitly on weak memory models using release-acquire semantics.

Alongside the thesis, a prototype is developed for the proposed system to detect race conditions in multithreaded programs compiled into LLVM-bytecode. This is done to show that the system can detect problems caused when running a program using releaseacquire memory models. However, the program was correct under sequential memory models.

The prototype correctly proved the correctness of the sequential versions of Peterson's and Dekker's Algorithm. Moreover, the prototype detected the errors that arise when Peterson's and Dekker's Algorithms run without modifications using release-acquire memory models.

# Contents

xv

| K            | ırzfassung                                               | xi                     |

|--------------|----------------------------------------------------------|------------------------|

| $\mathbf{A}$ | estract                                                  | xiii                   |

| C            | ntents                                                   | $\mathbf{x}\mathbf{v}$ |

| 1            | Introduction                                             | 1                      |

|              | 1.1 Aim and Research Questions                           | 3                      |

|              | 1.2 Outline                                              | 4                      |

| 2            | Background                                               | 5                      |

|              | 2.1 Sequential Consistency                               | 5                      |

|              | 2.2 Release-Acquire                                      | 6                      |

|              | 2.3 LLVM                                                 | 6                      |

|              | 2.4 Race Condition                                       | 11                     |

|              | 2.5 Kronecker Algebra                                    | 15                     |

| 3            | Building the Matrix Representation                       | 31                     |

|              | 3.1 Program Skeleton                                     | 31                     |

|              | 3.2 Setting Dependencies                                 | 37                     |

| 4            | Prototype                                                | 45                     |

|              | 4.1 Creating Blocks                                      | 45                     |

|              | 4.2 Building the Skeleton                                | 46                     |

|              | 4.3 Dependencies                                         | 46                     |

|              | 4.4 Optimization                                         | 47                     |

|              | 4.5 Collecting Further Information                       | 49                     |

|              | 4.6 Detecting Dependency Type                            | 49                     |

|              | 4.7 Creating the Graph                                   | 50                     |

|              | 4.8 Detecting Errors                                     | 52                     |

| 5            | Examples                                                 | 55                     |

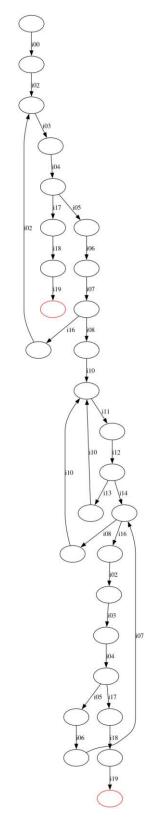

|              | 5.1 Peterson's Algorithm - Sequential Consistent Version | 55                     |

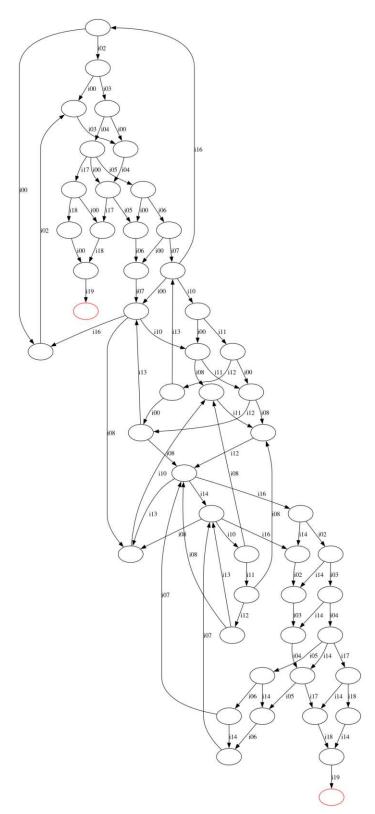

|              | 5.2 Peterson's Algorithm - Release-Acquire Version       | 59                     |

|              |                                                          |                        |

|               | 5.3              | Peterson's Algorithm - Modified Release-Acquire Version | 62 |

|---------------|------------------|---------------------------------------------------------|----|

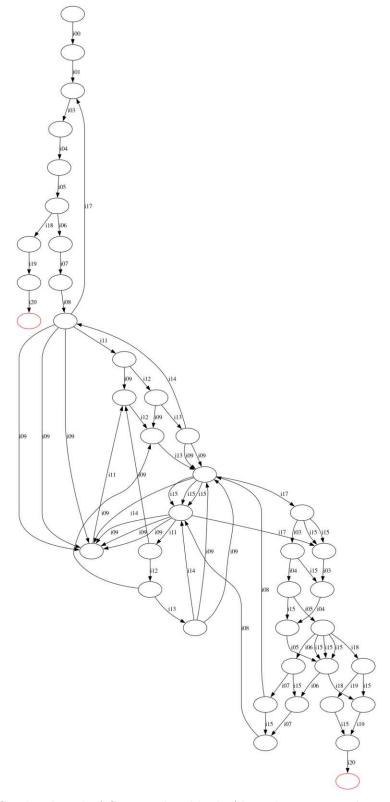

|               | 5.4              | Dekker's Algorithm - Sequential Consistent Version      | 64 |

|               | 5.5              | Dekker's Algorithm - Release-Acquire Version            | 68 |

|               | 5.6              | Dekker's Algorithm - Modified Release-Acquire Version   | 71 |

| 6             | Rela             | ated Work                                               | 75 |

|               | 6.1              | Dynamic Partial Order Reduction                         | 75 |

|               | 6.2              | Iris                                                    | 76 |

|               | 6.3              | Context Bound Analysis                                  | 77 |

| 7             |                  | cussion                                                 | 79 |

|               | 7.1              | Time                                                    | 80 |

| 8             | Con              | aclusion and Future Work                                | 83 |

| $\mathbf{Li}$ | $\mathbf{st}$ of | Figures                                                 | 85 |

| $\mathbf{Li}$ | $\mathbf{st}$ of | Tables                                                  | 87 |

| $\mathbf{Li}$ | st of            | Algorithms                                              | 87 |

| Bi            | blios            | graphy                                                  | 89 |

CHAPTER

## Introduction

When developing programs, many developers make assumptions about the program and its execution that do not always hold. One of these assumptions is that the compiled machine code is executed with a sequentially consistent memory model.

Sequential consistency is the traditional model for executing code. Executing code sequentially consistently means that the instructions are executed in the order of the program code. While this makes programs very predictable and would make it easy to reason about a program's behavior, this usually does not hold for performance reasons.

Modern Central processing units (CPUs) make use of weak memory models. Weak memory models weaken the constraints of sequential consistency by allowing the compiler and CPU to reorder instructions in ways that do not change the result of those instructions. This allows the CPU to maximize its available resources by, for example, fetching multiple values from memory in parallel or calculating multiple values at once.

Furthermore, it can schedule the execution of slow instructions before faster ones. This has the effect that multiple faster instructions can be done in parallel during the calculation of the slow instruction. Once the slow one is finished, any other instruction that depends on its result can be executed. If, instead, multiple slow instructions were done in parallel, followed by the slow one, all instructions dependent on the slow one now have to wait for them to complete. At the same time, the CPU may run idle since there might be no independent instructions for it to execute in parallel.

Another case that can cause the execution order to differ from the order written by the programmer is when compile-time optimizations reorder the code. This might be done to better utilize the CPU pipeline, branch prediction, or similar systems used by the CPU to speed up code execution.

A second assumption many developers make is to assume that the effect of every instruction is seen immediately by all other threads and in the same order. This is not the case.

```

1

2

b

=

0

3

4

thread0

5

a = 1

6

print(b)

7

8

9

thread1 {

10

b = 1

11

print(a)

12

```

Figure 1.1: Race Condition Caused by Delayed Synchronization

Figure 1.2: Example How Optimization Might Influence Execution Order

Instead, every thread may observe writes to memory in different orders; this allows, for example, both threads in Figure 1.1 to print 0 since both threads might still read an old value even though the other thread has overwritten it.

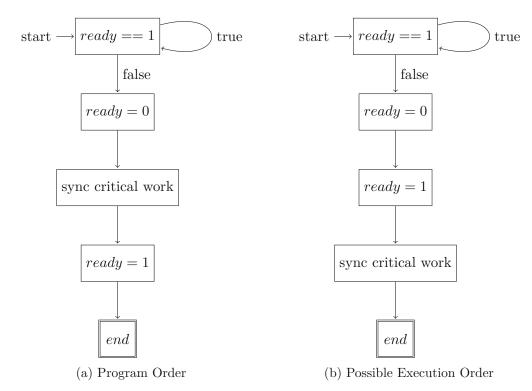

The previously mentioned changes in execution order are designed not to change the program in ways that impact the result of it. However, this is only true for single-threaded applications since the optimizations are done per thread. Figure 1.2a shows, assuming

the check and setting of ready is done atomically, a way of how synchronization-critical code can be wrapped to ensure multiple threads cannot enter the critical section at the same time. Without any optimization, this code would work fine even in multithreaded programs. However, during optimization, the instruction reading and modifying the ready variable will be considered independent of the synchronization-critical code, which allows the CPU to execute both simultaneously; the resulting possible execution order can be seen in Figure 1.2b. This order makes it possible for the variable ready to be reset to 1 before the critical code is finished and, for this reason, allows multiple threads to enter the section simultaneously which can cause a race condition.

A race condition occurs in a system when multiple threads attempt to modify or access shared resources simultaneously. This might cause the program to be unpredictable since its result can depend on the order in which the threads access the shared resources. Race conditions will be further explained in Section 2.4.

Developers can use atomic instructions and memory fences to ensure that neither the compiler nor the CPU reorders synchronization-critical code. Using them allows the programmer to restrict the compiler and CPU's ability to reorder instructions and ensure data synchronization between threads. Thus, they are critical for the correct execution of the program.

However, setting these memory fences is not always easy, and bugs caused by wrong synchronization in weak memory models are not easily detectable by a developer. Even though the problem is undecidable [AAAK19], many verification tools have been developed to help developers detect problems caused by wrong synchronization [LR09, AAC+12, BM08, AAAK19].

#### 1.1 Aim and Research Questions

The aim of this thesis is to develop a new approach to address the previously mentioned issues using Kronecker Algebra. Kronecker Algebra allows the modeling of reordered instruction, the interleaving of concurrent programs [BB14], as well as the detection of race conditions within the program [Bli15].

The following research questions (RQs) were formulated to support the aim and structure of the research process.

- RQ1: Can Kronecker Algebra effectively capture the interactions between threads in concurrent programs following the release acquire model?

- RQ2: To what extent can Kronecker Algebra assist in detecting and resolving data races in programs using the release acquire model?

- RQ3: What are the limitations and challenges of applying Kronecker Algebra to verify the correctness of concurrent programs under the release acquire model?

#### **Delimitations** 1.1.1

The system will prioritize using Kronecker Algebra extensively but not exclusively, to ensure that the time required to verify smaller algorithms remains reasonable.

This also means it will not focus on fixing the state explosion caused by the amount of possible interleavings between the threads.

Lastly, the system will not allow for any dynamic creation of threads during execution.

#### 1.2 Outline

The thesis contains two parts. In the first part, a system that uses Kronecker Algebra to detect race conditions within programs using weak memory models will be developed. The second part will develop a prototype that applies the developed system to programs compiled to LLVM-bytecode. Applying the prototype to several examples shows that the system can correctly detect race conditions. Further, related work will be shown in Section 6.

## Background

This chapter will explain the memory models used in the thesis. Further, a short overview of LLVM, race conditions, and Kronecker Algebra will be given.

#### 2.1Sequential Consistency

Sequential consistency ensures that all threads see every write-to memory in the same order. This makes working with programs using sequential consistency intuitive since every read is guaranteed to read the newest value of the system. Note that this system does not require that every write is immediately synchronized over all threads, only that the write is synchronized to a thread before that thread reads the value.

On its own, this does not prevent race conditions. Take the following program execution as an example:

- Thread A: read value x

- Thread B: read value x

- Thread A: calculate based on x and save it back to x

- Thread B: calculate based on x and save it back to x

In this example, the calculation of thread A is overwritten by thread B with a value that is based on a read that occurred before thread A wrote that value. Algorithms have been developed to prevent this from happening. Section 2.4 will provide further details.

#### 2.2Release-Acquire

A concurrent program that is correct under a sequential memory model is not always correct under a weak memory model. For this reason, different types of synchronization techniques exist. One of those techniques is the release-acquire memory model.

In the release-acquire model, memory accesses are categorized into releases and acquires. A release operation typically stores a value in a shared memory location, while an acquire operation is associated with loading a value from a shared memory location. These operations serve as synchronization points between different memory accesses in the program that define which instructions must be performed before and after.

In the case of a thread performing a release operation on a shared memory location, all memory writes performed before the release are guaranteed to be visible to other threads that perform an acquire operation on the same memory afterward. This ensures that ordering constraints are preserved across threads. Furthermore, the acquire-operator guarantees that no memory writes after the instruction is moved to before the acquireinstruction.

Using these two operators, a programmer can ensure the order of execution to make sure no reordering can occur that threatens the correctness of the concurrent system.

#### 2.3 LLVM

Low-Level Virtual Machine [llvb], or LLVM, is a compiler infrastructure designed to generate code as well as to analyze and optimize it. It was initially implemented for C and C++ but has since been used for many other programming languages like Swift, Rust, and Zig, having compilers that utilize LLVM.

At the core of LLVM is an intermediate representation language that serves as a platformindependent abstraction of program code. This intermediate language allows any optimization techniques implemented for LLVM to be used in any programming language that utilizes LLVM for code generation. It also makes it easier to support different architectures since one compiler, compiling the intermediate language to the target architecture, can be reused by different languages.

#### 2.3.1 Code Structure

LLVM programs are divided into one or multiple modules. In the case of compiling C code using LLVM, each module is equivalent to an object file. Each module consists of global variables and functions.

A function is then divided into one or multiple blocks. A block consists of a list of one or multiple instructions containing exactly one terminator instruction at the end. Terminator instructions alter the control flow of the program, like, for example, RET or BR. Since these terminator instructions are only allowed at the end of the block, and

all control flow-altering instructions jump to the beginning of a block, this means that assuming sequential consistency, when a block is entered, all instructions within the block are executed one after the other with no control flow allowing any instruction to be skipped or repeated till the execution of the block is completed.

Some important LLVM instructions for this thesis can be seen in Table 2.1.

It is important to mention that ALLOCA returns a pointer to the created address and globals pointers to the values. For this reason, to access or change the values, a STORE or LOAD is needed.

| Name                 | Usage                                                                                                                                                | Overview                                                                                         |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| STORE                | STORE <ty> <va>, ptr <po></po></va></ty>                                                                                                             | Stores value in <va> to <po> as type <ty></ty></po></va>                                         |

|                      | STORE atomic <ty> <va>, ptr <po></po></va></ty>                                                                                                      | Atomic version that uses the ordering <or></or>                                                  |

|                      | <or>, align <al></al></or>                                                                                                                           | ment <al></al>                                                                                   |

| LOAD                 | $\langle re \rangle = LOAD \langle ty \rangle$ , ptr $\langle po \rangle$                                                                            | saves the value of <po> of type <ty> into <re></re></ty></po>                                    |

|                      | $\langle re \rangle = LOAD$ atomic $\langle ty \rangle$ , ptr $\langle per \rangle$                                                                  | Atomic version that uses ordering <or> and alignment</or>                                        |

|                      | <or>, align <al></al></or>                                                                                                                           | <al></al>                                                                                        |

| BR                   | BR i1 <con>, label <iftrue>, label <if-< td=""><td>if value in <con> is 0 jump to block <iffalse> else to</iffalse></con></td></if-<></iftrue></con> | if value in <con> is 0 jump to block <iffalse> else to</iffalse></con>                           |

|                      | false>                                                                                                                                               | <iffrue></iffrue>                                                                                |

|                      | BR label <dest></dest>                                                                                                                               | Unconditional jump to block <dest></dest>                                                        |

| ICMP                 | $\langle re \rangle = icmp \langle co \rangle \langle ty \rangle \langle op1 \rangle \langle op2 \rangle$                                            | Compares the values $\langle op1 \rangle$ and $\langle op2 \rangle$ of type $\langle ty \rangle$ |

|                      |                                                                                                                                                      | using the operator in $\langle \cos \rangle$ returning 1 to $\langle \cos \rangle$ if            |

|                      |                                                                                                                                                      | comparision is true or 0 otherwise, or a list of such                                            |

|                      |                                                                                                                                                      | values if $\langle op1 \rangle$ and $\langle op2 \rangle$ are lists. Possible values             |

|                      |                                                                                                                                                      | of $\langle \cos \rangle$ can be seen in Table 2.2                                               |

|                      | $\langle re \rangle = i cmp \ same sign \langle co \rangle \langle ty \rangle \langle op1 \rangle$                                                   | guarantees that $\langle op1 \rangle$ and $\langle op2 \rangle$ have the same sign               |

|                      | $\langle op2 \rangle$                                                                                                                                |                                                                                                  |

| $\operatorname{RET}$ | RET <ty> <va></va></ty>                                                                                                                              | Returns value <va> of type <ty> from the function</ty></va>                                      |

|                      | RET void                                                                                                                                             | Return from a void function                                                                      |

| PHI                  | $\langle re \rangle = PHI \langle ty \rangle [\langle val \rangle, \langle bl \rangle], \dots$                                                       | saves <val> of type <ty> to <re> if last executed</re></ty></val>                                |

|                      |                                                                                                                                                      | block was<br><br>bl>                                                                             |

| ALLOCA               | $\langle re \rangle = ALLOCA \langle ty \rangle$                                                                                                     | allocates memory for type <ty> on the stack, returns</ty>                                        |

|                      |                                                                                                                                                      | pointer to data                                                                                  |

Table 2.1: List of Important LLVM Instructions [llva], (Optional Values Are Not Included in Usage)

| Name | Operation               |  |

|------|-------------------------|--|

| eq   | equal                   |  |

| ne   | not equal               |  |

| ugt  | unsigned greater than   |  |

| uge  | unsigned greater than   |  |

| ult  | unsigned less than      |  |

| ule  | unsigned less or equal  |  |

| sgt  | signed greater than     |  |

| sge  | signed greater or equal |  |

| slt  | signed less than        |  |

| sle  | signed less or equal    |  |

Table 2.2: List of Possible ICMP Operators

#### 2.3.2 LLVM API

The LLVM API is part of the LLVM project and contains tools to parse and modify the intermediate language of LLVM. This structure makes implementing new tools for analyzing and optimizing code easier and allows them to be used on all languages that compile to LLVM bytecode.

The LLVM API can load a LLVM code file using the parseIRFile function and the function returns an LLVM module object that already contains much-needed information. The following will list important types and valuable functions of the LLVM API.

#### Module

The module class represents an LLVM module and allows access to the filename using getName, but most importantly, allows access to an iterator over all functions using functions as well as globals to access an iterator over global variables.

#### Function

It represents both function declaration and definition. Both can be differentiated using the isDeclaration function. It also contains an iterator to iterate through all blocks of the function.

### **BasicBlock**

Represents a LLVM Block. Most notably, the class contains an iterator that allows iteration through all block instructions in order. Further, the functions 11vm::predecessors and 11vm::successors, when called on a block, return all possible predecessor and successor blocks, which allows to follow the control flow through the blocks easily.

### Value

Value is the base class for many other classes, including BasicBlock, Instruction, GlobalValue, ConstantInt, and ConstantData.

It is used as the return value of many functions that have to return many different types. The function llvm::dyn\_cast allows a program to verify the exact type and cast it so that the return value can be handled differently depending on the exact type.

#### Use

Use is another subclass of Value and the parent class of everything that can be passed as an argument to an instruction. This includes all the previously mentioned Value subclasses: BasicBlock, Instruction, GlobalValue, ConstantInt, and ConstantData.

#### Instruction

This is the base class for all LLVM Instructions. Some important functions the class provides are:

- getParent: returns block instruction is part of

- operands: returns iterator over all arguments given to the instruction

- getOpcode: allows verification of which type of instruction it is.

- getNextNode (getNextNonDebugInstruction): returns the instruction that, in code, is written directly after the given one (ignoring debug instructions)

- getPrevNode (getPrevNonDebugInstruction): returns the instruction that, in code, is written directly above the given one (ignoring debug instructions)

Once cast to the specific subtype representing the exact LLVM instruction, the specific class contains functions to more easily differentiate between the return values of operands.

For example, the class PHINode contains the functions getIncomingValue and getIncomingBlock to easily access which value a variable is set to when which BasicBlock was the predecessor block, while the class ICmpInst contains getPredicateName to easily access and differentiate between the different compare operators given in Table 2.2.

Figure 2.1: Example Read-Modify Race Condition

#### 2.4 Race Condition

Race conditions are a significant problem when dealing with concurrent programs [NM92]. These conditions occur when the outcome of a program depends on the sequence or timing of uncontrollable events. In essence, multiple threads or processes compete for shared resources, and the execution outcome becomes unpredictable due to the timing of their operations.

Usually, the cause of race conditions is the lack of synchronization between concurrent processes that access shared resources like files or variables. When multiple threads or processes attempt to access and modify these resources simultaneously, the final state of the resource becomes dependent on the timing and interleaving of their operations. This leads to inconsistent or erroneous behavior of the program, often resulting in bugs, crashes, or security vulnerabilities.

There are different forms of race conditions:

- Read-Modify-Write

- Check-Then-Act

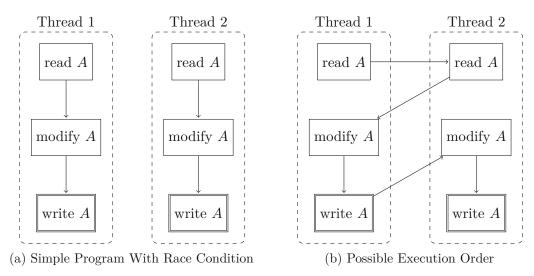

A Read-Modify-Write race occurs when multiple threads access the same resource, modify it, and then save it back. This can result in one of the modifications being lost.

Figure 2.1b shows such an example. In the example, thread 1 and thread 2 read the value of A, followed by thread 1 modifying and saving the values, followed by thread 2 modifying and saving different values.

Figure 2.2: Example Check-Then-Act Race Condition

Since both threads read the original value first, both modify it using that original value. When one thread saves its modified value, the second one completely overwrites it with a value that does not depend on the value written by the previous thread, thus effectively voiding the execution of the first one as if it never occurred.

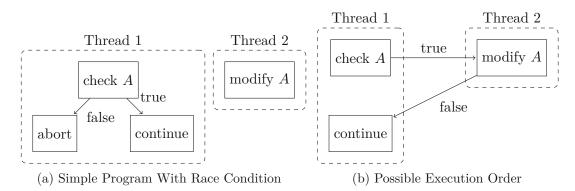

A Check-Then-Act race happens when a thread checks for a specific condition to hold and then acts depending on the result of the previous check. A second thread may modify resources used in the condition check in between it occurring and the first thread acting on the check, treating the resource as if the condition holds while it no longer does. An example can be seen in Figure 2.2b.

There have been algorithms developed to ensure that such problems cannot arise, and so only one thread has access to a variable from when it reads the value till it saves a calculated value based on it.

Two examples of such algorithms are Dekker's Algorithm [Dij62] and Peterson's Algorithm [Pet81]. Implementations of these algorithms can be seen in Figure 2.3.

#### Peterson's Algorithm 2.4.1

Peterson's Algorithm [Pet81] works by each thread first setting a variable that signals its intent to enter the critical section, followed by a turn variable that gives priority to another thread. Depending on what process 1 does during the time process 0 is setting those variables, one of three scenarios can happen when checking the condition as seen in line 8 in Figure 2.3a.

process\_1 is not trying to enter the critical section, in which case flaq[1] is false, and turn equals 1 when process\_0 is checking the while condition. Thus, the condition is false, and process\_0 can enter the critical section.

process\_1 is currently in the critical section. As can be seen in Figure 2.3a, this means that process\_1 has set flag[1] to true. Since process\_0 is setting turn to 1, both parts of the while condition hold, and it awaits process 1 to exit the critical section and reset flag[1] to false in line 25.

process\_1 is also trying to enter the critical section. In this case, it depends on which order the turn variable is set. If process\_0 sets turn first, then process\_1 will overwrite the value. This causes the while condition of process\_0 to be false and it enters the critical section while process\_1 waits. Otherwise, the roles are reversed, and process\_1 can enter.

#### Dekker's Algorithm 2.4.2

Dekker's Algorithm [Dij62] uses the same variables, but it differs in when and how they are checked. As can be seen in Figure 2.3b, when it tries to enter the critical section, it only sets its flag variable to true in line 6. After this, the same three scenarios can happen.

process\_1 is not trying to enter the critical section, in which case flag[1] is false. Thus, when process\_0 is checking the outer while condition, the condition is false, and the thread skips the loop and enters the critical section.

process\_1 is currently in the critical section. In this case, it depends on the current value of turn. If turn is 0, process\_0 is looping in the outer loop till process\_1 exits the critical section. Otherwise, it will enter the if condition and loop within the inner loop till process\_1 exits the section.

process\_1 is also trying to enter the critical section. In this case, both threads will enter the loop, and depending on the current value of turn, one of the two threads will enter the if condition, disabling its intent to enter the section to allow the other thread to enter.

```

bool flag [2] = \{false, false\};

int turn = 0;

2

3

void process_0() {

flag[0] = true;

6

7

while (flag[1])

if (turn != 0) {

8

flag[0] = false;

9

while (turn != 0)

10

continue;

11

flag[0] = true;

12

bool flag [2] = \{false, false\};

1

13

2

int turn = 0;

14

3

// Beginning Critical Section

15

4

void process_0() {

16

// End Critical Section

5

17

flag[0] = true;

6

turn = 1;

18

7

flag[0] = false;

turn = 1;

19

while (flag[1] \&\& turn == 1)

8

20

9

continue;

21

10

// Begin Critical Section

void process_1() {

22

11

23

12

// End Critical Section

flag[1] = true;

24

while (flag[0])

13

flag[0] = false;

25

14

}

if (turn != 1) {

26

15

flag[1] = false;

27

16

void process_1() {

while (turn != 1)

28

17

continue;

29

18

flag[1] = true;

flag[1] = true;

30

19

\mathrm{turn} \; = \; 0 \, ;

31

20

while (flag[0] \&\& turn == 0)

32

21

{\bf continue}\,;

// Beginning Critical Section

33

22

// Beginning Critical Section

34

// End Critical Section

23

35

24

// End Critical Section

turn = 0;

36

25

flag[1] = false;

flag[1] = false;

37

}

}

26

38

(a) Peterson's Algorithm

(b) Dekker's Algorithm

```

Figure 2.3: C Implementation of Peterson's and Dekker's Algorithm (turn and flag Must Be Sequentially Consistent Atomics)

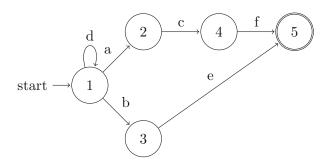

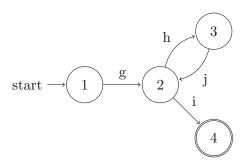

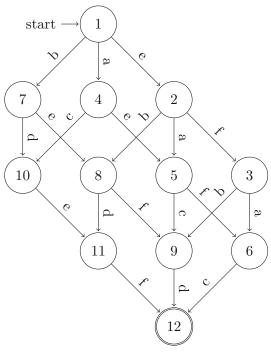

Figure 2.4: FSM  $F_0$

#### 2.5 Kronecker Algebra

Kronecker Algebra expands the standard matrix operations (e.g., matrix addition, matrix multiplication). At its core is the Kronecker Product.

The following is an overview of the necessary parts of Kronecker Algebra as described in the Kronecker Booklet [Bli15].

#### 2.5.1Finite State Machine (FSM) as Matrix

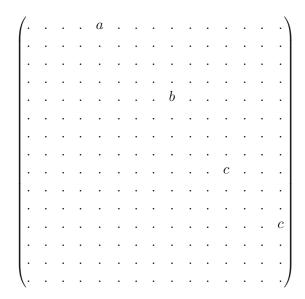

Every FSM can be converted into an n by n matrix, with n being the number of states in the FSM. This is done by labelling every node with a unique number from 1 to n and then creating an n by n matrix where every transition within the FSM from a starting node with the ID s to an end node with the ID e is added to the matrix by setting the value at row s and column e to the label of the transition and all elements not set in this way being set to 0.

Take the FSM  $F_0$  in Figure 2.4 as an example. This finite state machine can be converted into a 5 by 5 matrix by setting the following positions.

- (1,1) to value d

- (1,2) to value a

- (1,3) to value b

- (2,4) to value c

- (3,5) to value e

- (4,5) to value f

This results in the following matrix:

$$\begin{pmatrix} d & a & b & 0 & 0 \\ 0 & 0 & 0 & c & 0 \\ 0 & 0 & 0 & 0 & e \\ 0 & 0 & 0 & 0 & f \\ 0 & 0 & 0 & 0 & 0 \end{pmatrix}$$

It is important to know that this loses the information about which nodes are considered end and starting nodes. To not lose this information we can create an initial node vector and an end node vector.

The initial node vector of an m by m matrix is a vector of size m in which all elements are set to 0 except for elements with the ID of starting nodes. In the example above this results in the vector  $S_{F_0} = (1, 0, 0, 0, 0)$ .

Equally, we can create the end node vector by only marking elements that share the ID with end nodes. This results in the end node vector

$$E_{F_0} = \begin{pmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 1 \end{pmatrix}$$

for the example above.

From now on, all 0 values of matrices will be represented with a dot for readability. Furthermore, it is assumed that all used FSMs only have one starting node, which will always be given the id 1. If this is applied to the matrix above, the result is the following:

$$\begin{pmatrix} d & a & b & . & . \\ . & . & . & c & . \\ . & . & . & . & e \\ . & . & . & . & f \\ . & . & . & . & . \end{pmatrix}$$

#### 2.5.2 Kronecker Product

The Kronecker Product is denoted by  $\otimes$  and defined as:

$$A \otimes B = \begin{pmatrix} a_{1,1} \cdot B & \dots & a_{1,n} \cdot B \\ \vdots & \ddots & \vdots \\ a_{m,1} \cdot B & \dots & a_{m,n} \cdot B \end{pmatrix}$$

For a matrix A of dimensions m by n.

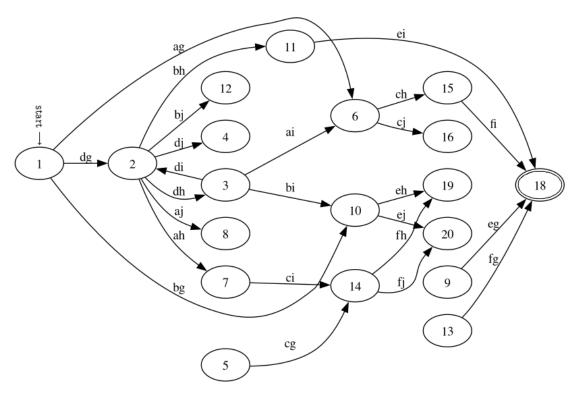

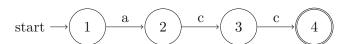

Figure 2.5: FSM  $F_1$

As an example, the Kronecker Product of the FSM in Figures 2.4 and 2.5 is:

$$\begin{pmatrix} d & a & b & . & . \\ . & . & . & c & . \\ . & . & . & . & e \\ . & . & . & . & f \\ . & . & . & . & . \end{pmatrix} \otimes \begin{pmatrix} . & g & . & . \\ . & . & h & i \\ . & j & . & . \\ . & . & . & . \end{pmatrix} =$$

Its graph representation is given in Figure 2.6 and the resulting FSM with all not reachable nodes removed in Figure 2.7.

Figure 2.6: Result of the Kronecker Product of the Automata Shown in 2.4 and 2.5

Figure 2.7: Result of the Kronecker Product of the Automata Shown in 2.4 and 2.5 Without Unreachable Nodes

As seen in the figures, this results in a new FSM equivalent to the two automata running in lockstep, which ends as soon as one of them runs into a dead end. But note that not all nodes that have no outgoing edges are valid end nodes of our new graph.

To calculate all valid start and end nodes of a graph  $A \otimes B$  we first have to create the initial state vectors  $S_A$  and  $S_B$  as well as the final state vectors  $E_A$  and  $E_B$ . Then the initial state vector of  $A \otimes B$  can be calculated using  $S_A \otimes S_B$  with the final state vector being calculated as  $E_A \otimes E_B$ .

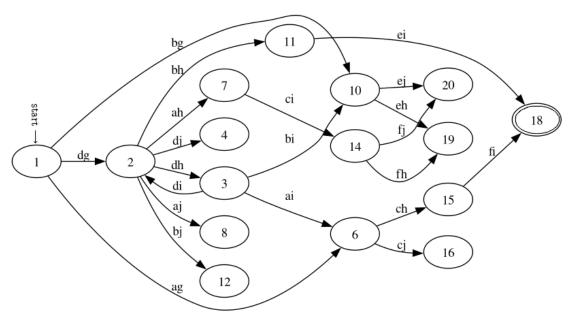

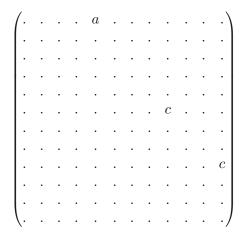

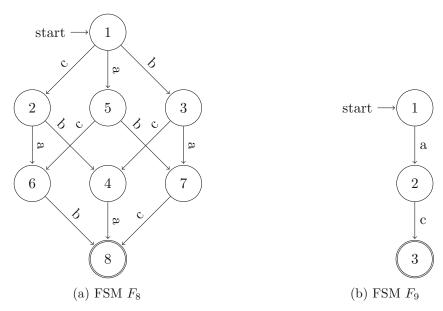

#### 2.5.3 Synchronized Kronecker Product

The Synchronized Kronecker Product, denoted for clarity as  $\otimes$ , is equivalent to the standard Kronecker Product with one difference. Every matrix element resulting from the Kronecker Product is set to 0 if its value is not equal to xx, with x being some label name or x otherwise.

As an example, the Kronecker Product of the matrix representations of the automata shown in Figure 2.8 and Figure 2.9 is:

$$\begin{pmatrix} . & a & . & . & . \\ . & . & b & . & . \\ . & . & . & c & . \\ . & . & . & . & c \\ . & . & . & . & . \end{pmatrix} \otimes \begin{pmatrix} . & a & . \\ . & . & b \\ . & . & c \end{pmatrix} =$$

While its Synchronized Kronecker Product is:

$$\begin{pmatrix} . & a & . & . & . \\ . & . & b & . & . \\ . & . & . & c & . \\ . & . & . & . & c \\ . & . & . & . & . \end{pmatrix} \dot{\otimes} \begin{pmatrix} . & a & . \\ . & . & b \\ . & . & c \end{pmatrix} =$$

Figure 2.8: FSM  $F_2$

Figure 2.9: FSM  $F_3$

Figure 2.10: Result of the Synchronized Kronecker Product of the Automata  $F_2$  and  $F_3$

The graphical representation can be seen in Figure 2.10. As can be seen, the graphs in Figures 2.10 and 2.8 are equivalent except for the node IDs and thus isomorphic.

However, there are matrices where this is not the case. Take the matrix representations of the Figures 2.11 and 2.9 as an example:

$$\begin{pmatrix} \cdot & a & \cdot & \cdot \\ \cdot & \cdot & c & \cdot \\ \cdot & \cdot & \cdot & c \\ \cdot & \cdot & \cdot & \cdot \end{pmatrix} \dot{\otimes} \begin{pmatrix} \cdot & a & \cdot \\ \cdot & \cdot & b \\ \cdot & \cdot & c \end{pmatrix} =$$

Figure 2.11: FSM  $F_4$

Note that the label a is in the 5th column of the result matrix, but the two c labels are in rows 6 and 9, which means they are unreachable. In this example, the resulting graph only contains one edge with the label a, meaning it is not isomorphic to the left operator of the Synchronized Kronecker Product.

When analyzing the two examples, someone might realize that in the first example, the FSM in Figure 2.8 can be simulated by the FSM in Figure 2.9, while in the second 2.9 cannot simulate 2.11 and make the conclusion that the operation results in an isomorphic graph if the right side of the operator simulates the left side and a non-isomorphic graph if not.

This is not necessarily the case. As an example, take the Synchronized Kronecker Product between Figure 2.12 and Figure 2.9:

Figure 2.12: FSM  $F_5$

Figure 2.13: Result of Synchronized Kronecker Product of the Automata  $F_5$  and  $F_3$

While the resulting graph in Figure 2.13 is isomorphic to the one in Figure 2.12, the FSM in 2.9 does not halt in the end node when reaching the end node of 2.12.

The final nodes of a graph calculated using the (Synchronized) Kronecker Product can be calculated by building the Kronecker Product of the vectors containing the final nodes of the underlying graphs.

If both conditions are satisfied, graph A is isomorphic to graph  $A \otimes B$ , and both have equivalent final nodes. All execution orders of graph B can also be found in graph A with the difference that graph A might encounter labels not present in graph A.

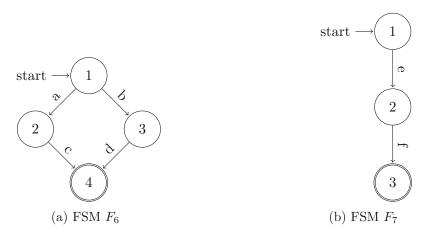

#### Kronecker Sum 2.5.4

Kronecker Sum is defined for matrix A and matrix B as:

$$A \oplus B = A \otimes I_n + I_m \otimes B$$

With A being an m by m, B an n by n matrix, and  $I_k$  the k by k identity matrix.

As an example, the Kronecker Sum between FSMs shown in Figures 2.14a and 2.14b is:

$$\begin{pmatrix} \cdot & a & b & \cdot \\ \cdot & \cdot & \cdot & c \\ \cdot & \cdot & \cdot & d \\ \cdot & \cdot & \cdot & \cdot \end{pmatrix} \oplus \begin{pmatrix} \cdot & e & \cdot \\ \cdot & \cdot & f \\ \cdot & \cdot & \cdot \end{pmatrix} =$$

$$\begin{pmatrix} . & a & b & . \\ . & . & . & c \\ . & . & . & d \\ . & . & . & . \end{pmatrix} \otimes \begin{pmatrix} 1 & . & . \\ . & 1 & . \\ . & . & 1 \end{pmatrix} + \begin{pmatrix} 1 & . & . & . \\ . & 1 & . & . \\ . & . & 1 & . \\ . & . & . & 1 \end{pmatrix} \otimes \begin{pmatrix} . & e & . \\ . & . & f \\ . & . & . \end{pmatrix} =$$

| $\begin{pmatrix} . & . & . & a & . & . & b & . & . & . & . & . \\ . & . & . & . & a & . & . & b & . & . & . & . \\ . & . & . & . & . & a & . & . & b & . & . & . & . \\ . & . & . & . & . & .$ |   |   |   |    |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----|---|

| $\left \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                     |   |   |   |    |   |

|                                                                                                                                                                                                |   |   |   |    | 1 |

|                                                                                                                                                                                                |   |   |   |    | 1 |

| 1 1                                                                                                                                                                                            |   |   | • |    |   |

| $\begin{vmatrix} \cdot & \cdot $                                                                                               |   | ٠ |   |    | = |

| $\begin{bmatrix} \cdot & d & \cdot & \cdot$                                                                                            |   | • | • |    |   |

|                                                                                                                                                                                                | f | • | • |    |   |

|                                                                                                                                                                                                | ٠ | • | ٠ |    |   |

|                                                                                                                                                                                                | ٠ |   |   |    |   |

|                                                                                                                                                                                                | • |   | • | f  |   |

| (                                                                                                                                                                                              | • | • | • | ٠, | , |

| $\left\langle \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                              |   |   |   |    |   |

| $\begin{bmatrix} \cdot & \cdot & f & \cdot & a & \cdot & \cdot & b & \cdot & \cdot & \cdot \end{bmatrix}$                                                                                      |   |   |   |    |   |

| $\begin{bmatrix} \cdot & \cdot & \cdot & \cdot & a & \cdot & \cdot & b & \cdot & \cdot & \cdot \end{bmatrix}$                                                                                  |   |   |   |    |   |

| $\left[ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                    |   |   |   |    |   |

| $\begin{bmatrix} \cdot & \cdot & \cdot & \cdot & f & \cdot & \cdot & \cdot & c & \cdot \end{bmatrix}$                                                                                          |   |   |   |    |   |

| $\begin{bmatrix} \cdot & c \end{bmatrix}$                                                                                              |   |   |   |    |   |

| $\begin{bmatrix} \cdot & \cdot & \cdot & \cdot & \cdot & \cdot & e & \cdot & d & \cdot & \cdot \end{bmatrix}$                                                                                  |   |   |   |    |   |

|                                                                                                                                                                                                |   |   |   |    |   |

|                                                                                                                                                                                                |   |   |   |    |   |

| $\begin{bmatrix} \cdot & e & \cdot \\ & \cdot & & \cdot & \cdot & \cdot & \cdot & \cdot & \cdot & e \end{bmatrix}$                     |   |   |   |    |   |

|                                                                                                                                                                                                |   |   |   |    |   |

Similar to the Kronecker Product, this produces a new FSM, a combination of the two input FSMs. However, unlike the Kronecker Product, where the result is that the two input FSMs are executed in lockstep, the Kronecker Sum results in a Finite State Machine equivalent to executing all interleavings of the input FSMs.

Figure 2.14: Examples FSM for Kronecker Sum

Figure 2.15: Result of Kronecker Sum Between  $F_6$  and  $F_7$

Figure 2.16: Examples FSM for Kronecker Skip

#### 2.5.5Kronecker Skip

Kronecker Skip is defined as:

$$A \odot U = A_V \otimes I_m + A_S \stackrel{.}{\otimes} U$$

With  $A_V$  being the matrix A with all elements that exist in U set to 0,  $A_S$  being A with all elements that do not exist in U set to 0, and  $I_m$  being an identity matrix of size mwith m being the size of matrix U.

As an example, take the Kronecker Skip of the graphs in Figures 2.16a and 2.16b:

$$\begin{pmatrix} . & c & b & . & a & . & . & . \\ . & . & . & b & . & a & . & . \\ . & . & . & c & . & . & a & . \\ . & . & . & . & . & . & . & a \\ . & . & . & . & c & b & . & . \\ . & . & . & . & . & . & . & b \\ . & . & . & . & . & . & . & . & c \\ . & . & . & . & . & . & . & . & . \end{pmatrix} \odot \begin{pmatrix} . & a & . \\ . & . & c \\ . & . & . & . \end{pmatrix} =$$

Figure 2.17: Result of Kronecker Skip Between  $F_8$  and  $F_9$

| Sibliothek, |  |

|-------------|--|

| Z           |  |

| ,          |   |   |   |   |   | , |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | `   |  |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|--|

| <i>(</i> · |   |   |   |   | • | b | • | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   | . ) |  |

|            |   |   |   |   |   |   | b |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . ] |  |

| ١.         |   |   |   |   |   |   |   | b |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |  |

|            | • | • | • | • | • |   |   |   |   | _ |   |   |   |   |   |   |   | • | • | • | • | • |     |  |

| ١.         | • | • | • | • | • | • | ٠ |   |   |   |   |   |   |   |   | • | • | • | • | • | • | • |     |  |

| ١.         |   |   |   |   | • | • | • | • | • |   | b |   | • |   |   |   |   |   |   |   |   |   |     |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |  |

| ١.         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .   |  |

| ١.         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |  |

| l          | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • |     |  |

|            | • | • | • | • | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | .   |  |

| ١.         |   | • |   | ٠ | ٠ | ٠ | • | • | ٠ | • |   | • | ٠ |   |   | • | ٠ | ٠ |   | • |   |   |     |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b |   |   |   |   |   |   |   |     |  |

| ١.         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b |   |   |   |   |   |   |     |  |

|            | • | · |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | · |     |  |

| ١.         | • | • | • | • | • | • | • | • | • |   |   |   |   |   |   |   |   |   |   | • | , | • |     |  |

| ١.         | • | ٠ | • | ٠ | ٠ | • | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | • | • | • | • | • | ٠ | • | • | b | • |     |  |

| ١.         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b |     |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b   |  |

| ١.         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .   |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |  |

| ١.         | • | • | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • |     |  |

| ١.         | • | ٠ | • | • | ٠ | • | • | • | ٠ | ٠ | • | ٠ | ٠ | • | • | • | ٠ | • | • | • | ٠ | ٠ |     |  |

| ١.         |   |   |   |   | ٠ | • | • | ٠ | ٠ |   |   |   | • |   |   |   |   |   |   |   |   |   |     |  |

|            |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .   |  |

| ١.         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . ] |  |

|   |     | /  |   |   |   |   |   |   |   |   |   |   |   |   | а |   |   |   |   |   |   |   |   |   | \    |   |

|---|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|---|

|   | - 1 |    | • | • | • | • | • | • | • | • | • | • | • | • | a | • | • | • | • | • | • | • | • | • | ٠, ا | 1 |

|   | - [ |    |   |   |   |   | c |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | a |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ ا  |   |

|   | - 1 |    |   | • |   |   | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | a |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | • |   |   |   |   |   |   |   |   | • | • | ٠ | • | • |   | • | • | ٠ | ٠ ا  |   |

|   | - 1 | ٠  | • | • | • | • | • | • | • | • | ٠ | • | c | • | • | ٠ | • | • | • | • | • | ٠ | • | • | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | ٠ | • | • | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | a | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ ا  | = |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   | c |   |   |   |   |   |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | C | • | • | • | • | • | • | • | • | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |

|   | - 1 | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | .    |   |

|   | - 1 |    |   | • |   |   |   | • |   |   |   | • |   |   |   |   |   |   |   | • |   |   | • |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | ٠ | Ė    |   |

|   | ł   | ٠  | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | ٠ | • | • | • | • | • | ٠ | • | • |      |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | c    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | _    |   |

|   | - 1 | •  | • | • |   | • | • | • |   | • | • | • | • | • | ٠ | • | • | • | ٠ | ٠ | • | • | • | • |      |   |

|   |     |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .    |   |

|   | - 1 |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |

|   | 1   | ٠  | • | • | • | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | • | ٠ | • | • | .    |   |

| \ | 1   | (. |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . ]  |   |

|   | (.  |   |   |   |   |   | b |   |   |   |   |   |   | a |   |   |   |   |   |   |   |   |   | . \      |

|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------|

|   |     |   |   |   |   | c |   | b |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .        |

|   | •   | ٠ |   | ٠ | ٠ |   |   | • |   | 7 |   |   | • | • | ٠ | ٠ | ٠ | ٠ | ٠ | • | ٠ | ٠ | • |          |

|   | •   | • | • |   |   |   |   | • |   |   | , | • |   |   |   |   | • | • | • | • |   | • |   | ٠        |

|   |     |   |   |   |   |   |   |   |   |   |   | , |   |   |   |   |   |   |   |   |   |   |   | - 1      |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | a |   |   |   | - 1      |

|   |     |   |   |   |   |   |   |   |   |   |   | c |   |   |   |   |   |   |   |   |   |   |   | .        |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .        |

|   |     |   |   | • | ٠ | ٠ | ٠ | ٠ | ٠ |   |   |   |   |   | ٠ |   |   |   | ٠ |   | • | ٠ | a | ·        |

|   | •   | ٠ | • | ٠ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | ٠ | ٠ | ٠ | .        |

|   |     | • | • | • | ٠ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |          |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | - 1      |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 7 |   |   |   |   |   |          |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b |   | .        |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | b | :        |

|   |     | • |   | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ |   |   | • | • | ٠ | ٠ |   | ٠ | ٠ | • | ٠ | ٠ | ٠ | $b \mid$ |

|   |     | • | • | ٠ | ٠ | ٠ | ٠ |   |   |   |   |   |   |   |   |   |   |   |   | • |   |   | ٠ | c        |

|   |     |   |   |   | • | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |          |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |          |

|   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . ]      |

| 1 | \ . |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . ]      |

The graph representation can be seen in Figure 2.17. The graph shows that the resulting FSM is equivalent to the graph left of the operator but with all paths removed in which an edge with the label a does not precede an edge labeled c.

CHAPTER

31

# Building the Matrix Representation

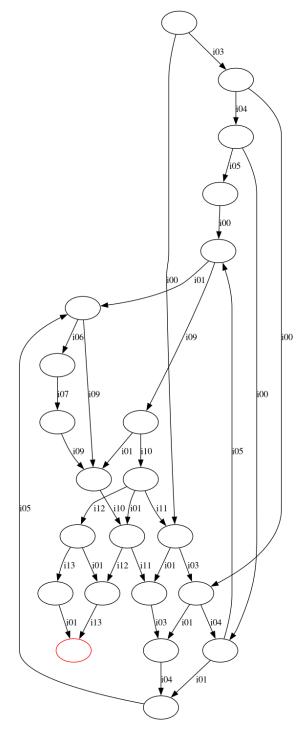

The following sections explain how a list of instructions and LLVM blocks can be converted into a matrix representation.

#### 3.1 Program Skeleton

The first step is to generate a matrix that represents the program's basic structure. This means the matrix should contain all instructions and should already respect control flow dependencies. This means the matrix should model the program as if all its instructions are entirely independent.

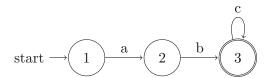

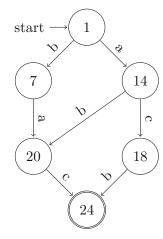

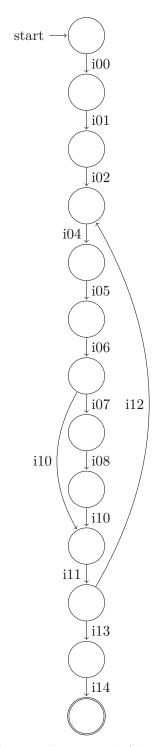

#### 3.1.1 Generating Blocks

A list of matrices can be generated in the first step, with each matrix representing all possible execution orders within one LLVM block. The simplest version to do this is to calculate the Kronecker Sum of a list of matrices of the form

$$\begin{pmatrix} . & x \\ . & . \end{pmatrix}$$

for every instruction x contained in the block. Figure 3.1a shows the result of a Kronecker Sum operation between three matrices with the instructions a, b, and c.

While this way of modeling a block works for many blocks, it has two flaws:

Firstly, modeling many dependencies between instructions in two different blocks is challenging. For this reason, a pseudo instruction will be added that will be labeled using

Figure 3.1: Example Creation of Blocks

bxx (xx being a unique numeric ID for each block). Further, all regular instructions will, from now on, be labeled using ixx. The purpose of these pseudo instructions is to model dependencies that ensure that all instructions within a block must be executed after a specific instruction. For us to be able to use the label for this purpose, we have to ensure that our pseudo instruction is guaranteed to be executed first within the block. This can be done by taking the Kronecker Sum of all instructions, including the pseudo-instruction, and applying the Kronecker Skip with matrices of the form:

$$\begin{pmatrix} . & bxx & . \\ . & . & iyy \\ . & . & . \end{pmatrix}$$

For each instruction ID, y within the block, and xx is the ID of that block's pseudoinstruction. So, for a block with the ID 00 and the instructions i00, i01, and i02, the block conversion would be done using the following formula:

$$\begin{pmatrix} . & b00 \\ . & . \end{pmatrix} \oplus \begin{pmatrix} . & i00 \\ . & . \end{pmatrix} \oplus \begin{pmatrix} . & i01 \\ . & . \end{pmatrix} \oplus \begin{pmatrix} . & i02 \\ . & . \end{pmatrix} \odot$$

$$\begin{pmatrix} . & b00 & . \\ . & . & i00 \\ . & . & . \end{pmatrix} \odot \begin{pmatrix} . & b00 & . \\ . & . & i01 \\ . & . & . \end{pmatrix} \odot \begin{pmatrix} . & b00 & . \\ . & . & i02 \\ . & . & . \end{pmatrix}$$

The resulting FSM can be seen in Figure 3.1b.

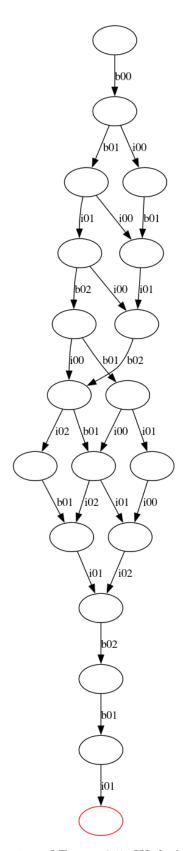

The second problem is that if we continue with these blocks, we will run into the problem of them not being able to model loops. For now, the goal of the blocks is that a Kronecker Sum of all blocks in a program results in a matrix that models all possible executions if all dependencies are ignored. However, since the Kronecker Sum only creates possible interleavings between the FSM, the result cannot contain a loop if none of the input matrices contain one.

For this reason, if a block is part of a loop, which means there is some path through the program that starts and ends at that block, the possibility of every instruction within the block being succeeded by itself at some point must be modeled. Therefore, the matrices to model the existence of an instruction with the ID xx are modified to the following:

$$\begin{pmatrix} . & ixx \\ ixx & . \end{pmatrix}$$

and

$$\begin{pmatrix} . & byy \\ ixx & . \end{pmatrix}$$

It is used to model the dependency that the instruction ixx must be preceded by the block-specific pseudo instruction byy. A resulting example graph can be seen in Figure 3.2. Note that this introduces the limitation that an instruction has to be executed before the block is executed a second time. This is deliberate and will be explained in Section 3.1.2.

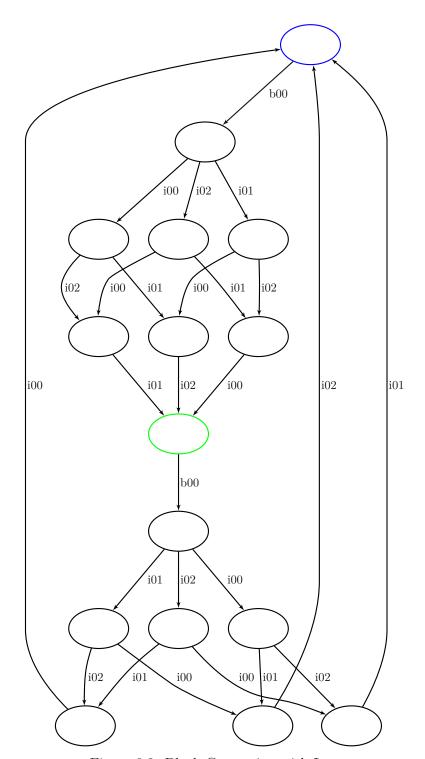

Also note that the block in Figure 3.2 can be simplified by creating a graph that merges both nodes that have outgoing b00 edges, meaning all incoming edges of the node that is marked green instead point to the starting node marked in blue. This halves the size of the graph representing that block and makes all graphs using that block smaller. From now on, the "loop-block" will be simplified.

#### 3.1.2Limitations of Loops

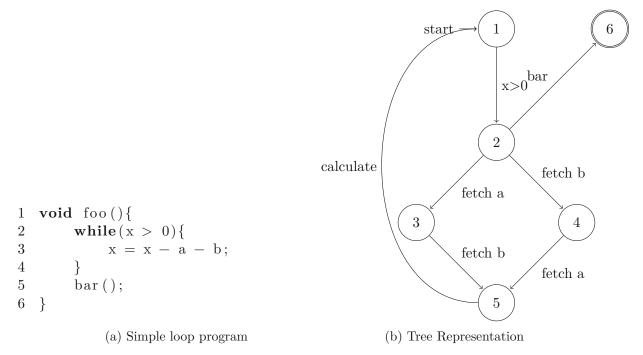

Loops cause a unique challenge when modeling them using matrix representation. When modeling the function in Figure 3.3a, the matrix representation should show that there is the possibility that the calculation within the loop is executed multiple times. To model this, the last edge of the part of the graph that models the inside of the loop can target the node before the check within the while loop is done, as seen in Figure 3.3b.

Figure 3.2: Block Conversion with Loop

Figure 3.3: Example of a Loop That Can Be Modelled in Matrix Form

However, not every loop can be modeled so easily. When looking at an example where an instruction is not producing any output used by any other instruction within the loop or its conditions, problems in modeling them occur. Following are two groups of loops where this is the case:

- 1. Produced value is only used after the loop terminates (3.4a).

- 2. Produced value is only used by other threads (3.4b).

In the example in Figure 3.3b all instructions within the loop must be finished before a new iteration can start. This means the instructions can only be delayed till the beginning of the next loop iteration. In the Figures 3.4a and 3.4b this is not the case, instead the instructions calculating and modifying y can be delayed till the following iteration of the loop or even till after termination of the loop. This has the effect that not only do we have to model the situation in which our first iteration of the loop executes this instruction, but we also have to model the situation in which this iteration delays it. This has the effect that the model has to show that the second iteration of the loop can either execute the instruction not at all or up to twice, depending on if it delays the execution, executes the instruction of the previous loop, or executes the instruction of this and the previous loop.

Every following iteration suggests that the next iteration might execute the instruction again. Since the modeled graph does not model the exact amount of iterations, and

```

1

void foo(){

void foo(){

1

2

while (x > 0)

2

while (x > 0)

3

y += 1;

3

x -= b;

4

x -= b;

4

y = foobar();

5

5

6

6

bar();

print(y);

7

7

}

```

(a) Loop Instruction is Independent of Other (b) Produced Value is Independent of Everything That is Executed Within the Thread Instruction Within the Loop

Figure 3.4: Examples of Loops Not Easily Modeled

detecting the maximum amount of iterations in many cases is impossible, an infinite amount of iterations would need to be modeled to model all possible execution orders. This would result in an infinite graph and, therefore, an infinite matrix, which is not usable for any further analysis.

The way of generating the blocks is described in the previous sections, results in a graph in which those situations are not possible. Instead, the resulting graph models a program in which all loop instructions must be executed before the next iteration starts. This, of course, might cause false negatives in such cases.

An argument might be made that only modeling a small number of iterations of every loop might be enough to detect the majority of errors. This would allow for unrolling the loops and would reduce the size required to model such problems to a finite space, but this will not be explored any further in this thesis.

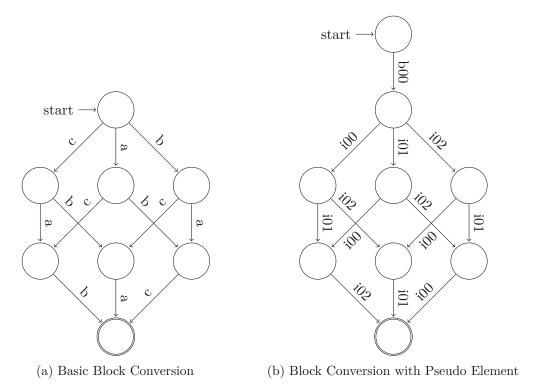

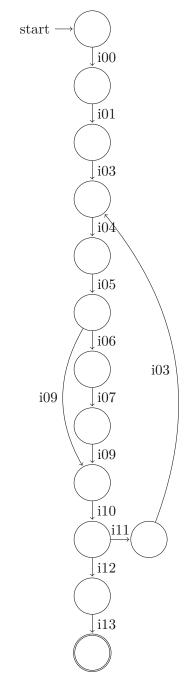

#### 3.1.3 Generating the Skeleton

The matrix resulting from the Kronecker Sum of the matrices from the previous steps does not yet respect the program's control flow. Currently, it allows all blocks and their containing instructions to be executed in an arbitrary order. The following describes how a matrix can be created that, when applied using Kronecker Skip, results in a new matrix that respects control flow dependencies.

We start by adding an edge from node 1 to 2 for the first block and labeling the edge with the name of the pseudo instruction of that block. After that, we repeat the following.

If the block has a single successor, add an edge labeled with the successor block name to either a new node, in case the successor block has not been reached before, or a node that already has a predecessor edge with that label.

If the block has multiple successors, add a new edge labeled with the name of the instruction that decides which successor block is chosen to a new node. Then, add an

edge for each successor block, labeled with that successor's name, to an existing node with a predecessor edge with that label or a new node if such a node does not exist.

Adding the jump instructions ensures that all instructions of the successor blocks are executed after the condition that decides which successor is chosen. This enforces dependencies caused by control flow.

This skeleton-matrix could be replaced with several matrices of similar style as the one explained in Section 3.2 between the LLVM BR and similar end-instructions and its successor blocks pseudo-instructions. However, merging those dependencies into one skeleton matrix makes setting dependencies easier. Furthermore, as will be seen in Section 4.4, this is an optimization implemented in the prototype that decreases the calculation time by reducing the number of Kronecker operations and allows the removal of multiple BR instructions from the graph.

#### 3.2 Setting Dependencies

This section focuses on how the matrices are constructed to model an instruction i00depending on an instruction i01. For the simplest form, this was already shown in Section 3.1.1 where the following matrix

$$\begin{pmatrix} . & b00 & . \\ . & . & i00 \\ . & . & . \end{pmatrix}$$

was used for non-loops and the matrix

$$\begin{pmatrix} . & b00 \\ i00 & . \end{pmatrix}$$

for loops to ensure b00 always precedes i00.

This was enough to create the blocks since, by the nature of LLVM blocks, all instructions within the block are executed whenever the block is entered without any conditional executions, which would result in some instructions only being executed sometimes or multiple times.

#### 3.2.1Dependency on Previous Iteration of a Loop

Even if both instructions are within the same LLVM block, the previously shown two "simple" rules are insufficient. Take the code in Figure 3.5a as an example; the print statement and the assignment to a will be combined into the same LLVM block. Since the print statement is outputting the value of the variable a, starting from the second iteration of the loop, it depends on the assignment of the previous iteration.

3

4

a = 0;

2

3 foo{ 4

a = 1while X:

print(a) 5 a = 15 6 6 a = a + 1print(a) print(a)

if X:

(a) Example in Which In-(b) Example in Which In-(c) Example in Which Instrucstruction Depends on the Pre-struction Depends on Instruc-tion in Loop Depends on Invious Iteration of Loop tion Inside Condition struction Outside It

Figure 3.5: Different Dependency Examples

If we label the print statement i00 and the assignment i01, then the rule:

$$\begin{pmatrix} . & i01 \\ i00 & . \end{pmatrix}$$

would ensure that the print cannot be moved before the assignment. More precisely, it would ensure that, when executing the code, any i00 is always preceded by an i01 without another i00 being in between them.

But our execution order is  $i00, i01, i00, i01, i00, i01, \dots$ , with the first i00 not being preceded by an i01. Therefore, the matrix would not cause the intended result.

In this specific case, the fix is to ignore that dependency altogether. As explained before, the graph is modeled so that all instructions must be executed before the block can be executed again. This means the construction of the graph already ensures that i00 and i01 of the first iterations are both executed before the block is reentered and, therefore, that the assignment i01 of the first iteration is executed before the print i00 of the second iteration.

Once we look outside a single block, we see many more cases in which the above rules are insufficient. Two further examples can be seen in Figures 3.5b and 3.5c.

### **Dependency With Condition**

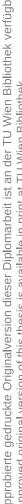

The basics of Figure 3.5b can be expressed with the block-matrices:

$$\begin{pmatrix} . & b00 & . \\ . & . & i00 \\ . & . & . \end{pmatrix} \begin{pmatrix} . & b01 & . \\ . & . & i01 \\ . & . & . \end{pmatrix} \begin{pmatrix} . & b02 & . \\ . & . & i02 \\ . & . & . \end{pmatrix}$$

combined with the skeleton

$$\begin{pmatrix} . & b00 & . & . & . \\ . & . & i00 & . & . \\ . & . & . & b01 & b02 \\ . & . & . & . & b02 \\ . & . & . & . & . \end{pmatrix}$$

with i00 being the condition, i01 being the assignment, i02 the print statement, and the bxx being block instructions. Applying the skip operator with the basic rule:

$$\begin{pmatrix} . & i01 & . \\ . & . & i02 \\ . & . & . \end{pmatrix}$$

results in the matrix:

A graphical representation with and without the applied rule can be seen in Figures 3.6a and 3.6b.