#### A PhD THESIS ON

# Dependable and Energy Efficient Design of Embedded Systems: A Cross-Layer **Approach**

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### **Doctor of Technical Science**

in

Engineering Sciences: Electrical Engineering (UE 786 710)

by

## Saeed Seyedfaraji

11944048

### **Supervisor:**

Associate Prof. Dr. -Ing. Privatdoz.in Semeen Rehman

Vienna, Austria March 2025

## **Abstract**

Embedded systems are at the heart of modern technology, powering diverse applications ranging from autonomous vehicles to medical devices and Internet of Things (IoT) solutions. These systems face unique constraints, such as limited energy budgets, real-time performance requirements, and stringent reliability demands. However, as processing capabilities continue to grow, the separation of memory and processing in traditional von Neumann architectures presents a significant challenge for embedded systems: the memory wall, which causes delays in data transfer between the processor and memory. This issue, characterized by the disparity between processor speeds and memory access latencies, exacerbates inefficiencies in embedded systems, where both energy and computational resources are scarce.

As Richard Sites observed in 1996: "Today's chips are largely able to execute code faster than we can feed them with instructions and data. The real design action is in memory subsystems—caches, buses, bandwidth, and latency." This statement highlights the persistent challenge in modern computing, particularly for embedded systems where the combination of constrained resources and real-time performance demands amplifies the inefficiencies introduced by the memory wall.

To address these challenges, novel approaches have redefined data processing within memory systems. Among these, Processing in Memory (PIM) architectures have emerged as a transformative solution, integrating computation directly within memory to minimize data movement and the associated energy per operation consumption. By reducing the reliance on traditional memory subsystems, PIM alleviates delays caused by the gap between processing speed and memory access times for data loads while enhancing energy efficiency, which is an essential requirement in embedded systems.

Despite its promise, existing PIM-based techniques face critical limitations in real-world deployments. For example, Spin Transfer Torque Random Access Memory (STT-RAM), a leading non-volatile memory technology for PIM, suffers from high write energy and latency due to stochastic switching behavior and process variations. Similarly, Static Random Access Memory (SRAM), widely employed in embedded accelerators, experiences inaccuracies in in-memory computations caused by nonlinearities in the Bit-Line (BL) discharge process. These challenges undermine the dependability and energy efficiency of PIM solutions, preventing them from realizing their full potential in memory-centric applications such as artificial intelligence, while limiting their ability to meet the real-time control and high-performance computing demands, which are crucial for embedded systems where speed and reliability are essential.

In order to address the above-mentioned challenges, this thesis proposes a cross-layer approach to achieving dependable and energy-efficient design for embedded systems, leveraging both volatile and non-volatile memory technologies. By addressing the unique constraints and performance demands of embedded systems, this thesis presents various innovative PIM-based techniques and system-level tools to overcome these limitations and advance the field of embedded computing. In particular, PIMbased systems face robustness challenges, and the lack of comprehensive modeling and benchmarking frameworks complicates the effective development and utilization of these PIM-based systems.

To address these research gaps, this thesis makes the following contributions, a) Developing advanced modeling and benchmarking frameworks for PIM-based systems; b) Designing robust and efficient PIM circuit architectures for improved reliability and performance. Through these key contributions, this thesis advances the field by offering both system-level tools for evaluating STT-RAM architectures and practical solutions for enhancing the efficiency, accuracy, and reliability of SRAM-based memory accelerators. These innovations collectively address long-standing challenges in memorycentric computing systems. To systematically address these challenges, the contributions of this thesis include the aspects of Volatile Memorys (VMs) and Non-Volatile Memorys (NVMs):

#### 1. Volatile Memory

- OPTIMA: A modeling framework for rapid design-space exploration of SRAM-based accelerators, addressing circuit nonlinearities and power variations critical for embedded system design [1].

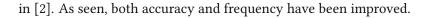

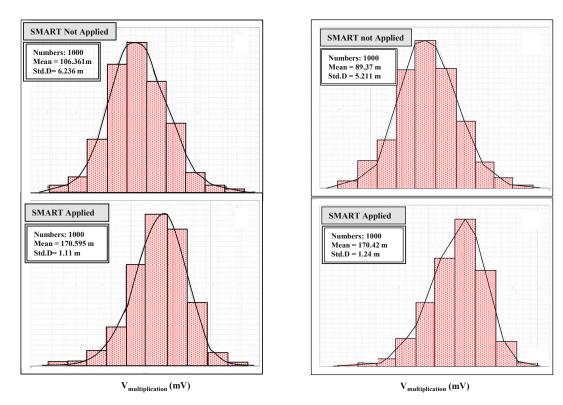

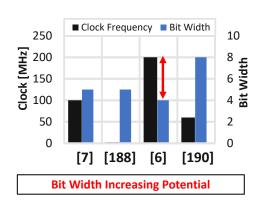

- AID: A circuit design technique that linearizes BL discharge in SRAM, significantly improving accuracy and reducing energy consumption in in-memory multiplication accelerators [2].

- EMAC: A method leveraging digital-to-time Word-Line (WL) modulation and logical weight encoding to enhance energy efficiency and accuracy in analog SRAM-based Multiplication and Accumulation (MAC) accelerators with minimal accuracy degradation in real-world embedded applications [3].

#### 2. Non-Volatile Memory

• An open-source, extendable STT-RAM memory controller integrated into the gem5 simulator, enabling evaluations of power, latency, and throughput to guide optimization strategies [4]. • A novel write optimization technique combining stochastic switching and circuit-level ap-

and process variations [5].

proximations to reduce write energy and latency while enhancing robustness against soft errors

TW **Sibliothek**, Die approbierte gedruckte Originalversion dieser Dissertation ist an der TU Wien Bibliothek verfügbar.

\*\*Nour knowledge hub\*\*

The approved original version of this doctoral thesis is available in print at TU Wien Bibliothek.

# Kurzfassung

Eingebettete Systeme stehen im Zentrum der modernen Technologie und treiben eine Vielzahl von Anwendungen an, die von autonomen Fahrzeugen über medizinische Geräte bis hin zu Internet of Things (IoT)-Lösungen reichen. Diese Systeme unterliegen einzigartigen Einschränkungen, wie begrenzten Energiebudgets, Echtzeitanforderungen und strengen Zuverlässigkeitsanforderungen. Mit zunehmender Verarbeitungskapazität stellt jedoch die Trennung von Speicher und Verarbeitung in traditionellen Von-Neumann-Architekturen eine erhebliche Herausforderung für eingebettete Systeme dar: die memory wall, die Verzögerungen beim Datentransfer zwischen Prozessor und Speicher verursacht. Dieses Problem, das durch die Diskrepanz zwischen Prozessorgeschwindigkeit und Speicherzugriffszeiten gekennzeichnet ist, verstärkt Ineffizienzen in eingebetteten Systemen, in denen sowohl Energie- als auch Rechenressourcen knapp sind.

Wie Richard Sites bereits 1996 feststellte: "Today's chips are largely able to execute code faster than we can feed them with instructions and data. The real design action is in memory subsystems—caches, buses, bandwidth, and latency." Diese Aussage unterstreicht die anhaltende Herausforderung in der modernen Informatik, insbesondere für eingebettete Systeme, bei denen die Kombination aus begrenzten Ressourcen und Echtzeitanforderungen die durch die memory wall verursachten Ineffizienzen verstärkt.

Um diese Herausforderungen zu bewältigen, wurden neue Ansätze zur Datenverarbeitung innerhalb von Speichersystemen entwickelt. Unter diesen haben sich PIM-Architekturen als eine transformative Lösung herausgestellt, die Rechenoperationen direkt in den Speicher integrieren, um die Datenbewegung und den damit verbundenen Energieverbrauch pro Operation zu minimieren. Durch die Reduzierung der Abhängigkeit von herkömmlichen Speichersubsystemen verringert PIM Verzögerungen, die durch die Lücke zwischen Prozessorgeschwindigkeit und Speicherzugriffszeiten bei Datenladungen entstehen, während es gleichzeitig die Energieeffizienz verbessert - eine wesentliche Anforderung in eingebetteten Systemen.

Trotz ihres Potenzials stoßen bestehende PIM-basierte Techniken in realen Anwendungen auf kritische Einschränkungen. Beispielsweise leidet STT-RAM, eine führende nichtflüchtige Speichertechnologie für PIM, unter hohem Schreibenergieverbrauch und hoher Latenz aufgrund stochastischer Schaltvorgänge und Prozessvariationen. Ebenso weist SRAM, das häufig in eingebetteten Beschleunigern verwendet wird, Ungenauigkeiten bei In-Memory-Berechnungen auf, die durch Nichtlinearitäten im BL-Entladeprozess verursacht werden. Diese Herausforderungen beeinträchtigen die Zuverlässigkeit und Energieeffizienz von PIM-Lösungen, wodurch sie ihr volles Potenzial in speicherzentrierten Anwendungen wie künstlicher Intelligenz nicht ausschöpfen können. Gleichzeitig schränken sie ihre Fähigkeit ein, den Echtzeitsteuerungs- und Hochleistungsrechenanforderungen gerecht zu werden, die für eingebettete Systeme essenziell sind.

Um diese Herausforderungen zu bewältigen, schlägt diese Dissertation einen schichtenübergreifenden Ansatz zur Entwicklung zuverlässiger und energieeffizienter eingebetteter Systeme vor, der sowohl flüchtige als auch nichtflüchtige Speichertechnologien nutzt. Durch die Berücksichtigung der spezifischen Einschränkungen und Leistungsanforderungen eingebetteter Systeme werden in dieser Arbeit verschiedene innovative PIM-basierte Techniken und systemorientierte Werkzeuge vorgestellt, um diese Einschränkungen zu überwinden und das Gebiet des eingebetteten Rechnens voranzutreiben. Insbesondere stehen PIM-basierte Systeme vor Herausforderungen hinsichtlich der Robustheit, und das Fehlen umfassender Modellierungs- und Benchmarking-Frameworks erschwert die effektive Entwicklung und Nutzung dieser PIM-basierten Systeme.

Um diese Forschungslücken zu schließen, trägt diese Dissertation zu folgenden Aspekten bei: a) Entwicklung fortschrittlicher Modellierungs- und Benchmarking-Frameworks für PIM-basierte Systeme; b) Entwurf robuster und effizienter PIM-Schaltungsarchitekturen zur Verbesserung der Zuverlässigkeit und Leistung.

Durch diese wesentlichen Beiträge treibt diese Arbeit das Fachgebiet voran, indem sowohl systemorientierte Werkzeuge zur Evaluierung von STT-RAM-Architekturen als auch praktische Lösungen zur Steigerung der Effizienz, Genauigkeit und Zuverlässigkeit von SRAM-basierten Speicherbeschleunigern bereitgestellt werden. Diese Innovationen adressieren gemeinsam langjährige Herausforderungen in speicherzentrierten Rechensystemen.

Um diese Herausforderungen systematisch zu adressieren, umfassen die Beiträge dieser Dissertation die Aspekte von VMs und NVMs:

#### 1. Volatile Memory

- OPTIMA: Ein Modellierungsframework für die schnelle Entwurfsraumanalyse von SRAM-basierten Beschleunigern, das Schaltungsnichtlinearitäten und Leistungsvariationen berücksichtigt, die für das Design eingebetteter Systeme entscheidend sind [1].

- AID: Eine Schaltungstechnik zur Linearisierung der BL-Entladung in SRAM, die die Genauigkeit

- erheblich verbessert und den Energieverbrauch in In-Memory-Multiplikationsbeschleunigern reduziert [2].

- EMAC: Eine Methode, die digitale-zu-Zeit-WL-Modulation und logisches Gewichtscodieren nutzt, um die Energieeffizienz und Genauigkeit in analogen SRAM-basierten MAC-Beschleunigern zu verbessern, mit minimalen Genauigkeitsverlusten in realen eingebetteten Anwendungen [3].

### 2. Non-Volatile Memory

- Ein Open-Source, erweiterbarer STT-RAM-Speichercontroller, der in den gem5-Simulator integriert ist und die Bewertung von Leistung, Latenz und Durchsatz ermöglicht, um Optimierungsstrategien zu entwickeln [4].

- Eine neuartige Schreiboptimierungstechnik, die stochastisches Schalten und schaltungstechnische Approximationen kombiniert, um den Schreibenergieverbrauch und die Latenz zu reduzieren, während gleichzeitig die Robustheit gegenüber Soft-Fehlern und Prozessvariationen verbessert wird [5].

### Erklärung

Hiermit erkläre ich, dass die vorliegende Arbeit ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt wurde. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet.

Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder in ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

### Copyright Statement

I, Saeed Seyedfaraji, hereby declare that this thesis is my own original work and, to the best of my knowledge and belief, it does not:

- Breach copyright or other intellectual property rights of a third party.

- · Contain material previously published or written by a third party, except where this is appropriately cited through full and accurate referencing.

- · Contain material which to a substantial extent has been accepted for the qualification of any other degree or diploma of a university or other institution of higher learning.

- · Contain substantial portions of third party copyright material, including but not limited to charts, diagrams, graphs, photographs or maps, or in instances where it does, I have obtained permission to use such material and allow it to be made accessible worldwide via the Internet.

| Signature:                  |                   |

|-----------------------------|-------------------|

| Vienna, Austria, March 2025 | Saeed Seyedfaraji |

## Acknowledgment

I am deeply grateful to my supervisor, Associate Prof. Dr.-Ing. Privatdoz. Semeen Rehman, whose unwavering support and guidance have been instrumental in shaping this Ph.D. thesis. Her mentorship has been invaluable, and without her encouragement, this work would not have been possible.

I extend my sincere thanks to Univ.Prof. Dipl.-Ing. Dr. techn. Axel Jantsch for his years of support and leadership as the head of the Institute of Computer Technology. His guidance has played a crucial role in my academic journey. I am also profoundly appreciative of Prof. Kuan-Hsun Chen and Univ.Prof. Dipl.-Ing. Dr. techn. Axel Jantsch for their insightful feedback and contributions as co-examiners.

My heartfelt gratitude goes to my colleagues at the Institute of Computer Technology, Microwave, and Circuit Engineering. Their camaraderie and collaboration have enriched my research experience. I am especially grateful to Mr. Baset Mesgari, whose guidance, expertise, and unwavering support have been instrumental in shaping my research. His collaboration has profoundly influenced my work, and I deeply appreciate his invaluable insights. I also extend my gratitude to Mr. Asad Aftab, whose support and discussions have contributed significantly to my research journey.

Finally, I reserve my deepest appreciation for my wife, Farzaneh Namdarpour. Her unwavering support, patience, and encouragement have been my pillar of strength throughout this journey, making every challenge more bearable and every success more meaningful.

# **Dedication**

To my father and mother, whose presence in my life shines as brightly as stars in the night sky, illuminating my path with their wisdom, love, and unwavering support throughout every journey and endeavor.

To my beloved wife, who embodies the very essence and purpose of life itself. Her presence brings meaning, joy, and fulfillment to every moment, and her love is the guiding light that brightens my days.

Lastly, to the courageous and resilient men and women of my homeland, Iran, who tirelessly strive for freedom and equality. Their determination, perseverance, and sacrifices inspire hope and serve as a reminder of the enduring human spirit in the pursuit of justice and liberty for all.

# List of publication

- [1]. Seyedfaraji, S., Shakibhamedan, S., Seyedfaraji, A., Mesgari, B., TaheriNejad, N., Jantsch, A., & Rehman, S. (2024). E-MAC: Enhanced In-SRAM MAC Accuracy via Digital-to-Time Modulation. IEEE Journal on Exploratory Solid-State Computational Devices and Circuits (JXCDC) [3].

- [2]. Seyedfaraji, S., Jager, S., Shakibhamedan, S., Aftab, A., & Rehman, S. (2024). OPTIMA: Design-Space Exploration of Discharge-Based In-SRAM Computing: Quantifying Energy-Accuracy Trade-offs. In Proceedings of the 61st ACM/IEEE Design Automation Conference (DAC) [1].

- [3]. Seyedfaraji, S., Bichl, M., Aftab, A., & Rehman, S. (2024). HOPE: Holistic STT-RAM Architecture Exploration Framework for Future Cross-Platform Analysis. IEEE Access [4].

- [4]. Seyedfaraji, S., Mesgari, B., & Rehman, S. (2022). AID: Accuracy improvement of analog dischargebased in-SRAM multiplication accelerator. In 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE) [2].

- [5]. Seyedfaraji, S., Mesgari, B., & Rehman, S. (2022). SMART: Investigating the Impact of Threshold Voltage Suppression in an In-SRAM Multiplication/Accumulation Accelerator for Accuracy Improvement in 65 nm CMOS Technology. In 2022 25th Euromicro Conference on Digital System Design (DSD) [6].

- [6]. Seyedfaraji, S., Daryani, J. T., Aly, M. M. S., & Rehman, S. (2022). EXTENT: Enabling approximationoriented energy efficient STT-RAM write circuit. IEEE Access [5].

## **Contents**

| Al | ostrac | et      |                                                                                     | iii |

|----|--------|---------|-------------------------------------------------------------------------------------|-----|

| Κι | ırzfa  | ssung   |                                                                                     | vi  |

| 1  | Intr   | oductio | on                                                                                  | 1   |

|    | 1.1    | Proble  | m Motivation                                                                        | 4   |

|    | 1.2    | Resear  | rch Questions and Objectives                                                        | 7   |

|    | 1.3    | Struct  | ure of the Thesis                                                                   | 8   |

| 2  | Bac    | kgroun  | d and Related Work                                                                  | 11  |

|    | 2.1    | Differ  | ent Memory Technologies                                                             | 12  |

|    | 2.2    | Proces  | ss in Memory (PIM) Architectures and Classification                                 | 20  |

|    |        | 2.2.1   | Architectural Design of PIM                                                         | 20  |

|    |        | 2.2.2   | PIM by Application Domain                                                           | 24  |

|    |        | 2.2.3   | PIM by Memory Technology                                                            | 25  |

|    |        | 2.2.4   | PIM by Evaluation Methodology                                                       | 25  |

| 3  | Des    | ign and | l Evaluation of Robust In-SRAM Computing Circuits                                   | 31  |

|    | 3.1    | SRAM    | Fundamental Operation Principles and Structures                                     | 33  |

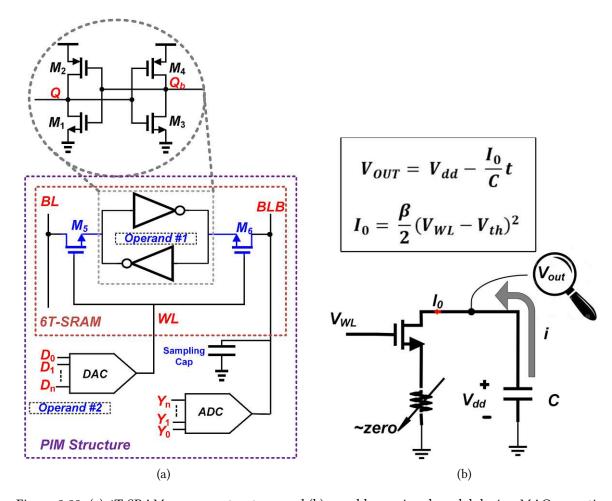

|    | 3.2    | Quant   | itative Description of Mixed-Mode Multiplication Using a 6T-SRAM cell $$            | 33  |

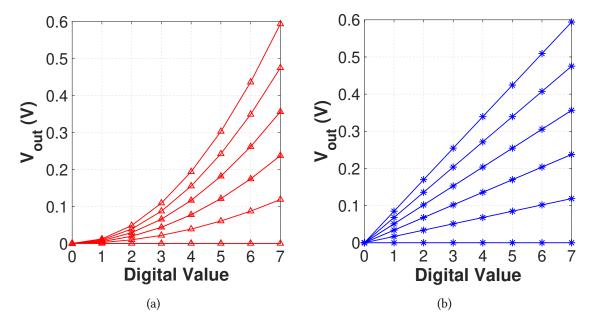

|    | 3.3    | Mappi   | ing the Digital Data to the Analog Voltage of $V_{WL}$ and Linearity Issue $\ldots$ | 37  |

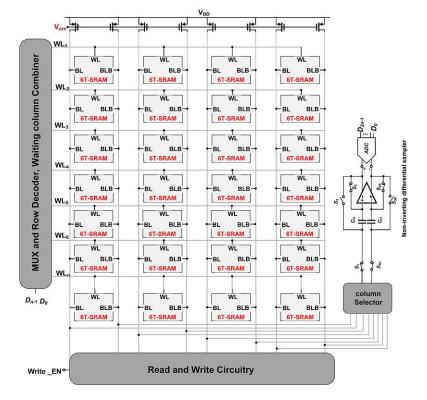

|    | 3.4    | Multi-  | Bit Calculation In 6T-SRAM                                                          | 38  |

|    | 3.5    | Experi  | imental Setup in 65nm CMOS Technology                                               | 40  |

|    | 3.6    | Invest  | igating the Impact of Threshold Voltage Suppression in an In-SRAM MAC $ .  .  . $ . | 41  |

|    |        | 3.6.1   | Body Effect of the MOSFET                                                           | 42  |

|    |        | 3.6.2   | Experimental Setup and Comparison                                                   | 44  |

|    | 3.7    | Design  | n-Space Exploration of Discharge-Based In-SRAM Computing                            | 46  |

xviii

Bibliography

|   |     | 3.7.1   | In-SRAM Computing Error Sources                                  | 47  |

|---|-----|---------|------------------------------------------------------------------|-----|

|   |     | 3.7.2   | Proposed Modeling Framework: OPTIMA                              | 49  |

|   |     | 3.7.3   | Case Study: In-SRAM Multiplier                                   | 51  |

|   |     | 3.7.4   | Application Analysis                                             | 54  |

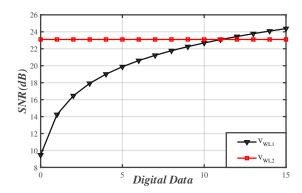

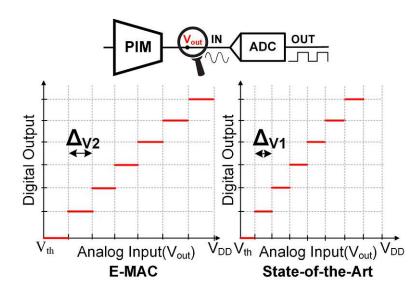

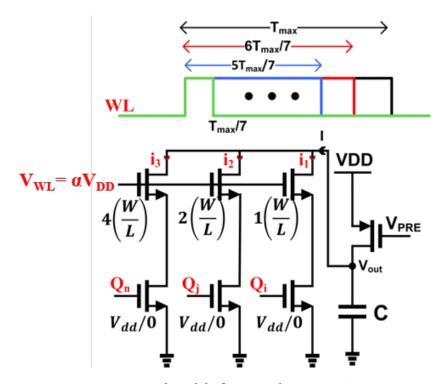

|   | 3.8 | Enhan   | ced In-SRAM MAC Accuracy via Digital-to-Time Modulation          | 56  |

|   |     | 3.8.1   | Problem of Non-linear Voltage Drops During MAC Operation         | 58  |

|   |     | 3.8.2   | Our Novel E-MAC Technique, and Concept Overview                  | 60  |

|   |     | 3.8.3   | Problem of Identical Results with Diverse Voltage Drops          | 63  |

|   |     | 3.8.4   | Analytical Model and E-MAC Circuit Implementation and Results    | 65  |

|   |     | 3.8.5   | Performance Evaluation                                           | 68  |

|   |     | 3.8.6   | Data-Awareness                                                   | 69  |

|   |     | 3.8.7   | CNN Implementation, Evaluation, and Results                      | 69  |

| 4 | Imn | rovina  | the Reliability and Energy Efficiency of STT-RAM Systems         | 77  |

| 4 | •   | ·       |                                                                  |     |

|   | 4.1 | -       | n-Level Exploration of STT-RAM Technology                        | 78  |

|   |     | 4.1.1   | Need for STT-RAM-based System Modeling                           | 78  |

|   |     | 4.1.2   | STT-RAM Fundamental Operation Principles and Structure           | 80  |

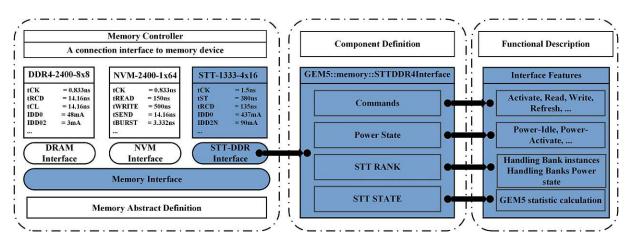

|   |     | 4.1.3   | System level modeling and Evalution framework                    | 82  |

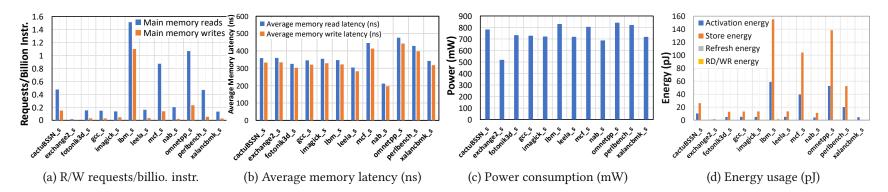

|   |     | 4.1.4   | STT-RAM Performance Evaluation                                   | 92  |

|   |     | 4.1.5   | STT-RAM Power and Energy Breakdown                               | 92  |

|   |     | 4.1.6   | DRAM Metrics                                                     | 93  |

|   |     | 4.1.7   | Comparing STT-RAM and DRAM Results                               | 93  |

|   | 4.2 | Enabli  | ng Approximation-Oriented Energy Efficient STT-RAM Write Circuit | 97  |

|   |     | 4.2.1   | Reliability Challenges in STT-RAM                                | 97  |

|   |     | 4.2.2   | Proposed Approximated Write Driver                               | 101 |

|   |     | 4.2.3   | Cross-Layer Evaluation of Proposed Approximated Write Driver     | 104 |

| 5 | Con | clucion | and Future Works                                                 | 111 |

| J |     |         |                                                                  |     |

|   | 5.1 |         | Summary                                                          | 111 |

|   | 5.2 | Future  | Works                                                            | 112 |

Contents

115

# **List of Tables**

| 2.1  | Comprehensive comparison of different memory technologies [7–21]                     | 13  |

|------|--------------------------------------------------------------------------------------|-----|

| 3.1  | AID vs. state-of-the-art techniques                                                  | 40  |

| 3.2  | SMART vs. state-of-the-art techniques                                                | 45  |

| 3.3  | Selected design corners                                                              | 54  |

| 3.4  | DNN classification accuracies for CIFAR10                                            | 55  |

| 3.5  | DNN classification accuracies for ImageNet                                           | 55  |

| 3.6  | Encoding scheme of operands in a MAC process                                         | 61  |

| 3.7  | All possible 3-bit operands multiplication                                           | 65  |

| 3.8  | Comparison with state-of-the-art in-SRAM analog-based MAC accelerators               | 67  |

| 3.9  | Performance results for float quantized, and proposed model for LeNet5-Inspired CNN. | 71  |

| 3.10 | Comparison with the related works, tested with the MNIST Dataset                     | 73  |

| 3.11 | Performance results for float, quantized, and proposed model for VGG16 $$            | 73  |

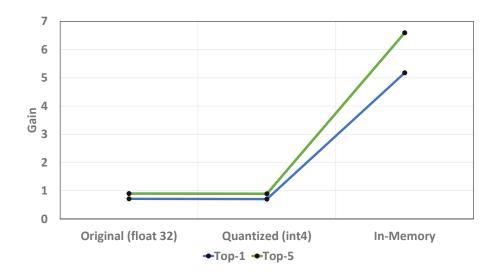

| 3.12 | Energy usages and gains of VGG16 per inference.                                      | 74  |

| 3.13 | Comparison with state-of-the-art techniques [22], [2]                                | 74  |

| 4.1  | Memory configuration for the simulated STT-RAM device                                | 89  |

| 4.2  | Systems configuration for STT-RAM and DRAM                                           | 90  |

| 4.3  | Configuration of the memory cell                                                     | 105 |

| 4.4  | MTJ cell physical parameters                                                         | 106 |

| 4.5  | EXTENT vs. state-of-the-art techniques                                               | 107 |

|      |                                                                                      |     |

# **List of Figures**

| 1.1  | Histogram of data volume and future prediction                                              | 2  |

|------|---------------------------------------------------------------------------------------------|----|

| 1.2  | The von Neumann architecture and CPU-centric design approach [23]                           | 3  |

| 1.3  | Memory hierarchy: data movement from main memory to register files                          | 5  |

| 1.4  | Energy consumption of data movement (nJ) and comparison with AND operation [24]             | 5  |

| 1.5  | Energy consumption of data movement between memory hierarchy levels [25]                    | 6  |

| 1.6  | Relative energy of data movement for HPC benchmark [25]                                     | 6  |

| 2.1  | Schematic of a DRAM cell [26]                                                               | 14 |

| 2.2  | Schematic of an SRAM cell [2]                                                               | 15 |

| 2.3  | Schematic of an FLASH cell [27]                                                             | 16 |

| 2.4  | Schematic of an STT-RAM cell [28]                                                           | 17 |

| 2.5  | Schematic of an PCM cell and the state transition [29]                                      | 18 |

| 2.6  | Basic structures of RRAM and FeRAM cells [30,31]                                            | 20 |

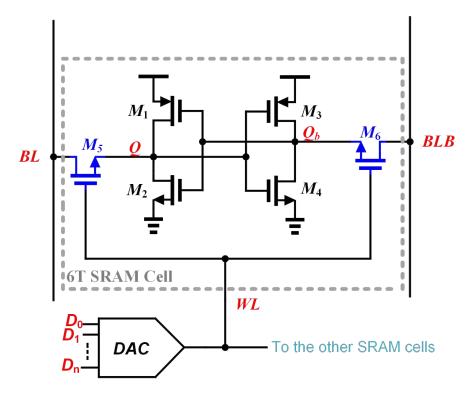

| 2.7  | PIM architecture and ReRAM crossbar for matrix–vector multiplication proposed by $[32]$     | 22 |

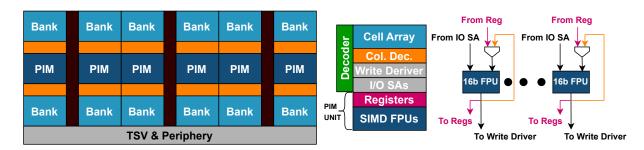

| 2.8  | HBM DRAM die organization with PIM unit and its data path, presented in [33] $$             | 24 |

| 2.9  | PIMCaffe system architecture by [34]                                                        | 28 |

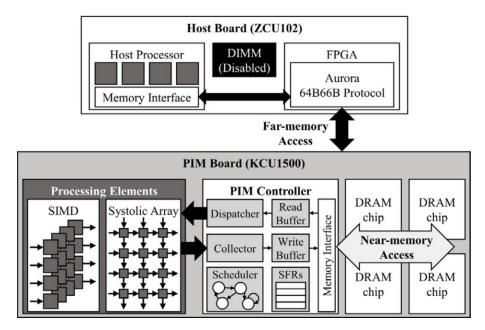

| 2.10 | Architecture the proposed UPMEM-based PIM simulator [35]                                    | 29 |

| 3.1  | Standard single bit 6T-SRAM memory cell                                                     | 32 |

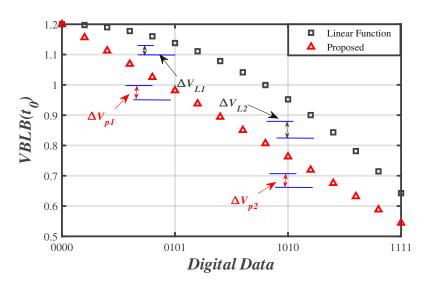

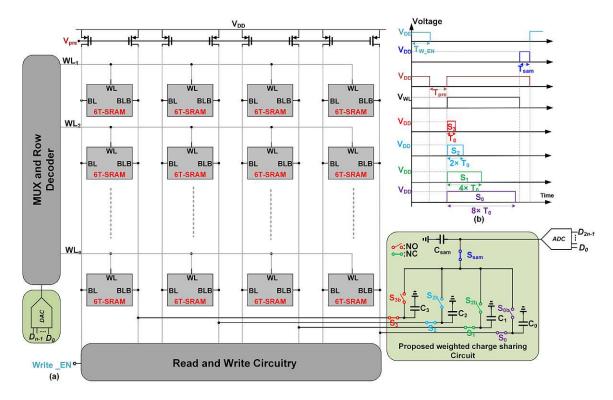

| 3.2  | Non-linear behavior of BLB voltage and effect of proposed linear root function technique $$ | 34 |

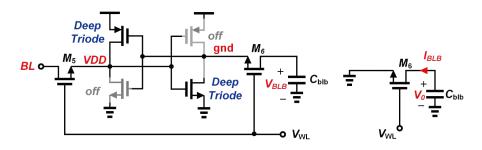

| 3.3  | Equivalent circuit diagram of discharge behavior of BLB                                     | 35 |

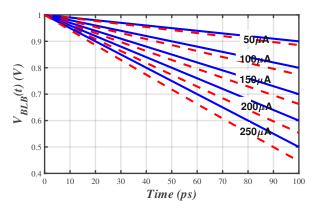

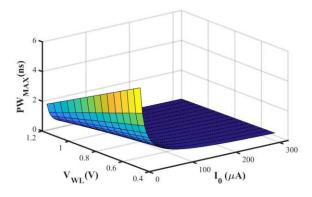

| 3.4  | discharge behavior of BLB (a), and 3D representation of $PW_{max},I_0,$ and $V_{wl}$ (b)    | 36 |

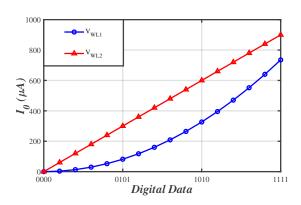

| 3.5  | $I_0$ versus digital data using equations 3.7 and 3.8                                       | 37 |

| 3.6  | SNR simulation based on Eq. 3.7 and, 3.8                                                    | 37 |

| 3.7  | In-Memory multiplication operation 4-bit $D_i n$ multiply by 4-bit $J_s$ digital data       | 39 |

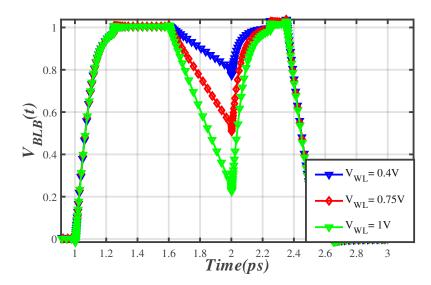

| 3.8  | Simulated $V_{BLB}(t)$ vs. time for different $V_{WL}$                                      | 41 |

| 3.9  | The worst-case standard deviation of our proposed analog multiplication                     | 41 |

|      |                                                                                             |    |

| 3.10 | Observation of the $V_{bulk}$ and the width of the transistor on $V_{TH}$                              | 43 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 3.11 | Body biasing effect on discharge of VBLB for a: [2] and for b: [22]                                    | 45 |

| 3.12 | The architecture of SMART, the body biasing is applied in the access transistor                        | 45 |

| 3.13 | The effect of SMART on state-of-the-art techniques                                                     | 46 |

| 3.14 | State-of-the-art in-SRAM multiplication design space                                                   | 47 |

| 3.15 | BLB discharge non-idealities                                                                           | 48 |

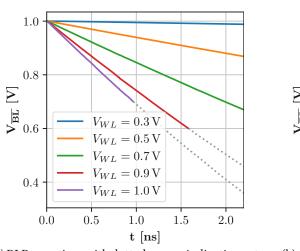

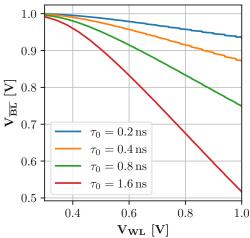

| 3.16 | Influence of PVT variations on the BLB discharge in TSMC 65 nm technology $\dots$                      | 49 |

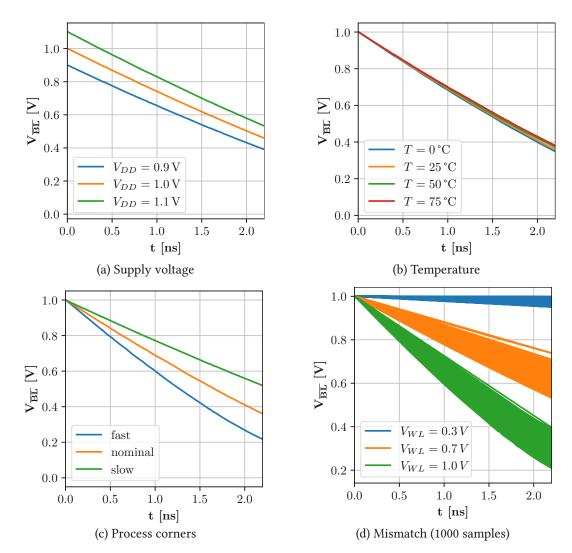

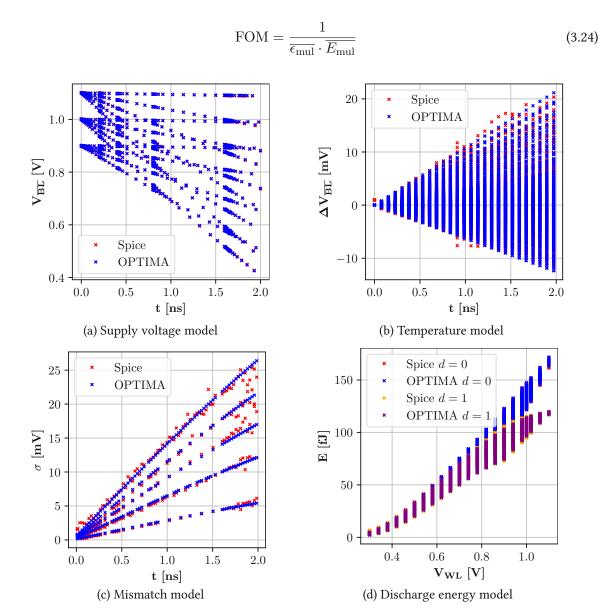

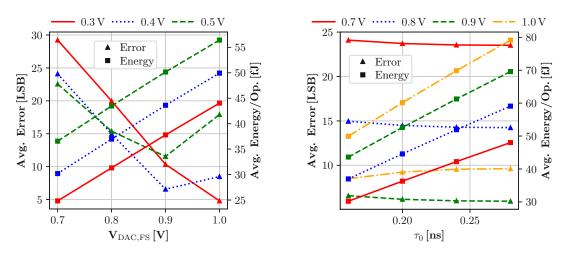

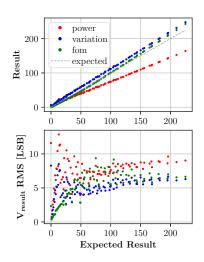

| 3.17 | OPTIMA discharge modeling evaluation                                                                   | 52 |

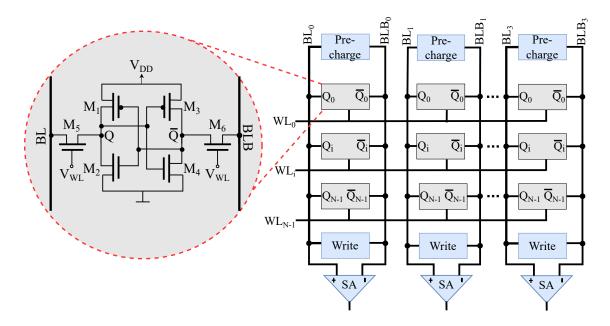

| 3.18 | 6T SRAM cell and SRAM array                                                                            | 53 |

| 3.19 | Design space corners simulations with OPTIMA for different values of $V_{\mathrm{DAC},0}$ with         |    |

|      | $	au_0=1.6\mathrm{s}$ (left) and $V_{\mathrm{DAC,FS}}$ with $V_{\mathrm{DAC,0}}=0.4\mathrm{V}$ (right) | 53 |

| 3.20 | Average multiplication results and analog standard deviations (left) as well as influence              |    |

|      | of voltage and temperature variations on the error (right) for the selected corners $$ . $$ .          | 54 |

| 3.21 | Conceptual ADC transfer function for E-MAC vs. state-of-the-art techniques [2, 22, 36]                 | 56 |

| 3.22 | (a) 6T-SRAM memory structure, and (b) equal large signal model during MAC operation                    | 59 |

| 3.23 | State-of-the-art BLB discharge behavior (a) non-linear [22, 36–38], and (b) linear tech-               |    |

|      | nique [2]                                                                                              | 59 |

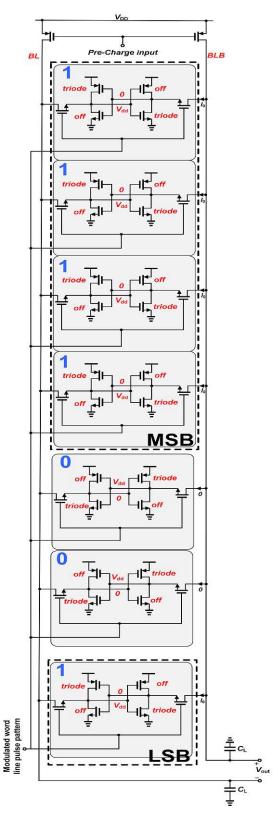

| 3.24 | Structure of the proposed 6T-SRAM PIM                                                                  | 61 |

| 3.25 | Large-signal model of circuits during MAC operations                                                   | 62 |

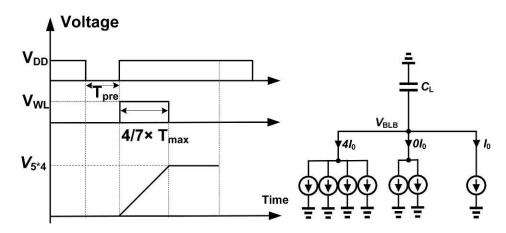

| 3.26 | Operand encoding scheme for MAC operation $(5 \times 4)$                                               | 64 |

| 3.27 | Discharge behavior during MAC operation $(5 \times 4)$                                                 | 65 |

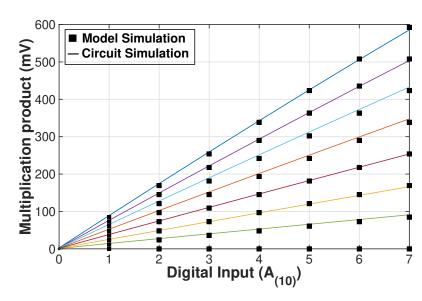

| 3.28 | The circuit results verify the accuracy of the proposed analytical model                               | 66 |

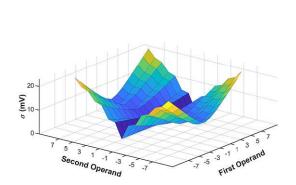

| 3.29 | STD and the cell area of the proposed circuit                                                          | 67 |

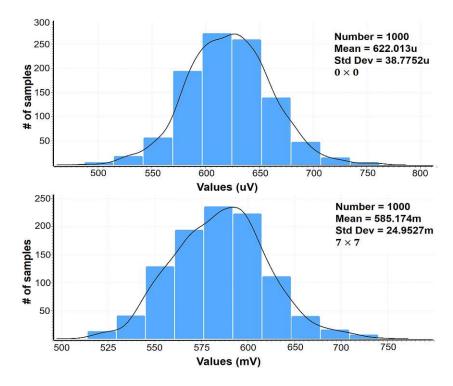

| 3.30 | MC simulation for 1000 points for both best $(0\times 0)$ and worst $(7\times 7)$ multiplications .    | 68 |

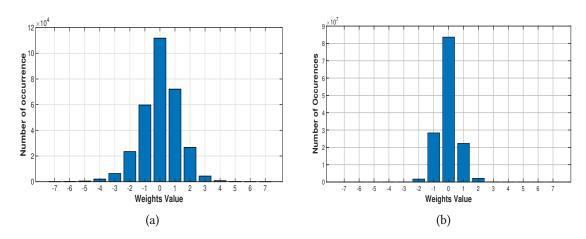

| 3.31 | (a) Histogram of the CNN weights, and (b) profiling of VGG16 weight distribution $ . $ . $ . $         | 69 |

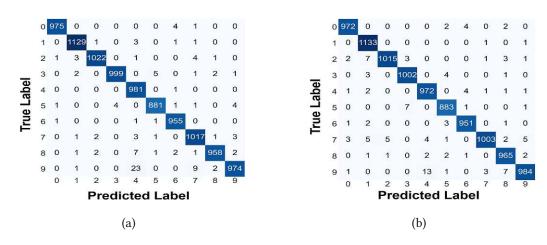

| 3.32 | Confusion matrix for the accelerated trained quantized CNN in (a) 8-bit and (b) 4-bit                  |    |

|      | number representations.                                                                                | 70 |

| 3.33 | MNIST dataset in two different number representation                                                   | 71 |

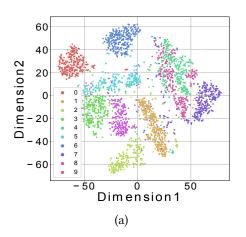

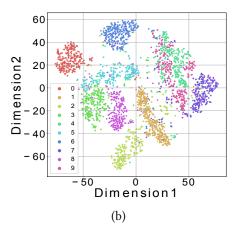

| 3.34 | T-SNE visualization of the MNIST dataset in (a) 8-bit and (b) 3-bit representation                     | 71 |

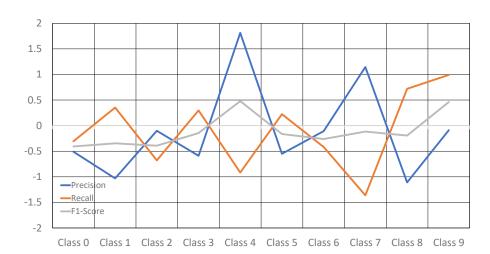

| 3.35 | Performance change for each metric.                                                                    | 72 |

| 3.36 | Combination of energy gain and performance metrics for VGG16 (Top1 and Top5)                           | 74 |

| 4.1  | Schematic representation of magnetic orientation and energy barrier between two MTJ                    |    |

|      | states [28]                                                                                            | 80 |

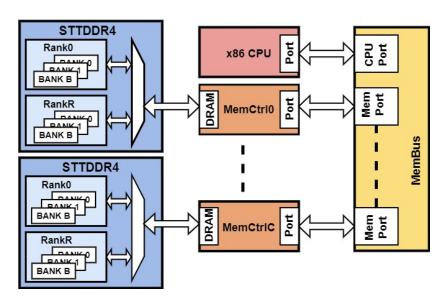

| 4.2  | The STTDDR4 Interface integration into the gem5 standard components library. Com-   |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | ponents in blue are modified or new to gem5, and components in white are unmodified |     |

|      | gem5 components                                                                     | 84  |

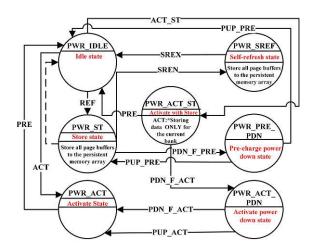

| 4.3  | Power state machine of STTDDR4 integration to gem5                                  | 85  |

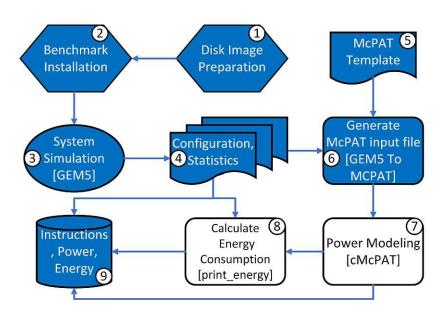

| 4.4  | An overview of HOPE framework, along with the contributions in blue                 | 90  |

| 4.5  | Architecture of the STT-RAM simulated system                                        | 91  |

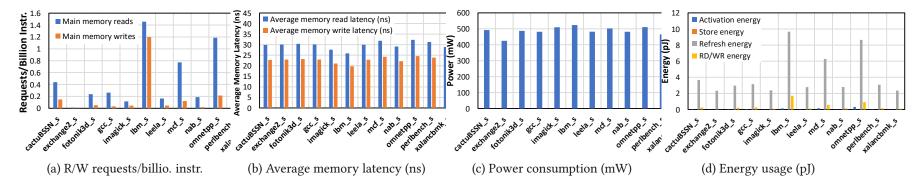

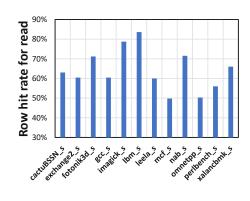

| 4.6  | STT-RAM evaluation metrics for different application                                | 95  |

| 4.7  | DRAM evaluation metrics for different application                                   | 95  |

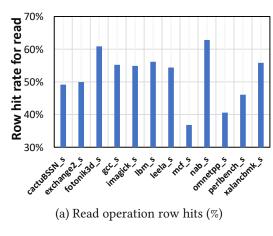

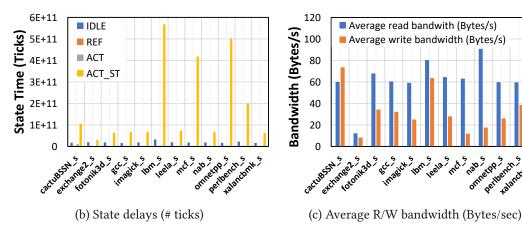

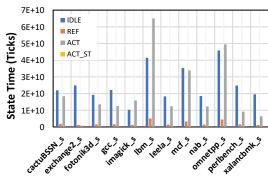

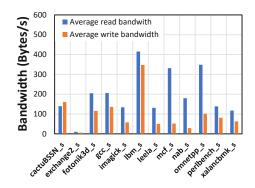

| 4.8  | STT-RAM row hits, state time, and bandwidth usage                                   | 96  |

| 4.9  | DRAM row hits, state time, and bandwidth usage                                      | 96  |

| 4.10 | STT-RAM stochastic write operation                                                  | 98  |

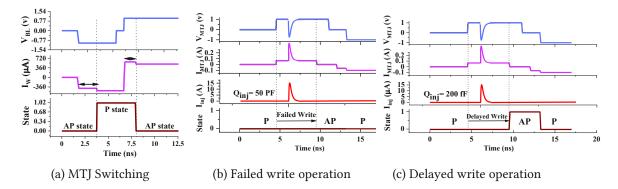

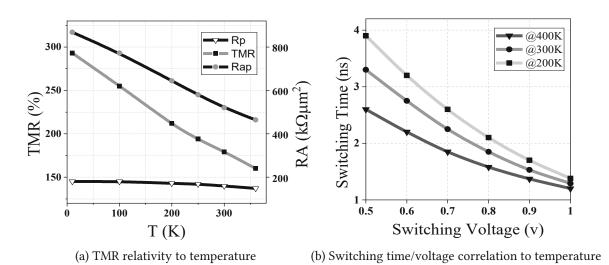

| 4.11 | STT-RAM stochastic write operation                                                  | 100 |

| 4.12 | Proposed architecture of write circuit                                              | 102 |

| 4.13 | Simulation waveform of different levels                                             | 106 |

| 4.14 | Normalized energy improvement compared to state of the art                          | 108 |

| 4.15 | Process and voltage variation effect                                                | 109 |

## Acronyms

| ADC | Analog-to-Digital Converter. xxii, 22, 34, 40, 48, 51, 56, 57, 58, |

|-----|--------------------------------------------------------------------|

|-----|--------------------------------------------------------------------|

63, 70

AxC Approximate Computing. 4

Bit Error Rate. 33, 34, 37, 38, 44

BER

BLBit-Line. iii, iv, vii, 5, 6, 15, 33, 34, 39, 47, 49, 50, 51, 57, 58, 60,

63, 66, 111

**BLB** Bit-Line-Bar. xxi, xxii, 33, 34, 35, 36, 37, 38, 39, 40, 41, 42, 47,

48, 49, 50, 51, 57, 58, 59, 63, 65, 67, 70

Computing In Memory. 21, 27

CIM

**CMOS** Complementary Metal-Oxide Semiconductor. xvii, 3, 12, 14,

20, 21, 25, 32, 40, 41, 42, 44, 47, 58, 65, 66, 67, 78, 107, 109

**CNN** Convolutional Neural Network. xviii, xxii, 21, 57, 68, 69, 70,

71, 72, 74, 112

CPU Central Processing Unit. 15, 23, 26, 29

**CVS** Clustered Voltage Scaling. 101

Digital-to-Analog Converter. 37, 38, 39, 44, 48, 51, 52, 56, 57,

DAC 112

DNN Deep Neural Network. xix, 21, 22, 26, 28, 47, 54, 55, 56, 68, 69,

70

DPU DRAM Processing Unit. 29

DRAM Dynamic Random Access Memory. xviii, xix, xxi, xxiii, 2, 11,

12, 14, 15, 18, 20, 22, 23, 24, 25, 26, 27, 29, 77, 78, 79, 80, 83, 85,

86, 87, 88, 89, 90, 93, 94, 95, 96, 98

**DVFS** Dynamic Voltage and Frequency Scaling. 101

Acronyms xxvi

DVS Differential Voltage Sampling. 63, 65

DVS Dynamic Voltage Scaling. 101

Ferroelectric Field Effect Transistor. 21, 22

**FeFET**

**FeRAM** Ferroelectric Random Access Memory. xxi, 19, 20

FL Fixed Layer. 80, 98 **FOM** Figure of Merit. 52

**FPGA** Field Programmable Gate Array. 4, 23, 28, 29

FPU Floating-Point Unit. 24

Graphics Processing Unit. 4, 21

**GPU**

High Bandwidth Memory. xxi, 23, 24, 25

**HBM**

HDC Hyperdimensional Computing. 21

**HMC** Hybrid Memory Cube. 23, 25

**HPC** High Performance Computing. xxi, 6, 83

HRS High Resistance State. 18, 19

International Data Corporation. 1, 2

IDC

**IMC** In-Memory Computation. 47, 51

IoT Internet of Things. vi

**IRDS** International Roadmap for Devices and Systems. 78

ISA Instruction Set Architecture. 79

Last Level Cache. 104

LLC

Low Resistance State. 18 LRS

Least Significant Bit. 33, 39, 44, 51, 54, 62 LSB

Multiplication and Accumulation. iv, viii, xvii, xviii, xix, xxii,

MAC 22, 32, 40, 41, 42, 43, 44, 45, 56, 57, 58, 59, 60, 61, 64, 65, 67, 111,

112

MC Monte Carlo. xxii, 40, 44, 54, 66, 67, 68, 109

MIM Metal-Insulator-Metal. 18, 20

ML Machine Learning. 4, 26

MLC Multi-Level Cell. 16, 17, 18

Acronyms xxvii

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor. xvii, 35,

42, 48, 56

**MPU** Memory Processing Unit. 27

**MRAM** Magnetoresistive RAM. 21

**MSB** Most Significant Bit. 33, 39, 44, 62

Magnetic Tunnel Junction. xix, xxii, 16, 17, 80, 81, 83, 98, 99, MTJ

101, 102, 103, 104, 105, 106, 109

**MVM** Matrix-Vector Multiplication. 25, 26

N-channel Metal-Oxide-Semiconductor. 36, 42, 43, 58, 61, 101,

**NMOS** 105

NN Neural Network. 23, 24, 56

NoC Network-on-Chip. 22

NVM Non-Volatile Memory. iv, vii, 5, 8, 11, 12, 14, 17, 18, 19, 25, 78,

79, 82, 83, 87

NVMe Non-Volatile Memory Express. 4

Operating Systems. 23, 79, 88, 89

OS

Phase Change Memory. xxi, 17, 18, 78

**PCM**

PE Processing Element. 11

PIM Processing in Memory. iii, iv, vi, vii, xvii, xxi, xxii, 3, 4, 5, 6, 7,

8, 9, 11, 12, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 32, 33, 46, 47,

56, 57, 61, 65, 88

**PMOS** P-channel Metal-Oxide-Semiconductor. 100, 105

PuM Processing using Memory. 23

PV Process Variation. 100

**PVT** Process, Voltage, and Temperature. xxii, 5, 8, 32, 46, 47, 48, 49,

52, 53

PW Pulse Width. 33, 35, 36, 39, 40, 42, 44

**PWM** Pulse Width Modulation. 60

**PZT** Lead Zirconate Titanate. 19, 20

Resistive Random Access Memory. xxi, 21, 22

ReRAM

ResNet Residual Network. 21

Acronyms xxviii

RL Rotation Layer. 80, 98 **RMS** Root Mean Square. 51

RNN Recurrent Neural Network. 21

RRAM Resistive RAM. xxi, 12, 14, 16, 18, 19, 20, 25, 27

Strontium Bismuth Tantalate. 19

SBT

SEU Single-Event-Upset. 20

**SIMD** Single Instruction Multiple Data. 24, 29 **SIMT** Single Instruction Multiple Threads. 27

SLC Single-Level Cell. 15, 17

Signal to Noise Ratio. xxi, 37, 38, 44, 48 **SNR**

SoC System-on-Chip. 18

**SRAM** Static Random Access Memory. iii, iv, vii, viii, xvii, xviii, xix,

xxi, xxii, 5, 6, 7, 8, 9, 11, 12, 14, 15, 19, 20, 21, 25, 32, 33, 34, 35,

38, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49, 51, 53, 54, 55, 56, 57,

58, 59, 61, 63, 65, 66, 67, 72, 74, 75, 78, 98, 111, 112, 113

STD Standard Deviation. xxii, 67

STT-RAM Spin Transfer Torque Random Access Memory. iii, iv, vi, vii,

> viii, xviii, xix, xxi, xxiii, 5, 6, 7, 8, 9, 11, 12, 14, 16, 17, 18, 20, 21, 25, 77, 78, 79, 80, 81, 82, 83, 84, 85, 86, 87, 88, 89, 90, 91, 92, 93, 94, 95, 96, 97, 98, 99, 100, 101, 102, 103, 104, 105, 106, 107,

108, 109, 110, 111, 112, 113

Thermal-Controlled Magnetic Anisotropy. 97

**TCMA**

Tunnel Magnetoresistance Ratio. 82, 99, 100, 106, 108 **TMR**

TPU Tensor Processing Unit. 4

**TSF** Thermal Stability Factor. 98

**TSMC** Taiwan Semiconductor Manufacturing Company. xxii, 27, 49

**TSV** Through Silicon Via. 23

Voltage-Controlled Magnetic Anisotropy. 100

**VCMA**

VM Volatile Memory. iv, vii, 5, 6, 8, 12

Write Error Rate. 98, 100, 104

**WER**

Acronyms

xxix

TU **Bibliothek**, Die approbierte gedruckte Originalversion dieser Dissertation ist an der TU Wien Bibliothek verfügbar.

The approved original version of this doctoral thesis is available in print at TU Wien Bibliothek.

WL

Word-Line. iv, viii, xvii, xxi, 33, 34, 35, 36, 37, 38, 39, 40, 41,  $42,\,44,\,47,\,48,\,49,\,50,\,51,\,56,\,58,\,60,\,62,\,63,\,112$

## Chapter 1

## Introduction

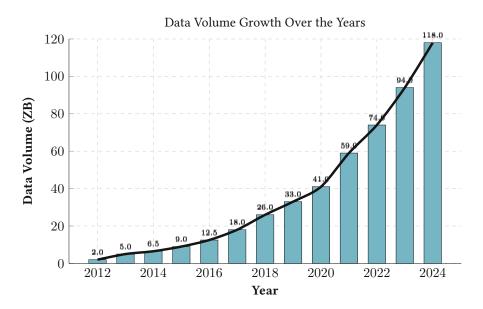

We are currently navigating through an era overwhelmed by an unprecedented surge in data from diverse sources. Recent findings highlight that Google processes 3.5 billion searches daily, resulting in over 2.5 quintillion bytes of data. Concurrently, projections from Dell EMC suggest a doubling of global data every two years, with expectations of reaching 40,000 Exabytes (trend depicted in Fig. 1.1, a phenomenon widely recognized as Big Data within the scientific community [39].

From an economic perspective, International Data Corporation (IDC) forecasts underscore Big Data's growing significance as a revenue generator. Specifically, the global market value of Big Data and business analytics rose by over 50% from \$122 billion in 2015 to \$187 billion in 2019 [40]. However, understanding Big Data necessitates examining its technological foundations, historical development, and the challenges posed by its voluminous growth. The primary challenge lies in storing, managing, and computing the vast quantities of data efficiently, as depicted in Fig. 1.1.

Big Data encompasses massive, varied datasets that often exceed the capabilities of traditional computing systems. According to the Gartner dictionary, Big Data is characterized by its volume, velocity, and variety. However, current systems fall short in efficiently storing, analyzing, and visualizing this data, which significantly hampers the ability to support decision-making processes. As a result, the scientific community continues to face challenges in extracting meaningful insights from this wealth of data.

Big Data's influence extends across diverse domains, including business, management, and research, where it has revolutionized numerous sectors. Its applications span global economies, healthcare, retail, manufacturing, astronomy, environmental science, and large-scale e-commerce. This extensive usage highlights the pressing need for advanced computing systems capable of effectively managing and processing such vast datasets.

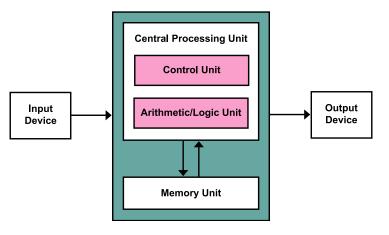

The rapid growth of data volumes, propelled by Big Data, has exposed critical limitations in tra-

Figure 1.1: Histogram of data volume and future prediction

ditional computing architectures, particularly the von Neumann architecture. This processor-centric model, also known as the Princeton model, has served as the foundation for computer systems for decades [41]. However, its design, which necessitates significant data movement between memory and the CPU, proves inefficient for large-scale data processing. The von Neumann model consists of essential components, including a processing element with an arithmetic logic unit, processor registers, memory for storing data and instructions, external mass storage, and input/output mechanisms, all interconnected via a shared bus [42]. Fig. 1.2 illustrates this architecture.

Main memory plays a pivotal role in nearly all digital systems, from data centers and clouds to mobile devices and healthcare systems. Despite advancements, modern applications demand faster and more efficient data analysis. A study by IDC projects global data to surpass 100 ZB. However, memory bandwidth limitations remain a significant bottleneck [25, 43-48]. This bottleneck arises due to two primary factors: the processor-centric design and the memory wall. The former involves substantial data movement between memory and the CPU, while the latter highlights the challenges in developing high-capacity, low-latency, and cost-effective memory technologies [49–53].

Over the past decade, the data demands of applications such as Big Data, genome detection, and pattern recognition [49,54] have intensified, requiring extensive real-time or offline data transfer. To address these challenges, novel hardware accelerators tailored for data-centric applications have emerged. These accelerators leverage distributed memory systems and parallel processing architectures, emphasizing the importance of reliable memory modules [55, 56].

Scaling down charge-based memory technologies such as Dynamic Random Access Memory (DRAM) and flash has exacerbated these challenges. As these technologies approach smaller nodes, issues

Figure 1.2: The von Neumann architecture and CPU-centric design approach [23]

like increased leakage power, reduced reliability, and higher costs become prominent [57, 58]. Similarly, Complementary Metal-Oxide Semiconductor (CMOS) downscaling faces limitations, further compounding the energy and reliability challenges [59]. These scaling constraints emphasize the urgent need for innovative memory architectures to overcome the memory wall.

Among the proposed solutions, Processing in Memory (PIM) has emerged as a particularly promising approach. By performing computations directly within memory, PIM minimizes data movement and significantly reduces energy consumption [60]. Studies reveal that PIM can reduce energy consumption by up to 49.1% and improve performance by 44.6% compared to traditional architectures [61]. This positions PIM as a viable solution for handling the growing demands of Big Data applications.

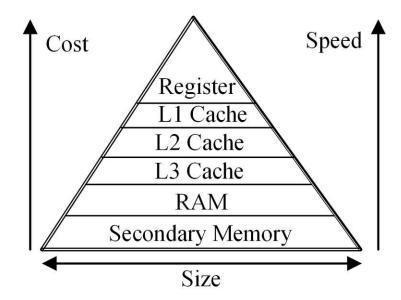

At the micro-architecture level, contemporary computing systems face three critical challenges [41]: the memory wall, parallel processing limitations, and the power wall. The memory wall arises from the latency and bandwidth gap between memory and processors, while the complexity of parallel programming and data management limits multi-core utilization. The power wall, stemming from thermal constraints and power dissipation, restricts further frequency scaling. Together, these challenges emphasize the need for innovative approaches to reduce data movement and enhance system efficiency.

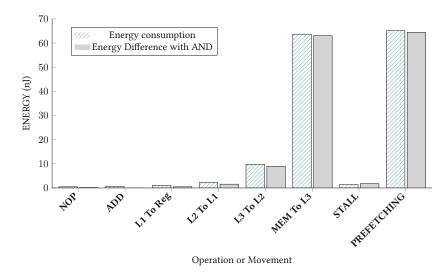

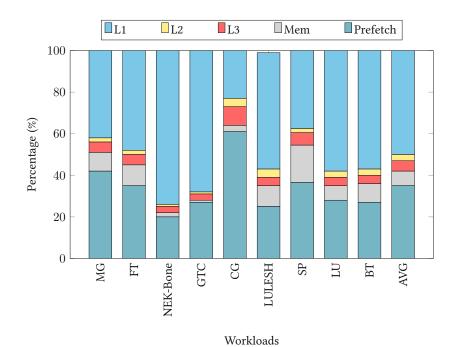

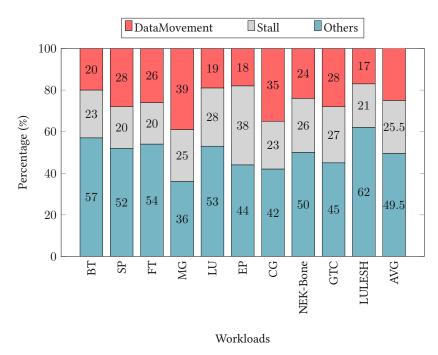

Studies, such as [24], provide valuable insights into the energy and latency costs associated with data movement (see Fig. 1.4, 1.5, and 1.6) By using microarchitecture benchmarks with high memory access footprints, they quantitatively analyze energy consumption for various operations, revealing that data movement accounts for a significant portion of energy use. Similarly, research highlights PIM's potential to address these inefficiencies, particularly in embedded devices where data movement constitutes over 67.5% of energy consumption [25].

To address the memory wall and the associated data challenges, several forward-thinking strategies have been proposed:

- 1. **Process In Memory (PIM):** This approach eliminates data transfer by processing data directly within memory, making it ideal for real-time analytics and large datasets [22, 60, 62].

- 2. Approximate Computing (AxC): By accepting controlled inaccuracies, AxC reduces energy consumption and speeds up processing [50,63-66].

- 3. Non-Volatile Memory Express (NVMe) and Storage-Class Memory: These technologies enhance performance by merging memory speed with storage permanence [67, 68].

- 4. Hardware Accelerators (Graphics Processing Units (GPUs), Field Programmable Gate Arrays (FPGAs), Tensor Processing Units (TPUs)): Specialized hardware accelerates tasks like machine learning and simulations [69].

- 5. Distributed and Edge Computing: This paradigme reduces latency by processing data closer to its source or across multiple machines [70].

- 6. Quantum Computing: Leveraging qubits, quantum systems promise unparalleled processing speeds [71,71].

- 7. 3D Stacking and Advanced Packaging Technologies: These technologies improve communication between components, mitigating the memory wall [72].

While techniques such as AxC and hardware accelerators have been explored, they come with limitations. AxC sacrifices accuracy for energy efficiency, which may not suit all applications [63]. Hardware accelerators, although efficient, require complex programming models. In contrast, PIM offers a scalable and generalized solution, reducing energy and latency by minimizing data movement between processor and memory [60]. Consequently, this thesis focuses on PIM-based solutions for overcoming traditional memory architecture limitations. By leveraging both volatile and non-volatile memory technologies, we aim to address critical challenges such as energy efficiency and latency, pushing the boundaries of data processing efficiency.

#### **Problem Motivation** 1.1

Modern data-centric applications, such as Machine Learning (ML) and real-time analytics, demand high-performance memory solutions that can overcome the limitations of traditional memory hierarchies, often referred to as the "memory wall." Conventional architectures struggle to support the large volumes of data required for these applications, leading to significant latency and energy inefficiencies due to frequent data movement between memory and processing units. This challenge drives the exploration of PIM techniques, where computations occur closer to the data, minimizing the bottlenecks associated with conventional memory systems. Consequently, selecting effective PIM-compatible memory technologies is crucial to achieving both performance and energy efficiency improvements.

1.1. Problem Motivation 5

Figure 1.3: Memory hierarchy: data movement from main memory to register files

Figure 1.4: Energy consumption of data movement (nJ) and comparison with AND operation [24]

This thesis explores Static Random Access Memory (SRAM) as a promising candidate for volatile memory and Spin Transfer Torque Random Access Memory (STT-RAM) as a suitable choice for Non-Volatile Memory (NVM) in PIM architectures, addressing the unique challenges and benefits each offers.

SRAM-based systems present key advantages as Volatile Memory (VM) due to their high read/write speeds and reliability, which makes them ideal for applications demanding fast data retrieval and high processing throughput in real-time. However, conventional SRAM-based computing faces nonlinearities and Process, Voltage, and Temperature (PVT) variations that can degrade performance in PIM applications. This thesis proposes solutions such as the OPTIMA framework, which models Bit-Line (BL) discharge behavior in 6T-SRAM, enhancing design-space exploration for in-memory multipliers. Further, techniques like AID [2] and EMAC [3] have been introduced to address accuracy limitations by

Figure 1.5: Energy consumption of data movement between memory hierarchy levels [25]

Figure 1.6: Relative energy of data movement for High Performance Computing (HPC) benchmark [25]

tackling BL non-linearities, thereby improving energy efficiency and computational precision. These contributions position SRAM as a viable PIM solution that aligns with the high-performance demands of VM applications in data-centric workloads.

STT-RAM, with its non-volatility, high density, and low leakage power, represents an advantageous alternative for non-volatile memory in PIM. Despite these benefits, challenges such as high write energy and latency have historically limited STT-RAM's industrial adoption. This thesis addresses these issues

through a dual approach: first, by developing the HOPE framework, an open-source STT-RAM memory controller that enables accurate performance and energy evaluation within the gem5 simulator; and second, by proposing approximation techniques to reduce write energy and latency. These methods exploit the stochastic switching behavior of STT-RAM cells, achieving significant energy and latency reductions, and enabling reliable integration of STT-RAM in PIM applications. By improving write efficiency, this work establishes STT-RAM as a promising NVM candidate for PIM, balancing energy efficiency with the endurance required for data-intensive applications.

The complementary qualities of SRAM and STT-RAM in PIM applications provide a robust foundation for addressing the diverse memory requirements of modern computing systems. While SRAM delivers the speed and precision needed for high-frequency operations, STT-RAM offers energy-efficient, persistent storage, essential for applications that demand both immediate data access and non-volatility. By exploring these technologies in parallel, this thesis contributes to a more nuanced understanding of PIM's potential, aiming to overcome the memory wall through targeted enhancements in both volatile and non-volatile memory domains. Together, SRAM and STT-RAM offer a path towards scalable, efficient, and reliable PIM systems suited to the next generation of data-centric applications.

#### **Research Questions and Objectives** 1.2

Building upon the challenges posed by the rapid expansion of data, architectural bottlenecks, and inefficiencies in current memory systems, this thesis aims to explore innovative memory-centric solutions. The primary focus is on the application of PIM techniques, leveraging both STT-RAM and SRAM technologies to overcome the memory wall. The research questions guiding this work are:

- 1. What are the key reliability challenges faced by STT-RAM and SRAM in PIM-based architectures, and how can these be mitigated?

- Both volatile and non-volatile memory technologies present distinct reliability issues, such as write errors in STT-RAM and non-linearity in SRAM-based computations. The objective of this thesis is to investigate these problems and develop hardware-level solutions to enhance the reliability and overall robustness of PIM systems.

- 2. How can STT-RAM-based PIM systems be analyzed for performance, power, and energy consumption before deployment?

Towards this the objective is to develop an open-source framework for evaluating power, latency, and energy characteristics of STT-RAM-based PIM architectures under real workloads. It will integrate analytical modeling, simulations, and empirical validation to assess system efficiency prior to deployment.

3. How to optimize the energy consumption and latency of STT-RAM write operations without compromising the reliability?

Towards this, the objective is to investigate approximation-oriented techniques in STT-RAM that exploit its inherent stochastic switching behavior to enable energy-efficient write operations while ensuring system-level reliability.

4. How to perform a fast design space exploration that can efficiently analyze energy consumption latency, and accuracy in a discharge-based in-SRAM computing circuits, while accounting for PVT variations?

Towards this, the objective is to develope a modeling framework designed to accelerate designspace exploration for discharge-based in-SRAM computing circuits that enables efficient trade-off analysis by providing fast and accurate evaluation of energy, latency, and accuracy while incorporating the impact of PVT variations.

#### Structure of the Thesis 1.3

This thesis addresses the research questions and challenges outlined in section 1.2, presenting original contributions to the fields of STT-RAM and SRAM technologies as candidates for PIM architectures. The thesis is organized into four main chapters:

Chapter 2 provides a review of the state-of-the-art approaches in memory technology, focusing on both NVM and VM options. This literature review establishes the foundational context for the thesis, examining the key characteristics, limitations, and opportunities within STT-RAM and SRAM technologies relevant to PIM applications.

Chapter 3 discusses SRAM as a promising VM candidate for PIM applications, highlighting the work conducted to mitigate non-linearity issues inherent in SRAM-based computations. This chapter presents methods such as the OPTIMA framework [1] for modeling SRAM discharge behavior, as well as the AID [2] and EMAC [3] techniques, which are developed to improve the accuracy, energy efficiency, and reliability of in-SRAM computation.

In Chapter 4, we focus on addressing STT-RAM write errors, energy, and latency. We propose a novel optimization technique that leverages stochastic switching and circuit-level approximations to reduce write energy and latency while enhancing robustness against soft errors, process variations, and write error reliability challenges [5]. In addition to this, we present a modeling and benchmarking framework for STT-RAM-based systems, integrating an extendable STT-RAM memory controller into

the gem5 simulator. This framework enables the design and evaluation of STT-RAM architectures, analyzing power, latency, and throughput before deployment.

Finally, Chapter 5 draws together the findings from the previous chapters, summarizing the contributions of this research to the fields of memory technology and PIM. This chapter also explores future research directions, offering insights into potential improvements and further studies that could extend the work on STT-RAM and SRAM technologies within advanced computing architectures.

## Chapter 2

# **Background and Related Work**

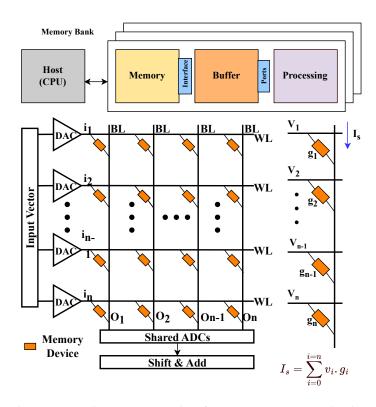

To address data movement overhead in memory-centric applications, advanced memory technologies have enabled closer integration of memory and processing units, leading to the concept of PIM. PIM mitigates data movement overhead between memory and processing units, thereby reducing latency and energy consumption. This is achieved by integrating computational elements within or near memory, such as in-memory ICs, 3D-stacked layers, memory controllers, or processor caches [73].

PIM methodologies can be categorized into two types: (1) architectures where memory chips execute basic operations and (2) designs where data is loaded from memory into adjacent processing elements (Processing Elements (PEs)) for computation. Although PIM concepts are not new, past efforts faced obstacles such as the complexity of integrating processing and memory elements on a single chip and the limited benefits of reducing memory access overhead for workloads with relatively small working sets (e.g., early database queries or embedded system applications).

With the development of 3D-stacked technology, PIM architectures have gained renewed interest across various application domains. This thesis categorizes recent PIM approaches into three groups: (a) modifying traditional memory technologies (e.g., DRAM, SRAM, NVMs) to enable basic computations, (b) enhancing memory controllers with computational capabilities, and (c) 3D-stacked architectures that integrate multiple processing and memory components on a single chip. This work specifically focuses on advancing digital in-STT-RAM and analog-based in-SRAM PIM architectures (category a), aiming to improve energy efficiency and computation accuracy. These two memory types were selected due to their potential for non-volatility and high-density storage (STT-RAM) and their ability to support fast, in-memory analog computations (SRAM), making them promising candidates for energy-efficient and scalable PIM solutions.

#### **Different Memory Technologies** 2.1

Before discussing the state-of-the-art PIM techniques, it is critical to first analyze memory technologies concerning power, energy, and latency. Understanding these attributes helps system designers tailor their choices to application demands. Table 2.1 compares key factors such as endurance, read/write energy, latency, and CMOS compatibility, with insights from literature [7-21]. The selection of memory for PIM must balance speed, endurance, and power efficiency to ensure feasibility. While volatile memories offer high-speed access, they require continuous power, whereas non-volatile memories provide data retention but often suffer from higher latency and limited endurance.

Broadly, memory technologies fall into two categories:

- 1. Volatile memories (VMs): These require power to retain data and are primarily used for temporary storage in fast-access applications. SRAM and DRAM are the dominant types, offering low latency and high-speed operation. As shown in Table 2.1, SRAM has the lowest read/write latency (<5 ns) and the highest endurance (1016 cycles), making it ideal for cache memory and high-performance computing. However, its large cell size (>100  $F^2$ ) limits its scalability. DRAM provides a smaller cell size  $(4-12 F^2)$  and similar latency ( $\approx 2-5$  ns), making it more area-efficient. However, due to its need for periodic refresh operations, DRAM consumes significant power, reducing its suitability for energy-constrained PIM applications [74]. The high access speed of VM makes it well-suited for in-memory computing, but its volatility limits long-term data storage.

- 2. Non-volatile memory (NVM): NVM retains data without power and is commonly used for persistent storage. Table 2.1 highlights key NVM types such as flash, STT-RAM, PCMRAM, and Resistive RAM (RRAM), each with distinct trade-offs. Flash memory, widely used in SSDs and storage devices, offers high density but suffers from excessive write latency (500 µs) and limited endurance (10<sup>6</sup> cycles), making it unsuitable for frequent memory operations. Emerging NVM technologies, such as PCMRAM and RRAM, exhibit better endurance ( $10^{10}$ – $10^{12}$  cycles) but still suffer from higher write latencies (>30 ns). In contrast, STT-RAM balances non-volatility, high endurance (10<sup>16</sup> cycles), and moderate latency (5–20 ns), approaching DRAM-like speeds without requiring refresh power. Furthermore, STT-RAM has a lower write energy (0.1–2.5 pJ) compared to PCMRAM (18 pJ), making it a more energy-efficient alternative. These attributes make STT-RAM a strong candidate for digital PIM, whereas SRAM remains the preferred choice for analog in-memory computing due to its ultra-fast access speed and high endurance. Continued advancements in NVM aim to further optimize speed, energy efficiency, and endurance, making these technologies increasingly viable for PIM applications [8].

Table 2.1: Comprehensive comparison of different memory technologies [7–21]

| Characteristic     | STT-RAM                                 | PCMRAM    | RRAM       | Fe-FET           | FLASH               | SRAM      | DRAM        |

|--------------------|-----------------------------------------|-----------|------------|------------------|---------------------|-----------|-------------|

| Non-volatility     | +                                       | +         | +          | +                | +                   | -         | -           |

| Data Retention     | 10                                      | 10        | 10         | 10               | 10                  | -         | -           |

| (years)            |                                         |           |            |                  |                     |           |             |

| Cell Endurance     | $10^{16}$                               | $10^{12}$ | $10^{10}$  | $10^{12}$        | $10^{6}$            | $10^{16}$ | $10^{15}$   |

| (cycles)           |                                         |           |            |                  |                     |           |             |

| Cell Size $(F^2)$  | 6-20                                    | 4-8       | 4          | 4-8              | 4-6                 | >100      | 4-12        |

| Technology node    | 45                                      | 65        | 40         | 5                | 15                  | 10        | 32          |

| (nm)               |                                         |           |            |                  |                     |           |             |

| Read Latency (ns)  | 2-20                                    | 20-50     | <10        | 10               | $25x10^{3}$         | <5        | 2           |

| Write Latency (ns) | 5-20                                    | 30        | 5          | 10               | $500 \text{x} 10^3$ | <5        | 5           |

| Erase Latency (ns) | 5-20                                    | 30        | 10         | 10               | 2 ms                | <5        | 5           |

| Write Energy (pJ)  | 0.1-2.5                                 | 18        | 0.1        | 1                | 0.1 - 1             | <0.1      | <0.1        |

| Erase Energy (pJ)  | 1                                       | 18        | 0.1        | 1                | $10^{3}$            | <1        | <1          |

| Suppliers          | uppliers Toshiba, Samsung, Intel, Panas |           | Panasonic, | Globalfoundries, | Micron,             | Qualcomm, | Samsung, Sk |

|                    | Hitachi                                 | WD, IBM   | Micron     | FMC              | Samsung             | Intel     | Hynix       |

Figure 2.1: Schematic of a DRAM cell [26]

## **DRAM Memory Technology:**

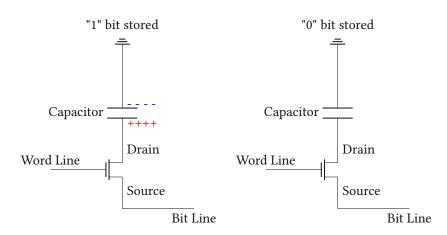

DRAM has been a cornerstone of computational systems for decades, originally introduced by Robert H. Dennard et al. [75]. The development of DRAM continues to advance, particularly with the advent of new CMOS fabrication technologies that push toward smaller feature sizes, now reaching 10nm and smaller, as highlighted in recent study [76]. At its core, a DRAM cell features a simple yet effective 1T1C (one transistor and one capacitor) structure (see Fig. 2.1, more details in [26]).

One of the DRAM's key advantages is its bit cell's architecture, which achieves high storage density due to minimal area requirements per cell. This efficiency results in compact DRAM cell sizes, recently achieving dimensions as small as  $4F^2$  [77]. However, DRAM's design is not without its drawbacks. The primary issue lies in charge leakage from the tiny capacitors used to store bit states, necessitating regular refresh cycles to retain data. These refresh cycles, inherent to both maintenance and read operations (as reading a DRAM cell discharges the capacitor, requiring a restore operation afterward), are significant energy consumers. Studies indicate that refresh operations can account for over 20% of a DRAM device's total energy consumption [78,79].

Moreover, DRAM's performance speed lags behind that of SRAM and various NVMs. Comparative analyses (see Table 2.1) reveal that SRAM, STT-RAM, and RRAM all significantly outpace DRAM, with speed improvements by a factor of up to 50 in read and write latencies [80].

## **SRAM Memory Technology:**

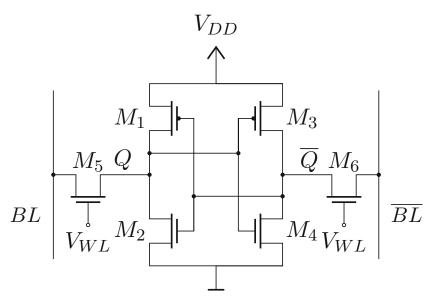

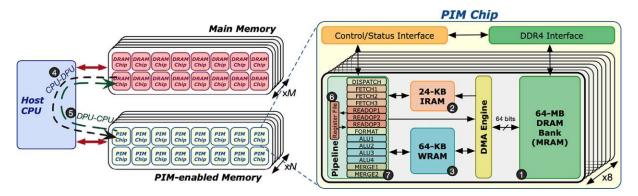

SRAM, a staple in electronic devices since the 1960s, offers a distinct approach to data storage without relying on capacitors. As depicted in Fig. 2.2, a standard SRAM cell consists of six transistors. The data storage mechanism involves two cross-coupled inverters (formed by transistors  $M_1, M_2, M_3, M_4$ ), which enable the cell to maintain its state as long as power is supplied. Transistors  $M_5$  and  $M_6$  serve

Figure 2.2: Schematic of an SRAM cell [2]

as gateways for reading and writing operations.

For read operations, activating at least one access transistor suffices, but leveraging both—alongside precharged BLs—can enhance the speed, as demonstrated in recent advancements [81]. Write operations, on the other hand, necessitate aligning the new data bit with both BLs: the direct bit value with the true BL and its complement with the inverted line. Pre-charging the BLs has also been shown to optimize write performance [82].

While SRAM cells outpace DRAM in terms of read and write speeds, they come with the trade-off of larger cell sizes. This results in lower memory density and higher production costs. Given these characteristics, SRAM's use is predominantly reserved for cache memory and register files within Central Processing Units (CPUs), where its rapid access times justify the limited memory capacity and higher expense.

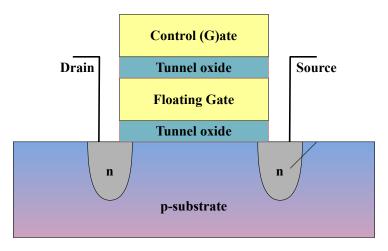

## **FLASH Memory Technology:**

Flash memory, invented by Masuoka in the late 1980s [83], is a durable, non-volatile storage medium widely used in electronic devices. It is composed of arrays containing numerous flash cells, each based on a floating gate transistor mechanism. These transistors utilize a control gate and a floating gate to manage the charge within the floating gate, as illustrated in the referenced Figure 2.3. Electrons are introduced to or removed from the floating gate through a process known as Fowler-Nordheim tunneling [84], which alters the transistor's threshold voltage  $(V_{th})$ . This alteration defines the cell states in Single-Level Cell (SLC) flash memory, distinguishing between the binary '1' and '0' through different  $V_{th}$  levels.

The enduring nature of flash memory stems from its ability to maintain the charge in the floating gate, ensuring data retention even without power. The memory is 'programmed' by charging the floating gate, and it can be 'erased' by applying an inverse voltage, clearing the stored data.

Flash memory comes in two main types: NOR and NAND. NAND flash is preferred for its higher storage capacity despite NOR flash's faster read capabilities. Erasing data in NAND flash affects entire blocks, necessitating a sequence of steps for rewriting data: identifying a free block, erasing it, transferring modified data from the old to the new block, and then marking the old block as free.

Moreover, flash memory supports Multi-Level Cells (MLCs), which store multiple bits per cell through various threshold voltage levels, enhancing storage density. Despite its benefits, flash memory's drawbacks include slower read/write speeds, limited cell lifespan due to wear from erasing cycles, and higher energy consumption for writing compared to technologies like STT-RAM or RRAM.

Figure 2.3: Schematic of an FLASH cell [27]

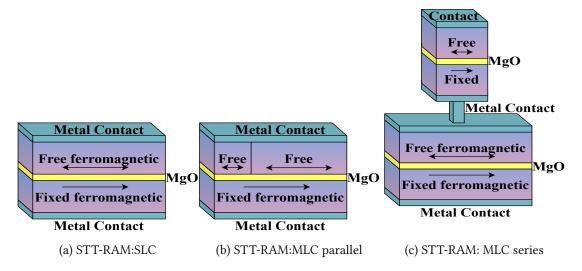

## **STT-RAM Memory Technology:**

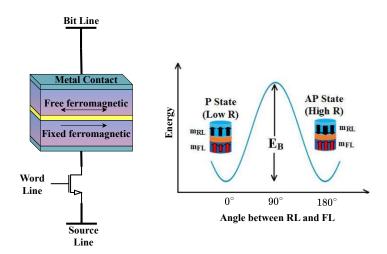

STT-RAM is a durable memory technology that relies on magnetic layers to store data [85]. Inside each STT-RAM cell is a component known as the Magnetic Tunnel Junction (MTJ), comprising a fixed magnetic layer, a non-magnetic barrier, and a free magnetic layer. The fixed layer's magnetic direction stays constant, while the direction of the free layer can be altered during operation. These layers are typically constructed using cobalt-iron-boron (CoFeB) for the magnetic parts and magnesium oxide (MgO) for the barrier, as noted in the referenced material. The MTJ's resistance varies depending on whether the magnetic layers align; it's lower when they match and higher when they oppose. This resistance variation encodes the bit's state in the cell [86-88].

A key benefit of STT-RAM is the compact size of its MTJ elements, which can be as small as six times the feature size squared  $(6F^2)$ . This small footprint allows for densely packed memory cells. For even

greater densities, MLC configurations are used, involving at least two STT-RAM cells arranged either in parallel or in series. A SLC setup is depicted in Fig. 2.4a, while parallel and serial MLC arrangements are illustrated in Figs. 2.4b and 2.4c, respectively. In MLC designs, the size variation of the free layers (in parallel arrangements) or the entire MTJ stack (in serial arrangements) is crucial. Larger magnetic layers require more current to alter their magnetic direction than smaller ones. This size-dependent change in resistance helps distinguish between the different levels in MLCs during readout processes [68,88].

Figure 2.4: Schematic of an STT-RAM cell [28]

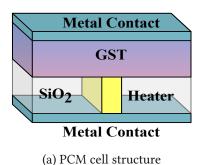

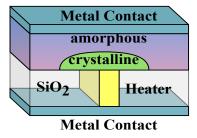

## Phase Change Memory (PCM) Memory Technology:

PCM is a NVM technology that utilizes chalcogenide glass, typically composed of germanium, antimony, and tellurium (Ge2Sb2Te5 or GST), to store data [89, 90]. This material can switch between crystalline and amorphous states when heated, a process detailed in various studies. In its crystalline form, which represents a logical "1", GST has low electrical resistance, while its amorphous state, signifying a logical "0", has significantly higher resistance—the difference being roughly a thousandfold. Each PCM cell includes a GST element alongside a heater, often made from titanium nitride (TiN), which rapidly heats up to at least 600°C [91].

To erase data or set a cell to "0", the GST is heated to approximately 600°C, causing it to lose its crystalline structure. It then cools down quickly, within tens of nanoseconds, resulting in an amorphous state. To write data or set a cell to "1", the GST is heated just enough to reach the crystallization temperature but not so much that it melts, and then it is cooled down more gradually. This precise control is necessary to ensure that the GST transforms completely into the crystalline state without accidentally remelting due to excessive heat. These state transitions are depicted in Fig. 2.5a for erasing and Fig. 2.5b for writing the data bit.

(b) PCM: state transition  $0 \rightarrow 1$

Figure 2.5: Schematic of an PCM cell and the state transition [29]

For higher storage capacities, PCM uses MLC technology, which stores multiple bits in a single cell by partially crystallizing the GST to achieve intermediate resistance levels. This method involves precisely controlling the transition process to create semi-amorphous states with resistance values that fall between the fully amorphous and fully crystalline extremes.

The advantages of PCM lies in its small cell size and its swift read and write operations, making it a promising solution for future memory requirements [89].

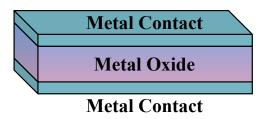

## **RRAM Memory Technology:**

RRAM is a type of NVM technology. It stores bits using the resistance levels in a Metal-Insulator-Metal (MIM) configuration, which forms the core structure of an RRAM cell (illustrated in figure 2.6a). The metal layers serve as electrodes connecting the cell to the memory circuit. A Low Resistance State (LRS) represents a logical "1," while a High Resistance State (HRS) signifies a logical "0." The state of the cell is changed by applying a voltage of a specific strength, direction, and duration [31].

RRAM operation can be influenced in two ways: either through the strength of the voltage applied (unipolar RRAM), or the direction of the voltage (bipolar RRAM). Similar to STT-RAM, PCM, and DRAM, RRAM can achieve high storage densities, with cells as small as  $4F^2$ , and boasts quick write and read times ranging from 5 to 50 ns. RRAM offers several advantages. First, cells do not require an access transistor and can be wired directly to the bit and word lines, simplifying cell access. This straightforward architecture allows for RRAM cells to be stacked in layers, creating 3D memory structures that significantly increase density. This is especially beneficial for memory packages or System-on-Chip (SoC) designs where space is at a premium [92].

The insulator layer, typically composed of slightly conductive materials like  $HfO_x$  or  $TaO_x$ , is critical in an RRAM cell. To set a cell to LRS, a high voltage is applied, forming nanoscale conductive paths, or filaments, between the metal electrodes through the insulator. This process is made possible by the displacement of oxygen ions, which ordinarily prevent the formation of these filaments. When these ions are removed, they leave behind vacancies that facilitate conductivity. Conversely, to revert

to HRS, oxygen ions are reintegrated into the vacancies, which breaks the conductive path and restores high resistance. The ability to switch between states by controlling the presence of oxygen ions within the dielectric is a key feature of RRAM, as detailed in the literature on cell failure mechanisms [93].

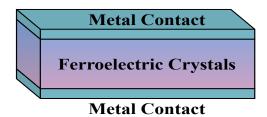

## Ferroelectric Random Access Memory (FeRAM) Technology:

FeRAM is an advanced NVM technology. A FeRAM cell is structured similarly to an RRAM cell but includes a layer of ferroelectric crystals instead of an insulator, as depicted in Fig. 2.6b. These ferroelectric layers are made from materials like Lead Zirconate Titanate (PZT)<sup>1</sup> or Strontium Bismuth Tantalate (SBT)<sup>2</sup>, which exhibit spontaneous polarization and an electric field [94,95]. The relationship between polarization and the electric field is characterized by a hysteresis loop, indicating that the polarization can be manipulated by an external electric field and remains in a residual state once the field is removed, thereby retaining data.

Ferroelectric materials, unlike ordinary crystals with symmetrically arranged atoms, contain crystals where an atom is displaced into a non-symmetrical position, creating a non-centrosymmetric structure. This displacement imparts a directional charge to the crystal, making it act like a dipole that determines the crystal's polarization direction.

An array of these ferroelectric crystals forms a FeRAM layer, where each crystal has its own dipole. Initially, these dipoles are unorganized, but with the application of a minimal external field, they can be oriented in the same direction. This alignment allows for the storage of a bit state in a FeRAM cell. The polarization—and thus the stored bit state—can be reversed by applying an external field in the opposite direction. The two polarization states correspond to logical "0" and "1". In a read operation, these states result in different charges that a sense amplifier can discern to determine the bit state. This read process is destructive, leading to a loss of charge, which makes a subsequent "Write after Read" procedure essential to restore the bit state.

FeRAM boasts remarkable endurance, with up to  $10^{14}$  write cycles, and offers a variety of cell designs that balance speed and density [96]. Configurations range from 6-transistor-2-capacitor (6T2C) structures, which resemble SRAM access times, to compact 1-transistor (1T) layouts, as shown in the literature [97]. However, the relatively large cell size, dictated by the charge needed for reliable sensing, and the necessity of a "Write after Read" process due to destructive reads, stand as the main drawbacks of FeRAM [96, 98, 99].

FeRAM cells are particularly susceptible to high temperatures, which can lead to two detrimental effects: Imprint and Thermal Depolarization. Imprint is an irreversible behavior where long-term ex-

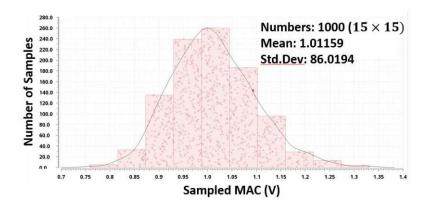

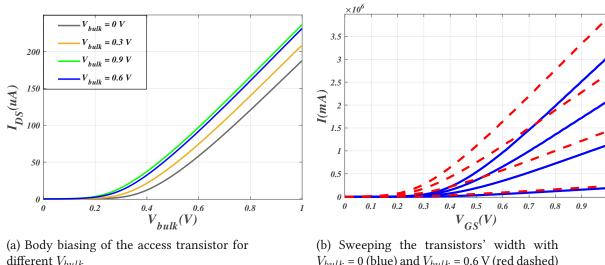

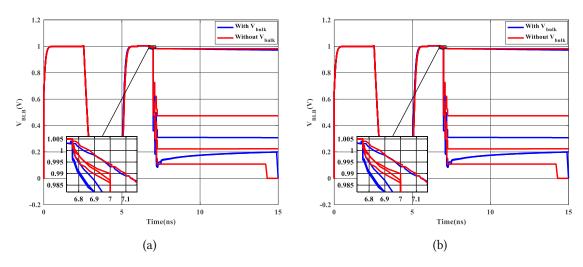

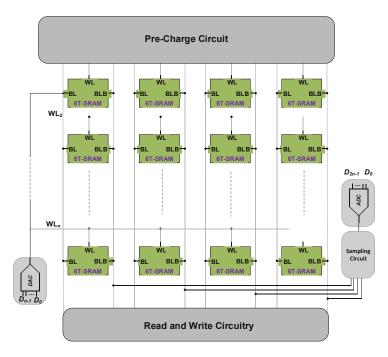

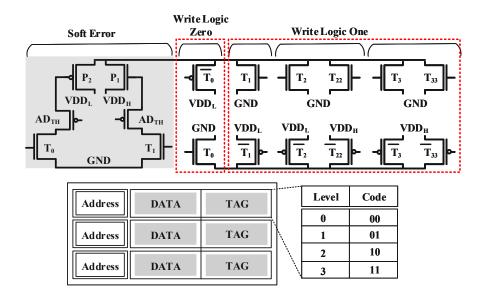

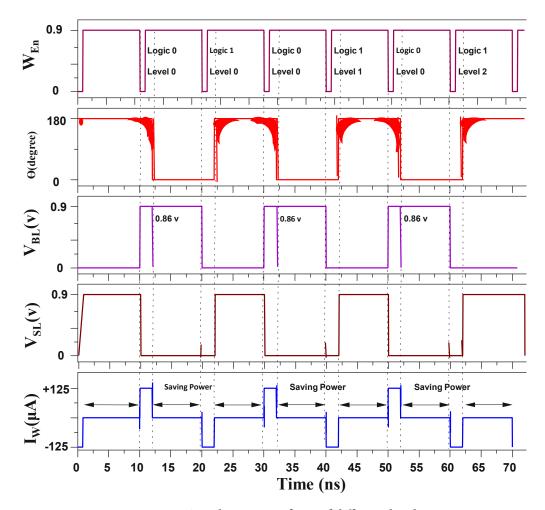

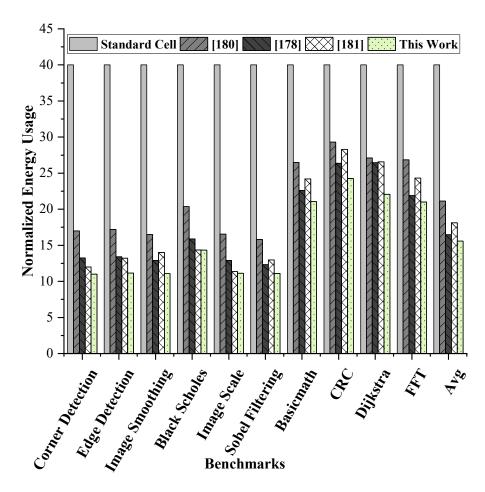

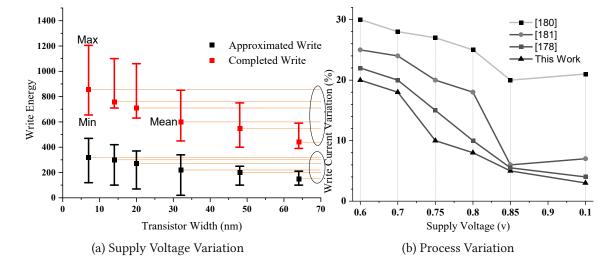

<sup>&</sup>lt;sup>1</sup>from the chemical formula Pb[Zr<sub>x</sub>Ti<sub>1-x</sub>]O<sub>3</sub>