# Dissertation

vorgelegt von

# **Matthias Wess**

# Estimation, Profiling and Modeling of DNNs for Embedded Systems

Zur Erlangung des akademischen Grades

Doktor der technischen Wissenschaften (Dr.techn.)

Wien, Austria, März 2025

Univ.-Prof. Dr. Axel Jantsch Betreuer:

Technische Universität Wien

Gutachter: Univ.Prof. Dr.-Ing. Dipl.-Ing. Daniel Müller-Gritschneder

Technische Universität Wien

Gutachter: Prof. Mario Casu

Politecnico di Torino

# **Contribution to Original Knowledge**

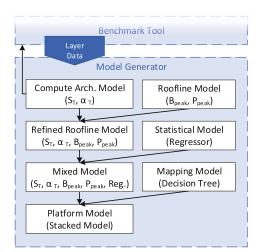

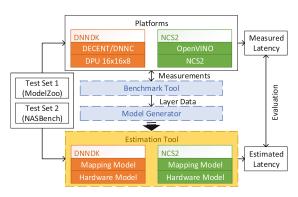

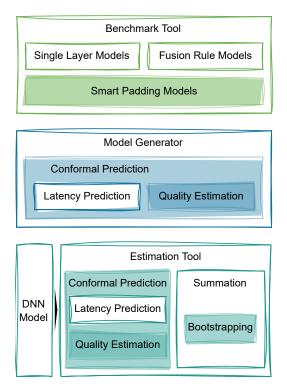

- ANNETTE Framework and Layer-Specific Optimization: A novel Deep Neural Network (DNN) latency estimation framework, ANNETTE, is introduced, which separates the optimization phase from per-layer estimation. This separation enables more accurate latency estimation and facilitates efficient and targeted improvements to DNN architectures [Paper I] [1].

- Refined Roofline Model and Mixed Statistical Modeling: A refined roofline model is proposed for latency estimation, combined with mixed modeling techniques to enhance the selection of datapoints for statistical modeling. This method improves the accuracy of latency estimation by strategically choosing relevant datapoints while drastically reducing the number of required latency measurements [Paper I] [1].

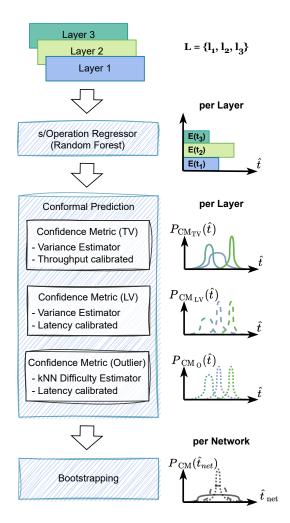

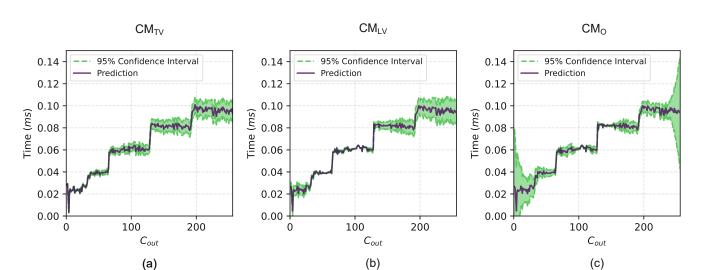

- Conformal Prediction for Latency Estimation: Latency estimation inherently involves approximations, often yielding rough estimates of median or mean latency values rather than predictions for specific execution times due to sparse measurements or high variability in the data. To address these limitations, conformal prediction methods are applied to latency estimation, introducing confidence measures that quantify uncertainties and provide reliable ranges for the latency estimation. This approach enhances the robustness and trustworthiness of the latency estimation process [Paper II] [2].

- · Quantization with Weighted Quantization-Regularization (WQR) and Layer-Specific Precision Scaling: The work adapts regularization-based methods for quantization (WQR), tailoring them to specific quantization functions. It demonstrates how combining these methods with per-layer precision scaling of the numeric format achieves higher compression quality reducing the required memory for execution without compromising accuracy of the DNN algorithm [Paper III] [3].

- Power Profiling Methodology: A new power profiling methodology is presented, highlighting that not all hardware platforms operate with equal efficiency across different layers. This showcases the variability in energy consumption and helps guide more informed hardware and layer-specific optimizations [Paper IV] [4].

# **List of Original Publications**

This dissertation is based on the following original publications, which are referred to in the text by their Roman numerals:

Paper I

Matthias Wess, Matvey Ivanov, Christoph Unger, Anvesh Nookala, Alexander Wendt, and Axel Jantsch. Annette: Accurate neural network execution time estimation with stacked models. IEEE Access, 9:3545-3556, 2021.

Paper II

Matthias Wess, Daniel Schnöll, Dominik Dallinger, Matthias Bittner, and Axel Jantsch. Conformal prediction based confidence for latency estimation of DNN accelerators: A black-box approach. IEEE Access, 12:109847-109860, 2024

Paper III

Matthias Wess, Sai Manoj Pudukotai Dinakarrao, and Axel Jantsch. Weighted quantizationregularization in DNNs for weight memory minimization toward HW implementation. IEEE Transac $tions\ on\ Computer\ Aided\ Design\ \&\ Integrated\ Circuits\ and\ Systems,\ 37(11):2929-2939,\ 2018.$

Paper IV

Matthias Wess, Dominik Dallinger, Daniel Schnöll, Matthias Bittner, Maximilian Götzinger, and Axel Jantsch. Energy profiling of DNN accelerators. 26th Euromicro Conference on Digital System Design (DSD), pages 53-60, 2023.

The following peer-reviewed papers and book chapter (Paper VIII) were already accepted or published in the course of the author's doctoral studies but are not included in this thesis:

Paper V

Matthias Wess, Sai Manoj Pudukotai Dinakarrao and Axel Jantsch. Neural network based ECG anomaly detection on FPGA and trade-off analysis. IEEE International Symposium on Circuits and Systems, pages 1-4, 2017.

Author's Contribution: Training, quantization and FPGA implementation of machine learning algorithm Relevance to this Thesis: Detailed trade-off analysis on the relationship between bit-width, speed-up, and accuracy for scaling weights and features in a practical FPGA implementation

Paper VI

Bernhard Haas, Matthias Wess, Alexander Wendt and Axel Jantsch. Neural Network Compression Through Shunt Connections and Knowledge Distillation for Semantic Segmentation Problems. IEEE International Symposium on Circuits and Systems, pages 349-361, 2021.

Author's Contribution: Collaboration and discussions on combining Shunt Connection algorithm in with Knowledge Distillation, model execution time analysis

Relevance to this Thesis: Model compression techniques tailored for embedded platforms

Paper VII

Daniel Schnöll, Matthias Wess, Matthias Bittner, Maximilian Götzinger, and Axel Jantsch, Fast, quantization-aware DNN training for efficient HW implementation. Euromicro Conference on Digital System Design, pages 700-707, 2023.

Author's Contribution: Primarily contributed to writing and conceptual formulation, collaborative discussions on Batch Normalization for Quantization-Aware Training

Relevance to this Thesis: Explores hardware-efficient quantization methods for deep learning models

Paper VIII

Alexander Wendt, Horst Possegger, Matthias Bittner, Daniel Schnöll, Matthias Wess, Dušan Malić, Horst Bischof and Axel Jantsch, A Pedestrian Detection Case Study for a Traffic Light Controller. Embedded Machine Learning for Cyber-Physical, IoT, and Edge Computing, pages 75-96, 2023.

Author's Contribution: Collaborative discussions related to implementation challenges, provided expertise in inference frameworks and model conversion

**Relevance to this Thesis:** Real-world use case emphasizing the challenges of testing models on diverse platforms.

Paper IX

Daniel Schnöll, Dominik Dallinger, Matthias Wess, Matthias Bittner, Axel Jantsch, Towards Optimal Implementations of Neural Networks on Micro-Controller, presented at Workshop on IoT, Edge, and Mobile for Embedded Machine Learning at ECML-PKDD, 2024.

Author's Contribution: Collaborative discussions related to performance modeling

Relevance to this Thesis: Microcontrollers present a different target and other restrictions. Model Compression and Quantization remain relevant topic

# Paper X

Matthias Bittner, Daniel Hauer, Matthias Wess, Dominik Dallinger, Daniel Schnöll, Konrad Diwold and Axel Jantsch, Interpretable Load Forecasting with Structured State Space Neural Networks, presented at Workshop on Machine Learning for Sustainable Power Systems at ECML-PKDD, 2024.

Author's Contribution: Research on related work and collaborative discussions

Relevance to this Thesis: Demonstrates the importance of model interpretability, efficient neural networks for forecasting

# Paper XI

Matthias Bittner, Daniel Hauer, Matthias Wess, Daniel Schnöll, Konrad Diwold and Axel Jantsch, Forecasting Load Profiles and Critical Overloads with Uncertainty Quantification for Low Voltage Smart Grids, presented at International Conference on System Reliability and Safety, 2024.

Author's Contribution: Research on related work and collaborative discussions regarding uncertainty quantification Relevance to this Thesis: Demonstrates a real-world use case with various uncertainty quantification methods

# Paper XII

Axel Jantsch, Song Han, Lin Meng, Oliver Bringmann, Haotian Tang, Shang Yang, Hengyi Li, Matthias Wess and Martin Lechner, Special Session: Estimation and Optimization of DNNs for Embedded Platforms, International Conference on Hardware/Software Codesign and System Synthesis, pages 21-30, 2024.

**Author's Contribution:** Provided latency estimation results

Relevance to this Thesis: Estimation and optimization of deep learning models for embedded platforms

# Contents

| 1 | Intr               | roduction                                               | 2  |

|---|--------------------|---------------------------------------------------------|----|

|   | 1.1                | Design and Implementation Flow for Deep Neural Networks | 3  |

|   |                    | 1.1.1 Training                                          | 8  |

|   |                    | 1.1.2 Hardware-Specific Optimization                    | 8  |

|   |                    | 1.1.3 Inference                                         | 8  |

|   | 1.2                | Relevance of Publications                               | 8  |

| 2 | Late               | ency Prediction                                         | 9  |

|   | 2.1                | Latency Estimation Methods                              | 9  |

|   | 2.2                | Challenges Addressed in this Work                       | 11 |

|   | 2.3                | Impact on the State of the Art                          | 12 |

| 3 | Qua                | nntization                                              | 13 |

|   | 3.1                | DNN Quantization-Specific Considerations                | 14 |

|   |                    | 3.1.1 Over-Parameterization                             | 14 |

|   |                    | 3.1.2 Evaluating Quantization Quality                   | 14 |

|   |                    | 3.1.3 Quantization Granularity                          | 14 |

|   |                    | 3.1.4 Quantization and Training                         | 14 |

|   |                    | 3.1.5 Quantization Schemes                              | 15 |

|   | 3.2                | Challenges Addressed in this Work                       | 15 |

|   | 3.3                | Impact on the State of the Art                          | 16 |

| 4 | Hardware Profiling |                                                         | 17 |

|   | 4.1                | Different Goals of Profiling                            | 17 |

|   | 4.2                | Metrics to Profile                                      | 18 |

|   | 4.3                | Profiling Granularity                                   | 18 |

|   | 4.4                | Challenges in Profiling DNNs                            | 18 |

|   | 4.5                | Challenges Addressed in this Work                       | 19 |

| 5 | Con                | nclusions and Outlook                                   | 20 |

# Chapter 1

# Introduction

In the past decade, Deep Neural Networks (DNNs) have become crucial for solving complex tasks across various domains such as computer vision [5], time-series analysis [6], and natural language processing [7]. These algorithms typically involve two main phases: a computationally intensive training phase, where models learn from large datasets, and an inference phase, where trained models are deployed to make real-time predictions. This development has resulted in a significant increase in the availability of hardware optimized for both phases, not only in cloud environments but also in energy-constrained edge and embedded systems [8]. This dissertation focuses on inference and aims to improve the design flow from the original model to its real-world hardware implementation.

When tackling specific problems using DNNs, considering the final hardware solution from the beginning is often not feasible. When tackling specific problems using DNNs, considering the final hardware solution from the start is often impractical. Even if feasible, factors such as cost, scalability, and the continuous evolution of Artificial Intelligence (AI) models must be considered to ensure a viable implementation.

For many applications, the main challenge lies in developing a functional machine learning model that achieves satisfactory accuracy. In other cases, constraints such as latency, power consumption and cost necessitate the use of embedded platforms. Deploying trained algorithms on these platforms can be challenging due to limitations in memory and computing power.

In straightforward cases that fall into well-defined categories, such as object detection or image classification, developers can utilize existing tools, code repositories, and vendor-provided workflows to speed up the development process.

However, several real-world use cases do not fit neatly into these predefined tasks. Each problem presents unique intricacies that machine learning engineers must address before optimizing the system's performance on embedded platforms. Consequently, the path from training a DNN to its final hardware implementation is marked by several critical design decisions that ultimately determine the success of the project.

Fortunately, the rise in AI popularity has led to an abundance of tools that simplify downstream implementation and provide access to pre-trained DNNs. Resources such as Hugging Face [9], pre-trained models in TorchVision [10], Ultralytics' YOLO implementations [11], benchmarks such as MLPerf, exchange standards like Open Neural Network Exchange Format (ONNX) [12], and inference frameworks like TensorRT [13] and OpenVINO [14] have significantly accelerated developments across all areas. The increased accessibility of these tools enables researchers and developers to focus on addressing the unique challenges of their specific applications.

Despite the availability of these tools, many numerous challenges remain. With each new DNN model and hardware platform, the design space continually expands, making it increasingly difficult to navigate. As a result, benchmarks that were published just a few years ago quickly become outdated, and tedious experiments must be conducted for each new DNN architecture and hardware platform. To accelerate the design and implementation process of DNNs, this thesis aims to address key obstacles in the design flow, streamlining the search for the optimal implementation with the best combination of hardware and DNN architecture.

Section 1.1 provides an overview of the design and implementation flow of DNNs on embedded hardware. The Chapters 2, 3, and 4 offer more detailed insights. The chapters of this work align with the publications on DNN latency prediction ([Paper I] [1], [Paper II] [2]), quantization ([Paper III] [3]), and hardware profiling ([Paper II] [2], [Paper IV] [4]), addressing their respective challenges.

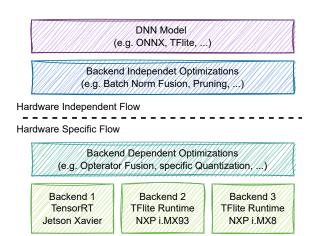

### Design and Implementation Flow for Deep Neural Networks 1.1

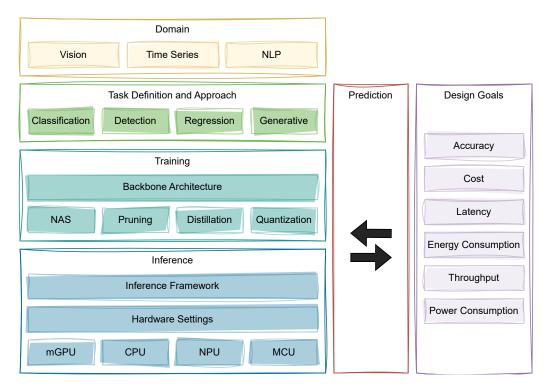

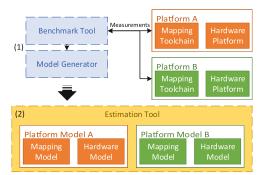

Figure 1.1 provides a rough and incomplete overview of the design space. Within each of the indicated points are numerous subcategories, leading to an exponentially growing number of possible implementations to a specific problem.

Figure 1.1: Overview of the design space for DNN design and hardware inference.

The domain of a machine learning task is usually determined by the application. However, there are cases where a problem can be approached from different perspectives, leading to a shift to another domain. This transformation is a critical design decision that can greatly impact the accuracy and performance of the solution. It often allows for the utilization of better-suited algorithms for the task. For example, converting raw audio data to spectrograms enables the

use of image-focused DNNs to address tasks such as keyword spotting [15].

Next, the framing of the problem plays a crucial role in the design process. While some tasks, such as classification or object-detection, are well-defined, with established methods available to solve them, many real-world problems pose greater challenges. For instance, a problem that involves identifying objects could be framed either as a classification task (recognizing object types) or a detection task (locating objects). Selecting the right task and approach is critical, as it shapes the subsequent steps in machine learning model design and hardware selection [16].

Pretrained backbones can serve as a starting point, requiring only minor adaptations to address a specific machine learning task. However, since these backbones are trained on generic datasets, they are often not the optimal choice for specialized applications. To meet design goals, methods like Neural Architecture Search (NAS) can help automate the process of exploring and identifying the best architecture for the task [17]. Techniques such as pruning [18], and knowledge distillation [19] are commonly applied to optimize the model for accuracy and efficiency, particularly when targeting specific resource-constrained hardware platforms [20]. Similarly, quantization offers the opportunity to optimize DNNs for hardware friendly inference [3].

Finally, selecting the appropriate hardware for model inference is critical, as it must meet performance, resource and cost constraints. Each hardware platform supports specific inference frameworks, such as TensorRT [13] or OpenVINO [14] which offer different deployment options, compatibility with training frameworks, and vary in how efficiently they optimize model inference performance [21]. Additionally, different hardware platforms support various data types, which affects precision, speed, and compatibility [4], and are often optimized for specific application domains. Beyond these technical factors, considerations like product life-cycle, scalability, and future updates are important to ensure the solution remains adaptable and sustainable in the long term. While hardware and development costs are not technical constraints, they are crucial for economic viability. They impact production, scalability, and market success, making a technically feasible solution impractical if costs exceed budget limits. Thus, cost is key in product development but does not determine technical feasibility.

Resulting from all these considerations the different implementations can be compared with respect to accuracy, latency, throughput, power and energy consumption, cost and other metrics. For each of those design goals in isolation it is usually quite easy to define the optimal outcome:

- 1. **Accuracy** should be as high as possible (↑),

- 2. **Latency** should be as low as possible  $(\downarrow)$ ,

- 3. **Power and energy consumption** should be as low as possible  $(\downarrow)$ ,

- 4. **Cost** should be as low as possible  $(\downarrow)$ ,

However, these goals are often interconnected, and additional factors such as available dataset size or hardware limitations also come into play. As a result, it becomes difficult to pinpoint a single target for the final solution. Given this complexity, it is essential to establish constraints for each design goal and parameter to guide the development process effectively and ensure a balanced solution [22].

Meeting design goals—such as optimizing accuracy, latency, and power consumption—requires careful balancing of trade-offs. In real-time applications, achieving low latency is crucial, as quick model responses are essential. Latency

estimation can play a key role in early-stage design decisions by helping to rapidly narrow the design space and identify feasible solutions.

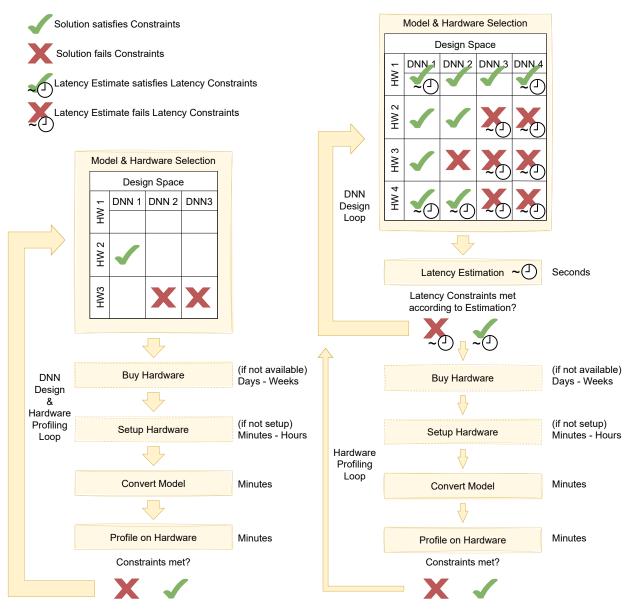

For example, consider a real-world scenario where a baseline solution addresses the problem with sufficient accuracy. From there, the next step is to define key constraints such as latency, throughput, power consumption, and energy consumption. Once these parameters are established, we attempt to run the model on the available hardware. If the model meets the performance requirements and the hardware is cost-effective, the process is complete. However, if the solution does not satisfy the constraints, we can either adapt the machine learning model, apply further optimizations, or select different hardware and adjust the hardware settings.

Figure 1.2: Simplified DNN design flow comparing the traditional approach (left) and the optimized approach with latency estimation (right). Latency estimation speeds up the process, enabling broader exploration of viable solutions and informed decisions before hardware acquisition and testing.

This iterative process of testing various models with different hardware platforms and configurations, shown on the left side of Figure 1.2, can become cumbersome, especially when the necessary hardware is not readily available. While it is difficult to predict the accuracy of different algorithms, inference latency can be reliably estimated [2]. By applying latency estimation, the design space of feasible solutions can be rapidly narrowed, eliminating the need for a bruteforce approach and streamlining the development process. Figure 1.2 visualizes how latency estimation reduces the need for profiling by splitting the DNN design and hardware profiling loop. As applying latency estimation is only a matter of seconds, a broader and more complete design space can be explored before making informed decisions about which hardware to acquire, setup and test. This approach filters out solutions that fail to meet the defined constraints and supports the design of DNNs for hardware that may not yet be available. As a result, developers can focus on optimizing algorithms rather than repeatedly profiling them on hardware.

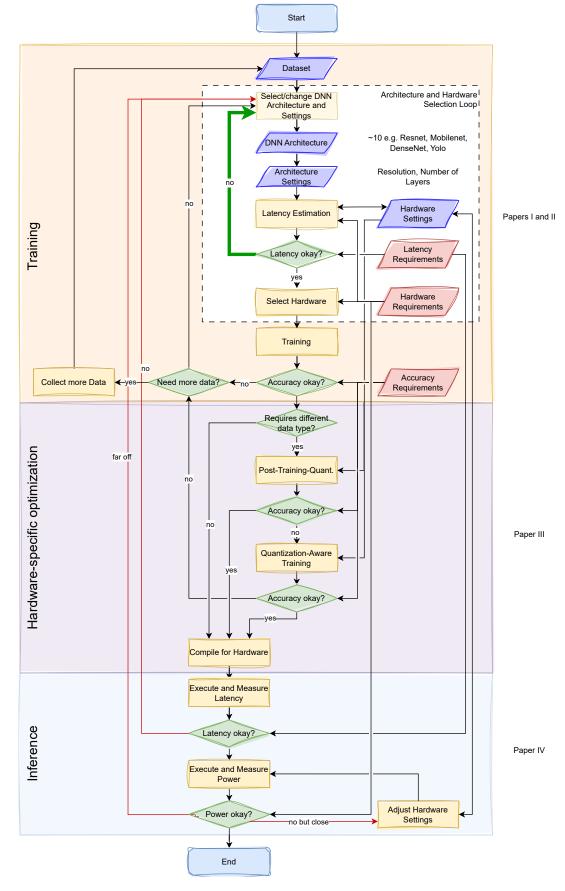

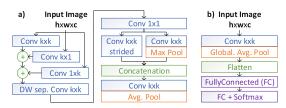

Going forward, Figure 1.3 sketches a more detailed design flow for DNN hardware implementation. For this work we view pruning similarly to knowledge distillation as a method to reach an optimal DNN architecture by adjusting the trade-off between accuracy and compute intensity [21]. The resulting design flow can be split into three phases: Training, Hardware-specific Optimization, and Inference.

Figure 1.3: DNN design flow for hardware implementation

### **Training** 1.1.1

The process begins with defining the task and gathering the relevant dataset. A network architecture, or a set of architectures, is then selected. Latency estimation is performed to provide an early indication of model suitability for deployment on specific hardware platforms. This step helps eliminate models that are computationally expensive or slow. Once promising models are identified, training proceeds with floating-point precision. After training, the model's accuracy is evaluated. If the required accuracy is achieved, the model proceeds to hardware-specific optimization.

# Hardware-Specific Optimization

During this phase, the hardware's requirements are assessed, particularly regarding supported data types (e.g., FP32 vs. INT8). Firstly, Post-Training Quantization (PTO) is applied, as it is a simpler and more efficient and low effort method that does not require retraining. However, if PTQ leads to a significant accuracy drop, Quantization-Aware Training (QAT) can be employed to recover the lost accuracy. Once the model reaches acceptable accuracy levels, it is compiled for the target hardware. If any hardware-specific adjustments, such as different architectures or datatypes, are necessary, the process loops back to the training phase.

### 1.1.3 **Inference**

The final phase involves compiling the model for the hardware and deploying it. Latency is measured to ensure predictions made prior to training the model are met. If the latency is acceptable, power profiling is carried out to confirm the model's energy efficiency. If latency exceeds the estimations, the model or hardware selection may require further adjustment.

### **Relevance of Publications** 1.2

The publications presented in this thesis address critical challenges of the DNN design and implementation flow. In the Training phase, the research on latency estimation (ANNETTE [Paper I] [1]) and the application of Conformal Prediction [Paper II] [2] introduce methodologies to achieve accurate latency estimation and confidence intervals for performance predictions, improving the selection of network architectures. In the Hardware-specific Optimization phase, studies on quantization and memory minimization [Paper III] [3] help maintain model accuracy while optimizing for hardware limitations. Finally, in the **Inference phase**, the research on black-box benchmarking and energy profiling [Paper IV] [4] enables the evaluation of latency and power/energy consumption, ensuring that the DNN is optimized for both performance and energy efficiency on the target hardware platforms. These contributions collectively offer a comprehensive framework for optimizing DNNs across the entire design flow.

# Chapter 2

# **Latency Prediction**

In comparison to the vast amount of research available in the training and software areas of AI, the field of latency estimation for DNNs remains relatively small. Several factors contribute to this disparity:

Firstly, while AI algorithms themselves have seen groundbreaking advancements, the development and analysis of hardware for executing these algorithms has traditionally lagged behind. This gap is partly why Graphic Processing Units (GPUs) became central to AI development, despite being originally designed for graphics processing. The flexibility of GPUs allowed them to be quickly adapted for neural network training and inference, but the specialized development of hardware for DNNs has taken more time to mature [23].

Secondly, the initial surge in AI focused on applying algorithms to various datasets, offering abundant opportunities for researchers without necessitating immediate concern for hardware performance on embedded devices. Deploying these algorithms in real-time scenarios introduces additional complexity, requiring sophisticated optimization tools, including accurate latency estimation models [Paper I] [1]. The heterogeneity of hardware platforms further complicates this issue. DNNs are deployed on a wide range of hardware (e.g., GPUs, Field Programmable Gate Arrays (FPGAs), Neural Processing Units (NPUs)), each with unique characteristics [24]. This diversity makes it difficult to create generalized performance models.

Moreover, much of AI's early deployment occurred in cloud-based or offline environments where latency and realtime performance were not primary concerns. Only with the increasing demand for real-time applications such as autonomous driving, has the need for accurate performance estimation tools become critical [25]. Yet, many developers still rely on benchmarks or prior knowledge when selecting hardware platforms, instead of using dedicated tools for precise latency prediction.

# **Latency Estimation Methods**

When comparing DNN architectures, metrics such as Floating Point Operation (FLOP) and parameter counts are commonly used, as they offer a straightforward way to quantify aspects like computational complexity and memory requirements. However, while these proxy metrics are useful for initial comparisons, they do not capture how the algorithms are actually mapped onto hardware [Paper I] [1]. The computational efficiency of different hardware platforms for

the same network architecture can vary significantly depending on factors such as the utilized set of operations, the sequence in which these operations are executed, and the interconnections between them [23].

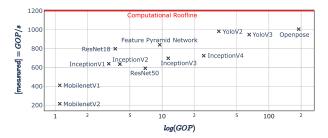

Analytical approaches attempt to improve upon this by estimating performance based on theoretical hardware capabilities [26]. For example, dividing the total number of operations by the hardware's theoretical peak number of Floating Point Operations per second (FLOPs/s) provides a rather optimistic latency estimate, as hardware vendors typically report peak performance numbers that assume perfect utilization of all compute resources, which is rarely achievable in practice. Additionally, factors like memory access patterns and parallelism overhead are not captured in such simplistic calculations.

The roofline model [26] offers an improvement by incorporating memory bandwidth alongside computational performance. It provides a visualization of performance bounds based on both computation and memory access, making it useful for understanding how well a DNN architecture utilizes available hardware.

While the roofline model itself is simple the challenge lies in properly applying it to DNNs for accurate latency estimation. For inference, the DNN is partitioned across the available hardware resources. As the roofline model fails to cover such aspects it can result in largely inaccurate predictions. Nonetheless, for compute-heavy layers such as convolutional layers, where these design challenges have a smaller impact, the roofline model can still yield reasonably accurate performance estimates [Paper I] [1].

Building upon the roofline model, several approaches have been developed to better account for hardware-specific details. Improvements in modeling the memory hierarchy and extending the roofline model to accommodate more realistic predictions by focusing on different aspects. For instance, the models introduced by ANNETTE [1] and Blackthorn [27] refine performance models by focusing on compute parallelism overhead. Other models [Paper IX] [28], [29] provide deeper insights by diving down to the level of basic operations and instructions, which is especially relevant for Microcontroller Units (MCUs) and other low-power devices.

Moreover, simulators like SCALE-Sim [30] and SimPyler[31] offer detailed simulation-based approaches to predict latency more accurately for specific hardware architectures. These simulators offer precise insights by modeling low-level hardware interactions. However, they can be time-consuming to use and often require extensive hardware knowledge, which may limit their practicality for rapid prototyping or when evaluating a vast design space.

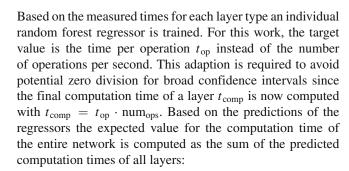

Machine learning-based approaches have emerged as a promising alternative for latency prediction. In these methods, the target device is extensively benchmarked to collect execution time data for various network layers and configurations. This data is then used to train machine learning models that predict execution time based on network characteristics and hardware parameters. The core methodology across these approaches remains similar, with differences in feature engineering, applied machine learning algorithms, and data collection strategies [Paper I] [1], [Paper II] [2], [32].

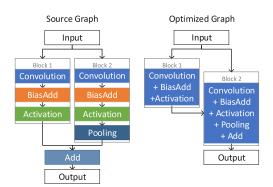

# **Optimization Challenge**

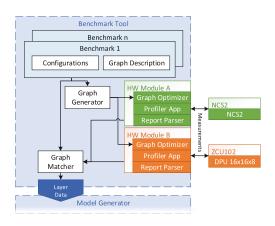

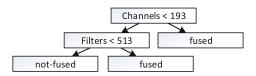

One of the core challenges in performance estimation lies in correctly capturing and modeling the mapping of layers of a neural network to the specific hardware resources. The per-layer approach remains a valid technique, where the performance of each individual layer is estimated separately. However, this method struggles to account for inter-layer optimizations, such as operation fusions and shared memory usage between layers. Tools like ANNETTE [Paper I] [1]

address this by using decision trees to detect possible fusions between layers. Similarly, nn-Meter [33] includes specific kernels for different combinations of layers and benchmarks them to find the best configuration. The methodology begins by identifying available kernels and optimizations, then benchmarks those combinations to achieve accurate performance estimates. For example, care must be taken when measuring multiple layers simultaneously. To avoid skewed results ANNETTE and nn-Meter utilize Random Forests for per-kernel predictions after performing a layer fusion rule detection. PerfSAGE [34], DIPPM [35], SLAPP [36] rely on Graph Neural Networks (GNNs) to capture cross-layer optimizations. In more complex cases, such as those involving graph neural networks [32], data collection can be more comprehensive or restricted to a smaller design space, capturing information for possible layer configurations.

### **Required Data for Accurate Modeling**

A second key challenge is balancing the need for accurate performance predictions while minimizing the amount of data required to train the models. Since the design space is vast, collecting exhaustive data for all possible configurations is impractical. Therefore, it becomes essential to identify the most representative data points. Hybrid approaches, combining empirical measurements with analytical models, are often employed to achieve this balance [Paper I] [1] [37]. ANNETTE, for instance, performs parameter sweeps and selects specific points to measure, focusing on scenarios where the compute architecture is optimally utilized. By combining the machine learning models, trained on this data, with analytical models, ANNETTE is able to deliver robust predictions with fewer data points. Performance representatives [37] further improved this concept by using integer division to reduce machine model complexity. Blackthorn [27] uses a model-in-the-loop approach to dynamically adjust the required measurement points during runtime. This approach significantly reduces the number of required data points but may not capture the exact behavior in all scenarios due to the underlying model assumptions.

### Hardware Heterogenity

Handling heterogeneous hardware platforms, such as NVIDIA devices where different parts of the network can be assigned to different cores (e.g., GPU vs. Deep Learning Accelerator cores) or mobile SoCs, remains a significant challenge [38]. Often, this mapping is done manually, with developers specifying which network components should be assigned to specialized compute resources. While statistical estimation models can benchmark layers on specific devices and automate parts of this process, there is no universally applicable solution to handling hardware heterogeneity. The problem is particularly challenging in scenarios where layers need to be dynamically mapped to different cores based on real-time performance considerations.

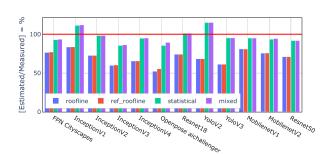

# Challenges Addressed in this Work

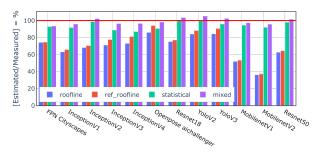

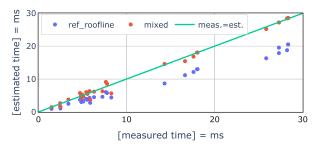

The primary contribution of this research lies in the development of systematic approaches, most notably ANNETTE [Paper I] [1] and its underlying models. ANNETTE has significantly advanced the establishment of a structured methodology for benchmarking, particularly on hardware with varying computational efficiencies. By combining analytical and statistical models, ANNETTE strikes an effective balance between minimizing the number of measurements required and maintaining high accuracy. Additionally, the integration of layer-level optimizations, such as layer-fusion [39], has improved prediction accuracy at the network level. As a result, the system achieved prediction errors within a range of approximately 5-15% [Paper I] [1].

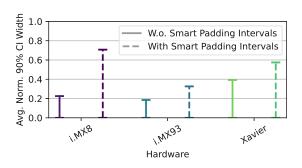

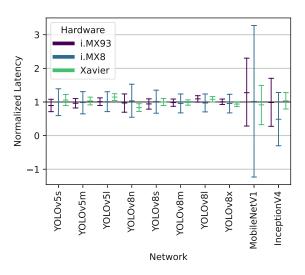

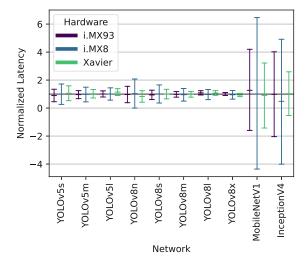

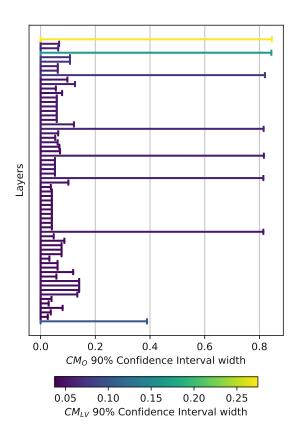

Building on this, we introduced a confidence framework as an extension to ANNETTE, leveraging conformal predic-

tion [Paper II] [2]. This framework serves two key purposes: first, it provides a mechanism to evaluate whether the prediction model sufficiently covers the entire design space. If the model cannot confidently predict performance for certain regions, developers are notified, allowing them to either refine the model or avoid architectures that are unlikely to meet the required specifications. This enhances the ability to interpret results and make more informed decisions when selecting hardware or DNN architectures, particularly in edge cases where the model might be less reliable. Additionally, the framework aids in the assessment and refinement of the generated models. In parallel with the development of this framework, a smart benchmarking approach was introduced [Paper II] [2], enabling the generation of ANNETTE models without requiring per-layer benchmarks, further streamlining the design process.

### 2.3 Impact on the State of the Art

The ANNETTE framework laid the foundation for structured performance modeling of DNNs. The ACADL-based automated performance modeling framework [29] builds upon ANNETTE's stacked modeling approach by introducing a formalized architecture description language for hardware accelerators, thereby extending on the architectural description of the refined roofline model. The Performance Representatives method [37] refines ANNETTE's benchmarking strategy, reducing the number of required training samples while maintaining estimation accuracy. The SLAPP framework [36] extends ANNETTE's operator-level and layer-wise estimations by leveraging graph-based learning techniques to model execution times at a subgraph level. Together, these works demonstrate the lasting impact of ANNETTE on scalable, efficient, and hardware-aware DNN performance estimation.

# Chapter 3

# Quantization

Quantization is a crucial technique in optimizing DNNs for efficient deployment across a wide range of devices [40]. Unlike other optimization methods which primarily focus on reducing the size or complexity of neural network architectures, quantization aims to reduce the data type size of weights and feature maps within the already defined architecture. As a result quantization is commonly applied in addition to architecture optimization techniques such as pruning [41]. The transition to smaller data types not only reduces the amount of data that needs to be moved between memory and compute units, which is a critical bottleneck in many DNN applications, but also simplifies operations [40]. Integer operations, for instance, are less complex and consume less power compared to floating-point operations, but this comes with a trade-off in precision [42]. Quantization, therefore, must be carefully managed to minimize the loss of accuracy, particularly as lower precision formats are adopted [43].

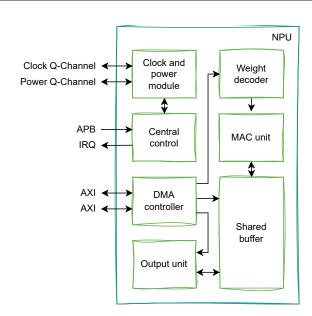

In today's landscape, many embedded and specialized devices designed to run DNNs are equipped with compute units that are optimized for specific data types. For example, Nvidia GPUs are tailored for FP32 and FP16 but also support INT8 operations to enhance performance [44]. Similarly, Central Processing Units (CPUs) commonly support several datatypes but also integrate Single Instruction, Multiple Data (SIMD) engines and instructions optimized for FP16 and INT8 [45]. NPUs, on the other hand, are often focused on executing INT8 computations due to the balance they strike between precision and efficiency [46]. Furthermore, newer hardware architectures are introducing support for even more specialized data types such as BrainFloat16 or even INT4 and INT2, pushing the boundaries of efficiency in DNN inference [47, 44].

Applying quantization is especially valuable in scenarios where resource constraints are a significant consideration, such as in mobile devices, autonomous systems, and real-time edge computing applications [48, 49, 50]. By reducing the bit-width of weights and activations, quantization helps decrease the computational and memory demands of neural networks, resulting in improved speed, energy efficiency, and memory usage [51]. As the demand for deploying DNNs in real-world, resource-limited environments grows, quantization remains an essential tool for achieving both high performance and energy efficiency [23].

### **DNN Quantization-Specific Considerations** 3.1

In general, quantization describes the well-established concept to map most often continuous input values to a set of output values by applying a quantization function f, typically achieved with rounding and truncation [51]. Interestingly, DNNs bring some new opportunities and challenges to the problem of quantization [51].

### **Over-Parameterization** 3.1.1

Firstly, DNNs are essentially large constructs composed primarily of matrix multiplications and non-linear activation functions. Therefore, both training and inference are computationally intensive tasks that can be challenging to handle. Consequently, optimizing data types and operations can lead to significant gains in energy-efficiency and throughput [23, 39]. However, despite enormous efforts of researchers to develop slim and efficient DNN architectures, these networks remain heavily over-parameterized, especially when models optimized for standard datasets like ImageNet are applied to real-world use cases with a limited set of classes [52, 53]. This over-parameterization enables techniques such as pruning and quantization to achieve high compression rates at minimal to no accuracy loss [18, 54].

# **Evaluating Quantization Quality**

Secondly, DNNs do not necessarily solve well-posed or well-conditioned problems, but are usually trained by minimizing the result of a loss function which approximates the prediction error of the DNN on a training dataset. Due to the overparameterized nature of DNNs there are multiple different models that optimize the prediction accuracy sufficiently [55]. As a result, it is possible to have a high quantization error between the original and the quantized model with still very good prediction and generalization performance [56, 41]. In some cases, minimizing quantization error might be important, for instance to maintain the exact behaviour of the original DNN. However, in general, DNNs can be treated as black-boxes where only the resulting accuracy matters. This contrasts with traditional quantization methods, which focus on preserving the original signal as closely as possible [57].

# **Quantization Granularity**

Besides these two aspects, which provide additional degrees of freedom compared to standard quantization, other important considerations make the quantization of DNNs even more complex. The layered structure of neural networks allows for the application of varying quantization schemes and compression rates at different granularity levels, such as per-model, per-layer [Paper III] [3] or even per-channel quantization [51]. However, to fully exploit the benefits of these approaches, the hardware must be capable of supporting variable precision operations across layers and channels. Consequently, no single solution has emerged as universally optimal.

# **Quantization and Training**

The final key consideration is how quantization interacts with the training process. As floating-point precision is essential for gradient-based optimization methods, which rely on small, incremental updates to weights, specifically extreme quantization poses a problem. To avoid this, PTQ [58, 59] separates the training from the quantization step, by applying the quantization after the model has been fully trained. Usually PTQ is fast and resource-efficient as it requires no additional training, but it can result in significant accuracy reduction since the model has not been exposed to the quantization effects during training. Thus, as an alternative, QAT [56, 42] integrates the quantization process. By simulating the effects of quantization during training (fake-quantization), the model can adapt its weight representations to be more robust to lower precision, reducing accuracy loss when the final quantized model is deployed.

A major challenge in QAT is the non-differentiability of quantization functions, such as rounding, which interrupts the gradient flow needed for backpropagation. Several strategies have been proposed to address this issue [51, 42, 3, 60, 61, 62]. Straight-Through Estimation (STE) is a common approach that bypasses the rounding operation by approximating the gradient of the quantization function as the identity function [51].

Further quantization techniques involve the introduction of randomness into the rounding process, rather than deterministically rounding values to the nearest quantization level (stochastic quantization) [42] or encouraging weights to settle into values that are easier to quantize, by applying regularization during training (weight regularization) [3]. Alternatively, making quantization parameters dynamic and learnable during training, as in PACT and LSQ, which allow quantization ranges and step sizes to adapt during training, results in more flexible and precise quantization, improving the final model's performance [60, 61, 62].

### **Quantization Schemes** 3.1.5

When applying quantization, several schemes must be considered. We can distinguish between symmetric and asymmetric, and uniform and non-uniform quantization schemes. It must be considered, that not all presented methods fit all of the quantization schemes [Paper III] [3]. Therefore the target quantization schemes have to be taken into consideration when choosing the quantization methodology. For INT8 quantization, for example simple PTQ can be sufficient [63], depending on the task, DNN architecture and target accuracy.

### 3.2 Challenges Addressed in this Work

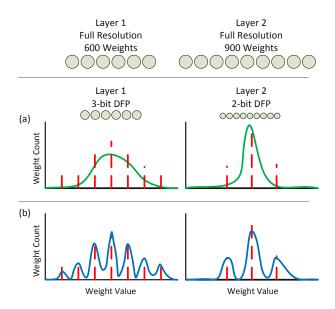

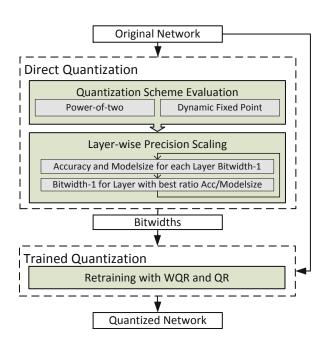

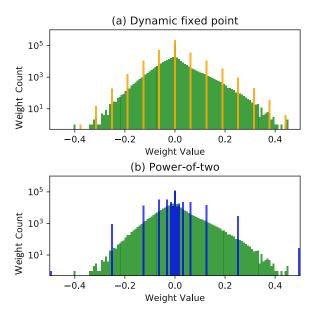

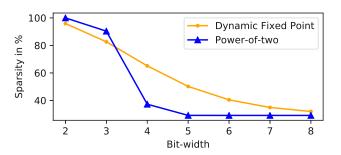

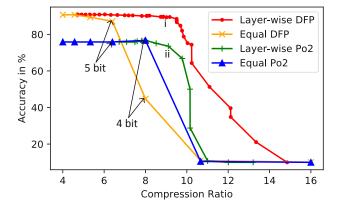

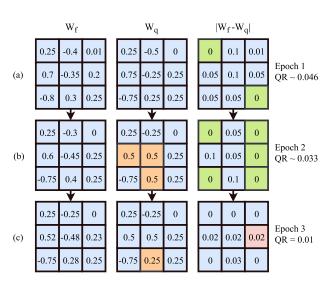

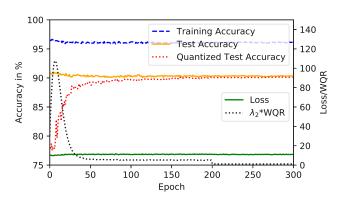

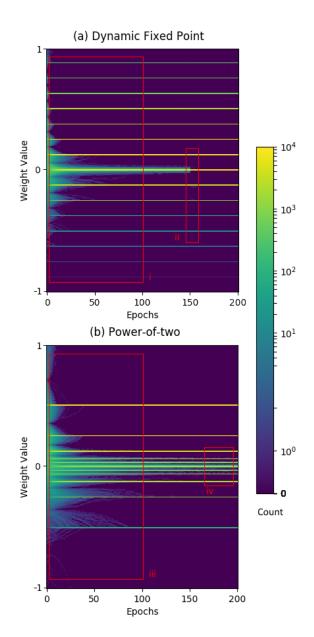

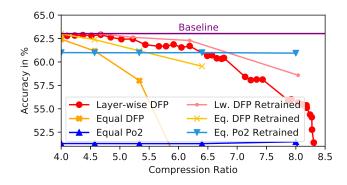

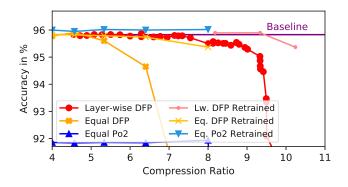

We addressed the challenge of balancing memory compression and accuracy retention in neural networks, particularly for deployment on devices with limited memory and computational resources [Paper III] [3]. Based on the previous discussions, the work makes use of different quantization bit-widths at the layer granularity while enforcing quantization through an additional regularization term. Furthermore, the method is evaluated using two quantization schemes: Dynamic Fixed Point (DFP) and Power-of-Two (Po2).

The main contribution of this work is the introduction of WOR, a technique that enhances quantization by adding a regularization term to the loss function during training. This term forces the weights to gravitate toward quantization levels, thereby reducing quantization error and improving accuracy after quantization. The results show that adapting the regularization term, to the applied quantization function can increase the achievable accuracy. Additionally, Layerwise Precision Scaling using a greedy algorithm is deployed to ensure that more critical layers retain higher precision, while less sensitive layers are quantized more aggressively.

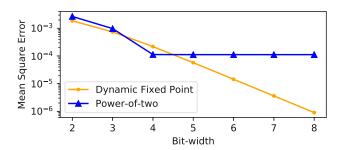

The results of the method are compared for two quantization schemes: DFP and Po2. The findings show that DFP performs well at higher bit-widths, while Po2, which simplifies operations into bit-shifts, is preferred for lower bitwidths. It is demonstrated that WQR achieves significant compression ratios (up to 9.33x for the SVHN dataset) with minimal accuracy degradation, making it a highly efficient technique for hardware implementations [Paper III] [3].

At the time this method was introduced, it represented a step forward in quantizing DNNs for resource-constrained environments. As deep learning has progressed and workloads have grown more complex, the exact method may not be entirely sufficient on its own. Nonetheless, the core principles remain sound, and WQR can be effectively combined with other quantization or optimization methods. The results achieved in this work address several recurring challenges as DNN models continue to grow:

- Datatypes: Current trends favor smaller integer and low-bitwidth floating-point types [64]. Since Po2 based schemes lack flexibility and their effectiveness depends on the weight distribution, they are unlikely to gain broader adoption.

- Granularity: Adjusting precision at the layer or block level is currently the most efficient approach to optimize DNNs [65]. For instance, Nvidia's platforms allow for the use of different datatypes in different parts of the network, illustrating the growing importance of fine-grained control.

- OAT Approach: At 8-bit precision, STE is usually sufficient for maintaining accuracy. However, for lower precision levels, it will be interesting to see which quantization technique becomes dominant. A combination of techniques, including STE, stochastic rounding, and quantization regularization, is theoretically viable. For fine-tuning, the regularization-based approach may better preserve the original behaviour of the DNN.

### 3.3 Impact on the State of the Art

The WQR approach presented in this work has influenced research in QAT and hardware-efficient deep learning models. Singhal et al. [66] extend WQR by incorporating non-uniform quantization with learnable bit multipliers, improving flexibility and fault tolerance in low-bit neural networks. [67] builds upon WQR's structured regularization principles to optimize weight representations, reducing hardware complexity through efficient sub-expression sharing. QFALT [68] directly applies Quantization Regularization to enhance fault tolerance in quantized models, ensuring weight robustness in unreliable hardware environments.

# Chapter 4

# **Hardware Profiling**

After successful implementation and optimization, the final step in the general DNN implementation workflow is profiling the execution on the target platform [Paper IV] [4]. For this we assume that the resulting accuracy is already evaluated and meets the requirements. In contrast to accuracy evaluation, inference profiling is mostly used to verify the fulfillment of latency and throughput requirements. However, there are plenty of other reasons why a developer might want to assess performance metrics of an application and record a detailed profile. Consequently, the approach taken heavily depends on the deployment requirements of the DNN application and the expected insights. This section outlines the different goals of profiling, the specific metrics of interest, and the granularity at which profiling can be applied. It also explores some of the unique challenges associated with profiling DNNs.

### **Different Goals of Profiling** 4.1

The specific objective of profiling a DNN determines the profiling strategy and the types of insights sought. We can identify several distinct goals for profiling, each with a particular focus [23]:

- · General Profiling and Bottleneck Identification: Profiling can be used to gain an overall understanding of the entire application, identify specific bottlenecks that limit performance, and detect inefficient layers within the network [69]. This involves analyzing the entire pipeline to identify stages or layers that are costly in terms of computation, memory, or data transfer. The gathered knowledge can be used for further optimization efforts such as quantization, pruning, or hardware-specific tuning.

- · Hardware Configuration Optimization: Profiling helps identify the best hardware settings for optimal performance or other design goals, which may include adjusting clock speeds or determining the ideal number of active and used hardware resources, such as processor cores [70].

- Software and Compiler Configuration Optimization: Use profiling to identify optimal software configurations and compiler settings for optimizing performance. This includes adjusting compiler optimization flags, selecting efficient libraries or frameworks, and fine-tuning application-specific parameters [28]. Examples are optimizing for throughput or latency, improving memory usage, and determining the ideal number of threads for parallel execution.

• Data Collection for Modeling: Profiling can also be used to gather data about resource usage, performance, and hardware behavior to model the behavior of DNNs executed on hardware. This data can be used to generate estimation models that help optimize deployment for future tasks [34].

### 4.2 **Metrics to Profile**

When profiling a DNN, several inference metrics are commonly analyzed to gain insights into the performance of the actual execution on hardware. The most crucial metrics for real-time applications are latency, which measures the time taken to execute the DNN from input to output, and throughput, which quantifies the number of inferences the system can process over a given period [23]. For battery-powered or energy-constrained devices, understanding the power and **energy consumption** of the hardware during the execution of the DNN becomes essential [Paper IV] [4]. Finally, hardware resource utilization is key to understanding how well the DNN architecture leverages the underlying hardware [34].

### **Profiling Granularity** 4.3

Finally, the profiling can occur at different levels, starting with the processing pipeline level, where the entire application process, including stages like input, pre-processing, core DNN computation, and decision-making, is analyzed to provide an overview of latency and resource utilization across all components. At a more focused level, profiling can target specific parts of the network, such as the backbone or task-specific heads, to understand how each section contributes to the computational load and identify areas for optimization. Finally, profiling can be performed on individual kernels, offering insights into specific operations that could benefit from optimization or more efficient implementation [Paper IV] [4].

### Challenges in Profiling DNNs 4.4

Although, most hardware vendors provide tools to enable hardware profiling, several open challenges remain. The granularity at which profiling is conducted significantly influences the complexity of acquiring the desired metrics. While in-depth profiling, such as per-kernel latency analysis, is available through tools like Nvidia's Nsight Systems [71] for their Jetson mobile Graphic Processing Unit (mGPU) platform, these tools often introduce overhead, which can skew the results. Nevertheless, relative measurements are still valuable for understanding trends and identifying inefficiencies. On other platforms, such as the NXP i.MX93 development board (i.MX93) [72], extracting similar metrics proves much more difficult, making it challenging to develop tools that work uniformly across different hardware architectures.

Furthermore, obtaining accurate power consumption and hardware resource usage data presents an even greater challenge. Although systems generally have built-in sensors to monitor power usage for system protection, their sampling rates are frequently limited [Paper IV] [4]. Similarly, vendors are often reluctant to disclose detailed hardware utilization information to avoid exposing their internal architectures to reverse engineering.

Lastly, when profiling DNNs, it is essential to consider adjustable settings that can fine-tune both hardware and software. Hardware settings, such as clock speeds, the number of active cores, and power modes, significantly impact key metrics

like latency, throughput, and energy consumption [Paper IV] [4] [70]. A thorough understanding and adjusting these settings enables optimal tuning of the hardware to meet performance requirements. On the software side, execution strategies, including, parallelism, scheduling, and the specific optimization goal (e.g. maximizing throughput, reducing latency, or minimizing power consumption) are equally important. As a result, even for one specific hardware and DNN combination the design space remains vast.

### 4.5 Challenges Addressed in this Work

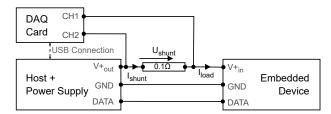

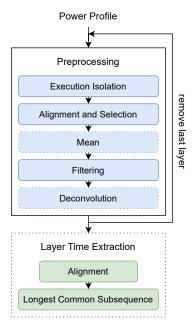

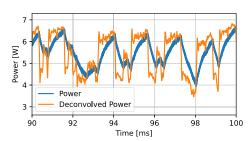

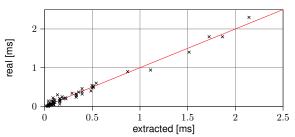

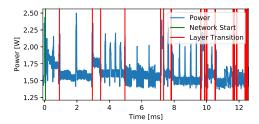

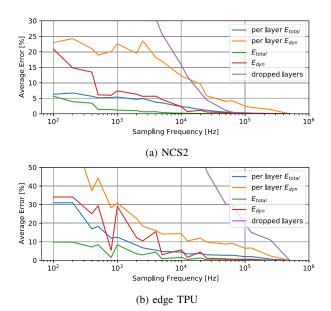

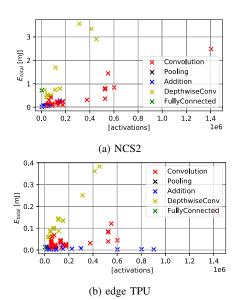

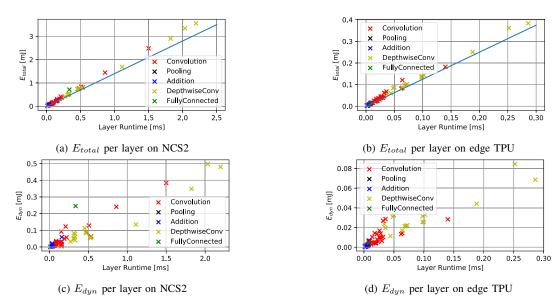

To tackle these challenges we presented two main approaches: Our first approach involved using power side-channel analysis to study the power implications of different operations in the DNN. This method involved monitoring the power consumption of the device while running different layers of a neural network and extracting insights from the power profiles. By correlating the power traces with the known network structure, we were able to understand which layers and operations were the most power-intensive. This approach is especially useful in scenarios where direct access to profiling tools is unavailable or restricted, since it also allowed for extracting per-kernel latency numbers. The method was applied on different neural network accelerators, such as the Intel Neural Compute Stick 2 (NCS2) [73], the Coral Edge Tensor Processing Unit (Edge TPU) [74], and the NXP i.MX8M+ development board (i.MX8M+) [75], revealing the energy efficiency of specific layers under various hardware and software settings like clock frequency or parallel execution threads. The results showed that for the three DNN accelerators, the relationship between power consumption and energy per image can be optimized by adjusting either the number of parallel inference requests or the clock frequency. In both scenarios, power consumption rises when shifting to higher throughput modes, but still leads to a reduction in energy consumed per image overall [Paper IV] [4]. While energy consumption strongly correlates with latency, variations in dynamic power consumption can be attributed to additional factors such as memory access patterns and data movement overheads [76]. Furthermore, the analysis and comparison of different layer types revealed that depth-wise separable convolution layers exhibit lower compute efficiency than standard convolution layers. The systematic benchmarking approaches applied in [Paper I] [1] and [Paper II] [2] provide a solid foundation for conducting a more in-depth analysis, enabling further investigation into underlying performance bottlenecks and improvements in energy consumption modeling.

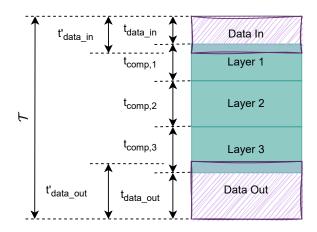

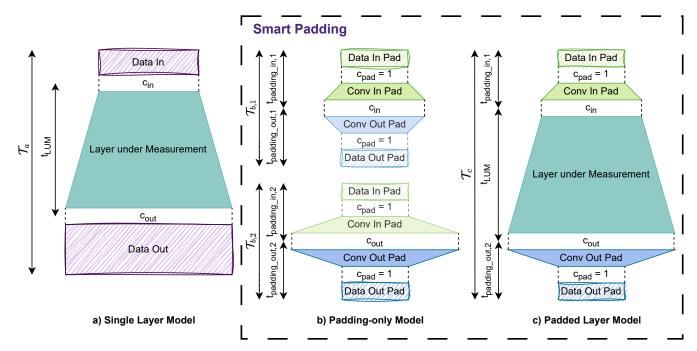

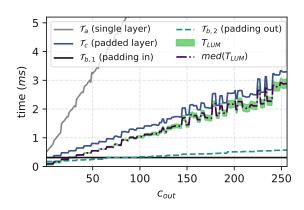

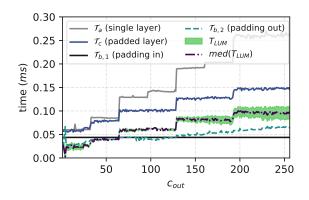

While the power measurements were useful, a more robust technique was required for gathering single layer benchmark data in cases where per-layer latency figures were unavailable. To address this, we introduce a smart padding method [Paper II] [2], which involves using padded versions of specific layers to isolate their performance and measure their impact accurately. The padding involves adding dummy input and output operations, which helps to minimize the overhead from data transfer and makes it easier to isolate the computation of a particular layer. The smart padding approach enables the creation of per-layer abstraction models even when profiling insights are limited. It compensates for data transfer and pipeline inefficiencies, enabling more accurate latency prediction while also significantly reducing the complexity of layer-specific benchmarks. We demonstrated the effectiveness of this approach on the NVIDIA Jetson Xavier AGX (Jetson Xavier) [77], i.MX93 [72], and i.MX8M+ [75] platforms. The empirical results showed that smart padding reduced prediction errors to below 10% for the tested devices [Paper II] [2].

# Chapter 5

# **Conclusions and Outlook**

This thesis has made contributions toward building a structured design and implementation flow for DNN, addressing key challenges in estimation, quantization, and profiling. Through the development of new methodologies and frameworks such as ANNETTE, this work has introduced solutions that enhance the efficiency of DNN deployment on a range of hardware platforms, also highlighting the areas that require further development to achieve the overall goal of a generalizable design and implementation flow.

In the area of estimation, this thesis successfully implemented latency estimation [Paper I] [1] to create a more holistic understanding of DNN behavior on embedded hardware. The combination of analytical and stochastic models proved to be crucial in this field. The introduction of a confidence framework [Paper II] [2] further improves the usability of the prediction results, allowing for more informed performance tuning across a wide range of architectures.

The next logical step is to connect latency estimation with resource utilization and power consumption models, bringing them together into a unified framework. Such a model would not only offer more comprehensive performance predictions but also make use of benchmarking across diverse hardware settings. This could also enable accurate predictions for upcoming hardware generations, leveraging architectural insights. Moreover, refining the confidence methods to include optimizations that occur during graph compilation, will further increase the trustworthiness of the predictions. An additional focus will need to be on an automated analysis and estimation whether a network can be inferred on a target device. This way developers can ensure that the selected or designed network contains only supported layers and fits within the memory constraints of the target hardware.

Quantization plays a crucial role in optimizing DNNs for deployment on resource-constrained devices. The development of WQR provides a method for dynamically adjusting layer precision based on its criticality. However, quantization remains a challenging and evolving area. There is no single method that is perfect for all networks and hardware platforms, and given the rapid pace at which DNN architectures evolve, this is unlikely to change. The field is moving toward smaller integer datatypes, such as INT4 and INT2 [78], but striking the right balance between compression and accuracy will continue to be a key focus.

As the landscape of DNN architectures shifts, future research should aim to improve the flexibility of quantization techniques, ensuring that they can adapt to the demands of new architectures. Although post-training quantization

will likely remain the standard due to its simplicity, methods for QAT will be essential in cases where precision must be maintained despite aggressive quantization. Standards and support for different quantization types will also need to evolve, providing developers with more tools to handle the increasing complexity of DNNs.

Profiling is another area where this thesis has made progress. The use of power side-channel analysis provided valuable insights into the power and latency performance of DNNs at a granular level [Paper IV] [4]. This allows for a detailed understanding of how individual operations impact overall performance, particularly when deployed on embedded platforms. However, despite these advancements, the complexity of the post-processing required for power side-channel analysis prevented the full automation of these measurements. This presents a challenge for scaling the methodology to broader use cases. Additionally, the introduction of the smart padding technique enabled accurate layer isolation for latency profiling, even in the absence of detailed hardware transparency [Paper II] [2].

Future efforts should aim to combine both approaches to enable power consumption and resource estimation. The smart padding could potentially increase the reliability of the power measurements. Automation will also be key to making profiling more scalable, enabling real-time assessments across different hardware platforms, and streamlining the benchmarking process. As hardware architectures continue to diversify, automated profiling tools will be crucial for ensuring that performance predictions remain accurate and consistent across platforms.

As the focus of AI development increasingly shifts toward Large Language Models (LLMs) like GPT [79] and BERT [80], the methodologies developed in this thesis take on new relevance. While this work primarily Convolutional Neural Networks (CNNs), the growing prominence of LLMs presents a set of unique challenges that must be addressed in future research. LLMs are typically much larger than traditional CNNs for vision applications, and their resource requirements, particularly in terms of memory and power consumption, are substantially higher. The resource and power estimation techniques developed here provide a strong foundation, but they will need to be adapted to the specific needs of LLMs. The primary difficulty lies in the fact that many LLM implementations are still highly customized, relying on handoptimized code to achieve maximum performance [81, 82]. Unlike CNNs, where inference frameworks have become widely adopted, LLMs lack such standardization, making their optimization more complex.

Looking ahead, it will be essential to develop more sophisticated resource and power estimation models that fit specifically to LLMs. Hardware support for LLMs is also still evolving, and future research should explore how to optimize these models for next-generation hardware platforms, ensuring that both efficiency and performance are maximized. Standards for LLM optimization will need to mature, and tools that can automate the benchmarking and profiling of these large-scale models will be crucial for their successful deployment.

As AI models and hardware continue to evolve, the need for adaptable, flexible, and efficient design methodologies will only grow. The contributions made in this thesis provide a strong foundation for this evolution, offering valuable insights and tools that will help drive further advancements in DNN optimization. By continuing to refine these methods and adapting them to new technologies, the field will move closer to realizing a fully automated, generalizable DNN design and implementation flow.

In general, there are several major areas to address in extending this research, although their priority will depend on developments in both the community and industry. The following items provide a high-level overview, focusing on situations where resources are limited:

# • Latency Prediction:

- ANNETTE has recently been adapted to work with ONNX, enabling experiments on a variety of state of the art DNNs. Moving beyond CNNs to include transformer-based and other architectures will likely unveil new challenges, and resolving them should further improve latency estimation accuracy.

- In addition to latency, predicting the usage of memory and other resources is crucial. These factors can determine whether a DNN is actually deployable on a given platform. This is especially important for the TinyML domain.

- With the rise of LLMs, time-series models are also gaining traction. Compared to most computer vision workloads, the temporal dependency in frames or samples introduces distinct inference optimization and scheduling strategies, which latency estimation tools should account for, including the different execution scenarios

- Cross-platform prediction that leverages knowledge of prior hardware generations and different architectures is essential. Learning how efficiently one operator performs relative to another across architectures can streamline early design decisions.

### • Quantization:

- Develop hardware-aware, mixed-precision strategies with a focus on automated and general methods. This involves detecting layers that are highly sensitive to quantization and recommending suitable precision assignments and hardware mappings based on that sensitivity.

- Investigate lightweight approaches to QAT (e.g., partial QAT), balancing compute overhead with accuracy requirements, and ensuring these methods align with supported execution standards on common hardware.

- Extend quantization efforts to newer or emerging architectures such as State Space Models (SSMs), which may have different sensitivity patterns and numerical properties than CNNs or transformer-based networks. [83]

### • Hardware Profiling:

- Expand the smart padding (black-box) approach to capture inter-layer interactions and events, improving granularity in performance analysis, but also providing additional insights for estimation.

- Combine vendor-specific insights (e.g., profiling tools, architecture documentation) with black-box measurement approaches to build a more holistic profiling framework.

- Apply the smart padding approach to power profiling, aiming to provide more accurate energy measurements with minimal post-processing overhead.

# Acknowledgments

This dissertation would not have been possible without the support of many people. I would like to express my sincere gratitude to:

- ... my supervisor Axel Jantsch for his excellent guidance, professional advice, and the many inspiring discussions that have significantly shaped this work.

- ... Herbert Taucher, Hannes Muhr, and Martin Matschnig, who made this work possible by initiating the cooperation with TU Wien helped me align my research with practical relevance.

- ... my colleagues at the CD Laboratory, whose company made even the hardest problems and the occasional bite into granite - surprisingly enjoyable.

- ... all the people at ICT, ISAS, and Siemens for the opportunities to learn far beyond my own field and for ensuring that there was never a shortage of good conversations, creative ideas, or freshly brewed coffee.

- ... my brothers and friends, for being fellow travelers not always in the same direction, but always with enough drive to race across the seven seas, or at least up the next summit.

- ... my parents, Maria and Wolfgang, for their constant support and for helping me grow into someone who doesn't always pick the *mittlere*, but often chooses the scenic route instead.

- ... my partner Miriam, whose support and energy got me through every crux this journey had to offer.

This work was supported in part by the Austrian Federal Ministry for Digital and Economic Affairs, in part by the National Foundation for Research, Technology and Development, and in part by the Christian Doppler Research Association.

# **Bibliography**

- [1] M. Wess, M. Ivanov, C. Unger, A. Nookala, A. Wendt, and A. Jantsch, "ANNETTE: accurate neural network execution time estimation with stacked models," IEEE Access, vol. 9, pp. 3545-3556, 2021.

- [2] M. Wess, D. Schnöll, D. Dallinger, M. Bittner, and A. Jantsch, "Conformal prediction based confidence for latency estimation of DNN accelerators: A black-box approach," IEEE Access, vol. 12, pp. 109847-109860, 2024.

- [3] M. Wess, S. M. P. Dinakarrao, and A. Jantsch, "Weighted quantization-regularization in dnns for weight memory minimization toward HW implementation," IEEE TCAD, vol. 37, no. 11, pp. 2929–2939, 2018.

- [4] M. Wess, D. Dallinger, D. Schnöll, M. Bittner, M. Götzinger, and A. Jantsch, "Energy profiling of DNN accelerators," in DSD, pp. 53-60, IEEE, 2023.

- [5] S. V. Mahadevkar, B. Khemani, S. Patil, K. Kotecha, D. R. Vora, A. Abraham, and L. A. Gabralla, "A review on machine learning styles in computer vision—techniques and future directions," IEEE Access, vol. 10, pp. 107293-107329, 2022.

- [6] N. Mohammadi Foumani, L. Miller, C. W. Tan, G. I. Webb, G. Forestier, and M. Salehi, "Deep learning for time series classification and extrinsic regression: A current survey," ACM Computing Surveys, vol. 56, pp. 1–45, Apr. 2024.

- [7] D. W. Otter, J. R. Medina, and J. K. Kalita, "A survey of the usages of deep learning for natural language processing," IEEE Transactions on Neural Networks and Learning Systems, vol. 32, pp. 604–624, Feb. 2021.

- [8] P. Dhilleswararao, S. Boppu, M. S. Manikandan, and L. R. Cenkeramaddi, "Efficient hardware architectures for accelerating deep neural networks: Survey," IEEE Access, vol. 10, pp. 131788–131828, 2022.

- [9] Hugging Face, "Hugging face: The ai community building the future." https://huggingface.co. Accessed: 2024-12-08.

- [10] TorchVision Contributors, "Torchvision: Datasets, transforms, and models for computer vision." https:// pytorch.org/vision/, 2024. Accessed: 2024-12-08.

- [11] Ultralytics, "Ultralytics volo: State-of-the-art object detection models." https://github.com/ ultralytics/yolov5, 2024. Accessed: 2024-12-08.

- [12] O. Community, "Onnx: Open neural network exchange." https://onnx.ai, 2024. Accessed: 2024-12-08.

- [13] N. Corporation, "Nvidia High-performance deep learning inference." https:// tensorrt: developer.nvidia.com/tensorrt, 2024. Accessed: 2024-12-08.

- [14] I. Corporation, "Openvino toolkit: Optimize and deploy ai inference." https://www.intel.com/content/ www/us/en/developer/tools/openvino-toolkit.html, 2024. Accessed: 2024-12-08.

- [15] V. Franzoni, "Cross-domain synergy: Leveraging image processing techniques for enhanced sound classification through spectrogram analysis using cnns," Journal of Autonomous Intelligence, vol. 6, Aug. 2023.

- [16] J. Xu, L. Zhao, S. Zhang, C. Gong, and J. Yang, "Multi-task learning for object keypoints detection and classification," Pattern Recognition Letters, vol. 130, pp. 182-188, 2020. Image/Video Understanding and Analysis (IUVA).

- [17] T. Elsken, J. H. Metzen, and F. Hutter, "Neural architecture search: A survey," in JMLR, 2018.

- [18] S. Han, H. Mao, and W. J. Dally, "Deep compression: Compressing deep neural networks with pruning, trained quantization and huffman coding," in ICLR, 2016.

- [19] B. Haas, A. Wendt, A. Jantsch, and M. Wess, "Neural network compression through shunt connections and knowledge distillation for semantic segmentation problems," in AIAI, vol. 627 of IFIP Advances in Information and Communication Technology, pp. 349-361, Springer, 2021.

- [20] T.-J. Yang, Y.-H. Chen, and V. Sze, "Designing energy-efficient convolutional neural networks using energy-aware pruning," CVPR, July 2017.

- [21] O. Bekhelifi and N.-E. Berrached, "On optimizing deep neural networks inference on cpus for brain-computer interfaces using inference engines," in 2024 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, IEEE, May 2024.

- [22] H. Cai, L. Zhu, and S. Han, "ProxylessNAS: Direct neural architecture search on target task and hardware," in ICLR Poster, 2019.

- [23] V. Sze, Y.-H. Chen, T.-J. Yang, and J. S. Emer, "Efficient processing of deep neural networks: A tutorial and survey," Proceedings of the IEEE, vol. 105, pp. 2295–2329, Dec. 2017.

- [24] L. Mei, H. Liu, T. Wu, H. E. Sumbul, M. Verhelst, and E. Beigne, "A uniform latency model for dnn accelerators with diverse architectures and dataflows," in DATE, IEEE, Mar. 2022.

- [25] S. Miraliev, S. Abdigapporov, V. Kakani, and H. Kim, "Real-time memory efficient multitask learning model for autonomous driving," IEEE Trans. Intell. Veh., vol. 9, no. 1, pp. 247-258, 2024.

- [26] S. Williams, A. Waterman, and D. A. Patterson, "Roofline: an insightful visual performance model for multicore architectures," Commun. ACM, vol. 52, no. 4, pp. 65-76, 2009.

- [27] M. Lechner and A. Jantsch, "Blackthorn: Latency estimation framework for cnns on embedded nvidia platforms," IEEE Access, vol. 9, pp. 110074-110084, 2021.

- [28] D. Schnöll, D. Dallinger, M. Wess, M. Bittner, and A. Jantsch, "Towards optimal implementations of neural networks on micro-controller," in Presented at Workshop on IoT, Edge, and Mobile for Embedded Machine Learning at ECML-PKDD, 2024.

- [29] K. Lübeck, A. L. Jung, F. Wedlich, M. M. Müller, F. N. Peccia, F. Thömmes, J. Steinmetz, V. Biermaier, A. Frischknecht, P. P. Bernardo, and O. Bringmann, "Automatic generation of fast and accurate performance models for deep neural network accelerators," CoRR, vol. abs/2409.08595, 2024.

- [30] A. Samajdar, J. M. Joseph, Y. Zhu, P. N. Whatmough, M. Mattina, and T. Krishna, "A systematic methodology for characterizing scalability of DNN accelerators using scale-sim," in ISPASS, pp. 58-68, IEEE, 2020.

- [31] Y. Braatz, D. S. Rieber, T. Soliman, and O. Bringmann, "Simpyler: A compiler-based simulation framework for machine learning accelerators," in ASAP, pp. 213-220, IEEE, 2023.

- [32] K. G. Mills, F. X. Han, J. Zhang, F. Chudak, A. S. Mamaghani, M. Salameh, W. Lu, S. Jui, and D. Niu, "GENNAPE: towards generalized neural architecture performance estimators," in AAAI, pp. 9190-9199, AAAI Press, 2023.

- [33] L. L. Zhang, S. Han, J. Wei, N. Zheng, T. Cao, Y. Yang, and Y. Liu, "nn-meter: towards accurate latency prediction of deep-learning model inference on diverse edge devices," in MobiSys, MobiSys '21, pp. 81-93, ACM, June 2021.

- [34] Y. Chai, D. Tripathy, C. Zhou, D. Gope, I. Fedorov, R. Matas, D. Brooks, G.-Y. Wei, and P. Whatmough, "Perfsage: Generalized inference performance predictor for arbitrary deep learning models on edge devices," CoRR, vol. abs/2301.10999, 2023.

- [35] K. Panner Selvam and M. Brorsson, "DIPPM: A deep learning inference performance predictive model using graph neural networks," in Lecture Notes in Computer Science (J. Cano, M. D. Dikaiakos, G. A. Papadopoulos, M. Pericàs, and R. Sakellariou, eds.), vol. 14100 of Lecture Notes in Computer Science, pp. 3-16, Springer Nature Switzerland, 2023.

- [36] Z. Wang, P. Yang, L. Hu, B. Zhang, C. Lin, W. Lv, and Q. Wang, "Slapp: Subgraph-level attention-based performance prediction for deep learning models," Neural Networks, vol. 170, pp. 285–297, Feb. 2024.

- [37] A. L. Jung, J. Steinmetz, J. Gietz, K. Lübeck, and O. Bringmann, "It's all about PR smart benchmarking AI accelerators using performance representatives," CoRR, vol. abs/2406.08330, 2024.

- [38] S. Liu, W. Zhou, Z. Zhou, B. Guo, M. Wang, C. Fang, Z. Lin, and Z. Yu, "Deep learning inference on heterogeneous mobile processors: Potentials and pitfalls," in Workshop on Adaptive AIoT Systems at MobiSys, pp. 1-6, ACM, 2024.

- [39] T. Chen, T. Moreau, Z. Jiang, L. Zheng, E. Q. Yan, H. Shen, M. Cowan, L. Wang, Y. Hu, L. Ceze, C. Guestrin, and A. Krishnamurthy, "TVM: an automated end-to-end optimizing compiler for deep learning," in OSDI (A. C. Arpaci-Dusseau and G. Voelker, eds.), pp. 578-594, USENIX Association, 2018.

- [40] B. Jacob, S. Kligys, B. Chen, M. Zhu, M. Tang, A. G. Howard, H. Adam, and D. Kalenichenko, "Quantization and training of neural networks for efficient integer-arithmetic-only inference," in CVPR, pp. 2704-2713, Computer Vision Foundation / IEEE Computer Society, 2018.

- [41] S. Han, J. Pool, J. Tran, and W. Dally, "Learning both weights and connections for efficient neural networks," in NIPS, pp. 1135-1143, 2015.

- [42] M. Courbariaux, Y. Bengio, and J.-P. David, "Binaryconnect: Training deep neural networks with binary weights during propagations," in NIPS, pp. 3123-3131, 2015.

- [43] K. Wang, Z. Liu, Y. Lin, J. Lin, and S. Han, "HAQ: hardware-aware automated quantization with mixed precision," in CVPR, pp. 8612-8620, Computer Vision Foundation / IEEE, 2019.

- [44] H. Wu, P. Judd, X. Zhang, M. Isaev, and P. Micikevicius, "Integer quantization for deep learning inference: Principles and empirical evaluation," CoRR, vol. abs/2004.09602, 2020.

- [45] V. Vanhoucke, A. W. Senior, and M. Z. Mao, "Improving the speed of neural networks on cpus," in Workshop on deep learning and unsupervised feature learning at NIPS, 2011.

- [46] N. P. Jouppi et al., "In-datacenter performance analysis of a tensor processing unit," in ISCA, pp. 1–12, ACM, 2017.

- [47] D. D. Kalamkar, D. Mudigere, N. Mellempudi, D. Das, K. Banerjee, S. Avancha, D. T. Vooturi, N. Jammalamadaka, J. Huang, H. Yuen, J. Yang, J. Park, A. Heinecke, E. Georganas, S. Srinivasan, A. Kundu, M. Smelyanskiy, B. Kaul, and P. Dubey, "A study of BFLOAT16 for deep learning training," CoRR, vol. abs/1905.12322, 2019.

- [48] M. Cococcioni, F. Rossi, E. Ruffaldi, S. Saponara, and B. D. de Dinechin, "Novel arithmetics in deep neural networks signal processing for autonomous driving: Challenges and opportunities," IEEE Signal Process. Mag., vol. 38, no. 1, pp. 97-110, 2021.

- [49] W. Chen, H. Qiu, J. Zhuang, C. Zhang, Y. Hu, Q. Lu, T. Wang, Y. Shi, M. Huang, and X. Xu, "Quantization of deep neural networks for accurate edge computing," JTEC, vol. 17, no. 4, pp. 54:1-54:11, 2021.