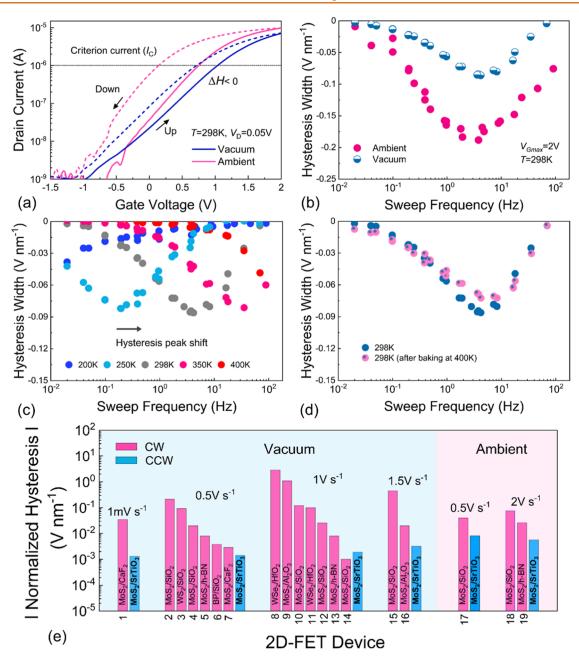

www.acsnano.org

# Stability and Reliability of van der Waals High-κ SrTiO<sub>3</sub> Field-Effect Transistors with **Small Hysteresis**

Seyed Mehdi Sattari-Esfahlan,\* Allen Jian Yang, Rittik Ghosh, Wenwen Zheng, Gerhard Rzepa, Theresia Knobloch, Mario Lanza, Xiao Renshaw Wang, and Tibor Grasser\*

Downloaded via 213.208.157.39 on July 7, 2025 at 08:37:24 (UTC). See https://pubs.acs.org/sharingguidelines for options on how to legitimately share published articles.

Cite This: ACS Nano 2025, 19, 12288-12297

**ACCESS** I

Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: Single-crystal SrTiO<sub>3</sub> (STO) is an ultrahigh-κ insulator with an expected low interface trap density that promises high breakdown strength and has great potential to boost the reliability of two-dimensional (2D) field-effect transistors (FETs). Here we provide a detailed study of the performance, stability, and reliability of MoS2 FETs with STO gate insulators. Most importantly, we observe a small hysteresis for electric fields up to 8 MV cm<sup>-1</sup> at a sweep rate range spanning 0.01-1 V s<sup>-1</sup> and sweep times of kiloseconds. Interestingly, the hysteresis is counterclockwise and bias temperature instability (BTI) is often anomalous, both likely caused by the diffusion of oxygen vacancies. We also show that

the hysteresis dynamics in MoS<sub>2</sub>/STO FETs are reproducible over a long time, which underlines their high reliability. Our findings show that STO is a promising gate insulator that might help overcome critical obstacles to highly reliable 2D nanoelectronics.

KEYWORDS: single-crystal SrTiO<sub>3</sub>, hysteresis width, high-k insulators, field-effect transistors, counterclockwise hysteresis, bias temperature instability

# INTRODUCTION

Ultralow power field-effect transistors (FETs) for nextgeneration two-dimensional (2D) nanoelectronics demand insulators with a high dielectric constant (k) to minimize leakage currents and allow scaling of the physical thickness of the gate dielectric. In addition, a high-quality insulator/channel interface, a large band offset to the semiconducting channel, negligible charge trapping at the interface, and a small density of defects in the gate insulator, to enable good scalability of the equivalent oxide thickness (EOT) are desired. In this regard, various insulators including oxides, 3-5 crystalline 2D materials, 6,7 and amorphous insulators, 8,9 along with oxidized 2D materials 10-12 have been studied for being used in 2D FETs. Contrary to traditional semiconductors like silicon, a seeding layer (an initial layer needed to grow the oxide layer) is required to grow high-k oxides on 2D semiconductors, which can damage the 2D/insulator interface. 13 A clean van der Waals interface can be fabricated by using crystalline 2D insulators such as h-BN<sup>1</sup> or ionic 3D crystals like CaF<sub>2</sub>. Unfortunately, crystalline 2D materials such as h-BN often have a relatively small dielectric constant which eventually

results in high leakage currents when the equivalent thickness is reduced below 1 nm.14 Strontium titanate (SrTiO3), STO for short, is a perovskite material with an ultrahigh dielectric constant (~300).15 STO has an atomically flat surface, allowing the fabrication of multilayer 2D van der Waals heterostructures with atomically sharp interfaces. 16 Furthermore, Yang et al. have transferred wafer-scale STO on MoS<sub>2</sub> using an efficient van der Waals integration technique. 17 Their approach addresses the structural mismatch such as poor 2D/ insulator interface quality and suggests a potential route for the integration of a broad range of oxide-2D material heterostructures for FET device applications. In addition, their report demonstrated the successful fabrication of STO FET devices with MoS<sub>2</sub>, focusing on describing fabrication details and basic

Received: January 18, 2025 Revised: March 12, 2025 Accepted: March 13, 2025 Published: March 19, 2025

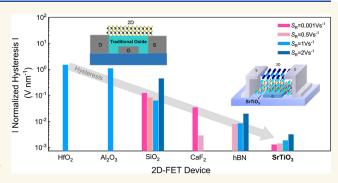

Figure 1. (a) Schematic of the MoS<sub>2</sub>/STO high-k 2D FET with bottom-gate configuration (inset: optical image). (b) A top-view image of the device taken by SEM. The cyan rectangle indicates the approximate location of the FIB cut, as shown in (c) for the HAADF-STEM, EDS, and TEM analyses. (d) The cross-sectional TEM image of the vertically stacked MoS<sub>2</sub>/STO/Au/Cr heterostructure on a SiO<sub>2</sub>/Si substrate from the area highlighted in the cyan rectangle and the corresponding EDS elemental map shows the distribution of Mo, S, Sr, Ti, O, Cr, and Au. (e) Normalized  $I_D$ – $V_D$  characteristic of the device shows saturation at lower  $V_G$ . (f) Normalized  $I_D$ – $V_G$  characteristics were measured by applying different  $V_D$ .

device characteristics. However, benchmarking the potential of a gate insulator material with technological importance demands an accurate understanding of its long-term stability and reliability.

Here, we evaluate the reliability of MoS<sub>2</sub>/STO FETs by examining changes in the transfer characteristics, the dynamics of hysteresis, and bias temperature instability (BTI) in the temperature range 76 to 400 K. We demonstrate that the crystalline STO employed in our samples produces very low counterclockwise (CCW) hysteresis and moderate anomalous BTI at all studied temperatures. Most importantly, we observe that the hysteresis does not change over time following electrical and high-temperature stress.

# **RESULTS AND DISCUSSION**

**Device Structure and Initial Electrical Characterizations.** Figure 1a displays a schematic and an optical image of one of the employed bottom-gate 2D-FET with a high-k STO insulator. The device fabrication details are discussed in the Methods section and the schematics of the fabrication procedure are shown in Figure S1 (in the Supporting Information). Our MoS<sub>2</sub>/STO FETs have typical channel dimensions of  $L=2.5~\mu{\rm m}$  and  $W=5~\mu{\rm m}$ . However, the channel widths may vary among different devices due to the heterogeneity (diversity in size) of the exfoliated MoS<sub>2</sub> flakes. The top-view layout of a device is shown in the scanning electron microscopy (SEM) image (Figure 1b). To confirm the correct fabrication of our devices, we cut a fresh device using a focused ion beam (FIB) at the location indicated with a cyan rectangle as seen in Figure 1b, and fabricated 100 nm-

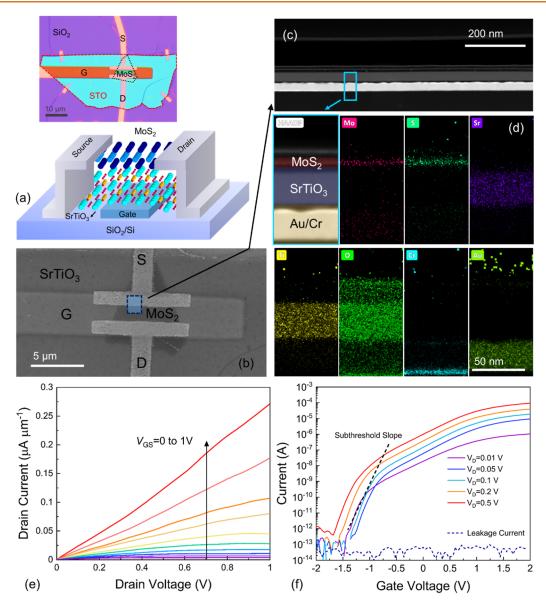

Figure 2. (a) Typical  $I_{\rm D}-V_{\rm G}$  characteristics of a MoS<sub>2</sub>/STO FET measured in vacuum showing a small hysteresis. The  $I_{\rm D}-V_{\rm G}$  characteristics were measured (b) using different gate voltage windows, and (c) during 8 months at vacuum and ambient conditions. (d) Temperature dependence of the  $I_{\rm D}-V_{\rm G}$  characteristics and (e) corresponding leakage current at different T.

thick lamellae. Then, we acquired high-angle annular dark field (HAADF) cross-sectional scanning transmission electron microscope (STEM) images coupled with Energy-dispersive X-ray spectrometry (EDS) elemental maps. The images shown in Figure 1c,d confirm that the structure of the device indeed corresponds to a vertically stacked  $MoS_2/STO/Au/Cr$  heterostructure on a  $SiO_2/Si$  substrate. The multilayered  $MoS_2$  placed on the STO thin film with a physical thickness of  $\sim$ 32 nm, is shown in the top-left panel of Figure 1d. The EDS maps confirm the distribution of Mo, S, Sr, Ti, O, Cr, and Au in the heterostructure. We also acquired high-resolution cross-sectional transmission electron microscopy (TEM) images of the device which confirms the correct crystalline structure of the STO film (see Figure S2).

Typical output  $I_D$ – $V_D$  characteristics measured at different  $V_G$  show promising performance with current saturation and good current control (Figure 1e). The  $I_D$ – $V_G$  characteristics of

the device at different  $V_D$  are shown in Figure 1f, where  $I_D$  is normalized to the channel width (W). Our STO FET showed a maximum normalized current of  $\sim$ 20  $\mu$ A  $\mu$ m<sup>-1</sup> (at  $V_{\rm D}$  = 0.1 V), an  $I_{on}/I_{off}$  ratio of  $10^{7}$ , and a subthreshold slope (SS) value of 270 mV dec<sup>-1</sup>. Also, atomic-force microscope (AFM) imaging was conducted to determine the STO thickness and surface morphology. The thickness of the STO thin film was found to be ~32 nm (see Figure S3). Also, capacitancevoltage (C-V) characteristics for metal/STO/metal (MIM) devices (Figure S4a,b) we conducted at different frequencies as shown in Figure S4c. The capacitance value was found to be constant in the frequency range of 1 kHz to 1 MHz. Based on the C-V data, the relative dielectric constants (k) for a few STO MIM structures were estimated to be about 26 based on a saturation capacitance of ~0.65 pF and device area of ~128  $\mu$ m<sup>2</sup>. Since a low leakage current is critical for reliable FET operation, we determined the leakage current density-electric

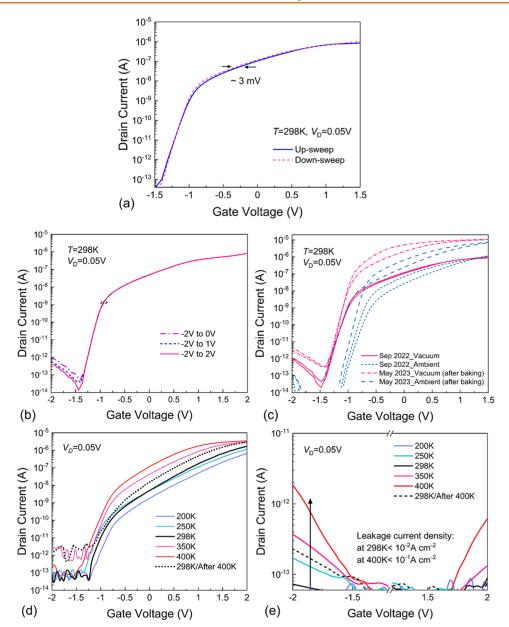

Figure 3. (a) The  $I_D$ – $V_G$  characteristics at vacuum and ambient conditions at T=298 K. Normalized hysteresis widths  $\Delta V_H$  as a function of measurement frequency extracted using a constant current criterion at (b) vacuum and ambient conditions, (c) at different temperatures measured at vacuum conditions, and (d) hysteresis width evolution after high temperature baking steps at 400 K. (e) Comparison of the absolute normalized hysteresis width measured on various 2D-FET technologies at different sweeping rates: 1, ref 2; 2, ref 25; 3, ref 29; 4, ref 30; 5, ref 31; 6, ref 32; 7, ref 2; 8, ref 33; 9, ref 34; 10, ref 35; 11, ref 33; 12, ref 7; 13, ref 7; 14, ref 7; 15, ref 36; 16, ref 36 (in vacuum); 17, ref 30; 18, ref 37; 19, ref 37 (in ambient).

field characteristics of our  $\rm MoS_2/STO$  FET, see Figure S5. The device exhibited a leakage current density of  $\sim 10^{-4}$  A cm<sup>-2</sup> at 7.8 MV/cm at an equivalent oxide thickness of  $\sim 4.8$  nm, which is small compared to values measured on many other common gate insulators. <sup>14,18–20</sup> The small leakage current of our STO is likely due to the crystalline structure which minimizes trapassisted tunneling. However, further improvement in the processing steps, including the 2D transfer, sample cleaning procedure, and growth quality of the insulator will likely further reduce the leakage current and the observed SS of the devices.

Transfer Characteristics and Temperature-Dependent Leakage Current.  $I_{\rm D}-V_{\rm G}$  characteristics were measured at T=298 K using both forward and backward sweeps, see Figure 2a. For a sweep rate of  $S_{\rm R}=0.1$  V s<sup>-1</sup>, we observe no significant difference in  $I_{\rm D}$  during up- and down-sweeps of the gate voltage, with a small hysteresis width  $(\Delta V_{\rm H})$  less than 3 mV. Also, we investigate the dependence of the  $I_{\rm D}-V_{\rm G}$  characteristics measured at T=298 K for different gate voltage sweep ranges at  $S_{\rm R}=1$  V s<sup>-1</sup>. As shown in Figure 2b, the main device parameters such as threshold voltage  $(V_{\rm TH})$  and SS are independent of the gate bias window width. Moreover, to check whether our devices age over a long time

period with repetitive measurement processes both at room temperature and at higher temperatures for baking, we tracked I<sub>D</sub>-V<sub>G</sub> characteristics during eight months of measurements followed by storage of the devices at vacuum and ambient conditions. As shown in Figure 2c, after the storage of the FETs under ambient conditions for 1 day, the threshold voltage is shifted to more positive values. Also, the hysteresis width was increased compared to the vacuum measurement, which is seemingly due to adsorbents which cause a 2× increase in hysteresis almost over the whole range of  $V_{\rm G}$ . However, we did not observe any significant effect on the SS and saturation current caused by ambient exposure. In addition, we measured device characteristics eight months after a high-temperature measurement at 350 and 400 K. An increase in the saturation currents can be seen for the curves repeated after eight months which may originate from the reduction of the contact resistances through the backing process in different stages of the experiments. Moreover, we did not observe a considerable threshold voltage shift of about 190 mV for our device over this eight-month storage time. Thus, a comparison of the  $I_D$ – $V_G$  curves measured over eight months proves that the device maintained its functionality over time.

The thermal activation of charge trapping, as well as impurity, and vacancy diffusion, is crucial for 2D-FET performance. Thus, understanding the impact of temperature is necessary for evaluating device behavior. We investigated the transfer curve of the device in the temperature range of 76 K to 400 K and we show some representative  $I_D$ – $V_G$  curves in Figure 2d. The critical device parameters were extracted to understand the role of temperature on the transfer characteristics. Most importantly, the drain current decreases with decreasing temperature where the saturation current reduces by almost 2 orders of magnitude when going from 400 K to 76 K. Also, the evolution of the On and Off currents as well as the threshold voltages throughout the temperature range are demonstrated in Figure S6. The On/Off current ratio was degraded at elevated temperatures and  $V_{\mathrm{TH}}$  gradually shifted toward more negative values at high temperatures (see Figure S6a,b). The  $V_{\rm TH}$  at room temperature is ~0.7 V and shifts to 1.6 V at 76 K. Despite the positive shift of  $V_{\rm TH}$  at low temperatures, it shifted to a negative voltage of  $\sim$  -0.25 V at 400 K. In Figure 2e we show the gate leakage current  $(I_G)$  over temperature. We obtained a small leakage current  $I_{\rm G}$  at T = 298 K which increased to  $\sim 10^{-1}$  A cm<sup>-2</sup> at 400 K which is still below 1 A cm<sup>-1</sup> at  $V_G = 2$  V. However,  $I_G$  is increased by about 2 orders of magnitude at 400 K, likely due to an increased thermionic emission over the relatively small barrier.

Analysis of the Hysteresis. To investigate the hysteresis behavior in the device, we show  $I_{\rm D}-V_{\rm G}$  characteristics measured in a vacuum and 1 h after ambient exposure at  $f_{\rm s}=4$  Hz as shown in Figure 3a. The sweeping frequency is  $f_{\rm s}=1/t_{\rm sw}$  where  $t_{\rm sw}$  is the time for one entire sweep in Figure 3b. The hysteresis width is calculated as  $V_{\rm H}=V_{\rm TH,down}-V_{\rm TH,up}$  using a constant current criterion ( $I_{\rm C}$ ) for the determination of the threshold voltage. Our device exhibits a small counterclockwise hysteresis width in vacuum which increases by a factor of 2 following ambient exposure. The measured hysteresis widths are normalized by the equivalent oxide thickness<sup>21</sup> (EOT = 4.8 nm). Interestingly, while the majority of our devices show CCW hysteresis (Figure 3b), a single device showed clockwise (CW) hysteresis. The hysteresis values remain small for all  $f_{\rm s}$  and with a maximum normalized

value of  $\sim$ 74 mV nm<sup>-1</sup>. The hysteresis width peak value is increased by about 2.5× to  $\sim$ 190 mV nm<sup>-1</sup> during exposure of the device to the ambient.

While CW hysteresis is typically due to charge trapping of the electrons from the channel in insulator defects, several other mechanisms have been proposed as contributors to counterclockwise (CCW) hysteresis ( $\Delta V_{\rm H} < 0$ ) such as carrier tunneling through the traps in the MoS<sub>2</sub> layer, <sup>22</sup> thermal activation of oxide defects, <sup>23</sup> and mobile ions in the insulator layer. <sup>24,25</sup> We propose that the CCW hysteresis in our MoS<sub>2</sub>/STO FETs is caused by the diffusion of oxygen vacancies initially formed in the STO thin film during growth. <sup>26,27</sup> A schematic illustration of the diffusion of mobile oxygen ions at different gate voltages is given in Figure S7. Also, we suggest that the increased CCW hysteresis in ambient conditions could be related to the adsorption/diffusion of oxygen and water molecules into the STO which modifies the concentration of available oxygen vacancies.

The normalized hysteresis width versus the sweeping frequency  $f_s$  at different temperatures is shown in Figure 3c. The hysteresis width is observed to be CCW at all temperatures while the peak of the hysteresis moves toward increasingly higher frequencies for elevated temperatures. The initial measurement was conducted at T = 298 K where a CCW hysteresis with a peak at  $\sim f_s = 0.1$  Hz is observed. Then, the temperature was reduced to 250 and 200 K, respectively. Notably, the hysteresis peak was observed to be shifted to smaller  $f_s$  (faster sweeping rate) at lower temperatures (250 and 200 K) consistent with the fact that the mobility of the mobile ions decreases at lower temperatures. Then, we increased the temperature to 350 and 400 K, and the hysteresis peak shifted to faster sweeping frequencies. Also, to determine whether any electrochemical changes occurred in the device at these high temperatures, we measured the hysteresis width at 298 K after the measurement at 400 K as shown in Figure 3d. Importantly, the overall behavior of the hysteresis before/after the high-temperature step remained consistent which confirms recovery of the device. While virtually all devices showed CCW hysteresis, one of our devices showed CW hysteresis as a response to the same measurement procedure (Figure S8a), which is likely attributed to the higher trap density within the STO caused by variations in device processing for this particular sample. Similar to the hysteresis peak in Figure 3c, one can observe that the hysteresis peak shifts to higher frequencies as the time constants of the involved traps become smaller at higher temperatures. Also, at high sweep frequencies, the hysteresis width becomes slightly larger as the temperature is increased. However, only the left part of the hysteresis peak could be recorded in our measurements. A similar behavior was observed in previous works for MoS<sub>2</sub> FETs<sup>7,28</sup> with SiO<sub>2</sub> and CaF<sub>2</sub> as an insulator. The link of the CW hysteresis with charge trapping in STO close to the MoS<sub>2</sub> interface is shown in Figure S8b. In general, a small hysteresis width is considered a critical factor for reliable device operation. Therefore, we compare the  $\Delta V_{

m H}$  of our devices with various 2D FET technologies at different V<sub>G</sub> sweeping rates and at vacuum/ ambient conditions as shown in Figure 3e. Our MoS<sub>2</sub>/STO device shows promising hysteresis stability compared to other devices with ultralow hysteresis widths of around 2, and 9 mV nm<sup>-1</sup> at vacuum and ambient conditions, respectively (e.g., at a sweeping rate of 0.5 V/s).

Bias Temperature Instability (BTI). Oxide border traps can capture and emit carriers, resulting in various insta-

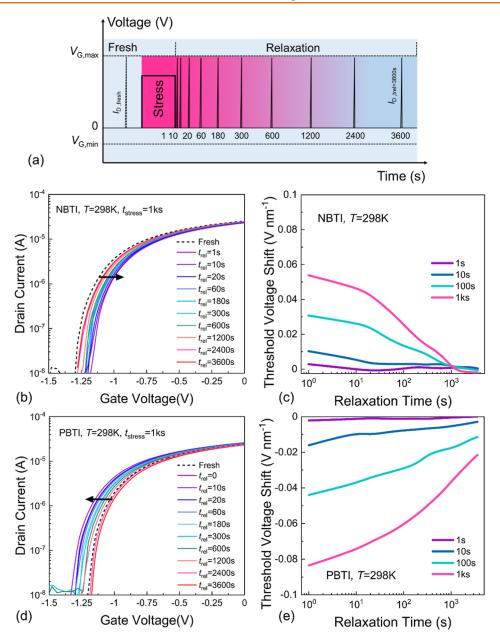

Figure 4. (a) A BTI measure-stress-measure procedure. Evolution of the transfer characteristics after applying subsequent BTI stresses with increasing stress times of  $t_s = 1$  s, 10 s, 100 s, and 1 ks, under (b) negative stress bias and (c) corresponding NBTI shift, and similarly at positive stress bias (d,e) for the MoS<sub>2</sub>/STO FETs at T = 298 K.

bilities. 9,34,38 In addition to hysteresis in the transfer characteristics, the long-term drift of the threshold voltage is among the most recognized reliability challenges in 2D- and Si-FET devices, particularly due to its strong bias and temperature dependence. 19,32,39,40 The application of gate bias stress for a certain time  $t_s$  shifts  $V_{\rm TH}$  typically due to electron capture in defects moved below the Fermi level  $(E_{\rm F})$ . If a positive stress bias is applied, one speaks of positive BTI (PBTI) and similarly, of negative BTI (NBTI) for a negative stress bias.<sup>41</sup> Note that the hysteresis width  $\Delta V_{

m H}$  as discussed in the previous section is closely related to the BTI  $V_{\rm TH}$  shift. Typically, the faster population of the traps contributes to the hysteresis while the slower ones to BTI.7 We show the employed BTI measure-stress-measure procedure in Figure 4a. First, we applied negative stress bias  $(V_{G,stress})$  to the device to perform NBTI measurements. We show the normalized BTI (normalized by the factor of EOT, the same as for hysteresis) results obtained by subsequent stress/relaxation cycles for different stress times  $(t_s)$ . Then, we measured transfer characteristics before applying any stress voltages. Next, the FET is subjected to negative gate bias stress  $(V_{G,\text{stress}})$  for varying stress times of  $t_s = 1$ , 10, 100, and 1 ks. After the stress period, an  $I_D$ – $V_G$  curve is measured to determine the  $V_{TH}$  shift using a constant criterion current. We observed a positive  $V_{\rm TH}$ shift (degradation) of the  $I_{\rm D} - V_{\rm G}$  characteristics for NBTI at higher stress times which recovers nearly completely (Figure 4b). However, the  $V_{\rm TH}$  shift becomes more pronounced with increasing stress time but it is still relatively small even at a long stress time (e.g., 55 mV nm<sup>-1</sup> at  $t_s = 1$  ks and shortest recovery time  $t_{rel} = 1$  s). Next, we applied a positive  $V_{G,stress}$  to investigate PBTI. The  $I_D$ – $V_G$  characteristics in Figure 4c show that the shift is negative for PBTI and its absolute value is

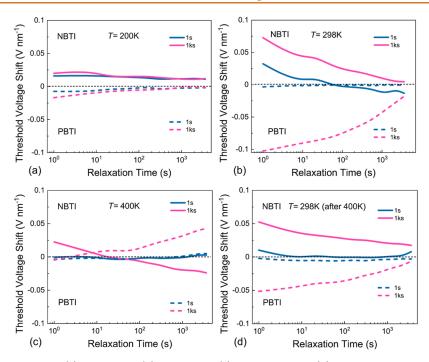

Figure 5. Anomalous NBTI/PBTI, at (a) T = 200 K, (b) T = 298 K, (c) T = 400 K, and (d) T = 298 K after high-temperature annealing.

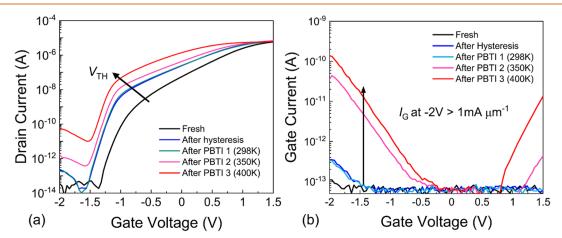

Figure 6. (a) Change in the  $I_D$ - $V_G$  characteristics and (b)  $I_G$ - $V_G$  characteristics after a series of hysteresis and BTI measurements.

larger than for NBTI. The NBTI and PBTI behavior of the device are shown in Figures 4d,e, respectively. The device shows small degradation under various PBTI stresses. Both the observed BTI degradation and the narrow hysteresis width  $\Delta V_{\rm H}$  at T=298 K consistently indicate good device stability and reliability. Also, the recovery after NBTI stress is faster than recovery after PBTI stress. Note that the sign of the  $V_{\rm TH}$ shift is different for NBTI and PBTI and that both are anomalous, 42 that is, having a different sign of what would be expected from charge trapping. This aligns with the hysteresis measured at T = 298 K (Figure 3b,c) and suggests that migrating oxygen ions existing inside the STO thin film could also be responsible for this anomalous degradation. Also note that PBTI is relatively larger than NBTI at stress time  $t_s = 1$  ks, possibly because the mobile species is in a different charge state and has a different migration barrier.

Next, we analyzed the impact of temperature on the dynamics of BTI. A sequence of measurements was carried out at T = 200, 298, and 400 K. Then, BTI was remeasured at 298 K following the measurement at 400 K using the same

measurement procedure as that of Figure 4. We show the normalized NBTI/PBTI degradation at T = 200 K after a stress time of  $t_s = 1$  s and 1 ks in Figure 5a. The degradation seems to be small with an anomalous  $V_{\rm TH}$  shift of <20 mV nm<sup>-1</sup> for both NBTI and PBTI. This is expected because mobile ions would freeze out at low temperatures and thus not contribute to BTI. After switching back to T = 298 K the degradation becomes more pronounced and also again being anomalous (Figure 5b). The PBTI degradation seems to be somewhat larger than NBTI. With increasing the temperature to T = 400 K, BTI at short relaxation time is reduced. During recovery, both NBTI and PBTI directions change from anomalous to regular for long recovery times (Figure 5c). We argue that in addition to the mobile ions in STO, charge trapping from the MoS<sub>2</sub> channel can be activated at higher temperatures. Finally, we performed a BTI test back at T = 298K (10 days after performing the BTI at T = 400 K) and the anomalous BTI is pronounced again where there is a small difference between the  $V_{\rm TH}$  shifts recorded pre- and postannealing. The device was fully recovered after NBTI

degradation within about 7 h (Figure 5d). However, PBTI only partially recovers possibly due to the contribution of deeper trap levels inside the gate oxide layer or some more permeant changes in the device occurring during stress.

Finally, we compare the transfer curve of our devices after each measurement step including hysteresis and frequent BTI tests as shown in Figure 6a. We observe a negative  $V_{TH}$  shift of the transfer curve after the sequence of hysteresis measurements compared to the fresh devices, indicating the occurrence of fixed positive charges in the STO film. While no additional changes in the  $I_{\rm D}{-}V_{\rm G}$  characteristics were observed after the 298 K BTI experiment,  $V_{\mathrm{TH}}$  was shifted to more negative voltages and SS degraded after PBTI tests at T = 350 K and T= 400 K. The negative shift of  $V_{\rm TH}$  is related to the accumulation of positive charges in STO, possibly the creation of oxygen vacancies during the voltage stress and annealing cycles. Also, the leakage current increased by more than 2 orders of magnitude compared to the fresh device as shown in Figure 6b. However, even at high temperatures, the leakage current density remains smaller than 1 mA  $\mu$ m<sup>-1</sup>.

### **CONCLUSIONS**

We fabricated MoS<sub>2</sub> FETs using single crystalline STO as a high-k dielectric and conducted an in-depth study on their electrical properties, hysteresis dynamics, and bias temperature instability. We observed that the MoS<sub>2</sub>/STO FETs had good electrical stability, most of them with a small CCW (anomalous) hysteresis. The hysteresis behavior is reproducible and remains relatively stable over 8 months. The CCW hysteresis is attributed to the diffusion of oxygen vacancies initially formed during STO growth. Also, BTI degradation is found to be anomalous which is likely also caused by mobile oxygen vacancies in the STO layer. The high long-term stability of our devices confirms that crystalline STO is a promising insulator for next-generation 2D nanoelectronics.

# **METHODS**

**Material Preparation.** The  $\rm Sr_3Al_2O_6$  (SAO) sacrificial layer was grown by PLD on a bulk STO (001) substrate kept at 800 °C. Then, the STO film was grown at 750 °C and cooled to room temperature. The oxygen partial pressures for SAO and STO growth were  $2\times 10^{-5}$  and  $1\times 10^{-1}$  Torr, respectively. After growth, the STO film was lifted off by covering it with a PDMS sheet and dissolving the SAO layer in deionized water. The STO film on PDMS was aligned under an optical microscope and pressed onto the prefabricated Au gate electrodes on  $\rm Si/SiO_2$  substrates. The STO film remained on the  $\rm Si/SiO_2$  substrates after peeling off the PDMS sheet for the next device fabrication steps.

**Device Fabrication.** The STO film was grown by the pulsed laser deposition (PLD) method on  ${\rm TiO_2\text{-}terminated}$  STO (001) substrates. The back gate electrode was fabricated on a  ${\rm SiO_2/Si}$  substrate followed by thermal deposition of 5 nm Cr and 60 nm Au. Next, the STO surface was covered by a PDMS sheet and was peeled off gently to leave the STO flake on the initially cleaned  ${\rm SiO_2/Si}$  substrate containing the fabricated back gate electrode. Then, the mechanically exfoliated  ${\rm MoS_2}$  flake was aligned under an optical microscope and transferred to  ${\rm STO/SiO_2/Si}$ . The drain and source electrode area were determined using electron-beam lithography followed by thermal deposition of 5 nm Cr and 60 nm Au. Finally, a metal lift-off was carried out to remove extra metals and achieve drain and source electrodes.

**Material Characterization.** HADDF-STEM imaging and EDX analysis were performed at 200 kV using Titan Cs probe equipment from FEI. The AFM surface profile and thickness were performed by the Reith-83 instrument.

**Electrical Measurement.** Both  $I_{\rm D}-V_{\rm G}$  and  $I_{\rm D}-V_{\rm D}$  characteristics were performed using a Keithley 2636 parameter analyzer in the chamber of a Lakeshore vacuum probe station ( $\sim$ 2 × 10<sup>-6</sup> Torr) in dark conditions. The hysteresis of the  $I_{\rm D}-V_{\rm G}$  characteristics was studied by performing double sweeps at different sweep times. The BTI behavior was measured by subsequent stress/recovery tests.

# **ASSOCIATED CONTENT**

# **Solution** Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.5c01145.

Fabrication process, TEM images of metal/STO/metal structure, AFM, capacitance measurements, current density over electric field, and hysteresis mechanism (PDF)

#### **AUTHOR INFORMATION**

# **Corresponding Authors**

Seyed Mehdi Sattari-Esfahlan — Institute for Microelectronics (TU Wien), 1040 Vienna, Austria; orcid.org/0000-0002-4596-6015; Email: sattari@iue.tuwien.ac.at

Tibor Grasser — Institute for Microelectronics (TU Wien), 1040 Vienna, Austria; orcid.org/0000-0001-6536-2238; Email: grasser@iue.tuwien.ac.at

## **Authors**

Allen Jian Yang — Division of Physics and Applied Physics, School of Physical and Mathematical Sciences, Nanyang Technological University, Singapore 637371, Singapore Rittik Ghosh — Institute for Microelectronics (TU Wien),

1040 Vienna, Austria; o orcid.org/0000-0003-3656-9533

Wenwen Zheng — Materials Science and Engineering Program, Physical Sciences and Engineering Division, King Abdullah University of Science and Technology, Thuwal 23955-6900, Saudi Arabia

Gerhard Rzepa – Global TCAD Solutions, 1010 Vienna, Austria

Theresia Knobloch — Institute for Microelectronics (TU Wien), 1040 Vienna, Austria; ocid.org/0000-0001-5156-9510

Mario Lanza – Department of Materials Science and Engineering, National University of Singapore, Singapore 117575, Singapore

Xiao Renshaw Wang — Division of Physics and Applied Physics, School of Physical and Mathematical Sciences, Nanyang Technological University, Singapore 637371, Singapore; School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, Singapore; orcid.org/0000-0002-5503-9899

Complete contact information is available at: https://pubs.acs.org/10.1021/acsnano.5c01145

#### Notes

The authors declare no competing financial interest.

# **ACKNOWLEDGMENTS**

We would like to express our gratitude to Huawei Technologies R&D Belgium for their generous financial support, which was instrumental in advancing this research. Furthermore, this work was supported by the European Research Council under Grant Agreement no. 101055379 (F2GO). Also, X.R.W. acknowledges support from the Singapore Ministry of Education (MOE) Academic Research

Fund Tier 3 grant (MOE-MOET32023-0003) entitled "Quantum Geometric Advantage". Eventually, S.M.S-E acknowledges the Vienna University of Technology Library for financial support through its Open Access Funding Programme.

# **REFERENCES**

- (1) Yankowitz, M.; Ma, Q.; Jarillo-Herrero, P.; LeRoy, J. B. van der Waals heterostructures combining graphene and hexagonal boron nitride. *Nat. Rev. Phys.* **2019**, *1*, 112–125.

- (2) Illarionov, Y. Y.; Banshchikov, A. G.; Polyushkin, D. K.; et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. *Nat. Electron.* **2019**, *2*, 230–235.

- (3) Allain, A.; Kis, A. Electron and hole mobilities in single-layer WSe<sub>2</sub>. ACS Nano **2014**, 8, 7180–7185.

- (4) Pan, Y.; Jia, K.; Huang, K.; Wu, Z.; Bai, G.; Yu, J.; Zhang, Z.; Zhang, Q.; Yin, H. Near-Ideal Subthreshold Swing MoS<sub>2</sub> Back-Gate Transistors with an Optimized Ultrathin HfO<sub>2</sub> Dielectric Layer. *Nanotechnology* **2019**, *30*, 095202.

- (5) Bolshakov, P.; Zhao, P.; Azcatl, A.; Hurley, P. K.; Wallace, R. M.; Young, C. D. Improvement in Top-gate MoS<sub>2</sub> Transistor Performance Due to High Quality Backside Al<sub>2</sub>O<sub>3</sub> Layer. *Appl. Phys. Lett.* **2017**, *111*, 032110.

- (6) Liu, Y.; Weiss, N. O.; Duan, X.; Cheng, H. C.; Huang, Y.; Duan, X. Van Der Waals Heterostructures and Devices. *Nat. Rev. Mater.* **2016**, *1*, 16042.

- (7) Illarionov, Y. Y.; Rzepa, G.; Waltl, M.; Knobloch, T.; Grill, A.; Furchi, M. M.; Mueller, T.; Grasser, T. The Role of Charge Trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN Field-Effect Transistor. 2D Mater. **2016**, *3*, 035004.

- (8) Hasan, M. M.; Roy, S.; Mohit; Tokumitsu, E.; Chu, H.-Y.; Kim, S. C.; Jang, J. High performance, amorphous InGaZnO thin-film transistors with ferroelectric ZrO<sub>2</sub> gate insulator by one step annealing. *Appl. Surf. Sci.* **2023**, *611*, 155533.

- (9) Sattari-Esfahlan, S. M.; Kim, H.-G.; Hyun, S.-H.; Choi, J. H.; Hwang, H. S.; Kim, E. T.; Park, H. G.; Lee, J. H. Low-Temperature Direct Growth of Amorphous Boron Nitride Films for High-Performance Nanoelectronic Device Applications. *ACS Appl. Mater. Interfaces* **2023**, *15*, 7274–7281.

- (10) Zou, X.; Liang, H.; Li, Y.; Zou, Y.; Tian, F.; Sun, Y.; Wang, C. 2D Bi<sub>2</sub>O<sub>2</sub>Te Semiconductor with Single-Crystal Native Oxide Layer. *Adv. Funct. Mater.* **2023**, 33, 2213807.

- (11) Chamlagain, B.; Cui, Q.; Paudel, S.; Cheng, M. M.-C.; Chen, P.-Y.; Zhou, Z. Thermally Oxidized 2D TaS<sub>2</sub> as a High-k Gate Dielectric for MoS<sub>2</sub> Field-Effect Transistors. 2D Mater. **2017**, 4, 031002.

- (12) Lai, S.; Byeon, S.; Jang, S. K.; Lee, J.; Lee, B. H.; Park, J.-H.; Kim, Y.-H.; Lee, S. HfO<sub>2</sub>/HfS<sub>2</sub> Hybrid Heterostructure Fabricated via Controllable Chemical Conversion of Two-Dimensional HfS<sub>2</sub>. *Nanoscale* **2018**, *10*, 18758–18766.

- (13) Sheng, Y.; Chen, X.; Liao, F.; Wang, Y.; Ma, J.; Deng, J.; Guo, Z.; Bu, S.; Shen, H.; Bai, F.; Huang, D.; Wang, J.; Hu, W.; Chen, L.; Zhu, H.; Sun, Q.; Zhou, P.; Zhang, D. W.; Wan, J.; Bao, W. Gate Stack Engineering in MoS<sub>2</sub> Field-Effect Transistor for Reduced Channel Doping and Hysteresis Effect. *Adv. Electron. Mater.* **2021**, 7, 2000395.

- (14) Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; Mayorov, A. S.; Peres, N. M.; et al. Electron Tunneling through Ultrathin Boron Nitride Crystalline Barriers. *Nano Lett.* **2012**, *12*, 1707–1710.

- (15) Couto, N. J.; Sacépé, B.; Morpurgo, A. F. Transport through graphene on SrTiO<sub>3</sub>. *Phys. Rev. Lett.* **2011**, 107, 225501.

- (16) Huang, J.-K.; Wan, Y.; Shi, J.; Zhang, J.; Wang, Z.; Wang, W.; Yang, N.; Liu, Y.; Lin, C.-H.; Guan, X.; Hu, L.; Yang, Z.-L.; Huang, B.-C.; Chiu, Y.-P.; Yang, J.; Tung, V.; Wang, D.; Kalantar-Zadeh, K.; Wu, T.; Zu, X.; Qiao, L.; Li, L.-J.; Li, S. High-κ Perovskite Membranes as Insulators for Two-Dimensional Transistors. *Nature* **2022**, *605*, 262–267.

- (17) Yang, A. J.; Han, K.; Huang, K.; Ye, C.; Wen, W.; Zhu, R.; Zhu, R.; Xu, J.; Yu, T.; Gao, P.; et al. Van der Waals integration of high- $\kappa$  perovskite oxides and two-dimensional semiconductors. *Nat. Electron.* **2022**, *5*, 233–240.

- (18) Guha, S.; Cartier, E.; Bojarczuk, N. A.; Bruley, J.; Gignac, L.; Karasinski, J. High-Quality Aluminum Oxide Gate Dielectrics by Ultra-High-Vacuum Reactive Atomic-Beam Deposition. *J. Appl. Phys.* **2001**, *90*, 512–514.

- (19) Iwai, H.; Ohmi, S.; Akama, S.; Ohshima, C.; Kikuchi, A.; Kashiwagi, I.; Taguchi, J.; Yamamoto, H.; Tonotani, J.; Kim, Y.; Ueda, I. Advanced gate dielectric materials for sub-100 nm CMOS. In *Digest. International Electron Devices Meeting*; IEEE, 2002, pp 625–628.

- (20) Illarionov, Y. Y.; Knobloch, T.; Uzlu, B.; Banshchikov, A. G.; Ivanov, I. A.; Sverdlov, V.; Otto, M.; Stoll, S. L.; Vexler, M. I.; Waltl, M.; et al. Variability and high temperature reliability of graphene field-effect transistors with thin epitaxial  $CaF_2$  insulators. *npj 2D Mater. Appl.* **2024**, *8*, 23.

- (21) Knobloch, T.; Waldhoer, D.; Davoudi, M. R.; Karl, A.; Khakbaz, P.; Matzinger, M.; Zhang, Y.; Smithe, K. K. H.; Nazir, A.; Liu, C.; Illarionov, Y. Y. Modeling the Performance and Reliability of Two-Dimensional Semiconductor Transistors. In 2023 International Electron Devices Meeting (IEDM); IEEE, 2023, pp 1–4.

- (22) Sup Choi, M.; Lee, G. H.; Yu, Y. J.; Lee, D. Y.; Hwan Lee, S.; Kim, P.; Hone, J.; Jong Yoo, W. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. *Nat. Commun.* **2013**, *4*, 1624.

- (23) Kaushik, N.; Mackenzie, D. M.; Thakar, K.; Goyal, N.; Mukherjee, B.; Boggild, P.; Petersen, D. H.; Lodha, S. Reversible hysteresis inversion in MoS<sub>2</sub> field effect transistors. *npj 2D Mater. Appl.* **2017**, *1*, 34.

- (24) Provias, A.; Knobloch, T.; Kitamura, A.; O'Brien, K. P.; Dorow, C. J.; Waldhoer, D.; Stampfer, B.; Penumatcha, A. V.; Lee, S.; Ramamurthy, R.; Clendenning, S. Reliability Assessment of Double-Gated Wafer-Scale MoS<sub>2</sub> Field Effect Transistors through Hysteresis and Bias Temperature Instability Analyses. In 2023 International Electron Devices Meeting (IEDM); IEEE, 2023, pp 1–4.

- (25) Ye, Z.; Yuan, Y.; Xu, H.; Liu, Y.; Luo, J.; Wong, M. Mechanism and Origin of Hysteresis in Oxide Thin-Film Transistor and its Application on 3-D Nonvolatile Memory. *IEEE Trans. Electron Devices* **2017**, *64*, 438–446.

- (26) Kalabukhov, A.; Gunnarsson, R.; Börjesson, J.; Olsson, E.; Claeson, T.; Winkler, D. Effect of oxygen vacancies in the SrTiO 3 substrate on the electrical properties of the LaAlO 3/SrTiO 3 interface. *Phys. Rev. B:Condens. Matter Mater. Phys.* **2007**, 75 (12), 121404

- (27) Park, J.; Kwon, D. H.; Park, H.; Jung, C. U.; Kim, M. Role of oxygen vacancies in resistive switching in Pt/Nb-doped SrTiO<sub>3</sub>. *Appl. Phys. Lett.* **2014**, *105* (18), 183103.

- (28) Illarionov, Y. Y.; Banshchikov, A. G.; Polyushkin, D. K.; Wachter, S.; Knobloch, T.; Thesberg, M.; Vexler, M. I.; Waltl, M.; Lanza, M.; Sokolov, N. S.; Mueller, T.; Grasser, T. Reliability of scalable MoS<sub>2</sub> FETs with 2 nm crystalline CaF<sub>2</sub> insulators. 2D Mater. **2019**, *6*, 045004.

- (29) Lan, C.; Kang, X.; Meng, Y.; Wei, R.; Bu, X.; Yip, S.; Ho, J. C. The origin of gate bias stress instability and hysteresis in monolayer WS<sub>2</sub> transistors. *Nano Res.* **2020**, *13*, 3278–3285.

- (30) Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. *ACS Nano* **2012**, *6*, 5635–5641.

- (31) Vu, Q. A.; Fan, S.; Lee, S. H.; Joo, M. K.; Yu, W. J.; Lee, Y. H. Near-zero hysteresis and near-ideal subthreshold swing in h-BN encapsulated single-layer MoS<sub>2</sub> field-effect transistors. 2D Mater. **2018**, 5, 031001.

- (32) Illarionov, Y. Y.; Waltl, M.; Rzepa, G.; Kim, J. S.; Kim, S.; Dodabalapur, A.; Akinwande, D.; Grasser, T. Long-term stability and reliability of black phosphorus field-effect transistors. *ACS Nano* **2016**, 10, 9543.

- (33) Oliva, N.; Illarionov, Y. Y.; Casu, E. A.; Cavalieri, M.; Knobloch, T.; Grasser, T.; Ionescu, A. M. Hysteresis Dynamics in

- Double-Gated n-Type WSe<sub>2</sub> FETs with High-k Top Gate Dielectric. *IEEE J. Electron Devices Soc.* **2019**, *7*, 1163–1169.

- (34) Illarionov, Y. Y.; Knobloch, T.; Waltl, M.; Rzepa, G.; Pospischil, A.; Polyushkin, D. K.; Furchi, M. M.; Mueller, T.; Grasser, T. Energetic mapping of oxide traps in MoS<sub>2</sub> field-effect transistors. 2D Mater. **2017**, 4, 025108.

- (35) Illarionov, Y. Y.; Smithe, K. K.; Waltl, M.; Knobloch, T.; Pop, E.; Grasser, T. Improved hysteresis and reliability of MoS<sub>2</sub> FETs with high-quality CVD growth and  $Al_2O_3$  encapsulation. *IEEE Electron Device Lett.* **2017**, *38*, 1763–1766.

- (36) Cho, A. J.; Yang, S.; Park, K.; Namgung, S. D.; Kim, H.; Kwon, J. Y. Multi-layer MoS<sub>2</sub> FET with small hysteresis by using atomic layer deposition Al<sub>2</sub>O<sub>3</sub> as gate insulator. *ECS Solid State Lett.* **2014**, *3*, Q67.

- (37) Lee, C.; Rathi, S.; Khan, M. A.; Lim, D.; Kim, Y.; Yun, S. J.; Youn, D. H.; Watanabe, K.; Taniguchi, T.; Kim, G. H. Comparison of trapped charges and hysteresis behavior in hBN encapsulated single MoS<sub>2</sub> flake based field effect transistors on SiO<sub>2</sub> and hBN substrates. *Nanotechnology* **2018**, *29*, 335202.

- (38) Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Charge trapping at the MoS<sub>2</sub>-SiO<sub>2</sub> interface and its effects on the characteristics of MoS<sub>2</sub> metal-oxide-semiconductor field effect transistors. *Appl. Phys. Lett.* **2015**, *106*, 103109.

- (39) Stampfer, B.; Zhang, F.; Illarionov, Y. Y.; Knobloch, T.; Wu, P.; Waltl, M.; Grill, A.; Appenzeller, J.; Grasser, T. Characterization of single defects in ultrascaled MoS<sub>2</sub> field-effect transistors. *ACS Nano* **2018**, *12*, 5368–5375.

- (40) Puschkarsky, K.; Grasser, T.; Aichinger, T.; Gustin, W.; Reisinger, H. Review on SiC MOSFETs high-voltage device reliability focusing on threshold voltage instability. *IEEE Trans. Electron Devices* **2019**, *66*, 4604–4616.

- (41) Bias temperature instability for devices and circuits; Grasser, T., Ed.; Springer Science & Business Media, 2013.

- (42) Yang, G.; Chuai, X.; Niu, J.; Wang, J.; Shi, X.; Wu, Q.; Su, Y.; Zhao, Y.; Liu, D.; Xu, G.; Lu, C.; et al. Anomalous positive bias stress instability in MoS<sub>2</sub> transistors with high-hydrogen-concentration SiO<sub>2</sub> gate dielectrics. *IEEE Electron Device Lett.* **2019**, 40, 232–235.