# **Erkennung von Angriffen mit** mikroarchitektonischen Zuständen und Maschinellem Lernen

## **MASTERARBEIT**

zur Erlangung des akademischen Grades

## Master of Science

im Rahmen des Studiums

## **Technische Informatik**

eingereicht von

## Mariana da Silva Barros

Matrikelnummer 12202389

| an | der | Fakı | ıltät | für | Inform    | natik |

|----|-----|------|-------|-----|-----------|-------|

| an | ucı | ıanı | maı   | ıuı | 11 110111 | ıalın |

der Technischen Universität Wien

Betreuung: Univ. Prof. Dipl.-Ing. Georg Weissenbacher, D.Phil.

Mitwirkung: Alexander Pluska, MSc

Mai Al-Zubi. MSc

| Wien, 8. September 2025 |                         |                     |  |

|-------------------------|-------------------------|---------------------|--|

|                         | Mariana da Silva Barros | Georg Weissenbacher |  |

# Attack Detection with **Microarchitectural Traces and Machine Learning**

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Master of Science**

in

## Computer Engineering

by

## Mariana da Silva Barros

Registration Number 12202389

to the Faculty of Informatics

at the TU Wien

Advisor: Univ. Prof. Dipl.-Ing. Georg Weissenbacher, D.Phil.

Assistance: Alexander Pluska, MSc

Mai Al-Zubi, MSc

| Vienna, September 8, 2025 |                         |                     |

|---------------------------|-------------------------|---------------------|

|                           | Mariana da Silva Barros | Georg Weissenbacher |

## Erklärung zur Verfassung der Arbeit

Mariana da Silva Barros

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Ich erkläre weiters, dass ich mich generativer KI-Tools lediglich als Hilfsmittel bedient habe und in der vorliegenden Arbeit mein gestalterischer Einfluss überwiegt. Im Anhang "Übersicht verwendeter Hilfsmittel" habe ich alle generativen KI-Tools gelistet, die verwendet wurden, und angegeben, wo und wie sie verwendet wurden. Für Textpassagen, die ohne substantielle Änderungen übernommen wurden, haben ich jeweils die von mir formulierten Eingaben (Prompts) und die verwendete IT- Anwendung mit ihrem Produktnamen und Versionsnummer/Datum angegeben.

| Wien, 8. September 2025 |  |

|-------------------------|--|

|                         |  |

Mariana da Silva Barros

## Acknowledgements

First of all, I want to thank God for giving me the strength to overcome my limitations and don't give up. Without Him, I would not have arrived where I am today.

During my whole life and especially throughout my academic journey, the experiences I have lived and the people I have met made me who I am today. Therefore, I want to thank everyone in my life for all the support and help I have received. I thank my parents, Edna and Antônio, for being the basis that made me arrive here. I also thank my brother, Tiago, for all the encouragement given when I needed it.

I would like to thank my advisor, Prof. Georg Weissenbacher, for guidance and support during the development of this work. I also would like to thank Mai Al-Zubi and Alexander Pluska for their assistance during the process of writing this thesis. I also thank the Technical University of Vienna (TU Wien) for providing the education, opportunities, and infrastructure that allow the formation of so many people.

More important than where we arrive at the end of a path are the friendships that we make during the journey. I would like to thank my friends from IBCV for all the encouragement, support, and help along the way, and for helping me every day to become a better person.

## Kurzfassung

Optimierungen in modernen Rechnerarchitekturen ermöglichen einen schnelleren und effizienteren Informationszugriff, erhöhen jedoch gleichzeitig die Anfälligkeit für Angriffe und Informationslecks. Diese Schwachstellen werden unter anderem durch cachebasierte Seitenkanalangriffe (Side Channel Attacks) ausgenutzt, die gemeinsame Hardware-Ressourcen und Optimierungen der Rechnerarchitektur einsetzen, um gezielt mikroarchitektonische Seiteneffekte zu erwirken. Zahlreiche aktuelle Forschungsergebnisse zur Erkennung und Abwehr dieser Bedrohung fokussieren sich auf die Verwendung von Hardware Performance Counters (HPCs) zur indirekten Überwachung solcher Seiteneffekte. Eine zentrale Herausforderung besteht jedoch in der mangelnden Flexibilität der Überwachungsintervalle, die entweder Angriffe übersehen oder erheblichen Overhead erzeugen können, sowie in der begrenzten Generalisierbarkeit der erlernten Modelle. Diese Arbeit verfolgt das Ziel, cachebasierte Seitenkanalangriffe mittels maschinellen Lernens zu erkennen, indem ein Grenzwert-basiertes Verfahren zur Überwachung von HPCs eingesetzt wird. Sequenzen von Zeitintervallen zwischen den Überschreitungen von (automatisch ermittelten) Grenzwerten der HPCs dienen als Eingabe für ein T-LSTM-Modell, das zur Angriffserkennung eingesetzt wird. Experimente auf verschiedenen Plattformen und Architekturen und in unterschiedlichen Szenarien dienen der Evaluierung der Generalisierungsfähigkeit des Modells. Optimierungstechniken wie Normalisierung und Fine-Tuning werden eingesetzt, um die Leistungsfähigkeit weiter zu steigern. Das vorgeschlagene System erreicht eine Erkennungsgenauigkeit von über 99% im besten Fall (plattformspezifisch), sowie 98% in plattformübergreifenden Cross-Validierungs-Szenarien unter Verwendung von Fine-Tuning.

## Abstract

Recent advances in computer architecture make access to information faster and more efficient, but also make the computer prone to attacks and information leakage. This vulnerability is exploited, for example, by cache-based side-channel attacks, which make use of shared hardware resources and optimizations in the machine, and affect its microarchitectural traces. Recent studies on the detection and mitigation of this threat focus on the monitoring of Hardware Performance Counters (HPCs). However, among the faced challenges is the lack of flexibility on the monitoring time interval, which may miss attacks or generate a substantial overhead, as well as the lack of generalization for the learned model. Therefore, this work aims to detect cache side-channel attacks with a machine learning technique by using an overflow-based approach to monitor HPCs. The dataset composed by the sequence of triggered overflows for the HPC values, along with the time interval between overflows, is submitted as input to a T-LSTM model, which is trained to detect cache side-channel attacks. The experiments conducted in different scenarios and platforms aim to assess the model's generalization ability. Optimization techniques, as normalization and fine-tuning, are used to improve the model's performance. The detection accuracy of the proposed system is of over 99% in the best scenario (separate platforms), and 98% on the cross-validation across platforms scenario with the use of fine-tuning.

## Contents

| K  | Kurzfassung |                                                              |      |  |  |  |

|----|-------------|--------------------------------------------------------------|------|--|--|--|

| A  | bstract     |                                                              | xi   |  |  |  |

| Co | ontents     |                                                              | xiii |  |  |  |

| 1  | Introdu     | iction                                                       | 1    |  |  |  |

|    | 1.1 Mo      | otivation and Problem Statement                              | 1    |  |  |  |

|    | 1.2 Aiı     | m of the Work                                                | 2    |  |  |  |

|    | 1.3 Me      | ethodological Approach                                       | 3    |  |  |  |

| 2  | Theore      | tical Background                                             | 5    |  |  |  |

|    | 2.1 Ca      | che Side-Channel Attacks                                     | 5    |  |  |  |

|    | 2.2 Ha      | rdware Performance Counters                                  | 13   |  |  |  |

|    | 2.3 Ma      | achine Learning Techniques                                   | 15   |  |  |  |

| 3  | Related     | d Works                                                      | 19   |  |  |  |

|    | 3.1 HF      | Cs Monitoring for Cache Side-Channel Attack Detection        | 19   |  |  |  |

|    | 3.2 De      | ep Learning for Security                                     | 21   |  |  |  |

|    | 3.3 Ca      | che Side-Channel Attacks Detection on Different Environments | 22   |  |  |  |

| 4  | Metho       | Methodology                                                  |      |  |  |  |

|    | 4.1 Sys     | stem Overview                                                | 25   |  |  |  |

|    | 4.2 Da      | ta Selection                                                 | 26   |  |  |  |

|    | 4.3 Da      | taset Creation                                               | 28   |  |  |  |

|    | 4.4 LS      | TM Model Definition                                          | 30   |  |  |  |

|    | 4.5 Mo      | odel Training and Evaluation                                 | 31   |  |  |  |

| 5  | System      | Implementation                                               | 35   |  |  |  |

|    | 5.1 Ex      | perimental Setup                                             | 35   |  |  |  |

|    | 5.2 Da      | taset Creation                                               | 36   |  |  |  |

|    | 5.3 Mo      | odel Training and Evaluation                                 | 37   |  |  |  |

| 6  | Experi      | mental Evaluation                                            | 41   |  |  |  |

|    |             |                                                              | xiii |  |  |  |

|                                    | 6.1                                                      | Calibration Phase              | 41 |

|------------------------------------|----------------------------------------------------------|--------------------------------|----|

|                                    | 6.2                                                      | Dataset Creation               | 43 |

|                                    | 6.3                                                      | LSTM Model Experiments         | 44 |

| 7                                  | Con                                                      | nclusion                       | 55 |

|                                    | 7.1                                                      | Future Works                   | 56 |

| O                                  | vervi                                                    | ew of Generative AI Tools Used | 59 |

| Li                                 | ${f st}$ of                                              | Figures                        | 61 |

| Li                                 | ${f st}$ of                                              | Tables                         | 63 |

| A                                  | crony                                                    | vms                            | 65 |

| В                                  | ibliog                                                   | graphy                         | 67 |

| $\mathbf{A}$                       | ppen                                                     | $\operatorname{dix}$           | 73 |

| Implementation of Dataset Creation |                                                          |                                | 73 |

|                                    | Implementation of Model Training Training and Evaluation |                                |    |

|                                    | Imp                                                      | lementation of T-LSTM Model    | 85 |

CHAPTER.

## Introduction

#### 1.1 Motivation and Problem Statement

Recent advances in computer architectures make access to information faster and more efficient. Among the introduced optimizations, we can cite the use of caches, speculative execution, and CPU pipelines, for example. However, they also make computers more prone to attacks and information leakage. A recent type of attack that poses a threat to most modern architectures is cache-based side-channel attacks, which are efficient for the fact that they don't need additional devices or physical contact with the target  $[TZW^{+}20].$

This type of attack makes use of the shared hardware resources in the machine, such as memory and cache, and also of the optimizations on the access to these resources. Among them, the Spectre vulnerability is one example of a side-channel attack that exploits optimizations found in modern hardware architectures, such as branch prediction and speculative execution. This kind of attack makes use of these features to leak confidential information via side-channels [KHF<sup>+</sup>20]. As a result, side-channel attacks (and particularly Spectre Attacks) have an effect on microarchitectural traces of the machine, which are reflected on Hardware Performance Counters (HPC).

In the last years, techniques to identify when the machine is under attack have been developed, based on both software and hardware. Some of the most popular early approaches are: timing analysis, cache usage profiling, statistical analysis, specialized detection tools, or analysis of system behavior [SDO23]. However, recently, the use of Artificial Intelligence has also helped in this task. According to Al-Zu'bi [AZW24], a popular approach to detect such attacks deploys Machine Learning (ML) to identify suspicious micro-architectural patterns. This can be done, for example, by monitoring the machine HPCs that are affected by this kind of attack, such as branch mispredictions or cache misses.

However, even though there are significant efforts in creating mechanisms to detect cache side-channel attacks, there are still limitations associated with this task, as it is observed in several studies developed in recent years. Gulmezoglu et al. [GMES19] affirms that the main challenge is the fact that the existing works are based on existing attacks, and therefore lack the knowledge of new approaches. Tong et al. [TZW<sup>+</sup>20] and Mukhtar et al. [MMB<sup>+</sup>20] state that the overhead in detection systems still causes a lot of damage to performance. In addition, the fact that the attacks are also evolving and adapting to avoid detection makes it difficult to identify them using conventional techniques [SDO23]. Furthermore, the usual mechanisms created with this purpose are limited to a single architecture or require radical hardware modifications [MMB<sup>+</sup>20].

According to Kim et al. [KHK<sup>+</sup>24], cache side-channel attacks can be designed differently based on the target system environments, such as processor architecture, for example. Therefore, another main challenge related to the use of microarchitectural traces, such as Hardware Performance Counters, to detect Spectre attacks, is to build a model that generalizes well and is robust for different platforms. Since the affected traces are related to the computer architecture, the values will differ in different platforms, and this may make it more difficult for the model to detect attacks in these situations.

This work brings an approach to detect Spectre attacks by observing microarchitectural traces of the computer and using machine learning techniques. Hardware Performance Counters that are most affected by the side-channel attacks will be monitored, and when they reach a certain value (a pre-defined threshold), it may indicate that the machine is under attack. This case constitutes an overflow, and this information is provided to a detection system that will evaluate if the situation constitutes a threat to the computer. Since microarchitectural traces usually vary with different computer architectures, one of the main challenges is related to whether the detection model can be transferred across different platforms.

#### 1.2Aim of the Work

This work aims to provide a system that can detect the presence of cache side-channel attacks through the monitoring of microarchitectural features of the machine, using an overflow-based approach. The measured data should be analyzed over time and evaluated using Machine Learning techniques. In order to assess the robustness of the model, the detection task will be validated on different platforms.

The detection system has the goal to constantly monitor the Hardware Performance Counters and, based on the measured values and the frequency that they overcome pre-defined thresholds, identify whether the machine is under attack. Each time there is a threshold overflow at one of the measured HPCs, this information is sampled and sent to a deep learning model, which will assess if it is a benign application or a side-channel attack. This technique enables the data collection at a dynamic pace, depending on the processes running in the machine, and, at the same time, ensures a constant stream of data to the detection model. As a result, the performance overhead is expected to be smaller than the approach of sampling at a fixed time interval, which was performed in previous works.

However, the system must be robust enough to perform the detection in different architectures and load situations. Due to the fact that the monitored features are microarchitectural traces, they might differ across different architectures, which makes it a challenge to transfer the detection system across platforms. This work will evaluate whether this is possible and will try to overcome this obstacle through the use of an adapted LSTM model that dynamically adapts the learning with the input timing information. In addition, the calibration phase aims to find threshold values that enable the system to adapt to different architectures, while still being able to detect attacks. The system will also be evaluated with different benign applications, to guarantee that it is robust enough to detect attacks with different workload intensities.

The following research questions (RQs) should be answered at the end of this work:

- How well does the system generalize? In other words, is it possible to transfer the detection across different platforms?

- Is it possible to find thresholds for an unknown platform such that the system can detect Spectre Attacks? In other words, is it possible to calibrate the system for the microarchitectural features of each machine?

- Does the timing information on the measurements help to detect the attacks? In other words, does the LSTM model with dynamic temporal adaptation yield good results in this application?

- Does the calibration target influences in the learning processes?

- Do the normalization and fine-tuning techniques improve the system's performance?

- What is the minimum dataset size necessary for the fine-tuning step?

#### Methodological Approach 1.3

The methodological approach consists of the following steps:

## 1. Literature Review

Theoretical background and related works must be researched in order to understand the state-of-the-art, the techniques that have already been used to detect attacks, and the achieved performance.

## 2. Datasets Creation

Before training and testing the model that will detect the attacks, we need to generate datasets both in attack situations and while running benign applications.

These datasets are composed of samples taken each time a Hardware Performance Counter triggered an overflow, or, in other words, each time one of the monitored HPC values was above a previously defined threshold.

## • Calibration Phase

Since different platforms have different standard values for microarchitectural traces, this phase is necessary in order to define the thresholds for each monitored Hardware Performance Counter. This is done by sampling the HPCs for each architecture in various benign scenarios and selecting the thresholds that would allow us to detect attacks.

### Overflow-based Dataset Creation

We generate the datasets for training and evaluation of the model under different workloads, for the different platforms, using the thresholds determined in the previous step. Each sample of the dataset reflects an overflow triggering from one of the monitored HPCs, per process running in the machine. In addition to the overflow trigger, the sample also includes the timing information since the last overflow occurrence, and the information on whether the process is malicious (attack) or a benign application.

## 3. LSTM Modeling

Once we obtain the labelled overflow-based datasets, they will be applied to a supervised RNN (Recurrent Neural Network) model, which has the goal of learning whether there is an attack or not based on the monitored microarchitectural traces. The chosen approach, more specifically a LSTM (Long-term Short Memory) model, enables the use of the timing information to detect an attack. The architecture for an LSTM model that includes dynamic temporal information will be defined, based on the one proposed by Baytas et al. [BXZ<sup>+</sup>17]. This will enable the model to use the timing information on the datasets to learn to detect an attack.

## 4. Model Training and Evaluation

The defined model will be trained and evaluated using the generated datasets. Different scenarios will be tested to evaluate the generalization of the approach, not only among different applications, but mainly among different platforms. Normalization techniques will also be included in the system in order to improve performance.

### 5. Model Fine-Tuning

Another technique for performance optimization, the fine-tuning approach will be used to enable the model to perform the detection in an unknown platform with smaller overhead.

## 6. Results Analysis

The results obtained in the previous steps will be analyzed and compared in terms of performance and overhead.

## Theoretical Background

The chapter is organized as it follows. Section 2.1 explains the principle of cache sidechannel attacks, section 2.2 describes Hardware Performance Counters, and section 2.3 talks about Machine Learning Techniques employed in this work.

#### 2.1Cache Side-Channel Attacks

#### 2.1.1Cache Memory and Hierarchy

In modern computers, the cache memory is employed between the CPU and main memory (RAM memory) to address the performance gap between them [LM18]. In other words, the cache is used by the CPU to provide quicker access to data without the need to wait for the slower RAM. The cache works by buffering recently used data, so that the overall memory access time is significantly decreased [LM18].

Moreover, according to Lyu et al. [LM18], modern processors have the cache divided in different levels, as a further improvement to the access time. This way, the higher levels, closer to the processor, are smaller, faster, and more expensive, while the lower levels are bigger, but slower. According to Shen et al. [SCZ21], modern processors contain 3 levels of cache:

- L1 caches: per-core instruction and data caches.

- L2 caches: per-core unified caches.

- L3 cache: large cache shared across cores, also called Last-Level Cache (LLC).

Depending on whether the information requested by the CPU is available in the cache or not, we have a cache hit or miss, respectively. During the past decade, the difference in the access times of cache hits and misses has been exploited by cache-based side-channel attacks [HL17] [LM18].

According to He [HL17], an effective attacker is able to observe all of the victim's memory accesses and infer whether it is a cache hit or miss. Furthermore, by observing the cache shared with the victim, the attacker can also infer the memory address used by the victim. This way of getting the leaked metadata is what characterizes cache timing side-channel attacks, and it is used, for example, to derive the secret key to encryption algorithms [HL17].

However, it is not always the case that the attacker can observe all the times the victim accesses the cache. In this case, the attacker uses indirect observations, which can be done in two different ways, as described by He [HL17]. The first one, called "time-based" cache side-channel attacks (SCA), is where the attacker measures the access time of its own memory access, after interfering with the victim sometimes. The other one, called "access-based" SCA, happens when the attacker looks at the total time of the victim's security-critical operation.

#### 2.1.2Speculative Execution

According to Kocher et al. [KHF<sup>+</sup>20], modern processors deploy speculative techniques for optimization. This approach is related to the fact that, when the control flow of a program depends on a value stored in memory (and not in the cache), it may take hundreds of clock cycles to retrieve this value, while the processor is idle. Instead, with speculative execution, the processor predicts the direction of the control flow and executes the program speculatively [SCZ21]. If, when the actual result comes, the prediction is following the wrong path, the processor discards the precomputed results and go back to the last correct state. However, if the prediction is accurate, the processor commits to these results and continues to execute. According to [SCZ21], the speculative execution technique improves the performance significantly. However, it can be exploited by attackers to leak information and access sensitive data [AZW24] [GMES19].

#### 2.1.3 Attack Techniques

According to Shen et al. [SCZ21], there are various examples of microarchitectural cache side-channel attacks, and they usually involve the combination of different techniques. According to its relevance for this work, we will present two groups of approaches that are often combined to create attacks.

## Instrumented Attacks

In instrumented attacks, the attacker uses the cache side-channels to interfere with the victim's access patterns and then capture the victim's secret [SCZ21]. The difference in the latency of cache accesses in different situations is leveraged by the attacker in order to infer the victim's behavior [SCZ21].

These type of attacks can be further classified in two groups, as described by [SCZ21]. The first class, "flush-based", uses "clflush" instructions to flush the memory lines. The most common ones are Prime + Probe, Evict + Time, Flush + Reload, and Flush + Flush.

• Prime + Probe  $[MAB^{+}18]$

The Prime + Probe attack can be divided in three distinctive parts [LM18]

- 1. Prime: Initially, the attacker occupies specific (or all) cache sets with its own

- 2. The victim executes its own process

- 3. Probe: The attacker accesses the same data that it has previously loaded into the cache. If the data loaded by the victim is mapped to the same cache sets and evicts the attacker's data, there will be a cache miss, and consequently, a longer probe time. Otherwise, if the data is still in the cache, the probe time will be smaller.

Therefore, as Lyu et al. [LM18] explain, the attacker only measures its own running time, which makes it effective and noise-resistant. This attack technique uses the last-level cache (that is shared among many processors), but it can also be implemented at L1-data and L1-instruction [BRN24].

• Evict + Time [OST06]

According to [LM18], this is a time-driven attack that will use the execution time from the victim to learn information. Lyu [LM18] divides it into 3 stages:

- 1. The attacker triggers the victim process

- 2. Evict: The attacker fills a specific cache set with its own data, hoping to evict the victim data

- 3. Time: The attacker measures again the victim's execution time

The basic idea of the attack is to first establish a baseline time by preloading the victim's data [SCZ21]. Then, after evicting and running the victim code again, it gets a new execution time. This new time will be longer if the victim accessed the line evicted by the attacker [SCZ21]. On the other hand, the second execution will be faster if the evicted cache lines are not the same. Therefore, the timing of the second execution reveals the memory access pattern of the victim process [LM18].

According to Lyu et al. [LM18], there are some weaknesses in this technique. Firstly, there are strong assumptions made, such as, for example, the knowledge of the memory address of useful data. Secondly, the time measurement is imprecise in this case [LM18].

## • Flush + Reload [YF14]

Initially defined for the L1 cache and later extended to L3, this attack can determine a specific instruction or data accessed by the victim process [LM18]. The stages of the technique, as defined by Lyu et al. [LM18], are:

- 1. Flush: The attacker flushes a memory line (the target address) from the cache.

- 2. The attacker waits for the victim process to run, which is given by a preconfigured time [SCZ21].

- 3. Reload: The time to reload the memory line is measured. If the victim accesses the line evicted by the attacker, the execution time is longer [SCZ21].

According to He et al. [HL17], in this attack, the attacker shares a library or data with the victim. If the victim uses the shared data, those shared memory lines will be fetched into the cache. Then, after the reload operation, a hit in the attacker's reloads indicates that the corresponding memory line has been used by the victim [HL17].

## • Flush + Flush [GMWM16]

Created as a variation of Flush + Reload, this attack exploits timing variation in the "flush" instruction itself [SCZ21]. According to Ferracci [Fer19], the technique has only one phase, that is repeated in a loop: the execution of the "flush" instruction on a chosen shared memory line. The attacker measures this execution time, and based on that, he decides whether this memory line has been cached or not [Fer19]. Since the attacker does not load anything from the memory to the cache, the execution time refers only to a load by the victim process. As Ferracci [Fer19] also mentions, the repeated "flush" instruction also evicts the cache lines for the next loop.

## Transient-Execution Attacks

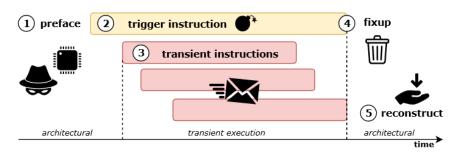

As described by Shen et al. [SCZ21], transient instructions execute unauthorized computations out of the intended code or data paths. Even though their results are never committed to the machine's architectural state, they still leave traces on the microarchitectural state [SCZ21]. Canella et al. [CBS<sup>+</sup>19] states that this feature has been exploited by transient execution attacks, which usually follow the flow shown in Figure 2.1.

According to Shen et al. [SCZ21] and Canella et al. [CBS<sup>+</sup>19], the general transient execution attack can be divided in 5 phases:

- 1. The attacker first prepares the micro-architecture and brings it to the desired state.

- 2. The attacker executes a trigger instruction, which is any instruction that will cause the following operations to be eventually squashed (as a mispredicted branch or data dependency, for example).

Figure 2.1: High-level overview of a transient execution attack [CBS<sup>+</sup>19]

- 3. Before committing the trigger instruction, the CPU continues to execute a sequence of transient instructions, which encode unauthorized data through a microarchitectural covert channel.

- 4. When it is retiring the trigger instruction, the CPU discovers the exception or misprediction and flushes the pipeline. This is done to discard any architectural effects of the transient instructions.

- 5. Finally, the attacker recovers the unauthorized transient computation results at the receiving end of the covert channel, and reconstructs the secret from the micro-architectural state.

Depending on what causes the trigger instruction, transient execution attacks can be classified into two groups [SCZ21]:

- Spectre-type attacks: they exploit transient execution following control or data flow misprediction.

- Meltdown-type attacks: they usually exploit transient execution attacks following a faulting instruction.

Being one of the main focuses of this work, the Spectre attack will be better described in the following section.

#### Spectre Attack 2.1.4

A general description of Spectre Attacks is that they trick a victim into transiently diverting from its intended execution path, which is done particularly by poisoning the processor's branch prediction system [SCZ21]. They guide the transient execution from the victim to some code snippets, which use the micro-architectural state to expose secrets. A key factor for this type of attack is that the execution is entirely in the victim's domain, and it can only leak data that is architecturally accessible [SCZ21].

Currently, there are several variants of Spectre attack, each one exploiting a different system component. Canella et al. [CBS<sup>+</sup>19] proposes a classification in two levels: firstly, according to the micro-architectural buffers that can trigger a prediction, and secondly, to the mistraining strategies that can be used to steer it.

## Spectre variant 1

The first variant of Spectre was proposed by Kocher et al. [KHF<sup>+</sup>20]. This approach poisons the Pattern History Table (PHT) to mispredict the direction of conditional branches (whether they are taken or not) [CBS<sup>+</sup>19]. In other words, as described by Ferracci [Fer19], the attacker mistrains the CPU branch predictor to mispredict the direction of a branch. This causes the processor to execute code that would not have been carried out otherwise.

Al-zubi [AZW24] describes the steps followed by Spectre attack:

- 1. Initially, the attacker tries to trick the CPU into making incorrect branch predictions, by continuously forcing the victim to engage in misleading behaviors.

- 2. Then, the attacker uses "flush" instructions to clear the cache, to force the victim process to get any data from the main memory (and not from the cache).

- 3. On the next step, the attacker tricks the victim process into executing speculative execution on sensitive data (the secret that the attacker is looking for).

- 4. The victim has to retrieve the secret from the main memory, since the cache was emptied by the attacker.

- 5. When the processor realizes the misprediction, it discards the results of the speculative computation. But the side effects on the cache are still visible to the attacker.

- 6. The attacker uses a high-precision timer to determine which values were read from the memory, and then, decode the secret. That is possible because a cache miss implies the victim has to read data from memory, and therefore takes longer, while a cache hit implies reading data from the cache, which is faster.

- 7. Finally, the attacker retrieves from the cache the secret value.

The implementation of variant 1 of the Spectre attack is available at [Spe18]. The example code for x86 architecture is provided by the authors of the original paper [KHF<sup>+</sup>20]. The specific idea is that the attacker uses bound checking to mistrain the victim process in the speculative execution of conditional branches. The code snippet on the figure 2.2 below is one example that can be exploited by this attack.

Kocher et al. [KHF<sup>+</sup>20] describe the execution of this example by the Spectre Attack. In this example, the variable x contains data that is controlled by the attacker. The

```

(x < array1_size)

y = array2[array1[x] * 4096];</pre>

```

Figure 2.2: Code snippet for bound checking in Spectre Attack [KHF<sup>+</sup>20]

conditional statement in this code needs to verify if the value of x is within a legal range. This is necessary to verify if the memory access to array1 is valid. According to Kocher et al. [KHF<sup>+</sup>20], during the phase 1 described above (mistraining phase), the attacker invokes the code while providing valid inputs, training the branch predictor to expect the conditional branch result to be true. On the next phase (exploit phase), the attacker provides a value of x that is out-of-bounds of array1. Instead of waiting for the calculation of the branch result (whether the value is valid or not), the processor employs speculative execution and guesses that the bound check will be true, executing the next instruction. Eventually, when the calculation of the bound check is completed, the CPU realizes the misprediction and reverts the changes made to the microarchitectural state. However, the cache state remains visible to the attacker, who can retrieve the secret byte.

According to Shen et al. [SCZ21], this variant of the attack takes advantage of the access to out-of-bounds memory that is done speculatively before the bound check resolves. Moreover, the Spectre attack combines speculative execution, branch prediction, and cache-based side-channels [AZW24].

## Other Spectre Variants

Since the proposal of variant 1 from Spectre attack, there have been developed other works that exploit this attack with different machine components.

• Spectre Variant 2 [KHF<sup>+</sup>20]

The Variant 2 of Spectre, proposed by the same authors, is also called Spectre-BTB (Branch Target Injection) [CBS<sup>+</sup>19]. This approach exploits indirect branches and poisons the Branch Target Buffer (BTB). The main idea here is that the attacker chooses a "gadget" from the victim's address space and influences the victim to speculatively execute the "gadget". Instead of relying on a vulnerability in the victim code, the attacker trains the BTB to mispredict a branch from an indirect branch instruction to the address of the gadget, which consists of a speculative execution of the gadget. In a similar manner as before, the processor reverts the effects of the incorrect speculative execution, but not the effects on the cache, therefore allowing a leakage of sensitive information via a cache side-channel.

Spectre-RSB (Return Address Injection) [MR18] [KKSAG18] According to Ferracci [Fer19], the third variant of Spectre is slightly different from the other ones because it uses the Return Stack Buffer (RSB). The main idea is that the return address value in the RSB is different from the one in the software stack, which leads the program to misspeculate to the address in the RSB. By triggering this misspeculation intentionally, an attacker can force a process to execute arbitrary code [Fer19].

• Spectre-STL (Speculative Store Bypass) [Hor18]

According to Canella et al. [CBS<sup>+</sup>19], speculation on modern CPUs also includes predicting dependencies in the data flow. The variant 4 from Spectre shows how the mispredictions by the memory disambiguator could be abused to speculatively bypass store instructions [SCZ21]. It is based on Store To Load (STL) dependencies, which require that a "load" instruction to the memory shall not be executed before all the previous "store" instructions that write to the same location have been completed [CBS<sup>+</sup>19]. The attack takes advantage of a performance feature that allows loads to speculatively execute even if the address of a preceding potentially overlapping store is unknown [SCZ21].

#### 2.1.5 Other Attacks

In this section, there will be discussed other variations and versions of related attacks that have been developed in the last few years. Since this work is focused on a comparison analysis of Intel and ARM architectures, we could only include in the experiments attacks that work on both platforms. Nevertheless, we will also describe other relevant attacks.

### Meltdown

Developed by Lipp et al. [LSG<sup>+</sup>20] in 2018, the Meltdown attack is one of the most famous in the group of transient-execution attacks. This attack targets data that is architecturally inaccessible by exploiting illegal data flow from faulting or assisted instructions [SCZ21]. As described by Canella et al. [CBS<sup>+</sup>19], in other words, Meltdown-type attacks exploits that exceptions are only raised upon the retirement of the faulting instruction. This allows transient instructions ahead in the pipeline to compute on unauthorized results of the instruction about to suffer a fault. So, even though the CPU discards any architectural effects of this computation, secrets may be leaked through microarchitectural covert channels  $[CBS^{+}19]$ .

### Rowhammer

The Rowhammer attack was proposed by Gruss et al. [GMM16] in 2016. It is based on the fact that DRAM cells have the possibility to leak charge over time. By accessing neighboring rows repeatedly, Rowhammer triggers the leak, which leads to bit flips and enables adversaries with low access rights to gain system privileges [GMES19]. In other words, the attack targets DRAM modules by repeatedly accessing a memory location, in order to cause voltage fluctuations and discharge nearby memory locations [BYL21].

Since this attack was adapted for the ARM architecture (Raspberry Pi platform) by Bekele et al. [BYL21], we also included it in the experiments conducted in this work.

### Foreshadow

Proposed in 2018 by Bulck et al. [BMW<sup>+</sup>18], the Foreshadow attack targets Intel SGX technology, more specifically enclaves, a private region of memory defined at the user-level or operating system code [Fer19]. The technique extracts a single byte from an SGX enclave, and can be divided in three distinct phases, as explained by Ferracci [Fer19]:

- 1. Plain text enclave data is cached.

- 2. The attacker dereferences the enclave secret and loads a secret-dependent oracle buffer entry into the cache, speculatively executing the transient instruction sequence.

- 3. The attacker executes the same as the receiving end of Flush + Reload technique, and reloads the oracle buffer slots to establish the secret byte.

#### **Hardware Performance Counters** 2.2

#### 2.2.1 Micro-architectural Traces and HPCs

According to Gregg [Gre14], Hardware Performance Counters (HPCs) are special-purpose registers included in modern processors that are used to track diverse processor events, such as clock cycles, instructions, branch misses, and cache hits. They are responsible for storing low-level hardware-related events in the CPU, which are tracked as counters and available in these registers [GMES19]. In other words, the purpose of HPCs is to monitor a hardware event, or to gather information on this event [Fer19].

The counters are used to collect information about the system behavior while an application is running, and are available for various performance events in all major architectures, as Intel and ARM, for example [GMES19]. According to Zhang et al. [ZZL16], most modern processors provide a Performance Monitor Unit (PMU), which enables applications to control HPCs.

Originally designed for software debugging and system performance tuning, HPCs have been recently exploited to detect security breaches and vulnerabilities [ZZL16]. As Zhang et al. [ZZL16] explain, the intuition behind is that HPCs can reveal characteristics of the programs' execution, which in turn can reflect the programs' security states. In addition, these counters offer advantages such as a minimal effect on speed and resilience to modification by an attacker [AZW24], as well as the fact that they introduce negligible performance overhead [ZZL16].

#### 2.2.2Relevant HPCs

Although there are several different events in each CPU model, only a limited number of events can be monitored concurrently in the system because the number of HPCs available in a processor is limited, according to Kim et al. [KHK<sup>+</sup>24]. This means that it is necessary to have a proper selection of events to monitor the effective utilization of HPCs.

In addition, as stated by Ferracci [Fer19], the events that can be monitored using HPCs depend on the available processor architectural family. That means that only certain events are available for monitoring on each architecture. That happens because the generation of a hardware event is physically triggered by data paths or control signals implemented in the actual control unit of the CPU, which is often subject to partial or complete re-implementation across different families of processing units [Fer19].

Therefore, for this work, we chose the events monitored by HPCs that are available in the architectures studied, and are relevant for the task of attack detection. In order to choose them, we used the first four HPC events in the ranking performed by Al-Zubi [AZW24]. The choice was motivated by a common goal with this work, the availability if the events in both architectures being monitored, and the possible number of HPCs to be monitored concurrently. The four selected HPCs are:

- Number of retired instructions

- Number of mispredicted branch instructions.

- Number of cache misses for the Level-1 Data Cache.

- Total number of CPU cycles.

The complete list of events is available at the "perf" tool documentation [Perb]:

#### 2.2.3**HPC** Monitoring

As explained in the previous section, and also confirmed by Moore [Moo02], performance monitoring hardware usually consists of a set of registers that record data about the processor's function, often accompanied by a set of control registers that allow the user to configure and control the performance monitoring hardware. In addition, many platforms, such as Intel and ARM, also provide hardware and operating system support for generating an interrupt to the performance monitoring software when a counter overflows a specific threshold [Moo02].

Therefore, hardware performance monitors can be used in one of the two modes, both with their own uses in performance analysis:

- 1. Sampling: mode to collect aggregate counts of event occurrences at a pre-defined time interval.

- 2. Overflow: mode to collect profiling data based on counter overflows.

The modes will be further explained in the following sections.

## Sampling

The first mode is the simplest one, where, for each event being monitored, a register is associated that stores the aggregate counts of the event. At a time interval defined by the user, this register (counter) is read by the system, and the value in the register is sampled. Depending on how the user defined it, the counter can either be reset at each time it is read, or the event count number can be accumulated.

This monitoring mode has a wide range of different applications in performance analysis, for example to identify performance bottlenecks or to relate performance problems to program locations [Moo02].

Moreover, this approach for measuring HPCs has been widely used in the detection of cache side-channel attacks [AZW24] [GMES19] [TZW<sup>+</sup>20] [KHK<sup>+</sup>24]. It brings the advantage that is simple to implement and safe, given the constant measurements. However, on the other side, the sampling interval is fixed, and, once defined, it cannot be changed.

## Overflow

Another approach for monitoring HPCs is based on the "overflow" feature mentioned by Moore [Moo02]. In this technique, the user defines, for a given event, a threshold value. Then, once the counting is initiated, the system keeps constantly checking the current count value for this given HPC and comparing it to the threshold. Once the value is equal or greater than the threshold, it generates an interrupt and follows a routine defined by the user. Then, the counter is reset.

In a similar way to the sampling mode, the overflow approach has numerous applications in system performance analysis. It has the advantage of not having a fixed sampling interval, which brings more flexibility to the monitoring. However, it is more complex to implement, and the subsequent analysis may be more difficult to perform.

#### 2.3 Machine Learning Techniques

As described by Zhou et al. [Zho21], Deep Learning (DL) is one of the Machine Learning (ML) methods that implements Artificial Neural Networks (ANN). A deep learning network is a neural network with multiple layers. Examples of deep learning networks include Deep Neural Networks (DNN), Convolutional Neural Networks (CNN), and Recurrent Neural Networks (RNN), among others [Zho21].

Due to its ability of learning patterns and detect anomalies, Machine Learning (ML) and, more specifically, DL, have a wide range of applications in security, including intrusion detection, malware analysis, or traffic anomalies [AZW24]. Pang et al. [PSCH21], for example, performs a review on how Deep Learning (DL) can be used for anomaly detection.

In this work, we will focus on the use of RNNs, and more specifically, LSTM networks, which will be explained in the following sections.

#### 2.3.1 **RNNs**

Recurrent Neural Networks (RNN) were first proposed and explained in 1990 by Elman [Elm90]. It consists of a type of Artificial Neural Network (ANN), which can be described as a neural network where the connections between the nodes resemble the neurons of a human brain.

As explained by Muhuri et al. [MCY<sup>+</sup>20], the principle of an ANN is based on the biological brain, where synapses are transmitted among neurons. In a neural network, signals are transmitted through connections from one node to another. Upon receiving a signal, the artificial neuron processes it and then transmits it to the connected nodes. In an ANN, both neurons and connections usually have weights to adjust the learning process. As they differ, the weights adjust the strength of the signal as it travels from the input to the output layer, across the hidden layers [MCY<sup>+</sup>20].

According to Muhuri et al. [MCY<sup>+</sup>20], an RNN should have at least three layers. Figure 2.3 below represents a simple RNN architecture with two hidden layers. The basic components of an RNN include input units, hidden units (which perform calculations to adjust the weights and produce the outputs), and output units [MCY<sup>+</sup>20].

Figure 2.3: A simple RNN  $[MCY^+20]$

As portrayed in the Figure 2.3, the one-way information flow in an RNN model flows

from the input units to the hidden units, and a directional loop compares the error of the current hidden layer to that of the previous one, and based on that, adjusts the weights between the hidden layers.

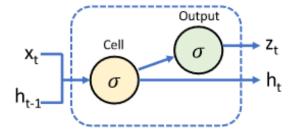

According to Gulmezoglu et al. [GMES19], in a typical RNN structure, the information cycles through a loop. That means that, when the model needs to make a decision, it uses the current input  $x_t$  and the hidden state  $h_{t-1}$  (where the learned features from the previous data samples are kept). In other words, a RNN algorithm produces output on the previous data samples, and the output is provided as feedback into the network [GMES19]. Figure 2.4 shows a simple diagram of a RNN cell.

Figure 2.4: RNN Cell [GMES19]

Recurrent Neural Networks can be described as the first algorithm to remember the temporal relations in the input through its internal memory. Therefore, they are widely used for tasks where sequential data is involved [GMES19]. However, conventional RNNs are not effective to learn long-term sequences, because with the increasing time steps, the amount of extracted information converges to zero and the model stops learning [GMES19] [MCY $^{+}20$ ].

#### 2.3.2 LSTM

Long Short-Term Memory (LSTM) models were first proposed by Hochreiter and Schmidhuber [HS97a] in 1997. They consist of modified RNN models, created in order to address the problem of the vanishing and exploding gradient in traditional RNNs [AP22]. Essentially, they extend the internal memory to learn longer time sequences, being able to bridge more than 1000 discrete time steps [GMES19] [MCY<sup>+</sup>20].

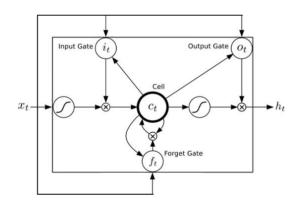

According to [MCY<sup>+</sup>20], LSTM networks replace all units in the hidden layer with memory blocks, and each of them has at least one memory cell. Each basic cell on a LSTM network consists of a memory cell, input, forget, and output gates, as represented by Fu et al. [FLM<sup>+</sup>18] in the Figure 2.5 below.

The basic principle of a LSTM cell is that the information flow is controlled by the three gates (input, forget, and output gates). The memory cells activate with the regulating gates, which control the incoming and outgoing information flow [MCY<sup>+</sup>20]. At each time step t, an LSTM cell receives the current input vector  $x_t$ , the previous hidden state  $h_{t-1}$ , and the previous cell state  $c_{t-1}$  [Sch15]. The memory cell keeps the learned

Figure 2.5: LSTM Cell [FLM<sup>+</sup>18]

information from the previous sequences. Connected to the memory cell, it is placed a forget gate (which are simple sigmoid threshold units), that can reset the state of the unit if the stored information is no longer needed  $[MCY^{+}20]$ . The LSTM cell produces two outputs: the current hidden state  $(h_t)$ , and the current cell state  $(c_t)$  [Sch15]. Finally, the output gate determines whether to pass the output of the memory cell to the next hidden state  $[FLM^+18]$ .

An LSTM layer consists of multiple LSTM cells working in parallel. In practice, multiple LSTM layers are often stacked by feeding the hidden state output of one layer into the next, which allows the network to model more complex temporal patterns [Sch15]. Therefore, LSTM networks can select distinct features in the time sequence data more efficiently than RNNs, which enables it to learn the long-term temporal relations in the input [GMES19].

#### 2.3.3 Other Machine Learning Techniques

In a general definition, Machine Learning (ML) techniques are able to improve their performance on a specific task with increasing experience [HTF09]. Therefore, ML techniques have various applications that involve learning a pattern or identifying anomalies. For this reason, traditional Machine Learning (ML) techniques have been widely used for attack detection and other security applications.

The most common ML techniques include linear, non-linear, and non-parametric algorithms (Logistic Regression (LR), Support Vector Classifier (SVC), Perceptron, Decision Tree, Linear Discriminant Analysis LDA), K-Nearest Neighbors (kNN)), probabilistic models (Gaussian Naive Bayes (GaussianNB)), ensemble learning methods (Random Forest (RF) and Gradient Boosting Classifier (GBC), as well as artificial neural networks (Multilayer Perceptron (MLP)). These algorithms are explained in details by Alpaydin [Alp20].

## Related Works

Due to the importance of assuring information security and privacy, especially with sensitive data, and the developments and increasing variations of cache side-channel attacks, there has been developed works on the detection of these threats. The most recent and better performing approaches with this objective use machine learning or deep learning techniques and can detect attacks with an accuracy of up to 99%.

### 3.1HPCs Monitoring for Cache Side-Channel Attack Detection

Since the initial implementations of cache side-channel attacks, there has been developed research works that look for ways to detect and identify these types of threats. Given the nature and general behavior of cache side-channel attacks, as explained in Section 2.1, one way to perform this task is by monitoring Hardware Performance Counters.

Al-Zubi and Weissenbacher [AZW24] perform a systematic evaluation of different machine learning techniques to detect Spectre Attack through the statistical profiling of microarchitectural traces. Initially, in order to determine the minimum number of features required for Spectre attack detection, the work samples up to 40 Hardware Performance Counters under different attack scenarios and uses statistical methods to rank them. The selection of HPCs (as well as the optimal number to be monitored) is performed using the Maximum Relevance Minimum Redundancy (mRMR) technique. The best-ranked HPCs that resulted from this experiment reflect execution (total instructions, total cycles) and branch behavior (conditional branches, branch instructions, correctly predicted branches, and branches taken). The datasets for the experiments of this work are generated by sampling the selected HPCs in scenarios, including cache side-channel attacks and benign applications.

In addition, the authors also identify the best-performing machine learning classifiers for this task. They use cross-validation to compare various ML models, including linear, non-linear, and non-parametric algorithms (Logistic Regression (LR), Support Vector Classifier (SVC), Perceptron, Decision Tree, Linear Discriminant Analysis (LDA), K-Nearest Neighbors (kNN)), probabilistic models (Gaussian Naive Bayes (GaussianNB)), ensemble learning methods (Random Forest Classifier (RF) and Gradient Boosting Classifier (GBC)), as well as artificial neural networks (Multilayer Perceptron Classifier (MLP)). The performance of the different classifiers on the same dataset is compared, as well as how the same algorithm performed over all datasets. Finally, a statistical analysis of the features shows that, as a result, the work finds that ensemble learning and Decision Trees outperform other machine learning methods for the detection.

As a result of development on both the attack and Artificial Intelligence techniques, various recent studies use hybrid techniques to improve the task of cache side-channel attacks detection. Tong et al. [TZW<sup>+</sup>20] developed a method based on the AES algorithm to use Hardware Performance Counters and detect different types of attacks, namely Flush + Reload, Prime + Probe, and Flush + Flush. The dataset used in the experiments is collected through the sampling of 24 HPCs, under 3 different loads, in 6 diverse scenarios (attack and benign applications).

The proposed approach first uses the random forest algorithm to filter the cache features, and select the 4 HPCs that yield the best results (DTLB READ, L1D ACCESS, DTLB ACCESS, and CACHE NODE). Then, the next step is to use Support Vector Machine (SVM) for classification to perform attack detection under different loads. The classification accuracy, precision, recall, and F1 score are measured for the different situations (attacks and loads). The system achieves a detection accuracy of 99.92% without any load, and 96.57% with full load.

A recent type of approach for this task involves the use of Recurrent Neural Networks, most specifically of Long-Term Short Memory (LSTM) algorithms [HS97b]. This technique is particularly suitable for sequential time series, due to its ability of learning both short and long-term dependencies.

The system proposed by Gülmezoglu et al. [GMES19] implements a generic model to detect unknown attacks in an unsupervised way, using HPCs. Initially, a training dataset is generated through sampling of HPCs when only benign applications are running. This data is fed to an LSTM model that learns this behavior pattern, using a sliding window technique to learn using smaller sequences. In the testing (online) phase, the data is collected from the same HPCs under both benign applications and attacks, while it dynamically predicts the next value. The Mean Squared Error between the predicted and real values is calculated, and it is used to detect malicious situations. Within a defined decision window, if all the calculated errors are bigger than a fixed threshold, an anomaly flag is set. Therefore, due to the unsupervised learning technique, the system is capable of detecting attacks even in situations where there is an unknown attack. The reported results show that the trained model is capable of detecting attacks such as Spectre, Meltdown, Zombieload, and Rowhammer, even without observing them during the training, with the highest F-score of 99,7%.

Most of the approaches that aim to detect cache side-channel attacks observe mainly the cache-related events. That is effective for the earlier variants of the attacks. However, in order to bypass this detection technique, recently proposed attacks use different approaches, as is the case with Prime + Abort, for example. Kim et al. [KHK<sup>+</sup>24] developed a system that can not only detect the conventional cache side-channel attacks, but also the new variants that exploit other hardware events.

The study focuses on the attacks FLUSH + RELOAD, PRIME + PROBE, and PRIME + ABORT, as well as the L3 cache. Initially, the work analyzes the attacks to identify which hardware events most closely relate to them, besides cache events. The patterns of these events is studied under six different conditions (which involve different attacks, different workloads, and different cryptographic applications), and they are selected based on their distribution pattern and temporal behavior. The five selected events are: L3 cache misses, unhalted cycles, retired instructions, and two Intel TSX events. Once the system collects the selected hardware events, the generated datasets are used to train the models. The authors employ Multi-Layer Perceptron, RNN, and LSTM deep-learning models to infer the presence of attacks, achieving an accuracy of over 99% with LSTM.

#### 3.2 Deep Learning for Security

Due to their flexibility and ability to identify patterns, RNNs and LSTMs are used in a variety of different applications. As explained in Section 2.3.2, LSTMs are modified RNNs that extend the internal memory to learn longer time sequences [GMES19]. For this reason, they are frequently used with problems involving sequential data and time series, as is often the case for attack detection. Several studies describe applications of deep learning techniques to mitigate security problems.

This is shown in the work developed by Yao et al. [YJDO19]. In this research, the authors propose a system that uses LSTM to detect privacy risks on Named Data Networks, more specifically, timing attacks. This type of attack uses the timing relation between the delivery of data that is cached and not cached to infer if certain contents were recently requested by the user. In order to detect this type of attack, the system observes several statistics of the network packets: requested content names, the interface from which each interest came, the arrival time of each interest packet, and the corresponding cache hit in each time window. This information is used to generate the input features from the supervised LSTM model: cache hit ratio, average request interval, request frequency, and types of requested contents. The performance is compared in terms of classification accuracy, detection ratio, false alarm ratio, and F-measure, achieving better results than previous works.

Another work that uses deep learning methods to detect network attacks is the one proposed by Liu et al. [LLLY19]. Due to the fact that using traditional machine learning

methods for attack detection in payloads depends heavily on feature engineering (which can be time-consuming and complex to implement), the authors propose an end-to-end detection system. They propose two techniques, one using CNN payload classification, and another one with RNN payload classification. Both have the same goal of detecting network attacks, like DOS, probe, U2R, and R2.

The first implemented technique, referred to by the authors as PL-CNN, exploits the ability of CNNs to extract local region features, in order to consider the entire data stream (and not single bytes). Since network traffic is made up of packets, in which payloads appear in the form of data streams, the authors propose another payload classification model based on an RNN. Since RNNs can learn feature representations from data by storing previous states, it is used to identify specific sequences that can distinguish normal from anomalous communications. The experiments resulted in the best accuracy of 99.36% using PL-CNN, and 99.98% using PL-RNN on public datasets.

Similarly, Fu et al. [FLM<sup>+</sup>18] also proposes the use of RNNs for network attack detection. The technique proposed in this work is based on Long-Short Term Memory (LSTM), and an end-to-end detection is developed, including data preprocessing, feature abstraction, training, and detection. The system focuses on detecting network attacks based on payloads, and the experiments are conducted on the NSL-KDD dataset. The obtained results show that the proposed method outperforms several attack detection techniques based on feature detection and Bayesian or SVM classifiers.

Recently, hybrid approaches have also been used to classify network behavior and identify network attacks, which shows the relevance of this threat. Muhuri et al. [MCY<sup>+</sup>20] develops an intrusion detection system that combines the use of a genetic algorithm for optimal feature selection and LSTM with a Recurrent Neural Network for identifying attacks. The work also aims for network attacks, and it is trained and tested using the public NSL-KDD dataset. After the data is initially preprocessed, the features are selected using a genetic algorithm (GA), which selects a subset of 99 features from the original 122. Then, the data is input to the LSTM-RNN model, which is trained and subsequently evaluated.

The system performance was measured with accuracy, recall, precision, F-score, and confusion matrix, with both binary and multi-class classification. The results show that the use of the genetic algorithm increases the classification accuracy in both cases. A comparison with other techniques, such as support vector machine and random forest, also shows that the proposed system outperforms them.

### 3.3Cache Side-Channel Attacks Detection on Different **Environments**

Despite the development of attack detection systems, which aim to improve performance and cover multiple variants of cache side-channel attacks, it is not always the case that the threats target conventional processors. Improvements on the attacks also include the adaptation to different environments, which leads to the need of detection systems that focus on these specific situations.

One of the first works to focus on attack detection, by Zhang et al. [ZZL16], proposes a system to detect cache-based side-channel attacks in multi-tenant cloud systems. The approach is composed by two parts: it uses signature-based detection to identify when the machine is executing a cryptographic application, and at the same time uses anomalybased detection techniques to identify abnormal cache behaviors that are typical from attacks. This technique brings the innovation of focusing on the root causes of cache side-channel attacks, making it difficult to evade, in addition to being able to detect the attack in real-time. Furthermore, it does not require any new hardware support or modifications. The work achieves high detection accuracy, with a performance overhead of at most 5%.

A more recent work, proposed by Bhade et al. [BPSS24], implements a detection system for cache side-channel attacks that is hardware-based. The approach successfully detects multiple cache timing attacks on multiple sensitive locations simultaneously, with minimal performance overhead. The system is evaluated by synthesizing the entire detection algorithm in a block, which is tested in a RISC-V processor, under different workload conditions. The work achieves more than 98% detection accuracy with an overhead of 0.9 to 2.1\%, without any impact on its maximum operating frequency.

Even though most studies on cache side-channel attacks (both on generation and detection) have been performed in Intel processors, ARM CPUs are becoming more popular and are being used in more systems. Since ARM processors have a different cache organization and instruction set than Intel processors, the original versions of cache side-channel attacks do not work in this environment. However, there have been developed works that adapt the attacks to ARM CPUs, as is the case of Lipp et al. [LGS+16].

The work initially identifies the challenges for implementing cache side-channel attacks in ARM processors: the fact that the last-level caches are not inclusive, usually there are multiple CPUs that do not share a cache, ARM processors do not support a flush instruction, they use a pseudo-random replacement policy, and cycle-accurate timings require root access. Then, the authors adapt the attacks and demonstrate the applicability of the cache attacks on ARM environments. The adaptations work irrespective of the actual cache organization, and their functionality is demonstrated on Android smartphones.

# Methodology

### System Overview 4.1

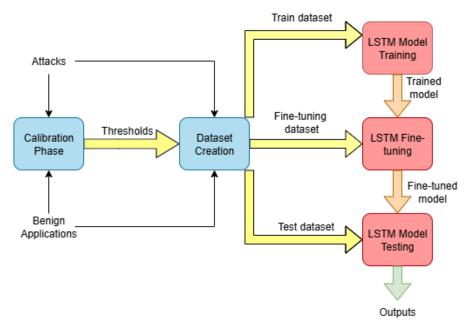

As described in Chapter 1, the implemented system has the aim of identifying cache side-channel attacks by monitoring HPCs, using an overflow-based approach. In order to evaluate whether the learning could be transferred among different architectures, the experiments were conducted in two different architectures. Figure 4.1 shows the general overview of the system flow.

Figure 4.1: Proposed System Overview

Initially, the datasets are created using the overflow technique while monitoring the HPCs running on the machine. In other words, the system is monitoring the values of the selected Hardware Performance Counters and, when the value of either of them exceeds a defined threshold, a sample of the dataset is collected. Therefore, it is first necessary to determine the threshold values for each HPC. This is done in the Calibration Phase, where the system is constantly monitoring the HPC values while benign applications are running. At the same time, it keeps adjusting the values of the thresholds until the overflow events are sampled at around a defined frequency. Once the thresholds are defined, the training dataset itself is created using these fixed values by monitoring the overflows, while attacks and benign applications are also running on the computer. In the next step, after their creation, the datasets are used for training and evaluating the deep learning model. The defined LSTM model was initially trained using the training and validation datasets. Then, in order to assure that the learned knowledge is transferred among different architectures, the model goes through a fine-tuning phase. And finally, the resulting model is evaluated on the test dataset. With the aim of guaranteeing the robustness of the model, the training and evaluation were performed on various scenarios, including different dataset combinations from both platforms.

#### 4.2**Data Selection**

Prior to the generation of the datasets to train and evaluate the system, it is necessary to define how to create then. That includes defining which HPCs will be monitored to better identify the attacks, ensuring that they are available for monitoring on the two chosen platforms. In addition, both the attacks and the benign applications need to be determined according to their relevance to the attack detection task and the availability on the platforms.

#### 4.2.1 **HPCs Definition**

As mentioned in Section 2.2.2, there is a variety of HPCs available on the different computer architectures. However, in addition to the constraint of the availability of the event counter, each platform has a limitation on how many events can be monitored concurrently. In this work, we perform experiments both on Intel and ARM architectures.

Modern Intel CPUs support three fixed and four programmable counters per core [Int25]. The ARM computer, more specifically a Raspberry Pi in our case, can support up to four HPCs being monitored concurrently [Ras22]. Therefore, in order to guarantee that the datasets created in both platforms can be used interchangeably, the number of HPCs being monitored concurrently needs to be chosen in accordance with the limitations of both of them. In this case, we chose to create the datasets by monitoring four events concurrently.

In the next step, it is necessary to define which HPCs will be monitored for overflows. This has to be done first by observing the list of available events on each platform. The

events available for monitoring in the Intel platform are available in [perc]. For the Raspberry Pi platform (ARM architecture), the list of available events can be found at [perd].

From the list of available HPC events for monitoring, it is necessary to choose the ones that best reflect the behavior of the computer during the cache SCA. In her work, Al-zubi [AZW24] performed an evaluation and ranked the events that are most related to this type of situation. This evaluation was made using the technique of Maximum Relevance Minimum Redundancy (mRMR) [FTS20], which identifies features that are least related to each other and most strongly correlated with the class.

After the described steps, the four HPC events to be monitored concurrently by our system are:

- PERF COUNT HW INSTRUCTIONS = Counts the number of retired instructions.

- PERF COUNT HW BRANCH MISSES = Counts the number of mispredicted branch instructions.

- PERF COUNT HW CACHE L1D/RESULT MISS = Counts the number of cache misses for the Level-1 Data Cache.

- PERF COUNT HW CPU CYCLES = Counts the total number of CPU cycles.

#### 4.2.2 Attacks

Among the list of implemented Cache SCA, as described in Section 2.1, we needed to select the attacks that we aim to detect in this work. Since we are also aiming to perform transfer learning between two different architectures, the attacks involved in the experiments need to have an available implementation that works on both the chosen platforms for our experiments.

Due to its relevance and number of variants, the main attack that we aim to detect in this work was Spectre Attack [KHF<sup>+</sup>20], explained and described in Section 2.1.4. This attack was extensively studied, both in works that also aim to detect it, as in works that propose different variations for it. The variants chosen to be explored in this work are: Spectre variant 1 and variant 2.

In order to increase the generalization ability of the proposed system, we also included the Rowhammer attack in our experiments [GMM16]. In addition to the most common implementation of this attack, there is also an adapted implementation for the ARM architecture, more specifically, for the Raspberry Pi platform [BYL21].

#### 4.2.3 Benign Applications

The aim of this work is to develop a system that is able to detect the presence of cache SCA regardless of the remaining workload running in the computer at the same time.

Therefore, it is necessary to train and evaluate the system in different scenarios and under different workloads, to ensure that the technique is still able to identify it.

In order to cover both situations of light and heavy workloads, the datasets created to train and evaluate the system included applications from the following classes:

- Normal workload: includes internet browsing, file explorer, file compressing, text and spreadsheet editing

- Encoding: includes string, video, and audio encoding

- Reasoning: includes SAT solvers

- Benchmarks: includes computationally heavy benchmarks

- Memory stress tests

- Firewall management

The complete list of benign applications used in the dataset creation is shown in Section 5.2.3.

#### 4.3 **Dataset Creation**

After the selection of the HPC events to be monitored, the attacks and benign applications to be used in the dataset creation, the next step is to effectively create them.

Previous works that use HPC events to detect attacks usually employ the sampling technique to monitor these events [AZW24] [TZW<sup>+</sup>20] [GMES19] [KHK<sup>+</sup>24] [BPSS24] That means that, repeatedly after a pre-defined time interval (for example, 100 ms), the system measures the values of HPCs. Each measurement consists of a sample in the dataset, which is used as an input to a ML model that aims to learn patterns and detect attacks.

However, this technique has some limitations. First, the fact that the time interval is fixed does not allow flexibility on the monitoring. If, on the one hand, the attack is faster than the interval, the system might miss the attack. However, on the other side, if the attack is much slower, the overhead produced will be significantly higher, generating more data than is necessary.

Secondly, the sampling approach results in the model learning the pattern for attacks in a specific platform or architecture. However, different platforms behave differently with respect to HPC values, due to the differences in the architecture, memory, and cache. Therefore, the model learning is not transferred among platforms, which means that a model learned in one platform cannot be used to detect attacks in a different one.

In order to overcome these limitations and generate a model that better performs in the attack detection of different platforms, this work proposes that the datasets be created using an overflow-based approach. As mentioned in Section 4.1, this technique is composed of two parts: the calibration phase and the overflow monitoring.

#### 4.3.1 Calibration Phase

The initial step of the dataset creation is to perform the calibration, or, in other words, to determine the thresholds for each HPC to trigger an overflow. This needs to be executed for each platform, taking into account the benign applications.

On this calibration phase, we set initial values for the selected HPCs. In order to select these initial values, we performed the sampling of the event counters every 100 ms, while running the applications. Then, we calculated the average of the sampled values, and subtracted their standard deviation. These calculated results are defined as the initial threshold for each HPC.