# Improving Synthesis of Skolem **Functions and Boolean Circuits**

## DISSERTATION

zur Erlangung des akademischen Grades

### Doktor der Technischen Wissenschaften

eingereicht von

Dipl.-Ing. Franz-Xaver Reichl

Matrikelnummer 01356186

| an der Fakultat für Informatik                                                |                  |                       |

|-------------------------------------------------------------------------------|------------------|-----------------------|

| der Technischen Universität Wien                                              |                  |                       |

| Betreuung: Dr. Friedrich Slivovsky<br>Zweitbetreuung: Prof. Dr. Stefan Szeide | er               |                       |

| Diese Dissertation haben begutachtet:                                         |                  |                       |

|                                                                               |                  |                       |

|                                                                               | Christoph Scholl | Jie-Hong Roland Jiang |

| Wien, 28. November 2024                                                       |                  |                       |

| wien, 20. November 2024                                                       |                  | Franz-Xaver Reichl    |

# Improving Synthesis of Skolem **Functions and Boolean Circuits**

## DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

### Doktor der Technischen Wissenschaften

by

Dipl.-Ing. Franz-Xaver Reichl

Registration Number 01356186

| to the Faculty of Informatics                                           |                  |                       |

|-------------------------------------------------------------------------|------------------|-----------------------|

| at the TU Wien                                                          |                  |                       |

| Advisor: Dr. Friedrich Slivovsky<br>Second advisor: Prof. Dr. Stefan Sz | reider           |                       |

| The dissertation has been reviewed                                      | by:              |                       |

| _                                                                       | Christoph Scholl | Jie-Hong Roland Jiang |

| Vienna, November 28, 2024                                               |                  |                       |

|                                                                         |                  | Franz-Xaver Reichl    |

## Erklärung zur Verfassung der Arbeit

Dipl.-Ing. Franz-Xaver Reichl

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

| Wien   | 28 | Novem | her | 2024 |

|--------|----|-------|-----|------|

| vvien. |    | novem | Dei | 2024 |

## Acknowledgements

First and foremost, I would like to thank my supervisor Friedrich Slivovsky for his guidance and his advices, and for introducing me to the world of (D)QBF. Even though, due to the pandemic the conditions for starting a PhD were not optimal, Friedrich's support helped me to make first steps in the academic world. I really enjoyed working with you, thanks! I am also very glad that I had Stefan Szeider as my second advisor, thanks a lot for your support. Moreover, I would like to thank my reviewers Christoph Scholl and Jie-Hong Roland Jiang for their detailed and valuable feedback.

Special thanks also go to my colleagues at the Algorithms and Complexity group. In particular, I would like to thank Doris Brazda for helping to shoulder all the bureaucratic burdens. Moreover, I would like to thank Alexis, Hai, Johannes and Vaidyanathan for having lots of great lunch and coffee breaks. Further, I would like to thank Anna Prianichnikova for her support in the LogiCS doctoral college.

I would also like to thank my parents for their continuous support. In particular, I would like to thank my mother for always encouraging my interest in math. Moreover, I also want to thank my grandparents for their part in a childhood I happily look back at.

The work presented in this thesis was funded by the Vienna Science and Technology Fund (WWTF) (10.47379/ICT19060) and the Austrian Science Fund (FWF) (10.55776/W1255).

## Kurzfassung

Vom Standpunkt der Komplexitätstheorie geht man davon aus, dass es für das Erfüllbarkeitsproblem der Aussagenlogik (SAT) keinen effizienten Algorithmus gibt. Nichtsdestotrotz können moderne Entscheidungsprozeduren für SAT Formeln mit Millionen von Variablen und Klauseln lösen. Der Erfolg dieser Prozeduren motiviert die Arbeit an Entscheidungsprozeduren für stärkere Logiken, wie abhängigkeitsquantifizierte boolsche Formeln (DQBF). Aufgrund der effizienten Entscheidungsprozeduren für das SAT-Problem wurden viele verschiedene Probleme mittels einer Kodierung in Aussagenlogik gelöst. Dies umfasst im Speziellen das Problem der Berechnung von kleinen Schaltkreisen.

Eine Entscheidungsprozedur für DQBF DQBF erweitern die Aussagenlogik mit universellen und existenziellen Quantoren über Wahrheitswerte. Im Gegensatz zu quantifizierten boolschen Formeln (QBF) werden in DQBF die Abhängigkeiten von existentiellen Variablen explizit angegeben und nicht implizit durch die Ordnung der Quantoren bestimmt. Wir präsentieren einen neuen Algorithmus für das Erfüllbarkeitsproblem von DQBF, der direkt mit Skolemfunktionen arbeitet. Der Algorithmus nutzt Definitionen im Sinne der Aussagenlogik, um eindeutig bestimmte Skolemfunktionen zu berechnen. Des Weiteren nutzt der Algorithmus durch Gegenbeispiele geleitete induktive Synthese (CEGIS), um die Skolemfunktionen der verbleibenden Variablen zu adaptieren. Dadurch kann der Algorithmus für erfüllbare DQBF Skolemfunktionen ohne Mehraufwand bestimmen. Wir werden zeigen, dass der Algorithmus tatsächlich das Entscheidungsproblem für DQBF löst. Dieser Algorithmus wurde in einem Programm names PEDANT implementiert. In einer experimentellen Evaluierung werden wir zeigen, dass Pedant für Standardbenchmarks mehr Formeln als andere aktuelle Entscheidungsprozeduren lösen kann.

Minimierung von Schaltkreisen Es gibt keine effizienten Algorithmen, um kleinstmögliche Schaltkreise für eine bestimmte boolsche Funktion zu bestimmen. Aus diesem Grund müssen heuristische Methoden angewandt werden, um kleine Schaltkreise zu berechnen. Wir schlagen eine neue Methode zum Minimieren von Schaltkreisen vor. Diese Methode ist eine SAT-basierte lokale Verbesserungsmethode (SLIM). Um einen Schaltkreis zu verkleinern, werden iterativ Teilschaltkreise eines gegebenen Schaltkreises durch kleinstmögliche Schaltkreise ersetzt. Die für die Ersetzungen verwendeten Schaltkreise werden dabei entweder mittels einer SAT- oder einer QBF-Kodierung ermittelt. Hierfür

ist es möglich, sowohl Teilschaltkreise mit einem einzelnen Ausgang als auch Schaltkreise mit mehreren Ausgängen zu betrachten. Um eine möglichsts große Freiheit für das Auffinden einer Ersetzung zu erhalten, werden don't cares des Teilschaltkreises berücksichtigt. Diese Minimierungsmethode wurde in einem Programm namens ESLIM implementiert. Basierend auf einer experimentellen Evaluierung zeigen wir, dass ESLIM zusammen mit dem Standardprogramm für die Schaltkreissynthese ABC bessere Ergebnisse liefert als ABC alleine. Schlussendlich zeigen wir auch, dass mit ESLIM viele der aktuell kleinsten

Schaltkreise der EPFL Benchmarkmenge weiter verkleinert werden können.

**TU Sibliothek**, Die approbierte gedruckte Originalversion dieser Dissertation ist an der TU Wien Bibliothek verfügbar.

The approved original version of this doctoral thesis is available in print at TU Wien Bibliothek.

## Abstract

While the propositional satisfiability problem SAT is intractable, from a theoretical perspective, modern SAT solvers can still handle formulas with millions of variables and clauses. This success of SAT solving motivates research on decision procedures for even stronger logics like Dependency Quantified Boolean Formulas (DQBF). To make use of the capabilities of modern SAT solvers, various different problems have been encoded in propositional logic. In particular, this includes the problem of finding small circuits.

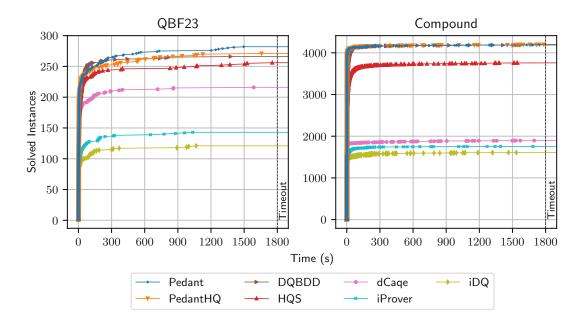

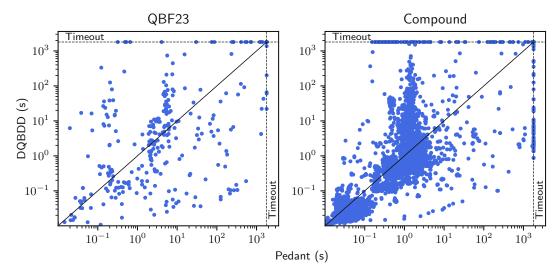

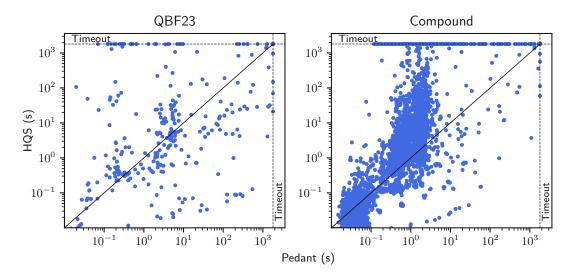

**Deciding DQBF** DQBF extend propositional logic by universal and existential quantification over truth values. Unlike to Quantified Boolean Formulas (QBF), in DQBF, dependencies of existentially quantified variables are explicitly stated and not implicitly determined by the ordering of quantifiers. We propose a new decision procedure for DQBF that directly reasons at the level of Skolem functions. The procedure makes use of propositional definitions to extract uniquely defined Skolem functions and counterexample guided inductive synthesis (CEGIS) to refine Skolem functions for the remaining variables. This allows to derive Skolem functions for satisfiable DQBF with no overhead. We will proof that the proposed algorithm is indeed a decision procedure for DQBF. Moreover, in an experimental evaluation, we will show that our solver PEDANT that implements the proposed algorithm, surpassed the performance of state-of-the-art DQBF solvers on standard benchmarks.

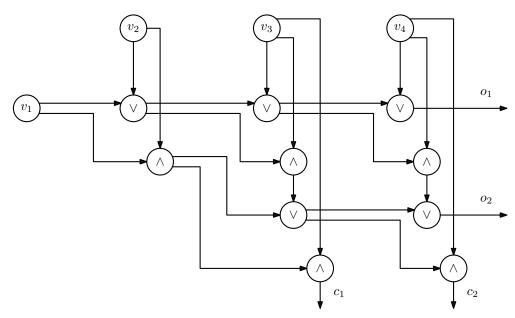

**Circuit Minimization** Determining provably minimum size circuits computing a given Boolean function is computationally intractable. For this reason heuristic, methods need to be considered for obtaining small circuits. We propose a new circuit minimization approach that belongs to the SAT-based Local Improvement Method (SLIM) framework. In this approach, we incrementally replace subcircuits of a given circuit by minimum size replacement circuits. This is achieved by either making use of a QBF or of a SAT encoding. The presented method allows to consider both single- and multi-output subcircuits. Additionally, it makes use of the full implementational freedom for determining a replacement circuit by taking don't cares into account. We implemented this minimization method in the tool ESLIM. In an experimental evaluation, we show that using ESLIM together with the state-of-the-art synthesis tool ABC results in significantly smaller circuits compared to applying ABC alone. Moreover, we used ESLIM to further improve the current best solutions for the EPFL benchmark set.

# Contents

| K            | urzfassung                                                                                                                                                                                              | ix                                   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| $\mathbf{A}$ | bstract                                                                                                                                                                                                 | xi                                   |

| C            | ontents                                                                                                                                                                                                 | xiii                                 |

| Pı           | reface                                                                                                                                                                                                  | xv                                   |

| Ι            | Deciding DQBF by Model Extraction                                                                                                                                                                       | 1                                    |

| 1            | Introduction – Part I                                                                                                                                                                                   | 3                                    |

| 2            | Background – Part I         2.1 Basic Concepts          2.2 Propositional Definitions          2.3 DQBF          2.4 Proof Systems for DQBF          2.5 Solving DQBF          2.6 Applications of DQBF | 7<br>7<br>10<br>12<br>14<br>16<br>18 |

| 3            | A Two-Phase Algorithm                                                                                                                                                                                   | 19                                   |

| 4            | Counterexample-Guided Algorithm 4.1 Overview                                                                                                                                                            | 23<br>24<br>25<br>29<br>35           |

| 5            | Experiments – Part I  5.1 Implementation                                                                                                                                                                | <b>51</b> 51 52                      |

| 6            | Conclusions – Part I                                                                                                                                                                                    | 59                                   |

|              |                                                                                                                                                                                                         | xiii                                 |

| II        | Local Improvement of Circuits                          | 61                              |

|-----------|--------------------------------------------------------|---------------------------------|

| 7         | Introduction – Part II                                 | 63                              |

| 8         | Background - Part II  8.1 Basic Concepts               | 67<br>67<br>72<br>73<br>74      |

| 9         | Encodings for Exact Synthesis 9.1 Normalizing Circuits | <b>7</b> 5<br>75<br>77<br>82    |

| 10        | Circuit Minimization  10.1 Subcircuit Selection        | 87<br>88<br>89<br>100           |

| 11        | Experiments – Part II  11.1 Implementation             | 105<br>106<br>106<br>107<br>112 |

| <b>12</b> | Conclusions – Part II                                  | 117                             |

| Po        | ostface                                                | 119                             |

| Lis       | st of Figures                                          | 121                             |

| Lis       | st of Tables                                           | <b>12</b> 3                     |

| Lis       | st of Algorithms                                       | 125                             |

| Bi        | bliography                                             | 127                             |

## **Preface**

Deciding satisfiability of propositional logic (SAT) is the prototypical NP-complete problem [Coo71]. As such, from a theoretical point of view, the SAT problem is considered to be intractable. Nevertheless, SAT-solvers show ever improving performance [HJS19; Fro+21, and modern SAT solvers can handle formulas with millions of variables [MLM21]. This motivates research on decision procedures for the satisfiability problem of logics with an even higher complexity, like Dependency Quantified Boolean Formulas (DQBF) [PR79]. While deciding satisfiability of DQBF is harder than deciding satisfiability of propositional logic, the higher expressiveness of DQBF might outweigh the slower decision procedures for practical applications. We will present a new decision procedure for DQBF in Part I.

Several applications of DQBF were proposed in recent years. One of the most prominent applications is partial equivalence checking (PEC) [Git+13b; BCJ14a]. In PEC we are given a circuit containing unspecified parts and a specification for the circuit. The goal is to check whether there are implementations for the missing parts such that the circuit satisfies the specification. If such implementations exist, it is also of interest to find some implementations. Deciding PEC can be done by encoding the problem into DQBF and by checking the satisfiability of the encoding. Moreover, implementations for the unspecified parts can be obtained from a model of the encoding.

Partial equivalence checking can be applied in the integrated circuit engineering change order (ECO) problem [JKL20]. In ECO an already optimized circuit is given, whose specification is changed. Now the task is to modify the given circuit such that the new specification is satisfied. The ECO problem is of practical relevance, as it can for example be used to fix functional errors in an already optimized circuit design without the need of computing a new design from scratch. By cutting out subcircuits from the given implementation, we can make use of PEC in order to check if there are implementations for the now missing parts of the circuit such that the new specification is satisfied. Of course, we are not only interested if such implementations exist, but we also want to obtain some implementations. As discussed above, the missing parts in PEC can be obtained from a model of a DQBF encoding.

As the given circuit is in general already optimized, we do not want to use any circuit for realizing the modifications, but we want to use already optimized ones. One metric for optimizing circuits that can be of interest is the circuit size. This is a motivation for the second part of this thesis, which is concerned with reducing the size of circuits.

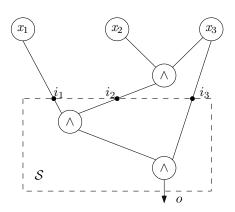

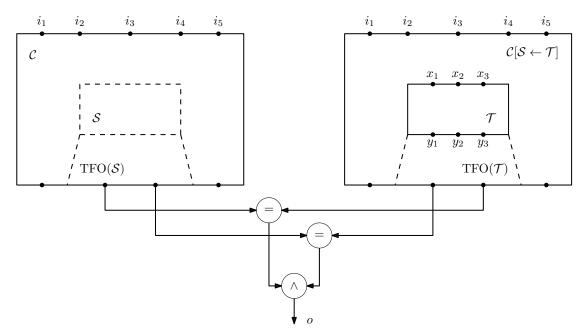

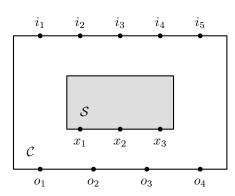

For computing circuits with a small size the efficiency of modern SAT solvers can be harnessed [Haa+20; KPS22]. We propose a new SAT/QBF-based circuit minimization method that improves circuits by rewriting subcircuits in Part II. This method allows handling single-output as well as multi-output subcircuits. Additionally, it exploits the full implementational freedom of subcircuits by taking don't cares into account.

Part I Deciding DQBF by Model Extraction Dependency Quantified Boolean Formulas (DQBF) extend Quantified Boolean Formulas (QBF) by allowing to explicitly specify the dependencies of existentially quantified variables. Consequently, in general, DQBF have existential variables with incomparable dependency sets. Deciding satisfiability of DQBF is NEXPTIME-complete [PAR01]. As such, it has a higher complexity than SAT or even the satisfiability problem of Quantified Boolean Formulas (QBF), which is PSPACE-complete [SM73]. While deciding DQBF is hard, the possibility of explicitly specifying dependencies allows to concisely encode several problems, which is not possible with SAT or even QBF. As mentioned earlier, a prominent example for an application of DQBF is partial equivalence checking [Git+13b].

In practice encoding problems in DQBF requires efficient procedures for deciding DQBF. Recent years showed a significant increase in the performance of available solvers. Still one shortcoming of several solvers is that they only provide yes/no answers but no certificates. Certificates are useful not just for validating the results of solvers, but models for satisfiable formulas can be of relevance in practice. As we saw earlier, models can be used to find implementations of the missing parts in partial equivalence checking.

In this part, we present a new decision procedure for DQBF that is able to generate certificates for satisfiable DQBF with no overhead. We will first discuss the fundamental idea of this procedure based on a simplified decision procedure for DQBF in Chapter 3. Next, in Chapter 4 we will introduce an advanced decision procedure for DQBF that is based on incrementally refining a candidate model. Finally, in Chapter 5, we will compare our solver Pedant, that is based on the proposed decision procedure, with state-of-the-art DQBF solvers on standard benchmark sets.

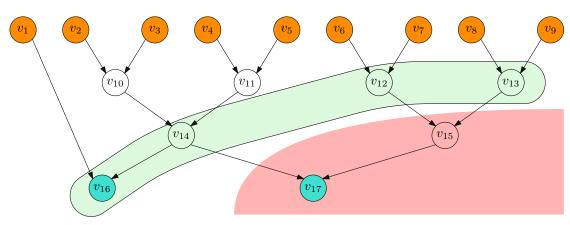

Part II Local Improvement of Circuits The ever-increasing size and complexity of modern integrated circuits makes both the design and the optimization of circuits a challenging task, both are unthinkable without some form of automation. Among others, one task for optimizing circuits is the reduction of a circuit's size. The increasing prices of silicon wafers in recent years [Gai21] indicate that small circuits are of importance in practice.

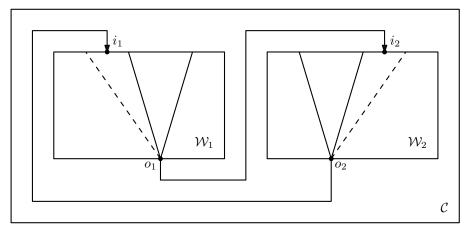

Computing a minimum size circuit for a given Boolean function is an NP-complete problem [ILO20]. This is reflected by the observation that, in practice, finding minimum size circuits is limited to very small circuits with not many more than 10 fanin-2 gates [KKY09; CMM23]. For this reason, heuristic methods need to be considered. One approach is to improve a circuit by replacing subcircuits with smaller circuits. Typically,

this approach is limited to single-output [Rie+19] subcircuits, or it does not fully capture the implementational freedom for finding a replacement circuit [KPS22; Lee+18].

In this part, we will introduce a new method for minimizing circuit sizes that is based on replacing subcircuits by optimal replacement circuits. This method makes use of the full implementational freedom of multi-output subcircuits. First, we will discuss SAT and QBF encodings for computing minimum size circuits in Chapter 9. Next, we will adapt these encodings for computing minimum size replacement circuits of subcircuits in Chapter 10. These encodings can then be used for incrementally replacing subcircuits. This approach for minimizing circuits is implemented in the ESLIM system. In Chapter 11, we will experimentally evaluate ESLIM on standard benchmarks.

The two parts were written such that they can be read independently. This was not possible without introducing some redundancies in the preliminaries of the two parts.

**Publications** This thesis is based on the following publications:

- 1. Franz-Xaver Reichl, Friedrich Slivovsky, and Stefan Szeider. "Certified DQBF Solving by Definition Extraction". In: Theory and Applications of Satisfiability Testing - SAT 2021 - 24th International Conference, Barcelona, Spain, July 5-9, 2021, Proceedings. Vol. 12831. Lecture Notes in Computer Science. Springer, 2021, pp. 499–517

- 2. Franz-Xaver Reichl and Friedrich Slivovsky. "Pedant: A Certifying DQBF Solver". In: 25th International Conference on Theory and Applications of Satisfiability Testing, SAT 2022, August 2-5, 2022, Haifa, Israel. Vol. 236. LIPIcs. Schloss Dagstuhl - Leibniz-Zentrum für Informatik, 2022, 20:1–20:10

- 3. Franz-Xaver Reichl, Friedrich Slivovsky, and Stefan Szeider. "Circuit Minimization with QBF-Based Exact Synthesis". In: Thirty-Seventh AAAI Conference on Artificial Intelligence, AAAI 2023, Washington, DC, USA, February 7-14, 2023. AAAI Press, 2023, pp. 4087–4094

- 4. Franz-Xaver Reichl, Friedrich Slivovsky, and Stefan Szeider. "eSLIM: Circuit Minimization with SAT Based Local Improvement". In: 27th International Conference on Theory and Applications of Satisfiability Testing, SAT 2024, August 21-24, 2024, Pune, India. Vol. 305. LIPIcs. Schloss Dagstuhl - Leibniz-Zentrum für Informatik, 2024, 23:1-23:14 - Runner-up for the best student paper award.

The following software was implemented as part of this thesis. Software

**Pedant** A model-generating DQBF solver.

Available at: https://github.com/fslivovsky/pedant-solver

**eSLIM** A tool for minimizing Circuits applying the SLIM framework.

Available at: https://github.com/fxreichl/eSLIM

# Part I Deciding DQBF by Model Extraction

CHAPTER.

## Introduction – Part I

The last decades showed tremendous progress in propositional satisfiability (SAT) solving [HJS19; Fro+21]. This resulted in a growing number of applications of SAT in various domains, ranging from AI planning [Rin21] over software verification [Kro21] to the exact synthesis of circuits [KKY09; Haa+20]. Moreover, efficient SAT solvers were essential for recent progress in constrained sampling and counting [Mee+16], two problems with many applications in artificial intelligence. In these cases, SAT solvers are used to deal with problems from complexity classes beyond NP. Consequently, propositional encodings grow super-polynomially in the size of the original instances. For this reason, these problems are not directly encoded in propositional logic but have to be reduced to a sequence of SAT instances.

The success of SAT solving on the one hand, and the inability of propositional logic to succinctly encode problems of interest on the other hand, have prompted the development of decision procedures for more succinct generalizations of propositional logic such as Quantified Boolean Formulas (QBF). Deciding QBF is PSPACE-complete [SM73] and thus believed to be much harder than SAT, but in practice, the benefits of a smaller encoding may outweigh the disadvantage of slower decision procedures [Fay+17]. A QBF is true if it has a model, which is a family of Boolean functions (often called Skolem functions) that satisfy the matrix of the input formula for each assignment of universal variables. The arguments of each Skolem function are implicitly determined by the nesting of existential and universal quantifiers.

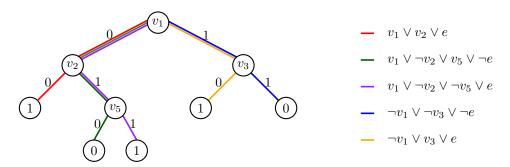

Going even further, we can generalize QBF to Dependency Quantified Boolean Formulas (DQBF). DQBF extend QBF by allowing to explicitly state a dependency set for each existential variable, which is a subset of universal variables allowed as arguments of the corresponding Skolem function [PAR01; BCJ14a]. Consequently, unlike in QBF, the sets of arguments of the Skolem functions may no longer be ordered with respect to set inclusion. As Skolem functions in DQBF may have incomparable dependency sets, it is

not necessarily possible to coordinate the Skolem functions for two existential variables. Consider the DQBF

$$\Phi = \forall u_1, u_2 \exists e_1(u_1), e_2(u_2).(u_1 \land u_2) \Leftrightarrow (e_1 \lor e_2).$$

In this formula, we want to find an assignment of  $e_1$  that only depends on  $u_1$  and an assignment of  $e_2$  that only depends on  $u_2$ , such that at least one existentially quantified variable is assigned to true if and only if both universally quantified variables are assigned to true. As the dependency sets are not comparable, the Skolem function for  $e_1$  may not "react" to the Skolem function for  $e_2$  and vice versa. Since the clause  $e_1 \vee e_2$  must be satisfied in case both  $u_1$  and  $u_2$  are assigned to true, we can assume w.l.o.g. that  $e_1$  is assigned to true in this case. But  $e_1$  must not react to  $u_2$ . This causes a counterexample, as  $e_1$  is also assigned to true, whenever  $u_1$  is assigned to true and  $u_2$  to false. Therefore, we cannot find Skolem functions for the formula.

The additional expressiveness provided by the explicit dependency sets comes with a price: deciding DQBF is NEXPTIME-complete [PR79; PAR01]. Thus, it is believed to be even much harder than QBF. Before, we mentioned that, in practice, it can be beneficial to use QBF instead of SAT, due to the succinctness of QBF encodings, despite the slower decision procedures for QBF. Similarly, the expressiveness of DQBF can outweigh its slower decision procedures.

DQBF have been used for encoding several different problems. The most prominent one is probably partial equivalence checking (PEC). In PEC, we are given a circuit that contains unspecified parts. The goal is to check whether there is some implementation of these parts, such that the entire circuit satisfies a given specification [Git+13b]. DQBF have also been used for succinctly encoding the existence of Boolean functions subject to a set of constraints [Rab17] and for bounded synthesis [Fay+17]. Moreover, the problem of succinct graph 3-colorability or the problem of checking the existence of Hamiltonian cycles were reduced to DQBF [Che+22]. Furthermore, DQBF solvers could be used as backend solvers for other logics in NEXPTIME. This includes Effectively Propositional Logic (EPR) [Lew80], or certain bit-vector logics for satisfiability modulo theories (SMT) [KFB16].

Several decision procedures for DQBF have been developed in recent years. Conceptually, these solvers either reduce to SAT or QBF by instantiating [Frö+14] or eliminating universal variables [Git+15; Wim+17; GSW19; Síč20], or lift Conflict-Driven Clause Learning (CDCL) to non-linear quantifier prefixes by imposing additional constraints [FKB12; TR19. We believe these methods should be complemented with algorithms that directly reason at the level of Skolem functions [RS16]. A strong argument in favor of such an approach is the fact that DQBF instances often have a large fraction of unique Skolem functions that can be obtained by definition extraction, but the current solving paradigms have no direct way of exploiting this [Sli20].

<sup>&</sup>lt;sup>1</sup>An approach that does not fit this simplified classification is the First-Order solver IPROVER [Kor08].

As in the case of SAT solvers, it is not always sufficient to "only" obtain a yes/no answer from a DQBF solver for deciding the satisfiability of a formula. For example, solving a PEC instance, a yes/no answer only allows to conclude whether an implementation of the missing parts exists. But in case there is such an implementation, we do not know how such an implementation looks like. For this reason, it can be beneficial if DQBF solvers also return Skolem functions for each existentially quantified variable for satisfiable DQBF—similar to SAT solvers returning satisfying assignments for satisfiable formulas. In the case of partial equivalence checking, the Skolem functions describe the input-output relations of each unknown part. While DQBF solvers that can generate Skolem functions [Wim+16a] exist, most solvers do not compute Skolem functions. Using decision procedures for DQBF that reason directly at the level of Skolem functions could thus help to generate Skolem functions with no overhead.

In this part, we describe a new decision procedure for DQBF in the Counter-Example Guided Inductive Synthesis (CEGIS) paradigm [Sol+06; SJB08; JS17]. The procedure follows a dual strategy. To show satisfiability of formulas, it keeps a candidate model for the considered formula. This candidate is initialized by computing propositional definitions for existentially quantified variables in terms of their dependency sets. The algorithm then tries to refine this candidate to obtain an actual model. For this purpose, it incrementally determines counterexamples for the current candidate. These counterexamples are then used to refine the candidate, such that the updated candidate does not yield the same counterexample again in subsequent iterations. If at some point no further counterexamples can be found, we can conclude that the current candidate is an actual model, which means that the formula is satisfiable. In this case, the algorithm can return a Skolem function for each existentially quantified variable with no overhead.

To show unsatisfiability of formulas, the algorithm computes a sequence of clauses. The literals in these clauses correspond to existentially quantified variables, annotated by universal assignments of their dependency set. We use a SAT solver to check whether these clauses are satisfiable or not. In case they are unsatisfiable, it is not possible to refine the candidate to a model, i.e., the given DQBF is unsatisfiable.

We will show that the proposed algorithm is indeed a decision procedure for DQBF. For this purpose, we will show that the clauses, used to show unsatisfiability, correspond to clauses that can be derived by the  $\forall \text{Exp+Res}$  proof system for DQBF [JM13; Bey+19]. As this proof system is sound, the unsatisfiability of these clauses shows the unsatisfiability of the given DQBF.

We implemented the decision procedure in a system named PEDANT. In an experimental evaluation on standard benchmark sets, PEDANT could solve more instances than other state-of-the-art DQBF solvers.

Organization of Part I First, we will cover notations and definitions used throughout this part in Chapter 2. In this chapter, we will also give a brief overview of related work. Next, we will introduce a two-phase algorithm for deciding DQBF in Chapter 3. This

algorithm is not indented for a practical application. Instead, it introduces some key ideas. In Chapter 4, we describe our main decision procedure for DQBF. In Chapter 5, we experimentally evaluate our DQBF solver PEDANT, which implements this procedure. Finally, we conclude this part of the thesis in Chapter 6.

This part is mainly based on our previously published papers on DQBF solving. In particular, the two-phase algorithm, presented in Chapter 3, was covered in [RSS21]. A basic form of the CEGIS algorithm, presented in Chapter 4, was first discussed in [RSS21]. The version of the algorithm, presented in this thesis, is based on the algorithm given in [RS22]. We will discuss some parts of the algorithm that have not been covered in detail before, this in particular includes the conflict minimization. While in an extended version of [RSS21] we already showed that the algorithms are decision procedures, we both simplified the arguments and adapted them to the newest version of the CEGIS algorithm.

## Background – Part I

In this chapter, we will introduce terminology and notations used throughout this part of the thesis. Moreover, we will give a brief overview of related work.

### 2.1Basic Concepts

We will denote the set of positive natural numbers by  $\mathbb{N}^*$  and for  $n \in \mathbb{N}^*$  we will denote the set  $\{1,\ldots,n\}$  by [n].

### 2.1.1Graphs

In this section, we will briefly introduce concepts and notations from graph theory, used in this part of the thesis. For a comprehensive introduction to graph theory, we refer the reader to Diestel's book [Die00].

A directed graph G is a pair (V, E) s.t.  $E \subseteq V \times V$ . We denote elements of V as vertices and elements of E as edges of the graph G. Given a directed graph G, we denote its vertices by V(G) and its edges by E(G). A directed graph is *finite* if it has a finite number of vertices and edges. Throughout this thesis we will only consider finite directed graphs. Thus, if we talk about graphs we always mean finite directed graphs.

Let G be a graph with vertices  $v_1$  and  $v_2$  s.t. G contains the edge  $(v_1, v_2)$ . Then we denote  $v_2$  as a successor of  $v_1$  and  $v_1$  as a predecessor of  $v_2$ . Let  $X \subseteq V(G)$  be a set of vertices then we define the graph G-X as the graph with vertices  $V(G)\setminus X$  and edges  $\{(v_1, v_2) \in E(G) \mid v_1 \notin X, v_2 \notin X\}.$

A path P in a graph G is a sequence of vertices  $v_0, v_1, \ldots, v_n$  with  $(v_i, v_{i+1}) \in E(G)$  for each  $0 \le i < n$ . Additionally, for each  $i \in [n]$ , we say that P contains the edge  $(v_{i-1}, v_i)$ . We say that P connects the vertices  $v_0$  and  $v_n$ . If there is a path connecting two vertices x and y, we say that x is connected to y. The length of a path P is the number of edges

in P. Let P be a path of length  $\ell$  with  $\ell \geq 1$ . The path P is cyclic if  $v_0 = v_{\ell}$ . A graph is cyclic if it contains a cyclic path and acyclic if it does not. A graph that is both directed and acyclic is often referred to as directed acyclic graph (DAG). All graphs considered in this thesis are DAGs.

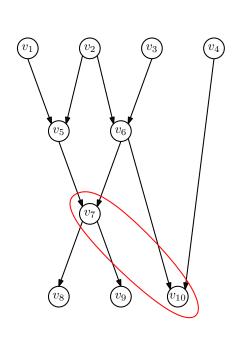

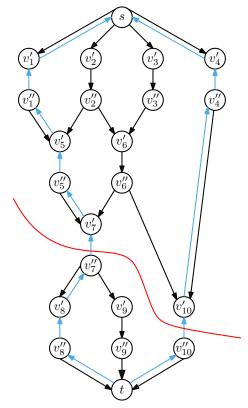

Let G be a graph and  $A, B, S \subseteq V(G)$  sets of vertices. If, for every pair of vertices a, bwith  $a \in A$  and  $b \in B$ , and every path P connecting a and b, there is a vertex  $s \in S$  s.t. P contains s, then S is a separator for A and B. A separator S for A and B is minimal if, for every subset  $S' \subseteq S$ , the set S' is not a separator for A and B. A minimum separator for A and B is a separator S of minimum size.

### 2.1.2Flows

For a comprehensive introduction of flows we again refer to Diestel's book [Die00] respectively to the book by Cormen et al. [Cor+09], which also covers algorithms for max-flow computation.

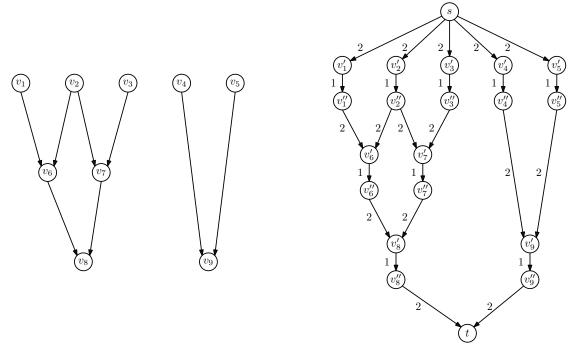

A flow network F is a tuple (G, s, t, c) where G is a graph  $(V, E), s, t \in V$  and c is a function  $c: V^2 \to \mathbb{R}_{>0}$ . We call the vertex s the source of F, t the sink of F and the function c the capacity of F. For the sake of simplicity we always assume that c(u,v)=0if  $(u,v) \notin E$ . Additionally, we assume that there are no vertices v with  $(v,s) \in E$  or  $(t,v) \in E$ . A flow f of F is a function  $f: V^2 \to \mathbb{R}$ . The flow f has to satisfy the following two conditions:

- 1. For all  $(u, v) \in V^2$  we have  $0 \le f(u, v) \le c(u, v)$ .

- 2. For each vertex  $u \in V \setminus \{s,t\}$  we have  $\sum_{v \in V} f(v,u) = \sum_{v \in V} f(u,v)$ .

We define |f| as the value  $\sum_{v \in V} f(s, v)$ . A maximal flow of F is a flow f with maximal |f|. A cut C of the flow network F is a pair (S,T), s.t., S and T form a partition of V with  $s \in S$  and  $t \in T$ . The capacity c(S,T) of a cut (S,T) is given by the value  $\sum_{u \in S} \sum_{v \in T} c(u, v)$ . A minimum cut is a cut with the smallest possible capacity. The net Flow f(S,T) of a cut (S,T) is given by the value  $\sum_{u\in S}\sum_{v\in T}f(u,v)-\sum_{u\in S}\sum_{v\in T}f(v,u)$ . The residual capacity  $c_f$  of a flow f is a function  $c_f:V^2\to\mathbb{R}_{\geq 0}$  that is defined as follows. For edges  $e = (v_1, v_2)$  we have  $c_f(v_1, v_2) = f(e) - c(e)$  and  $c_f(v_2, v_1) = f(e)$ . For all other pairs of vertices  $c_f$  is defined as 0. The residual graph  $G_f$  for a flow f is a graph with vertices V(G) and edges defined as follows: Let  $v_1, v_2 \in V(G)$  then  $G_f$  contains the edge  $(v_1, v_2)$  if  $c_f(v_1, v_2) > 0$ .

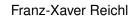

### 2.1.3 **Decision Trees**

Throughout this thesis we will only consider decision trees for classifying binary features with binary classes. Thus, we will only introduce a simplified version of decision trees.

The set of features F is defined as  $F = \mathbb{B}^n$  for some  $n \in \mathbb{N}$ . A decision tree for F is a rooted binary tree T with root  $T_r$ . Every leaf vertex  $\ell$  in T is labeled by a boolean value For a non-leaf vertex v we denote its left child by left(v) and its right child by right(v).

A decision tree T for  $\mathbb{B}^n$  represents a Boolean function  $f_T: \mathbb{B}^n \to \mathbb{B}$ . For defining  $f_T$ , we first introduce a function  $f':V(T)\times\mathbb{B}^n\to\mathbb{B}$ . In the following let  $b\in\mathbb{B}^n$ . For a non-leaf v we define

$$f'(v,b) = \begin{cases} f'(left(v),b), & \text{if } b_{feature(v)} = 0\\ f'(right(v),b), & \text{otherwise} \end{cases}.$$

For a leaf node  $\ell$  we define  $f'(\ell, b)$  as  $class(\ell)$ . Finally, f(b) is defined as  $f'(T_r, b)$ .

**Decision Tree Learning** Classical decision tree learning procedures like ID3 [Qui86] or C4.5 [Qui93] induce a decision tree given a set of samples (i.e., realizations of the features) which are labeled with a class. For the application of decision trees which we will consider later, samples are not given a priori, but incrementally generated. Because of that, we consider *Hoeffding trees* [DH00]. *Hoeffding trees* are incrementally induced decision trees. Starting from a single root node, the leaves of the tree are periodically checked for splits. For this purpose, new samples are first sorted into one of the leaves of the tree. To represent the encountered samples, each leaf is equipped with counters for each realization of each feature and each possible class. The leaves are then labeled with the class of the majority of the samples. As soon as sufficiently many samples—a value  $n_{min}$  that is set as a parameter of the tree—were sorted into a leaf, the leaf is checked for a split. In this case the best two features for a split are selected based on a heuristic like information gain. If the heuristic evaluation function does not sufficiently differ between these features no split is introduced and the node is checked again as soon as  $n_{min}$  new samples arrived. Otherwise, the node is split with respect to the optimal feature computed before. In the new leaves the counters are initialized by 0, which means that old samples do not need to be remembered. It was shown that Hoeffding trees can be asymptotically arbitrarily close to a decision tree learned by traditional batch learning [DH00].

### Propositional Logic 2.1.4

In this section, we will summarize notations and concepts for propositional logic, and the propositional satisfiability problem (SAT). For a comprehensive overview of SAT, including solving techniques, complexity results and applications, we refer to the Handbook of Satisfiability [Bie+21].

A literal is either a propositional variable or its negation. Given a literal  $\ell$ , we denote the variable in  $\ell$  by  $var(\ell)$ . A clause is a disjunction of literals and a term a conjunction of literals. A formula in *conjunctive normal form* (CNF) is a disjunction of clauses. We identify formulas in CNF by sets of clauses and both clauses and terms with sets of

literals. Let C be a clause and  $\varphi$  a CNF. We define the set var(C) of variables in C as  $\{var(\ell) \mid \ell \in C\}$  and the set  $var(\varphi)$  of variables in  $\varphi$  as  $\bigcup_{C \in \varphi} var(C)$ .

We denote the set  $\{0,1\}$  of boolean values by  $\mathbb{B}$ . An assignment  $\sigma$  of a set of variables Vis a function  $V \to \mathbb{B}$ . We denote the domain of an assignment  $\sigma$  by  $\mathbf{dom}(\sigma)$ . The set of all assignments of V is denoted by  $\mathbb{B}^V$ . Let  $\sigma$  be an assignment of V then for a set of variables W with  $W \subseteq V$ , we define the restriction of  $\sigma$  to W as the function  $\sigma|_{W}$  that is defined by  $\sigma|_{W}(x) = \sigma(x)$  for each x in W. Moreover, for two disjoint sets of variables V and W and assignments  $\sigma_1$  of V and  $\sigma_2$  of W, we define the union of  $\sigma_1$  and  $\sigma_2$  as  $\sigma_1 \cup \sigma_2 : V \cup W \to \mathbb{B}$  such that  $\sigma_1 \cup \sigma_2(x) = \sigma_1(x)$  for  $x \in V$ , and  $\sigma_1 \cup \sigma_2(x) = \sigma_2(x)$ for  $x \in W$ . An assignment  $\sigma$  can be extended to literals by setting  $\sigma(\neg v) = 1 - \sigma(v)$ . We define the instantiation  $C[\sigma]$  of a clause C by an assignment  $\sigma$  as follows. If there is a literal  $\ell \in C$  such that  $var(\ell) \in \mathbf{dom}(\sigma)$  and  $\sigma(\ell) = 1$  then  $C[\sigma] = \top$ . Otherwise,  $C[\sigma] = \{\ell \in C \mid var(\ell) \notin \mathbf{dom}(\sigma)\}$ . We say that  $\sigma$  satisfies C if  $C[\sigma] = \top$ , and we say that  $\sigma$  falsifies C if  $C[\sigma] = \emptyset$ . Similarly, we can define instantiations of terms. We define the instantiation  $\varphi[\sigma]$  of a CNF  $\varphi$  by an assignment  $\sigma$  as follows. If every clause  $C \in \varphi$ is satisfied by  $\sigma$  then  $\varphi[\sigma] = \top$ . Otherwise,  $\varphi[\sigma] = \{C[\sigma] \mid C \in \varphi, C[\sigma] \neq \top\}$ . We say that  $\varphi$  is satisfied by  $\sigma$  if  $\varphi[\sigma] = \top$ , and we say that  $\varphi$  is falsified by  $\sigma$  if  $\sigma$  falsifies a clause in  $\varphi$ . A CNF  $\varphi$  is satisfiable if there is an assignment that satisfies  $\varphi$ , and it is unsatisfiable if there is no satisfying assignment. Whenever convenient, we identify an assignment  $\sigma$  of a set X with the term  $\{x \mid x \in X, \sigma(x) = 1\} \cup \{\neg x \mid x \in X, \sigma(x) = 0\}.$ In particular, for an assignment  $\sigma$  we identify  $\neg \sigma$  with the clause that is the result of negating the associated term.

While satisfiability of a CNF is witnessed by a satisfying assignment, we can use propositional resolution to show unsatisfiability. Resolution is a refutational proof system that allows to derive a sequence of clauses  $C_1, \ldots, C_n$  from a CNF  $\varphi$ . For each  $i \in [n]$  the clause  $C_i$  is either a clause from  $\varphi$  or it is derived by the resolution rule, which is shown below.

$$\frac{C_1 \cup \{v\} \qquad C_2 \cup \{\neg v\}}{C_1 \cup C_2}$$

(resolution)

If we can derive a sequence of clauses  $C_1, \ldots, C_n$  from  $\varphi$ , we say that  $C_n$  is derivable from  $\varphi$ . If the empty clause  $\perp$  can be derived from  $\varphi$ , we call the derivation a refutation. The resolution proof system is sound and refutationally complete. This means there is a refutation of a CNF  $\varphi$  if and only if  $\varphi$  is unsatisfiable.

### 2.2Propositional Definitions

In this section, we recall basic definitions/notations for propositional definitions. We stick to the notation used by Slivovsky [Sli20].

**Definition 2.1.** Let  $\varphi$  be a propositional formula,  $X \subseteq var(\varphi)$  a set of variables and  $x \in var(\varphi)$ . Then x is implicitly defined in  $\varphi$  by X if  $\sigma(x) = \tau(x)$  for any satisfying

assignments  $\sigma$  and  $\tau$  of  $\varphi$  with  $\sigma|_X = \tau|_X$ . A definition for x in  $\varphi$  by X is a formula  $\psi$ with  $var(\psi) \subseteq X$  such that  $\psi[\sigma] = \sigma(x)$  holds for every satisfying assignment  $\sigma$  of  $\varphi$ . If there is a definition  $\psi$  for x in  $\varphi$  by X then x is explicitly defined in  $\varphi$  by X.

**Remark 2.1.** We can see that for any satisfying assignment  $\sigma$  of  $\varphi$  and any definitions  $\psi_1$  and  $\psi_2$  for a variable v in  $\varphi$  by X we have  $\psi_1[\sigma] = \psi_2[\sigma]$ . Conversely, for a falsifying assignment  $\sigma$ , we can have  $\psi_1[\sigma] \neq \psi_2[\sigma]$ . This in particular means that definitions are not uniquely determined.

For propositional logic it can be shown that implicit and explicit definability coincide.

**Theorem 2.1** (Propositional version of Beth's theorem). Let  $\varphi$  be a propositional formula,  $X \subseteq var(\varphi)$  a set of variables and  $x \in var(\varphi)$ . Then x is explicitly defined in  $\varphi$  by X iff it is implicitly defined in  $\varphi$  by X.

For a proof of this theorem we refer to [LM08]. Thus, we just say that a variable x is defined in  $\varphi$  by X if it is implicitly defined. Given a formula  $\varphi$  and a variable  $v \in var(\varphi)$ , let v' denote some new variable. We now define the formula  $\varphi'_X$  as the formula which is obtained by replacing each  $v \in var(\varphi) \setminus X$  by v'. To check whether a variable is defined we can use the following theorem.

**Theorem 2.2** (Padoa's method). Let  $\varphi$  be a formula,  $x \in var(\varphi)$  and  $X \subseteq var(\varphi)$  s.t.  $x \notin X$ . Then x is defined in  $\varphi$  by X iff for each satisfying assignment  $\sigma$  of  $\varphi \wedge \varphi'_X$  the assignment  $\sigma$  also satisfies  $\neg x \lor x'$ .

For a proof of this theorem we again refer to [LM08]. As an immediate corollary we get the following.

Corollary 2.1. Let  $\varphi$  be a formula,  $x \in var(\varphi)$  and  $X \subseteq var(\varphi)$  s.t.  $x \notin X$ . Then x is defined in  $\varphi$  by X iff  $\varphi \wedge x \wedge \varphi'_X \wedge \neg x'$  is unsatisfiable.

In order to compute definitions, we first need to recall the definition of an interpolant. We follow the notation by Slivovsky [Sli20].

**Definition 2.2.** Let  $\varphi$  and  $\psi$  be two propositional formulas s.t.  $\varphi \wedge \psi$  is unsatisfiable. Then an interpolant I for  $\varphi$  and  $\psi$  is formula with the following properties:

- $\varphi$  implies I, i.e.,  $\varphi \wedge \neg I$  is unsatisfiable.

- $I \wedge \psi$  is unsatisfiable

- $var(I) \subseteq var(\varphi) \cap var(\psi)$

Slivovsky proved the subsequent theorem that allows to obtain definitions from interpolants [Sli20].

**Theorem 2.3.** Let  $\varphi$  be a propositional formula and  $X \subseteq var(\varphi)$  a set of variables. A variable  $x \in var(\varphi) \setminus X$  is defined by X in  $\varphi$  iff  $\varphi \wedge x \wedge \varphi'_X \wedge \neg x'$  is unsatisfiable, and every interpolant of  $\varphi \wedge x$  and  $\varphi'_X \wedge \neg x'$  is a definition for x in  $\varphi$  by X.

An approach for computing interpolants from resolution refutations is given in [McM03]. To compute interpolants in practice, an interpolating version of MINISAT [ES03] bundled with the Extavy model checker [GV14; VGM15] can be used.

### 2.3DQBF

Dependency Quantified Boolean Formulas (DQBF) combine QBF with the idea of Henkin quantifiers, which were introduced for first-order logic [Hen61]. Thus, DQBF extend QBF by allowing to explicitly state dependencies for existential (universal) variables. This is in contrast to QBF, where dependencies of a variable are implicitly determined by the syntactic order of quantifiers. DQBF were first described by Peterson and Reif [PR79].

**Syntax** We only consider closed DQBF in prenex conjunctive normal form (PCNF). That is, each DQBF  $\Phi$  has the shape  $Q.\varphi$ , where  $\varphi$  denotes the matrix of  $\Phi$  and Q the prefix of  $\Phi$ . The matrix  $\varphi$  is a propositional formula in CNF that only consists of variables contained in the prefix. The prefix has the shape  $Q = \forall u_1, \dots, u_n \exists e_1(D_1), \dots, e_m(D_m)$ . We refer to the variables  $U = \{u_1, \dots, u_n\}$  as the universal variables of  $\Phi$  ( $var_{\forall}(\Phi)$ ) and to the variables  $E = \{e_1, \dots, e_m\}$  as the existential variables of  $\Phi$  ( $var_{\exists}(\Phi)$ ). For each  $i \in [m]$  we require that  $D_i \subseteq U$ . We call the set  $D_i$  the dependencies of  $e_i$   $(D_{\Phi}(e))$ . If the DQBF is clear from the context we will just use D(e). A Quantified Boolean Formula (QBF) can be considered as a special form of DQBF, where existential variables can be linearly ordered according to their dependencies. This means for a QBF  $\Phi$  there is a linear ordering  $\leq_{\exists}$  on  $var_{\exists}(\Phi)$  such that for every existential variables x and y with  $x \leq y$ , we have  $D(x) \subseteq D(y)$ .

DQBF of the above shape are also said to be in S-Form [BCJ14a]. An alternative form are DQBF in H-Form [BCJ14a]. These formulas extend Henkin quantifiers by allowing to explicitly state dependencies of universal variables in terms of existential variables. Thus, the prefix of a DQBF in H-Form has the shape  $Q = \exists e_1 \dots, e_n \forall u_1(D_1), \dots, u_m(D_m)$ . As in the case of formulas in S-Form, the prefix contains a set of existential variables E and a set of universal variables U, but for each  $i \in [m]$  we require  $D_i \subseteq E$ . Throughout this thesis we will only consider DQBF in S-Form.

**Semantics** Let  $\Phi = \mathcal{Q}.\varphi$  be a DQBF and let  $e \in var_{\exists}(\Phi)$ . We call a function  $f_e: \mathbb{B}^{D(e)} \to \mathbb{B}$  a Skolem function for e. Let  $f = (f_e)_{e \in var_{\exists}(\Phi)}$  be a family of Skolem functions. For a universal assignment  $\sigma$ , we define the existential assignment  $f(\sigma)$  by  $f(\sigma)(e) = f_e(\sigma|_{D(e)})$ . We will refer to the assignment  $f(\sigma)$  as the response of f to  $\sigma$ . The family f is a model if for each universal assignment  $\sigma$  the assignment  $\sigma \cup f(\sigma)$  satisfies

the matrix  $\varphi$ . A DQBF is said to be satisfiable or true if it has a model. And it is said to be *unsatisfiable* or *false* if it does not.

Deciding DQBF was shown to be NEXPTIME-complete [PR79; PAR01]. Recently, it was shown that even deciding 3-DQBF<sup>1</sup> is NEXPTIME-complete [FT23]. Since, deciding QBF is PSPACE-complete [SM73], deciding DQBF is harder than deciding QBF—assuming that NEXPTIME is not contained in PSPACE. Recently some tractable subclasses of DQBF have been identified [Sch+19; Gan+20].

**Decision Procedures** Let P be a procedure that takes a DQBF as input and returns satisfiable or unsatisfiable. If the procedure P always terminates and yields satisfiable if and only if the given DQBF is satisfiable then P is decision procedure for DQBF.

**Dependency Schemes** Dependency schemes allow to remove spurious dependencies from a DQBF. We follow the definition of dependency schemes used in [BBP20]. For this purpose, we first introduce a relation  $\leq_{\mathcal{Q}}$  as follows. Let  $\Phi$  and  $\Phi'$  be two DQBF with the same matrix. Then we have  $\Phi \leq_{\mathcal{Q}} \Phi'$  if  $var_{\exists}(\Phi) = var_{\exists}(\Phi')$  and for each  $e \in var_{\exists}(\Phi)$ we have  $D_{\Phi}(e) \subseteq D_{\Phi'}(e)$ . We can now define dependency schemes as follows:

**Definition 2.3.** A dependency scheme is a polynomial-time computable function  $\mathcal{D}$  that maps DQBF to DQBF s.t.  $\mathcal{D}(\Phi) \leq_{\mathcal{Q}} \Phi$  for each formula  $\Phi$ .

A dependency scheme  $\mathcal{D}$  is said to be fully exhibited if  $\Phi$  is satisfiable if and only if  $\mathcal{D}(\Phi)$ is satisfiable.

In this thesis we will only consider the reflexive resolution path dependency scheme  $\mathcal{D}^{RRS}$ .  $\mathcal{D}^{RRS}$  was first introduced for QBF [SS16]. We follow the definition of  $\mathcal{D}^{RRS}$  in [BBP20].

**Definition 2.4.** Let  $\Phi = \mathcal{Q}.\varphi$  be a DQBF. Then the reflexive resolution path dependency scheme  $\mathcal{D}^{RRS}(\Phi)$  is defined as the DQBF  $\Phi' = \mathcal{Q}'.\varphi$ , whose prefix is defined as follows. The prefix Q' contains the same existential and universal variables as Q. Moreover, for each existential variable e the set  $D_{\Phi'}(e)$  is defined as the subset of  $D_{\Phi}(e)$  s.t. for each  $u \in D_{\Phi'}(e)$  there must be a sequence of clause  $C_1, \ldots, C_k$  in the matrix  $\varphi$  and a sequence of existential literals  $\ell_1, \dots, \ell_{k-1}$  that satisfy the following conditions:

- $u \in C_1$  and  $\neg u \in C_k$

- for some  $j \in [k-1]$  we have  $var(\ell_i) = e$

- for each  $j \in [k-1]$  we have  $\ell_i \in C_i, \neg \ell_i \in C_{i+1}$  and  $u \in D(var(\ell_i))$

- for each  $j \in [k-2]$  we have  $var(\ell_i) \neq var(\ell_{i+1})$

$<sup>^{1}</sup>$ A k-DQBF is a DQBF with k existentially quantified variables.

### 2.4**Proof Systems for DQBF**

While a model shows that a DQBF is satisfiable, unsatisfiability can be shown by applying proof systems. Different proof systems for DQBF have been proposed. These in particular include QBF proof systems that have been lifted to DQBF, like DQBF-Q-Res [KKF95; BCJ14a], DQBF-QU-Res [Gel12; Bey+19], DQBF- $\forall Exp$ +Res [JM13; Bey+19] and DQBF-IR-calc [BCJ14b; Bey+19]. Throughout this thesis, we will only consider the DQBF variants of the proof systems, thus we will omit the DQBF prefix when referring to the proof systems. All of these proof systems are refutational clausal proof systems. This means that the proof systems consist of sets of rules that allow to derive a sequence of clauses  $C_1, \ldots, C_n$ . We call such a sequence of clauses a P-derivation of  $C_n$ , where P denotes the respective proof system. In these derivations each clause can be derived from previously derived clauses, or from the DQBF itself. A derivation of the empty clause  $\perp$  is called a *refutation*. All proof systems mentioned above are sound, but only  $\forall \text{Exp+Res}$  and IR-calc are refutationally complete [BCJ14a; Bey+19]. In this thesis, we will only consider the expansion based proof systems  $\forall \text{Exp+Res}$  and IR-calc. Next we will describe  $\forall \text{Exp+Res}$  and then IR-calc.

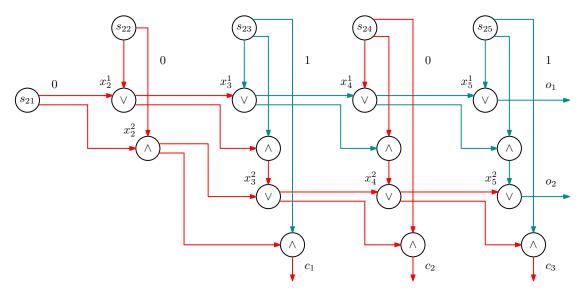

The intuition behind expansion-based proof systems is that we can transform a (D)QBF to an equisatisfiable propositional formula by instantiating each universal variable both by 0 and 1 and by conjoining the resulting formulas. This procedure is called expansion. Unsatisfiability of the original QBF/DQBF can then be shown by resolution on the expanded formula. For the expansion it is necessary that existential variables are replaced by new variables for each assignment to its dependencies. Consider the following DQBF:

$$\forall u_1, u_2 \exists e_1(u_1), e_2(u_2).(e_1 \lor u_1) \land (e_2 \lor u_2) \land (u_1 \lor \neg e_1 \lor \neg e_2).$$

Expansion yields the following propositional formula:

$$e_1^{\neg u_1} \wedge e_2^{\neg u_2} \wedge \left(\neg e_1^{\neg u_1} \vee \neg e_2^{u_2}\right) \wedge \left(\neg e_1^{\neg u_1} \vee \neg e_2^{\neg u_2}\right)$$

We annotate existential variables with assignments of their dependencies to distinguish variables for different assignments. By applying propositional resolution, one can now easily verify that this propositional formula is unsatisfiable. Thus, also the initial (D)QBF is unsatisfiable.

The above example also shows that not all clauses from the expansion are necessary for the propositional resolution step (e.g.,  $(\neg e_1^{\neg u_1} \lor \neg e_2^{u_2})$  is not part of the refutation). Instead of expanding all clauses of the matrix and using these clauses for propositional

14

$$\frac{1}{\{\ell^{\sigma|_{D(var(\ell))}} \mid \ell \in C, var(\ell) \in var_{\exists}(\Phi)\}}$$

(axiom)

The axiom rule allows to derive a new clause from  $\Phi$ . Here  $\sigma$  denotes a total assignment of the universal variables that falsifies each universal literal in a clause C from the matrix. For a variable  $x^{\tau}$  we call  $\tau$  the annotation of x. Note that variables with different annotations denote different variables.

$$\frac{C_1 \cup \{e^{\tau}\} \qquad C_2 \cup \{\neg e^{\tau}\}}{C_1 \cup C_2}$$

(resolution)

The resolution rule applies propositional resolution to derive a new clause from the clauses  $C_1 \cup \{e^{\tau}\}$  and  $C_2 \cup \{\neg e^{\tau}\}$ . The clauses only consist of annotated existential literals. This in particular means that e is an existential variable and  $\tau$  an assignment for D(e).

Figure 2.1: The rules of  $\forall \text{Exp+Res}$ , where  $\Phi$  is the given DQBF.

resolution, we can consider  $\forall \text{Exp+Res}$  proof system. The rules for  $\forall \text{Exp+Res}$  are given in Figure 2.1. The proof system allows to expand any clause C from the matrix with a total assignment of the universal variables that falsifies each universal literal in C. The resulting clauses can then be used for propositional resolution. Here it is important, that variables with different annotations are considered as different variables. Thus, resolution can only be applied if the annotations match. As mentioned above,  $\forall \text{Exp+Res}$  is sound and refutationally complete, i.e., the empty clause  $\perp$  can be derived if and only if the given DQBF is unsatisfiable [Bey+19].

In the  $\forall \text{Exp+Res}$  system, we always have to instantiate with total assignments. Even for clauses with few universal literals, total assignments for the universal variables must be used. By weakening this constraint to partial assignments, we obtain the IR-calc proof system. The rules for IR-calc are given in Figure 2.2. In IR-calc, we can instantiate clauses with the smallest possible universal assignment that falsifies all universal literals. We can then extend the annotations of the existential literals in case this is necessary for a resolution step. Like  $\forall \text{Exp+Res}$ , IR-calc is sound and refutationally complete [Bey+19].

We say that a proof system  $P_1$  p-simulates a proof system  $P_2$  if every  $P_1$  proof of some formula  $\varphi$  can be converted to a  $P_2$  proof of  $\varphi$  by a polynomial time procedure. Additionally, a family  $\mathcal{F}$  of (DQBF) PCNFs separates  $P_1$  from  $P_2$  if  $\mathcal{F}$  has polynomial size refutations in  $P_1$  but not in  $P_2$  [BB20; CR79]. It is easy to see that IR-calc p-simulates  $\forall \text{Exp+Res.}$  It was shown that there is a family of QBF PCNFs  $\mathcal{F}$  that separates IR-calc from ∀Exp+Res [JM15; BB20]. As DQBF-IR-calc, respectively DQBF-∀Exp+Res extend their QBF variants, the separation for QBF is carried over to DQBF. This means that IR-calc can be considered as stronger than  $\forall \text{Exp+Res}$ .

$$\frac{1}{\{\ell^{\sigma|_{D(var(\ell))}} \mid \ell \in C, var(\ell) \in var_{\exists}(\Phi)\}}$$

(axiom)

The axiom is similar to the same named rule in  $\forall \text{Exp+Res}$ . The major difference is that here  $\sigma$  denotes a partial assignment of the universal variables that falsifies each universal literal in a clause C from the matrix.

$$\frac{C}{\{l^{\tau \circ \sigma|_{D(var(l))}} \mid l^{\tau} \in C\}}$$

(instantiation)

The instantiation rule allows to specialize the annotations in a clause C by some universal assignment  $\sigma$

$$\frac{C_1 \cup \{e^{\tau}\} \qquad C_2 \cup \{\neg e^{\tau}\}}{C_1 \cup C_2} \text{ (resolution)}$$

Similarly as  $\forall \text{Exp+Res}$  also IR-calc uses the propositional resolution rule. The difference is that now annotations are not necessarily total.

Figure 2.2: The rules of IR-calc.

### 2.5 Solving DQBF

Several decision procedures for DQBF have been developed in recent years. In contrast to SAT, where CDCL-based solvers play a dominant role [MLM21], there is a larger variety of different solving approaches for DQBF. We give a brief overview of some existing solving techniques for DQBF. For a more detailed discussion of DQBF solving methods, we refer to the surveys by Scholl and Kovásznai [Kov16; SW18].

• One approach to solving DQBF is realized in the DQDPLL procedure. DQDPLL lifts the DPLL procedure for SAT and for QBF to DQBF. As DPLL assigns variables one after another, it entails a linear ordering of variables, whereas in a DQBF there is generally no linear ordering of variables with respect to their dependencies. As a consequence, DPLL needs to be equipped with additional constraints: it can be necessary to enforce the same assignment for an existential variable for different paths in the assignment tree [FKB12]. A solving technique related to DQDPLL is implemented in the solver DCAQE. DCAQE lifts the idea of clausal abstraction from QBF to DQBF. The core idea is that each existential (universal) variable is associated with a propositional formula that indicates which clauses can be satisfied (falsified) by assigning this variable. The solver uses these formulas to construct an assignment step by step, where the order is determined by the dependencies. In this process the formulas associated with each variable are used to obtain assignments for

the variables. If there is no suitable assignment—every assignment to an existential variable falsifies the matrix, respectively every assignment to a universal variable satisfies the matrix—the associated formula gives a reason. This reason can then be used to jump back to a previously considered variable and to modify its associated formula [RT15; TR19].

- Another approach is to reduce DQBF either to SAT or QBF. The solver IDQ instantiates each clause C with a partial universal assignment that falsifies every universal literal in C. Existential literals for different instantiations are considered as different. Thus, if the resulting propositional formula is unsatisfiable, then also the initial DQBF is unsatisfiable. On the other hand, if the propositional formula is satisfiable, then the initial DQBF is not necessarily satisfiable, as some existential variables might not be assigned consistently. In that case additional clauses that further constrain the formula might need to be added [Frö+14].

- While IDQ reduces DQBF to SAT, the solver HQS reduces DQBF to QBF. The basic idea of HQS is to eliminate universal variables by expanding them to obtain a QBF. In order to reduce the number of introduced additional existential variables, this approach is refined by only removing universal variables from individual dependency sets. These variables are selected such that a smallest possible number of eliminations suffices to obtain a QBF [Git+15; Wim+17; GSW19]. HQS is a competitive DQBF solver that won the DQBF track of the QBF Evaluation in the years 2018 and 2019 [PSS24]. The solver DQBDD builds on the ideas used in HQS. DQBDD constructs a Binary Decision Diagram (BDD) for a given DQBF. To do this, quantifiers are pushed into the matrix. Then, a BDD is constructed by expanding both universal and existential quantifiers [Síč20; SS21b]. DQBDD is a competitive solver that won the DQBF track of the QBF Evaluation in 2020 [PSS24].

- Besides the solvers presented above, DQBF can also be solved by a translation to Effectively Propositional Logic (EPR). The satisfiability problem for EPR is NEXPTIME-complete [Lew80]. Thus, there is a polynomial reduction from DQBF to EPR. After translating a DQBF to EPR, the solver IPROVER [Kor08] can be applied, for instance.

- Last but not least, we also want to mention Manthan a tool for synthesizing Skolem Functions. Manthan first computes satisfying assignments of the matrix. Then it applies decision tree learning to obtain initial candidate Skolem functions for each existential variable, from the sampled satisfying assignments. These candidates are then iteratively refined. While MANTHAN is incomplete, it could still solve some formulas that could not be handled by any other state of the art DQBF solver [GRM20; Gol+21; GRM23].

### Applications of DQBF 2.6

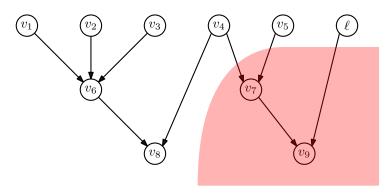

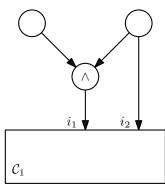

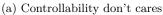

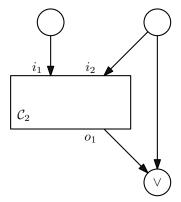

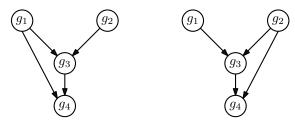

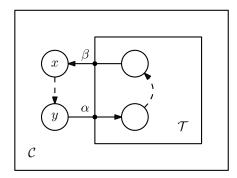

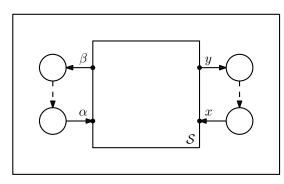

While DQBF is not as widely used to solve (practical) problems as SAT or QBF, several interesting applications were developed in recent years. One of these is Partial Equivalence Checking (PEC) [Git+13b; Git+13a]. In PEC, circuits that contain unspecified parts (black boxes) are considered. For these parts we only know the inputs and the outputs, but not the implementation. The goal of PEC is to decide whether there is some implementation of the black boxes such that the resulting circuit satisfies a given specification. Gitina et al. [Git+13b] showed that PEC can be encoded as DQBF. The core idea of the encoding is to represent the outputs of the black boxes by existentially quantified variables that only depend on variables representing the inputs of the unspecified part.

Several other applications of DQBF have been proposed. DQBF can be considered to encode the existential quantification of Boolean functions [Rab17]. Here, the task is that a formula containing applications of an unspecified function is given. We want to check whether there is some Boolean function that satisfies the given formula. The core idea of the DQBF encoding is to represent applications of the function by existentially quantified variables with disjoint dependency sets. DQBF have also been used for Reactive Synthesis [Fay+17]. Here, a system specification is given in temporal logic. The goal is to find a transition system that satisfies the given specification. Additionally, Chen et al. [Che+22] discussed the reduction of further NEXPTIME-complete problems to DQBF. These reductions include the problem of succinct graph 3-colorability or the problem of checking the existence of Hamiltonian cycles.

Moreover, DQBF solvers could be used as backend solvers for other logics in NEXPTIME. This includes the already mentioned logic EPR [Lew80], but also certain bit-vector logics for satisfiability modulo theories (SMT) [KFB16].

# A Two-Phase Algorithm

In this section, we will introduce a fairly simple algorithm for deciding DQBF. The primary purpose of this algorithm is to introduce basic concepts for the main algorithm which we will introduce in the next chapter. The description given in this chapter is based on our paper [RSS21].

The algorithm is presented in Algorithm 1. First we will discuss the algorithm step by step. Then we will show that Algorithm 1 is a decision procedure for DQBF.

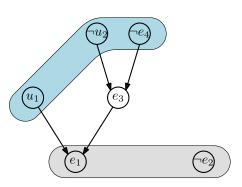

**Description of the algorithm** The main idea of Algorithm 1 is to compute a Skolem function for each existential variable. To obtain the Skolem functions, propositional definitions are computed. The algorithm then checks whether the Skolem functions describe a model.

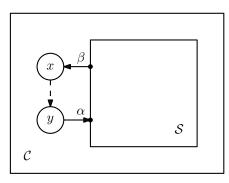

To realize this idea the algorithm proceeds in two phases. In the first phase (GENERATE-DEFINITIONS), it computes a definition  $\gamma_e$  for each existential variable e. In general, not every existential variable e has a definition by D(e). To still obtain definitions the algorithm introduces a set A of auxiliary arbiter variables whose semantics are encoded in a set  $\psi_A$  of arbiter clauses, both of which are empty initially.

For each existential variable e, we now first use Theorem 2.3 to check definability of e(line 7)—we assume that a procedure SAT, which checks satisfiability of a propositional formula, is given. If a variable e is not defined then there must be an assignment  $\sigma$ for D(e) such that the assignment of e is not fixed under  $\sigma$ . This means that there are satisfying assignments  $\rho_1$  and  $\rho_2$  of the matrix  $\varphi$  with  $\rho_1|_{D(e)} = \rho_2|_{D(e)} = \sigma$  and  $\rho_1(e) \neq \rho_2(e)$ . We can obtain such an assignment  $\sigma$  by considering the condition from Theorem 2.3 (line 8)—we assume that a procedure GETMODEL, which computes a satisfying assignment for a satisfiable propositional formula, is given. Next, we fix the assignment for e under  $\sigma$ . For this purpose, we introduce an arbiter variable  $e^{\sigma}$ . The aim of this new variable is to determine the value of the Skolem function for e under

```

Algorithm 1 Solving DQBF by definition extraction.

1: procedure TWOPHASE(\Phi)

\psi_D, \psi_A \leftarrow \text{GENERATEDEFINITIONS}(\Phi)

2:

return FINDARBITERASSIGNMENT(\Phi, \psi_D, \psi_A)

3:

4: procedure GENERATE DEFINITIONS(\Phi)

\psi_D \leftarrow \emptyset, \ \psi_A \leftarrow \emptyset, \ A \leftarrow \emptyset

5:

for each e \in var_{\exists}(\Phi) do

6:

7:

while not isDefined(e, \varphi \land \psi_A, D(e) \cup A) do

\sigma = \text{GETUNDEFINEDREASON}(e, \varphi \land \psi_A, D(e) \cup A)|_{D(e)}

8:

A \leftarrow A \cup \{e^{\sigma}\}

9:

\psi_A \leftarrow \psi_A \land (e^{\sigma} \lor \neg \sigma \lor \neg e) \land (\neg e^{\sigma} \lor \neg \sigma \lor e)

10:

\gamma_e \leftarrow \text{GETDEFINITION}(e, \varphi \land \psi_A, D(e) \cup A)

11:

\psi_D \leftarrow \psi_D \wedge (e \leftrightarrow \gamma_e)

12:

return \psi_D, \psi_A

13:

14: procedure FINDARBITERASSIGNMENT(\Phi, \psi_D, \psi_A)

\tau \leftarrow \bigwedge_{a \in A} a, \ blockingClauses \leftarrow \emptyset

15:

loop

16:

17:

if ISSAT(\neg \varphi \land \psi_D \land \tau) then

\sigma \leftarrow \text{GETMODEL}(\neg \varphi \wedge \psi_D \wedge \tau)|_{var_{\forall}(\Phi)}

18:

\tau' \leftarrow \text{GETCORE}(\varphi \wedge \psi_A \wedge \sigma, \tau)|_A

19:

blockingClauses \leftarrow blockingClauses \land \neg \tau'

20:

\mathbf{if}\ {\tt ISSAT}(blockingClauses)\ \mathbf{then}

21:

\tau \leftarrow \text{GETMODEL}(blockingClauses)

22:

else

23:

24:

return unsatisfiable

25:

else

26:

return Satisfiable

27: procedure ISDEFINED(v, \delta, X)

return \neg ISSAT(\delta \wedge v \wedge \delta'_X \wedge \neg v')

28:

29: procedure GETUNDEFINEDREASON(v, \delta, X)

return GETMODEL(\delta \wedge v \wedge \delta'_X \wedge \neg v')

30:

```

32:

31: **procedure** GETDEFINITION $(v, \delta, X)$

return GetInterpolant $(\delta \wedge v, \delta'_X \wedge \neg v')$

$\sigma$ . This means that e shall be assigned to true under  $\sigma$  iff  $e^{\sigma}$  is assigned to true. In subsequent iterations, we include these arbiter variables in the set of variables that can be used in a definition of e. To enforce the correspondence of the assignments of e and  $e^{\sigma}$ we also add the clauses  $e^{\sigma} \vee \neg \sigma \vee \neg e$  and  $\neg e^{\sigma} \vee \neg \sigma \vee e$  to subsequent definability checks. If there are multiple assignments  $\sigma$  of D(e) for which the assignment of e is not fixed, we introduce arbiter variables for all of them. When the inner loop terminates, we know that e is defined by  $D(e) \cup A$  in  $\varphi \wedge \psi_A$ . We can thus obtain a definition by computing an interpolant (line 11)—for this purpose we assume that a procedure GETINTERPOLANT is given. The definition is then added to the formula  $\psi_D$  that contains the definitions for every existential variable.

In the second phase (FINDARBITERASSIGNMENT) we then want to find an assignment of the arbiter variables under which the definitions obtained in the first phase are a model. Starting with an initial assignment  $\tau^1$ , we use a SAT solver to check whether the formula  $\neg \varphi \wedge \psi_D$  consisting of the negated matrix of the input DQBF and the definitions from the first phase is satisfiable under  $\tau$  (line 17). If the formula is unsatisfiable then there is no universal assignment  $\sigma$  that can falsify  $\varphi$  under  $\tau$  and  $\psi_D$ . Thus,  $\tau$  and  $\psi_D$  describe a model for  $\Phi$  and so the algorithm returns SATISFIABLE. If, on the other hand, the formula is satisfiable, then the matrix can be falsified by some universal assignment  $\sigma$ under  $\tau$  and  $\psi_D$ . This in particular means that  $\varphi \wedge \psi_A$  must be unsatisfiable under  $\tau$ and  $\sigma$ —if the formula would be satisfiable the assignments of the existential variables would need to adhere to the definitions in  $\psi_D$ , but we know that  $\varphi$  is falsified under  $\sigma$ ,  $\tau$  and  $\psi_D$ . Thus, we can compute a sub-assignment  $\tau'$  for  $\tau$  such that  $\varphi \wedge \psi_A \wedge \sigma$ remains unsatisfiable under  $\tau'$ . But this means that for every arbiter assignment that contains  $\tau'$ , we can falsify the matrix. For this reason arbiter assignments used in subsequent iterations must differ from  $\tau'$ . This is realized by adding the clause  $\neg \tau'$  to a set of blocking clauses that is empty initially. A new assignment  $\tau$  for the arbiter variables is obtained by a satisfying assignment for the blocking clauses. If the set of blocking clauses is unsatisfiable, we cannot find a new assignment for the arbiters that differs from all previous assignments  $\tau'$ . Thus, for every arbiter assignment  $\tau$  the matrix  $\varphi$  is falsified under  $\psi_D \wedge \tau$  for some assignment to the universals  $\sigma$ . So there cannot be a model and the DQBF is unsatisfiable.

**Proofs** Next we will show that Algorithm 1 is a decision procedure for DQBF. For this purpose, we will first show that the algorithm always terminates. Then, we show that if the algorithm reports satisfiability of a DQBF  $\Phi$  then  $\Phi$  is satisfiable. Finally, we show that if a DQBF  $\Phi$  is satisfiable then the algorithm reports the satisfiability of  $\Phi$ .

**Lemma 3.1** (termination). Algorithm 1 terminates.

*Proof.* The procedure GENERATEDEFINITIONS terminates as there are only finitely many assignments  $\sigma$  and an assignment  $\sigma$  cannot be repeated within the inner loop. The proce-

<sup>&</sup>lt;sup>1</sup>In Algorithm 1 we initialize  $\tau$  as the assignment that maps each arbiter variable to true, but we could use any assignment.

dure FINDARBITERASSIGNMENT terminates as there are only finitely many assignments for the arbiter variables A and these are not repeated.

**Theorem 3.1.** If Algorithm 1 reports satisfiability of a DQBF  $\Phi$ , then  $\Phi$  is satisfiable.

*Proof.* Let  $\Phi$  be a DQBF s.t. the algorithm reports satisfiability of  $\Phi$ . We have to show that  $\Phi$  is indeed satisfiable. As the algorithm reports satisfiability of  $\Phi$  there must be a formula  $\psi_D$  and an arbiter assignment  $\tau$  s.t.  $\neg \varphi \wedge \psi_D \wedge \tau$  is unsatisfiable. The construction of  $\psi_D$  ensures that every assignment  $\sigma$  of the universal variables can be extended to a unique assignment  $\hat{\sigma}$  of all variables that satisfies  $\psi_D \wedge \tau$ . We define for each existential variable e a Skolem function  $f_e$  that is given by  $f_e(\sigma|_{D(e)}) = \hat{\sigma}(e)$ . We denote the family of all Skolem functions by f. Now let  $\sigma$  be an arbitrary but fixed assignment of the universal variables. As  $\neg \varphi \land \psi_D \land \tau$  is unsatisfiable, we can conclude that  $\sigma \cup f(\sigma)$  falsifies  $\neg \varphi$ . But this means that  $\sigma \cup f(\sigma)$  satisfies  $\varphi$ . As  $\sigma$  was arbitrary this means that f is a model for  $\Phi$  and this in turn means that  $\Phi$  is satisfiable.

**Theorem 3.2.** If a DQBF  $\Phi$  is satisfiable, then Algorithm 1 reports satisfiability of  $\Phi$ .