Die approbierte Originalversion dieser Diplom-/ Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich.

The approved original version of this diploma or master thesis is available at the main library of the

Vienna University of Technology. http://www.ub.tuwien.ac.at/eng

http://www.ub.tuwien.ac.at

FÜR INFORMATIK **Faculty of Informatics**

# Analysis of the Failure Behavior of Memory Management Units

### DIPLOMARBEIT

zur Erlangung des akademischen Grades

### **Diplom-Ingenieur**

im Rahmen des Studiums

### Technische Informatik

eingereicht von

### **Oliver Hechinger, BSc**

Matrikelnummer 0726503

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger

Wien, 03.12.2013

(Unterschrift Verfasser)

(Unterschrift Betreuung)

# Erklärung zur Verfassung der Arbeit

Oliver Hechinger, BSc Maria-Kuhn-Gasse 6/3/18, 1100 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Danksagung

Mit dem Ende dieser Diplomarbeit schließe ich mein Studium ab und es ist an der Zeit all jenen die bei eben diesem mitgewirkt haben zu danken. Bevor ich aber dazu komme, möchte ich mich herzlichst bei meinem Betreuer Herrn Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Andreas Steininger für die bestmögliche Betreuung die sich ein Student nur wünschen kann bedanken.

Großer Dank gilt meinen Eltern für die fortwährende Unterstützung und die Finanzierung meiner Bildungslaufbahn. Obendrein möchte ich mich auch bei Wolfgang Wallner, BSc für die unzähligen gemeinsam gemeisterten Herausforderungen bedanken. Nicht unerwähnt bleiben soll auch Martina Lang, MA, die mich viele Jahre während meines Studiums motiviert hat und somit auch zu diesem Abschluss ihren Beitrag geleistet hat. Überdies gilt mein Dank all meinen Freunden, die neben Vollzeitarbeit und Diplomarbeit für die notwendige Abwechslung gesorgt haben.

Abschließend noch ein herzliches Dankeschön an Herrn Dr. Bernd Müller von der Robert Bosch GmbH für den Auftrag zu der nun vorliegenden Arbeit.

# Abstract

A promising approach for lowering the complexity of safety critical embedded systems like, e.g., the distributed network of Electronic Control Units (ECUs) in a modern car, is to combine the functionality of multiple ECUs in one unit. Doing so, however, gives rise to the problem of mutual influence of otherwise independent functionalities. Hence, proper separation in between them becomes critical and mandatory. One foundation for this is to introduce a hardware enforced memory separation.

This work is going to describe two different memory protection mechanisms, i.e., the hardware enforced separation in multiple memory regions by a Memory Protection Unit (MPU) and the full memory virtualization by virtual memory. The latter is nowadays common in PCs and even mobile phones and is implemented in a hardware assisted fashion by using a Memory Management Unit (MMU). This work is going to put its focus on this hardware unit and its failure possibilities. To the best of our knowledge, no such in-depth elaboration about MMU failure modes exists.

The MMU features provided by a selection of modern embedded system processors are presented and described. These features are then abstracted in a theoretical MMU, termed hypothetical MMU, consisting of multiple functional blocks. The functionalities and interconnections of these blocks are explained and an in-depth analysis of the failure modes of this MMU is provided. The analysis is based on a single-fault assumption w.r.t. faults within the MMU and additionally considers wrong memory accesses by the processor in combination with MMU internal faults.

In order to confirm, extend or refute the theoretical analysis, a simulation based fault injection in the MMU of the LEON3 processor is performed. This fault injection covers all internal signals of a synthesized version of the MMU and is implemented with tool support. The results of the fault injection are analyzed for their validity and possible bias due to the implemented fault injection method.

While the quantitative forecasting of failure rates is not an objective of this thesis, it is shown that MMUs are prone to critical failure modes and thus should be appropriately protected if a usage in a safety critical system is targeted. The fault injection shows that the theoretical analysis sufficiently covers the experienced failure behavior. Furthermore, especially critical components are pinpointed with relative failure rates and different fault mitigation mechanisms are presented along with an evaluation of their feasibility.

# Kurzfassung

Ein erfolgversprechender Ansatz, um die Komplexität sicherheitskritischer Systeme – wie zum Beispiel dem verteilten Netzwerk von Steuergeräten in einem modernen Auto – zu reduzieren, ist es die Funktionalität mehrerer Steuergeräte auf eines zusammenzufassen. Dadurch ergibt sich allerdings die Möglichkeit, dass sich andernfalls unabhängige Funktionalitäten gegenseitig beeinflussen. Deshalb wird in diesem Fall eine zuverlässige Abgrenzung zwischen den Funktionalitäten unverzichtbar. Eine Grundlage hierfür ist eine in Hardware realisierte Speicherabgrenzung.

Diese Diplomarbeit beschreibt zwei unterschiedliche Speicherabgrenzungsmöglichkeiten. Dies sind einerseits die Hardware-realisierte Unterteilung in verschiedene Speicherregionen mittels einer Memory Protection Unit (MPU) und andererseits die vollständige Speichervirtualisierung durch virtuelle Speicherverwaltung. Letzteres ist der heutzutage übliche Ansatz in PCs sowie Smartphones und wird durch eine sogenannte Memory Management Unit (MMU) Hardware-unterstützt implementiert. Diese Arbeit wird ihr Hauptaugenmerk auf diese Hardwareeinheit und ihre Fehlermöglichkeiten legen. Uns ist bisher keine derartige Ausarbeitung über MMU Fehlermöglichkeiten bekannt.

Die MMU Funktionen einer Auswahl moderner Prozessoren für eingebettete Systeme werden dargestellt und beschrieben. Auf Basis dieser Funktionen wird eine theoretische MMU, bestehend aus unterschiedlichen Blöcken, abstrahiert. Die Funktionen und Querverbindungen dieser Blöcke werden erklärt und auf ihre Fehlermöglichkeiten untersucht. Die Analyse beruht auf einer Einzelfehlerannahme bezüglich Fehler innerhalb der MMU und behandelt zusätzlich noch Kombinationen aus illegalen Speicherzugriffe des Prozessors mit internen Fehlern der MMU.

Um diese theoretische Analyse zu bestätigen, zu erweitern oder zu widerlegen, wird eine simulationsbasierte Fehlereinstreuung in die MMU des LEON3 Prozessors durchgeführt. Diese Fehlereinstreuung deckt alle internen Signale einer synthetisierten Version dieser MMU ab und wird automatisiert durchgeführt sowie ausgewertet. Die Ergebnisse der Fehlereinstreuung werden auf ihre Validität und mögliche systematische Messabweichungen untersucht. Des Weiteren werden die Ergebnisse der theoretischen Analyse zugeordnet.

Während die quantitative Vorhersage der Fehlerraten kein Ziel dieser Arbeit ist, wird gezeigt dass MMUs anfällig für kritische Fehlermöglichkeiten sind und deshalb ausreichend Schutzmaßnahmen getroffen werden müssen, wenn ihr Einsatz in sicherheitskritischen Systemen angestrebt wird. Überdies zeigt sich, dass die theoretische Analyse das festgestellte Fehlerverhalten ausreichend abdeckt. Zusätzlich werden besonders kritische Teile mit relativen Fehlerraten offenbart und verschiedene Schutzmaßnahmen beschrieben, sowie auf ihre Anwendbarkeit überprüft.

# Contents

| 1 | Intr |                                                                            |    |

|---|------|----------------------------------------------------------------------------|----|

| T |      | oduction                                                                   | 1  |

|   | 1.1  | Motivation                                                                 | 1  |

|   | 1.2  | Aims and Scope                                                             | 2  |

|   | 1.3  | Terminology and Background                                                 | 2  |

|   |      | 1.3.1 Faults, Errors and Failures                                          | 2  |

|   |      | 1.3.2 Transient Faults                                                     | 3  |

|   | 1.4  | Methodical Approach and Structure                                          | 4  |

| 2 | Ove  | rview of Memory Management and Protection Approaches                       | 5  |

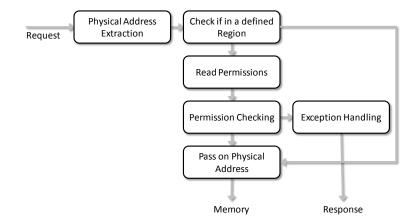

|   | 2.1  | Memory Protection Units                                                    | 5  |

|   | 2.2  | Virtual Memory                                                             | 6  |

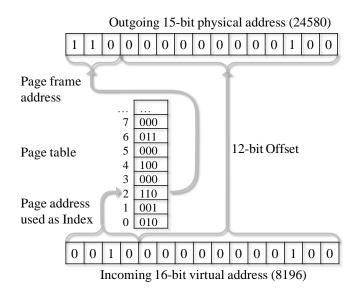

|   |      | 2.2.1 Paging                                                               | 6  |

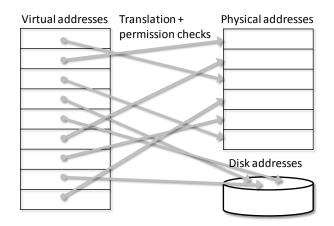

|   |      | 2.2.2 Memory Protection                                                    | 9  |

|   |      | 2.2.3 Memory Sharing                                                       | 9  |

|   |      | 2.2.4 Performance Optimizations                                            | 10 |

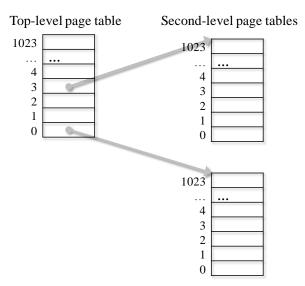

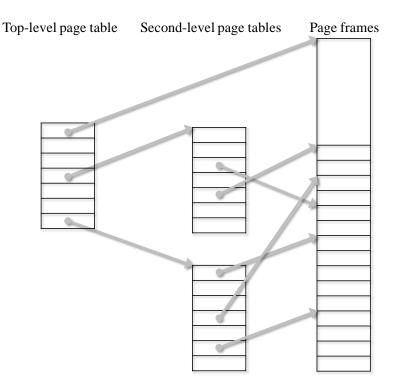

|   |      | 2.2.5 Multilevel Page Tables                                               | 11 |

|   |      | 2.2.6 Timing Uncertainty of Virtual Memory                                 | 13 |

|   | 2.3  | Function Blocks                                                            | 14 |

| 3 | Syne | opsis of Existing Memory Management Units Implementations                  | 17 |

|   | 3.1  | Memory Management Units of the ARM Architecture represented by ARM Cor-    |    |

|   |      | tex A9 and Cortex A15                                                      | 20 |

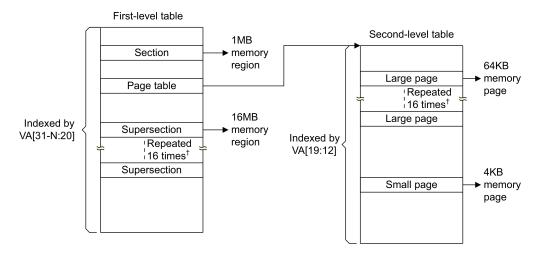

|   |      | 3.1.1 Cortex A9                                                            | 20 |

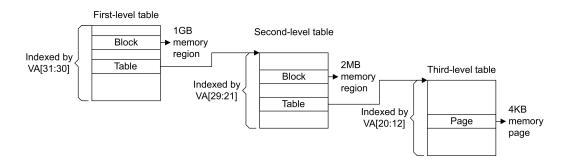

|   |      | 3.1.2 Cortex A15                                                           | 22 |

|   | 3.2  | Memory Management Units of the Analog Devices Inc. Blackfin Architecture   |    |

|   |      | represented by Analog Devices Inc. ADSP-BF54x                              | 24 |

|   | 3.3  | Memory Management Units of the Power Architecture represented by Freescale |    |

|   |      | Semiconductor e200z4                                                       | 25 |

|   | 3.4  | Memory Management Units of the SPARC Architecture represented by Aeroflex  |    |

|   |      | Gaisler LEON3 and LEON4                                                    | 26 |

|   | 3.5  | Memory Management Unit of the Altera Corporation NIOS II Architecture      | 27 |

| 4 | Fail       | ure Mode Analysis of a Hypothetical Memory Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31       |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 4.1        | Fault Hypothesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31       |

|   | 4.2        | Description of Function Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32       |

|   |            | 4.2.1 Considered MMU Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33       |

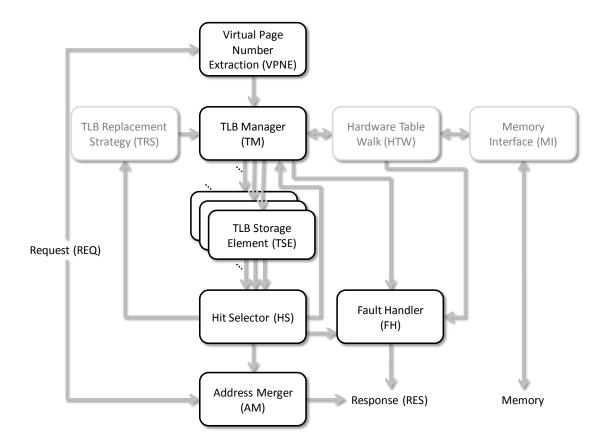

|   |            | 4.2.2 Virtual Page Number Extraction (VPNE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33       |

|   |            | 4.2.3 Optional: Translation Lookaside Buffer (TLB) Replacement Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|   |            | (TRS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34       |

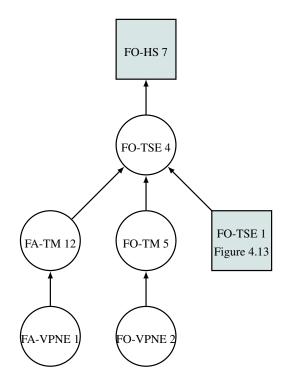

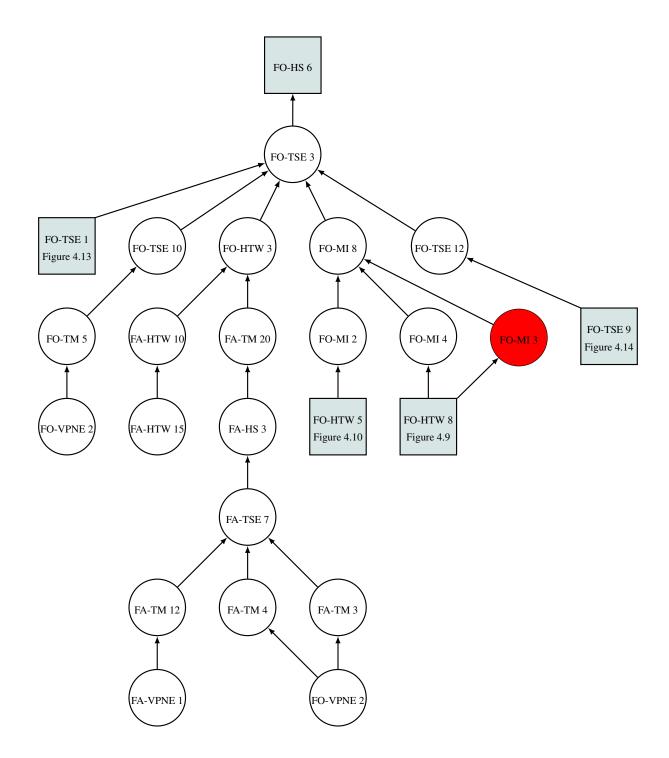

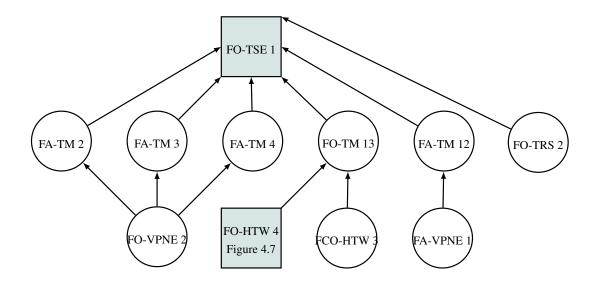

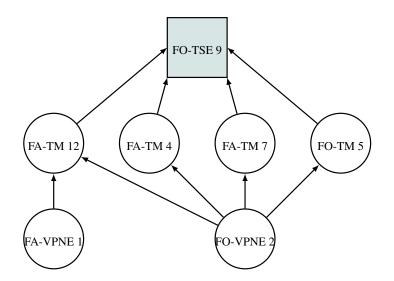

|   |            | 4.2.4 TLB Storage Element (TSE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35       |

|   |            | 4.2.5 Hit Selector (HS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37       |

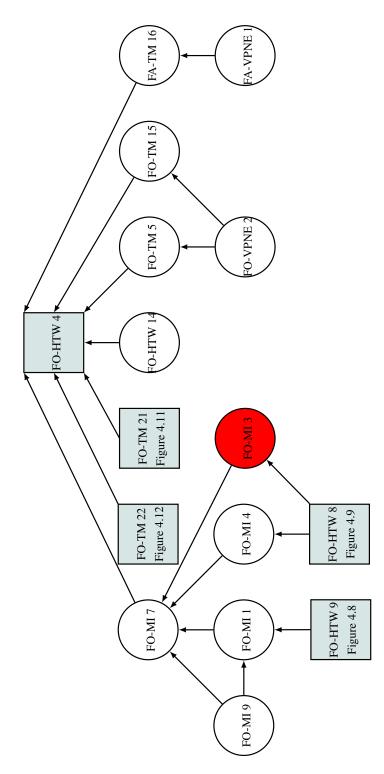

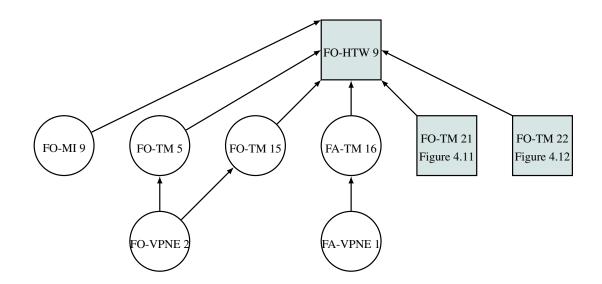

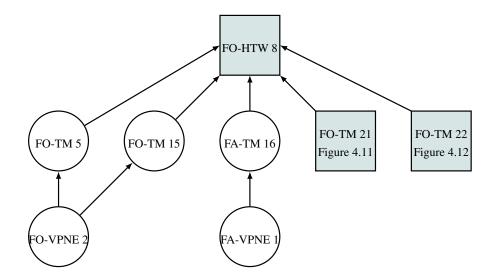

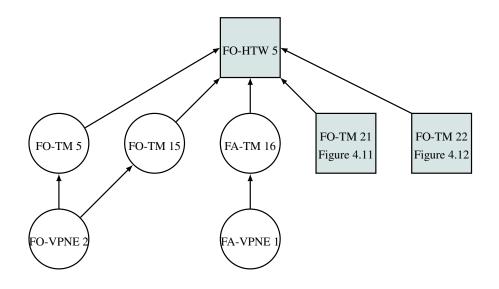

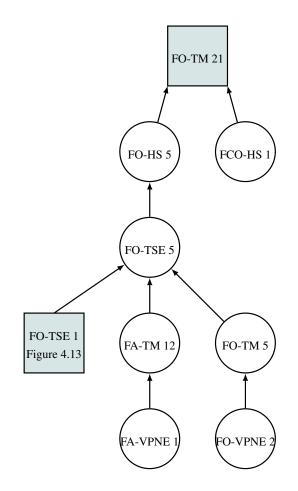

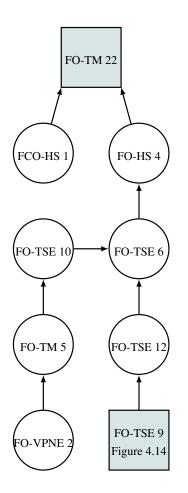

|   |            | 4.2.6 Optional: Hardware Table Walk (HTW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38       |

|   |            | 4.2.7 TLB Manager (TM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39       |

|   |            | 4.2.8 Fault Handler (FH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42       |

|   |            | 4.2.9 Address Merger (AM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42       |

|   |            | 1 2 ( )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43       |

|   | 4.3        | $\partial$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44       |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44       |

|   |            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45       |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45       |

|   |            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46       |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46       |

|   |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46       |

|   | 4.4        | 1 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46       |

|   |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46       |

|   |            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48       |

|   |            | 4.4.3 Output Failures after MI block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50       |

|   |            | 4.4.4 Intermediate Failure Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50       |

|   | 4.5        | Conclusion of the Failure Mode Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59       |

| 5 | Fou        | It Injection Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61       |

| 3 | гац<br>5.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61       |

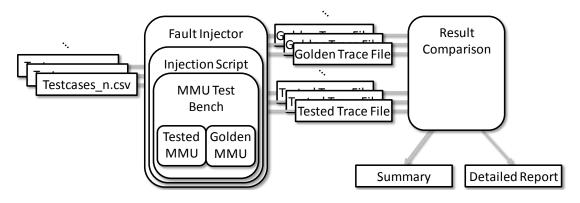

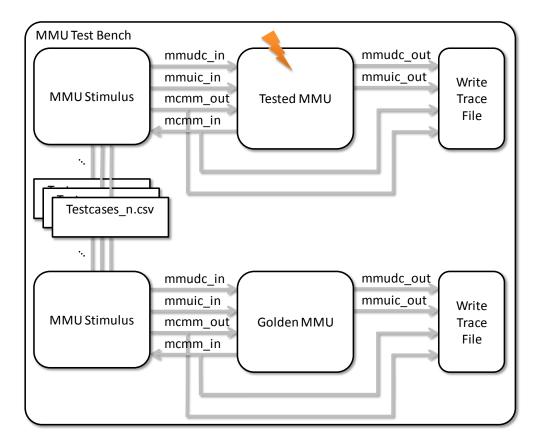

|   | 5.2        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62       |

|   | 5.3        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62<br>62 |

|   | 5.4        | C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64       |

|   | 5.4        | Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65       |

|   |            | 5.4.2 Fault Injection GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68       |

|   |            | 5.4.3 Result Comparison GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68       |

|   | 5.5        | Parameters         Paramet | 75       |

|   | 5.5        | 5.5.1 Workload of the Test Bench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75       |

|   |            | 5.5.1     Workload of the rest bench       5.5.2     Fault Injection Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79       |

|   | 5.6        | Result Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 82       |

|   | 5.0        | 5.6.1 Influence of the Workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82<br>82 |

|   |            | 5.6.2 Influence of the Workload Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84       |

|   |            | 5.6.3 Detected First Faults per Indicated Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87       |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 07       |

|                                                             | 5.6.4                                                                                                                                | Special Cases due to the Fault Injection                                                                                                                                                                                                          | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                             | 5.6.5                                                                                                                                | Consequences of Deviating Actions                                                                                                                                                                                                                 | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

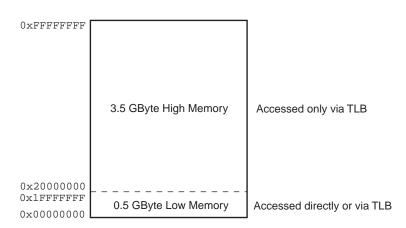

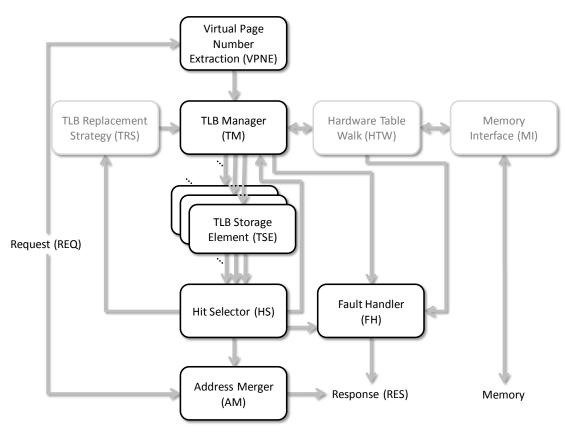

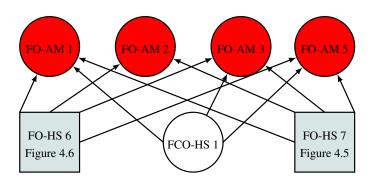

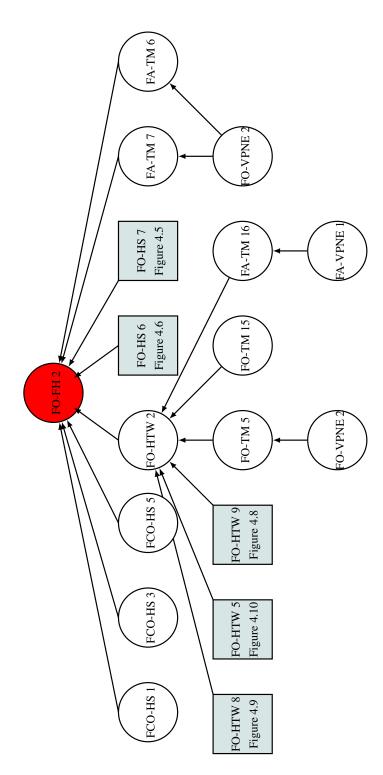

|                                                             | 5.6.6                                                                                                                                | Consequences of Deviating Data                                                                                                                                                                                                                    | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |