# Kronecker Algebra Based Analysis of Shared Memory Concurrent Systems

#### DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

#### Doktor der Technischen Wissenschaften

by

Dipl.-Ing. Robert Mittermayr

Registration Number 9825671

| to the Faculty of Informatics         |                                                     |                                                          |

|---------------------------------------|-----------------------------------------------------|----------------------------------------------------------|

| at the TU Wien                        |                                                     |                                                          |

| Advisor: Ao. UnivProf. DiplIng.       | Dr. techn. Johann Blieberger                        |                                                          |

| The dissertation has been review      | ed by:                                              |                                                          |

|                                       | Ao. UnivProf. DiplIng. Dr. techn. Johann Blieberger | Associate Prof. DiplIng.<br>Dr. techn. Bernd Burgstaller |

| Vienna, 17 <sup>th</sup> August, 2016 |                                                     |                                                          |

| , <del></del>                         |                                                     | DiplIng. Robert Mittermayr                               |

# Kronecker Algebra Based Analysis of Shared Memory Concurrent Systems

#### DISSERTATION

zur Erlangung des akademischen Grades

#### Doktor der Technischen Wissenschaften

eingereicht von

Dipl.-Ing. Robert Mittermayr

Matrikelnummer 9825671

| an der Fakultät für Informatik   |                                                        |                                                          |

|----------------------------------|--------------------------------------------------------|----------------------------------------------------------|

| der Technischen Universität Wien |                                                        |                                                          |

| Betreuung: Ao. UnivProf. DiplIr  | ng. Dr. techn. Johann Blieberger                       |                                                          |

|                                  |                                                        |                                                          |

| Diese Dissertation haben begutad | chtet:                                                 |                                                          |

|                                  | Ao. UnivProf. DiplIng.<br>Dr. techn. Johann Blieberger | Associate Prof. DiplIng.<br>Dr. techn. Bernd Burgstaller |

| Wien, 17 August, 2016            |                                                        |                                                          |

|                                  |                                                        | Dipi. ing. Hobort wittermayi                             |

# Erklärung zur Verfassung der Arbeit

Dipl.-Ing. Robert Mittermayr Johannesstr. 6 3304 St. Georgen am Ybbsfelde

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

| Wien, 17 August, 2016 |                            |

|-----------------------|----------------------------|

|                       | DiplIng. Robert Mittermayr |

### Acknowledgements

I would like to express my gratitude to all those who gave me the possibility to complete this thesis.

I sincerely thank Prof. Bernd Burgstaller for his valuable hints and tips for further improvements. He often brought new aspects into my dissertation.

I am deeply indebted to my supervisor Prof. Johann Blieberger. His guidance, help, and stimulating suggestions helped me in all the time of research for this thesis.

Especially, I would like to thank my lovely wife Kathrin for all the support that she gave me during the years I have been working on this thesis. This work would not have been possible without her patient love.

### Abstract

Program analysis of multi-threaded software is still a challenge. Beside other reasons, this comes from the fact that synchronization has to be taken into account. In particular, a suitable graph based model has been missing. In this dissertation, we introduce a novel graph based approach. It is based on the idea that thread interleavings can be studied with a matrix calculus. This is a novel approach in this research area. Our sparse matrix representations of a program are manipulated using Kronecker algebra. In the course of this dissertation we extend it and prove some important properties. The underlying graph – which we call concurrent program graph (CPG) – represents a multi-threaded program and plays a similar role for concurrent systems as control flow graphs do for sequential programs. Thus a suitable graph model for program analysis of multi-threaded software is set up. Due to synchronization, e.g., via synchronization primitives like semaphores and barriers, it turns out that often only very small parts of the resulting graph are actually needed, whereas the rest is unreachable. A lazy implementation of matrix operations ensures that unreachable parts are never calculated. This speeds up processing significantly and shows that our approach is very promising. We parallelized this lazy algorithm and thus gain additional speedup by exploiting the power of modern multi-core architectures.

In this dissertation, we will show how we use CPGs to detect deadlocks statically in concurrent programs.

We present a new synchronization construct modeling barriers. By applying this, we are able to statically analyze Ada multi-tasking programs that employ barriers for synchronization issues. It turns out that our Kronecker algebra implementation can be used out-of-the-box for CPGs using such barrier synchronization primitives.

In addition, we show that CPGs can be used as a basis for a worst-case execution time (WCET) analysis of multi-threaded programs. We employ a generating functions based approach for setting up data flow equations which are then solved by well-known elimination based data flow analysis methods. With this approach, we are able to calculate the WCET (including stalling times) of multi-threaded programs with a non-linear function solver. Non-linearity turns out to be inherent to the multi-threaded WCET problem.

Finally, we show how our Kronecker algebra based approach can be adopted in the field of railway systems. For multiple trains in a railway disposition system and based on given routes, it can be used to suggest deadlock-free movements only. Additional

constraints, such as overtaking and train connections, may be taken into account. Our railway approach was already extended by others, e.g., to save energy by minimizing stop and go of trains.

### Kurzfassung

Programmanalyse von nebenläufigen Programmen ist immer noch eine Herausforderung. Das kommt unter anderem daher, dass Synchronisation berücksichtigt werden muss. Im Speziellen fehlte bisher ein geeignetes Graphenmodell. Mit dieser Dissertation führen wir einen graphenbasierten Ansatz ein. Dieser fußt auf der Idee, dass zeitlich verschränkte Abarbeitung (thread interleavings) durch einen Matrizenkalkül betrachtet werden kann. Dies ist neu in diesem Forschungsgebiet. Die dünnbesetzten Matrizen eines Programmes werden mittels Kronecker Algebra-Operationen manipuliert. Im Zuge dieser Dissertation wird diese erweitert und manch wichtige Eigenschaft bewiesen. Der zugrundeliegende Graph, den wir concurrent program graph (CPG) nennen, repräsentiert ein nebenläufiges Programm und spielt eine ähnliche Rolle wie Kontrollflussgraphen für sequentielle Programme. Daher ist er ein geeignetes Modell für die Programmanalyse von nebenläufigen Programmen. Es stellt sich heraus, dass durch Synchronisation (z.B. durch Synchronisationsprimitive wie Semaphoren oder Barrieren) oft nur ein sehr kleiner Teil des resultierenden Graphen nötig und der Rest unerreichbar ist. Eine verzögerte (im Englischen oft als "lazy" bezeichnete) Auswertung der Matrixoperationen stellt sicher, dass unerreichbare Teile nie berechnet werden. Das beschleunigt die Berechnung signifikant und zeigt, dass unser Ansatz vielversprechend ist. Die Parallelisierung dieses Algorithmus für Mehrkern-Architekturen ermöglichte eine signifikante Laufzeit-Reduktion.

In dieser Dissertation zeigen wir, wie CPGs zum statischen Finden von Deadlocks in nebenläufigen Programmen verwendet werden können.

Des Weiteren führen wir ein neues Synchronisationskonstrukt, das Barrieren modelliert, ein. Dieses Konstrukt ermöglicht die statische Analyse von nebenläufigen Ada-Programmen, die Barrieren zur Synchronisation verwenden. Programme, die auf diese Synchronisationsprimitive bauen, können mit unserer völlig unveränderten Kronecker Algebra-Implementierung analysiert werden.

Zusätzlich zeigen wir, dass CPGs als Basis für eine Analyse der maximalen Laufzeit – im Englischen oft als worst-case execution time (WCET) bezeichnet – verwendet werden können. Wir verwenden einen Ansatz, der auf erzeugende Funktionen basiert. Datenflussgleichungen werden durch etablierte (sogenannte elimination based) Datenflussanalysemethoden gelöst. Mit diesem Ansatz wird es möglich, die WCET von nebenläufigen Programmen zu berechnen. Diese WCET inkludiert auch Zeiten, in denen Threads blockiert sind. Mittels eines nicht-linearen Funktionslöser werden die Gleichungen gelöst. Es zeigt sich, dass nebenläufigen WCET-Problemen Nicht-Linearität inhärent ist.

Schließlich zeigen wir, wie unser Kronecker Algebra-Ansatz im Bereich der Eisenbahn verwendet werden kann. Bei gegebenen Fahrstraßen wird es dadurch Dispositionssystemen möglich, für mehrere Züge automatisch deadlockfreie Zugbewegungen vorzuschlagen. Zusätzliche Bedingungen, wie z.B. Überholungen und Zugverbindungen, können dabei beachtet werden. Dieser Ansatz wurde bereits von anderen erweitert, um z.B. durch Minimierung von Brems-/Beschleunigungszyklen energiesparend zu fahren.

### Contents

| Al | bstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | xi                                |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Κı | urzfassung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | xiii                              |

| Li | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xvii                              |

| Li | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xix                               |

| 1  | Introduction1.1 Motivation1.2 Thesis Overview and Contributions1.3 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 2                               |

| 2  | Preliminaries  2.1 Overview  2.2 Semiring  2.3 Control Flow Graphs  2.4 Semaphores  2.5 Edge Splitting  2.6 Basic Matrix Notations and Operations  2.7 Correspondence between Matrices and Directed Graphs  2.8 Limitations                                                                                                                                                                                                                                                                                                                                                                                                 | . 8<br>. 8<br>. 9<br>. 11<br>. 14 |

| 3  | Kronecker Algebra – A Matrix Calculus 3.1 Kronecker Product / Zehfuss Product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |

| 4  | Concurrent Program Graphs 4.1 Generating a Concurrent Program's Matrix 4.2 Determining Entry and Final Nodes of CPGs 4.3 ○-Operation and Synchronization 4.4 Unreachable Parts Caused by Synchronization 4.5 Properties of CPGs 4.6 Efficient Implementation of the ○-Operation 4.7 Concurrent Program Graphs 4.8 Determining a Concurrent Program's Matrix 4.9 Determining Entry and Final Nodes of CPGs 4.1 CPGs 4.2 Determining Entry and Final Nodes of CPGs 4.3 O-Operation and Synchronization 4.4 Unreachable Parts Caused by Synchronization 4.5 Properties of CPGs 4.6 Efficient Implementation of the ○-Operation | . 30<br>. 31<br>. 32<br>. 33      |

|              | 4.7<br>4.8                             | Lazy Implementation of Kronecker Algebra                                                                                                                    |                          |

|--------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 5            | <b>Dea</b> 5.1                         | dlocks  Deadlock Example                                                                                                                                    | <b>43</b> 44             |

| 6            | Exa 6.1 6.2 6.3 6.4 6.5                | mples and Empirical Data  Deadlock Example                                                                                                                  | 50<br>52<br>55           |

| 7            | Stat                                   | cic Analysis of Barriers Barriers                                                                                                                           | <b>61</b> 62             |

| 8            | Wor<br>8.1<br>8.2                      | rst-Case Execution Time Analysis  Worst-Case Execution Time Analysis on RCPGs                                                                               |                          |

| 9            | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6 | dlock Avoidance for Railway Systems  Deadlocks in Computers vs. Deadlocks in Railway Systems  Railway System Model                                          | 100<br>102<br>106<br>106 |

| 10           | 10.1<br>10.2<br>10.3<br>10.4           | Ated Work  Kronecker Algebra  Data Structures Modeling Concurrent Systems  Static Analysis of Barriers  Worst-Case Execution Time Analysis  Railway Systems | 112<br>112<br>112        |

| 11           | 11.1                                   | Summary                                                                                                                                                     | 117<br>117<br>119        |

| $\mathbf{A}$ | The                                    | State Explosion Problem                                                                                                                                     | 125                      |

| Bi           | bliog                                  | graphy                                                                                                                                                      | 129                      |

## List of Figures

| 2.1 | Pseudocode Factorial                                        | 9  |

|-----|-------------------------------------------------------------|----|

| 2.2 | CFG of Factorial                                            | 10 |

| 2.3 | Semaphores                                                  | 10 |

| 2.4 | Semaphores with Non-blocking v-operations                   | 11 |

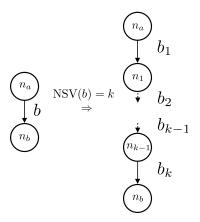

| 2.5 | Edge Splitting for $k$ Synchronization Primitive Calls      | 13 |

| 2.6 | Edge Splitting for $k$ Shared Variable Accesses             | 14 |

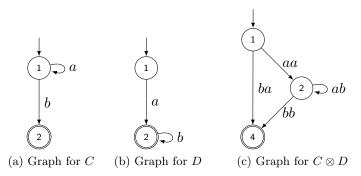

| 3.1 | Simultaneous Executions via Kronecker Product $C\otimes D$  |    |

| 3.2 | Simultaneous Executions via Kronecker product $E \otimes F$ | 21 |

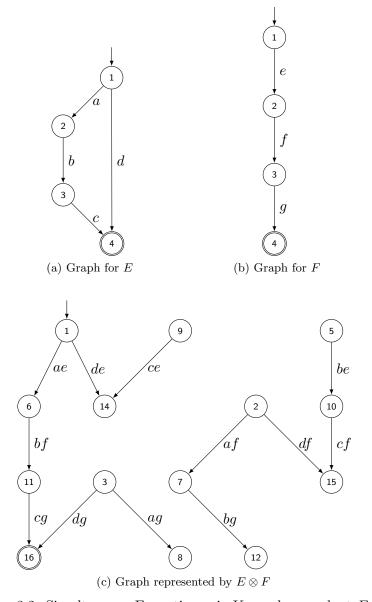

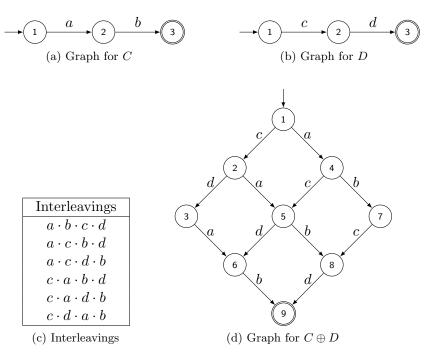

| 3.3 | The Graphs of $C, D,$ and $C \oplus D$                      | 23 |

| 3.4 | A Simple Cartesian Product Graph $(C \oplus D)$             | 25 |

| 4.1 | Overview                                                    | 28 |

| 4.2 | Mutual Exclusion Example                                    | 34 |

| 4.3 | Unreachable Parts of the Mutual Exclusion Example           | 35 |

| 4.4 | Example Program with Self-Deadlock                          | 37 |

| 4.5 | CPGs are Irreducible                                        | 40 |

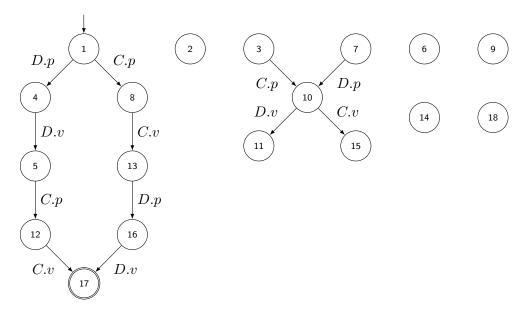

| 5.1 | Deadlock Example                                            | 46 |

| 5.2 | Some Unreachable Parts of the Deadlock Example              | 47 |

| 6.1 | A Second Deadlock Example                                   | 51 |

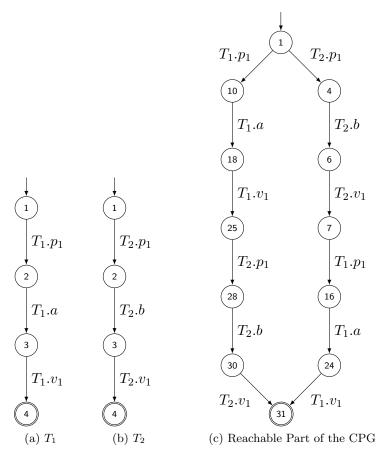

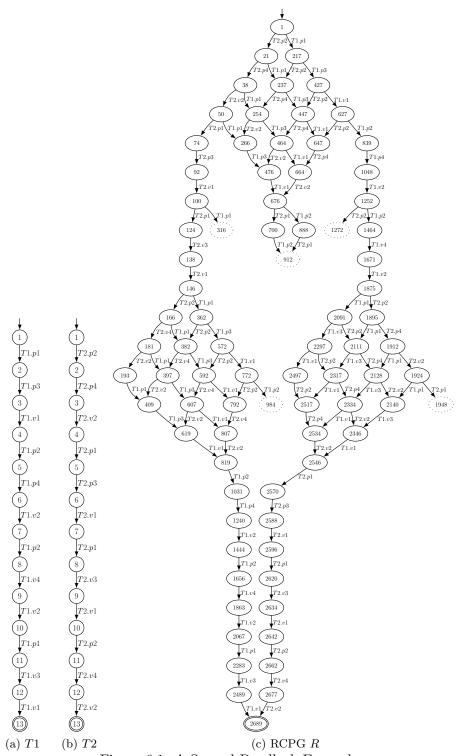

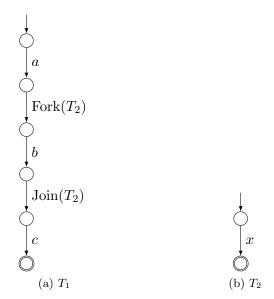

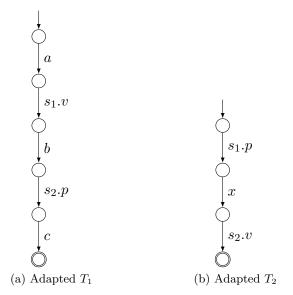

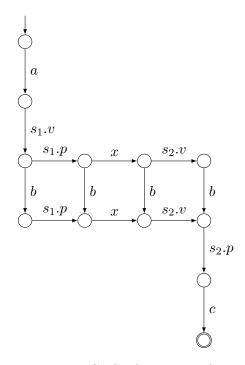

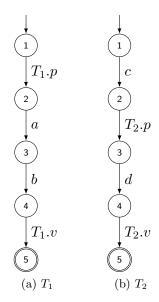

| 6.2 | RCFGs for Example Consisting of $T_1$ and $T_2$             | 52 |

| 6.3 | Adapted RCFGs for Example Consisting of $T_1$ and $T_2$     | 53 |

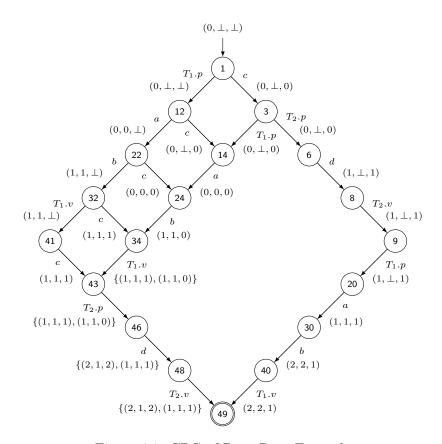

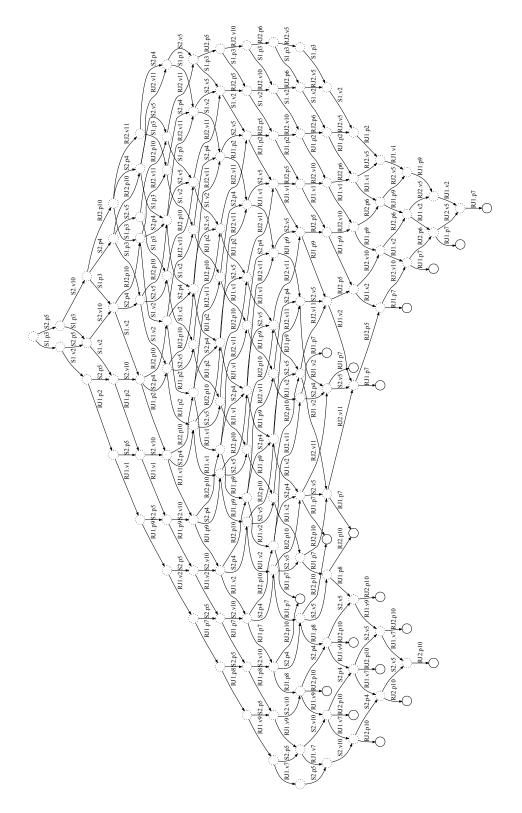

| 6.4 | RCPG of the $T_1$ - $T_2$ -System                           | 53 |

| 6.5 | Client-Server Example                                       | 54 |

| 6.6 | Data Race Example                                           | 55 |

| 6.7 | RCFGs for Data Race Example                                 | 56 |

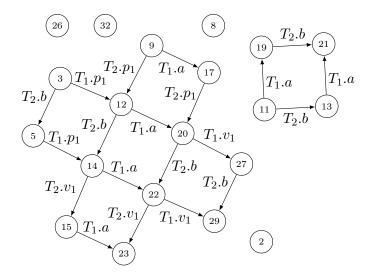

| 6.8 | CPG of Data Race Example                                    | 58 |

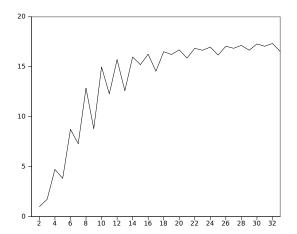

| 6.9 | Improvements via a Parallel Version                         | 60 |

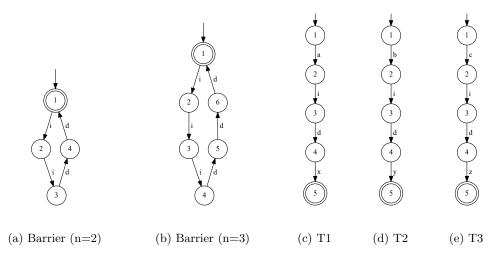

| 7.1 | RCFGs of Tasks T1, T2, and T3 Using a Barrier               |    |

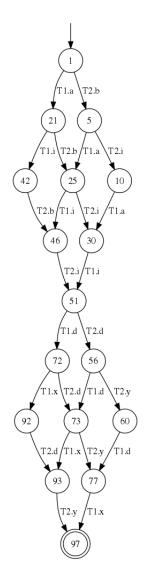

| 7.2 | CPG for Program Consisting of T1 and T2                     |    |

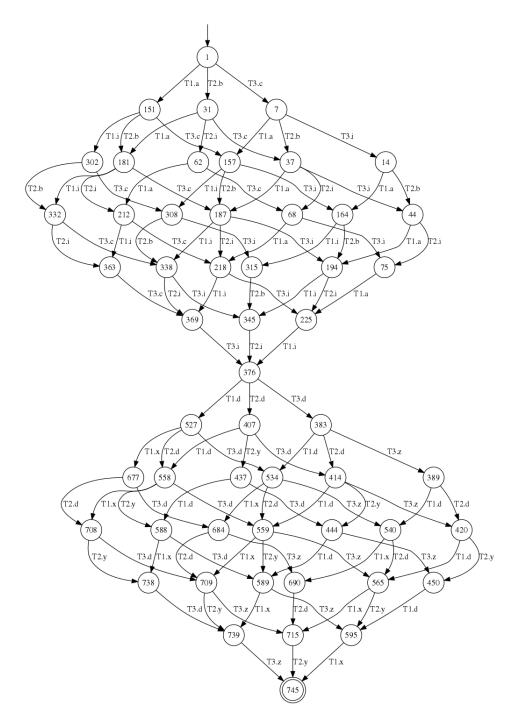

| 7.3 | CPG for Program Consisting of T1, T2, and T3                | 66 |

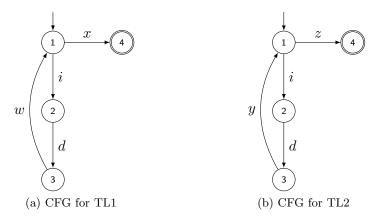

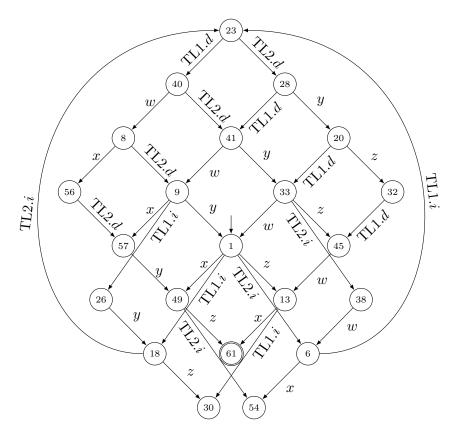

| 7.4  | CFGs for Example Consisting of TL1 and TL2                               |

|------|--------------------------------------------------------------------------|

| 7.5  | CPG for Program Consisting of TL1 and TL2                                |

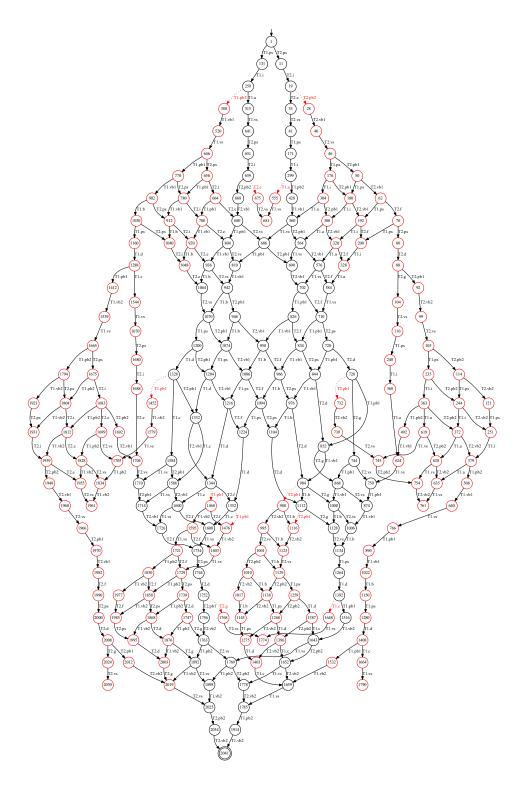

| 7.6  | CPG of Reusable Barrier Solution using Semaphores                        |

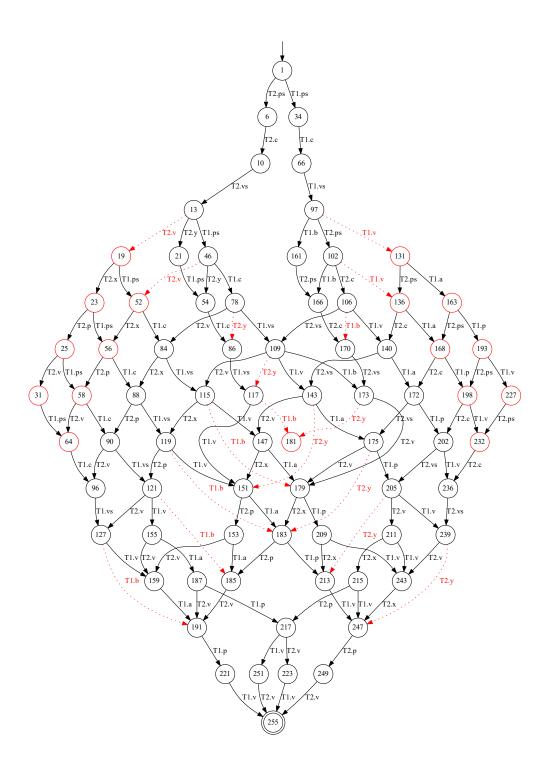

| 7.7  | CPG of Non-Reusable Barrier Solution using Semaphores                    |

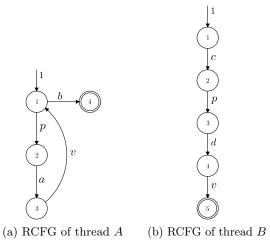

| 8.1  | RCFGs of Threads $A$ and $B$                                             |

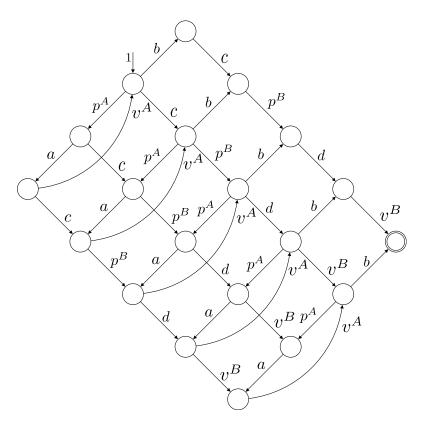

| 8.2  | Kronecker Sum $A \oplus B$ of Threads $A$ and $B$                        |

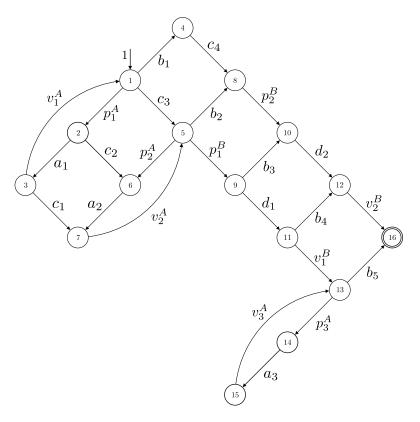

| 8.3  | RCPG                                                                     |

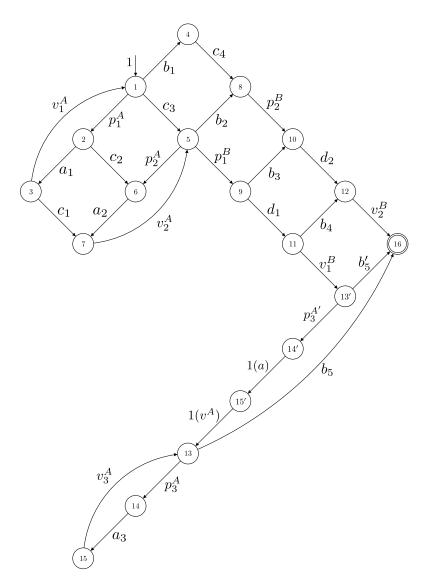

| 8.4  | Adapted RCPG                                                             |

| 9.1  | Graph $(C \oplus D) \otimes S$                                           |

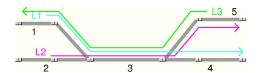

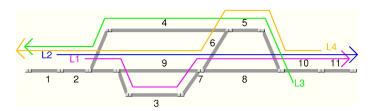

| 9.2  | A Simple Example                                                         |

| 9.3  | Possible Train Movements                                                 |

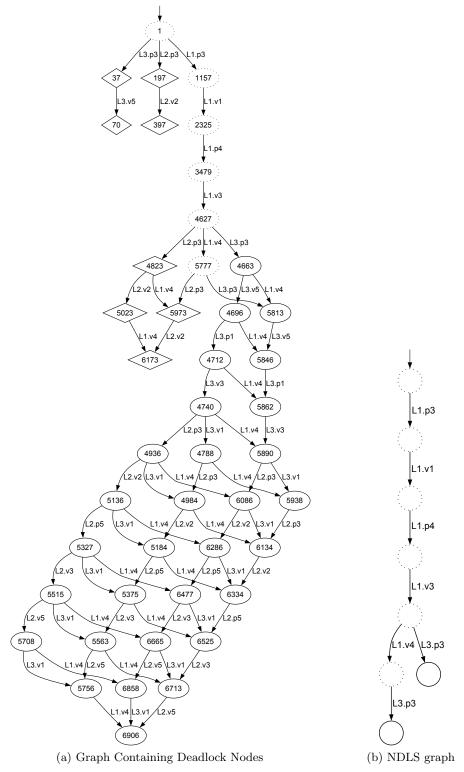

| 9.4  | A More Elaborate Example                                                 |

| 9.5  | Resulting NDLS Graph                                                     |

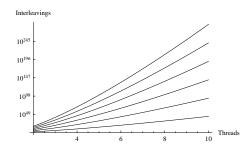

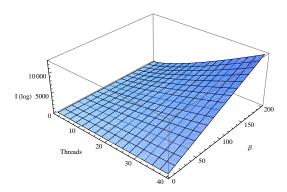

| A.1  | Interleavings for Fixed Number of Statements per Thread                  |

| 11.1 | Interleavings for a Variable Number of Threads and Statements per Thread |

### List of Tables

| 6.1 | Empirical Data                                                                                                                                                                                       | 59  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 8.1 | WCET for $\ell=2$ and Multiple Values of $\tau_c$                                                                                                                                                    | 94  |

| 9.2 | Differences between the Deadlock Problem in Computer and Railway Systems Routes of Trains $L_1, L_2$ , and $L_3 \ldots \ldots \ldots \ldots \ldots$ Four Possible Outcomes of an Analyzing Algorithm | 103 |

| A.1 | Computation Results of Program $\mathcal{P}$                                                                                                                                                         | 126 |

CHAPTER 1

### Introduction

"The hardest thing is to go to sleep at night, when there are so many urgent things needing to be done. A huge gap exists between what we know is possible with today's machines and what we have so far been able to finish."

- DONALD ERVIN KNUTH, U.S. American computer scientist and ACM Turing Award winner 1974, 1938-

This dissertation is about analysis of concurrent programs including worst-case execution time analysis and deadlock detection. In order to generate graphs representing concurrent programs, we adopt the so-called Kronecker algebra which we explore and extend in the course of this thesis. In addition, we apply Kronecker algebra to support deadlock free train disposition in railway systems.

Organization of this chapter is as follows. We begin by motivating the topic in Section 1.1. In Section 1.2 we give a brief overview and highlight the major contributions of this doctoral thesis. Finally, we present the overall organization of this dissertation in Section 1.3.

#### 1.1 Motivation

For safety-critical systems, dependable systems and robust embedded systems, software has to be provably correct. In particular, this is a very important issue, e.g., in the fields of medical systems, aviation, rail, and automotive industries. In general, deadlock freedom is a desired property. In addition, for real-time systems also the maximum computation time is an important issue, i.e., to have a computation result within a certain time. It is widely agreed that the problem of determining upper bounds on execution times for sequential programs has been more or less solved [WEE+08]. With the advent of multi-core processors scientific and industrial interest focuses on analyzing and verifying multi-threaded applications. Analysis of multi-threaded software is still a challenge. Beside other reasons, this comes from the fact that synchronization has to

be taken into account. For sequential programs, control flow graphs are often used as a basis for static program analysis. An equivalent model for multi-threaded programs taking synchronization between threads into account has been missing.

#### 1.2 Thesis Overview and Contributions

The idea that thread interleavings of concurrent programs can be studied with a matrix calculus is novel in this research area. We are immediately able to support conditionals, loops, and synchronization. Our sparse matrix representations of the program are manipulated using a lazy implementation of Kronecker algebra. We use synchronization primitives (e.g semaphores and barriers) for thread synchronization. One goal is generating a data structure called *concurrent program graph* (CPG) which describes all possible interleavings and incorporates synchronization while preserving completeness. CPGs play a similar role for concurrent systems as control flow graphs (CFGs) do for sequential programs.

We prove that CPGs in general can be represented by sparse adjacency matrices. Thus the number of entries in the matrices is linear in their number of lines. Hence efficient algorithms can be applied to CPGs.

In the worst-case, the number of lines increases exponentially in the number of threads. In general, however, a CPG contains many nodes and edges unreachable from the entry node. We propose two major optimizations. First, if the program contains a lot of synchronization, only a very small part of the CPG is reachable. Thanks to a lazy implementation of the matrix operations, only the reachable part is computed. As a second optimization we have parallelized the CPG generation in order to exploit modern many-core hardware architectures. Both optimizations speed up processing significantly and show that our approach is very promising.

In the first place, we use CPGs as a vehicle for detecting deadlocks of multi-threaded programs. Deadlocks show up as a natural property of a concurrent program's adjacency matrix, namely as zero lines.

CPGs can also be used to analyze multi-threaded programs using barriers as a synchronization aid. We propose a novel barrier synchronization construct and compare it to a semaphore-based barrier implementation. As a byproduct, we show how our CPG-based approach can be used as a basis for proving semaphore-based barrier implementations and their usage scenarios correct.

In this dissertation, CPGs are used to show how to calculate the WCET of the underlying concurrent system. We adopt the generating functions-based approach presented in [Bli02, Section 4]. Since concurrent programs may contain blocking because of synchronization between threads, the terms execution time and worst-case execution time (WCET) do not apply directly to concurrent systems. However, we stick to the term WCET for concurrent systems. The reader, however, has to be aware of the fact that, in general, the WCET includes stalling time.

CPGs together with several techniques form a framework for analyses of various properties of multi-threaded shared memory programs. We will see that additional techniques

including data flow analysis, symbolic evaluation, and (automata based) model checking can be applied to CPGs.

We also adapt our Kronecker algebra based deadlock detecting approach to railway systems. For multiple trains and a given track topology, all possible train movements can be calculated. States which will probably, certainly and certainly not lead to a deadlock of the involved trains are distinguished. The approach may take into account additional constraints, e.g., overtaking and train connections.

The main contributions of this dissertation are:

- 1. A framework for analyzing concurrent systems. By using a matrix calculus which is often referred to as *Kronecker algebra*, we are able to model concurrent systems as matrices. We model thread interleavings and synchronization via semaphores by using Kronecker sum, Kronecker product, and a slightly modified Kronecker product operator which we call *selective Kronecker product*.

- 2. An approach for calculating the entries of the matrices lazily. In order to exploit multi-core architectures, we implemented a parallel version and thereby gained a very good speedup.

- 3. An approach for detecting deadlocks in concurrent systems.

- 4. We show how to model Ada's barriers such that Kronecker algebra can be employed for static analysis. This is done by introducing a novel synchronization primitive modeling the semantics of barriers. We compare our barrier synchronization primitive with a barrier implementation based on semaphores. As a byproduct, we show how our CPG-based approach can be used as a basis for proving semaphore-based implementations correct.

- 5. We propose a worst-case execution time analysis approach for concurrent programs and focus on automatically calculating and incorporating stalling times (e.g. caused by lock contention). We employ a generating functions-based approach for setting up data flow equations which are solved by well-known elimination based data flow analysis methods or an off-the-shelf equation solver. The WCET of multi-threaded programs can finally be calculated with a non-linear function solver. This novel approach is suitable for both, namely parallel and concurrent systems.

- 6. A deadlock avoidance approach for railway systems. For multiple trains and a given track topology, we are able to calculate all possible train movements. Some lead and some do not lead to deadlocks. From some points on no deadlocks are reachable and the trains can proceed with their movements in any order. From certain other points a deadlock is inevitable. Our approach, which may take into account additional constraints such as overtaking and train connections, can be used to avoid such situations and to suggest only deadlock-free train movements.

7. Proofs concerning properties of matrices representing concurrent programs and their operations. We proof a new property of the Kronecker sum of matrices which we call *Mixed Sum Rule*. In addition, we proof the *sparsity* of matrices representing concurrent systems, i.e., the number of entries in such a matrix is linear in its order.

Because we already have published parts of this thesis there already exist publications and projects building upon the matrix calculus established during the work for this dissertation. Our Kronecker algebra based approach is already used in the following papers. In [BB14] Kronecker algebra is applied in order to statically analyze Ada multi-tasking programs that employ protected objects for synchronization issues.

Our Kronecker algebra model is also used in the railway domain. The adaptations required for the railway domain were done during the work done for this doctoral thesis and appeared in [MBS12]. It was extended in several publications. For example, a Kronecker algebra based method for determining the travel time of trains in railway systems is presented in [VBS12]. Travel time analysis in railway systems may be compared to WCET analysis in computer systems. The approach of [MBS12] was also adopted in the *EcoRailNet* project. It was a joint project of ÖBB-Infrastruktur AG, ÖBB-Produktion GmbH, Thales Austria GmbH, and Vienna University of Technology (Institute of Computer Aided Automation) funded by the Austrian Ministry for Transport, Innovation and Technology (New Energy 2020, Project ID: 834586). The aim of the project was to save energy by minimizing stop and go of trains. Instead of only taking into account one single train, a railway system consisting of multiple trains turned out to be a solvable global optimization problem which can be solved fast and automatically [Vol14].

#### 1.3 Outline

The outline of this doctoral thesis is as follows. In Chapter 2 some preliminaries such as our semiring, control flow graphs, edge splitting, and basic matrix notation and operations are introduced. The used matrix calculus, often referred to as Kronecker algebra, and some of its properties are introduced in Chapter 3. Our model of concurrency, its properties, and optimizations like our lazy approach are presented in Chapter 4. Chapter 5 demonstrates how we are able to detect deadlocks. In Chapter 6 we give examples and present empirical data. We introduce a novel barrier synchronization primitive and compare it to semaphore-based barrier implementations in Chapter 7. Chapter 8 is devoted to worst-case execution time analysis of concurrent programs and we present a detailed example. In Chapter 9 we show how our Kronecker algebra approach can be applied to railway systems in order to avoid deadlocks in train disposition systems. In Chapter 10 we survey related work. We draw our conclusion and outline possible future work in Chapter 11. Finally, we give an introduction to the state explosion problem and show how the number of interleavings can be calculated for an arbitrary number of threads and their corresponding statements in Appendix A.

"We can only see a short distance ahead, but we can see plenty there that needs to be done."

- ALAN TURING, English computer scientist, mathematician, logician, cryptanalyst and theoretical biologist, 1912-1954

CHAPTER 2

### **Preliminaries**

"Je mehr ich über die Sprache nachdenke, desto sonderbarer kommt es mir vor, dass sich die Leute jemals verstehen."

– KURT FRIEDRICH GÖDEL, Austrian, and later American, logician, mathematician, and philosopher, 1906-1978

In this chapter, we introduce preliminaries and basic notation required throughout this dissertation. We start with introducing our semiring and continue with Control Flow Graphs (CFGs). In addition, we show how we represent synchronization primitives, e.g., semaphores. Then we show how to split edges in order to get Refined Control Flow Graphs (RCFGs) from each thread's CFG. Edge splitting is done for synchronization primitive calls. For value-sensitive analysis, we propose an edge splitting for shared variables, too. This procedure ensures the granularity needed for manipulation with the matrix calculus as introduced below in Chapter 3. Because our models representing multi-threaded programs is generated out of matrices, we state basic matrix notations, terminology, operations, and discuss how matrices correspond to directed graphs. Finally, we mention some limitations which we admit throughout this dissertation.

#### 2.1 Overview

We model shared memory concurrent systems by threads which use synchronization primitives, e.g., semaphores and barriers, for synchronization. Threads and synchronization primitives are represented by CFGs [Hec77, ASU86, AP02]. *Edge splitting* which is described in Subsection 2.5 has to be applied to the edges containing synchronization primitive calls. The resulting *Refined CFGs* (RCFGs) are represented by adjacency matrices. These matrices are then manipulated by Kronecker algebra. We assume that the edges of RCFGs are labeled by elements of a semiring defined in the following section.

#### 2.2 Semiring

In this section, we define our semiring. Similar definitions and further properties of semirings can be found in [KS86].

Our semiring  $\langle \mathcal{L}, +, \cdot, 0, 1 \rangle$  consists of a set of labels  $\mathcal{L}$ , two binary operations + and  $\cdot$ , and two constants 0 and 1 such that

- 1.  $\langle \mathcal{L}, +, 0 \rangle$  is a commutative monoid,

- 2.  $\langle \mathcal{L}, \cdot, 1 \rangle$  is a monoid,

- 3. left and right distributivity of  $\cdot$  over +:

- $\forall l_1, l_2, l_3 \in \mathcal{L} : l_1 \cdot (l_2 + l_3) = l_1 \cdot l_2 + l_1 \cdot l_3$  and

- $(l_1 + l_2) \cdot l_3 = l_1 \cdot l_3 + l_2 \cdot l_3$  hold and

- 4. constant 0 is an absorbing element concerning the semiring operation '·':  $\forall l \in \mathcal{L} : 0 \cdot l = l \cdot 0 = 0$ .

Intuitively, our semiring is a unital ring without subtraction. For each  $l \in \mathcal{L}$  the usual rules are valid, e.g., l+0=0+l=l and  $1 \cdot l=l \cdot 1=l$ . In general  $\forall a,b \in \mathcal{L}: a \cdot b \neq b \cdot a$ . In case of juxtaposition and if it is clear in the context, we often write ab instead of  $a \cdot b$ . In addition, we equip our semiring with the unary star operation \*. For each  $l \in \mathcal{L}$ ,  $l^*$  is defined by

$$l^* = \sum\nolimits_{j>0} l^j, \text{ where } l^0 = 1 \text{ and } l^{j+1} = l^j \cdot l = l \cdot l^j \text{ for } j \geq 0.$$

The set of labels  $\mathcal{L}$  is defined by  $\mathcal{L} = \mathcal{L}_{V} \cup \mathcal{L}_{S}$ , where  $\mathcal{L}_{V}$  is the set of non-synchronization labels and  $\mathcal{L}_{S}$  is the set of labels representing synchronization primitive calls, e.g.,  $p_{i}$  and  $v_{i}$  referring to the operation p and v of semaphore i. The sets  $\mathcal{L}_{V}$  and  $\mathcal{L}_{S}$  are disjoint.

A prominent example for semirings are regular expressions (cf. [Tar81]) which can be used for describing the behavior of finite state automata. A second example for semirings is performing data flow analysis (e.g. [BB98, BB03, BBS99, BBM06, SBF00]).

If it is not clear in the context to which thread a label l belongs, we write  $l^X$  to denote that l belongs to thread X.

#### 2.3 Control Flow Graphs

We represent threads and synchronization primitives in form of control flow graphs. A Control Flow Graph (CFG) is a directed labeled graph defined by  $G = \langle V, E, n_e, V_f \rangle$  with a set of nodes V, a set of directed edges  $E \subseteq V \times V$ , a so-called entry node  $n_e \in V$ , and a set of final nodes  $V_f \subseteq V$ . An entry node has an incoming edge which has no source node. A final node is depicted with a double circle. We require that each  $n \in V$  is reachable through a sequence of edges from  $n_e$ .

```

Factorial ()

1 fact \leftarrow 1

2 n \leftarrow input ("Enter a number:")

3 while n \ge 1 do

4 fact \leftarrow fact * n

5 n \leftarrow n - 1

6 endwhile

7 Print (fact)

```

Figure 2.1: Pseudocode Factorial

Nodes can have at most two outgoing edges. Thus the maximum number of edges in CFGs is 2|V|. We will use this property later.

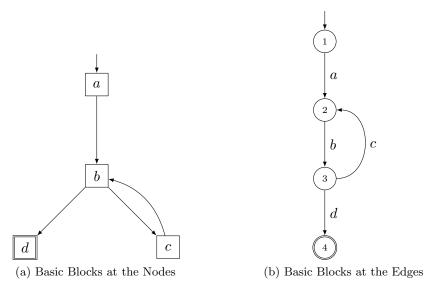

Usually CFG nodes represent basic blocks (cf. [ASU86]). Because our matrix calculus manipulates the edges, we need to have basic blocks on the edges. As usual the edges represent the transfer of control between the basic blocks. Each edge  $e \in E$  is assigned a basic block b. In this dissertation, we refer to basic blocks by edge labels as defined in the previous section. Labels out of the set  $\mathcal{L}_{S}$  refer to synchronization primitive calls. The remaining labels refer to the elements of  $\mathcal{L}_{V}$  which model basic blocks consisting of ordinary program statements, i.e., non-synchronization statements. The operations on the basic blocks are  $\cdot$ , +, and \* from the semiring defined above (cf. [Tar81]). Intuitively, the semiring operations  $\cdot$ , +, and \* model consecutive program parts, conditionals, and loops, respectively.

As an example for a control flow graph consider the pseudocode implementation of factorial depicted in Figure 2.1. Line 1 and 2 form CFG node a. Node b refers to the while condition of line 3. The lines 4 and 5 build CFG node c. Finally, CFG node d is constructed out of line 7. The corresponding CFG having the basic blocks on the nodes is presented in Figure 2.2a. Node a and d are the entry and final node, respectively, of the original CFG. In contrast to that, Figure 2.2b depicts the same example with the basic blocks at the edges. Node 1 is the entry node whereas node 4 is the final node of the transformed CFG.

#### 2.4 Semaphores

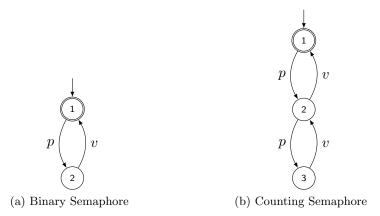

In order to model synchronization, we use synchronization primitives, e.g., semaphores which are presented in this section. During the course of this dissertation, we introduce additional synchronization primitives, namely barriers, in Chapter 7.

Semaphores [Dij65, Dijndb, Sta11] are a well-known vehicle for process synchronization, are available in all operating systems, and can be implemented efficiently. Semaphores typically implement two operations, namely p and v. Usually the operation p is used to acquire a resource, whereas v releases the resource. If the semaphore is already acquired by a thread, then the calling thread is being suspended and the thread is being added to the semaphore's first-in, first-out (FIFO) queue. After a thread releases the resource, the first thread from the queue is removed and resumes its execution. It has to be ensured

<sup>&</sup>lt;sup>1</sup>We chose the incoming edges.

Figure 2.2: CFG of Factorial

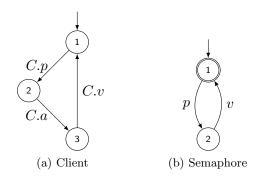

Figure 2.3: Semaphores

that both operations, namely p and v, are executed atomically. Note that semaphores are similar to mutexes. In contrast to semaphores, mutexes have an owner. This means that a locked mutex can only be unlocked by the process that locked the mutex. In this dissertation, we sometimes use this kind of freedom which semaphores give.

Similar to threads, synchronization primitives like semaphores can be represented in form of CFGs. For semaphore i the corresponding edges typically have labels such as  $p_i \in \mathcal{L}_S$  and  $v_i \in \mathcal{L}_S$ . Usually two or more distinct thread CFGs refer to the same semaphore to model synchronization.

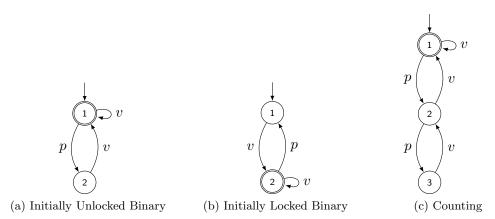

In Figure 2.3a and 2.3b a binary and a counting semaphore are depicted. The latter

Figure 2.4: Semaphores with Non-blocking v-operations

allows two threads to enter at the same time. In a similar way it is possible to construct semaphores allowing n non-blocking p-calls ( $n \in \mathbb{N}, n \ge 1$ ). Node 1 in Figure 2.3a and 2.3b is both, entry and final node.

So, for example, a thread cannot do semaphore calls in the order v followed by p when the semaphore DFA only allows a p-call before a v-call (this is the case when using the semaphore without the self-loop at node 1 as depicted in Figure 2.3a). The graph of such an erroneous program will contain a node from which the final node of that graph cannot be reached. This node is the one preceding the v-call. Such nodes can easily be found by traversing the program's graph we introduce in the course of this dissertation. Thus deadlocks of concurrent systems can be detected with little effort.

In Figure 2.4 an initially unlocked (a) and locked (b), respectively, binary and a counting semaphore (c) are depicted. The latter (like the counting semaphore in Figure 2.3b) allows two threads to enter at the same time. In contrast to the semaphores depicted in Figure 2.3, the semaphores in Figure 2.4 support multiple subsequent non-blocking v-calls. Similar to the initially locked semaphore shown in Figure 2.4b, we can construct an initially locked semaphore with potentially blocking v-operations, i.e., Figure 2.3a with entry node 2.

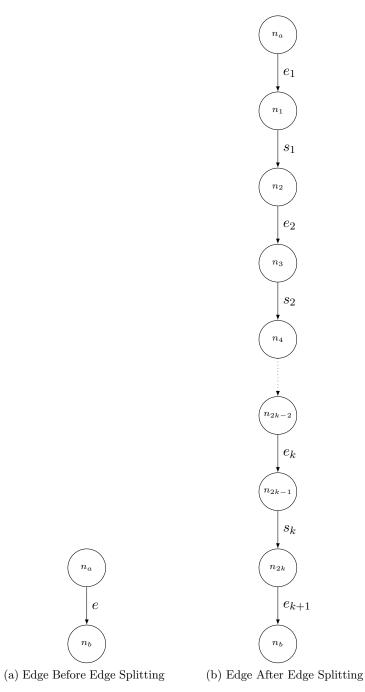

#### 2.5 Edge Splitting

As already mentioned above, we have the basic blocks on the incoming edges. A basic block consists of multiple consecutive statements without jumps. For our purpose we need a finer granularity which we achieve by splitting edges. We apply it to basic blocks containing synchronization calls and shared variables. For both, edge splitting results in a *Refined Control Flow Graph* (RCFG).

Edge splitting for calls to synchronization primitives, e.g., semaphore calls  $p_1$  and  $v_1$ , is as follows. We require that a call – referred to as  $s_i$  – has to be the only statement on the corresponding edge. In Figure 2.5, edge splitting is shown for the edge e depicted in Figure 2.5a. The edge's basic block is assumed to contain k synchronization primitive

calls. The resulting edges are presented in Figure 2.5b. The edge e is replaced by the edges  $e_1

ldots e_{k+1}$  and the nodes  $n_1

ldots n_{2k}$  are introduced. Roughly speaking, edge splitting maps a CFG edge e whose corresponding basic block contains k synchronization primitive calls to a subgraph  $o

begin{cases}

ldots n_1

ldots n_2

ldots n_2

ldots n_3

ldots n_2

ldots n_3

ldots n_4

ldots n_2

ldots n_4

l$

For shared variables, edge splitting can be done in a similar fashion. In contrast to calls to synchronization primitives, we do not require that shared variable accesses are the only statements on the corresponding edge. The remaining consecutive parts of the basic block are situated on the previous and succeeding edges, respectively. Note that edges representing a call to a synchronization primitive are not considered to access shared variables.

Let  $\mathcal{V}$  be the set of shared variables.<sup>2</sup> In addition, let each shared variable  $v \in \mathcal{V}$  be a volatile variable located in the shared memory which is accessed by two or more threads. Splitting an edge depends on the number of statements accessing shared variables in the corresponding edge (i.e. basic block). For edge e labeled by basic block b this number is being referred to as NSV(b). If NSV(b) > 1, then edge splitting has to be applied to edge e; the edge is used unchanged otherwise.

If edge splitting has to be applied to edge e which has basic block b assigned and NSV(b) = k then the basic blocks  $b_1, \ldots, b_k$  represent the subsequent parts of b in such a way that  $\forall b_i : \text{NSV}(b_i) = 1$ , where  $1 \leq i \leq k$ . Edges  $e_j$  get assigned basic block  $b_j$ , where  $1 \leq j \leq k$ . In Figure 2.6 splitting of an edge with basic block b and NSV(b) = k is depicted.

Edge splitting for shared variables is relevant for a value-sensitive analysis (such as symbolic analysis) when taking shared variables into account. This approach ensures a representation in a manner exact enough in order to allow modeling all possible context switches, i.e., interleavings. We say "exact enough" because by using basic blocks together with edge splitting, we already have coarsened the granularity compared to the statement-level. This helps to keep the generated graph model (which we define in Chapter 4) small. With a granularity on statement-level the graph model would be unnecessarily big. In addition, we do not lose any information nor accuracy for our analysis purposes.

From the used matrix calculus point of view, edge splitting ensures that it is possible to generate all necessary interleavings. Nevertheless, generating unnecessary interleavings should be prevented. When e.g. static scheduling is used, the dispatching points are usually known. If between two different shared variable accesses no dispatching is possible, then we relax the rule (i.e.  $\forall b_i : \text{NSV}(b_i) = 1$ ) above. This may lead to an coarser granularity on the RCFG-level.

<sup>&</sup>lt;sup>2</sup>As an approach for finding the set of shared variables in Ada programs we suggest [BBM06].

Figure 2.5: Edge Splitting for k Synchronization Primitive Calls

Figure 2.6: Edge Splitting for k Shared Variable Accesses

Without loss of generality, we assume that the statements in each basic block are atomic. Thus, while executing a statement, context switching is impossible. In RCFGs the finest possible granularity is at statement-level. If, according to the hardware architecture or program's semantic, atomic statements may access two or more shared variables, then we make an exception to the above rule, too, and allow two or more shared variable accesses on a single edge. Such edges have at most one of these atomic statements in their basic block and no additional statements accessing shared variables.

The effects of edge splitting for both, namely synchronization primitive calls and shared variable accesses, can be seen in the data race example given in Section 6.4. Each RCFG depicted in Figure 6.7 is constructed out of one basic block (cf. Figure 6.6).

#### 2.6 Basic Matrix Notations and Operations

In this section, we introduce basic matrix terminology, notations, and operations used in the remainder of this thesis.

A p-by-q matrix

$$M = (m_{i,j})$$

$$1 \quad 2 \quad \dots \quad q$$

$$1 \quad \begin{pmatrix} m_{1,1} & m_{1,2} & \dots & m_{1,q} \\ m_{2,1} & m_{2,2} & \ddots & \vdots \\ \vdots & \ddots & \ddots & \vdots \\ p & m_{p,1} & m_{p,2} & \dots & m_{p,q} \end{pmatrix}$$

has p rows and q columns. Thus it consists of p times q entries  $m_{i,j}$ . Note that  $m_{i,j}$ 's i and j denote its row and column, respectively, within matrix M.

We define the set of matrices  $\mathcal{M} = \{M = (m_{i,j}) \mid m_{i,j} \in \mathcal{L}\}$ . In the remaining parts of this dissertation only matrices  $M \in \mathcal{M}$  will be used. In addition let o(M) refer to the

order<sup>3</sup> of square matrix  $M \in \mathcal{M}$ . Furthermore, we will use zero matrices  $Z_n = (z_{i,j})$ , where  $\forall i, j : z_{i,j} = 0$  and  $o(Z_n) = n$ .

The identity matrix  $I_n$  of order n has ones at the main diagonal and zeros elsewhere. Thus

$$I_n = (m_{i,j}), \text{ where } m_{i,j} = \begin{cases} 1 & i = j, \\ 0 & \text{otherwise.} \end{cases}$$

By the definition above we already have  $I_1 = (1)$ . We additionally define  $I_0 = (1)$ .

Let M, N, and R be p-by-q matrices. In addition, let a be a label out of  $\mathcal{L}$ . In the following, the used indices range between  $1 \leq i \leq p$  and  $1 \leq j \leq q$ . We get  $a \cdot M$  and M + N as follows:

$$a \cdot M = a \cdot (m_{i,j}) = (r_{i,j}) = R$$

, where  $r_{i,j} = a \cdot m_{i,j}$  and  $M + N = (m_{i,j}) + (n_{i,j}) = (r_{i,j}) = R$ , where  $r_{i,j} = m_{i,j} + n_{i,j}$ .

Sometimes, we also use the transpose  $M^T$  of a p-by-q matrix M. The result is a q-by-p matrix which is defined by

$$M^T = (m_{i,j})^T = (m_{j,i}).$$

Intuitively, columns are turned into rows and vice versa.

**Definition 1 (Number of Nonzero Entries in a Matrix)** Let  $M = (m_{i,j}) \in \mathcal{M}$ . We denote the number of entries unequal to zero by  $||M|| = |\{m_{i,j} \mid m_{i,j} \neq 0\}|$ .

**Definition 2 (Sparse Matrix)** We call an n-by-n matrix M sparse if and only if  $||M|| \le c * n$ , where c is a constant independent from n.

#### 2.7 Correspondence between Matrices and Directed Graphs

There is a correspondence between matrices and graphs. In general, a directed labeled graph  $G\langle V, E, n_e \rangle$  consists of a set of labeled nodes V, a set of labeled directed edges  $E = V \times V$ , and an entry node  $n_e$ . Correspondence between directed graphs and matrices – in this context the latter are referred to as adjacency matrices – is as follows. In this dissertation, we label graph nodes simply by positive integers which reflect the row and column in the adjacency matrix. If there exists an entry  $m_{i,j} = a$  in an adjacency matrix, then a directed edge from node i to node j labeled by a exists in the corresponding directed graph. If  $m_{i,j} = 0$ , then there is no edge from node i to node j.

Because we usually work with sparse matrices, we suggest adjacency lists as an implementation for the matrices. In adjacency lists zeros are not stored explicitly. Only entries unequal to zero are stored in the lists. Compared to the approach, where all the  $o(M)^2$  matrix entries are stored explicitly, this helps to safe memory.

$<sup>^{3}</sup>$ A k-by-k matrix is known as square matrix of order k.

To keep things simple, we refer to edges, their labels, the corresponding basic blocks and the corresponding entries of the adjacency matrices synonymously. Analogously, we refer to a node, its node number, and its row and column in the corresponding matrix synonymously.

In the remainder of this dissertation, we often use the node numbers as generated by Kronecker sum, Kronecker product, or, concerning CPGs, we use the node numbers generated by our implementation.

#### 2.8 Limitations

Theoretical results such as [Ram00] state that synchronization-sensitive and context-sensitive analysis is impossible even for the simplest analysis problems. Our system model differs in that it supports subprograms only via inlining and recursions are not allowed.

"Die Grenzen meiner Sprache bedeuten die Grenzen meiner Welt."

– LUDWIG WITTGENSTEIN, Austrian-British philosopher, 1889-1951

Proposition 5.6, Tractatus Logico-Philosophicus, 1922

# Kronecker Algebra – A Matrix Calculus

"I hear and I forget.

I see and I remember.

I do and I understand."

- CONFUCIUS, Chinese teacher, politician, and philosopher, 551-479 BC

Kronecker product and Kronecker sum form the so-called Kronecker algebra. In this chapter, we define both operations, state properties, and give examples on matrix and graph/automata level. For the Kronecker sum we prove associativity and a new property which we call *Mixed Sum Rule*.

## 3.1 Kronecker Product / Zehfuss Product

"No scientific discovery is named after its original discoverer."

— Stigler's law of eponymy, 1980

Kronecker product allows to model synchronization [BK02, Pla85]. In this section, we state a definition, give examples, and present properties used in this thesis.

**Definition 3 (Kronecker Product)** Given an m-by-n matrix A and a p-by-q matrix B, their Kronecker product  $A \otimes B$  is an mp-by-nq block matrix defined by

$$A \otimes B = \begin{pmatrix} a_{1,1} \cdot B & \cdots & a_{1,n} \cdot B \\ \vdots & \ddots & \vdots \\ a_{m,1} \cdot B & \cdots & a_{m,n} \cdot B \end{pmatrix}.$$

As stated in [Mil11] the Kronecker product is also being referred to as Zehfuss product or direct product of matrices. Knuth notes in [Knu11] that Kronecker never published anything about it. Zehfuss was actually the first publishing it in the 19th century [Zeh58]. Following Stigler's law of eponymy, Kronecker product is usually not called Zehfuss product.

In terms of formal automata, the Kronecker product calculates the simultaneous executions of the input matrices. Thus, the operation  $\otimes$  can be used to synchronize automata. In the following, we give an example.

## 3.1.1 Examples

## Example 1

For this example, we use the following matrices A and B of order 2 and 3, respectively:

$$A = \begin{pmatrix} a_{1,1} & a_{1,2} \\ a_{2,1} & a_{2,2} \end{pmatrix} \text{ and } B = \begin{pmatrix} b_{1,1} & b_{1,2} & b_{1,3} \\ b_{2,1} & b_{2,2} & b_{2,3} \\ b_{3,1} & b_{3,2} & b_{3,3} \end{pmatrix}.$$

The Kronecker product  $A \otimes B$  is a matrix of order 6 given by

$$A\otimes B=\begin{pmatrix} a_{1,1}b_{1,1} & a_{1,1}b_{1,2} & a_{1,1}b_{1,3} & a_{1,2}b_{1,1} & a_{1,2}b_{1,2} & a_{1,2}b_{1,3}\\ a_{1,1}b_{2,1} & a_{1,1}b_{2,2} & a_{1,1}b_{2,3} & a_{1,2}b_{2,1} & a_{1,2}b_{2,2} & a_{1,2}b_{2,3}\\ a_{1,1}b_{3,1} & a_{1,1}b_{3,2} & a_{1,1}b_{3,3} & a_{1,2}b_{3,1} & a_{1,2}b_{3,2} & a_{1,2}b_{3,3}\\ a_{2,1}b_{1,1} & a_{2,1}b_{1,2} & a_{2,1}b_{1,3} & a_{2,2}b_{1,1} & a_{2,2}b_{1,2} & a_{2,2}b_{1,3}\\ a_{2,1}b_{2,1} & a_{2,1}b_{2,2} & a_{2,1}b_{2,3} & a_{2,2}b_{2,1} & a_{2,2}b_{2,2} & a_{2,2}b_{2,3}\\ a_{2,1}b_{3,1} & a_{2,1}b_{3,2} & a_{2,1}b_{3,3} & a_{2,2}b_{3,1} & a_{2,2}b_{3,2} & a_{2,2}b_{3,3} \end{pmatrix}$$

## Example 2

In this example, we show how we calculate all possible simultaneous executions of the two automata represented by the matrices

$$C = \begin{pmatrix} a & b \\ 0 & 0 \end{pmatrix} \text{ and } D = \begin{pmatrix} 0 & a \\ 0 & b \end{pmatrix}.$$

The corresponding automata are depicted in Figure 3.1a and 3.1b, respectively. The Kronecker product  $C \otimes D$  is given by

$$C \otimes D = \begin{pmatrix} 0 & aa & 0 & ba \\ 0 & ab & 0 & bb \\ 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \end{pmatrix}.$$

<sup>&</sup>lt;sup>1</sup>Zehfuss proved that  $\det(A \otimes B) = \det^n(A) \det^m(B)$ , if A and B are matrices of order m and n, respectively, and entries from the domain of real numbers.

In Figure 3.1c the result on automata level is depicted. For each edge in the resulting automaton, actually two edges, i.e. one edge of each of the two input automata, are executed. The first label represents an edge of the first input automata, whereas the second label refers to an edge of the second input automaton. How we determine entry and final nodes is described in Chapter 4. We use this notion here in order to have a complete presentation from an automata point of view.

Figure 3.1: Simultaneous Executions via Kronecker Product  $C \otimes D$

## Example 3

For this example, we use the matrices

$$E = \begin{pmatrix} 0 & a & 0 & d \\ 0 & 0 & b & 0 \\ 0 & 0 & 0 & c \\ 0 & 0 & 0 & 0 \end{pmatrix} \text{ and } F = \begin{pmatrix} 0 & e & 0 & 0 \\ 0 & 0 & f & 0 \\ 0 & 0 & 0 & g \\ 0 & 0 & 0 & 0 \end{pmatrix}.$$

The corresponding graphs are depicted in Figure 3.2a and 3.2b, respectively. For a concise presentation of the 16-by-16 matrix of the Kronecker product  $E \otimes F$  we introduce the helper matrices  $H_1$ ,  $H_2$ ,  $H_3$ , and  $H_4$  as follows:

$$H_{1} = \begin{pmatrix} 0 & ae & 0 & 0 \\ 0 & 0 & af & 0 \\ 0 & 0 & 0 & ag \\ 0 & 0 & 0 & 0 \end{pmatrix}, \qquad H_{2} = \begin{pmatrix} 0 & de & 0 & 0 \\ 0 & 0 & df & 0 \\ 0 & 0 & 0 & dg \\ 0 & 0 & 0 & 0 \end{pmatrix},$$

$$H_{3} = \begin{pmatrix} 0 & be & 0 & 0 \\ 0 & 0 & bf & 0 \\ 0 & 0 & 0 & bg \\ 0 & 0 & 0 & 0 \end{pmatrix}, and \qquad H_{4} = \begin{pmatrix} 0 & ce & 0 & 0 \\ 0 & 0 & cf & 0 \\ 0 & 0 & 0 & cg \\ 0 & 0 & 0 & 0 \end{pmatrix}.$$

Then we get the resulting matrix

$$E \otimes F = \begin{pmatrix} Z_4 & H_1 & Z_4 & H_2 \\ Z_4 & Z_4 & H_3 & Z_4 \\ Z_4 & Z_4 & Z_4 & H_4 \\ Z_4 & Z_4 & Z_4 & Z_4 \end{pmatrix}.$$

The corresponding graph is depicted in Figure 3.2c. Starting from the entry node 1 not all nodes are reachable. In the reachable part only the path  $1 \to 6 \to 11 \to 16$  leads to the final node 16. Choosing the edge  $1 \to 14$  a further simultaneous execution is impossible.

## 3.1.2 Properties

In the following, we list some basic properties of the Kronecker product. Let A, B, C, and D be matrices. Kronecker product is non-commutative because in general

$$A \otimes B \neq B \otimes A$$

.

It is permutation equivalent because there exist permutation matrices P and Q such that  $A \otimes B = P(B \otimes A)Q$  (cf. [Gra81, Wei62]). If A and B are square matrices, then  $A \otimes B$  and  $B \otimes A$  are even permutation similar, i.e.,  $P = Q^T$ . It is associative [Gra81, Pla85] as

$$A \otimes (B \otimes C) = (A \otimes B) \otimes C. \tag{3.1}$$

In addition, Kronecker product distributes over + [Gra81], i.e.,

$$A \otimes (B+C) = A \otimes B + A \otimes C, \tag{3.2}$$

$$(A+B) \otimes C = A \otimes C + B \otimes C. \tag{3.3}$$

Hence for example  $(A + B) \otimes (C + D) = A \otimes C + B \otimes C + A \otimes D + B \otimes D$ .

Properties concerning connectedness of the corresponding undirected and directed graphs can be found in [Wei62] and [McA63, HT66], respectively. A recent publication about connectedness of the resulting graphs is [HIK11]. Additional properties and proofs can be found in [Bel97, Gra81, Dav81, Hur94].

### 3.2 Kronecker Sum

In this section we define the Kronecker sum of matrices, give examples, and state some important properties. We also relate the operation to Cartesian product graphs.

**Definition 4 (Kronecker Sum)** Given a matrix A of order m and a matrix B of order n, their Kronecker sum  $A \oplus B$  is a matrix of order mn defined by

$$A \oplus B = A \otimes I_n + I_m \otimes B,$$

where  $I_m$  and  $I_n$  denote identity matrices<sup>2</sup> of order m and n, respectively.

This operation must not be confused with the direct sum of matrices, group direct product or direct product of modules for which the symbol  $\oplus$  is used too.

<sup>&</sup>lt;sup>2</sup>Identity matrix  $I_n$  is an n-by-n matrix with ones on the main diagonal and zeros elsewhere.

Figure 3.2: Simultaneous Executions via Kronecker product  $E\otimes F$

## 3.2.1 Examples

In this section we present two Kronecker sum examples.

## Example 4

In this example, we again use the matrices A and B from Example 1. The Kronecker sum  $A \oplus B$  is given by

$$A \otimes I_3 + I_2 \otimes B = \\ \begin{pmatrix} a_{1,1} & a_{1,2} \\ a_{2,1} & a_{2,2} \end{pmatrix} \otimes \begin{pmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{pmatrix} + \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix} \otimes \begin{pmatrix} b_{1,1} & b_{1,2} & b_{1,3} \\ b_{2,1} & b_{2,2} & b_{2,3} \\ b_{3,1} & b_{3,2} & b_{3,3} \end{pmatrix} = \\ \begin{pmatrix} a_{1,1} & 0 & 0 & a_{1,2} & 0 & 0 \\ 0 & a_{1,1} & 0 & 0 & a_{1,2} & 0 \\ 0 & 0 & a_{1,1} & 0 & 0 & a_{1,2} & 0 \\ a_{2,1} & 0 & 0 & a_{2,2} & 0 & 0 \\ 0 & 0 & a_{2,1} & 0 & 0 & a_{2,2} & 0 \\ 0 & 0 & 0 & a_{2,1} & 0 & 0 & a_{2,2} \end{pmatrix} + \begin{pmatrix} b_{1,1} & b_{1,2} & b_{1,3} & 0 & 0 & 0 \\ b_{2,1} & b_{2,2} & b_{2,3} & 0 & 0 & 0 \\ 0 & 0 & 0 & b_{1,1} & b_{1,2} & b_{1,3} \\ 0 & 0 & 0 & b_{2,1} & b_{2,2} & b_{2,3} \\ 0 & 0 & 0 & b_{3,1} & b_{3,2} & b_{3,3} \end{pmatrix} = \\ \begin{pmatrix} a_{1,1} + b_{1,1} & b_{1,2} & b_{1,3} & a_{1,2} & 0 & 0 \\ b_{2,1} & a_{1,1} + b_{2,2} & b_{2,3} & 0 & a_{1,2} & 0 \\ b_{3,1} & b_{3,2} & a_{1,1} + b_{3,3} & 0 & 0 & a_{1,2} \\ a_{2,1} & 0 & 0 & a_{2,1} & 0 & b_{2,1} & a_{2,2} + b_{2,2} & b_{2,3} \\ 0 & 0 & a_{2,1} & 0 & b_{2,1} & a_{2,2} + b_{2,2} & b_{2,3} \\ 0 & 0 & a_{2,1} & 0 & b_{2,1} & a_{2,2} + b_{2,2} & b_{2,3} \\ 0 & 0 & a_{2,1} & 0 & b_{2,1} & a_{2,2} + b_{2,2} & b_{2,3} \\ 0 & 0 & a_{2,1} & 0 & b_{2,1} & a_{2,2} + b_{2,2} & b_{2,3} \\ 0 & 0 & 0 & a_{2,1} & b_{3,1} & b_{3,2} & a_{2,2} + b_{3,3} \end{pmatrix}.$$

## Example 5

In this example, we use the matrices

$$C = \begin{pmatrix} 0 & a & 0 \\ b & 0 & c \\ 0 & 0 & 0 \end{pmatrix} \text{ and } D = \begin{pmatrix} 0 & d \\ 0 & 0 \end{pmatrix}.$$

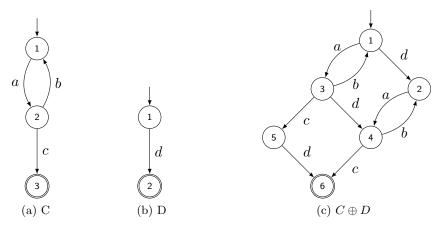

The corresponding graphs are depicted in Figure 3.3a and 3.3b. The matrix  $C \oplus D$  can be calculated as follows.

Figure 3.3: The Graphs of C, D, and  $C \oplus D$

The corresponding graph is depicted in Figure 3.3c.

## 3.2.2 Properties

In the following, we list and proof some properties of the Kronecker sum of matrices A, B, and C. The Kronecker sum is non-commutative because for element-wise comparison in general  $A \oplus B \neq B \oplus A$ . However, it essentially commutes because from a graph point of view, the graphs represented by matrices  $A \oplus B$  and  $B \oplus A$  are structurally isomorphic, i.e., starting from the entry node to the final node the same paths in terms of edge labels are possible. Only the node numbers may be different in  $A \oplus B$  compared to  $B \oplus A$ . Both matrices, namely  $A \oplus B$  and  $B \oplus A$ , consist of the same number of entries unequal to 0 and have the same order.

Now we state a property of the Kronecker sum which we call *Mixed Sum Rule*.

**Lemma 1** Let the matrices A and C have order m and B and D have order n. Then we call

$$(A \oplus B) + (C \oplus D) = (A + C) \oplus (B + D)$$

the Mixed Sum Rule.

**Proof 1** By using Equations (3.2) and (3.3) and Definition 4 we get

$$(A \oplus B) + (C \oplus D) = A \otimes I_n + I_m \otimes B + C \otimes I_n + I_m \otimes D$$

$$= (A + C) \otimes I_n + I_m \otimes (B + D)$$

$$= (A + C) \oplus (B + D).$$

For example let the matrices A and B be written as  $A = \sum_{i \in I} A_i$  and  $B = \sum_{j \in J} B_j$ , respectively. In addition, let the sets I and J have the same number of elements, i.e., |I| = |J|. By using the mixed sum rule we can write  $A \oplus B = \sum_{i \in I, j \in J} A_i \oplus B_j$ .

We will frequently use the *Mixed Sum Rule* from now on without further notice. Kronecker sum is also associative, as  $(A \oplus B) \oplus C$  and  $A \oplus (B \oplus C)$  are equal.

Lemma 2 Kronecker sum is associative.

**Proof 2** In the following, we will use  $I_m \otimes I_n = I_{m.n}$ . Note that Z denotes zero matrices. We have

$$A \oplus (B \oplus C) = A \oplus (B \otimes I_{o(C)} + I_{o(B)} \otimes C)$$

$$\{adding \ Z_{o(A)}\} = (A + Z_{o(A)}) \oplus (B \otimes I_{o(C)} + I_{o(B)} \otimes C)$$

$$\{Lemma \ 1\} = (A \oplus (B \otimes I_{o(C)})) + (Z_{o(A)} \oplus (I_{o(B)} \otimes C))$$

$$\{Equation \ (3.1), \ Definition \ 4\} = (A \oplus (B \otimes I_{o(C)})) + I_{o(A)} \otimes I_{o(B)} \otimes C$$

$$\{associativity \ of \ +, \ Definition \ 4\} = A \otimes I_{o(B).o(C)} + I_{o(A)} \otimes B \otimes I_{o(C)} + I_{o(A).o(B)} \otimes C$$

$$\{commutativity \ of \ +\} = A \otimes I_{o(B)} \otimes I_{o(C)} + I_{o(A).o(B)} \otimes C + I_{o(A)} \otimes B \otimes I_{o(C)}$$

$$\{Definition \ 4\} = ((A \otimes I_{o(B)}) \oplus C) + I_{o(A)} \otimes B \otimes I_{o(C)}$$

$$\{Definition \ 4\} = ((A \otimes I_{o(B)}) \oplus C) + ((I_{o(A)} \otimes B) \oplus Z_{o(C)}$$

$$\{Lemma \ 1\} = (A \otimes I_{o(B)} + I_{o(A)} \otimes B) \oplus (C + Z_{o(C)})$$

$$\{remove \ Z_{o(C)}\} = (A \otimes I_{o(B)} + I_{o(A)} \otimes B) \oplus C$$

$$\{Definition \ 4\} = (A \oplus B) \oplus C.$$

The associativity properties of the operations  $\otimes$  and  $\oplus$  imply that the n-fold operations

$$\bigotimes_{i=1}^{k} A_i \quad \text{and} \quad \bigoplus_{i=1}^{k} A_i$$

are well defined. Let  $n_i$  denote the order of matrix  $A_i$  and  $I_n$  the identity matrix of order n. Then we can write the n-fold Kronecker sum for k matrices  $A_i$ , where  $1 \le i \le k$  similar to Buchholz and Kemper [BK02] and Ciardo et al. [CM99] as

$$\bigoplus_{i=1}^k A_i = \sum_{i=1}^k I_{n_1} \otimes \cdots \otimes I_{n_{i-1}} \otimes A_i \otimes I_{n_{i+1}} \otimes \cdots \otimes I_{n_k} = \sum_{i=1}^k I_{i-1} \otimes A_i \otimes I \prod_{j=i+1}^k n_j.$$

Finally, note that the Kronecker sum of adjacency matrices generates only self-loops out of self-loops in the input matrices. This can easily be seen because on the main diagonal, the Kronecker sum contains only entries of the main diagonal of the two input matrices. A self-loop at node i is defined as an entry  $m_{i,i} \neq 0$  in the corresponding adjacency matrix M.

Additional properties of the Kronecker sum can be found in [PA91].

Figure 3.4: A Simple Cartesian Product Graph  $(C \oplus D)$

## 3.2.3 Relation of Kronecker Sum to Cartesian Product Graph

By calculating the Kronecker sum of the adjacency matrices of two graphs  $G_1$  and  $G_2$ , the adjacency matrix of the Cartesian product graph [IKR08, HIK11] of  $G_1$  and  $G_2$  is computed (cf. [Knu11]).

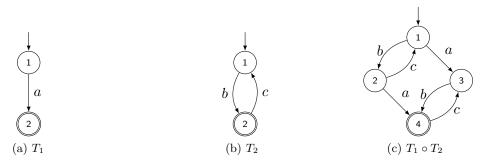

The Kronecker sum calculates all possible interleavings of two concurrently executing automata (see e.g. [Küs91] for a proof; in that context the Kronecker sum is referred to as Hurwitz product) even for general graphs, e.g., CFGs including conditionals and loops. In Chapter 4 we calculate the maximum number of nodes and edges in such Cartesian graphs, whereas in the Appendix A it is shown how the number of interleavings can be calculated for an arbitrary number of threads and their statements. The following example illustrates interleavings of two threads and how the Kronecker sum handles it.

**Example 6** Let the matrices C and D be defined as follows:

$$C = \begin{pmatrix} 0 & a & 0 \\ 0 & 0 & b \\ 0 & 0 & 0 \end{pmatrix} \qquad D = \begin{pmatrix} 0 & c & 0 \\ 0 & 0 & d \\ 0 & 0 & 0 \end{pmatrix}.$$

The graph corresponding to matrix C is depicted in Figure 3.4a, whereas the graph of matrix D is shown in Figure 3.4b. The regular expressions associated with the CFGs are  $a \cdot b$  and  $c \cdot d$ , respectively. All possible interleavings by executing C and D applying

an interleavings semantics are shown in Figure 3.4c. The adjacency matrix  $C \oplus D$  is calculated by

In Figure 3.4d the graph represented by the adjacency matrix  $C \oplus D$  is depicted. It is easy to see that all possible interleavings are generated.

As a concluding remark of this chapter, we note that Kronecker algebra is a special case of tensor algebra. The tensor product of matrices is the Kronecker product and the tensor sum of matrices is the Kronecker sum of the matrices (cf. [Pla85]).

## Concurrent Program Graphs

"A computer program is organized complexity."

- EDSGER WYBE DIJKSTRA, Dutch computer scientist and ACM Turing Award winner 1972, 1930-2002

In this chapter, we introduce *concurrent program graphs* (CPGs) as a data structure modeling concurrent systems. CPGs play a similar role for concurrent systems as control flow graphs (CFGs) do for sequential programs. They describe, e.g., all possible interleavings and incorporate synchronization. In the course of this dissertation, we will see that CPGs can be used as a basis for analyses of issues, e.g., deadlocks, inherent in concurrent programs.

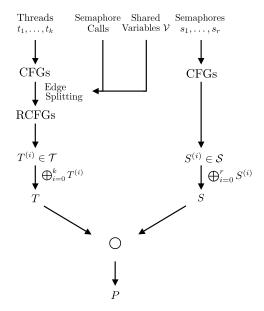

Our system model consists of a finite number of threads and semaphores. Both, threads and semaphores, are represented by Control Flow Graphs (CFGs). Edge splitting has to be applied to the edges of threads which results in Refined CFGs (RCFGs), whereas the CFGs of semaphores are RCFGs without modification. The RCFGs are stored in form of adjacency matrices. The matrices have entries which are referred to as labels  $l \in \mathcal{L}$  as defined in Section 2.1. Let  $\mathcal{S}$  and  $\mathcal{T}$  be the sets of adjacency matrices representing RCFGs of semaphores and threads, respectively. The matrices are manipulated by using conventional Kronecker algebra operations together with some extensions which we define in the course of this chapter. Similar to [BK02] we describe synchronization by Kronecker products and thread interleavings by Kronecker sums.

Formally, the system model consists of the tuple  $\langle \mathcal{T}, \mathcal{S}, \mathcal{L} \rangle$ , where

- $\bullet$   $\mathcal{T}$  is the set of RCFG adjacency matrices describing threads,

- S refers to the set of RCFG adjacency matrices describing semaphores, and

Figure 4.1: Overview

•  $\mathcal{L}$  denotes the set of labels out of the semiring defined in Section 2.1. The labels (or matrix entries) of the *i*th thread's adjacency matrix  $T^{(i)} \in \mathcal{T}$  are elements of  $\mathcal{L}$ , whereas the labels (or matrix entries) of the *j*th synchronization primitive's adjacency matrix  $S^{(j)} \in \mathcal{S}$  are elements of  $\mathcal{L}_{S}$ .

A concurrent program graph (CPG) is a graph  $C = \langle V, E, n_e, V_f \rangle$  with a set of nodes V, a set of directed edges  $E \subseteq V \times V$ , a so-called entry node  $n_e \in V$  and a set of final nodes  $V_f \subseteq V$ . The sets V and E are constructed out of the elements of  $\langle \mathcal{T}, \mathcal{S}, \mathcal{L} \rangle$ . Details on how we generate the sets V and E follow in the next sections. Similar to RCFGs, the edges of CPGs are labeled by  $l \in \mathcal{L}$ .

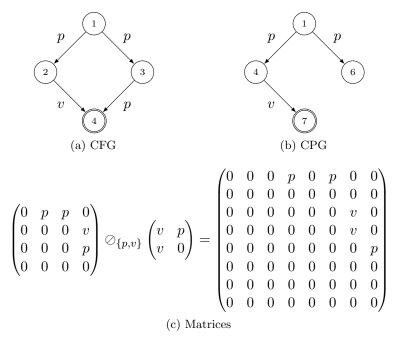

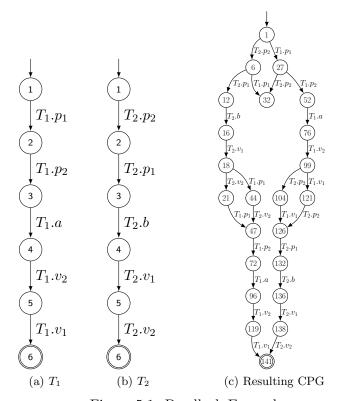

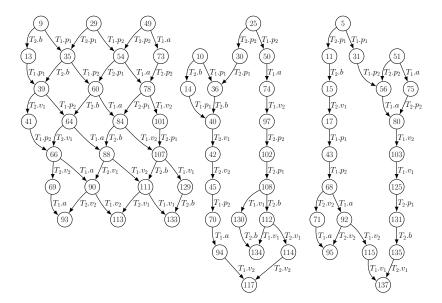

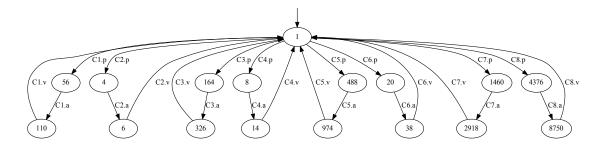

In Figure 4.1 an overview of how we generate a concurrent program's adjacency matrix is given. As described in Section 2.5, the semaphore calls and the shared variable information may be used as input for edge splitting. As an output, we get RCFGs represented by the matrices  $T^{(i)}$ . The matrices T and S are the interleaved threads and semaphores, respectively. The ring operator  $\circ$  is used to generate the matrix P out of T and S. The matrix P statically represents the concurrent programm consisting of k threads and k semaphores. The underlying graph is the CPG. In the following, we define the k-operation used in Figure 4.1.

We will see that for concurrent programs containing synchronization only a part of the graph represented by the full matrix is reachable. To this part of the CPG we refer to as reachable CPG (RCPG). Because our implementation only generates RCPGs, we usually mean the reachable part (RCPG) when referring to a CPG. The full matrix is only interesting when, e.g., arguing about worst-case scenarios regarding the number of nodes.

The remainder of this chapter is organized as follows. In Section 4.1 we show how the matrix of a concurrent program can be generated from a mathematical point of view. How we determine entry and final nodes of CPGs is discussed in 4.2. We prove that CPGs correctly model synchronization in Section 4.3. In Section 4.4 it is shown how unreachable parts arise from synchronization between threads. We prove important properties in Section 4.5. In Section 4.6 we extend the Kronecker algebra with our selective Kronecker product and show how the definitions of Section 4.1 can be simplified. Section 4.7 is devoted to a lazy implementation of our extended Kronecker algebra. Finally, in Section 4.8 it is proven that in general CPGs are irreducible.

## 4.1 Generating a Concurrent Program's Matrix

Let  $T^{(i)} \in \mathcal{T}$  and  $S^{(i)} \in \mathcal{S}$  refer to the matrices representing thread i and synchronization primitive i, respectively. Let  $M = (m_{i,j}) \in \mathcal{M}$ . In addition, we define the matrix  $M_l$  with entries equal to l and zeros elsewhere:

$$M_l = (m_{l;i,j}), \text{ where } m_{l;i,j} = \begin{cases} l & \text{if } m_{i,j} = l, \\ 0 & \text{otherwise.} \end{cases}$$

We obtain the matrix T representing k interleaved threads by

$$T = \bigoplus_{i=1}^{k} T^{(i)}$$

, where  $T^{(i)} \in \mathcal{T}$ .

According to Figure 2.3, we have for binary semaphore i and counting semaphore j the following adjacency matrix of order two and three, respectively.

$$S^{(i)} = \begin{pmatrix} 0 & p_i \\ v_i & 0 \end{pmatrix} \text{ and } S^{(j)} = \begin{pmatrix} 0 & p_j & 0 \\ v_j & 0 & p_j \\ 0 & v_j & 0 \end{pmatrix}$$

In a similar fashion we can model counting semaphores of higher order.

The matrix S representing r interleaved synchronization primitives is given by

$$S = \bigoplus_{i=1}^{r} S^{(i)}$$

, where  $S^{(i)} \in \mathcal{S}$ .

The adjacency matrix representing program  $\mathcal{P}$  referred to as P is defined as

$$P = T \circ S = \sum_{l \in \mathcal{L}_{S}} (T_{l} \otimes S_{l}) + \sum_{l \in \mathcal{L}_{V}} (T_{l} \oplus S_{l}).$$

(4.1)

When calculating the left term of Equation 4.1, the Kronecker product exclusively operates on labels  $s_x \in \mathcal{L}_S$ , thus on labels referring to synchronization primitive calls. In the resulting matrix, we let the Kronecker product generate only entries consisting of two equal and concatenated labels  $s_x \cdot s_x$  and replace it with the single label  $s_x$ . This rule means that, e.g., for all  $v_x$  and  $p_x \in \mathcal{L}_S$ :

- $v_x \cdot v_x$  is replaced by  $v_x$  and

- $p_x \cdot p_x$  is replaced by  $p_x$ .

Note that, during the evaluation of the Kronecker product, all other combinations, e.g.,  $v_x \cdot p_x$  and  $v_x \cdot v_y$ , where  $x \neq y$  will not happen by definition because both input matrices are filtered such that both contain only entries of the same label. In Subsection 4.6, we describe how the  $\circ$ -operation can be implemented efficiently and how we get rid of this rather unaesthetic replacement.

## 4.2 Determining Entry and Final Nodes of CPGs

Assuming, without loss of generality, that each thread has an entry node with index 1, the entry node of the generated CPG has index 1, too.

When a program uses only binary semaphores as shown in Figure 2.3a, then the program's final node can be calculated as follows. If the r semaphores have an entry and a final node 1 and each thread i of k threads has one final node  $n_i$  and  $n_i$  is the order of the corresponding adjacency matrix of thread i (thus thread i's final node has the highest row/column number<sup>1</sup>), then the final node of the resulting CPG has final node

$$\prod_{i=1}^{k} n_i \cdot 2^r - 2^r + 1. \tag{4.2}$$

In general, a thread's CPG may have several final nodes and different types of synchronization primitives, e.g., semaphores and/or the barrier synchronization construct introduced below in Chapter 7. For these cases the following formula can be used to determine the final nodes. We refer to a node without outgoing edges as a sink node. Each sink node appears as a zero line in the corresponding adjacency matrix. A CPG's final node may also be a sink node (if the program terminates). However, CPG sink nodes and final nodes can be distinguished as follows. We use a vector determining the final nodes of thread i, namely  $F^{(i)}$ . In addition, vector  $G^{(j)}$  determines the final node of the synchronization primitive j. Both have ones at places q, when node q is a final node, zeros elsewhere. Then the vector

$$\bigotimes_{i=1}^{k} F^{(i)} \otimes \bigotimes_{j=1}^{r} G^{(j)} \tag{4.3}$$