# Negative Voltage Fault Injection Attacks on Microcontrollers

#### **DIPLOMARBEIT**

zur Erlangung des akademischen Grades

### **Diplom-Ingenieur**

im Rahmen des Studiums

#### **Hardware and Software Security**

eingereicht von

Christian Kudera, BSc.

Matrikelnummer 0926721

| an der Fakultät für Informatik  |

|---------------------------------|

| der Technischen Universität Wie |

Betreuung: Ao.Univ.Prof. Dipl.-Ing. Dr.techn. Wolfgang Kastner Mitwirkung: Dipl.-Ing. Dr.techn. Markus Kammerstetter, BSc.

| Wien, 20. Februar 2018 |                  |                  |

|------------------------|------------------|------------------|

|                        | Christian Kudera | Wolfgang Kastner |

|                        |                  |                  |

# Negative Voltage Fault Injection Attacks on Microcontrollers

### **DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

### **Diplom-Ingenieur**

in

**Hardware and Software Security**

by

Christian Kudera, BSc.

Registration Number 0926721

to the Faculty of Informatics

| to the raddity of information                                     |                                                             |                  |

|-------------------------------------------------------------------|-------------------------------------------------------------|------------------|

| at the TU Wien                                                    |                                                             |                  |

| Advisor: Ao.Univ.Prof. DiplIn<br>Assistance: DiplIng. Dr.techn. M | g. Dr.techn. Wolfgang Kastner<br>Markus Kammerstetter, BSc. |                  |

| Vienna, 20 <sup>th</sup> February, 2018                           |                                                             |                  |

| •                                                                 | Christian Kudera                                            | Wolfgang Kastner |

# Erklärung zur Verfassung der Arbeit

| Christian | Kude  | ra, BS | Sc.  |

|-----------|-------|--------|------|

| Altgasse  | 3/24, | 1130   | Wien |

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

| Wien, 20. Februar 2018 |                  |

|------------------------|------------------|

| ·                      | Christian Kudera |

## Danksagung

Ganz besonders möchte ich Herrn Prof. Wolfgang Kastner für die Betreuung und die Möglichkeit zur Erstellung der Arbeit danken.

Ein besonderer Dank gilt meinen Freunden und Kollegen am Vienna Seclab. Allen voran Dr. Markus Kammerstetter, der mich bei der Erstellung der Arbeit maßgeblich begleitet hat und mir immer mit Rat zur Seite stand. Daniel Burian, Markus Müllner und Viktor Ullmann, die immer ein offenes Ohr für meine Probleme hatten und mich mit viel Geduld unterstützt haben.

Ein großer Dank gebührt Daniel A. Maierhofer, der mit seinem Fachwissen im Bereich der Elektrotechnik eine große Unterstützung im analogen Schaltungsdesign war.

Der größte Dank gebührt aber meinen Eltern Edith und Paul Kudera, die mich von früher Kindheit an bei allen meinen Vorhaben unterstützt und begleitet haben.

# Acknowledgements

I would particularly like to thank Prof. Wolfgang Kastner for the support and the opportunity to create this master thesis.

Special thanks to my friends and colleagues at the Vienna Seclab. Above all, Dr. Markus Kammerstetter, who was instrumental in the creation of the work and was always on hand with advice. Daniel Burian, Markus Müllner and Viktor Ullmann, who always had an open ear for my problems and supported me with a lot of patience.

Many thanks go to Daniel A. Maierhofer, who was a great supporter of analogue circuit design with his expertise in the field of electrical engineering.

The biggest thanks deserve my parents Edith and Paul Kudera, who have supported and accompanied me since my early childhood.

# Kurzfassung

Fault Angriffe sind eine wohl bekannte Angriffsform im Bereich der Hardware Security. Eine verbreitete Art der Fault Injection ist das kurzfristige Variieren der Versorgungsspannung, wodurch ein dafür anfälliger Prozessor Instruktionen falsch interpretiert oder überspringt. Glücklicherweise erkennen immer mehr Hersteller von Mikrocontrollern die Wichtigkeit von gehärteter Hardware und implementieren Gegenmaßnahmen gegen Fault Angriffe. In dieser Arbeit wird eine neue Methode der Fault Injection Angriffe vorgestellt. Während die Spannungsversorgung bei herkömmlichen Angriffen lediglich in Richtung GND gezogen wird, wird bei der neuen Methode auch der negative Spannungsbereich ausgenutzt. Die Hypothese dieser Arbeit ist, dass dadurch kürzere Glitches und eine schnellere kapazitive Entladung erreicht werden. Durch die Nutzung von negativen Spannungen wird eine höhere Flankensteilheit erwartet, da Schaltungsimplementierungen innerhalb und außerhalb von Mikrocontrollern schneller entladen werden können. Im Rahmen der Arbeit wurde ein Prototyp für die neue Methode implementiert und evaluiert, um diese Hypothese zu überprüfen. Die Ergebisse zeigen, dass insbesondere in Gegenwart von höheren kapazitiven Lasten Fault Angriffe nicht nur vereinfacht, sondern überhaupt erst ermöglicht werden. Gegenüber klassischen Angriffen konnten zudem kürzere Glitches erreicht werden, sodass auch Controller mit höheren Taktraten angegriffen werden können.

## Abstract

Fault attacks are a well known physical attack type in the area of hardware security. A common fault injection technique is a short term variation of the supply voltage causing a vulnerable processor to misinterpret or skip instructions. Fortunately, an increasing number of microcontroller manufacturers recognize the importance of hardened hardware and implement countermeasures against fault attacks into their products. In this work, we present a new fault injection attack method. While conventional attacks pull the power supply rail to GND, in the new method we pull into the negative voltage supply range instead. The hypothesis of this work is that negative voltage fault injection attacks provide advantages over their conventional counterparts with respect to shorter glitch durations in presence of capacitive charges. Utilizing negative voltage during the generation of a fault, we expect higher slew rates due to faster discharging of the circuit implementations outside and within microcontrollers. Within this work, we implemented and evaluated a negative voltage fault injection prototype to test this hypothesis. The results show that especially in presence of higher capacitive loads, fault injection attacks are not only simplified, but they become feasible in the first place. In contrast to classical attacks, shorter glitches were achieved opening the attack vector even to controllers with higher clock rates.

# Contents

| K            | urzfa | ssung       |                                          | xi   |

|--------------|-------|-------------|------------------------------------------|------|

| A            | bstra | ıct         |                                          | xiii |

| $\mathbf{C}$ | onter | $_{ m nts}$ |                                          | xv   |

| 1            | Intr  | oduct       | ion                                      | 1    |

|              | 1.1   | Motiv       | ration                                   | . 1  |

|              | 1.2   | State       | of the Art                               | . 2  |

|              | 1.3   | Proble      | em Statement                             | . 2  |

|              | 1.4   | Metho       | $\operatorname{odology}$                 | . 3  |

|              | 1.5   | Outlin      | ne                                       | . 3  |

| <b>2</b>     | Mic   | rocon       | trollers                                 | 5    |

|              | 2.1   | Overv       | <i>r</i> iew                             |      |

|              | 2.2   | Semic       | conductors                               | . 5  |

|              |       | 2.2.1       | MOSFET                                   |      |

|              |       | 2.2.2       | Floating-Gate MOSFET                     | . 6  |

|              |       | 2.2.3       | CMOS                                     | . 7  |

|              | 2.3   | Comp        | onents                                   | . 8  |

|              |       | 2.3.1       | Processor Core                           | . 8  |

|              |       | 2.3.2       | Memory                                   | . 17 |

|              |       | 2.3.3       | Other Features                           | . 20 |

|              | 2.4   | Archit      | tectures                                 |      |

|              |       | 2.4.1       | Complexity of Instruction Set            |      |

|              |       | 2.4.2       | Linkage of the Processor and Data Memory |      |

|              | 2.5   | Softwa      | are Development                          |      |

|              |       | 2.5.1       | Programming                              |      |

|              |       | 2.5.2       | Download                                 |      |

|              |       | 2.5.3       | Debugging                                |      |

|              | 2.6   | Protec      | ction Mechanisms                         | . 24 |

| 3            | Fau   | lt Inje     | ection Attacks                           | 27   |

|              | 3.1   | Clock       | Glitching                                | . 28 |

|                                             | 3.2                                      | Voltage Glitching                                            | 28        |  |  |  |

|---------------------------------------------|------------------------------------------|--------------------------------------------------------------|-----------|--|--|--|

| 4                                           | Negative Voltage Fault Injection Attacks |                                                              |           |  |  |  |

|                                             | 4.1                                      | Basic Terms of Voltage Fault Injection Attacks               | 31        |  |  |  |

|                                             | 4.2                                      | Limitations of Conventional Voltage Fault Injection Attacks  | 33        |  |  |  |

|                                             | 4.3                                      | Expected Results of Negative Voltage Fault Injection Attacks | 35        |  |  |  |

| 5 Negative Voltage Fault Injection Hardware |                                          |                                                              |           |  |  |  |

|                                             | 5.1                                      | Hardware Requirements                                        | 39        |  |  |  |

|                                             | 5.2                                      | Design Approaches                                            | 40        |  |  |  |

|                                             |                                          | 5.2.1 Design Approach 1: Extended Conventional Circuit       | 40        |  |  |  |

|                                             |                                          | 5.2.2 Design Approach 2: NMOS-PMOS circuit                   | 40        |  |  |  |

|                                             |                                          | 5.2.3 Design Approach 3: NMOS circuit                        | 42        |  |  |  |

|                                             |                                          | 5.2.4 Selection of Design Approach                           | 45        |  |  |  |

|                                             | 5.3                                      | Implementation of Prototype                                  | 45        |  |  |  |

|                                             | 5.4                                      | Evaluation of Prototype                                      | 49        |  |  |  |

| 6                                           | Eva                                      | luation                                                      | 51        |  |  |  |

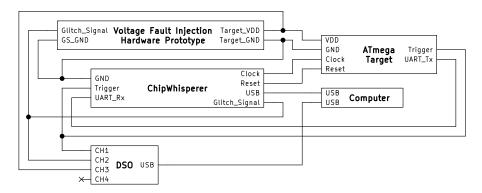

| U                                           | 6.1                                      | Test Setup                                                   | 51        |  |  |  |

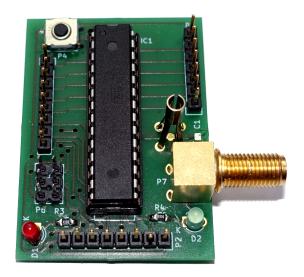

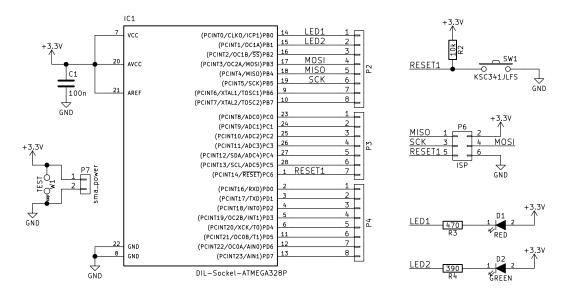

|                                             | 0.1                                      | 6.1.1 Target                                                 | 52        |  |  |  |

|                                             |                                          | 6.1.2 Voltage Fault Injection Hardware Prototype             | 55        |  |  |  |

|                                             |                                          | 6.1.3 ChipWhisperer                                          | 55        |  |  |  |

|                                             |                                          | 6.1.4 Digital Storage Oscilloscope                           | 56        |  |  |  |

|                                             |                                          | 6.1.5 PC                                                     | 56        |  |  |  |

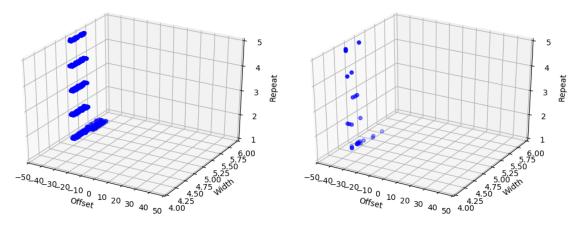

|                                             | 6.2                                      | Evaluation 1: ATmega Target without Decoupling Capacitor     | 58        |  |  |  |

|                                             | 6.2                                      | Evaluation 2: ATmega Target with Decoupling Capacitor        | 60        |  |  |  |

| 7                                           | Res                                      | ults                                                         | 61        |  |  |  |

| •                                           | 7.1                                      | Evaluation 1: ATmega Target without Decoupling Capacitor     | 61        |  |  |  |

|                                             | 1.1                                      | 7.1.1 Deactivated Brownout Protection                        | 61        |  |  |  |

|                                             |                                          | 7.1.2 Brownout: 2.7 Volt                                     | 65        |  |  |  |

|                                             |                                          | 7.1.3 Brownout: 1.8 Volt                                     | 68        |  |  |  |

|                                             | 7.2                                      | Evaluation 2: ATmega Target with Decoupling Capacitor        | 69        |  |  |  |

|                                             | 1.4                                      | 7.2.1 Deactivated Brownout Protection                        | 69        |  |  |  |

|                                             |                                          | 7.2.1 Deactivated Brownout Frotection                        | 72        |  |  |  |

|                                             |                                          | 7.2.3 Brownout: 1.8 Volt                                     | 74        |  |  |  |

|                                             |                                          |                                                              | • •       |  |  |  |

| 8                                           | Sun                                      | nmary and Conclusion                                         | 77        |  |  |  |

| 9                                           | Furt                                     | ther Work                                                    | <b>79</b> |  |  |  |

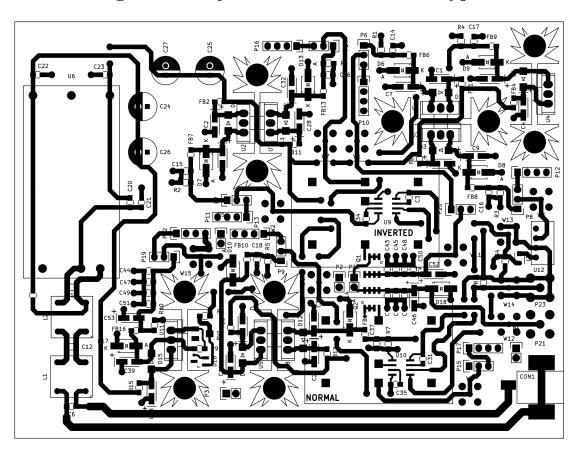

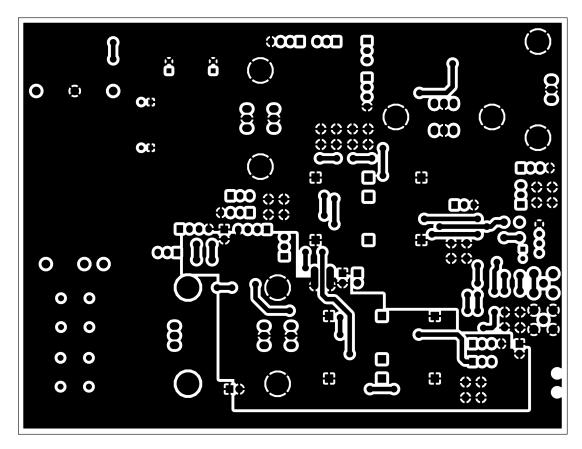

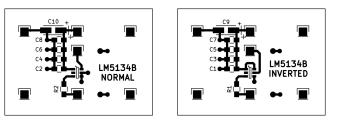

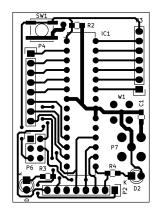

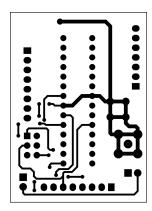

| $\mathbf{A}$                                | Prir                                     | nted Circuit Boards                                          | 81        |  |  |  |

|                                             | A.1                                      | Voltage Fault Injection Hardware Prototype                   | 81        |  |  |  |

|                                             |                                          | ATmega Target                                                | 83        |  |  |  |

| $\mathbf{B}$     | B Source Code 85 |                            |     |  |

|------------------|------------------|----------------------------|-----|--|

|                  | B.1              | Evaluation Software        | 85  |  |

|                  |                  | B.1.1 capture.py           | 85  |  |

|                  |                  | B.1.2 database.py          | 89  |  |

|                  |                  | B.1.3 models.py            | 91  |  |

|                  |                  | B.1.4 cwuserscript.py      | 92  |  |

|                  |                  | B.1.5 oscilloscope.py      | 94  |  |

|                  | B.2              | Glitch Software            | 95  |  |

|                  |                  | B.2.1 glitch.py            | 95  |  |

|                  | B.3              | Plot Software 2D           | 96  |  |

|                  |                  | B.3.1 plot2d.py            | 96  |  |

|                  | B.4              | Plot Software 3D           | 98  |  |

|                  |                  | B.4.1 plot3d.py            | 98  |  |

|                  | B.5              | Oscilloscope to CSV        |     |  |

|                  | D a              | B.5.1 osci2csv.py          |     |  |

|                  | В.6              | ATmega328P Target Firmware |     |  |

|                  |                  | B.6.1 main.c               | 101 |  |

| $\mathbf{C}$     | MvS              | SQL Database               | 105 |  |

|                  |                  | ·                          | 105 |  |

|                  |                  |                            |     |  |

| Lis              | st of            | Figures                    | 109 |  |

| Lis              | st of            | Tables                     | 111 |  |

| Gl               | ossar            | ry                         | 113 |  |

| Ac               | rony             | vms                        | 115 |  |

| Bibliography 117 |                  |                            |     |  |

CHAPTER 1

## Introduction

#### 1.1 Motivation

Today, microcontrollers are essential to our way of life and they are used in a wide range of embedded systems. Gartner, Inc. forecasts that 20.8 billion connected things will be in worldwide use in 2020 [1]. Data in embedded devices is often highly confidential and sensitive, so privacy and security expectations must be fulfilled. Furthermore, the highly distributed nature of embedded devices allows malicious attackers physical access to the systems. As a result, they must be hardened against any kind of physical attacks just the same.

Fault attacks are well known physical attacks in the area of hardware security. One of the most common fault injection technique is a short term variation in supply voltage, which may cause a processor to misinterpret or skip instructions [2].

Unfortunately, many manufacturers of embedded devices do not consider fault attacks during system development, although the dangers of fault attacks have been known for over 15 years. The first academic fault attack [3] was published in 2001 and describes a number of methods for attacking public key algorithms. A more recent real-world attack was the Xbox360 reset glitch attack [4] in 2012. The focus of the attack was to execute unsigned code to circumvent Microsoft's security concept. In a nutshell, the processor of the console was attacked by sending a short reset pulse that changed the behavior of the memcmp function. In presence of the fault attack, the function memcmp, used to check the bootloader SHA hash digest against a stored one, returned with the result that there was no difference. The attack thus circumvented the copy protection of the game console and made playing pirated games possible. The attack was impemented in the form of so called *mod chips* to be useable for everyday consumers. Mod chips are a mass market today.

Fortunately, more and more microcontroller manufacturers recognize the importance of hardened hardware and implement countermeasures into their products. However, since microcontrollers with countermeasures against fault attacks are more expensive in comparison to their unprotected counterparts, fault attacks are still feasible on many embedded devices. On these devices, fault injection attacks can also be utilized by independent security researchers to obtain the firmware in the presence of readout protections such as security fuses or bootloader protections. Without access to the firmware, independent in-depth security audits are not feasible and thus increase security-by-obscurity scenarios where security critical firmware can not be scrutinized for vulnerabilities.

#### 1.2 State of the Art

Recently, two commercial solutions for voltage fault injection attacks have been released: The VC Glitcher [5] including the Glitch Amplifier [6] by Riscure<sup>1</sup> and the ChipWhisperer [7] with the VC Glitch add-on by NewAE Technology Inc.<sup>2</sup>. While the Riscure solution allows negative voltages to some extent, both approaches primarily focus on conventional voltage fault injection attacks.

In 2000, Sergei P. Skorobogatov released a summary [8] of possible attack vectors on common microcontrollers. Even though the summary was released over a decade ago, most of the microcontrollers covered are still in use today. Voltage glitching was one of the described attack vectors, but negative voltage fault attacks are not covered.

In 2006, Bar-El et al. described different fault injection attacks on cryptographic implementations in their paper [2]. However, negative voltage fault attacks are not mentioned in their publication.

In 2014, Carpi et al. published a paper [9] which summarized a novel methodology for choosing multiple parameters required for effective faults on smart cards. Since their search space for the glitch voltage was between -5.0 V and -0.05 V, they handled negative voltage fault injection attacks, but only for low power smart cards and not for microcontrollers or larger controllers in general.

In the same year, Zussa et al. released a paper [10] where they analyzed positive and negative voltage fault attacks on Field Programmable Gate Arrays (FPGAs) with an on-chip voltmeter. Although they used negative voltage to inject the glitch, they didn't compare conventional voltage fault injection attacks against negative voltage fault injection attacks.

#### 1.3 Problem Statement

The hypothesis of this work is that negative voltage fault injection attacks provide advantages over their conventional counterparts with respect to shorter glitch durations

https://www.riscure.com

<sup>&</sup>lt;sup>2</sup>https://newae.com/

in presence of capacitive and inductive charges. Utilizing negative voltage during the generation of a fault, higher slew rates are expected due to the faster discharging of the circuit implementations outside and within microcontrollers. The aim of this work is thus to design and implement a negative voltage fault injection prototype to generate and evaluate these attacks against their conventional counterparts.

#### 1.4 Methodology

The methodological approach consists of three steps.

In the first step, a literature survey is conducted to obtain background knowledge on fault injection attacks. In existing work, different fault injection methods are identified and analyzed with regard to their usability for negative voltage fault injection attacks.

In the second step, different approaches and ideas for negative voltage glitch generation are explored and evaluated in Simulation Program with Integrated Circuit Emphasis (SPICE) simulations. Based on the results of these simulations, the requirements for electronic components are specified and a hardware prototype for negative voltage fault injection attacks is implemented. During prototyping, printed circuit boards are constructed, manufactured and assembled. Measurements conducted with the prototype are subsequently compared with the simulation results and circuit improvements are be conducted if necessary.

In the third step, the prototype and the negative fault injection approach are comprehensively evaluated on a real-world microcontroller in different configurations. During the evaluation, both conventional and negative voltage fault injection attacks are tested on the printed circuit prototype. The obtained results are then compared to determine whether negative voltage fault injection attacks provide advantages over conventional voltage fault injection attacks with respect to glitch duration, voltages and success rates.

#### 1.5 Outline

This work is structured as follows. Chapter 2 describes the fundamentals of microcontrollers to understand how fault injection attacks work in general. Chapter 3 provides an overview of voltage fault injection attacks and introduces the two well-known non-invasive glitching techniques clock glitching and voltage glitching. Chapter 4 highlights the limitations of conventional voltage fault injection attacks. Furthermore, the hypothesis of negative voltage fault injection attacks is provided. Chapter 5 presents the hardware prototype implementation. In a first step, the requirements are specified. Different approaches and ideas for negative voltage glitch generation are explored and evaluated in electronic SPICE simulations. Based on the results of these simulations, the requirements for electronic components are specified and hardware prototypes for negative voltage fault injection attacks are implemented. The different prototypes are evaluated and the most promising approach is selected. Chapter 6 describes the evaluation process and utilized

#### 1. Introduction

test setups to validate the hypothesis of this work. Chapter 7 presents and discusses the results of the evaluation. Chapter 8 summarizes the findings and presents a conclusion of the results. Finally, we provide an outlook and ideas for further work in Chapter 9.

CHAPTER 2

## Microcontrollers

This chapter describes the fundamentals of microcontrollers, which are important to understand how fault injection attacks work.

#### 2.1 Overview

Microcontrollers are integrated circuits containing a CPU, memories and accompanying peripherals within a single chip. According to Stan Augarten [11], the TMS 1000 was the fist microcontroller, which became commercially available in 1974. It combined a processor, a clock and memory on one chip and was targeted towards embedded systems.

Today, there are countless different types of microcontrollers on the market. They are typically customized to their area of application to minimize costs and required space. For example, the Atmel ATtiny4 [12] comes in a SOT-23 package with only 6 pins where, depending on the configuration, each pin except VCC and GND can be used for multiple functions. This specific type is low-cost, requires little space and has a low power consumption. At the same time, a compromise is made between performance and usability. In contrast, there are highly integrated microcontrollers with more than 200 pins and the border between microcontrollers and Systems-on-Chips (SoCs) becomes increasingly blurred. The larger controller types can be used for a wide range of applications and it is not uncommon that a full blown operating system such as Linux is used on them. The Raspberry Pi is a well known example for that, although it utilizes external non-volatile memory and, hence, no longer falls into the microcontroller definition where internal memory is used instead.

#### 2.2 Semiconductors

Semiconductors are a group of chemical elements with an electrical conductivity value between that of electrical conductors and that of non-conductors. By introducing foreign elements (doping) into a semiconductor compound material, the conductivity and the conduction characteristics (electron and hole conduction) can be specifically influenced. The combination of differently doped regions (i.e., with a lack of electrons (p-type) or an excess of free electrons (n-type)), for example in the case of a p-n junction, allows electronic components with a direction-dependent conductivity (e.g., a diode) or with a switching function (e.g., a transistor) [13].

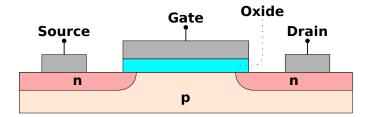

#### 2.2.1 MOSFET

Figure 2.1: Cross Section of an n-type MOSFET

Metal—oxide—semiconductor field-effect transistors (MOSFETs) are field-effect transistors (FETs) with an insulated gate. They can be either enhancement mode MOSFETs, meaning that they are *OFF* at zero gate-source voltage, or depletion mode MOSFETs, where they are *ON* at zero gate-source voltage. Due to the relevance for complementary metal-oxide-semiconductor (CMOS) technology, enhancement mode MOSFETs will be further discussed in Section 2.2.3.

MOSFETs can be distinguished in n-type and p-type MOSFETs. Figure 2.1 shows a cross section of a n-type MOSFET. Source and drain are n regions and the body is a p region. If the voltage  $U_{GS}$  between gate and source is lower the threshold  $U_{TH}$ , drain and source are not connected. If the voltage  $U_{GS}$  between gate and source is positive and higher as the threshold  $U_{TH}$  ( $U_{TH} > 0V$ ), a channel between drain and source forms due to electrostatic attraction of n-carriers and current can flow from drain to source.

In contrast, in p-type MOSFETs, source and drain are p regions and the body is an n region. If the voltage  $U_{GS}$  between gate and source is negative and lower as the threshold  $U_{TH}$  ( $U_{TH} < 0V$ ), current can flow from source to drain [14, 13].

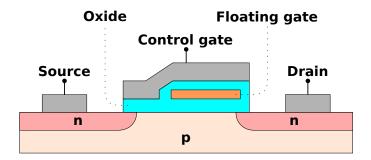

#### 2.2.2 Floating-Gate MOSFET

A floating-gate MOSFET (FGMOS) (Figure 2.2) is a MOSFET with a electrically isolated gate (floating-gate) and a secondary gate (control gate) deposited above the floating-gate. The floating-gate is surrounded by highly resistive, dielectric material (oxide) so that the contained charge remains stored even if the FGMOS is not biased. The floating-gate can be charged by applying a high voltage to control gate and drain, while source is connected to the ground. In modern FGMOS, the floating-gate is positioned over the n-channel of the drain. The charge can be discharged by applying high voltage to the

Figure 2.2: Cross Section of a Floating-Gate MOSFET

drain, while the control gate and source are connected to ground. In older FGMOS types, the electrical discharge was often not feasible. If there is no charge stored in the floating-gate, the behavior is similar to a normal MOSFET. However, if there is charge stored in the floating-gate, the transistor is effectively blocked since the charge in the floating-gate prevents the formation of a channel between drain and source [15]. Due to this property, the FGMOS can be used to store a bit. FGMOSs are thus utilized to form non-volatile memories which are described in more detail in Section 2.3.2.

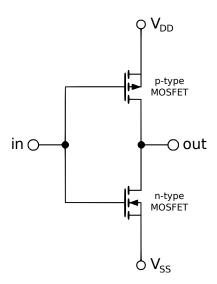

#### 2.2.3 CMOS

Complementary metal-oxide-semiconductor (CMOS) is a term for semiconductor devices where both n-type MOSFETs and p-type MOSFETs are used on a common substrate. It has a high noise immunity, a low static power consumption and the operating voltage can be between 0.75 V and 15.0 V. CMOS is the most widely used technology in microprocessors, microcontrollers, memory devices and other digital logic circuits [14].

Figure 2.3: CMOS Inverter

Figure 2.3 shows a CMOS inverter, which outputs a voltage representing the opposite logic-level to its input. If the p-type MOSFET is active and the n-type MOSFET is inactive, the output is connected to  $V_{DD}$ . Vice versa, if the p-type MOSFET is inactive and the n-type MOSFET is active, the output is connected to  $V_{SS}$  [14].

Table 2.1 provides an overview of typical logic levels at 5 V operating voltage. It should be noted that although the acceptable input logic level voltage range is relatively wide, the output level always resides in a small voltage range.

|      | Input                         | Output                                 |  |

|------|-------------------------------|----------------------------------------|--|

| LOW  | $0.0 \ { m V} - 1.5 \ { m V}$ | $0.0 \ \mathrm{V} - 0.05 \ \mathrm{V}$ |  |

| HIGH | 3.5  V - 5.0  V               | 4.95  V - 5.0  V                       |  |

Table 2.1: CMOS Logic Levels for 5 V Operating Voltage [14]

Table 2.2 provides an overview on different CMOS technologies and their characteristics. Among other factors, the speed of microcontrollers is primarily limited by the gate delay.

| Technology      | Abbr. | Power loss per gate | Processing time per gate |

|-----------------|-------|---------------------|--------------------------|

| Standard CMOS   | C     | 0.3 μW              | 90  ns                   |

| High speed CMOS | НС    | 0.5 μW              | 10 ns                    |

| Advanced CMOS   | AC    | 0.8 μW              | 3 ns                     |

Table 2.2: CMOS Characteristics [14]

#### 2.3 Components

This section explains the central components within a microcontroller. Since the implementation details of microcontrollers differ significantly between manufacturers, only a rough overview is provided.

#### 2.3.1 Processor Core

The processor core executes a program by processing instructions (e.g., logic, arithmetic, control and input/output instructions). The components of the core are explained on the basis of the Micro16 educational reference architecture introduced by Schildt et al. [16].

#### Registers

A register is a circuit comprising several flip-flop gates and stores a certain number of bits. Typically, the size of a standard register is equally large as the bus width within the core. In general, there are different types of registers depending on their application. *Data registers* hold data values such as integers and are used to store operands or the results of calculations. *Address registers* are used to address memory areas. *Status registers* (also known as *status flags*) are used to store truth values such as whether the result of a

previous calculation was zero (zero flag). In addition, there are *special purpose registers* which are explained in the following.

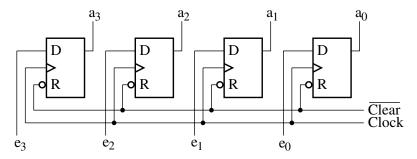

Figure 2.4: A 4-bit Register [16]

Figure 2.4 illustrates a 4-bit register built from four flip-flops. A flip-flop is a basic logic circuit storing one bit of data and it is typically manufactured in CMOS technology. The illustrated flip-flops have a data (D), a clock (>) and a reset (R) input and a one output. The register comprises 4 flip-flops and can thus store a 4-bit word. By holding R low for one clock cycle, the register is erased. When  $e_3$  and  $e_1$  are high and  $e_2$  and  $e_0$  are held low for one clock cycle, the word (1010) is stored. The current value of the register can be accessed through the outputs of the register.

#### Arithmetic Logic Unit (ALU)

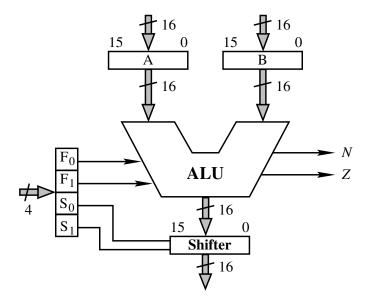

An ALU performs the arithmetic and logic operations. The Micro16 ALU visible in Figure 2.5 supports the following functions:

- Map a 16-bit data word received from register A to an output register without changing the value.

- Addition of two 16-bit data words received from registers A and B. The results are written to the output data and flag registers.

- Bitwise AND operation of two 16-bit data words received from registers A and B. The results are written to the output data and flag registers.

- Bitwise NOT operation of one 16-bit data word received from register A. The results are written to the output data and flag registers.

Additionally, the result of the four functions can be bitwise shifted to the left or to the right. The Micro16 ALU has a 2-bit control input  $(F_0F_1)$  to select which function should be executed and a 2-bit control input  $(S_0S_1)$  to select whether the result should be shifted (either left or right) or not. Furthermore, there are the *status flags* ZERO (Z) and NEGATIVE (N) which are set if the result of the operation is either zero or negative.

Figure 2.5: The Micro16 ALU [16]

| micro in-        |          | micro in-        |                   |

|------------------|----------|------------------|-------------------|

| struction        |          | struction        |                   |

| $(F_0F_1S_0S_1)$ | symbolic | $(F_0F_1S_0S_1)$ | symbolic          |

| (0000)           | A        | (1000)           | $A \wedge B$      |

| (0001)           | lsh(A)   | (1001)           | $lsh(A \wedge B)$ |

| (0010)           | rsh(A)   | (1010)           | $rsh(A \wedge B)$ |

| (0100)           | A+B      | (1100)           | $\neg A$          |

| (0101)           | lsh(A+B) | (1101)           | $lsh(\neg A)$     |

| (0110)           | rsh(A+B) | (1110)           | $rsh(\neg A)$     |

Table 2.3: Micro Instructions of the Micro16 ALU [16]

Table 2.3 shows the possible  $micro\ instructions$  and corresponding functions of the Micro 16 architecture.

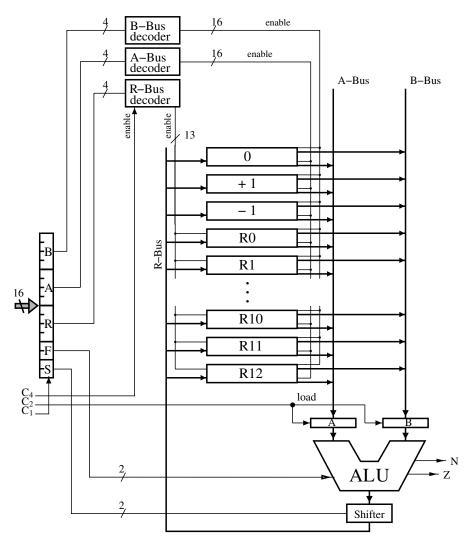

Overall, the registers A and B are connected to thirteen data registers ( $R_0 \dots R_{12}$ ) and three read-only data registers, containing the constants 0, - 1, + 1. The registers are connected via buses that are described in the following section.

#### Bus

A bus is an electrical connection between several components of a system and is used to share information between them. There are three types of buses: The *data bus*, the *address bus* and the *control bus*. The transmission of the bits can either be in parallel (e.g., simultaneously) or in serial (e.g., one bit after another). In the Micro16 architecture, the transmission is implemented in parallel so that a distinct bus wire is required for

each bit.

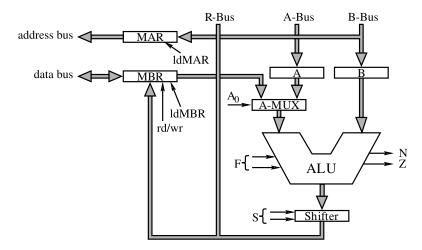

Figure 2.6: Micro16 ALU with Registers and Buses [16]

Figure 2.6 illustrates the bus connections within the Micro16 architecture. The thirteen registers  $(R_0 \dots R_{12})$  can write a value to buses A and B and they can read a value from bus R into the corresponding register. The three constant registers (0, -1, +1) can only write their static value to the buses A and B. Each register thus has either two or three enable inputs. To minimize the length of the micro instructions, the selection of the register is encoded in 4-bits and must be decoded in a bus decoder. For instance, to enable writing from register  $R_0$  to bus A, the value  $(0100)_2$  is transmitted to the A-bus decoder. Furthermore, the ALU registers A and B each have an input enabling reading from the buses A or B. The figure shows the timing signals  $C_1$ ,  $C_2$ ,  $C_4$  as well. These signals are used to coordinate the proper behavior of the processor core and they are be

explained in more detail in the following sections.

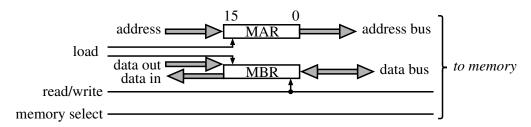

#### **Memory Connection**

To access the memory, the Micro16 architecture has two registers: The Memory Address Register (MAR) and the Memory Buffer Register (MBR) (Figure 2.7). The MAR addresses the location of the memory and is connected to an address bus. The MBR buffers data before it is written to the memory or after it is read from the memory. The MBR is connected to the data bus and can be switched between read and write mode via a read/write signal. The memory select signal triggers the memory to read or write a value from or to the MBR. Since the MAR is 16-bit long, addresses from 0 to  $2^{16} - 1$  can be addressed.

The reading process is divided into the following steps:

- 1. The address of the memory cell is written to MAR and the signals read/write and memory select are asserted.

- 2. The memory access time has to pass.

- 3. The MBR can read the value from the data bus into the register.

Figure 2.7: Micro16 Memory Connection [16]

Similarly, the writing process is divided into the following steps:

- 1. The address of the memory cell is written to MAR and the signal memory select is activated.

- 2. The memory reads the value from the MBR and writes it to the address defined in the MAR.

Figure 2.8 illustrates how the buses are connected to the MBR and MAR. With the signal A<sub>0</sub>, a multiplexer switches the A input of the ALU between bus A and the MBR. Since the micro instruction function (0000) maps a 16-bit data word from the ALU input to the output, the value of the MBR can be saved in each data register. The MAR is connected to bus B, so that the memory address can be stored in the data registers. The output of the ALU is written to the MBR, which is required at the writing process.

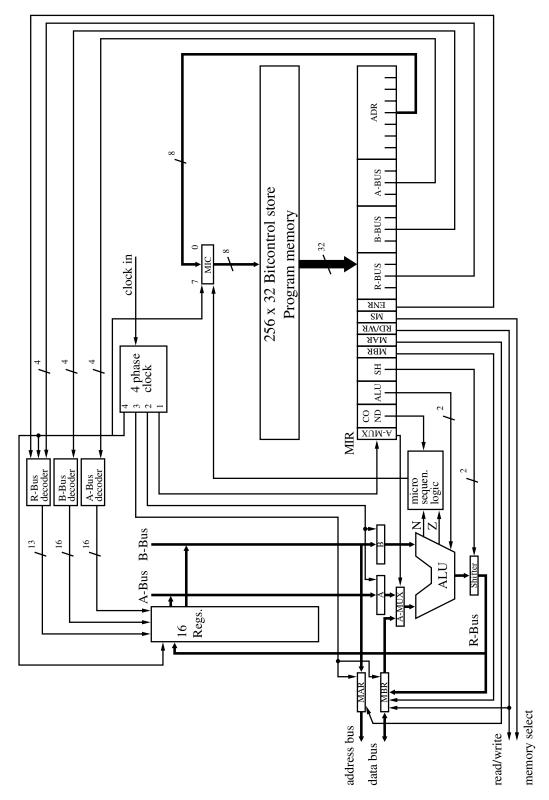

#### Program Memory and Micro Sequence Logic

Figure 2.10 shows the Micro16 architecture including new components that are described in the following. The program is stored in a 256x32 sized program memory. Since all micro instructions of the Micro16 architecture are 32-bits long, a program can have up to 256 instructions at most. The address of the current instruction is stored in the Micro Instruction Counter (MIC) also known as program counter in other architectures. The Micro Instruction Register (MIR) contains the current micro instruction.

The *micro sequence logic*, which enables conditional and unconditional jumps to an arbitrary position in the program, is connected to the MIC and to the status flags of the ALU. The micro instruction is extended by eight bit (ADR) for address representing

Figure 2.8: Micro16 ALU, Buses and Memory Connection [16]

the destination of the jump. In addition, the micro instruction is extended by two bits (*COND* for condition) to select the jump type. The type can be one of the following:

- $(00)_2$ : Do nothing

- $(01)_2$ : Jump, if the status flag N is one

- $(10)_2$ : Jump, if the staugs flag Z is one

- $(11)_2$ : Jump without any condition

#### Control Unit

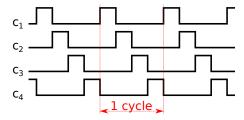

Figure 2.9: Micro16 Clock Timing Diagram

The control unit is a integrated logic block contained within the processor core. It coordinates the execution of a program by interpreting the instructions to provide timing and control signals for the other processor core units such as the ALU and the memory block. One important part is the clock component (4 phase clock). Based on a reference clock signal provided by an external crystal or an internal oscillator, it generates four successive clock signals (i.e., clock cycles) (Figure 2.9). The following describes functions of each clock cycle:

- C<sub>1</sub>: The micro instruction in the MIR is executed. The A-Mux multiplexer either selects the MBR or the A register as input for the ALU. The behavior of the micro sequence logic is selected and the ALU function is chosen. The MBR and MAR are either enabled or not. If the memory select bit is set, the memory is enabled and according to the RD/WR signal the function is selected. Values are written to the buses A and B. If the ENR bit is set the register, which will store the value from the R bus in C<sub>4</sub>, is selected.

- C<sub>2</sub>: The registers A and B read the current value from the buses A and B.

- C<sub>3</sub>: The MAR and MBR are enabled.

- C<sub>4</sub>: The ALU result is stored in the selected register. The next micro instruction is selected by the MIC.

Figure 2.10: Complete Micro16 Architecture [16]

#### 2.3.2 Memory

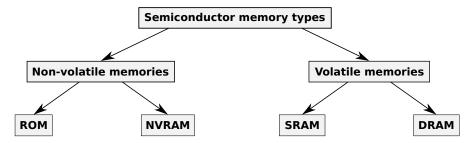

Figure 2.11: Different Types of Semiconductor Memory

Memory is used to store data and is implemented in microcontrollers as integrated circuit logic block. Figure 2.11 provides an overview of different memory types. In general, memory can be divided into volatile and non-volatile types [17]. Volatile memory loses the stored data if the power is turned off. In contrast, stored data can be retrieved from non-volatile memory even if the supply voltage has been turned off and back on again. Non-volatile memory can be further divided into read-only memory (ROM) and non-volatile random-access memory (NVRAM) while volatile memory can be divided into static random-access memory (SRAM) and dynamic random-access memory (DRAM).

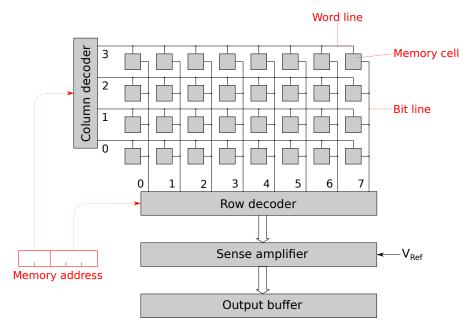

Figure 2.12: Typical Memory Layout

Although there are different types of memory, their fundamental on-chip design (Figure 2.12) is similar. A single bit is stored in a *memory cell*. Memory cells are laid out in an array on the surface of the chip, where each row represents a data word. Horizontally there are the word lines and vertically there are the bit lines. Usually, the two basic

operations performed by a memory are read, where a data word is read from the memory, and write, where a data word is written to a memory. The data word is accessed by the  $memory\ address$ , which is divided into a column and a row part. The memory address is decoded by a  $column\ decoder$  and a  $row\ decoder$  to select the proper data word. Since due to physical memory technology properties, the memory is typically not operating on the same logic levels, a sense amplifier is required [18]. The sense amplifier shifts the charge of each bit to a range which is comprehensible for the rest of the microcontroller. To decide whether a sensed charge level represents a 0 or a 1 bit, a voltage reference  $V_{Ref}$  is required for comparison purposes. After the sense amplifier, the addressed data word is finally stored in an output buffer. The following sections provide an overview of the different types of memory.

#### Static random-access memory (SRAM)

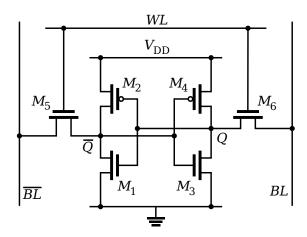

Figure 2.13: Circuit Diagram of an SRAM Cell, Built With Six MOSFETs [19]

An SRAM is a volatile memory that uses a bistable latching circuit to store a bit in a memory cell. The term static means that the SRAM does not need to be refreshed periodically to hold its content.

A typical SRAM memory cell, illustrated in Figure 2.13, is made up of six MOSFETs, known as 6T SRAM cell. The MOSFETs  $M_1$ ,  $M_2$ ,  $M_3$  and  $M_4$  form two cross-coupled inverters. Therefore, the memory cell has two stable states to store a bit. The MOSFETs  $M_5$  and  $M_6$  are used to control the access during read and write operations.

The advantages of SRAMs are low power consumption, no need of a refresh circuit and fast access time. However, the disadvantage is the required space due to the high amount of transistors. For that reason, SRAM is mainly used for areas where fast access time are important (e.g., caches).

### Dynamic random-access memory (DRAM)

A DRAM is a volatile memory storing each bit of data in a capacitor within an memory cell. However, the capacitor looses its charge over time so that the memory cell must be refreshed periodically. The advantages of the DRAM are fast access time, structural simplicity, low space requirements and low manufacturing costs. On the other hand, due to its dynamic nature, DRAM consumes large amounts of power and it requires logic for refreshing.

### Read-only memory (ROM)

A ROM is a non-volatile memory type. Depending on whether the ROM is reprogrammable, once programmed memory content can be re-programmed at a later point of time. In microcontrollers, a ROM is mainly used to store the firmware and bootloader code. In the following, the different types are described, whereby the chronological order reflects the time of development.

Mask ROM (MROM): In MROMs, the content of the memory is hardwired in the circuit layout of the integrated circuit. For a memory cell which should contain a logical 1, the word line is connected to the bit line, otherwise they are not connected and the memory cell contains a logical 0. The connection can be realized with a diode or a transistor. The advantage of MROMs is that they need less space compared to other ROM technologies and they are feasible at low cost for mass production. However, the content can not be modified and the ROM type is only cost efficient at high quantities.

Programmable ROM (PROM): A PROM can be programmed by a user with a PROM programmer only once. Each memory cell contains a connection between the word line and the bit line. The connection is achieved with a diode and a fuse or a floating-gate MOSFET, where the charge of the floating-gate can not be discharged. The programmer addresses the memory cells which should contain a logic 0. By applying high voltage to the addressed memory cells, the fuses are burned or the floating-gates of the floating-gate MOSFETs are charged as described in Section 2.2.2. As a result, for the addressed memory cells, the connections between word lines and bit lines are destroyed. The advantage of PROMs is that they can be programmed after chip fabrication. The disadvantage is that the PROM needs more space compared to the MROM and, hence, it is more expensive to manufacture.

Erasable programmable ROM (EPROM): The EPROM can be programmed and erased by the user a limited number of times. The structure of the EPROM is similar to the PROM. However, the connection in the memory cells is solely achieved with floating-gate MOSFETs where the charge of the floating-gates can not be discharged with high voltage. The programming works in the same manner as for PROMs. To erase the content of the memory cells, the memory gets exposed to strong ultraviolet light that discharges the floating-gates. The package of the memory thus contains a quartz window that is transparent to ultraviolet light. The advantage of EPROMs is that they can

be programmed and erased, but the number of reprogramming is limited and the package of the memory needs a quartz window, which increases the manufacture costs.

Electrical erasable programmable ROM (EEPROM): Today, EEPROMs, which can be programmed and erased by the user up to  $10^4 - 10^6$  times, have a great significance in the semiconductor technology [20]. The structure of the EEPROM is similar to the EPROM, but the floating-gate MOSFET can be erased with high voltage, as described in Section 2.2.2. A special variant of EEPROM is flash memory. Flash memory cells differ from EEPROM memory cells in the thickness of the surrounding floating-gate oxide. Since the oxide is thinner, a lower voltage is required for programming and erasing the memory cells. Therefore, the voltage converter and programming logic can be contained in microcontrollers. Considering write operations, typical EEPROM implementations allow individual addressing of words whereas Flash memories only allow addressing in blocks to achieve higher memory densities.

### Non-volatile random-access memory (NVRAM)

NVRAMs combine the advantages of SRAMs and ROMs. They contain an SRAM to achieve fast access times and they contain an EEPROM, where the data is stored if the power is turned off. The disadvantages are high manufacturing costs and large space requirements.

### 2.3.3 Other Features

#### Reset

In a microcontroller, the reset sets all peripherals including the CPU to a predefined initial state. Once the microcontroller's CPU is ready to execute instructions, execution starts at a hard-coded start address in the memory. This location is commonly known as reset vector.

The reset can be triggered by the following scenarios:

- External reset through an electrical signal at the reset pin

- Power-on reset (PoR), which generates a reset signal if power is applied to a microcontroller to ensure that the microcontroller starts operating in a known state

- Internal reset if a error is detected by the logic of the microcontroller

- Internal reset triggered by a program

### Bootloader

A bootloader handles the booting process after the reset procedure has finished. It extends the reset procedure and simplifies tasks such as firmware updates, loading a program from an external source into the DRAM or SRAM or encrypting and decrypting the user program. In general, there are two types of bootloaders. The first type is implemented by the manufacturer ("Mask-ROM bootloader") and is not available on all microcontrollers. It can not be modified by the user and gets directly executed after the reset procedure. The second type is a user bootloader that is implemented by the user and stored in the program memory. It gets executed either directly after the reset or after the execution of the manufacturer bootloader.

### 2.4 Architectures

The architecture of a microcontroller can be distinguished by the complexity of their instruction set or by the linkage of the instruction memory and data memory to the processor core. This following section provides an overview of these concepts.

### 2.4.1 Complexity of Instruction Set

### Reduced Instruction Set Computer (RISC)

In comparison to the Complex Instruction Set Computer (CISC) architecture, the RISC architecture has fewer and only rudimentary instructions that typically only need a single clock cycle to execute. The advantage of the RISC architecture is that the execution of instructions is very fast, but at the same time the disadvantage is that the instruction set is rather simple and hence the amount of necessary instructions to solve a complex task becomes larger. The software for a microcontroller is typically written in high-level programming languages and compiled through a compiler. As a result, the high level programming language abstracts the simplified instruction set from the developer. Mainly due to faster execution times per instruction and less ALU implementation complexity, the RISC architecture is widely used in microcontroller architectures [14].

RISC systems have a large on-chip register file. Due to the high number of registers, operands intermediate results and data can be kept in the registers. As a result, the traffic between the memory and the processor is reduced, which increases the speed of operation. However, a large register file requires a more complicated decoding logic, which increases the access time to any register.

Due to the small number of instructions, the RISC architecture is normally a load/store architecture. A load/store architecture is a computer architecture whose instruction set allows data memory accesses only with special *load* and *store* instructions.

### Complex Instruction Set Computer (CISC)

In comparison to RISC, the CISC architecture has a more complex instruction set. To avoid ALU implementation complexities, many implementations internally make use of microcode where a CISC instruction is represented by a number of less complex RISC instructions. Due to the internal microcode architecture, it is common for an instruction to take multiple clock cycles to execute. Hence, in comparison to RISC, the CISC

architecture has a more powerful instruction set resulting in less code size, but at the cost of more execution cycles per instruction [14].

Since the instructions at the CISC architecture can directly operate on memory, a small number of general purpose registers is required. Therefore, the register file is typically small at this architecture. However, the architecture is characterized by several special purpose registers for the stack pointer, interrupt handling, and so on.

### 2.4.2 Linkage of the Processor and Data Memory

### Von Neumann Architecture

Figure 2.14: Von Neumann Architecture

In the Von Neumann architecture, instructions and data are stored in the same memory (Figure 2.14) and, as a result, only one bus between the processor and the memory is required. While the advantage is that less hardware is needed, the disadvantage is that data and instructions can not be accessed at the same time and processing delays ("hazards") might be introduced [14].

### Harvard Architecture

Figure 2.15: Harvard Architecture

In the Harvard architecture, the instructions and data are stored in separate memories (Figure 2.15). Although two buses are required, the architecture is used more frequently due to its advantage that there are no additional delays when accessing instructions or data in memory at the same time [14].

### 2.5 Software Development

This section explains the fundamentals of software development for microcontrollers. The first part describes how a program is developed, followed by a description of how the program is downloaded into the microcontroller. Different programming and debugging standards are mentioned as well.

### 2.5.1 Programming

As described in Section 2.3.1, micro instructions are defined sequences of bits that control the data flow and instruction execution of the processor core. A machine instruction is either directly mapped to a micro instruction or to a series of micro instructions. For instance, the Micro16 architecture contains a left shift micro instruction. Therefore, a left shift machine instruction can directly use this micro instruction. However, the architecture does not contain a multiply micro instruction so that it can be only implemented as a series of micro instructions. An instruction set, with its instruction set architecture (ISA), is the interface between a microcontroller's software and its hardware. It defines the valid machine instructions the microcontroller can execute. The assembly language is a low-level programming language with a one-to-one mapping between the language and the instruction set. To simplify the programming, the assembly language uses mnemonic codes to refer to the machine instructions rather than using the instructions numeric values (opcodes) directly. The assembly program has to be translated to a binary form, also called *object file*, first. The result contains the machine code (text segment) and data such as global variables that typically reside in the (data segment). The translation itself from the mnemonic representation to the binary opcodes is done by the assembler. Normally, a program consists not only of one object file but of several object files and additional libraries. For this reason, the so-called linker merges the individual object files and libraries into a program. One of the disadvantages of the assembly language is that it has no abstraction from the instruction set. Hence, a developer has to know the assembly language for the specific architecture he is working on. For typical developers it is thus more convenient to a high-level programming language with a strong abstraction from the actual instruction set architecture instead. To translate a program written in a high-level programming language to a low-level assembler program, a compiler is used. The compiler needs to know the target architecture to generate the assembly code. Subsequently, the assembler can transform the generated assembly code into its binary opcode form.

### 2.5.2 Download

After a program has been assembled, the resulting binary must be downloaded into the microcontroller's memory. On the host computer side, this is usually done via the serial, parallel or usb interface. On the microcontroller side both standard and manufacturer proprietary programming interfaces exist. However, even though there are some standards such as JTAG [21] or SWD [22], the programming interfaces are often proprietary solutions developed by the microcontroller manufacturers. Another possibility is the usage of a bootloader, which was described in Section 2.3.3.

### **Programming Interfaces**

As described above, there are different programming interface types. As an example, the Atmel ATmega in-system programming (ISP) standard is described in the following.

In-system means, that the microcontroller can be programmed while it is already mounted to a printed circuit board. The programming wiring must fulfill the requirements defined in the respective datasheet [23]. The six microcontroller pins MISO, SCK, RESET, MOSI, +5V, GND are connected to a pin header. A programming adapter is connected to the pin header and on the other side, it is typically connected to the host computer via a USB interface. The adapter is controlled from the computer with a programming software. To enable the programming mode, the programmer pulls the RESET pin to low and transmits a "programming enable" command over the MOSI pin. If the programming mode is entered, the microcontroller responds with an acknowledge message over the MISO pin. Once the programming mode has been entered, further instructions like "write to program memory", "erase program memory" and "read program memory" are available. After programming is finished, the reset pin is released.

### 2.5.3 Debugging

A *debugger* can be used to search for errors in the developed program. State-of-the-art debuggers offers at least the following features:

- Breakpoints: Defined points in the code where the program execution should be stopped. After the stop, the values of the memory, variables and registers can be inspected.

- Single Stepping: One instruction is executed at a time. The execution is paused afterwards.

- Programming: Since the debugger has access to the program memory, it can be used to program the microcontroller as well.

To debug a microcontroller, the debugger program is executed on the host computer. There are different debugging interface standards. The most common ones are Joint Test Action Group (JTAG) and Serial Wire Debug (SWD).

### 2.6 Protection Mechanisms

Microcontrollers provide different protection mechanism to protect the program code from unauthorized readouts. Although the implementation of the mechanisms depend on the manufacturer, the common key concepts are either the use of locking bits or bootloader passwords and/or keys. The basic idea of a locking bit (also known as security fuse bit) is to disable reading the memory through the programming interface. If the protection bit is disabled, the memory is erased as well. With bootloader protections, the functionality to read the memory via bootloader functions is protected either with a cryptographic key, a signature or a password. If the user does not have the necessary credentials, the respective bootloader functions are not available. The big difference between those protection mechanism types is that security fuse bits are commonly implemented in hardware while the bootloader protection is implemented in software (i.e., the bootloader comprises of instructions that are executed by the same CPU that also executes the user's program).

## Fault Injection Attacks

A fault injection attack is a procedure to intentionally introduce an error in a system to alter its execution to the attackers advantage. Fault injection effects have been known for a long time.

In 1978, May et al. published a paper [24] which describes accidental faults caused by radioactive particles produced by elements naturally present in IC packaging material. These particles caused bit flips in sensitive chip areas and hence led to undesired errors.

According to Bar-El et al. [2], faults can be divided into *provisional faults*, where the system recovers itself after a reset or when the fault's stimulus ceases, and *destructive faults*, where the system is permanently affected or even destroyed. For fault injection attacks, only the first type is of interest.

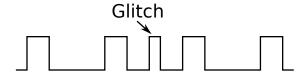

A special form of fault attacks are glitch attacks, where a pulse outside the normal operating specification is injected into the system. Glitches can be divided into *instruction glitches*, data glitches and clock-signal glitches [2, 25].

The aim of instruction glitches is to replace a single critical machine instruction like conditional jumps or the test instruction preceding them to another one. They can be used to extend the runtime of loops, for example in serial output routines to see more of the memory after the output buffer [26]. Anderson et al. described an attack on a cryptographic cipher function, where the rounds of the cipher were reduced to a single-round [27]. The aim of data glitching is to modify the data values that are used by the processor during program execution. Clock-signal glitches temporarily increase the clock frequency for one or more half cycles. As a consequence, some flipflops in the register-transfer-logic (RTL) sample their input before the new state has actually reached them. Logic blocks with low complexity may thus operate normally while more complex blocks do not finish in time and either output their previous or an intermediate state.

In general, there are two well-known non-invasive glitching techniques for creating reliable faults: *clock glitching* and *voltage glitching*. The following sections give an overview over the two techniques.

### 3.1 Clock Glitching

Since most common microcontrollers are based on synchronous logic, they require a system clock (see Section 2.3.1). To perform a clock glitch, the clock frequency is temporarily increased for one or more half cycles as illustrated in Figure 3.1.

In 2011, Balasch et al. published a paper [28] in which they analyzed how clock glitches affect commercial low-cost microcontrollers. They divided their results into effects of clock glitching on the program flow and effects of clock glitching on the data flow. According to the authors, the fetching of the next opcode can be affected such that it is replaced by another instruction. Skipping an instruction, which is sometimes mentioned in analyses of fault models, was not possible. The best and most stable results for effects on the data flow were obtained for multi-cycle instructions with memory access. Depending on the glitch period, the authors were able to prevent a given number of bits on the data bus from flipping.

Figure 3.1: Glitch in the Clock Signal

However, non-invasive clock glitching attacks can only be applied to microcontrollers that use an external clock signal. In contrast, many of today's microcontrollers rely on an internal RC oscillator instead so that non-invasive clock glitching is often not feasible.

## 3.2 Voltage Glitching

Variations in supply voltage during execution may causes a processor to misinterpret or skip instructions [2]. This attack is known as *voltage glitching*.

The use of voltage glitching has been extensively reported over the last decade [29, 30, 31]. However, only a few papers have investigated the underlying fault injection mechanisms. In 2006, Djellid-Ouar et al. published a paper [32] which summarized the effects of voltage glitches on CMOS circuits. They showed that voltage fault injection attacks cannot induce faults into flip-flops. Furthermore, they showed that faults occur because of timing constraint violations, which are caused by an increase of the combinatorial logic propagation delays. However, the results described by Djellid-Ouar et al. were only achieved by simulations. Consecutively, Zussa et al. contributed an experimental proof

[33] that voltage fault injection attacks lead to timing constraint violations in a similar way as clock glitches do.

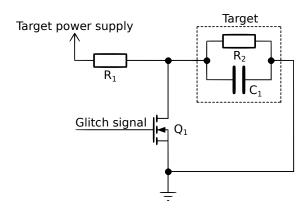

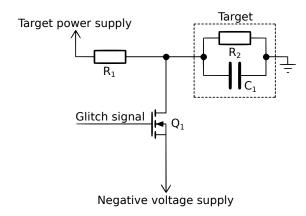

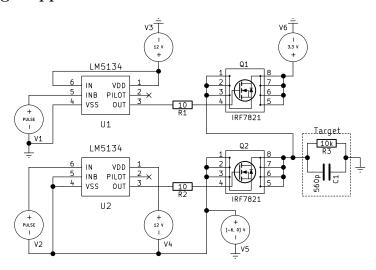

Figure 3.2: Method to Create a Glitch in the Power Supply Line of a Target

One of the easiest methods to create a glitch in the power supply line of a target is illustrated in Figure 3.2. NewAE Technology Inc.<sup>1</sup> uses this method [7, 34] in their commercial solution. If the logical glitch signal is high, the MOSFET  $Q_1$  shorts the power supply line of the target to GND. The capacitor  $C_1$  and resistor  $R_2$  build an equivalent circuit diagram for a microcontroller. The resistor  $R_1$  is required to prevent a short circuit between the power supply and GND.

<sup>1</sup>https://www.newae.com/

## Negative Voltage Fault Injection Attacks

While Section 3.2 provided an overview of voltage fault injection attacks that are hereafter referred to as conventional voltage faults attacks or conventional voltage glitching, this chapter highlights the limitations of conventional voltage fault injection attacks. Furthermore, the hypothesis of negative voltage fault injection attacks is described.

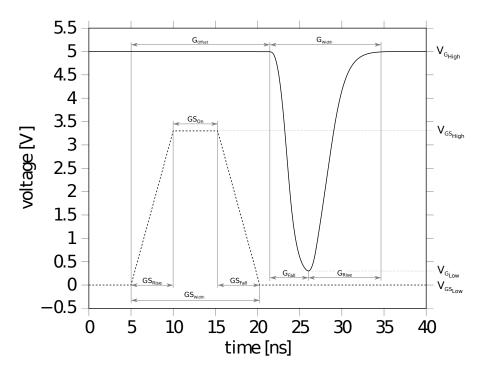

## 4.1 Basic Terms of Voltage Fault Injection Attacks

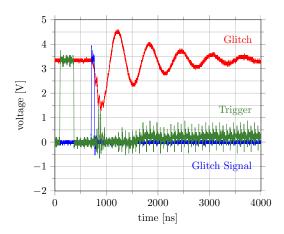

In this section, we first define a few basic terms to better understand and describe voltage fault injection attacks. Figure 4.1 provides an overview of a typical voltage glitch signal. The dotted waveform shows the logical glitch signal (i.e., the trigger for the glitch). If the logic level is high, a glitch should be inserted in the power supply line of a target. The second waveform illustrates the power supply line of a target with an inserted glitch.

The voltage levels and time periods are explained in the following.

- Glitch Signal Voltage High  $(V_{GS_{High}})$ : High logic level of the glitch signal.

- Glitch Signal Voltage Low  $(V_{GS_{Low}})$ : Low logic level of the glitch signal.

- Glitch Signal Width  $(GS_{Width})$ : The time period of the rectangular pulsed glitch signal from the moment it rises from  $V_{GS_{Low}}$  until reaching  $V_{GS_{Low}}$  again.

- Glitch Signal Rise Time  $(GS_{Rise})$ : The time period needed to rise from  $V_{GS_{Low}}$  to  $V_{GS_{High}}$ .

- Glitch Signal Fall Time  $(GS_{Fall})$ : The time period needed to fall from  $V_{GS_{High}}$  to  $V_{GS_{Low}}$ .

Figure 4.1: Glitch Signal (Dotted Waveform) and Power Supply Line of a Target with Inserted Glitch

- Glitch Signal On Time  $(GS_{On})$ : The time period how long the rectangular pulsed glitch signal is at  $V_{GS_{High}}$ .

- Glitch Voltage High  $(V_{G_{High}})$ : Voltage level when no glitch is inserted. Normally, this voltage is the required power supply line voltage of a target according to its datasheet.

- Glitch Voltage Low  $(V_{G_{Low}})$ : The lowest voltage level of an inserted glitch.

- Glitch Offset  $(G_{Offset})$ : The time period between the moment the glitch signal rises from  $V_{GS_{Low}}$  to the moment the voltage level of the power supply line voltage falls from  $V_{G_{High}}$ .

- Glitch Width  $(G_{Width})$ : The time period of the inserted glitch from the moment the voltage falls from  $V_{G_{High}}$  until the moment it reaches  $V_{G_{High}}$  again.

- Glitch Fall Time  $(G_{Fall})$ : The time period needed to fall from  $V_{G_{High}}$  to  $V_{G_{Low}}$ .

- Glitch Rise Time  $(G_{Rise})$ : The time period needed to rise from  $V_{G_{Low}}$  to  $V_{G_{High}}$ .

# 4.2 Limitations of Conventional Voltage Fault Injection Attacks

The limitations of the conventional voltage fault injection attacks are explained in this section. Several scientific publications have shown that the success of a glitch depends on the glitch duration  $G_{Width}$  and the glitch depth  $V_{G_{Low}}$  [35, 36]. It may even be necessary that the glitch duration  $G_{Width}$  should not be longer than one clock period. Especially with faster microcontrollers at higher clock speeds, the necessarily shorter glitch durations are becoming increasingly challenging. For a successful glitch, the parameters glitch duration  $G_{Width}$  and glitch depth  $V_{G_{Low}}$  must therefore be as freely adjustable as possible.

In the following, we show that the selection of glitch parameters for the conventional glitch generation method is significantly limited through capacitive charging and discharging effects in the glitch target device. Taking the exemplary schematic for the conventional method (Figure 3.2), the limitations and the resulting tradeoff can be described as follows. Resistor  $R_1$  is necessary to avoid a short-circuit during glitch generation. The glitch target device includes capacitive effects so that during a glitch, the target device needs to be charged or discharged until it reaches the glitch voltage  $(V_{G_{Low}})$ . If a low resistance is chosen for  $R_1$ , pulling down the voltage will lead to a high current flow where the MOSFET and the resistor build a voltage divider. The advantage of using a low resistance at  $R_1$  is the higher supply current that can be used to reach  $V_{G_{High}}$  after a glitch. The necessary discharging  $(G_{Fall})$  and charging time  $(G_{Rise})$  is thus reduced. Unfortunately, this advantage comes at the cost that due to the voltage divider, the achievable glitch voltage  $(V_{G_{Low}})$  will be significantly higher. In the worst case, the lowest possible glitch voltage will not be sufficient to produce a successful glitch. On the other hand, if a high resistance is chosen for  $R_1$ , the achievable glitch voltage  $(V_{G_{Low}})$  will be lower but at the cost of a significantly longer charging time  $(G_{Rise})$ . The minimum length of the glitch  $(G_{Width})$  is thus significantly limited. In the worst case, the achievable glitch length will be longer than a clock period and hence a single instruction can no longer be targeted with a glitch. For this reason, obtaining a short glitch  $(G_{Width})$  and a low glitch voltage  $(V_{G_{Low}})$  at the same time is not feasible in presence of capacitive effects. Instead, the relationship between these parameters is a tradeoff and the attacker can only optimize one of those parameters at a time.

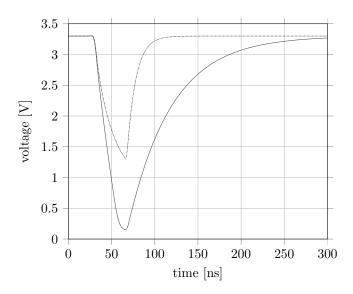

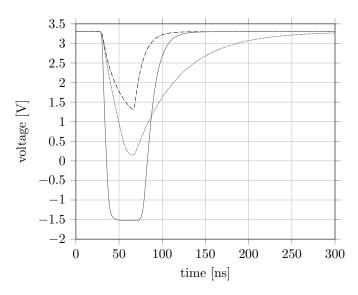

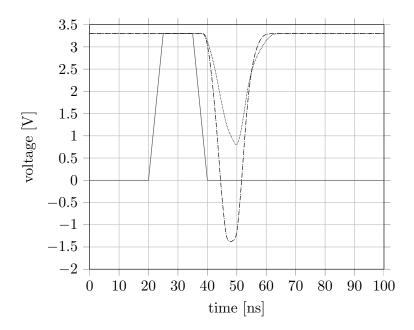

To demonstrate this tradeoff, we conducted two SPICE simulations with the LTSpice<sup>1</sup> tool: Simulation A represents the case where a higher resistance is chosen for  $R_1$  so that a lower glitch voltage  $(V_{G_{Low}})$  can be reached at the cost of a higher charging time  $(G_{Rise})$ . In contrast, in Simulation B a lower resistance is chosen for  $R_1$  to achieve a faster charging time at the cost of a higher glitch voltage  $(V_{G_{Low}})$ . Table 4.1 provides an overview of the used components and their values for these two test cases.

In Figure 4.2, the solid waveform shows the simulation results for Simulation A with an  $R_1$  value of 0.5  $\Omega$  while the dotted waveform shows the results of Simulation B with a

http://www.linear.com/designtools/software/

| Component                        | Simulation A | Simulation B |

|----------------------------------|--------------|--------------|

| Resistor R <sub>1</sub>          | 0.5 Ω        | 0.1 Ω        |

| Resistor R <sub>2</sub>          | 10 kΩ        | 10 kΩ        |

| Capacitor C <sub>1</sub>         | 560 pF       | 560 pF       |

| MOSFET $Q_1$                     | IRF7821 [37] | IRF7821 [37] |

| Power supply voltage level       | 3.3 V        | 3.3 V        |

| Glitch signal voltage level high | 3.3 V        | 3.3 V        |

| Glitch signal voltage level low  | 0.0 V        | 0.0 V        |

| Glitch signal turn on time       | 20 ns        | 20 ns        |

| Glitch signal rise time          | 5 ns         | 5 ns         |

| Glitch signal fall time          | 5 ns         | 5 ns         |

| Glitch signal on time            | 10 ns        | 10 ns        |

Table 4.1: Components and Values used for the Conventional Method LTSpice Simulations A and B

Figure 4.2: Comparison between Simulation A (solid) and Simulation B (dotted)

lower  $R_1$  value of 0.1  $\Omega$  instead. The capacitance of the capacitor  $C_1$  is intentionally chosen high, so that the limitations can be easier illustrated. The described tradeoff between the lowest possible glitch voltage  $(V_{G_{Low}})$  and the shortest possible glitch time  $(G_{Width})$  can be easily seen. For a successful attack, the slew rate (i.e., the glitch falling time  $G_{Fall}$  as well as the glitch rising time  $G_{Rise}$ ) has to be improved in presence of the capacitance and the following limitations.

# 4.3 Expected Results of Negative Voltage Fault Injection Attacks

The hypothesis of this work is that negative voltage fault injection attacks provide advantages over their conventional counterparts with respect to higher slew rates and shorter glitch durations in presence of capacitive and inductive charges within microcontrollers. Utilizing negative voltage during the generation of a fault, higher slew rates are expected due to the faster discharging of the circuit implementations within microcontrollers.

Figure 4.3: Extended Conventional Glitch Generation Method

To consider negative glitch voltages, we extend the conventional glitch generation method with a negative voltage supply as illustrated in Figure 4.3. Similar to Simulation B in the previous section, the current limitation is minimized by using a very small resistance for  $R_1$ . Although this minimization leads to an idealized very high current flow that is not feasible in practice (see Section 5.2.1 for details), the model allows to highlight the key concepts of negative voltage faults. In contrast to the conventional method, the source of MOSFET  $Q_1$  is not connected to GND, but to a variable negative voltage supply instead.

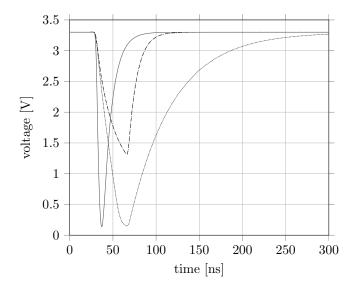

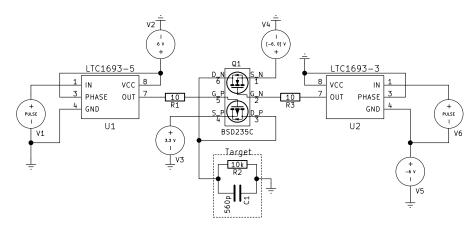

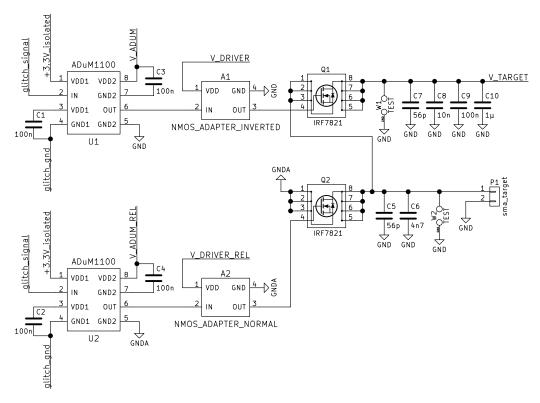

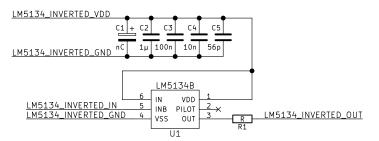

To compare the conventional voltage fault injection method with negative voltage fault injections, we conducted two simulations with different glitch signal on times  $(GS_{On})$ . In Simulation C, we use a glitch signal on time of 10 ns while Simulation D uses a significantly shorter time of 2.1 ns. The components and values used in the simulations are illustrated in Table 4.2.

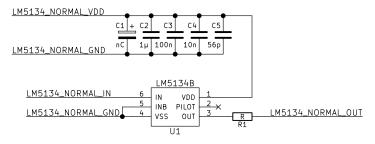

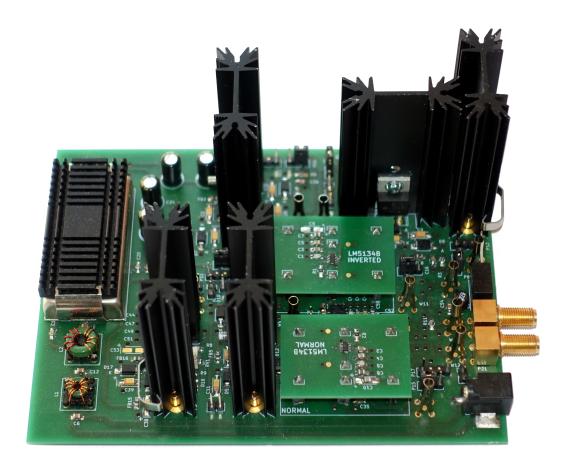

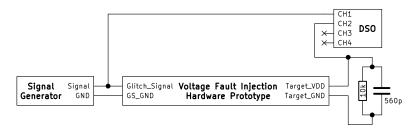

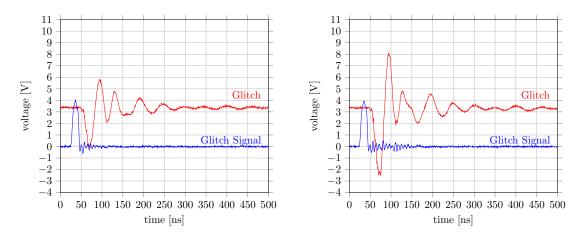

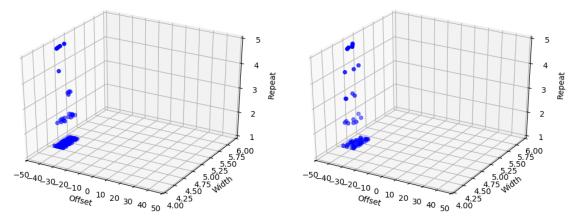

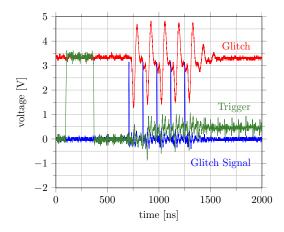

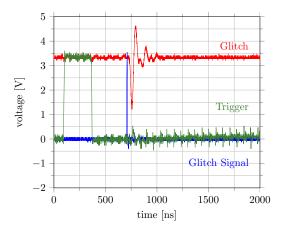

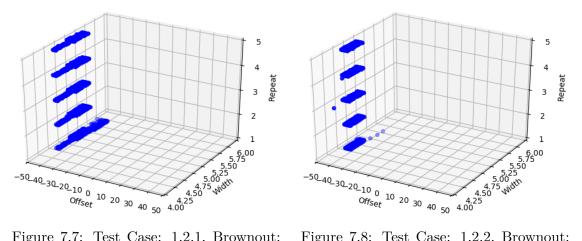

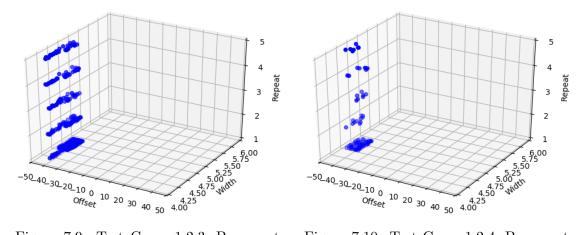

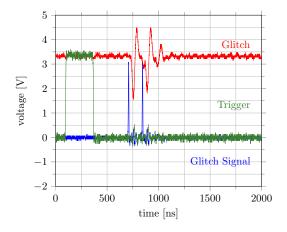

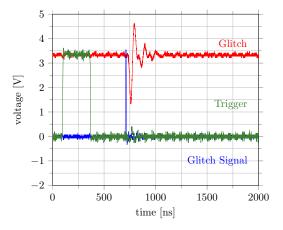

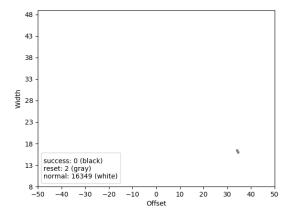

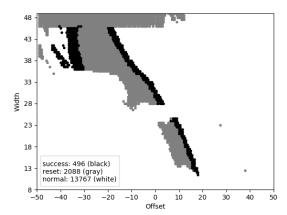

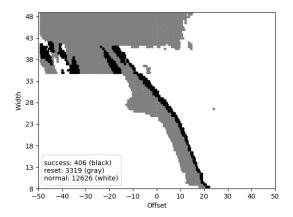

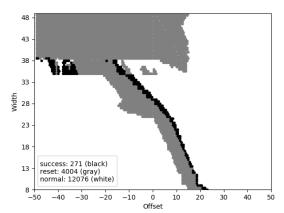

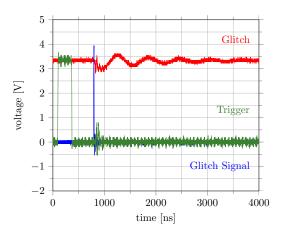

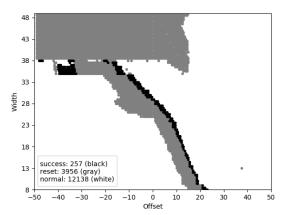

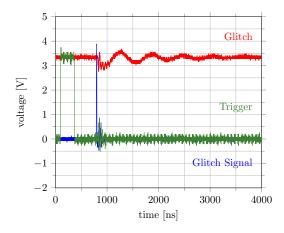

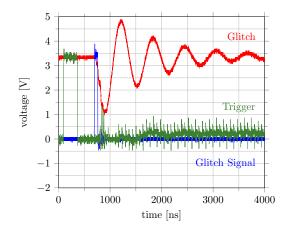

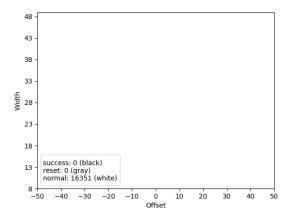

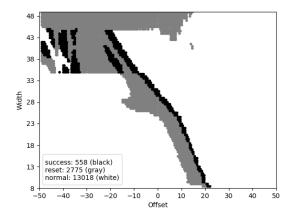

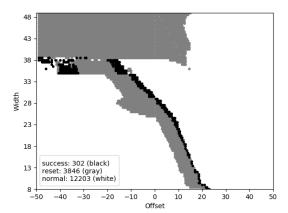

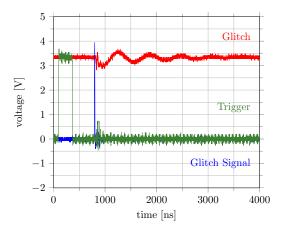

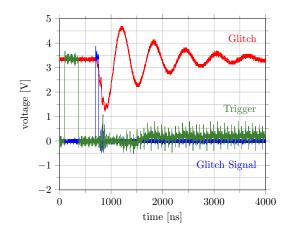

Simulation C is visible in Figure 4.4. The solid waveform shows the effect of the negative voltage glitch. Similarly to the conventional voltage fault injection, the resistor  $R_1$  and the MOSFET build a voltage divider so that the voltage  $V_{G_{Low}}$  does not reach the negative supply voltage level. However by choosing the negative supply voltage level accordingly, we can arbitrarily select  $V_{G_{Low}}$ . The high voltage differential between the power supply voltage level  $V_{G_{High}}$  and the glitch voltage  $V_{G_{Low}}$  causes a low fall time  $G_{Fall}$ . After the glitch, a low rise time  $G_{Rise}$  is achieved due to the low resistance of  $R_1$ . In contrast, the dotted and dot-dashed waveforms show the results of the simulation