## **DIPLOMA THESIS**

# Multiphase Switch-Mode BCM Controllers – Design Challenges in CMOS Implementation

supervised by

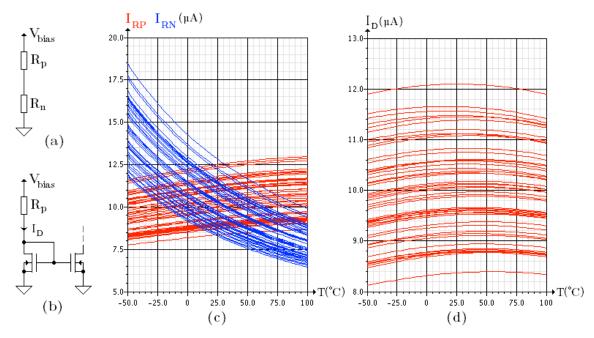

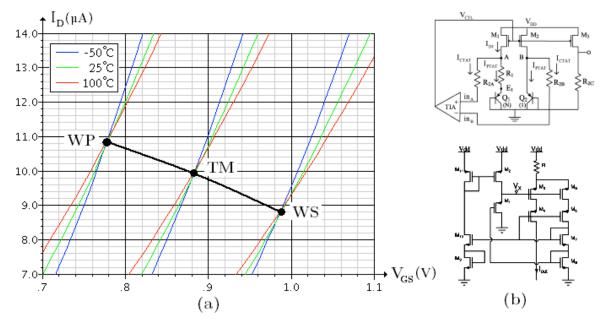

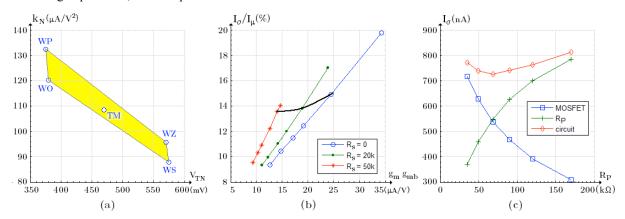

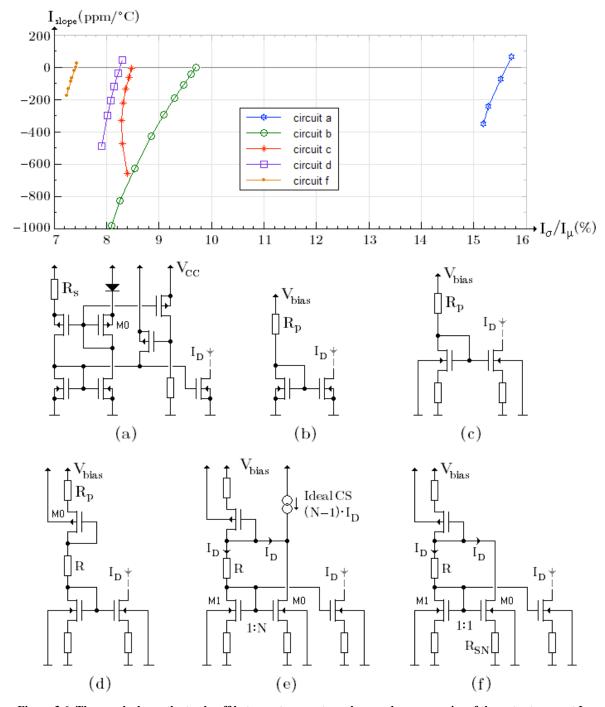

Univ.Prof. Mag.rer.nat. Dr.techn. Horst Zimmermann

performed at the Institute of Electrodynamics, Microwave and Circuit Engineering

by Jeff Graw, BSc. Matr. no. 0926400 Siebenbrunnengasse 7/6, 1050 Wien

Vienna, May 2015

#### Abstract

As population and demand for energy grow, global fossil fuel reserves decline at an alarming rate. The industry has responded with increasingly aggressive and environmentally destructive extraction techniques to supply the global energy demand. For example, oil extraction from the open tar sands pits in Canada is creating a massive environmental dead-zone which will be large enough to be seen from the moon. But declining reserves and environmental damage are only part of the problem; energy-related trade deficits burden entire countries with loans to central banks that can never be repaid, and interest payments that compound the debt.

Fortunately engineering is responding to the problem, and significant progress is being made. Local distributed energy production from renewable resources is reducing some of the burden in meeting the growing demand for energy, and large untapped reserves exist. But the silent revolution occurring is improved device and system efficiency. For instance, LED lights produce the same luminous flux at 8W that a 60W incandescent bulb once produced. Distributed among millions of homes, such energy-saving devices are having a far larger impact than could be seen from new energy production.

Advances in power systems are equally impressive. Today, a state-of-the-art commercial 50kW power converter operating at hundreds of amps will have a conversion efficiency exceeding 99%. But improvements in consumer goods have a potentially larger energy-saving impact. New consumer products should have high operational efficiencies *and* large converter dynamic range to reduce the vampire load in standby mode. Switch-mode efficiency is optimized by minimizing the combined switching, ohmic, and core losses. Multiphase systems help distribute the load, reducing losses and filter requirements, and improving the power factor. In this thesis some of the improvements that have been developed and new trends in published research are reviewed. The discussion is organized as follows:

- Chapter 1: The relative advantages and disadvantages of switch-mode operating modes are discussed. A comparison of the ohmic, switching, and magnetic core losses is made between continuous conduction (CCM) and boundary conduction (BCM) operating modes.

- Chapter 2: A survey of multiphase (master-slave) BCM controllers is made. Open-loop controllers in both current- and voltage-mode are compared for stability and relative advantages/disadvantages. A promising alternative to open-loop control is the closed-loop controller. It has a wider range of stable voltage-mode operation, provided technical issues are resolved in the design. A developing trend in multiphase converters is the coupled-inductor design; the windings of two or more phases are wound on the same magnetic core. Energy is coupled directly from the magnetizing phase to the demagnetizing phase via the mutual coupling, thus reducing the energy stored in the core. Such coupling can improve efficiency by reducing the core and ohmic losses.

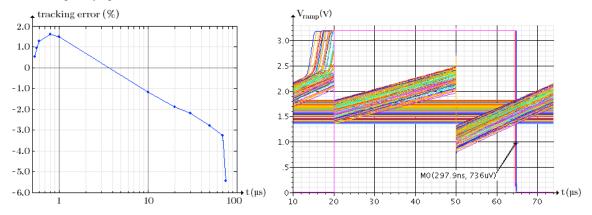

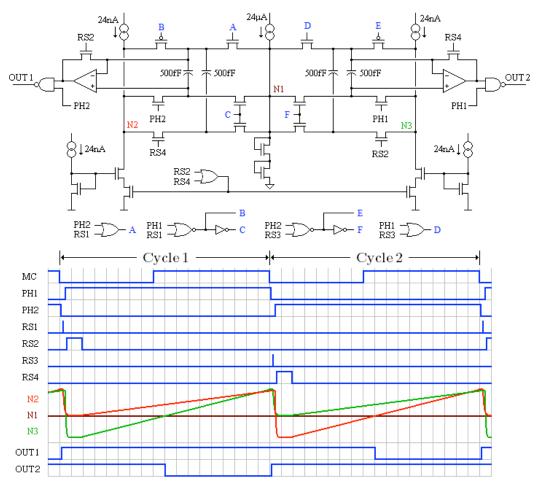

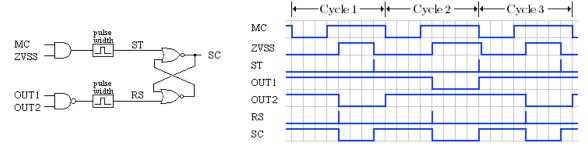

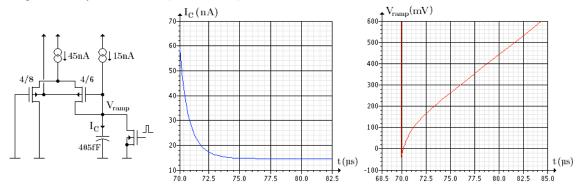

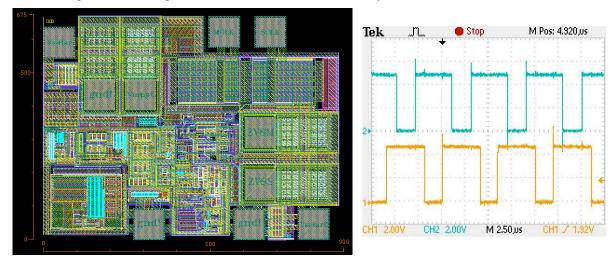

- Chapter 3: The industry trend is toward cheaper, compact integrated designs; an investigation is made into the practical issues of integrating a switch-mode controller in silicon. While the nominal design is straightforward, many problems are encountered when temperature effects, CMOS process variations, and component mismatches are included. Central to timing generation is a current reference, and various feedback techniques to help stabilize the current source against process and temperature are examined. A typical current source will have a 50% process-related current spread, and current mirroring into the nano-amp range adds a 30% mirroring error. A dual-slope ramp with correlated double sampling is used to cancel these errors, and only a 2% tracking error is seen in the final timing. Comparators are another component of the timing circuit with process-related problems. A rail-to-rail comparator with input hysteresis can latch at the rails on certain process corners; the comparator is also plagued with low gain on some process corners and input voltages. These problems could leave the controller in an uncontrolled (latched) or unknown (meta-stable) state, with disastrous consequences for the converter. To guarantee a robust design, these errors cannot be allowed to occur under any combination of process variation, operating condition, and system noise. Reset injection charge was used to prevent comparator latching errors. Additionally, a digital pulse-width conditioning circuit and the comparator output slew rate form a bandpass filter for system noise; when a minimum output slew rate is guaranteed, the bandwidth of this filter goes to zero and the design guarantees a meta-stable condition can never occur. The most challenging aspect of CMOS integration was the dynamic range that could be guaranteed by the design; a nominal-model dynamic range of 200 dropped to only 50 when the process corners were considered, and some corners saw high chip failure rates. The strategic use of injection charge, and delayed injection charge cancellation, was explored to address these problems. But to be truly competitive with discrete controllers, a nonlinear adaptive current reference is proposed that guarantees a dynamic range of more than 200. Such adaptations provide the needed performance to compete with discrete voltage-mode controllers, and to classify it as a "universal" BCM controller design.

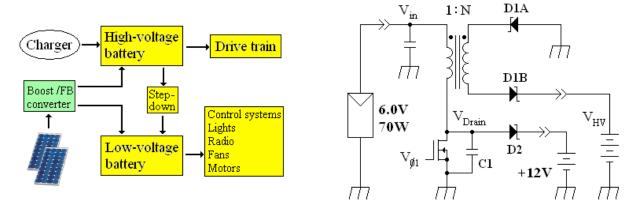

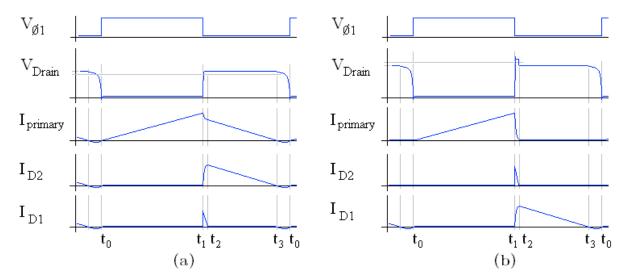

• Chapter 4: In this chapter an investigation is made of a class of hybrid converters capable of supplying two power outputs. These converters are useful in systems where a high-voltage output interfaces to a power train or utility grid, and a low-voltage output drives control systems. The boost-flyback converter is capable of adaptively directing power to two outputs, with charging priority given to the output with the heaviest load. This adaptive nature of the converter simplifies the controller requirements and hardware. However, a problem encountered with high-voltage flybacks is the inter-winding capacitance. In a high-voltage, low-current secondary circuit the energy needed to charge and discharge this capacitance can exceed the energy in the inductor windings. When this happens the converter will not start up, and the minimum power the converter can operate at is increased. The problem is addressed in the transformer design by reducing the parasitic capacitance of the windings. Depending on the design, the number of winding layers, wire density per layer, dielectric thickness between layers, direction the secondary is wound with reference to the primary, selecting which secondary layer is closest to the primary, selecting how the layers are wound, and the circuit configuration can be designed to reduce the winding capacitances. Design examples are discussed, and test results for a 330V design capable of operating down to a watt is shown.

BCM converters are an important emerging class of energy-saving power systems; in this thesis the question is raised as to whether a BCM controller implemented in silicon can achieve the same performance seen in controllers implemented with discrete components. Two requirements were imposed on the conceptual model. First, no failures should occur as the result of any combination of CMOS process variations, component mismatch errors, and converter operating conditions; preventing these failures means that some expensive production testing can be avoided. The second requirement was that the dynamic range should be large enough that a "universal controller" is developed. The dynamic range must be the guaranteed range when all process corners are considered. This would create portability, allowing the same controller to be used in different product designs.

6-sigma simulations are not sufficient to guarantee design robustness. A better approach is to look for mismatch errors using Monte Carlo simulation run from the weak process corners. The conclusions are drawn from these simulations and testing.

Although many problems were encountered, and every solution seemingly created new problems, in the end these problems were resolved through design. The conclusion then is that power systems controllers can be implemented in CMOS with no loss of controller performance. For large-scale production, replacing a PC board full of components with a single chip offers an attractive option in reducing product size, weight, and manufacturing costs. It is an option that should be considered seriously.

## Kurzfassung

Aufgrund des Wachstums der Weltbevölkerung und des daraus resultierenden immer höher werdenden Energiebedarfs, steigt der globale fossile Brennstoffverbrauch bei endlichen Reserven alarmierend an. Daher versucht die Industrie, diesem mit immer aggressiveren und immer umweltbelastender werdenden Fördermethoden entgegenzuwirken. Als Beispiel kann hier die Ölgewinnung aus Ölsand im Tagbau in Kanada genannt werden, welche eine massive ökologische Todeszone zur Folge hat, die sogar bald vom Mond aus zu sehen sein wird. Die immer geringer werdenden fossilen Brennstoffreserven, als auch die Umweltverschmutzung sind nur ein Teil des Problems. Aufgrund eines energiebedingten Handelsbilanzdefizits sind ganze Staaten dazu gezwungen, Kredite bei den jeweiligen Zentralnotenbanken aufzunehmen, welche aber nie zurückgezahlt werden können und darüber hinaus zusätzliche Belastungen aufgrund von Zinszahlungen bewirken.

Glücklicherweise nehmen sich die Ingenieurwissenschaften dieses Problems an, wobei signifikante Fortschritte gemacht werden. Lokale Energiegewinnung aus erneuerbaren Ressourcen vermindert einige Probleme, die durch den steigenden Energiebedarf versursacht werden, und in diesem Bereich sind noch einige Reserven vorhanden, die noch nicht genutzt werden. Die stille Revolution erfolgt auch aufgrund von optimierten Geräten und verbesserter Systemeffizienz. Als Beispiel können hier LED-Lampen angeführt werden, die bei einem Leistungsverbrauch von 8W die gleiche Beleuchtungsstärke wie eine alte 60W Glühbirne liefern. Bei einer flächendeckenden Verwendung durch Millionen von Verbrauchern haben solche energiesparenden Mittel eine viel größere Wirkung als die Erzeugung neuer Energien.

Der Fortschritt im Bereich der Stromversorgung ist beindruckend. Nach dem heutigen Stand der Technik hat ein industrieller 50kW Stromrichter, welcher bei Stromstärken von mehreren Hundert Ampere arbeitet, einen Wirkungsgrad, der sogar 99% überschreiten kann. Aber Verbesserungen und Optimierungen in elektrischen Konsumgütern haben einen potentiell noch größeren Energiespareffekt. Neuere Konsumgüter sollten dabei eine hohe Effizienz aufweisen und eingebaute Konverter sollten einen hohen Dynamikbereich besitzen, um den parasitären Verbrauch im Stand-by Modus zu verringern. Der Wirkungsgrad von Schaltnetzteilen kann mittels einer kombinierten Minimierung von Schaltverlusten, ohmschen Verlusten und Transformatorverlusten optimiert werden. Multiphasensysteme helfen die Last zu verteilen, die Verluste und Filteranforderungen zu reduzieren und den Leistungsfaktor zu verbessern. In dieser Masterarbeit werden einige Verbesserungen, die entwickelt wurden und die neue Trends in der Forschung darstellen, behandelt. Die Arbeit ist, wie folgt, aufgebaut:

- Kapitel 1: Die jeweiligen Vor- und Nachteile von verschiedenen Ansätzen in der Arbeitsweise von Schaltnetzteilen werden behandelt. Es wird ein Vergleich der ohmschen Verluste, der Schaltverluste und der Transformatorkernverluste bei einem Continuous-Conduction-Mode Wandler (CCM, Betrieb mit kontinuierlichem Strom) und einem Boundary-Conduction-Mode Wandler (BCM) angestellt.

- Kapitel 2: Ein Überblick über Multiphasen (Master-Slave) BCM Regelungen wird gegeben. Dabei werden verschiedene Steuerschaltungen ohne Regelkreis (sowohl Strom-, als auch als Spannungsregler) betrachtet und deren Stabilität, Vor- und Nachteile verglichen. Eine vielversprechende Alternative zur offenen Regelung sind Steuerschaltungen in einer geschlossenen Regelschleife. Diese haben einen weiten stabilen Bereich im Spannungsbetrieb, unter der Voraussetzung, dass einige technische Probleme gelöst werden. Ein Entwicklungstrend im Bereich der Multiphasenkonverter ist ein Design mit gekoppelten Spulen; die Windungen von zwei oder mehr Phasen sind auf demselben magnetischen Kern aufgewickelt. Die Energie wird direkt von der Magnetisierungsphase zur Entmagnetisierungsphase über gegenseitige Kopplung übertragen, wobei die Energie, welche im Kern gespeichert ist, vermindert wird. Solch eine Kopplung kann die Effizienz durch Reduzierung der Kernverluste und der ohmschen Verluste verbessern.

- Kapitel 3: Der Trend in der Industrie geht in Richtung billiger und kompakt integrierter Lösungen; eine Untersuchung der praktischen Aspekte von integrierten Schaltwandlersteuerungen in Silizium wurde gemacht. Obwohl das zugrundeliegende Schaltungskonzept unkompliziert wirkt, treten viele Probleme auf, da man Details wie Temperatureffekte, CMOS Prozessvariationen und Bauteildiskrepanzen mitberücksichtigen muss. Die Erzeugung einer Zeitbasis für die Schaltvorgänge basiert auf einem Referenzstrom. Daher werden unterschiedliche Rückkoppeltechniken, die die Stromquelle gegen Temperatur- und Prozessvariationen stabilisieren sollen, untersucht. Eine typische Stromquelle hat eine prozessverursachte Stromvariation, ausgehend vom nominalen Wert, von 50%, wobei einfache Stromspiegel für den Nano-Amperebereich noch 30% Fehler hinzufügen. Die Fehler werden mit Hilfe von einem Zweirampenansatz (positive und negative Steigung) mit korrelierter Doppelabtastung behoben, wobei als Resultat nur mehr 2% Fehler in der resultierenden Zeitgebung auftreten. Weitere Komponenten der Zeitgeberschaltung, wo prozessbezogene Probleme entstehen können, sind Komparatoren. Ein Komparator mit Eingangshysterese und mit einem Ausgangsspannungshub, der den kompletten Versorgungsspannungsbereich abdeckt (rail-to-rail), kann aufgrund des Auftretens von extremen Prozessungleichheiten falsch schalten, wobei kleine Verstärkungen und niedrige

Eingangsspannungen das Problem vergrößern. Diese Probleme könnten die Steuerschaltung in einem unkontrollierten oder undefinierten (keine Entscheidung des Komparators) Zustand belassen, was schlimme Konsequenzen für den Konverter hätte. Um ein robustes Design zu garantieren, darf nicht zugelassen werden, dass solche Fehler in jeder möglichen Kombination von Prozessvariationen, Arbeitszuständen und Systemrauschen, auftreten. Injizierte Schaltladungen wurden während des Zurücksetzens (Reset) verwendet, um Schaltfehler des Komparators zu vermeiden. Zusätzlich bilden eine Schaltung zur digitalen Pulsbreitenkonditionierung und die Flankensteilheit des Komparators am Ausgang einen Bandpassfilter für das Systemrauschen; wenn eine minimale Ausgangsflankensteilheit sichergestellt ist, geht die Bandbreite dieses Filters gegen Null und ein metastabiler Zustand kann nie auftreten. Die größte Herausforderung in der CMOS-Schaltungsentwicklung war der Aussteuerbereich, welcher vom Design garantiert werden konnte; ein nominaler dynamischer Bereich von 200 sank unter Berücksichtigung von extremen Prozessvariationspunkten auf 50, wobei hohe Fehlerraten in einigen Prozessvariationsecken auftraten. Um eine Lösung dafür zu finden, wurde der gezielte Gebrauch von Schaltinjektionsladungen und verzögerte Injektionsladungsauslöschung untersucht. Aber um wirklich mit diskreten Steuerschaltungen wettbewerbsfähig zu sein, wird eine nichtlineare, adaptive Stromreferenz vorgeschlagen, um einen dynamischen Aussteuerbereich von mehr als 200 zu garantieren. Solche Anpassungen liefern das benötigte Verhalten, um mit diskreten Spannungsreglern konkurrieren zu können und um das Design als "universelle" BCM Schaltung zu klassifizieren.

Kapitel 4: In diesem Kapitel wird eine Klasse von Hybridwandlern untersucht, die zwei Ausgänge zur Versorgung besitzen. Diese Wandler werden in Systemen gebraucht, wo ein Hochspannungsausgang an ein Aggregat oder ein Servicenetz angekoppelt wird und wo gleichzeitig ein Niederspannungsausgang Kontrollsysteme versorgt. Der Aufwärtssperrwandler kann die Leistungen, die an zwei verschiedene Ausgänge geliefert werden, anpassen, wobei die höchste Priorität dem Laden jenes Ausgangs mit der größeren Last gilt. Diese Adaptionsmöglichkeit des Wandlers vereinfacht die Anforderungen an den Regler und an die Hardware. Ein Problem, das man bei Hochspannungssperrwandlern antrifft, ist die Kapazität zwischen den Windungen der Spulen. In einer anschließenden Schaltung, die im Hochspannungs- und Niederstrombereich arbeitet, kann die Energie, die zum Laden oder Entladen dieser Kapazitäten gebraucht wird, die Energie in den Spulen übertreffen. In einem solchen Fall kann der Wandler nicht starten und die minimale Leistung, mit der der Wandler arbeitet, ist erhöht. Hier kann beim Design des Transformators Abhilfe geschaffen werden, wobei die parasitären Kapazitäten der Windungen reduziert werden müssen. In Abhängigkeit vom Design können die Anzahl der Windungsebenen, die Drahtdichte per Ebene, die dielektrische Dicke zwischen den Ebenen, die Wicklungsorientierung der sekundären Spule im Vergleich zur primären Spule, die Lage der sekundären Wicklungsebene im Verhältnis zur primären Ebene, die Art der Windung der Ebenen und die Schaltungsstruktur ausgesucht werden, um die Wicklungskapazitäten zu reduzieren. Es werden Beispiele von Designs erörtert und Testergebnisse einer 330V-Lösung, die bis zu einem Watt herab arbeitet, präsentiert.

BCM Wandler sind eine wichtige, aufkommende Klasse von energiesparenden Stromversorgungsystemen. In dieser Arbeit wird die Frage aufgeworfen, ob eine in Silizium integrierte BCM Steuerschaltung die gleiche Arbeitsleistung erreicht wie eine Schaltung, die aus diskreten Bauteilen aufgebaut wurde. Es werden zwei Anforderungen an das konzeptuelle Modell gestellt. Erstens sollten keine Fehler auftreten, die durch mögliche Prozessvariation, durch Bauteilungleichheiten und durch Arbeitsbedingungen des Wandlers entstehen können. Die Vermeidung solcher Fehler bedeutet, dass einige teure Produktionstests unterlassen werden können. Die zweite Anforderung ist, dass der dynamische Bereich groß genug sein soll, sodass eine universelle Steuerschaltung entwickelt werden kann. Der dynamische Bereich muss jener garantierte Bereich sein, wo alle extremen Technologietoleranzecken berücksichtigt sind. Dies würde Übertragbarkeit bringen, wobei dann der gleiche Regler in unterschiedlichen Produkten verwendet werden kann.

6-Sigma Simulationen sind nicht ausreichend, um ein robustes Design zu garantieren. Stattdessen wurden aufgrund von Ungleichheiten wegen der auftretenden Toleranzen der Technologie, Monte-Carlo Simulationen durchgeführt, um schlechte Konstellationen in der Toleranzvariation bei einer gegebenen Bauteilanordnung zu finden. Aus diesen Simulations- und Testergebnissen wurden dann Schlussfolgerungen gezogen.

Obwohl viele Probleme auftraten und jede Lösung scheinbar ein neues Problem hervorgerufen hat, wurde am Ende erkannt, dass diese Probleme durch ein gutes Design gelöst werden können. Schlussfolgernd kann man sagen, dass Stromversorgungssystemsteuerungen in CMOS Technologien ohne Verminderung der Arbeitsleistungsfähigkeit implementiert werden können. Für Großproduktionen wäre das Ersetzen einer Printplatte voller elektronischer Bauteile mit einer einzelnen integrierten Schaltung eine attraktive Option, um Produktgrößen, Gewicht und Produktionskosten zu reduzieren. Diese Möglichkeit sollte ernsthaft in Betracht gezogen werden.

## Acknowledgement

To the thousands of scientists and engineers who dedicated their lives to expanding our knowledge of the physical universe, for creating the discipline that we call engineering, and the field we know as electronics: may we honor your trust with its safekeeping.

This work was funded by the Austrian Federal Ministry for Transport, Innovation and Technology (BMVIT) via the Austrian Research Promotion Agency (FFG), by the European Nanoelectronics Initiative Advisory Council Joint Undertaking (ENIAC JU) in the Project Energy Efficient Electric Car (E3Car), and by AMS-AG and Vienna Hochschuljubiläumsstiftung. I would like to express my gratitude to these organizations for their financial support and the vision in making such projects possible.

I would also like to thank my colleagues from the Institute of Electrodynamics Microwave Circuit Engineering for their technical support in using Cadence. Wolfgang Gaberl and Reinhard Enne helped me through the difficult task of deciphering software errors and design rule checks. Additionally, I want to thank Harald Gall from AMS-AG for providing the services of producing the ASICs. My officemate Bernhard Goll graciously translated the abstract. In this I am reminded that every accomplishment is ultimately a team effort.

Finally, my most sincere appreciation goes to Univ. Prof. Dr.-Ing. Horst Zimmermann for his support and for the opportunity to participate in this research project, and to my wife Tanya for her financial and moral support through this long journey. Additional thanks go to Reinhard, Tanya, and Professor Zimmermann for their careful review of this document. And to my parents who taught me, if a job's worth doing, it's worth doing right.

# Contents

| Abstract                                             | i          |

|------------------------------------------------------|------------|

| Kurzfassung                                          | iii        |

| Acknowledgement                                      | v          |

| 1. Basic principles of power converters              | 1          |

| 1.1 Ripple currents                                  | 2          |

| 1.2 Ohmic losses                                     |            |

| 1.3 Switching losses: dynamic power dissipation      | 4          |

| 1.4 Dynamic switching losses as the switch turns on  | 4          |

| 1.5 Dynamic switching losses as the switch turns off | 6          |

| 1.6 Magnetic core losses                             |            |

| 1.7 CCM/BCM loss comparison                          |            |

| 1.8 Why use BCM?                                     |            |

| 1.9 References                                       |            |

| 2. Multiphase Interleaved BCM controllers            |            |

| 2.1 Basic BCM operation                              |            |

| 2.2 System diagram                                   |            |

| 2.3 Interleaving converter phases                    | 14         |

| 2.4 Open-loop controllers                            | 14         |

| 2.5 Closed-loop controllers                          |            |

| 2.6 Coupled-inductors                                |            |

| 2.7 References                                       |            |

| 3. Controller integration in silicon                 | 25         |

| 3.1 Current sources                                  |            |

| 3.1.1 Temperature and power supply variations        |            |

| 3.1.2 CMOS process variations                        |            |

| 3.2 Master controller                                |            |

| 3.2.1 Ramp generator circuit                         |            |

| 3.2.2 Rail-to-rail comparator                        |            |

| 3.2.3 Ramp reset timing                              |            |

| 3.3 Slave controller                                 |            |

| 3.3.1 Phase-lock ½ cycle delay tracking circuit      |            |

| 3.3.2 Slave controller circuit                       |            |

| 3.4 Current sources II                               |            |

| 3.5 Integrated CMOS controllers                      |            |

| 3.6 References                                       | 48         |

| 4. Application and results                           |            |

| 4.1 Boost-flyback converter                          |            |

| 4.2 Transformer design                               |            |

| 4.3 Test results                                     |            |

| 4.4 References                                       | 56         |

| 5 Complusion                                         | <b>5</b> 0 |

# **Abbreviations & Symbols**

A area

AC alternating current

$A_{center}$  cross-sectional area of center  $A_{core}$  cross-sectional area of core

$A_{gap}$  effective gap area AMS Austria Microsystems

ASIC application-specific integrated circuit

A<sub>V</sub> differential voltage gain

B magnetization

B current mirror gain

BCM boundary conduction mode CCM continuous conduction mode

C capacitance

C1... capacitor reference identifier

C<sub>drain</sub> drain capacitance

CDS correlated double sample  $C_{DS}$  drain-to-source capacitance

C<sub>gate</sub> gate capacitance

$C_{GD}$  gate-to-drain capacitance  $C_{GS}$  gate-to-source capacitance

CK clock

CMOS complementary metal-oxide-semiconductor

CMP comparator

C<sub>ox</sub> gate oxide capacitance

C'primary transformer secondary inter-winding capacitance reflected into the primary

CRT cathode ray tube

CS current source

$C_{secondary}$  transformer secondary inter-winding capacitance

CTAT complimentary-to-absolute temperature

CW clockwise D duty cycle

D1... diode reference identifier

dB decibel

DC direct current

DCM discontinuous conduction mode

DL delay line

DP differential pair

DSL dynamic switching loss

\*Emf electromotive force

ESD electrostatic discharge

ESR equivalent series resistance

f<sub>c</sub> converter frequency

FET field-effect transistor

$FF_M/FF-M$  master flip-flop  $FF_S/FF-S$  slave flip-flop

g<sub>m</sub> transconductance

$g_{mb} \hspace{1cm} transconductance \ due \ to \ body \ effect$

H magnetic field intensity

$H_{core}$  magnetic filed in the core material  $H_{gap}$  magnetic field in the air gap

H<sub>UGC</sub> ideal magnetic field intensity if the core was ungapped

$I_0$  initial current  $I_D$  drain current

I<sub>gate</sub> transient gate current

I<sub>in</sub> input current

I<sub>Invtr</sub> inverter current during switching

I<sub>L</sub> inductor current

$I_{Leq}$  the equivalent current in an uncoupled inductor with inductance  $L_{eq}$

I<sub>LM</sub> inductor current of the master phase

I<sub>Lpk,ref</sub> reference control voltage for the desired peak current

$I_{Lpk,ref-M}$  reference control voltage for the desired peak current of master phase  $I_{Lpk,ref-S}$  reference control voltage for the desired peak current of slave phase

$I_{LM,peak}$  peak master phase inductor current in steady-state operation

I<sub>LS</sub> inductor current of the slave phase

$I_{LU}$  equivalent inductor current in an uncoupled inductor with inductance  $L_{eq}$

I<sub>LU,peak</sub> peak current of the equivalent uncoupled inductor

I<sub>mirror</sub> output current from the current mirror

I<sub>peak</sub> peak current

$I_{peak\;dischrg} \quad \ peak\;current\;during\;discharge$

$I_{out}$  output current

I<sub>primary</sub> current in the transformer primary winding

$I_{rampM}$  ramp current of master  $I_{rampS}$  ramp current of slave

$I_{RN}$  return-side current contribution under nominal bias of a simple current source  $I_{RP}$  supply-side current contribution under nominal bias of a simple current source

I<sub>slope</sub> current slope

$I_{\sigma}$  standard deviation of simulated current

$\begin{array}{ll} I_{\mu} & \text{mean simulated current} \\ k & \text{coupling coefficient} \end{array}$

$\begin{array}{ll} k_N & & transconductance\ parameter\ for\ NMOS \\ k_P & & transconductance\ parameter\ for\ PMOS \end{array}$

kT/C mean-square thermal voltage noise across a capacitor

L inductor reference designator

L MOSFET channel length

LCD liquid crystal display

$l_{core}$  field path length through magnetic core

LED light-emitting diode

$l_{\rm gap}$  magnetic core air gap length L' MOSFET channel length

L<sub>eq</sub> equivalent inductance of an uncoupled inductor

$L_M$  inductance of master phase  $L_S$  inductance of slave phase

M mutual inductance

M1... MOS transistor reference designator

MC master clock

MOSFET metal-oxide-semiconductor field-effect transistor

MPPT maximum power point tracking

N number of turns in the inductor winding

N current mirror gain

N transformer turns ratio

N1... schematic node

NED negative edge detector NMOS n-channel MOSFET

OUT1... outputs from the ramp generator circuit, resets the slave clock

P<sub>DPD</sub> dynamic power dissipation switching loss

P<sub>DSL</sub> dynamic switching loss

PH1... control signals

P<sub>inverter</sub> power dissipated in the inverter during switching

P<sub>LM</sub> power in the master phase inductor

P<sub>LU</sub> power in an equivalent uncoupled inductor

PMOS p-channel MOSFET POR power-on reset

PTAT proportional-to-absolute temperature

P(t)<sub>CH</sub> power dissipated in the MOSFET channel

Q Flip-flop output clock QN Flip-flop output clock\_not

$Q_{drain}$  drain charge  $Q_{gate}$  gate charge

$r_{o}$  impedance looking into MOSFET drain  $r_{out}$  impedance looking into the output node

R resistor reference designator

R S-R latch input: reset

$\mathcal{R}_{core}$  magnetic reluctance in the core material

$\mathcal{R}_{gap}$  magnetic reluctance of the air gap

R<sub>CH</sub> MOSFET (drain-to-source) channel resistance when the switch is on

R<sub>DR</sub> output impedance of gate driver

R<sub>DS</sub> MOSFET drain-to-source small-signal resistance when used as a current source

R<sub>L</sub> load resistance

$R_{

m N}$  equivalent impedance of the load-side in a summing node  $R_{

m P}$  equivalent impedance of the supply-side in a summing node

RS1... ramp circuit reset interval RS S-R latch control signal: reset

R<sub>S</sub> added source resistance to induce the MOSFET body effect

S S-R latch input: set

S<sub>1</sub> PSPICE primitive voltage-controlled resistor (switch)

SC slave clock

S-R latch set-reset digital latch

ST S-R latch control signal: set

t time

$\begin{array}{lll} t_{cycle/}T_C & cycle \ period \\ t_d & delay \ time \\ T\text{-}FF & toggle \ flip\text{-}flop \\ t_{in} & input \ period \\ t_{off} & off \ period \\ t_{out} & output \ period \\ TM & transient \ model \end{array}$

$T_{SW}$  period of the master clock U1... component reference identifier

u<sub>B</sub> energy density

$\begin{array}{ll} U_C & \text{energy stored in capacitive reactance} \\ U_L & \text{energy stored in inductive reactance} \\ V_{bias} & \text{bias voltage for analog circuits} \end{array}$

$V_{BG}$  body to gate voltage

V<sub>core</sub> core volume

$V_{control}$  control signal for the ramp generator

V<sub>D1...</sub> diode voltage

$V_{DD/CC}$  digital supply voltage  $V_{drain}$  drain-node voltage

V<sub>DS</sub> MOSFET drain-to-source voltage

V<sub>gate</sub> MOSFET gate voltage

$\begin{array}{ll} V_{GB} & MOSFET \ gate-to-body \ voltage \\ V_{GS} & MOSFET \ gate-to-source \ voltage \\ V_{HV} & voltage \ of \ high-voltage \ battery \ stack \end{array}$

$V_{\text{hysteresis}}$  hysteresis voltage  $V_{\text{in}}$  input voltage

$\begin{array}{ll} V_{Invtr} & & inverter\ voltage\ (input\ and\ output) \\ V_{L} & & applied\ voltage\ across\ inductor \\ V_{offset} & & offset\ voltage\ /\ input\ offset \end{array}$

$\begin{array}{ll} V_{ON} & & \text{on-voltage} \\ V_{out} & & \text{output voltage} \end{array}$

V<sub>pp</sub> peak-to-peak voltage

V<sub>R</sub> voltage drop across resistor

$V_{Ramp} \qquad \quad ramp \ voltage$

$\begin{array}{lll} V_{RampM} & ramp \ voltage \ of \ master \\ V_{rms} & root-mean-squared \ voltage \\ V_{S} & MOSFET \ source \ voltage \\ V_{th} & MOSFET \ threshold \ voltage \\ V_{TN} & NMOS \ threshold \ voltage \\ V_{TP} & PMOS \ threshold \ voltage \\ \end{array}$

W width

W' MOSFET channel width

WO worst-case one process corner

WP worst-case power process corner

WS worst-case speed process corner

WZ worst-case zero process corner

XOR exclusive OR

ZCD-M zero-current detect signal of master ZCD-S zero-current detect signal of slave

ZCS zero-current switchingZTC zero temperature coefficientZVS zero-voltage switching

$\delta k_N$ ... transconductance process variation...

$\begin{array}{ll} \Delta B & \quad \mbox{peak-to-peak magnetization} \\ \Delta I_L & \quad \mbox{peak-to-peak inductor current} \end{array}$

$\Delta L$  inductance variation

Δt time interval

Δt<sub>in</sub> control signal timing error

$\Delta \Psi$  peak-to-peak flux

λ MOSFET channel-length modulation factor

μ carrier mobility

$\begin{array}{ll} \mu_0 & \text{permeability of free space} \\ \mu_{eff} & \text{effective permeability} \\ \mu_m & \text{material permeability} \\ \mu_N & \text{carrier mobility in NMOS} \\ \mu_r & \text{reversible permeability} \\ \sigma & \text{standard deviation} \end{array}$

τ exponential time constant

Ψ magnetic flux

$\Psi_{12}$  magnetic flux coupled from leg1 to leg2

## 1. Basic principles of power converters

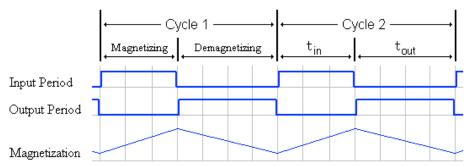

All switched-mode power converters have the same basic operation. The converter has an input period where energy is taken from the source and stored in an inductive core. An output period follows where the magnetized inductance is demagnetized and the energy is delivered to the load. Increasing the input period increases the converter power, provided the magnetizing core does not saturate.

Figure 1.1. Magnetizing and demagnetizing a core is the basic energy transfer mechanism in switched-mode power supplies.

Within this basic scheme, there are three principle modes of operation. In continuous conduction mode (CCM) the core is not fully demagnetized at the end of the cycle. With boundary conduction mode (BCM), the core is demagnetized right at the end of the cycle, and with discontinuous conduction mode (DCM) the core fully demagnetizes some time before the cycle ends. Each mode has advantages and disadvantages as will be discussed. The power converter hardware is the same for all three operating modes, but the controllers are very different.

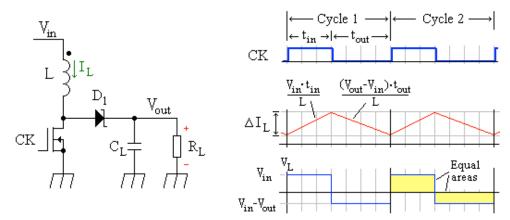

Figure 1.2. The inductor volt-second balance is used to find the CCM transfer function.

To better understand the operating modes, consider the boost converter shown in Figure 1.2. During the input period  $t_{in}$ , the inductor current must increase by  $t_{in} \cdot V_{in}/L$ . During the output period  $t_{out}$  the inductor current must decrease by  $t_{out} \cdot (V_{out} - V_{in})/L$ . In steady-state operation the net current change over the cycle period is zero. The inductor voltage-time product, shown as the yellow boxes in the figure, also averages to zero over the cycle; from this volt-second product the converter transfer function is obtained.

$$\frac{V_{in} \cdot t_{in}}{L} = \frac{(V_{out} - V_{in}) \cdot t_{out}}{L} \tag{1}$$

$$\frac{V_{out}}{V_{in}} = \frac{1}{1 - D} \tag{1}$$

D is the duty cycle, defined as  $t_{\rm in}$  /  $t_{\rm cycle}$ . This transfer function is valid for CCM and BCM operation. For a constant output voltage, the duty cycle can be changed to regulate against variations in the input voltage. However for changes in load power while the output voltage remains constant, the cycle time must be changed and the duty cycle held constant. This is because more power requires a longer input period to store the needed energy, and a constant output voltage requires a constant duty cycle. [1]

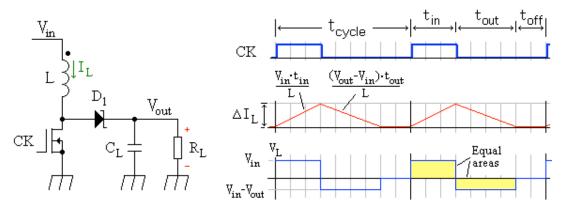

Figure 1.3. The inductor volt-second balance is used to find the DCM transfer function.

Figure 1.3 shows the timing for DCM operation. During the input period, the inductor current must increase by  $t_{in} \cdot V_{in}/L$ . During the output period the inductor current must decrease by  $t_{out} \cdot (V_{out} - V_{in})/L$ . In steady-state operation the net current change and inductor voltage-time product (area of colored boxes) average to zero over the cycle; from this volt-second product the converter transfer function in DCM is derived.

$$\frac{V_{in} \cdot t_{in}}{L} = \frac{(V_{out} - V_{in}) \cdot t_{out}}{L} \tag{2}\alpha$$

$$\frac{V_{out}}{V_{in}} = \frac{t_{out}}{t_{out} - D \cdot t_{cycle}}$$

(2)

From the transfer function the advantage of DCM is seen. The off period  $t_{\rm off}$  allows either voltage or power regulation by simply adjusting the duty cycle while keeping the cycle time constant. The relative simplicity of the controller makes DCM operation ideal for digital controllers where a constant clock frequency is used. [2]

### 1.1 Ripple currents

Depending on the system requirements, the power system designer has many options for controlling the ripple currents seen by the source and load. Depending on which mode and which converter is used, some converters will provide a near constant load to the source with very little ripple, while others will provide large ripple and even reversed current for part of the switching cycle. For renewable energy applications reverse-input currents can be a serious problem and require additional input filtering.

For many consumer applications output ripple may be the concern. Pulsed output from the converter means less voltage regulation and higher power supply noise. In these applications switch-mode converters like the Cúk and Zeta converters offer continuous output current at the cost of higher circuit complexity. [3]

There are no absolute rules, but generally CCM offers the lowest ripple, and DCM has the worst ripple performance. This can be seen in the waveforms shown in Figures 1.2 and 1.3. The peak-to-peak input current  $\Delta I_L$  can be made quite small in CCM, but in BCM this current always returns to zero, and in DCM the current returns to zero and parasitic elements cause oscillations that pulse current into and out of the source. Table 1.1 summarizes the comparative advantages and disadvantages of the three modes for the boost converter. [4]

| Operating mode | Voltage regulation | Power regulation               | Input current ripple | Output current ripple |

|----------------|--------------------|--------------------------------|----------------------|-----------------------|

| CCM            | Duty cycle         | T <sub>C</sub> and/or D        | Lowest               | High                  |

| BCM            | Duty cycle         | Cycle period (T <sub>C</sub> ) | Higher               | Higher                |

| DCM            | Duty cycle         | Duty cycle (D)                 | Highest              | Highest               |

Table 1.1. Comparison of the control and ripple currents for the three operating modes.

Which converter and operating mode will provide the highest efficiency? That largely depends on the application. Maximizing efficiency is a tradeoff between ohmic and switching losses. Understanding these losses is essential to good system design.

#### 1.2 Ohmic losses

Ohmic losses occur primarily in the inductor winding resistance and the channel resistance of the power switches. It is tempting to use larger diameter wires to reduce the winding resistance, but even moderately sized wires suffer eddy current losses within the wires. A better solution is to use many small diameter wires in parallel. Litz wires are specifically designed to reduce eddy current losses in the windings. [5] Design optimization is the tradeoff between ohmic and other losses; the resistance is decreased at the cost of increased switching and magnetic losses.

High frequency switching reduces the effective wire diameter (skin effect), so the AC resistance must be used in calculations. Parallel wires with high fill-factor can have high inter-winding capacitance, which can cause problems. In particular with high-voltage low-current low-power applications, the energy stored in the interwinding capacitance may actually exceed the energy stored in the inductance. In this case a reduced fill-factor with winding layer separation may be necessary. [6]

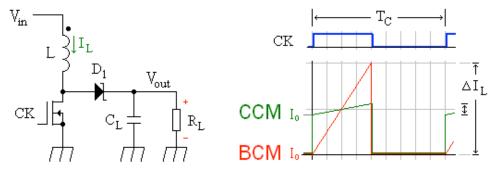

Figure 1.4 shows the comparative channel currents seen when the average CCM and BCM currents are equal. Current flows in the channel for only part of the cycle, but continuously in the inductor making inductor ohmic losses a concern.

Figure 1.4. MOSFET channel current in CCM and BCM operation. The average currents are equal.

BCM has twice the peak current and CCM current approaches a square wave in the extreme limit of infinite inductance. The current can be decomposed into the initial current  $I_0$  and the incremental current  $\Delta I_L$ . In BCM the initial current is zero, and in CCM the incremental current approaches zero. The total channel current and power are then:

$$I(t) = I_0 + \Delta I_L \cdot \frac{t}{t_{in}} \tag{3a}$$

$$I(t)^{2} = I_{0}^{2} + 2 \cdot I_{0} \cdot \Delta I_{L} \cdot \frac{t}{t_{in}} + \Delta I_{L}^{2} \cdot \frac{t^{2}}{(t_{in})^{2}}$$

(3β)

$$P(t)_{ch} = \int_0^{t_{cycle}} I(t)^2 \cdot R_{ch} dt \tag{4}$$

where  $R_{ch}$  is the channel resistance, and the inductor winding losses are considered separately. Carrying out the integration gives the average power dissipated in the channel resistance.

$$P_{ch} = I_0^2 \cdot R_{ch} \cdot t \Big|_0^{t_{in}} + R_{ch} \cdot I_0 \cdot \Delta I_L \cdot \frac{t^2}{t_{in}} \Big|_0^{t_{in}} + \frac{1}{3} \cdot R_{ch} \cdot \Delta I_L^2 \cdot \frac{t^3}{(t_{in})^2} \Big|_0^{t_{in}}$$

(5)

In BCM the first two terms become zero and the power lost is equal to the third term. In CCM as the inductance approaches infinity, the current approaches a rectangular pulse and  $\Delta I_L$  approaches zero. The lost power in CCM is then approximated by the first term. Comparing BCM against CCM in the limit of infinite inductance, the power losses due to resistance can be up to 1.33 times higher for BCM.

CCM reduces the ohmic losses in the MOSFET channel, but at the cost of a larger inductance (and higher inductor winding losses) or higher converter frequency. Inductor winding losses can be decreased by reducing the number of winding turns, which implies decreased inductance. To obtain a lower dI<sub>L</sub>/dt, a much higher converter switching frequency is then needed, and this increases the switching losses.

### 1.3 Switching losses: dynamic power dissipation

To reduce the channel resistance a wider MOSFET is used, which increases the gate capacitance. The channel resistance and gate capacitance are intrinsically linked and they are inversely proportional. From device physics the relationship between gate capacitance  $C_{GS}$  and channel resistance  $R_{ch}$  is:

$$R_{ch} = \int_0^L \frac{dl}{\mu \cdot Q(l) \cdot W'} \cong \frac{L'}{\mu \cdot W' \cdot C_{GS}(V_{GS} - V_{th})}$$

$$\tag{6}$$

The variables describe a MOSFET with channel length L', channel width W', carrier mobility  $\mu$ , and gate charge Q which varies across the channel length at effective gate voltage  $V_{GS}$ - $V_{th}$ . [7][8] The power lost charging and discharging the gate capacitance is called the *dynamic power dissipation*. [9] It is dependent on the gate-to-source voltage  $V_{GS}$  and frequency of the converter cycle  $f_c$ . The dynamic power dissipation is:

$$P_{dpd} = C_{GS} \cdot V_{GS}^{2} \cdot f_{c} \tag{7}$$

If complementary switches are used in the design, resonant gate drivers can be used to reduce this loss. The idea is to connect the gates of the two switches through a small inductor creating a resonant circuit. The gate charge of the 'on' switch assists the 'off' switch in turning on, and vice versa. The gate charge is then recycled, driver requirements (and losses) are reduced, and switching times can be improved. Considering that higher gate voltages are needed to get the lowest channel resistance, this circuit is an attractive gate drive solution. [10]

The dynamic power dissipation can easily exceed the ohmic losses. By combining equations 5 -7, the optimum channel resistance can be found – gate capacitance ratio for a given design and the best power MOSFET can be selected. Generally higher channel resistance favors low current designs, and lower channel resistance favors high current designs. However, this simple analysis ignores an important power loss in the system: the dynamic switching losses.

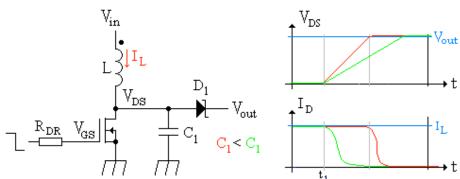

## 1.4 Dynamic switching losses as the switch turns on

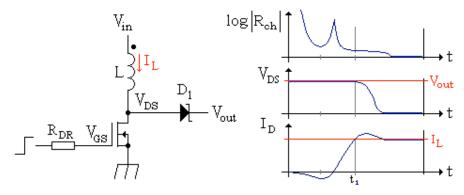

Dynamic switching losses occur when current is pushed into the channel as the switch turns on. In BCM the initial inductor current  $I_L$  is zero, so the dynamic switching losses are zero. However in CCM the drain voltage  $V_{DS}$  stays clamped at  $V_{out}$  until the drain current  $I_D$  exceeds  $I_L$  and  $D_1$  turns off. At time  $t_1$ , the channel resistance equals  $V_{out}/I_L$ . This resistance is two to three orders of magnitude greater than the channel on-resistance; the entire switching transient occurs before the switch is fully turned on. After  $t_1$  the drain current is limited by  $I_L$  as  $V_{DS}$  drops and the channel resistance decreases. Because of the overlap between the high drain voltage and the high drain current, power losses are high through the transition. The problem is exacerbated when D1 is implemented with a diode; the reverse-recovery of silicon diodes increases the overlap time and large current spikes associated with discharging the diffusion capacitance [11].

Figure 1.5. As the switch turns on in CCM,  $V_{DS}$  is clamped at  $V_{out}$  until  $I_D$  exceeds  $I_L$  and  $D_1$  turns off. After  $t_1$ ,  $I_D$  clamps at  $I_L$  and the drain voltage drops. The  $I_D$ - $V_{DS}$  overlap causes a large power dissipation.

Before  $t_1$  the power dissipation equals the integral of the drain-current  $\cdot$  output-voltage product. After the diode turns off, the power dissipation is then the integral of the inductor-current  $\cdot$  drain-voltage product. The drain voltage follows the saturation model with channel-length modulation factor  $\lambda$ , given in equation 8. [12] The dynamic switching loss is approximated using equation 9. This equation works for both rising and falling edges once the integration times are set correctly.

$$V_{DS} = \frac{I_D - \frac{1}{2} \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^2}{\frac{1}{2} \lambda \cdot \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot (V_{GS} - V_{TH})^2}$$

(8)

$$P_{DSL} = \int_{0}^{t_{1}} \frac{1}{2} \mu \cdot C_{ox} \cdot \frac{W'}{L'} \cdot (V_{GS} - V_{TH})^{2} \cdot (V_{DS} + \lambda V_{DS}^{2}) dt + \int_{t_{1}}^{T/2} I_{L} \cdot V_{DS} dt$$

(9)

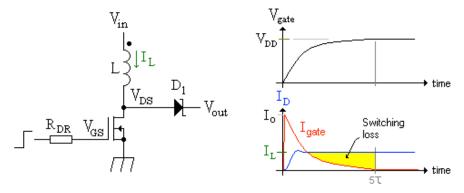

Assuming a simple gate driver model, the gate voltage  $V_{GS}$  increases to the gate driver supply voltage  $V_{DD}$  with exponential time constant  $\tau = R_{DR} \cdot C_{GS}$ . At five time constants the switch is fully on. The initial gate current  $I_0$  is  $V_{DD}$  divided by the driver output impedance  $R_{DR}$ . As the switch turns on,  $I_D$  will clamp at  $I_L$ .

• Consider now a hypothesis that *if* the transient gate current I<sub>gate</sub> exceeds I<sub>D</sub> until the switch is fully turned on, then the dynamic switching losses will be zero, and that *if* the drain current exceeds the gate current as the switch turns on dynamic switching losses will occur. Figure 1.6 shows the detail.

Figure 1.6. In CCM dynamic switching losses are reduced when carriers (holes) released from the gate interface supply part of the channel current as the switch turns on.

Dynamic switching losses will only be zero if  $I_D$  is zero; this occurs in BCM. In CCM the losses are minimized when  $I_{gate}$  supplies as much of the drain current as possible. The idea is to minimize the shaded area shown in Figure 1.6. Ideally, the charge on the gate  $(Q_{gate} = C_{GS} \cdot V_{DD})$  should exceed the charge coming into the drain  $(Q_{drain} = I_L \cdot 5\tau)$ . That comparison gives:

$$Q_{\text{gate}} > Q_{\text{drain}}$$

(10 $\alpha$ )

$$C_{GS} \cdot V_{DD} > I_L \cdot 5 \cdot R_{DR} \cdot C_{GS} \tag{106}$$

$$R_{DR} < \frac{V_{DD}}{5 \cdot I_{I}} \tag{10}$$

This suggests that the gate driver output impedance  $R_{DR}$  should be as low as possible. This reduces  $\tau$  and thus the current-time product of the shaded area. To test the validity of Equation 10 a PSPICE simulation is made and the results are given in Table 1.2. (Test conditions:  $R_{ch} = 1.31 m\Omega$ ,  $C_{GS} = 12.1 nF$ ,  $C_{DS} = 200 pF$ ,  $V_{out} = 12 V$ .) The gate driver supplies 151.25nJ ( $U = \frac{1}{2}CV^2$  for  $V_{DD} = 5V$ ), which is independent of  $R_{DR}$  or  $I_D$ . The shaded boxes show the loss when  $R_{DR}$  is greater than the value calculated in Equation 10.

| $R_{DR}$ | $I_L = 0A (BCM)$ | $I_L = 1.0A (CCM)$ | $I_L$ = 2.0A (CCM) | $I_L = 3.0A (CCM)$ |

|----------|------------------|--------------------|--------------------|--------------------|

| 100mΩ    | 0.6nJ            | 28nJ               | 42nJ               | 57nJ               |

| 500mΩ    | 0.3nJ            | 37nJ               | 60nJ               | 84nJ               |

| 1Ω       | 0nJ              | 43nJ               | 74nJ               | 106nJ              |

| 2Ω       | -0.2nJ           | 54nJ               | 96nJ               | 141nJ              |

| 5Ω       | -0.3nJ           | 78nJ               | 148nJ              | 224nJ              |

| 10Ω      | -0.5nJ           | 111nJ              | 222nJ              | 343nJ              |

Table 1.2. The table shows the simulated dynamic switching loss for a rising-edge gate transition at different values of gate resistance and drain current. These results support the assumption made with Equation 10.

Equations 8 and 9 tell us the optimum MOSFET parameters needed to minimize the dynamic switching loss. Equation 10 tells us the best gate driver design needed to minimize this loss. In all cases of CCM operation a faster driver with lower output impedance will reduce this switching loss, and this loss must be compared against the driver power requirements. In contrast, BCM dynamic switching losses are always zero even for slow gate driver circuits.

## 1.5 Dynamic switching losses as the switch turns off

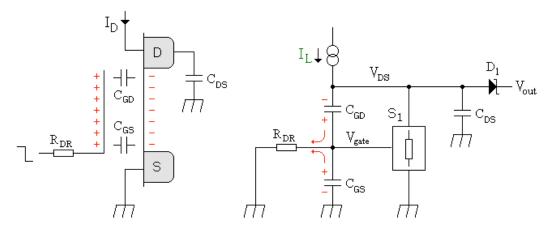

In both CCM and BCM the switch turns off at peak current. A poor design will have higher switching losses and undue component stresses. The problem with this circuit is the Miller Effect; power MOSFETs have very high gain, and the drain voltage increases rapidly. The energy coupled into the gate through the gate-to-drain capacitance  $C_{GD}$  can stall or even reverse the falling gate voltage. With a simple simulation the solution becomes clear. Based on the physical model, the circuit is shown in Figure 1.7. Instead of using the abstract small-signal voltage-controlled current source model, a more realistic model is made using a voltage-controlled resistor  $S_1$  (PSPICE switch).

Figure 1.7. A simple model is all that is needed to analyze the switching losses and determine the best approach to minimizing these losses.

Transient analysis can be done using Laplace transforms and nodal analysis. However, with two assumptions the analysis is greatly simplified. First, assume that the gate voltage has temporarily stalled and the gate capacitance is no longer discharging. This occurs when the current needed to charge  $C_{GD}$  equals the discharge current of  $C_{GS}$ :

$$\frac{V_{gate}}{R_{DR}} = C_{GD} \cdot \frac{dV_{DS}}{dt} \tag{11}$$

Here  $V_{\text{gate}}$  is the gate voltage, which stalls just below the threshold voltage. If the drain voltage rises faster than the condition set in Equation 11, the gate voltage will actually increase and the switch will start to turn on again. This can sometimes be seen as a small rise in the gate voltage as the switch turns off, and it causes larger switching losses. The prevention is to limit the drain voltage rise time.

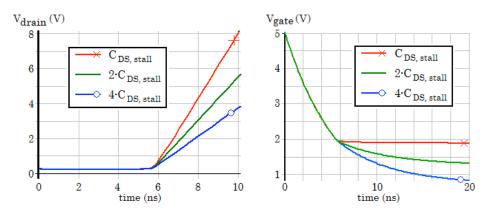

As the switch turns off, the channel resistance rises rapidly. The second analysis assumption is that the channel current drops so rapidly that the majority of the inductor current charges the drain node capacitance instead of going into the drain ( $I_L >> V_{DS}/R_{DS}$ ). The transistor small-signal gain does not affect the drain voltage slope; the slope is limited at  $dV_{DS}/dt = I_L/(C_{DS} + C_{DG})$ . Combining this with Equation 11 gives the new gate voltage stall condition:

$$C_{DS,stall} = C_{GD} \cdot \left( \frac{I_L \cdot R_{DR}}{V_{gate}} - 1 \right)$$

(12)

To avoid stalling the gate discharge, the drain capacitance must be larger than  $C_{DS,stall}$ . The simulation results in Figure 1.8 show the tradeoff between drain slope and the gate discharge rate. The drain circuit is an integrator, and when  $C_{DS}$  is about 10 times  $C_{DS,stall}$  the Miller Effect is essentially eliminated.

Figure 1.8. Increasing the drain node capacitance decreases the drain voltage rise time. The slower rise time decreases the Miller Effect and the switch turns off faster.

To reduce the slope, additional drain capacitance  $C_1$  may be needed. Increasing  $C_1$  decreases the  $V_{DS}$ - $I_D$  overlap, which decreases the dynamic switching losses.  $C_1$  effectively behaves as a snubber, a class of circuits that are used to reduce switching losses. [13] In BCM, the energy needed to charge the drain capacitance is returned to the source when it discharges. In CCM this charge is lost at switching, and added capacitance will cause higher dynamic power dissipation (Equation 7).

Figure 1.9. Adding drain capacitance helps the switch turn off faster, which reduces the  $V_{DS}$ - $I_D$  overlap. This overlap causes the dynamic switching loss seen as the switch turns off.

| Operating mode | $C_1$ | $I_{L}$ | MOSFET DSL/cycle | Loss @100kHz |

|----------------|-------|---------|------------------|--------------|

| CCM            | 0     | 5.0A    | 313nJ            | 31.3mW       |

| BCM            | 0     | 7.4A    | 497nJ            | 49.7mW       |

| BCM            | 2nF   | 7.4A    | 256nJ            | 25.6mW       |

| BCM            | 5nF   | 7.4A    | 128nJ            | 12.8mW       |

| BCM            | 10nF  | 7.4A    | 53nJ             | 5.3mW        |

Table 1.3. The table shows the effect of C<sub>1</sub> on dynamic switching loss as the MOSFET turns off.

## 1.6 Magnetic core losses

Switch-mode power systems convert energy by magnetizing and demagnetizing a magnetic core; changes in magnetization B generate core heating and losses [14]. Core losses increase as 1)  $\Delta B$  increases, and 2) dB/dt increases [15]. However, the energy U stored is also proportional to  $\Delta B$ . For a core with volume  $V_{core}$  (cross-sectional area  $A_{core}$  and closed magnetic field path length  $l_{core}$ ), magnetic field intensity H, and magnetization B, the energy stored in the core material over one converter cycle is then [16]:

$$U = \int_{B1}^{B2} H(t) \cdot l_{core} \cdot A_{core} \cdot dB(t) = V_{core} \cdot \int_{B1}^{B2} H(t) \cdot dB(t)$$

(13)

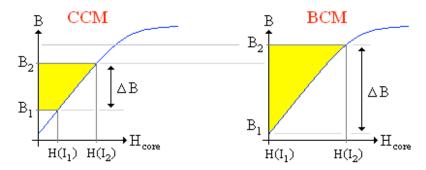

The stored energy is depicted graphically as the shaded area of the B·H product in Figure 1.10. CCM stores less energy per cycle because of the reduced current swing. To achieve the same power output in CCM, the inductance must be increased (H is increased by increasing the winding turns N), the converter frequency must be increased (Power = U/t), or the core volume must increase.

Figure 1.10. The core volume multiplied by the B·H product (shaded area) gives the converted energy per cycle. Because BCM has a larger  $\Delta I_L$ , it delivers more power than CCM for the same core and cycle time.

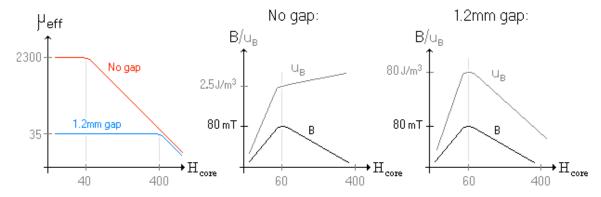

H is derived from Ampere's Law for an un-gapped core with length  $l_{core}$  and N winding turns carrying current  $I_L$  (Equation 14). The B·H slope is modulated by the effective permeability  $\mu_{eff}$  (Equation 15), which can be adjusted over a large range by adding an air gap with length  $l_{gap}$  (Equation 16) [17]. Increasing the air gap decreases  $\mu_{eff}$ , which decreases B. A practical limit is reached at a few millimeters [18] (industry gap E160 is 1.2mm) where the flux leakage rapidly increases the effective gap area  $A_{gap}$  beyond the core cross-sectional area  $A_{core}$ . Additionally,  $\mu_{eff}$  decreases with  $H_{core}$  due to a decrease in  $\mu_m(H_{core})$  (refer to  $\mu_r$  in material data sheets) [15]. This decrease in  $\mu_{eff}$  (Figure 1.11) mathematically describes core saturation.

$$H_{UGC} = \frac{N \cdot I_L}{l_{core}} \tag{14}$$

$$B = \mu_0 \cdot \mu_{eff} \cdot H_{UGC} = \mu_0 \cdot H_{gap} = \mu_0 \cdot \mu_m \cdot H_{core}$$

(15)

$$\mu_{eff}(H_{core}) = \frac{l_{core}}{\frac{l_{core}}{\mu_{m}(H_{core})} + l_{gap} \cdot \frac{A_{core}}{A_{gap}}} \cong \frac{l_{core}}{l_{gap}} \Big|_{H_{core} \to 0}$$

(16)

The energy density  $u_B$  (J/m³) is approximated in Equation 17. Ideally B·H (energy stored) should be maximized while  $\Delta B$  (core loss) is minimized; this occurs as  $H_{UGC}$  increases (via N·I<sub>L</sub>) and  $\mu_{eff}$  decreases (via  $l_{gap}$ ). Since B influences the core losses and H influences the ohmic losses (via the N·I product), the gap length is chosen to minimize the total loss.

$$u_{B} = u_{core} + u_{gap} = \frac{1}{2} \cdot \mu_{0} \cdot \mu_{m} \cdot H_{core}^{2} + \frac{1}{2} \cdot \mu_{0} \cdot \mu_{m}^{2} \cdot H_{core}^{2} = \frac{1}{2} \cdot \mu_{0} \cdot \mu_{eff} \cdot H_{UGC}^{2}$$

(17)

Figure 1.11 shows the result. The  $\mu_{eff}$  no-gap line (left image) is the material permeability  $\mu_m$ . The gap provides feedback that stabilizes  $\mu_{eff}$ ; without it the inductance would decrease rapidly above the specified H=40A/m in the 3C90 material data sheet. Since  $\mu_{eff}$  is a function of H, an optimum  $H_{core}$  at which the energy density is maximized is expected. This occurs around H=60A/m (E32/6 core, L=5 $\mu$ H). The energy density in the gap is  $\mu_m$  times larger than the energy density stored in the core material. The gap storage capability is best utilized when H=60A/m or less. That the gap decreases  $\Delta B$  is not immediately obvious since B peaks around 60mT in both cases. However  $H_{core}$ =60A/m occurs around  $I_L$ =2A for the un-gapped inductor, and around  $I_L$ =14A for the gapped inductor.

Figure 1.11. The core air gap stabilizes  $\mu_{eff}$ , increases the range of H and BH product, and reduces  $\Delta B$ .

The distinction between  $H_{core}$  and  $H_{UGC}$  is clarified with Equation 18.  $H_{UGC}$  is set by the applied magnetomotive force (N·I<sub>L</sub>). Part of this force magnetizes the core, and the rest is stored in the field across the gap. The core and gap reluctances determine the magnitude of  $H_{core}$ . In the un-gapped inductor,  $H_{core} = H_{UGC}$  and the entire applied force magnetizes the core, resulting in a very low input current at saturation. The gap increases the current at which saturation occurs.

$$H_{core} = H_{UGC} \cdot \frac{\Re_{core}(H_{core})}{\Re_{core}(H_{core}) + \Re_{gap}}$$

(18)

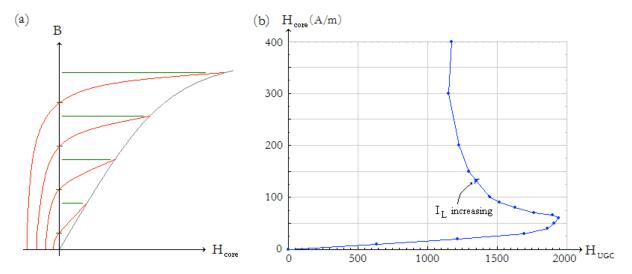

Material hysteresis causes the decrease in  $\mu_m$  as  $H_{core}$  increases; this is seen as a decreased B-H slope on a section of the B-H curve shown in Figure 1.12(a). If an AC signal is applied to the inductor, there is no net magnetization of the material and the permeability will be large (Amplitude permeability in the material data sheets). However, when current flow is restricted to only one direction as it is in switch mode systems, the core material becomes magnetized and  $\mu_m$  will decrease (reversible permeability  $\mu_r$  or  $\mu_{eff}$ ). This problem is exacerbated in CCM where there is a large DC current and small  $\Delta I_L$ . In this respect the current reversal seen in BCM (discussed in section 2.1) helps to keep the core from saturating.

The gapped  $\mu_{eff}$  shown in Figure 1.11 is idealized and may not accurately reflect true operation. The core reluctance  $\mathscr{R}_{core}$  is a function of  $H_{core}$  and as  $\mu_m$  decreases  $\mathscr{R}_{core}$  begins to increase. This causes the core flux to drop as  $H_{core}$  increases above 40A/m. A strange  $H_{UGC}$ - $H_{core}$  relationship results, as shown in Figure 1.12(b); the effect is similar to the negative resistance seen in some semiconductor devices. This effect is the result of a positive feedback ( $\uparrow H_{core} \rightarrow \mu_m \downarrow \rightarrow \mathscr{R}_{core} \uparrow \rightarrow H_{core} \uparrow$ ) that pushes the gapped inductor into saturation sooner than would be expected from the material data sheets. The best solution is to keep operation around the  $\mu_m$  knee or at least ensure some  $I_L$  reversal. This is one advantage of the coupled-inductor that will be discussed in section 2.6.

Figure 1.12. As  $H_{core}$  increases the B·H slope decreases (the material  $\mu_m$  decreases as the material becomes magnetized) (a). The  $\mu_m$  decrease causes the material reluctance to increase and when the inductor has an air gap the core flux may no longer increase monotonically with applied current. As the total reluctance increases and core flux decreases, the material begins to rapidly magnetize (b). The effect is similar to the negative resistance seen in some semiconductor devices.

Equation 19 compares the input power for CCM and BCM. The initial current  $I_0$  in CCM means that H can be large, while the lower  $\Delta I_L$  gives a lower  $\Delta B$ . To achieve the lower  $\Delta I_L$  in CCM, either the inductor must be larger (increased winding resistance) or the cycle time  $T_C$  must be shorter (increased dB/dt). The result is that CCM has lower total inductor losses in most, but not all cases.

$$\frac{1}{2} \cdot V_{in} \cdot \Delta I_{L,BCM} = I_0 \cdot V_{in} + \frac{1}{2} \cdot V_{in} \cdot \Delta I_{L,CCM}$$

(19)

The final design tradeoff is between core size and converter switching frequency. Increasing the core volume increases the stored energy; increasing the switching frequency increases the delivered power. Using a higher switching frequency allows a smaller core to be used; there are two good reasons to do this:

- Low frequency conversion needs higher inductance, which increases N. If the number of turns is doubled and the same fill factor is used, the resistance increases by 4x because the number of parallel windings must be cut in half. Higher frequency conversion decreases ohmic losses.

- Typically the inductor is one of the largest, heaviest, most expensive parts in the system, so design practice seeks to find the minimum core volume that meets the system requirements.

## 1.7 CCM/BCM loss comparison

The long analysis leads to an unsatisfying conclusion: neither mode has a clear advantage in converter efficiency. The design process is a compromise between switching, ohmic, and core losses. Generally, the lower switching losses will make BCM a better choice with high frequency switching, and the lower ripple current will give CCM lower ohmic and core losses. But when the design guidelines are followed, both modes will have similar efficiencies over most operating ranges. Table 1.4 gives a relative comparison of losses when the same core and cycle time are used:

| Operating | MOSFET   | MOSFET             | MOSFET P <sub>DSL</sub> | MOSFET P <sub>DSL</sub> | Inductor  | Inductor   |

|-----------|----------|--------------------|-------------------------|-------------------------|-----------|------------|

| mode      | $R_{CH}$ | $P_{\mathrm{DPD}}$ | (rising edge)           | (falling edge)          | core loss | ohmic loss |

| BCM       | Higher   | Same               | Zero                    | Lower *                 | Higher    | Higher     |

| CCM       | Lower    | Same               | Higher                  | Higher                  | Lower     | Lower      |

<sup>\*</sup> with sufficient drain capacitance.

Table 1.4. The table shows a comparison of the power losses for the two operating modes.

#### 1.8 Why use BCM?

Historically BCM converters were limited to low power systems (300W maximum), with limited applications in power factor correction and flyback converters [19]. The reflected impedance from the flyback secondary makes switching losses much higher for CCM converters. To deliver the same power, with the same converter efficiency, Dixon used a core with twice the volume for his CCM flyback converter compared against his BCM design example (he reduced switching losses by decreasing the converter frequency, and thus needed a larger core) [20].

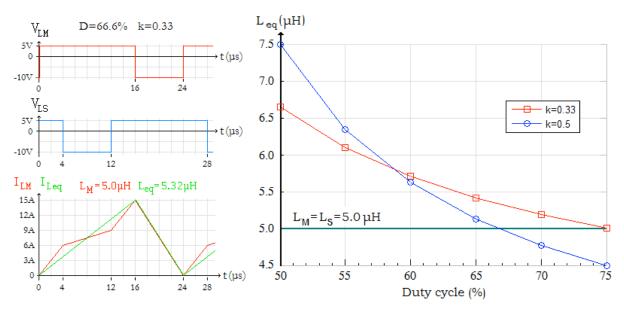

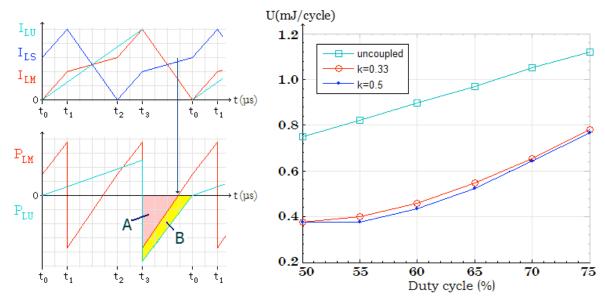

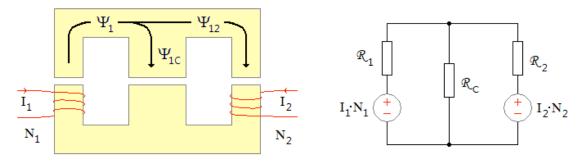

The performance limitations on BCM converters were soon solved and today they are seen in many state-of-the-art systems with efficiencies exceeding 99%, power up to 50kW, and hundreds of amps of current [21]. The breakthrough originated with Jamieson, who proposed "negative coupled inductors" [22]. Multiphase systems reduce current peaks by distributing the current in time; if two phases are 180° out-of-phase, the combined ripple current is reduced. Coupled inductors combine these two phases on the same core. When two inductors are mutually-coupled on the same core, the core flux and losses can be reduced [23].

The concept is simple: part of the energy from the magnetizing phase is coupled through the mutual inductance to the demagnetizing phase. This makes the inductance of the magnetizing phase appear larger, and so fewer winding turns may be used. The result is decreased core and ohmic losses. A secondary benefit is that the reduced magnetic flux means a smaller core can be used [24].

The analysis has ignored the DCM operating mode. It is easy to see that DCM will not give higher efficiency compared to the other operating modes. Figure 1.3 shows DCM timing; for the same cycle time and power, the peak current will always be *more* than twice the average current. However DCM has some distinct advantages; DCM is inherently stable because the input current will always start from zero. Additionally the constant cycle time makes DCM ideal for systems where asynchronous power supply noise is problematic. For instance a DCM controller can be synchronized to the pixel or line rate in imaging systems, thus reducing system noise.

#### 1.9 References

- [1] C.P. Basso, Switch-Mode Power Supplies, New York: McGraw Hill, 2008, pp. 21-26, 43-55.

- [2] N. Mohan *et al.*, Power Electronics: Converters, Applications, and Design, Third Edition, New York: John Wiley & Sons, 2003, pp. 174-177.

- [3] F. Zach, Leistungselektronik: Ein Handbuch, Fourth Edition, Wien: Springer-Verlag, 2010, pp. 961-968, 1046-1058.

- [4] N. Mohan *et al.*, Power Electronics: Converters, Applications, and Design, Third Edition, New York: John Wiley & Sons, 2003, pp. 177-178.

- [5] N. Mohan *et al.*, Power Electronics: Converters, Applications, and Design, Third Edition, New York: John Wiley & Sons, 2003, p. 771.

- [6] J.Graw and H. Zimmermann, "Charging multiple batteries using the boost-flyback converter" Energy Conference and Exhibition (ENERGYCON), 2012 IEEE International, 2012, pp. 963-967.

- [7] P.E. Allen, CMOS Analog Circuit Design, Second Edition, New York: Oxford University Press, 2002, p. 42.

- [8] D.A. Neamen, Semiconductor Physics and Devices, Third Edition, New York: McGraw Hill, 2003, p. 678.

- [9] R.J. Baker, CMOS Circuit Design, Layout, Simulation, Second Edition, New York: John Wiley & Sons, 2005, pp. 339-340.

- [10] Z. Yang, S. Ye, Y. Liu, "A new dual-channel resonant gate drive circuit for low gate drive loss and low switching loss" IEEE Trans. Power Electron., vol. 23, no. 3, pp. 1574-1583, May 2008.

- [11] S. Park and S. Choi, "Soft-switched CCM boost converters with high voltage gain for high-power applications," IEEE Trans. Power Electron., vol. 25, no. 5, pp. 1211–1217, May 2010.

- [12] A. S. Sedra, Microelectronics Circuits, Fourth Edition, New York: Oxford University Press, 1998, p. 370.

- [13] E. Jodar, J. Villarejo, J. Jimenez, "Multiphase ZVS active clamp boost converter: DC and dynamic current shring" IEEE Trans. Industrial Electronics, vol. 60, no. 11, pp. 4947-4959, Nov. 2013.

- [14] A.E. Drake, Magnetic Properties of Materials, National Physical Laboratory. Available:

http://www.kayelaby.npl.co.uk/general physics/2 6/2 6 6.html

[15] Ferroxcube corporation website, 3C90 material datasheet. Available:

http://www.ferroxcube.com/FerroxcubeCorporateReception/datasheet/3c90.pdf

- [16] R. Ramshaw and R. G. van Heeswijk, Energy Conversion Electric Motors and Generators, Philadelphia: Saunders College Publishing, 1990, pp. 43-48, 554.

- [17] G. B. Finke, Gapped Magnetic Core Structures, Magnetic Metals Corporation. Available:

http://www.magmet.com/pdf/GappedCoreStruct.pdf

- [18] A. Vazquez, A. Rodriguez, K. Martin, M. Arias, and M. Hernando, "Inductor optimization for multiphase interleaved synchronous bidirectional Boost converter working in discontinuous conduction mode with zero voltage switching" in IEEE Energy Conversion Congress and Exposition (ECCE), Sept 2013 pp. 4977-4984.

- [19] C.P. Basso, Switch-Mode Power Supplies, New York: McGraw Hill, 2008, pp. 187-191, 528-535.

- [20] L. H. Dixon, Magnetics Design for Switching Power Supplies, pp. 5\_12-5\_17. Available: <a href="http://www.ti.com/lit/ml/slup127/slup127.pdf">http://www.ti.com/lit/ml/slup127/slup127.pdf</a>

- [21] W. Yu, H. Qian, and J.-S. Lai, "Design of high-efficiency bidirectional DC–DC converter and high-precision efficiency measurement," IEEE Trans. Power Electron., vol. 25, no. 3, pp. 650–658, Mar. 2010.

- [22] R. S. Jamieson "Negative coupled inductors for polyphase choppers," U.S. Patent 4 442 401, Apr. 10, 1984.

- [23] J.-S. Lai, B. York, A. Koran, Y. Cho, B. Whitaker, and H. Miwa, "High efficiency design of multiphase synchronous mode soft-switching converter for wide input and load range," Proc. Int. Power Electron. Conf. Sapporo, Japan, June 2010, pp. 1849–1855.

- [24] Z. Xuning, P. Mattavelli, D. Boroyevich, "Impact of interleaving on input passive components of paralleled DC-DC converters for high power PV applications" 15th Int. Power Electron. and Motion Control Conf. 2012, pp. LS7d.5-1 LS7d.5-6.

## 2. Multiphase Interleaved BCM controllers

Which power converter operating mode is best (CCM/BCM/DCM)? The answer appears to be more a matter of preference than science as each mode has its own loyal following and creative engineering techniques to enhance performance. CCM suffers from comparatively higher switching losses, and many "soft-switching" solutions have been implemented [1]. BCM suffers from higher ohmic and core losses, and multiphase converters became a popular way to reduce these losses [2].

Soft switching in CCM is accomplished using an auxiliary resonant circuit or snubber. The basic idea is that current is diverted from the main power switch into the auxiliary circuit before switching occurs. This reduces switching losses of the main switch and reverse recovery losses in the diode. But this comes with the cost of additional circuit complexity –an additional inductor, capacitor, switch or switches, and control circuitry [3].

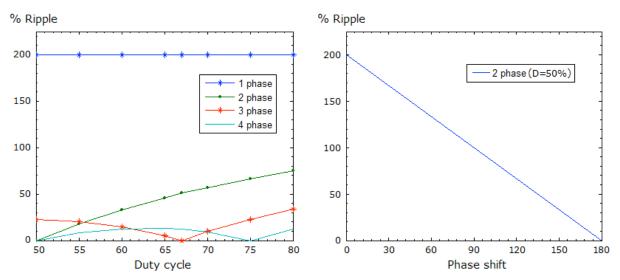

Multiphase BCM converters require additional inductors, switches, and control circuitry as well, and it may seem that there is no advantage to the multiphase BCM solution. However, multiphase converters have many advantages, and typically converters today will be multiphase regardless of the operating mode used. They increase power output while achieving higher efficiency and reducing the input current ripple. Current ripple reduction means that less input filtering is needed, reducing the size, cost, and weight [4].

Recently designers have favored converters with 180° phase-shifted interleaved pairs (2-phase, 4-phase...). The 180° phase shift minimizes the ripple seen by the source. It is called "ripple cancellation" because the source essentially sees a DC load and the ripple is due primarily to component mismatches [5]. For renewable energy sources such as solar panels, the reduced ripple means less decoupling capacitance is needed, and lower equivalent series resistance losses are seen. For grid connections, the lower ripple means lower harmonic distortion, and this interleaved design is seen widely in power factor correction [6]. Interleaving also reduces the output ripple, which improves the efficiency for charging batteries or improves voltage regulation for active loads. To achieve the highest performance, power systems today are likely to have the following features [7]:

- Soft switching to reduce switching losses. The best performance is achieved with the combination of zero-current switching (ZCS) and zero-voltage switching (ZVS).

- Interleaved multiphase design to reduce conduction and core losses.

- Coupled-induction between interleaved phases to reduce core losses and inductor size.

While it is clear that both CCM and BCM systems have realized high performance, the wider current swing with BCM better utilizes the magnetic core, and the return-to-zero causes fewer stability problems. Its growing popularity and technical challenges made a multi-phase BCM controller an interesting topic for this thesis.

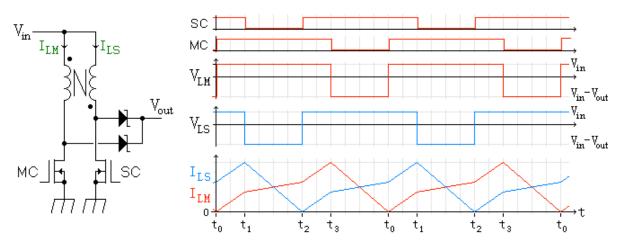

## 2.1 Basic BCM operation

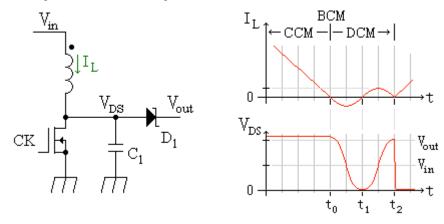

CCM is defined as switching before inductor demagnetization is complete (time  $t_0$  in Figure 2.1). At instant  $t_0$ , the inductor current is zero and the inductor is demagnetized. Technically, switching precisely at  $t_0$  is BCM; since the current is zero, BCM operates with ZCS. Diode D1 is current-starved so its reverse-recovery switching losses will be zero [8]. However, the drain node capacitance is still charged at  $V_{out}$ , and discharging it will result in dynamic power dissipation as defined in Equation 7.

Figure 2.1. The timing diagram helps clarify the definition of the three operating modes. At time  $t_0$  the inductor is demagnetized; switching at this instant would be BCM. BCM operates with ZCS, however a better switching time would be  $t_1$  when both ZCS (inductor current is zero) and ZVS (drain voltage is zero) occur. Technically, switching at  $t_1$  is DCM, but it is loosely defined as BCM as well. Switching randomly at any time after  $t_1$  is always regarded as DCM.

If switching does not occur at  $t_0$ , the drain node capacitance begins to discharge through the inductor; the charge is recycled to source  $V_{in}$  and is not lost in switching. The inductor and drain capacitance form a resonant circuit, which causes the drain voltage to oscillate around voltage  $V_{in}$ . Ideally, switching should occur on the first oscillation minima at time  $t_1$ , but the exact operation depends on the input and output voltages. The three cases are:

- V<sub>out</sub> < 2·V<sub>in</sub>: In this case the voltage minimum will not drop to zero. Switching at the minimum is called valley switching, and the charge remaining on the node capacitance is lost to switching.

- $V_{out} = 2 \cdot V_{in}$ : The drain voltage drops to zero at a delay of half of an oscillation cycle. Switching occurs at the voltage minimum when both the current and voltage are zero (ZCS and ZVS occur) [8]. In this case switching losses are minimized and the charge on the node capacitance is recycled.

- $V_{out} > 2 \cdot V_{in}$ : In this case the voltage attempts to drop below zero volts. If the switch is not turned on at the zero-crossing, the MOSFET body diode will forward-bias. Most power MOSFETs are designed to handle large body diode currents, but the device rating should be checked. Some designs use a current sensor to find  $t_0$ , and the half-cycle delay to  $t_1$  is calculated by the controller. In this case the delay should be reduced to minimize MOSFET power dissipation.

During the oscillation cycle, the source must accept current from the drain capacitance discharge, which is:

$$I_{peak \ dischrg} = (V_{out} - V_{in}) \cdot \sqrt{\frac{C_{drain}}{L}}$$

(20)

In DCM switching occurs asynchronously on this oscillation period causing a random inductor current component between  $\pm I_{peak \ dischrg}$ . This is undesired because it creates uneven phase currents, which increase the input ripple [9]. ZCS or ZVS operation solves the problem and it reduces switching losses. To distinguish between a random switching time in DCM and precise switching at time  $t_1$ , switching at  $t_1$  will be referred to as BCM. The confusion regarding this distinction is not lost with many researchers, as the  $t_0$ - $t_1$  time interval has been given many names: synchronous conduction mode [2], critical mode [8], transition mode [6], DCM/CCM boundary [10], to name just a few.

## 2.2 System diagram

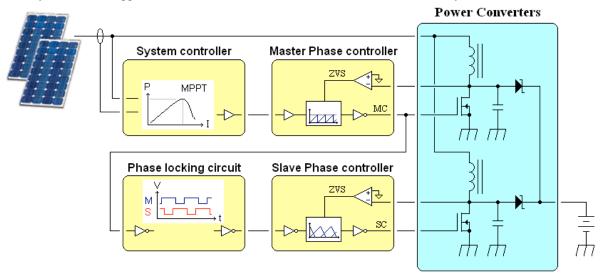

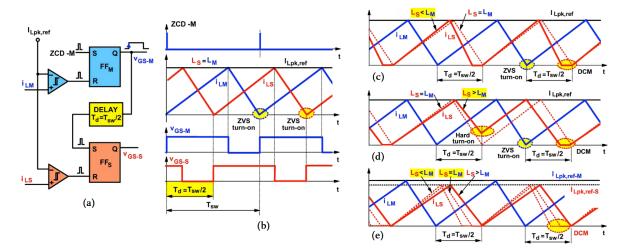

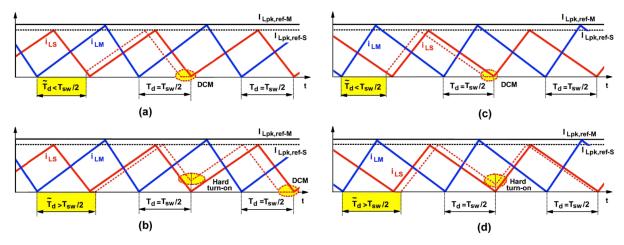

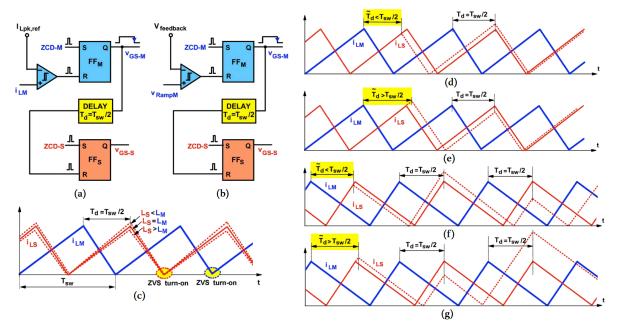

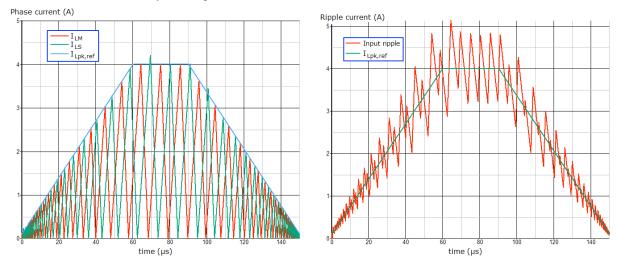

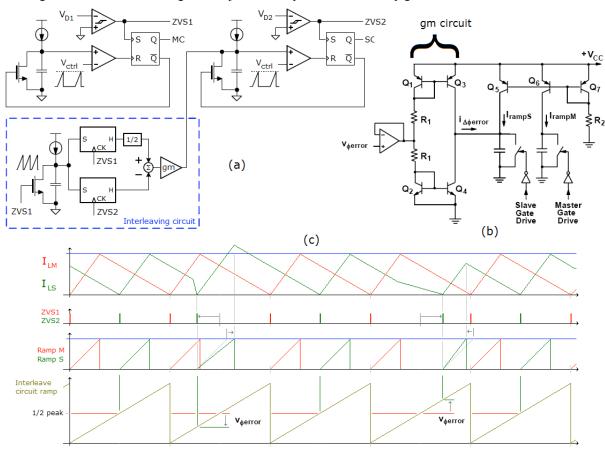

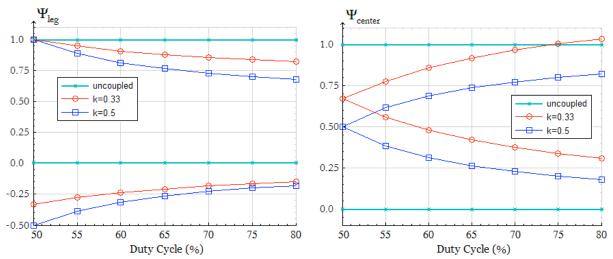

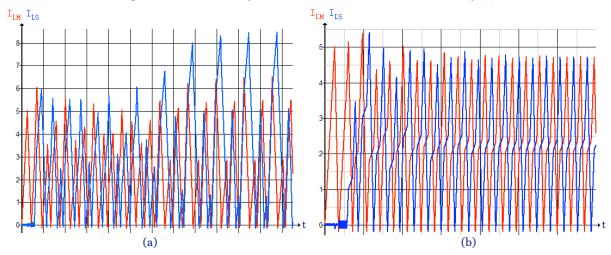

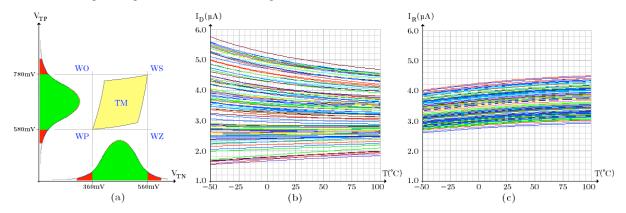

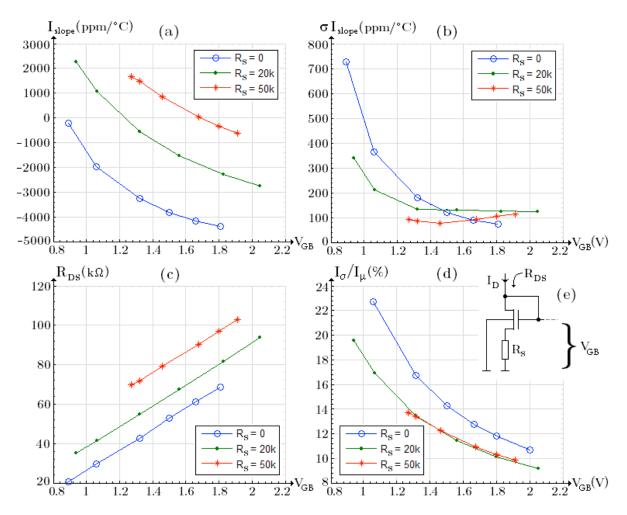

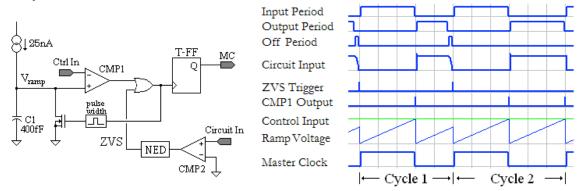

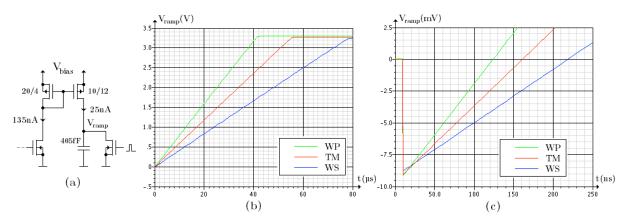

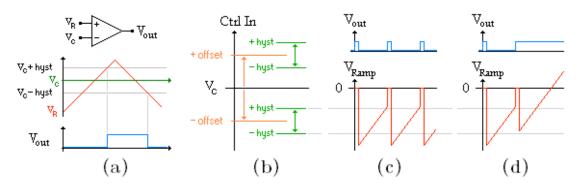

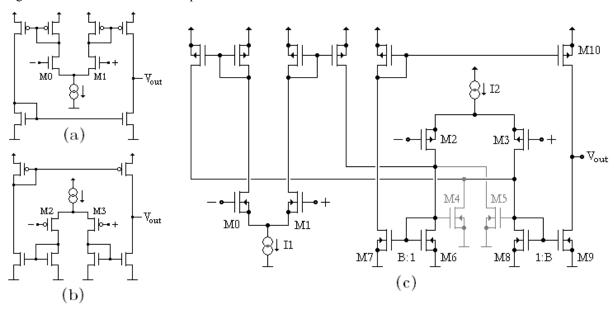

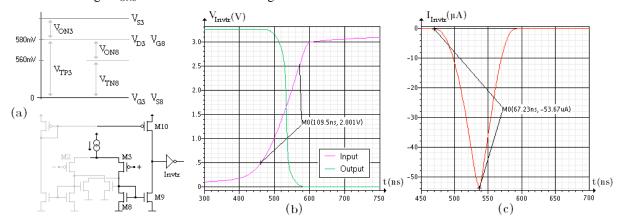

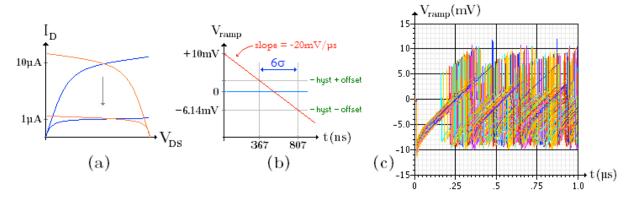

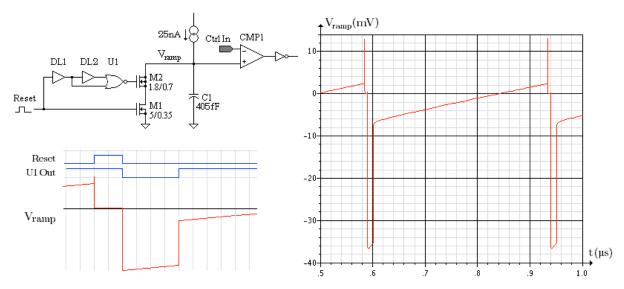

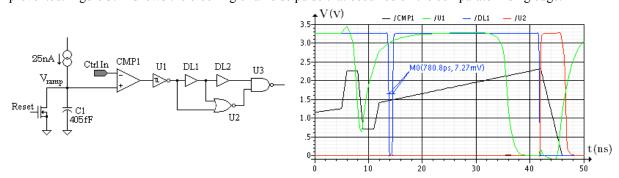

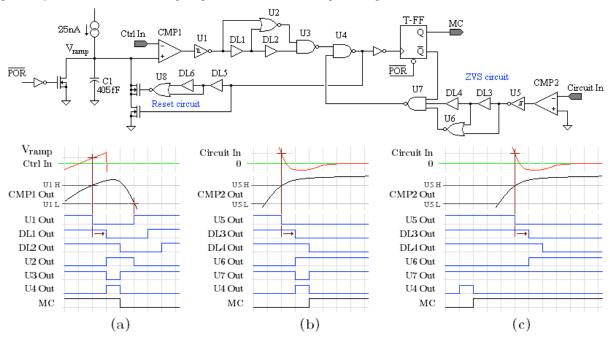

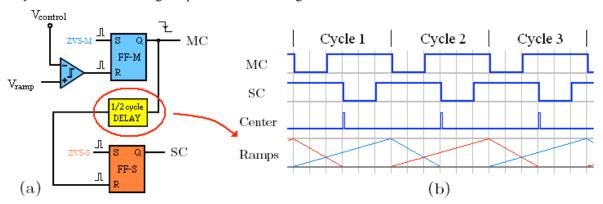

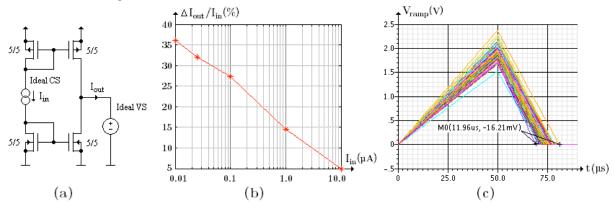

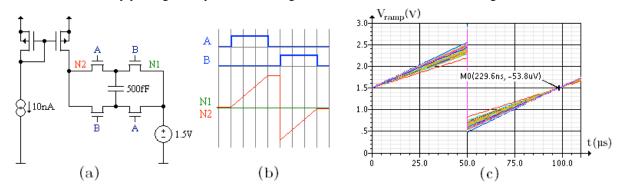

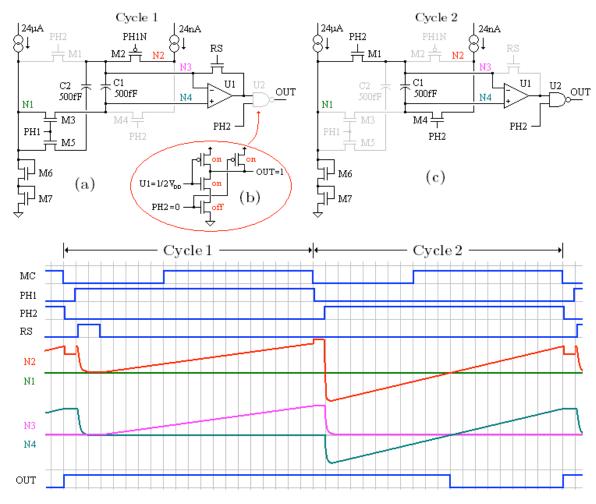

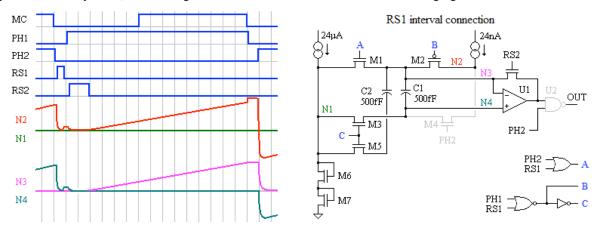

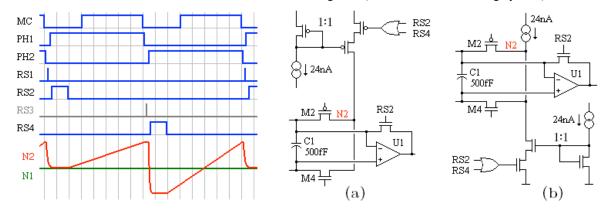

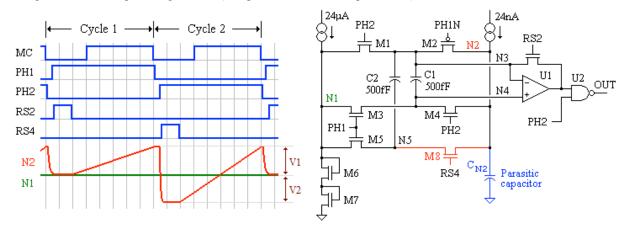

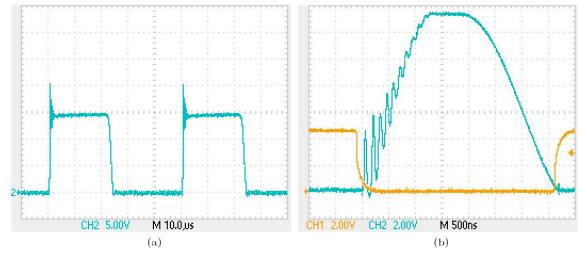

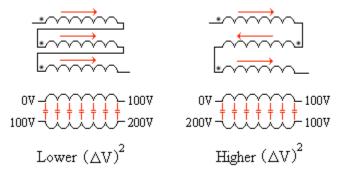

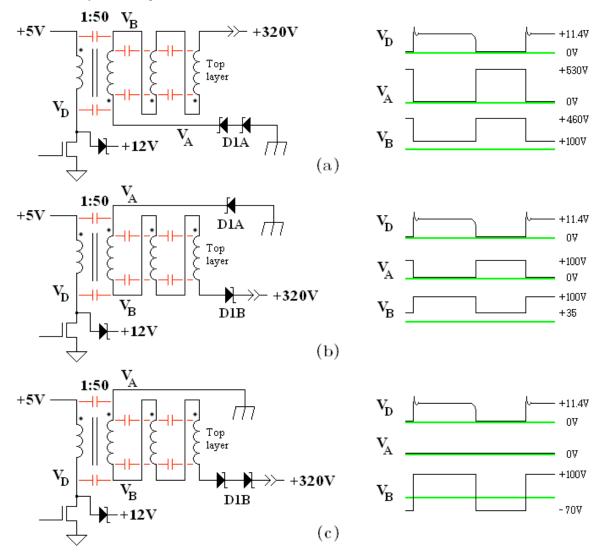

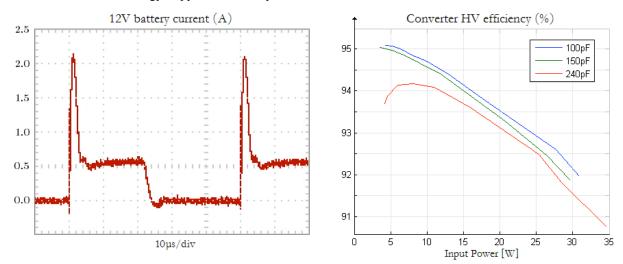

The full system actually has two controllers: a top-level system controller specific to the application, and a sub-controller that manages the converter timing. Different applications have different hardware requirements. A voltage-regulated converter adjusts the control signal according to the error between the output and reference voltages. However a renewable energy system with a battery output will have little or no output voltage control. Instead, a maximum power point tracking (MPPT) circuit may be used which prevents overdriving the source, and charges the battery according to the available power. It would be impossible to design a generic controller for every conceivable application. However, in both cases the same sub-controller may be used.