Die approbierte Originalversion dieser Diplom-/

Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich.

http://www.ub.tuwien.ac.at

TUB

WIEN Universitätsbibliothek

The approved original version of this diploma or

master thesis is available at the main library of the

Vienna University of Technology.

http://www.ub.tuwien.ac.at/eng

#### DIPLOMARBEIT

# Rekonfigurierbare Befehlssatzerweiterung zur Leistungssteigerung von Universalprozessoren

ausgeführt zur Erlangung des akademischen Grades eines Diplom-Ingenieurs unter der Leitung von

> Univ.Prof. Dr. Dietmar Dietrich Dr. Florian Schupfer Dipl.-Ing. Michael Rathmair

> > am

# Institut für Computertechnik (E384)

der Technischen Universität Wien

durch

Günther Mader Matr.Nr. 0826653 Reinprechtsdorferstraße 34/17, 1050 Wien

#### Kurzfassung

Rechenleistung, Energieeffizienz und Entwicklungsaufwand sind wesentliche Parameter bei der Entwicklung von Embedded Systems. Um diese Anforderungen zu erfüllen reicht es meist nicht aus einen leistungsstarken Universalprozessor mit mehreren Kernen zu verwenden. Der Trend geht daher in Richtung Verwendung von spezialisierter Hardware zur Unterstützung der Universalrechenkerne. So verfügen moderne Systeme oft neben mehreren Hauptprozessoren über eine immer größer werdende Anzahl von zusätzlichen Berechnungseinheiten, welche die Abarbeitung komplexer Funktionen beschleunigen [4]. Ziel ist die Optimierung des Verhältnisses von Rechenleistung und Energieeffizienz für das jeweilige Anwendungsgebiet. Um den Entwicklungsaufwand in Grenzen zu halten ist dabei eine effiziente Wiederverwendung des Designs erforderlich. Deshalb beschäftigt sich diese Diplomarbeit mit rekonfigurierbarer Hardware, welche sowohl Wiederverwendung des Designs bei der Hardwareentwicklung als auch von Hardwareressourcen während des Betriebs ermöglicht. Es wird ein Ansatz erarbeitet, der es erlaubt den Befehlssatz eines Universalprozessors zu erweitern. Dieser sieht eine Art Modulsystem vor um auch Änderungen und Erweiterungen des Applikationsgebietes für zukünftige Anwendungen abzudecken. Es besteht aus dem eigentlichen Prozessor mit einer generischen Schnittstelle und beliebigen rekonfigurierbaren Erweiterungsfunktionseinheiten, die daran angeschlossen werden können. Berechnungen und Konfigurierung der Erweiterungsblöcke werden über die Schnittstelle mit Erweiterungsbefehlen ausgeführt. Das ermöglicht hardware- und softwareseitig eine effiziente Wiederverwendung von Ressourcen, Design und Entwicklungsumgebung. Durch eine geeignete Demoimplemtierung wird die Funktionsfähigkeit des vorgestellten Ansatzes gezeigt und die durch die rekonfigurierbaren Erweiterungsinstruktion erzielbaren Steigerungen von Rechenleistung und Energieeffizienz dargestellt.

#### **Abstract**

Processing power, energy efficiency and development effort are essential parameters in the development of embedded systems. To meet these requirements, the use of a powerful general purpose processor with multiple cores is mostly not enough. Therefore the trend goes towards the use of specialized hardware to support the general purpose computing cores. Modern systems often are equipped with several processors and a permanently increasing number of additional computation units, which accelerate the execution of complex functions [4]. The aim is to optimize the ratio of computing performance and energy efficiency for the desired application. In order to keep the development effort within reasonable limits, efficient reuse of the design is required. To achieve this goal this thesis deals with reconfigurable hardware, which enables reuse of hardware design in the development stage as well as reuse of hardware resources during operation. An approach that allows to extend the instruction set of a general-purpose processor is developed. This provides a kind of module system to cover modifications and extensions of the application area also for future applications. It consists of the main processor with a generic interface and reconfigurable functional units as extensions which can be connected thereto. Calculations and configuration of the extension blocks are executed with extension commands via the interface. This enables hardware- and software-efficient reuse of resources, design and development environment. By demonstrating the functionality with a suitable implementation, the proposed approach is shown. Moreover the increase in computing power and energy efficiency achieved by the reconfigurable expansion instructions are illustrated.

# Inhaltsverzeichnis

| 1 | Ein | ${f leitung}$                                               | 1  |

|---|-----|-------------------------------------------------------------|----|

|   | 1.1 | Motivation und Zielsetzung                                  | 1  |

|   | 1.2 | Aufgabenstellung                                            | 4  |

|   | 1.3 | Gliederung der Arbeit                                       | 6  |

| 2 | Sta | nd der Technik                                              | 7  |

|   | 2.1 | Befehlssatzerweiterungen                                    | 7  |

|   | 2.2 | Die PRISC-1 Architektur                                     | 8  |

|   | 2.3 | Die OneChip Architektur                                     | 0  |

|   | 2.4 | Die ReRISC Architektur                                      | 1  |

|   | 2.5 | Vergleich der Architekturen                                 | 13 |

| 3 | Gev | vählter Ansatz                                              | 4  |

|   | 3.1 | Zielsetzung                                                 | 4  |

|   | 3.2 | Verwendeter RISC Prozessor                                  | .5 |

|   | 3.3 | Erweiterungskonzept                                         | 7  |

|   |     | 3.3.1 Schnittstelle vom Prozessor zu Erweiterungseinheiten  | 8  |

|   |     | 3.3.2 Schnittstelle von Erweiterungseinheiten zum Prozessor | 9  |

|   |     | 3.3.3 Kommunikationsablauf                                  | 20 |

|   |     | 3.3.4 Lösen von Ressourcenkonflikten                        | 22 |

|   |     | 3.3.5 Erweiterungsbefehle                                   | 23 |

|   | 3.4 | Erweiterungseinheiten                                       | 23 |

|   |     | 3.4.1 Beispiele und deren Rekonfigurierung                  | 24 |

|   |     |                                                             | 24 |

|   | 3.5 | Herangehensweise                                            | 26 |

| 4 | Bei | spielimplementierung 2                                      | 8  |

|   | 4.1 | Verwendete Entwicklungsumgebung und Hardware                | 28 |

|   | 4.2 | Prozessor                                                   | 28 |

|   |     | 4.2.1 Aufbau                                                | 29 |

|   |     | 4.2.2 Programmierung                                        | 32 |

|   |     | 4.2.3 Interrupt-Abarbeitung                                 | 33 |

|   | 4.3 | Transzendente Berechnungen (CORDIC)                         | 35 |

|   |     | 4.3.1 Basisalgorithmus                                      | 35 |

|   |     | 4.3.2 Modifikationen                                        | 37 |

|    |       | 4.3.3   | Konvergenzbereich und dessen Erweiterung |            |

|----|-------|---------|------------------------------------------|------------|

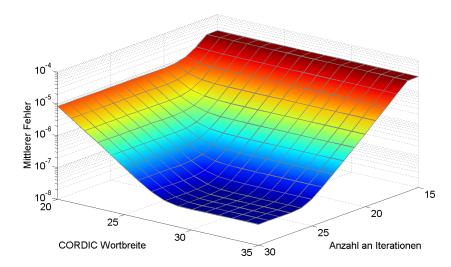

|    |       | 4.3.4   | Berechnungsgenauigkeit                   |            |

|    |       | 4.3.5   | Implementierung                          |            |

|    | 4.4   |         | rtierung des Zahlenformats               |            |

|    | 4.5   | Digita  | les Filter                               |            |

|    |       | 4.5.1   | Aufbau                                   | 47         |

|    |       | 4.5.2   | FIR- und IIR-Filter                      | 48         |

|    |       | 4.5.3   | Programmierung und Konfiguration         | 49         |

| 5  | Eval  | luierui | ng und Ergebnisse                        | <b>51</b>  |

|    | 5.1   | System  | $\operatorname{ntest}$                   | 51         |

|    |       | 5.1.1   | Prozessor                                | 52         |

|    |       | 5.1.2   | CORDIC-Erweiterung und Simulator         | 53         |

|    |       | 5.1.3   | Digitales Filter                         | 54         |

|    |       | 5.1.4   | Aufgetretene Probleme                    | 54         |

|    | 5.2   | Vergle  | ich Software-/Hardwarelösung             | 58         |

|    |       | 5.2.1   | CORDIC                                   | 58         |

|    |       | 5.2.2   | Konvertierung des Zahlenformats          | 59         |

|    |       | 5.2.3   | Digitales Filter                         | 60         |

|    |       | 5.2.4   | Zusammenfassung der Ergebnisse           | 61         |

|    |       | 5.2.5   | Demonstrationsprogramme                  | 61         |

| 6  | Zusa  | ammei   | nfassung                                 | 66         |

|    | 6.1   | Ausge   | führte Arbeit und Erkenntnisse           | 66         |

|    | 6.2   | Nicht   | behandelte Punkte                        | 67         |

|    | 6.3   | Ausbli  | m ck                                     | 69         |

| A  | Anh   | ang     |                                          | 70         |

|    | A.1   | IEEE7   | 754 Gleitkommazahlenformat               | 70         |

|    | A.2   | Belegu  | ing des Special Function Registers       | 71         |

|    | A.3   | Erweit  | serungsbefehlssätze                      | 72         |

| W  | issen | schaft  | liche Literatur                          | <b>7</b> 5 |

| In | terne | et Refe | erenzen                                  | 76         |

# Abkürzungen

Processing Element

PE

ADC

Analog/Digital Converter ADDR Address ADSP Application Domain Specific Processor Arithmetical and Logical Unit ALU Application Specific Integrated Circuit ASIC ASIP Application Specific Instruction-set Processor CISC Complex Instruction Set Computer CLKCLock (Taktsignal) COMmand (Spezialbefehl) COMCOordinate Rotation DIgital Computer CORDIC Complex Programmable Logic Device **CPLD** DEC **DECode** DeLuXe DLX Dynamically Programmable Gate Array **DPGA** Ein-/Ausgabe E/AENable ENEXecute  $\mathbf{E}\mathbf{X}$ Fetch FFTFast Fourier Transform Finite Impuls Response FIR **FPGA** Field Programmable Gate Array Graphical User Interface GUI GRant GR Interrupt IEEE Institute of Electrical and Electronics Engineers Infinite Impulse Response IIRInternet of Things IoT IPIntellectual Property Interrupt ReQuest IRQ Light Emitting Diode LED Look Up Table LUT MAC Multiply and ACcumulate Microprocessor without interlocked pipeline stages Assembler and Runtime Simulator MARS MEM MEMory-access MIPS Microprocessor without Interlocked Pipeline Stages Memory Management Unit MMUMUltipleXer MUX NAN Not A Number OPerand OP

PFU Programmable Functional Unit

PRISC PRogrammable Instruction Set Computer

PTR PoinTeR

R31 Register 31 (Rücksprungregister)

RDY ReaDY

ReRISC Reconfigurable Reduced Instruction Set Computer

RES RESult REQ REQuest

RISC Reduced Instruction Set Computer

ROM Read Only Memory

SA Shift Amount

SFR Special Function Register

SOC System On Chip SP Stack Pointer

SYNC SYNCronization (Pipeline-Synchronität) TFLOPS Tera FLoating-point Operations Per Second

VHDL Very high speed integrated circuit Hardware Description Language

WR WRite

WB Write-Back

# ${\bf Mathematische\ Symbole}$

| Symbol                        | Definition                                 | Einheit |

|-------------------------------|--------------------------------------------|---------|

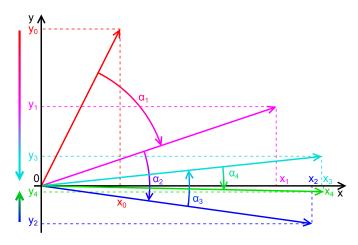

| α                             | Winkel einer CORDIC Teilrotation           | rad     |

| $\theta$                      | Soll-Rotationswinkel CORDIC-Algorithmus    | rad     |

| $\mid \widetilde{	heta} \mid$ | Ist-Rotationswinkel CORDIC-Algorithmus     | rad     |

| $\sigma$                      | Vorzeichen einer CORDIC Teilrotation       | 1       |

| $f_{abs}$                     | absoluter Fehler                           | 1       |

| $f_{rel}$                     | relativer Fehler                           | 1       |

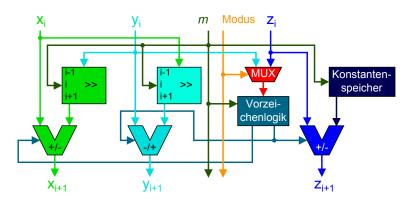

| i                             | CORDIC Iterations index (ganze Zahl)       | 1       |

| $in_1$                        | erster Eingangsoperand CORDIC-Erweiterung  | 1       |

| $in_2$                        | zweiter Eingangsoperand CORDIC-Erweiterung | 1       |

| k                             | Ergebnis bei Ganzzahldivision              | 1       |

| K                             | Dehnungsfaktor beim CORDIC-Algorithmus     | 1       |

| m                             | Index CORDIC-Koordinatensystem {-1,0,1}    | 1       |

| max                           | obere Integrationsgrenze                   | 1       |

| $\mid n \mid$                 | Anzahl CORDIC-Iterationen (ganze Zahl)     | 1       |

| $out_{ist}$                   | Ergebnis CORDIC-Hardware                   | 1       |

| $out_{soll}$                  | exaktes Ergebnis CORDIC-Funktion           | 1       |

| pos                           | mittlere Bitposition                       | 1       |

| R                             | Operator CORDIC-Teilrotation               | 1       |

| $\overrightarrow{v}$          | allgemeiner Vektor                         | 1       |

| x                             | Funktionsargument                          | 1       |

| x'                            | modifiziertes Funktionsargument            | 1       |

| $z^{-1}$                      | Verzögerung um einen Taktzyklus            | 1       |

| $x_i, y_i, z_i$               | CORDIC Iterationsvariablen                 | 1       |

# 1 Einleitung

Praktisch jedes digitale Gerät verfügt über programmierbare Elemente, meist in Form von Prozessoren. Zukunftsvisionen wie z. B. das IoT (Internet of Things) sehen sogar vor, verschiedenste Objekte des täglichen Lebens mit Intelligenz - also Prozessoren - auszustatten [5]. Diese Objekte sind miteinander vernetzt und verfügen oftmals über Sensoren, was eine Ausführung in Echtzeit und das Übertragen von Daten erfordert. So sollen durch die Verfügbarkeit und Auswertung sehr vieler Daten Dinge des täglichen Lebens vereinfacht und ein effizienterer Umgang mit Ressourcen wie etwa Energie ermöglicht werden. Weil dazu eine große Anzahl unterschiedlichster intelligenter Objekte erforderlich ist, müssen die darin eingebetteten Systeme sehr kostengünstig und für die jeweilige Applikation geeignet sein. Zudem sind viele dieser Systeme batteriebetrieben und schwer erreichbar, wodurch auch die Energieeffizienz ein wichtiger Faktor ist. Somit hängt die Verwirklichung des IoTs vor allem von der Verfügbarkeit energie- und kosteneffizienter Prozessoren mit ausreichender Rechenleistung ab.

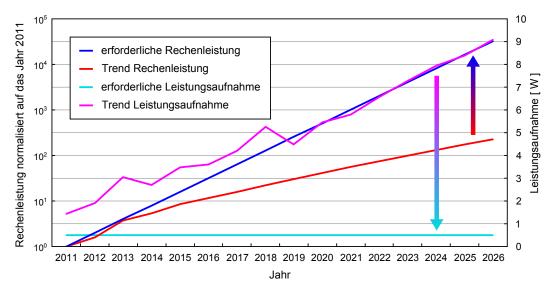

Auch wenn das IoT noch nicht Realität geworden ist, stellen Embedded Systems bereits heute einen Großteil des Hardwaremarktes dar und dieser Trend setzt sich fort [9]. Es wird davon ausgegangen, dass diese Systeme immer schneller und funktioneller werden, wobei eine Steigerung um den Faktor zwei alle zwei Jahre eine gängige Annahme ist [4]. Dass es jedoch schwierig werden wird zukünftige Erwartungen an Rechenleistung und Energieverbrauch zu erfüllen zeigt Abbildung 1.1 für den Bereich mobiler Consumerelektronik, welcher stark im Wachsen ist [2]. Die Bewältigung dieser zukünftigen Anforderung, auch bezüglich Entwicklungsaufwand und -kosten bilden die Motivation dieser Diplomarbeit und werden daher im folgenden Abschnitt genauer behandelt.

# 1.1 Motivation und Zielsetzung

Die Entwicklung neuer Produkte ist oft von starkem Kostendruck und kurzer Time-to-Market geprägt. Deshalb muss der Entwicklungsaufwand trotz ständiger Erhöhung der Funktionalität so gering wie möglich ausfallen. Das setzt eine Steigerung der Produktivität voraus, die auf Wiederverwertung und Minimierung des dabei entstehenden Overheads basiert. So ist es laut Prognosen im Consumerbereich bis zum Jahr 2026 erforderlich 98% eines Designs wieder zu verwenden [4].

Abbildung 1.1: Entwicklung wichtiger Systemparameter im mobilen Consumerbereich [4]

Deshalb wäre ein Universalprozessor das ideale Bauteil für neue Entwicklungen. Denn durch seinen universellen Aufbau ist der Prozessor in der Lage annähernd beliebige Aufgaben zu erfüllen und somit praktisch alle Anwendungsgebiete und Funktionen abzudecken. Auch seitens der Software ergeben sich durch Einsatz eines Universalprozessors Vorteile, weil immer der gleiche Befehlssatz zur Anwendung kommt. Dadurch können immer die selben Entwicklungsumgebungen verwendet und ältere Programme kompatibel gehalten werden.

Allerdings besteht auch ein ständiger Bedarf zur Erhöhung der Rechenleistung, die notwendig ist um die geforderte Funktionalität innerhalb eines vorgegebenen Zeitrahmens bereit zu stellen bzw. echtzeitfähige Systeme zu ermöglichen. Um das zu erreichen gibt es bei Universalprozessoren mehrere Möglichkeiten:

- neue Fertigungstechnologie / neuartige Transistoren

- Erhöhung der Taktfrequenz

- Verbesserung der Architektur / Steigerung der Komplexität eines Prozessorkerns

- größere Anzahl an Recheneinheiten

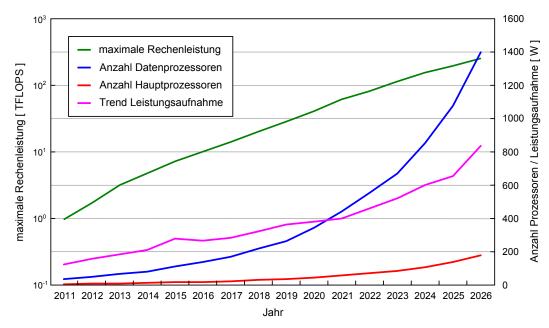

Während in den ersten Jahrzehnten der Mikroprozessorentwicklung die Leistungssteigerung vor allem auf den ersten drei Punkten basierte, muss heute ein anderer Weg gewählt werden. Zwar entwickelt sich die Fertigungstechnologie ständig weiter, allerdings kann die historisch verwirklichte Steigerung der Taktfrequenz um den Faktor 1,4 pro Technologiegeneration nicht mehr fortgesetzt werden [4]. Auch die Komplexität von Prozessorkernen ist mittlerweile an einem Punkt angelangt, an dem sich nur mehr wenig ändert. So verbleibt unter Annahme der selben zugrunde liegenden Technologie nur noch die Erhöhung der Anzahl an Recheneinheiten. Das findet bereits statt und ist in Abbildung 1.2 (TFLOPS = Tera Foating Point Operations Per Second) für die kommenden Jahre am Beispiel stationärer Consumerelektronik (z. B. Spielkonsolen) dargestellt.

Abbildung 1.2: Entwicklung wichtiger Systemparameter im stationären Consumerbereich [4]

Ein großes Problem, das mit der Duplikation von Rechenkernen einhergeht ist die Erhöhung der Leistungsaufnahme (siehe Abbildung 1.2). Bei Geräten mit Anschluss an das Stromnetz besteht die Schwierigkeit darin, die erforderliche elektrische Leistung in den Chip hinein zu bekommen und die entstehende Abwärme wieder abzuführen. Das kann bei Embedded Systems bereits ein Problem hinsichtlich der Kühlung des Chips darstellen [4]. Bei mobilen und batteriebetriebenen Geräten ergibt sich jedoch ein weitaus gravierenderes Problem, da diese nur einen sehr beschränkten Energievorrat zur Verfügung haben. Weil sich Energiespeicher nur sehr langsam weiterentwickeln, bleiben die Anforderungen an die Leistungsaufnahme für die kommenden Jahre voraussichtlich konstant (siehe Abbildung 1.1). Die dargestellte Grenze von 0,5 W gilt für mobile Consumerelektronik mit Ausnahme größerer Geräte wie Tablets und wird bereits überschritten [4]. So sind Universalprozessoren alleine oft nicht in der Lage die hohen Anforderungen an Rechenleistung und Energieeffizienz von Embedded Systems zu erfüllen.

Wird daher das Hauptaugenmerk des Designs eines solchen Systems auf die Effizienz der Hardware gelegt, besteht eine Optimierungsmöglichkeit darin, die Hardware exakt auf die Aufgabenstellung anzupassen. Neben einer möglichen Leistungssteigerung können damit Energiebedarf und die benötigte Chipfläche gesenkt werden [VS07, Kapitel 2.2.2]. Allerdings bringt eine derartige Anpassung auch eine Einschränkung der Funktionalität mit sich, sodass ein anwendungsspezifisch entworfener digitaler Schaltkreis für andere Anwendungen nicht mehr geeignet ist. Deshalb spielen bei diesen sogenannten ASICs (Application Specific Integrated Circuit) Entwicklungszeit und -kosten eine wesentliche Rolle [7].

Es gibt nicht nur die beiden konträren Ansätze von ASIC und Universalprozessor, sondern auch verschiedene Abstufungen, bei denen der Befehlssatz und die Hardware teilweise auf das Anwendungsgebiet angepasst sind. Man unterscheidet dabei zwischen ADSPs (Application Domain Specific Processor) und ASIPs (Application Specific Instruction-Set Processor), wobei z. B. DSPs (Digital Signal Processor) in die Kategorie der ADSPs fallen [GB11]. Diese Typen verfügen jedoch über eine statische Anpassung, sodass um das Beispiel des DSPs fortzuführen, der Befehlssatz speziell für Signalverarbeitungsalgorithmen ausgelegt ist. Wenn sich also das Anwendungsgebiet ändert, ist auch hier der Prozessor nicht mehr optimal geeignet und muss möglicherweise ersetzt werden.

Wegen Rechenleistung, Entwicklungsaufwand und Energieeffizienz wäre deshalb eine Kombination der Vorteile von ASICs, ADSPs und Universalprozessoren wünschenswert, um eine einzige Hardwarelösung für alle Problemstellungen zu haben. Dabei garantiert der Universalprozessor, dass alle aktuellen und zukünftigen Anwendungsgebiete abgedeckt werden und bestehende Software kompatibel bleibt. Der ADSP stellt immer die passenden Maschinenbefehle zur Verfügung, um eine effiziente Programmierung unter Benutzung von vorhandenen Entwicklungsumgebungen zu ermöglichen. Der ASIC schließlich gewährleistet eine optimale Hardware, welche im Stande ist alle Anforderungen in Bezug auf Rechenleistung und Energieeffizienz zu erfüllen. Da diese Hardware somit für alle Problemstellungen geeignet ist, erfüllt sich auch die Forderung nach einer effizienten Wiederverwertung des Designs.

Als Folge der in diesem Abschnitt durchgeführten Überlegungen bezüglich Prozessoreigenschaften wird die wissenschaftliche Problemstellung für den weiteren Verlauf der Diplomarbeit abgeleitet:

- Optimierung eines Universalprozessors hinsichtlich Rechenleistung und Energieeffizienz durch Befehlssatzerweiterung

- Beibehaltung von Standardbefehlssatz zur Maximierung der Wiederverwendung von Software und Entwicklungswerkzeugen

- zukünftige Erweiterbarkeit / Variation des Applikationsgebietes ohne Modifikation des Prozessorkerns zur Maximierung der Wiederverwendung des Hardwaredesigns und Minimierung des dabei entstehenden Overheads

# 1.2 Aufgabenstellung

Die Aufgabe dieser Diplomarbeit ist es, eine Lösung für die in Kapitel 1.1 präsentierte Problemstellung zu erarbeiten und eine eigene Prozessorarchitektur auf Basis dieser Anforderungen zu entwickeln. Das setzt einen flexiblen Aufbau des Prozessors voraus, wobei eine zweigeteilte Flexibilisierung vorgesehen ist.

Den ersten Teil der Flexibilisierung bilden spezielle Hardwareerweiterungen, die den Befehlssatz des Prozessors erweitern und optimal auf das aktuelle Aufgabenfeld angepasst werden können. Damit eine bestmögliche Ausnutzung der Erweiterungen erreicht werden kann, sollen diese rekonfigurierbar sein, zudem soll es möglich sein die Hardware auch während der Programmausführung über Maschinenbefehle zu rekonfigurieren. So kann der erweiterte Befehlssatz des Prozessors auf die Anforderungen einer laufenden Anwendung flexibel angepasst werden, um eine effiziente Abarbeitung der benötigten Operationen zu ermöglichen. Für die Erweiterungen bzw. die durch

sie zur Verfügung gestellten Befehle bedeutet das, dass sie je nach Konfiguration unterschiedliche Operationen ausführen können. Durch diese Form der Anpassung kann daher nicht nur die Rechenleistung gesteigert, sondern auch der Energieverbrauch durch die eine Verringerung der auszuführenden Befehle reduziert werden.

Der zweite Teil der Prozessorflexibilisierung sieht vor, die Prozessorerweiterungen austauschbar zu gestalten, um den Chip bereits vor der Fertigung konfigurieren zu können. Diese Möglichkeit zielt damit sowohl auf zukünftige Anwendungen, als auch auf eine optimale Ausstattung des Prozessors für existierende Anwendungen ab. Somit kann jeder Prozessor individuell auf seine spätere Aufgabe angepasst werden, wobei sogar Bibliotheken für Erweiterungen vorstellbar wären.

Auch für den Fall, dass eine gewünschte Erweiterung noch nicht existieren sollte, reduziert sich der Entwicklungs- und Testaufwand erheblich, da der eigentliche Prozessor nicht verändert wird und sich der Entwicklungsaufwand nur auf die neu zu entwerfenden Erweiterung bezieht. Durch die Trennung von Erweiterungsbefehlen und allgemeinen Prozessorkern können die Entwicklungskosten gesenkt und die Time-to-Market reduziert werden. Ein weiterer Vorteil bei der Verwendung eines fixen Prozessorkerns ist, dass der Standardbefehlssatz des Prozessors gleich bleibt und somit Kompatibilität zu früheren Programmen erhalten bleibt. Zudem können auch bereits vorhandene Compiler weiter verwendet werden und müssen nur für die Verwendung des erweiterten Befehlssatzes angepasst werden.

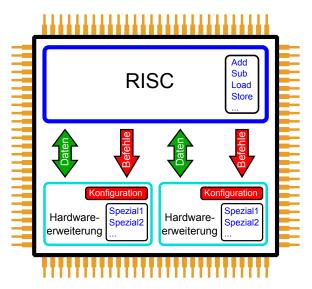

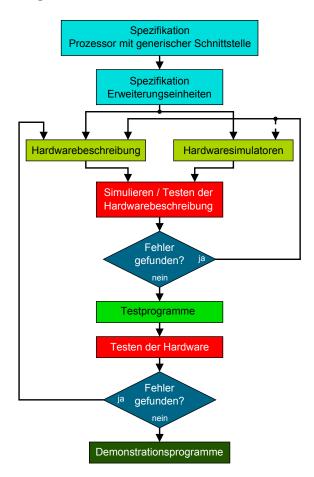

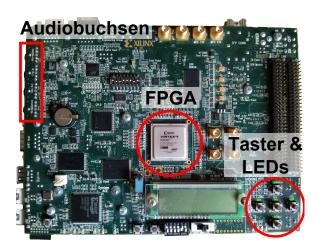

Das vorgestellte Konzept ist in Abbildung 1.3 dargestellt und soll im Zuge der Diplomarbeit zu einem konkreten Entwurf eines Prozessordesigns weiterentwickelt werden. Daraus soll eine Beispielimplementierung mittels VHDL (Very high speed integrated circuit Hardware Description Language) erstellt werden, wobei das Ziel der Implementierung ein funktionierender Prototyp in einem FPGA (Field Programmable Gate Array) ist. Als Ausgangspunkt dafür dient ein RISC (Reduced Instruction Set Computer) Prozessor. Dieser besitzt im Vergleich zum CISC (Complex Instruction Set Computer) Prozessor eine reduzierte Komplexität und ist daher besser geeignet um Modifikationen vorzunehmen. Der implementierte Prototyp soll dabei neben dem eigentlichen Prozessor über zwei zur Laufzeit rekonfigurierbare Hardwareerweiterungen verfügen. Die Rekonfiguration der Erweiterungseinheiten soll jedoch nicht auf Basis einer dynamischen Konfiguration des FPGAs erfolgen, sondern durch eine Rekonfiguration deren Struktur ermöglicht werden, um nicht auf FPGAs als Zielhardware beschränkt zu sein. Für das Hinzufügen oder gegebenenfalls Entfernen von Erweiterungskomponenten kann aber durchaus die Konfiguration des FPGAs dienen, da diese Art der Konfigurierung ohnehin vor einer eventuellen Fertigung vorgesehen ist.

Um die Funktionsfähigkeit des Prototypen zu zeigen, sollen Demonstrationsprogramme erstellt werden Es wird auf bereits existierende Assembler zurückgegriffen, da der Standardbefehlssatz des implementierten Prozessors kompatibel zu gängigen RISC-Architekturen sein soll. Mit Hilfe dieser Beispielprogramme soll abschließend die Rekonfiguration der Hardware gezeigt und die erzielbaren Leistungssteigerungen untersucht werden.

Abbildung 1.3: RISC mit rekonfigurierbaren Befehlssatzerweiterungen

## 1.3 Gliederung der Arbeit

Im ersten Teil dieser Arbeit werden die Möglichkeiten von rekonfigurierbaren Befehlssatzerweiterungen untersucht. Bestehende Arbeiten und Lösungen auf diesem Gebiet werden dazu in Kapitel 2 diskutiert und mit dem eigenen Ansatz verglichen. Nach diesem Überblick über den Stand der Technik wird in Kapitel 3 der Ansatz zur Verwirklichung des Konzepts aus Kapitel 1.2 im Detail vorgestellt. Darauf aufbauend wird ein beispielhaftes Hardwaredesign entwickelt, welches in Kapitel 4 vorgestellt wird.

Auf die zur Demonstration des Prototypen entwickelten Beispielprogramme wird in Kapitel 5 eingegangen. Dabei widmet sich das Kapitel im ersten Teil dem Testen der Hardware und der Erstellung dieser Tests. Für die Tests wurden im Zuge der Diplomarbeit Simulationsmodelle in MATLAB geschrieben, die das Verhalten der Ein- und Ausgänge unter Berücksichtigung des Timings darstellen. Dadurch ist es möglich, Stimulidaten für die Testbenches automatisch zu generieren. Im zweiten Teilabschnitt werden die implementierten Erweiterungsbefehle mit den Softwarependants des Standardbefehlssatzes ohne Hardwareerweiterungen gegenüber gestellt. Dabei wird sowohl auf die Leistungssteigerung, als auch den erhöhten Hardwareaufwand durch die Erweiterungen eingegangen. Außerdem werden insbesondere die bei der Implementierung aufgetretenen Probleme angeführt und diskutiert.

Den Abschluss der Arbeit bildet Kapitel 6, in dem die Arbeit und deren wichtigste Resultate zusammengefasst werden. Weiters gibt dieses Kapitel einen kurzen Ausblick auf mögliche Weiterentwicklungen. In Kapitel A werden zusätzliche Informationen für die Programmierung des implementierten Prozessors bereitgestellt. Außerdem befindet sich hier eine Auflistung der Erweiterungsbefehle für die Spezialhardwareerweiterungen.

# 2 Stand der Technik

Dieses Kapital widmet sich dem Stand der Technik und stellt vorhandene Konzepte kurz vor. Zuerst wird das Prinzip der Befehlssatzerweiterung vorgestellt und daran anschließend exemplarisch vorangegangene Arbeiten auf diesem Gebiet chronologisch präsentiert. Es wird auf die Vorund Nachteile der Arbeiten eingegangen und insbesondere die Unterschiede zu dieser Diplomarbeit behandelt und diskutiert.

# 2.1 Befehlssatzerweiterungen

Mit dem Standardbefehlssatz eines Universalprozessors kann zwar annähernd beliebige Funktionalität bereitgestellt werden, allerdings ist das in manchen Fällen sehr ineffizient und die Kosten in Form von Taktzyklen und benötigter Energie für diese Operationen sind signifikant. Treten solch ineffiziente Operationen häufig auf, kann dies bezüglich der benötigten Ausführungszeit ein Problem darstellen. Deshalb werden Prozessoren schon seit mehreren Jahrzehnten mit zusätzlichen Befehlen ausgestattet, die ansonsten sehr ineffiziente Operationen als direkte Maschinenbefehle bereitstellen. In den 1980er Jahren, als die Transistorzahl pro Chip noch auf wenige hunderttausend limitiert war [Bon98], wurden beispielsweise Coprozessoren entwickelt, die den Befehlssatz des Hauptprozessors mit Operationen basierend auf dem IEEE (Institute of Electrical and Electronics Engineers) Gleitkommazahlenformat (siehe Kapitel A.1) erweitern. Ein ausgewähltes Beispiel dafür ist der MC68881 Coprozessor von Motorola, welcher als Erweiterung der M68000 Familie konzipiert wurde [HC83]. Diese Form der Erweiterung zeichnet sich dadurch aus, dass Coprozessor und Hauptprozessor meist parallel arbeiten und zum Teil über eine eigene Speicheranbindung verfügen [GB11]. Während im Einführungsbeispiel der Coprozessor einen eigenen Chip darstellt, sind in aktuellen Implementierungen die Coprozessoren auf dem gleichen Chip wie die Hauptprozessoren verbaut. Beispiele dafür lassen sich sogar bei den in aktuellen FPGAs integrierten Prozessoren finden, wie etwa die Serie 7 von Xilinx FPGAs zeigt [13, Kapitel 3.2].

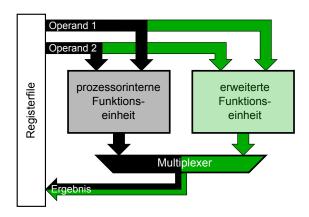

Eine weitere Form der Befehlssatzerweiterung stellt die Erweiterung über zusätzlich integrierte Funktionseinheiten dar. Diese Erweiterungsform entspricht dem Ansatz der Diplomarbeit und wird deshalb als einzige im Folgenden untersucht. Dabei handelt es sich um eine enge Kopplung mit dem Prozessor, wobei die Funktionseinheit parallel zur Ausführungseinheit im Datenpfad liegt [GB11]. Die wesentlichen Vorteile dieser Art der Anbindung ist der zu vernachlässigende Kommunikations-Overhead zwischen erweiterter Funktionseinheit und restlichem Prozessor, sowie die hohe erreichbare Kommunikationsbandbreite. Abbildung 2.1 zeigt dazu ein einfaches Beispiel mit einer Funktionseinheit als Erweiterung, welche wie die prozessorinterne Ausführungseinheit über zwei Eingänge und einen Ausgang verfügt.

Abbildung 2.1: Datenpfad erweitert mit zusätzlicher Funktionseinheit

Dabei ist ersichtlich, dass in diesem Beispiel alle Operationen auf Prozessorregistern ausgeführt werden. Um Beispiele für diesen Aufbau zu geben werden im Folgenden ausgewählte existierende Architekturen behandelt, die über solche Funktionseinheiten erweitert wurden. Dabei liegt das Hauptaugenmerk der Betrachtungen auf der Rekonfiguration und Flexibilität dieser Erweiterungen, was auch der Zielsetzung dieser Arbeit entspricht.

#### 2.2 Die PRISC-1 Architektur

Ein frühes Beispiel für die Befehlssatzerweiterung über eine zusätzliche rekonfigurierbare Funktionseinheit stellt die PRISC-1 Architektur dar [RS94], wobei PRISC für **PR**ogrammable Instruction Set Computer steht. Dieser Ansatz beinhaltet einige Kernpunkte der Diplomarbeit, allerdings gibt es auch manche Nachteile, die im Folgenden beleuchtet werden.

In der PRISC-1 Architektur wird ein universeller RISC Prozessor mit einer rekonfigurierbaren Funktionseinheit erweitert, welche als PFU (Programmable Functional Unit) bezeichnet wird. Den Ausgangspunkt bildet ein MIPS (Microprocessor without Interlocked Pipeline Stages) Prozessor, wie er auch in der Diplomarbeit verwendet wird. Der MIPS Prozessor ist ein 32 Bit RISC Prozessor, der 1984 an der Stanford Universität entwickelt wurde [RPJ+84] und in den Kapiteln 3.2 und 4.2 genauer behandelt wird. Die PFU ist ähnlich aufgebaut wie die rekonfigurierbare fine-grain Logik eines FPGAs, jedoch mit dem Ziel eine geringere Laufzeit zu besitzen als die normale, fest verdrahtete Ausführungseinheit des Prozessors. Durch die geringere Signallaufzeit wird gewährleistet, dass die erzielbare Taktfrequenz des gesamten Prozessorsystems in erster Näherung nicht negativ von der Erweiterung beeinflusst wird. Deshalb wurde ein einfacher Aufbau gewählt, welcher aus nur vier Logikebenen besteht, wobei jeweils Interconnection-Matrizen und

LUTs (Look Up Table) abwechselnd angeordnet sind. Sowohl die Interconnection-Matrizen, als auch die LUTs sind zur Laufzeit rekonfigurierbar, was mehrere hundert Taktzyklen in Anspruch nimmt. Die Ermittlung und Generierung der passenden Konfigurationen für diese Erweiterungseinheit erfolgt bei der Programmerstellung. Dabei werden nur solche Funktionen generiert, die zum einen mit den physikalischen Ressourcen implementiert werden können und zum anderen unter Beachtung der Rekonfigurationszeit einen Geschwindigkeitsvorteil verschaffen. Die Konfigurationen der extrahierten Funktionen werden dann in die Datei des ausführbaren Programms eingebunden. Durch Einführung eines neuen Befehlsformats werden die Zusatzfunktionen schließlich aufgerufen, wobei die Funktion selbst über ein 11 Bit langes Feld im Befehl codiert wird. Somit stehen 2047 unterschiedliche Funktionen zur Verfügung. Sobald eine solche Zusatzfunktion ausgeführt werden soll, wird zuerst der 11 Bit lange Funktionscode überprüft und festgestellt, ob die richtige Konfiguration geladen ist. Ist das der Fall, dann beträgt die Ausführungszeit genau einen Taktzyklus. Andernfalls wird eine Ausnahmebehandlung durchgeführt und es vergehen einige hundert Taktzyklen, bis die richtige Konfiguration geladen ist und der Befehl ausgeführt werden kann. Während dieser Zeit ist der gesamte Prozessor blockiert.

Durch den besprochenen Aufbau der PRISC-1 Architektur ergeben sich jedoch einige Nachteile, welche im Folgenden aufgezählt und erörtert werden.

#### • Beschränkung auf eine PFU

Im Gegensatz zu dem in dieser Diplomarbeit gewählten Ansatz wird nur eine PFU unterstützt, welche eine spezielle Funktion bereitstellt. Wird eine andere Funktion benötigt, muss die PFU jedes Mal umkonfiguriert werden.

#### • enormer Konfigurations-Overhead

Da der Prozessor bei jeder Rekonfigurierung aufgrund der Logikgranularität mehrere hundert Taktzyklen angehalten werden muss, reduziert sich der erzielbare Leistungsgewinn erheblich. So kann es vor allem in Kombination mit dem vorherigen Punkt vorkommen, dass viele potentiell beschleunigende Funktionen nicht mehr rentabel sind und daher wegfallen.

#### • Einschränkung der Verarbeitungszeit auf einen Taktzyklus

Die Hardware von PRISC-1 ist zwar nicht auf bestimmte Anwendungen beschränkt, allerdings können durch die geringe zur Verfügung stehende Verarbeitungszeit nur wenig komplexe logische Funktionen konfiguriert werden. Aus diesem Grund lässt der in Kapitel 3 gewählte Ansatz die Beschränkung auf nur einen Taktzyklus Verarbeitungszeit fallen, was folgende Auswirkungen hat:

- Es ist eine zusätzliche Kommunikation mit den anderen Prozessoreinheiten erforderlich. Der Hardwareaufwand dafür ist allerdings relativ gering und die Ausführungszeit wird nicht negativ beeinflusst.

- Die minimale Ausführungszeit der Erweiterungsbefehle wird von einem Taktzyklus auf drei erhöht, da beim gewählten Ansatz der in Abbildung 2.1 gezeigte Multiplexer in eine spätere Stufe der Prozessor-Pipeline verlegt wird.

- Theoretisch kann jede beliebige Operation mit passender Anzahl an Ein- und Ausgängen mit einer PFU realisiert werden.

- Durch die Verschiebung des Multiplexers wird die Anzahl an Logikebenen in der Ausführungseinheit um die des Multiplexers verringert. Wenn die Ausführungsstufe den kritischen Pfad für die Signallaufzeit der Prozessor-Pipeline darstellt, lässt sich dadurch eine etwas höhere Taktfrequenz erzielen.

#### • vorgeschriebene Verwendung des Funktionscodes

Durch dedizierte Verwendung des Funktionscodes zur Funktionsselektion geht die Möglichkeit zur freien Verwendung dieser Bits bei der Kommunikation mit der PFU verloren. Deshalb werden die Funktionscodes beim Ansatz dieser Arbeit im Unterschied zur PRISC-1 Architektur direkt an den Erweiterungsfunktionsblock übergeben, wodurch sich folgende Konsequenzen ergeben:

- Die Funktionscode-Bits k\u00f6nnen entweder zur Selektion einer bestimmten Konfiguration, als konstanter Operand oder als Konfiguration selbst interpretiert werden.

- Bei Vorhandensein einer falschen PFU-Konfiguration kann keine automatische Ausnahmebehandlung durchgeführt werden. Deshalb ist es Aufgabe des Compilers bzw. der Erweiterungseinheit, jeweils die richtige Konfiguration zu laden.

## 2.3 Die OneChip Architektur

Eine weitere Arbeit auf dem Gebiet der rekonfigurierbaren Befehlssatzerweiterungen stellt die 'OneChip' Architektur der Universität von Toronto dar [WC96]. Hier wird ebenfalls ein MIPS-ähnlicher Prozessor mit zusätzlichen Funktionseinheiten erweitert. Im Vergleich zur PRISC-1 Architektur wird allerdings die Beschränkung auf nur einen Taktzyklus Verarbeitungszeit in den PFUs aufgehoben.

Das Resultat dieser Arbeit ist ein Prozessor, dessen interne Ausführungseinheit mit ein oder mehreren zusätzlichen konfigurierbaren Funktionseinheiten erweitert werden kann. Dabei ist der Prozessorkern vollständig mit dem Standardbefehlssatz kompatibel und als fest verdrahtete Implementierung vorgesehen, wodurch die Kompatibilität zu älteren Programmen und Compilern erhalten bleibt. Die FPGA-ähnliche rekonfigurierbare Logik ist im Design um den Prozessorkern angeordnet und verfügt über zwei zusätzliche Speicher, wovon einer als Statusspeicher für die Funktionseinheiten dient und der zweite Speicher vorcompilierte Images für Konfigurationen der PFUs enthält. Durch diesen Aufbau und der Komprimierung der Konfigurationen ist es laut [WC96] theoretisch möglich die für die rekonfigurierbare Logik erforderliche Chipfläche stark zu reduzieren. Da diese Logik den Großteil der benötigten Chipfläche des vorgeschlagenen Designs bildet, profitiert auch die Gesamtfläche erheblich von diesen Optimierungen.

Da der Prototyp jedoch auf einem Multi-FPGA-System realisiert wurde, konnte von den oben genannten Optimierungen zur FPGA-Logik und dem fest verdrahteten Prozessorkern nicht Gebrauch gemacht werden. Somit ist das System aufgrund von Hardwarelimitierungen auf eine einzige PFU beschränkt und kann nur mit 1,25 MHz betrieben werden. Neben den Einschränkungen des Prototypen hat das Konzept dieses Systems allerdings auch den Nachteil, dass die Konfigurierung der PFUs nur während des Startvorganges möglich ist und somit eine dynamische Rekonfigurierung wegfällt. Während des Betriebs kann daher lediglich per Multiplexer zwischen den bereits konfigurierten PFUs umgeschaltet werden.

Eine direkte Weiterentwicklung hierzu stellt 'OneChip-98' [JC99] dar. Hier wird eine Möglichkeit der dynamischen Rekonfigurierung zur Laufzeit vorgeschlagen, welche mit vorgeladenen Konfigurationen arbeitet. Dafür wird ein DPGA (Dynamically Programmable Gate Array) verwendet, welches im Unterschied zum FPGA mehrere Konfigurationen parallel halten kann [TCE<sup>+</sup>95]. Dadurch besteht die Rekonfiguration aus einem Kontext-Switch. Dieser benötigt einen Taktzyklus und ist daher um viele Größenordnungen schneller als die Rekonfiguration eines FPGAs. Wird

nun ein Erweiterungsbefehl decodiert, bekommt ihn das DPGA zur Verfügung gestellt. Dieses schaltet dann bei Bedarf auf die entsprechende Konfiguration um und arbeitet den Befehl ab. Aufgrund der begrenzten Anzahl an vorgeladenen Konfigurationen, kann es jedoch vorkommen, dass die gewünschte Konfiguration nicht vorgeladen ist und somit erst geladen werden muss. Das kann per Compilerdirektive oder bei Bedarf erfolgen, wobei Letzteres allerdings eine erhebliche Befehlsverzögerung verursacht. Durch das Vorladen der neuen Konfiguration muss eine andere überschrieben werden (z. B. die längste nicht verwendete). Der Prozessor muss aber während dieses Vorganges im Gegensatz zur PRISC-1 Architektur nicht angehalten werden, da der rekonfigurierbare Teil das Laden der neuen Konfiguration selbst vornimmt.

Die zweite Weiterentwicklung von OneChip-98 stellt eine direkte Speicherschnittstelle dar, die es der PFU ermöglicht direkt auf Speicherinhalten zu operieren. Dadurch müssen diese nicht extra in das Registerfile des Prozessors geladen und anschließend wieder in den Speicher zurückgeschrieben werden. Das hat vor allem für die Verarbeitung von Datenblöcken wie z.B. bei der FFT (Fast Fourier Transform) Vorteile und die PFU kann unabhängig vom Prozessorkern parallel zu diesem arbeiten.

In dieser Diplomarbeit wurde solch eine Speicheranbindung zwar auch in Betracht gezogen, jedoch weist diese Form der Erweiterung bereits Charakterzüge einer Coprozessoranbindung auf. Das ist zum einen nicht Ziel der Arbeit und zum anderen gibt es auch bereits eine Spezialisierung auf blockbasierte Verarbeitung vor. Neben dem zusätzlichen Hardwareaufwand für die Speicheranbindung kommt es bei diesem Ansatz im Fall von Datenabhängigkeiten zwischen Prozessor und PFU zwangsläufig zu längeren Bearbeitungszeiten, da dazwischen immer Speicherzugriffe erforderlich sind. Außerdem besteht auch ohne eine zusätzliche Speicheranbindung die Möglichkeit der Parallelverarbeitung von Prozessor und PFU, da der restliche Prozessor bereits parallel dazu andere Befehle bearbeiten kann (siehe Kapitel 3). Die einzige Einschränkung im Vergleich zur direkten Speicheranbindung ist daher nur die begrenzte Anzahl von Eingangsoperanden und Ergebnissen pro Erweiterungsbefehl.

Bezüglich der dynamischen Rekonfigurierung der PFUs zur Laufzeit können leider keine weiteren Aussagen getroffen werden, da aufgrund von Hardwarebeschränkungen der DPGA-Ansatz und seine Funktionalität nicht in den OneChip-98 Prototypen übernommen wurden. Somit wird diese Architektur auch wieder nur beim Hochfahren einmalig konfiguriert und der weitere Programmablauf muss sich auf eine PFU-Funktionalität beschränken.

#### 2.4 Die ReRISC Architektur

Die ReRISC (Reconfigurable RISC) Architektur [VKTN06] stellt eine aktuelle Arbeit auf dem Gebiet der rekonfigurierbaren Befehlssatzerweiterungen dar. Als Basis wird auch hier wie bei OneChip-98 ein MIPS ähnlicher DLX (DeLuXe) Prozessor mit fünfstufiger Pipeline verwendet. Bezüglich der Befehlssatzerweiterung ist die Architektur ähnlich aufgebaut wie die PRISC-1 Architektur mit zwei signifikanten Unterschieden. Zum einen verwendet sie für die PFU im Gegensatz zu PRISC-1 coarse-grain Logik (siehe Kapitel 3.4.2) und zum anderen erstreckt sich die PFU über zwei Pipeline-Stufen des Prozessors. Ersteres hat den Vorteil, dass die maximale Rekonfigurationszeit wesentlich geringer ausfällt und die rekonfigurierbare Hardware effizienter arbeiten kann. Der zweite Unterschied sorgt dafür, dass auch komplexere Funktionen mit zwei Taktzyklen Verarbeitungszeit realisiert werden können. Zudem besteht die Möglichkeit, das Ergebnis sowohl nach der ersten, als auch nach der zweiten PFU-Stufe zurück in den prozessorinternen Datenpfad

zu routen. Komplexere Funktionen, die mehr als zwei Taktzyklen benötigen sind zwar möglich, jedoch muss dafür der Prozessor angehalten werden. Ein weiterer Unterschied von ReRISC zu den bereits behandelten Architekturen besteht in der Anzahl an Operandeneingängen der PFU, welche hier auf vier verdoppelt ist. Somit gibt es mehr Freiheitsgrade bei den möglichen Spezialbefehlen. Um gewünschte Funktionalität und Rekonfigurierbarkeit bereitstellen zu können, ist die PFU aus folgenden drei Ebenen aufgebaut:

- Prozessierungsebene

- Interconnection-Ebene

- Konfigurationsebene

Die Prozessierungsebene besteht aus einem Array von coarse-grain PEs (Processing Element), die jeweils eine einfache logische oder arithmetische Operation mit zwei Eingängen und einem Ausgang ausführen können. Am Ausgang eines solchen PEs befindet sich ein Multiplexer, mit dem zwischen direkten und registerten Ausgang selektiert werden kann. Dadurch ist es möglich bei Auswahl des direkten Ausgangs mehrere PEs innerhalb eines Taktzyklus in Serie zu schalten, solange die Laufzeit des kritischen Prozessorpfads nicht überschritten wird. Die Interconnection-Ebene ist für die Verbindung der PEs untereinander und zum restlichen Prozessor verantwortlich. Damit bildet sie neben den Multiplexern in den PEs den Hauptbestandteil der Rekonfigurierbarkeit. Um die dynamische Rekonfiguration der PFU zur Laufzeit kümmert sich die Konfigurationsebene, wobei das Rekonfigurieren ähnlich funktioniert wie es bei der OneChip-98 Architektur vorgeschlagen wurde. In einem lokalen Speicher befindet sich eine begrenzte Anzahl an Konfigurationen, auf die sofort zurückgegriffen werden kann. Wenn ein PFU-Befehl ausgeführt wird, überprüft die Konfigurationsebene, ob die erforderliche Konfiguration vorhanden ist und wendet diese bei Vorhandensein gleich an. Andernfalls wird ein Miss-Flag gesetzt und die erforderliche Konfiguration muss in den lokalen Speicher geladen werden, was aufgrund der coarse-grain Logik nur wenige Taktzyklen benötigt.

Ein sehr großer Vorteil dieser Architektur ist das Vorhandensein einer vollautomatischen Entwicklungsumgebung, welche die rekonfigurierbare Logik vor dem Benutzer verbirgt. Das wird dadurch erreicht, dass die Erweiterungsbefehle selbstständig ermittelt werden und die dafür notwendige Hardware automatisch generiert wird. Somit hat die Erweiterung keinen Nachteil auf die Programmierung, während sie bei der Programmausführung für erhebliche Beschleunigungen sorgt. Die Bereitstellung einer solchen Entwicklungsumgebung ist jedoch nicht das Ziel der Diplomarbeit und daher für einen Vergleich der Architekturen zweitrangig.

Auch wenn die ReRISC-Architektur im Vergleich zu seinen Vorgängern erhebliche Verbesserungen aufweist und diese auch wirklich in den Prototypen integriert wurden, gibt es dennoch Einschränkungen in der Flexibilität der erweiterten Funktionseinheiten. Durch den Aufbau der Anbindung der PFU wird eine maximale Verarbeitungszeit von nur zwei Taktzyklen nahegelegt. Auch wenn theoretisch längere Zeiten erlaubt sind, reduziert sich der dadurch mögliche Leistungsgewinn aufgrund der Tatsache, dass der Prozessor dazu angehalten werden muss. Aus diesem Grund wird eine Parallelverarbeitung von Prozessor und PFU verhindert. Diese Einschränkung gilt nicht für den in Kapitel 3 gewählten Ansatz, welcher außerdem im Gegensatz zur hier behandelten Architektur mehrere physikalische PFUs unterstützt, um explizit von deren Parallelverarbeitung Gebrauch zu machen.

# 2.5 Vergleich der Architekturen

Um einen Überblick über die in diesem Kapitel besprochenen Architekturen zu erhalten, sind die wichtigsten Merkmale dieser Architekturen in Tabelle 2.1 aufgelistet. Ebenfalls aufgelistet ist der eigene Ansatz, welcher im folgenden Kapitel im Detail besprochen wird und zum Ziel hat, möglichst viele Vorteile der bisherigen Arbeiten zu vereinen. Ein besonders wichtiger Punkt dabei ist die Flexibilität der Erweiterungseinheiten, die von keiner der vorgestellten Architekturen erreicht wird. So ist es in den bisher diskutierten Arbeiten nicht vorgesehen echte Hardware einfach auszutauschen um sie durch neue zu ersetzen und damit die Ausstattung des Prozessors vor der Fertigung anzupassen.

Tabelle 2.1: Vergleich der präsentierten Architekturen und des eigenen Ansatzes

| Architektur                             | PRISC-1      | OneChip          | OneChip-98    | ReRISC       | eigener<br>Ansatz |

|-----------------------------------------|--------------|------------------|---------------|--------------|-------------------|

| Basisprozessor                          | MIPS R2000   | MIPS R4400       | DLX           | DLX          | MIPS R2000        |

| kompatibel zu<br>Standardbefehlssatz    | ja           | ja               | ja            | ja           | ja                |

| Anzahl PFUs                             | 1            | 1 - ?*           | 1             | 1            | 1 - 4/8*          |

| Taktzyklen PFU                          | 1            | 1 -              | 1 -           | 1 - 2        | 3 -               |

| Rekonfigurierbarkeit                    | zur Laufzeit | beim Einschalten | zur Laufzeit* | zur Laufzeit | zur Laufzeit**    |

| Rekonfigurationszeit                    | viele Zyklen | =                | kurz*,***     | 0/1***       | 0/1**             |

| Prozessor stoppt bei<br>Rekonfiguration | ja           | -                | nein          | ja           | nein**            |

| Logikgranularität                       | fein         | fein             | fein          | grob         | grob**            |

| PFU-                                    | Registerfile | Registerfile     | Speicher      | Registerfile | Registerfile      |

| Datenanbindung                          | 2 Eingänge   | 2 Eingänge       | Speicher      | 4 Eingänge   | 2 Eingänge        |

<sup>\*</sup>nicht im Prototyp

<sup>\*\*</sup>Implementierungsabhängig

$<sup>\</sup>ensuremath{^{***}}$ nur wenn Konfiguration lokal vorhanden

# 3 Gewählter Ansatz

In diesem Kapitel wird der eigene Lösungsansatz beschrieben. Dafür wird zuerst die Problembeschreibung erörtert, bevor auf die Details der Lösung eingegangen wird. Außerdem wird auch theoretischer Hintergrund behandelt, um konkrete Entscheidungen besser nachvollzielbar zu machen.

# 3.1 Zielsetzung

Wie in der Einleitung Kapitel 1.2 bereits kurz umrissen, soll in einem Top-Down Entwurf ein RISC Prozessor mit rekonfigurierbaren Befehlssatzerweiterungen entwickelt werden. Dabei soll der Standardbefehlssatz des Prozessors unverändert bleiben, um mit vorhandenen Programmen und Compilern kompatibel zu sein. Die Erweiterungen sollen eng mit dem Prozessor als zusätzliche Funktionseinheiten gekoppelt sein um eine schnelle und effektive Kommunikation zu ermöglichen. Dazu werden die Erweiterungseinheiten parallel in den Datenpfad des Prozessors integriert.

Um eine Applikationsunabhängigkeit zu schaffen und auch zukünftige Befehlssatzerweiterungen zu ermöglichen, sollen beliebige Erweiterungen unterstützt werden. Dadurch wird es später möglich sein, den Prozessor vor der Fertigung auf die Anforderungen der späteren Applikation gezielt abzustimmen. Dies garantiert, dass applikations- oder applikationsgebietspezifische Erweiterungen, sowie Universalerweiterungen je nach Anforderung beliebig zusammengestellt werden können. Somit kann der Prozessor auf verschiedenste Weise optimiert werden wie z. B. auf Chipfläche, Rechenleistung, universeller Einsatzfähigkeit oder Energieverbrauch. Da diese Optimierungsziele sehr unterschiedlich sind, wird auch der dazu erforderliche Hardwareaufbau der Spezialerweiterungen sehr unterschiedlich sein. Deshalb ist es Teil der Zielsetzung, dass theoretisch jede Form von fine- und coarse-grain Logik, sowie fest verdrahteter Logik unterstützt werden soll.

Weiters wird gefordert, den Prozessor mit mehreren Funktionseinheiten erweitern zu können, um etwa statt einer universell konfigurierbaren Einheit mehrere, dafür aber spezialisiertere zu verwenden. Spezialisiertere Logik ist nicht nur schneller und energieeffizienter, sondern benötigt auch weniger Chipfläche als universell konfigurierbare Logik [VS07, Kapitel 2.3]. Außerdem kann so bei besonders hohen Anforderungen an die Rechenleistung die Parallelität der Einheiten ausgenutzt werden, wenn diese längere Operationen ausführen. Das setzt voraus, dass längere Verarbeitungszeiten in den Erweiterungsblöcken auch unterstützt werden. Dafür muss ein Mechanismus zur Synchronisation mit den anderen Prozessoreinheiten entwickelt werden, um keine Fehler durch

Ressourcenkonflikte zu verursachen. Dieses Problem würde ohne Erweiterungen nicht auftreten, weil die Prozessor-Pipeline mit ihrem statischen Ablauf die Ressourcenzugriffe eindeutig vorgibt.

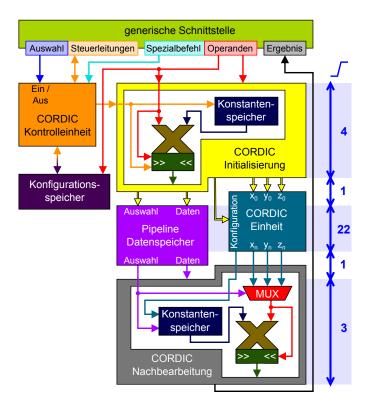

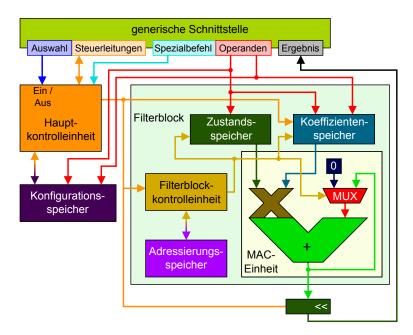

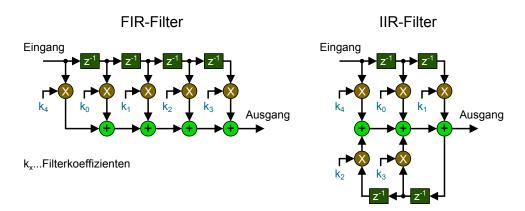

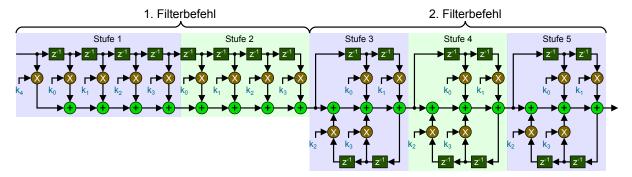

Die eben genannten Anforderungen sollen nach Entwicklung des Konzepts in einen Prototypen implementiert werden. Ein schematischer Aufbau solch eines Systems ist in Kapitel 1.2 Abbildung 1.3 dargestellt. Dabei ist es das Ziel neben dem Prozessor zwei rekonfigurierbare coarse-grain Erweiterungseinheiten zu entwickeln, welche komplexe Operationen ausführen und über wenige Bits zu konfigurieren sind. Diese Erweiterungen sind ein CORDIC-Algorithmus (COordinate Rotation DIgital Computer) in Hardware und ein digitales Filter. Außerdem soll eine dritte Erweiterungseinheit implementiert werden, die mit der Pipeline des Prozessors synchronisiert ist. Diese Erweiterung soll Konvertierungsfunktionen zwischen dem IEEE754 Gleitkommaformat [IEE08] und dem Zweierkomplement Fixkommaformat bereitstellen. Durch die Synchronisation mit der Prozessor-Pipeline ergeben sich mögliche Vorteile, von denen für die Anbindung der Erweiterungseinheit Gebrauch gemacht werden soll. So kann zum einen der Kommunikations-Overhead reduziert werden und zum anderen werden Ressourcenkonflikte ausgeschlossen. Die detaillierte Implementierung dieser Einheiten ist in Kapitel 4 zu finden.

Natürlich sind manuelle Implementierungen von Erweiterungseinheiten und deren Programmcodeanpassung für die Praxis unpraktikabel. Der Idealfall wäre eine vollautomatische Entwicklungsumgebung, in der der Code einer Hochsprache zuerst analysiert wird und unter optimaler

Ausnutzung der Hardware ein Maschinenprogramm erstellt wird. Dabei sollten auch die Konfigurationen der Erweiterungseinheiten mit den zugehörigen Maschinenbefehlen automatisch erzeugt

werden. Sofern die Zielhardware noch nicht existiert, sollte die Entwicklungsumgebung außerdem

in der Lage sein entsprechende Erweiterungskomponenten selbst zu generieren bzw. sie aus einer vorhandenen Bibliothek auszuwählen. Nach Erstellung der Hardware oder bei vorgegebener

Hardware sollten die Befehlssatzerweiterungen gewinnbringend in den Maschinencode eingearbeitet werden, ohne dass der Benutzer eingreifen muss.

#### 3.2 Verwendeter RISC Prozessor

Um den gewählten Ansatz der Implementierung zu präsentieren ist Kenntnis über den verwendeten Prozessor unerlässlich, welcher daher im Folgenden beschrieben wird.

Die Basis des Designs bildet ein RISC Prozessor, wobei ein RISC folgende Eigenschaften aufweist [Jam95, BMS13]:

- Load/Store Architektur

- Operationen werden auf Registern ausgeführt

- wenige, einfache Befehle konstanter Länge

- kurze und einfach gestaltete Pipeline, meist ein Taktzyklus pro Befehl

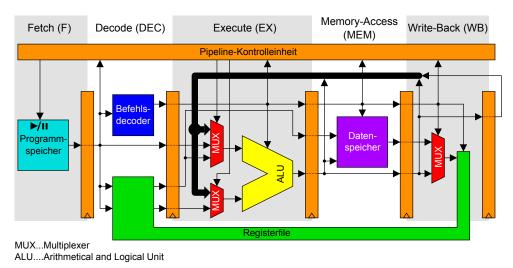

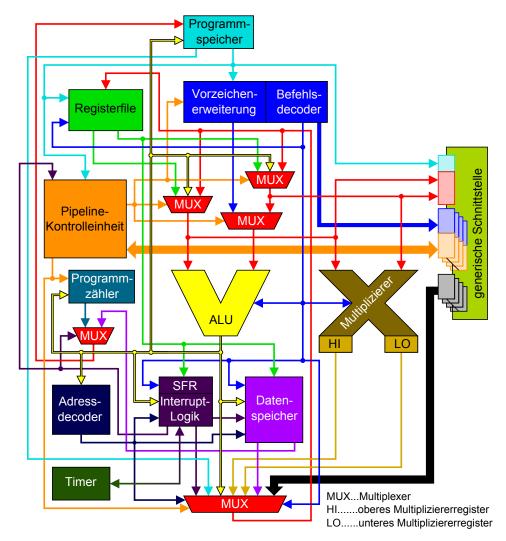

Der verwendete MIPS R2000 [KH92, Kapitel 2] ähnliche Prozessor besitzt eine fünfstufige Pipeline, welche in Abbildung 3.1 vereinfacht dargestellt ist. In der ersten Stufe, der Fetch-Stufe wird ein neuer Befehl vom Programmspeicher geladen. Dieser Befehl wird in der Decode-Stufe decodiert und die benötigten Operanden werden aus den Registern geladen. Die Execute-Stufe ist für

die eigentliche Befehlsabarbeitung verantwortlich. Hier werden sämtliche logische und arithmetische Operationen, sowie Speicheradressberechnungen ausgeführt. In der Memory-Access-Stufe wird im Falle von Lade- oder Speicherbefehlen auf den Datenspeicher zugegriffen. Das Ergebnis der Execute-Stufe bzw. der geladene Speicherinhalt des Datenspeichers wird in der letzten Stufe, der Write-Back-Stufe in das Ergebnisregister zurückgeschrieben.

Abbildung 3.1: Aufbau der MIPS Pipeline

Da das Ergebnisregister aufgrund des Pipeline-Aufbaus erst nach drei Taktzyklen den korrekten Wert enthält, kann es bei zu früher Weiterverarbeitung dieses Wertes zu Datenhazards kommen. Deshalb kümmert sich eine Kontrolleinheit um Datenabhängigkeiten und führt bei Bedarf ein noch nicht in das Registerfile zurückgeschriebenes Ergebnis per Multiplexer an den Eingang der Ausführungseinheit zurück. Im Falle von Ladebefehlen ist das nur bedingt möglich, da das geladene Datum erst in der letzten Pipeline-Stufe zur Verfügung steht, sodass die Pipeline angehalten werden muss, wenn zu früh auf dieses Datum zugegriffen wird. Auch darum kümmert sich die Kontrolleinheit.

Die Ausführungseinheit führt 32 Bit Operationen mit maximal zwei Eingangsoperanden und einem Ergebnis durch. Daher liegt es nahe, dass auch die erweiterten Funktionseinheiten mit dieser Anzahl an Operanden arbeiten, wodurch hier kein zusätzlicher Hardwareaufwand erforderlich ist. Um den Prozessor optimal an die Erweiterungseinheiten anzupassen und aufgrund des relativ einfachen Aufbaus wurde beschlossen, diesen selbst zu implementieren. Eine andere Möglichkeit wäre gewesen, auf vorhandene freie Lizenzen zurückzugreifen. Aufgrund der engen Kopplung von Prozessor und erweiterten Funktionseinheiten muss dabei aber tief in die Pipeline und deren Kontrolleinheit eingegriffen werden. Der daraus entstandene Aufwand wäre vergleichbar mit der durchgeführten spezifischen Implementierung. Die verbleibenden unbedingt benötigten Prozessoreinheiten wie Registerfile und Speicher stellen Standardeinheiten dar und sind daher in vereinfachter Form mit geringem Aufwand zu implementieren.

Der Standardbefehlssatz eines MIPS Prozessors wird durch den implementierten Prozessor eingehalten, mit der Ausnahme, dass einzelne Befehle (z. B. Division) nicht unterstützt werden. Diese sind für das Konzept der rekonfigurierbaren Befehlssatzerweiterungen unwesentlich, hätten aber einen erhöhten Entwicklungsaufwand erfordert und eventuell sogar zu Platzproblemen im verwendeten FPGA geführt. Der Befehlssatz verfügt über drei verschiedene Formate [KH92, Seite 3-1], deren Aufbau in Tabelle 3.1 dargestellt ist. In der ersten Zeile der Tabelle sind die Bitpositionen

im Befehlswort angegeben.

Tabelle 3.1: MIPS Befehlsformate

|          | 31-26              | 25-21  | 20-16 | 15-11 | 10-6      | 5-0      |

|----------|--------------------|--------|-------|-------|-----------|----------|

| R-Format | Opcode<br>(000000) | Rs     | Rt    | Rd    | SA        | Function |

| I-Format | Opcode             | Rs     | Rt    |       | Immediate |          |

| J-Format | Opcode             | Target |       |       |           |          |

Im R-Format sind alle Operationen codiert, die nur auf und mit Registern arbeiten. Der Operationscode, kurz Opcode ist dabei immer '000000' und die auszuführende Operation wird im Feld 'Function' codiert. Die beiden Eingangsoperanden sind die Registerinhalte der mit Rs und Rt codierten Register und das Ergebnis wird in Register Rt zurückgeschrieben. Durch diese Codierung können genau 32 verschiedene Register angesprochen werden, was auch der tatsächlichen Anzahl im Prozessor entspricht. Das Feld 'SA' (Shift Amount) wird nur für fixe Schiebebefehle benötigt und gibt an, um wie viele Bits ein Datum geschoben werden soll.

Befehle, die mit Konstanten arbeiten sind im I-Format codiert. Dazu gehören sowohl Lade- und Speicherbefehle, deren Adresse aus der übergebenen Konstanten plus einem Registerinhalt berechnet wird, als auch sämtliche Operationen, die eine Konstante als Operand haben. Die Konstante, in der Tabelle als 'Immediate' bezeichnet, wird dabei als 16 Bit vorzeichenbehaftete Zahl im Zweierkomplement interpretiert. Das mit Rs codierte Register enthält den zweiten Eingangsoperanden und das Ergebnis bzw. das geladene Datum wird in das Register Rt geschrieben.

Als drittes Befehlsformat gilt das J-Format, welches für Sprünge zu einer fixen Programmadresse, dem 'Target', verwendet wird. Da der Adressbereich des Prozessors 32 Bit beträgt und die Sprungadresse im Befehl nur 26 Bit lang ist, werden die oberen 6 Bit des Programmzählers für die Zieladresse verwendet.

Natürlich ergeben nicht alle Bitkombinationen gültige Maschinenbefehle, so sind z.B. auch im Opcode noch Kombinationen frei, welche beim MIPS für die Ansteuerung von Coprozessoren verwendet werden und in dieser Diplomarbeit zum Ansprechen der Erweiterungseinheiten dienen (siehe Kapitel 3.3.5).

# 3.3 Erweiterungskonzept

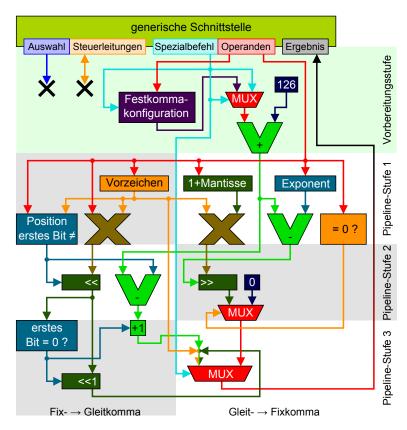

Das Erweiterungskonzept bestimmt die Anbindung der erweiterten Funktionseinheiten an den Basisprozessor und bildet den Kernpunkt dieser Arbeit. Mit diesem Konzept zur Erweiterung werden die Möglichkeiten im Design der Erweiterungskomponenten vorgegeben und der erzielbare Rechenleistungsgewinn, sowie die Erweiterbarkeit sind davon abhängig. Um die gewünschten Anforderungen zu erfüllen, wird eine generische Schnittstelle zwischen dem Prozessor und den Erweiterungseinheiten definiert. Dadurch wird die universelle Erweiterbarkeit und der einfache Austausch von Erweiterungskomponenten ermöglicht. Die Schnittstelle verfügt dabei über separate Leitungen für die beiden Kommunikationsrichtungen vom Prozessor zu den Erweiterungseinheiten und umgekehrt. In den folgenden Unterkapiteln werden diese Kommunikationsrichtungen im Detail vorgestellt und das Kommunikationsprotokoll spezifiziert.

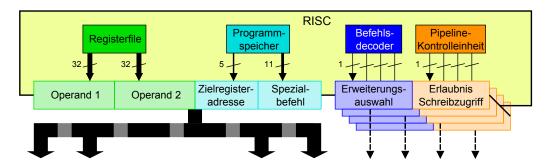

#### 3.3.1 Schnittstelle vom Prozessor zu Erweiterungseinheiten

Für die Kommunikation zu den Erweiterungsfunktionseinheiten ist eine einfache, gemeinsam genutzte Ausführung der meisten Steuer- und Datenleitungen ausreichend. Zwei Steuerleitungen müssen allerdings für jede Erweiterung gesondert vorhanden sein, um jeweils den richtigen Block anzusprechen. Der Aufbau der Schnittstelle ist in Abbildung 3.2 dargestellt. Die zwei 32 Bit Ausgangsoperanden der Schnittstelle sind äquivalent zu den Operanden der R-Befehle im Prozessorstandardbefehlssatz und werden direkt vom Registerfile bereitgestellt. Sie stellen die Eingangsoperanden für die Spezialerweiterungen dar. Ein weiterer Ausgangsparameter der Schnittstelle ist die Zielregisteradresse des Spezialbefehls. Diese ist erforderlich, da der Prozessor aufgrund der Allgemeinheit des Erweiterungskonzepts keine Information über die Ausführungsdauer einer Spezialoperation hat und es zudem sein kann, dass eine Erweiterungseinheit während der Abarbeitung eines Befehls weitere Befehle und damit auch Ergebnisregisteradressen aufnehmen kann. Durch die Bereitstellung der Zielregisteradresse als Ausgangsparameter der Schnittstelle muss sich der Prozessor nicht um die Zwischenspeicherung dieser Adressen kümmern und den Erweiterungseinheiten sind in dieser Hinsicht alle Möglichkeiten offen.

Abbildung 3.2: Schnittstelle vom Prozessor zu Spezialhardwareerweiterungen

Als gemeinsam genutzte Steuer- bzw. Datenleitungen wird ein 11 Bit breites Stück des aktuellen Maschinenbefehls ausgegeben. Dieser Teilbefehl wird im Folgenden als 'Spezialbefehl' bezeichnet. Hier sind zweierlei Besonderheiten gegeben. Zum einen wird dieser Teil des Befehls direkt aus dem Programmspeicher, also von der Fetch-Pipeline-Stufe gelesen. Zum anderen wird nicht vorgegeben, wie diese 11 Bit zu interpretieren sind. Aufgrund der ersten Besonderheit kann ein Erweiterungsblock vorbereitende Arbeiten für den kommenden Befehl während der Decodierungsstufe des Prozessors durchzuführen. Solche vorbereitende Arbeiten können etwa Zugriffe auf lokale Speicher, Laden von Konfigurationen, usw. sein. Somit können unter Umständen Befehlsabarbeitungen in den Erweiterungen beschleunigt werden. Durch die Interpretationsfreiheit des Spezialbefehls kann dieser von den Erweiterungen entweder als Funktionscode, als Operand oder als Konfiguration aufgefasst werden. Dabei ist auch eine Kombination dieser drei Varianten möglich.

Wie in Abbildung 3.2 dargestellt, werden für jedes Erweiterungsmodul zwei Steuerleitungen realisiert. Eine Steuerleitung stellt ein Auswahlsignal zur Verfügung, mit dem der gewünschte Funktionsblock angesprochen wird. Diese Steuerinformation ist jedoch erst einen Taktzyklus nach dem Spezialbefehl verfügbar, da der Befehl im Prozessor erst als Erweiterungsbefehl decodiert werden muss. Im Anschluss daran kann dann die korrekte Erweiterung ausgewählt werden. Das muss von den Spezialfunktionseinheiten berücksichtigt werden, um nicht zu früh falsche Operationen durchzuführen.

Da Erweiterungsbefehle verschieden lange Ausführungszeiten haben können und aufgrund maximaler Rechenleistung parallele Befehlsausführung zugelassen wird, kann es vorkommen, dass mehrere Erweiterungseinheiten gleichzeitig ein Register beschreiben wollen. Weil jedoch das Registerfile nur einen Schreibzugriff pro Taktzyklus erlaubt, stellt dieser Fall einen Ressourcenkonflikt dar und muss geregelt werden. Einen Teil dieser Zugriffsregelung bildet die zweite Steuerleitung, die einer Erweiterungseinheit signalisiert, wenn sie Schreibzugriff auf das Registerfile bekommt. Es wäre auch möglich das Registerfile auf die maximale Anzahl an Schreibzugriffen auszulegen. Allerdings würde dadurch der Hardwareaufwand erheblich steigen und Ressourcenkonflikte könnten trotzdem noch auftreten, wenn etwa mehrere Funktionseinheiten zur gleichen Zeit den gleichen Registerinhalt beschreiben wollten. Diese Konflikte müssten dann ebenfalls gelöst werden. Da dieser übermäßige zusätzliche Aufwand die dadurch gewonnene Leistungssteigerung vermutlich nicht rechtfertigen würde, wurde der Ansatz der Zugriffssteuerung gewählt. Dieser wird in Kapitel 3.3.4 noch im Detail behandelt.

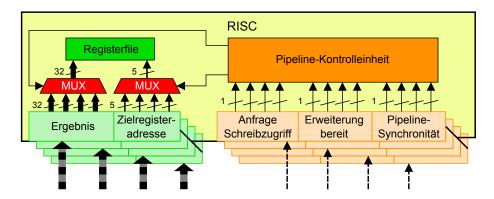

#### 3.3.2 Schnittstelle von Erweiterungseinheiten zum Prozessor

Für die Kommunikation von den Erweiterungseinheiten zum Prozessor sind für die maximal unterstützte Anzahl an Erweiterungen jeweils separate Steuer- und Datenleitungen vorgesehen, um eine schnelle und kollisionsfreie Kommunikation zu gewährleisten. Der Aufbau dieses Teils der Schnittstelle ist in Abbildung 3.3 dargestellt. Über den 32 Bit breiten Ergebniseingang gelangt das von der jeweiligen Erweiterungseinheit produzierte Ergebnis wieder zurück in den Prozessor. Zusätzlich beinhaltet die Eingangsschnittstelle die Adresse des Registers, in der das Ergebnis geschrieben werden soll. Dieser Registeradresseingang ist 5 Bit breit und entspricht somit dem Registeradressbereich des Prozessors.

Abbildung 3.3: Schnittstelle von Spezialhardwareerweiterungen zum Prozessor

Die restlichen drei Leitungen der Schnittstelle dienen als Steuerleitungen. Eine davon ist für die Beantragung des Schreibzugriffs auf das Registerfile zuständig, was für die Zugriffskontrolle erforderlich ist. Die zweite Steuerleitung signalisiert dem Prozessor die Bereitschaft der Erweiterungseinheit zur Aufnahme eines Befehls. Dies bedeutet, dass sie in der Lage ist einen neuen Befehl aufzunehmen. Da die generische Schnittstelle zwei Operationsmodi anhand der Befehlsverarbeitungsdauer einer Erweiterungseinheit unterscheidet, muss diese Information über die letzte Steuerleitung bereitgestellt werden. Dabei gibt ein gesetzter Zustand der Leitung an, dass die am entsprechenden Schnittstellenport befindliche Erweiterung mit der Prozessor-Pipeline synchronisiert ist. Als synchronisiert wird dabei eine gleiche Länge der Datenpfade von Erweiterungseinheit und den dazu parallelen Prozessoreinheiten verstanden. Falls diese Synchronisationsbedingung

erfüllt ist, kann auf jede weitere Steuerkommunikation verzichtet und das Ergebnis ohne Zugriffssteuerung in das Zielregister geschrieben werden. Dieser Vorgang benötigt um einen Taktzyklus weniger als die vollständige Schnittstellenkommunikation, wodurch das Ergebnis schneller verfügbar wird. Es ist auch ein Wechsel von Pipeline-Synchronisation auf beliebige Ausführungsdauer und umgekehrt möglich, jedoch muss der Erweiterungsblock dazu mindestens einen Taktzyklus davor Inaktivität signalisieren. Nur so kann gewährleistet werden, dass während des Wechsels kein Befehl mit falschem Kommunikationsschema an die Erweiterungseinheit gesendet wird. Somit kann auch hinsichtlich der Bearbeitungszeit von Erweiterungsbefehlen beliebig rekonfiguriert werden.

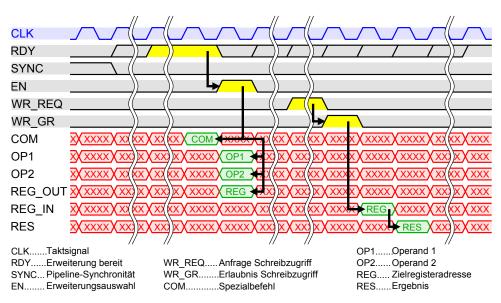

#### 3.3.3 Kommunikationsablauf

Der Kommunikationsablauf gestaltet sich aufgrund der engen Kopplung zwischen Prozessor und Erweiterungen sehr einfach und ist in Abbildung 3.4 dargestellt. Als Allererstes muss eine erweiterte Funktionseinheit signalisieren, ob sie mit der Prozessor-Pipeline synchron läuft oder nicht. Frühestens zeitgleich zu dieser Information darf die Einheit Bereitschaft melden. Nun muss die Erweiterung warten, bis sie vom Prozessor über die Schnittstelle angesprochen wird. Während dieser Zeit wird ständig das 11 Bit lange Stück aller bearbeiteten Maschinenbefehle an die Einheiten gesendet, welche diese Eingangsinformationen ignorieren müssen. Erst wenn vom Prozessor das Auswahlsignal für die entsprechende Erweiterung gesetzt wird, bedeutet das, dass der zuvor empfangene Spezialbefehl gültig ist. Gleichzeitig werden auch die zwei Eingangsoperanden, welche auch Konfigurationsinformationen enthalten können, von der generischen Schnittstelle bereitgestellt.

Abbildung 3.4: Kommunikationsablauf zwischen Prozessor und zusätzlicher Funktionseinheit

Ein weiteres mögliches Szenario ergibt sich wenn der Prozessor einen Spezialbefehl geladen hat, jedoch die entsprechende Erweiterung nicht bereit ist. In diesem Fall muss der Prozessor auf die Erweiterung warten, bis diese Bereitschaft signalisiert. Derartige Situationen sollten allerdings vom Compiler bzw. Programmierer vermieden werden, da die Erweiterungsblöcke die Programmabarbeitung beschleunigen sollen, anstatt sie zu behindern.

Für den nächsten Schritt ist entscheidend, ob die Erweiterungseinheit zur Prozessor-Pipeline synchron läuft oder nicht. Besteht Synchronität zum Prozessor, erübrigt sich jede weitere Kommunikation und der Prozessor erwartet nach einer Pipeline-Stufe die Zielregisteradresse, gefolgt vom Operationsergebnis nach der zweiten Stufe. Wenn aus irgendeinem Grund wie z. B. bei einem Rekonfigurationsbefehl kein Ergebnis produziert wird, muss sichergestellt werden, dass kein gültiger Registerinhalt fälschlicherweise überschrieben wird. Das ist Aufgabe der Erweiterung, welche am besten das Register null mit dem Wert null überschreibt. Aufgrund der Tatsache dass dieses Register beim verwendeten Prozessor per Definition den Wert null enthält [KH92, Seite 2-6], ist gewährleistet, dass nichts überschrieben wird. Der Wert null ist jedoch wichtig, da das Register in der Beispielimplementierung im Gegensatz zum Originalprozessor nicht fest auf null verdrahtet ist.

Ist die Erweiterungseinheit nicht mit der Prozessor-Pipeline synchronisiert wie in Abbildung 3.4, muss sie vor Fertigstellung einer Operation Schreibzugriff auf das Registerfile beantragen. Wenn keine Ressourcenkonflikte auftreten, wird dieser auch gewährt. Erfolgt keine Freigabe, so ist es die Aufgabe der Erweiterungseinheit weiter den Zugriff zu beantragen, sofern noch Bedarf besteht. Diese Prozedur wiederholt sich so lange, bis entweder der Schreibzugriff aus irgend einem Grund irrelevant geworden ist oder die Freigabe erteilt wird. Danach muss die Erweiterung im nächsten Taktzyklus die Adresse des Zielregisters und spätestens nach der zweiten steigenden Taktflanke das Operationsergebnis bereitstellen. Das heißt, die minimal mögliche Zeit für eine Operation ist um einen Taktzyklus länger als im synchronen Fall. Das ist auch der Hauptgrund für die Einführung und Unterstützung des synchronen Falls. Somit sind ab einer Verarbeitungszeit von zwei Taktzyklen beliebige Ausführungszeiten möglich. Zu beachten ist allerdings, dass bei Datenabhängigkeiten die Rückführung des Ergebnisses zurück zur Ausführungsstufe immer noch einen weiteren Taktzyklus in Anspruch nimmt. Deshalb ist die frühestmögliche Weiterverarbeitung des Resultats eines Spezialbefehls erst nach drei Taktzyklen, also zwei Befehlen dazwischen möglich. Bestehen noch kürzere Abhängigkeiten, werden von der Pipeline-Kontrolleinheit im synchronen Fall automatisch Leerbefehle eingefügt. Im nicht synchronen Fall ist das automatische Einfügen von Leerbefehlen nicht möglich, weshalb bei Datenabhängigkeiten gewartet werden muss, bis das Ergebnis vorhanden ist. Erfolgt ein verfrühter Lesezugriff auf das Ergebnisregister, wird auch keine Ausnahmebehandlung oder Ähnliches durchgeführt und die Aufgabe solche Fehler zu verhindern wird wieder der Programmerstellung übertragen.

Sofern im nicht synchronen Fall kein Schreibzugriff seitens der Erweiterung erforderlich ist, wird dieser auch nicht beantragt. Somit wird auch nichts in das Registerfile geschrieben. Der Prozessor wartet also nicht explizit bei Spezialbefehlen auf einen Schreibzugriff. Dadurch ergeben sich folgende zusätzliche Möglichkeiten:

#### • Operationen mit beliebig vielen Eingangsoperanden

Mächtige Spezialoperationen mit mehreren Eingangsoperanden können über eine Folge von Spezialbefehlen codiert werden, mit denen jeweils bis zu zwei Operanden übergeben werden.

#### • lokale Registerspeicherung in Erweiterungseinheiten

Sofern ein Spezialbefehl ein temporäres Zwischenergebnis oder mehrere Ergebnisse produziert, können diese in der Erweiterungseinheit zwischengespeichert werden, um den Overhead für das Speichern in das prozessorinterne Registerfile einzusparen bzw. die anderen Ergebnisse nicht zu verlieren. Über weitere Spezialbefehle können diese Ergebnisse im Anschluss weiter verarbeitet oder nacheinander ausgelesen werden.

#### • Verwendung von Erweiterungen als zusätzliche Prozessorports

Durch die Entkopplung der beiden Kommunikationsrichtungen der generischen Schnittstelle wird es den Erweiterungseinheiten ermöglicht, auch als E/A-Einheiten (Ein-/Ausgabe) mit integrierter Verarbeitung zu agieren. So kann die Einheit als Reaktion auf bestimmte Änderungen der E/A-Pins direkt in das Registerfile des Prozessors schreiben und zusätzlich einen Interrupt auslösen. Umgekehrt kann der Prozessor zu beliebigen Zeitpunkten Daten an die E/A-Einheit für die Weiterverarbeitung oder direkte Ausgabe senden.

#### 3.3.4 Lösen von Ressourcenkonflikten

Aufgrund der möglichen parallelen Befehlsabarbeitung durch die zusätzlichen Funktionseinheiten und deren unterschiedliche Ausführungszeiten kann es wie bereits erwähnt zu Zugriffskonflikten auf das Registerfile kommen. Das passiert, wenn zwei Operationsergebnisse zum gleichen Zeitpunkt fertig werden. In diesem Fall ist eindeutig geregelt, wie die Vergabe des Schreibzugriffs erfolgt.

Da davon ausgegangen wird, dass in den erweiternden Funktionseinheiten komplexere Befehle als im Prozessor selbst ausgeführt werden, haben immer die Hardwareerweiterungen Vorrang. Das bedeutet somit, dass die prozessorinterne Befehlsausführung immer unterbrochen wird, wenn sowohl die interne Ausführungseinheit als auch eine Erweiterungseinheit Ergebnisse schreiben wollen. Die weitere Selektion der Zugriffsvergabe ist ähnlich einfach und effizient gelöst. Alle Anschlüsse für Erweiterungskomponenten sind mit einer Nummer von null bis zur maximalen Anzahl an Erweiterungen minus eins versehen. Dabei hat die Erweiterung mit der Nummer null die höchste Priorität und die mit der größten Nummer die niedrigste. Somit bekommt bei gleichzeitigem Zugriffsantrag mehrerer Erweiterungen immer die mit der niedrigsten Nummer den Zugriff auf das Registerfile. Bei mehr als zwei gleichzeitigen Zugriffen ist das Prinzip dasselbe, nur dass im nächsten Taktzyklus der Schreibzugriff von den verbleibenden Einheiten erneut beantragt werden muss. Dieses Prinzip wird so lange ausgeführt, bis kein Ressourcenkonflikt mehr besteht und die prozessorinterne Ausführungseinheit wieder den Zugriff bekommt. Im schlimmsten Fall wird daher die Prozessorausführung für mehrere Taktzyklen unterbrochen. Um diesem negativen Effekt entgegenzuwirken gibt es zwei Möglichkeiten:

- Bei Sprung- oder Datentransferbefehlen zum Speicher benötigt der Prozessor keinen Schreibzugriff auf das Registerfile und muss somit nicht angehalten werden. Daher können bei Kenntnis der Ausführungszeiten der Erweiterungseinheiten und geschickter Anordnung der Maschinenbefehle solche Wartezyklen teilweise verhindert werden.

- Die Erweiterungen können so entworfen werden, dass diese synchron zur Prozessor-Pipeline arbeiten. Das ist jedoch Aufgrund der Komplexität der gewünschten Spezialbefehle nicht immer möglich.

Ein großer Vorteil der vorgestellten Zugriffsvergabe ist die Tatsache, dass der sofortige Schreibzugriff der Erweiterungseinheit mit der höchsten Priorität immer garantiert ist. Somit können an diese Erweiterungsschnittstelle mit höchster zugeordneter Zugriffspriorität Module angebunden werden, welche über eine eigene Pipeline verfügen. Es ist dabei ausgeschlossen, dass die Pipeline wegen Zugriffsproblemen angehalten werden muss und die Erweiterungseinheit ist daher immer in der Lage einen neuen Befehl pro Taktzyklus aufzunehmen (siehe CORDIC-Implementierung Kapitel 4.3). Deshalb muss sich die Erweiterung weder um das Anhalten der Pipeline kümmern, noch um das Steuersignal, welches anzeigt dass die Erweiterung bereit ist.

#### 3.3.5 Erweiterungsbefehle

Für die Befehlssatzerweiterung wird der Standardbefehlssatz des MIPS Prozessors um ein weiteres Befehlsformat ergänzt. Dieses Befehlsformat ist eine Kombination aus dem R-Format und den Coprozessoropcodes [KH92, Seite 3-14] des MIPS Prozessors die dadurch ersetzt werden. Weil davon ausgegangen wird, dass die Spezialhardwareerweiterungen die Funktionalität von Coprozessoren übernehmen können, stellt dies in der Regel kein Problem bezüglich der Funktionalität dar. Somit wirkt sich das Weiterverwenden der Coprozessoropcodes positiv auf die Anzahl möglicher Erweiterungen aus. Prinzipiell wäre jedoch auch eine Koexistenz der beiden Erweiterungstypen möglich, dazu müssten nur die entsprechenden Steuerleitungen des konkurrierenden Erweiterungsanschlusses entsprechend gesetzt werden um für den Prozessor transparent zu sein. Da jedoch der implementierte Prototyp aus Kapitel 4.2 eine Unterstützung für Coprozessoren nicht vorsieht, wird auf dieses Thema nicht näher eingegangen.

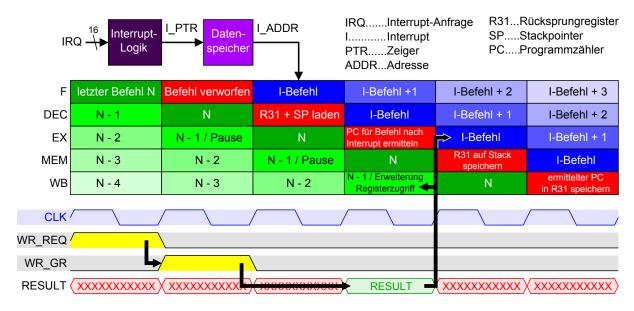

31-26 25-21 20-16 15-11 10-6 5-0 Opcode Coprozessor-Format RtRd Function Rs (0100XX)befehl Erweiterungs-Opcode Rd RsRt Special (010XXX) befehl

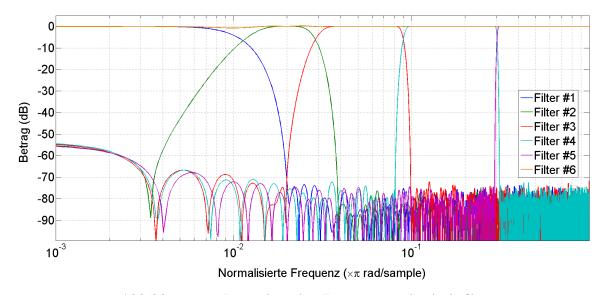

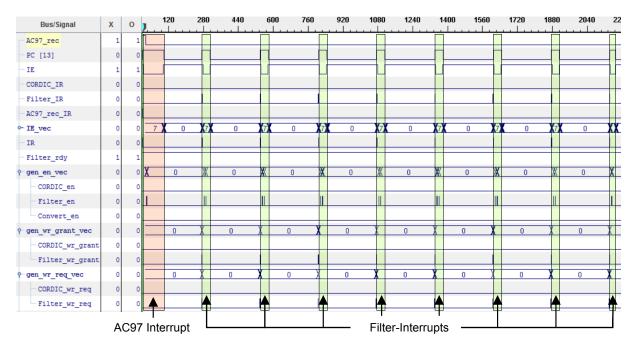

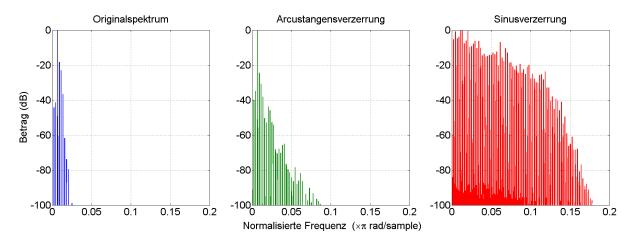

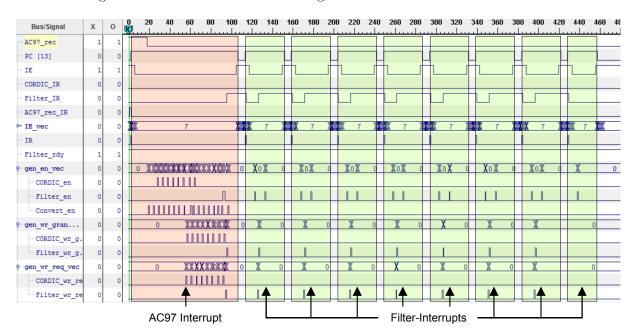

Tabelle 3.2: Befehlsformate für zusätzliche Befehle