Die approbierte Originalversion dieser Diplom-/ Masterarbeit ist in der Hauptbibliothek der Technischen Universität Wien aufgestellt und zugänglich.

TU UB

http://www.ub.tuwien.ac.a

TU UB

The approved original version of this diploma or master thesis is available at the main library of the Vienna University of Technology. DIPLOMARBEIT

# Silicon-Carbide-Based Closed-Loop Class-D Power Amplifier

ausgeführt zum Zweck der Erlangung des akademischen Grades eines Diplom-Ingenieurs

unter der Leitung von

Ao. Univ. Prof. Dipl.-Ing. Dr. techn. Johann Ertl

E370

Institut für Energiesysteme und Elektrische Antriebe

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik

von

Norbert Mehofer, BSc 0725424 Aspersdorferstraße 8/19 2020 Hollabrunn

Wien, im Dezember 2014

# Abstract

In many laboratories and electric testing centres there is a need for stable and predictive power sources providing power signals of arbitrary shape. This work presents the process of developing and realising a linear power amplifier – based on a class-D amplifier topology – applying the upcoming silicon carbide semiconductor technology. This technology is of special interest for the realisation of power sources due to its structural advantage of providing lower power losses. The developed system supports amplification of any signal sequence – coming from an arbitrary waveform generator – up to 1kHz with a maximum output voltage range of  $\pm 400$ V and a maximum current of  $\pm 10$ A – resulting in up to 4kW output power – at an overall physical size of approximately 2.5 litres.

The requirement for a high efficient amplifier unit demands a switching (Class-D) topology with a loss-less output filter consisting of power inductors and capacitors.

The state of the art silicon-based semiconductor technology is compared to the upcoming siliconcarbide (SiC) technology and the most important differences – that lead to the usage of the latter in the presented amplifier – are pointed out.

The chosen output filter configuration originally represents an only marginally stable system. This characteristic therefore necessitates the introduction of a feedback control structure in order to create a required overall transfer function of proper dynamic behaviour. The design requirements are fast rise and settling times, no remarkable overshoot in case of a step response, low voltage drop in case of a load step, high attenuation of the structural switching harmonics and limited current peaks in case of a square wave to avoid damaging on the semiconductor switches. Therefore, different controller concepts are developed and analysed theoretically. Based on the results, possible configurations are designed and verified by the use of common circuit simulation software. The most promising configuration – a system with a Bessel-like step response – is selected for realisation.

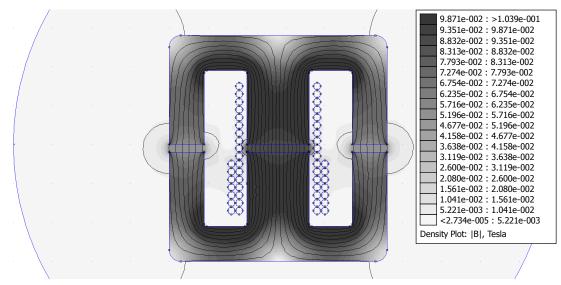

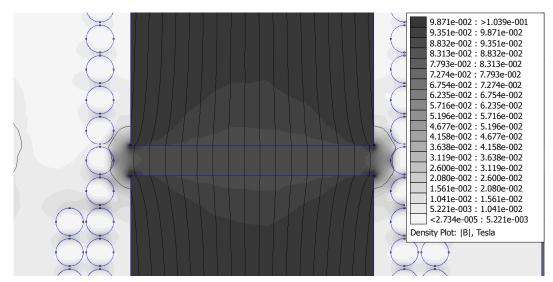

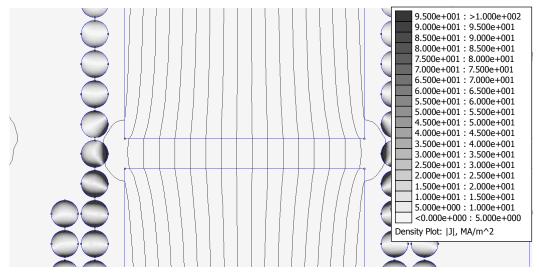

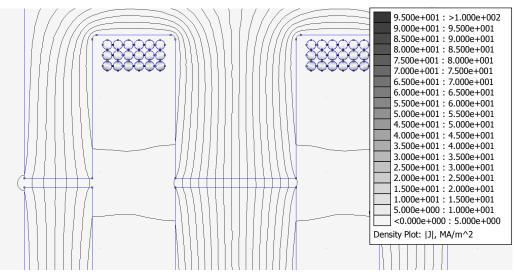

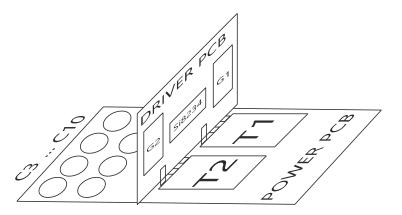

The realisation of the amplifier unit is described in detail. In particular, a specific unique design of the  $100\mu$ H main filter power inductor is shown, which is optimized to have low core and copper losses even in case of 100kHz 10A peak ripple current. FE-simulations gained by the simulation program FEMM support the design process. A novel gate driver – based on an RF transceiver and receiver isolation concept instead of using optocouplers – is developed in order to benefit from low conduction losses and fast switching times of the SiC-MOSFETs. A PCB-layout which minimizes the parasitic inductances in the connection paths between the DC link capacitors, the semiconductor switches and the gate drivers, guarantees a nearly ideal rectangular-shaped output voltage of the MOSFET half-bridge leg supporting very fast switching speed.

The overall circuit is tested on a broad range of the defined requirements and use cases. The results of the real system corresponds well to the theoretic/simulated ones, proved by oscilloscope measurements which are included in this work. Appearing problems in the test procedures are mentioned and possible improvements are discussed. Especially a full bridge converter topology, consisting of two identic half-bridge amplifier stages, is suggested. This structure would eliminate nearly all disadvantages observed in the test procedures. In addition, it will provide benefits such as an output voltage range being twice as high as the supply voltage range.

The presented amplifier demonstrates a well-working power source and forms a development basis for further researches on this topic, e.g. covering the full bridge converter consideration.

# Kurzfassung

Elektrische Laboratorien und Prüfanstalten benötigen vielfach Spannungsquellen für höhere Leistungen um Spannungen im Bereich der Netzspannung mit verschiedensten Signalverläufen bereitstellen zu können. In dieser Diplomarbeit wird der gesamte Entwicklungsprozess einer derartigen Leistungsquelle (Leistungsverstärker) beginnend beim grundsätzlichen Design bis hin zum Aufbau und den verschiedensten Testläufen dargestellt. Die Grundstruktur des Verstärkers basiert auf der des bekannten Klasse-D-Prinzips (Schaltverstärker) mit Reaktanz-Ausgangsfilter zur Unterdrückung der schaltfrequenten Signalkomponenten. Es können Eingangssignale bis zu einer Frequenz von 1kHz auf Ausgangsspannungen von  $\pm 400$ V und einem Ausgangsstrom von  $\pm 10$ A verstärkt werden, wobei das Gesamtsystem ein Volumen von ca. 2,5dm aufweist.

In der Arbeit wird eingangs die momentan in der Industrie etablierte Silizium Technologie für Halbleiterschalter der neuen, immer mehr konkurrenzfähiger werdenden Siliziumkarbid-Technologie (SiC) gegenübergestellt und die wichtigsten Unterschiede – die im konkreten Fall zum Einsatz von SiC-MOSFETs führen – aufbereitet dargestellt.

Das notwendige Ausgangsfilter besteht ausschließlich aus Induktivitäten und Kapazitäten und stellt ein somit grenzstabiles ungedämpftes System dar. Da die Dämpfung des Filters nicht über die Last erfolgt, ist es notwendig eine Regelung zu implementieren, die das Gesamtsystem stabilisiert und das gewünschte dynamische Verhalten (Transfer-Charakteristik) garantiert. Die Regelung wird optimiert auf schnelle Anstiegs- und Einschwingzeiten, auf minimales Überschwingen, geringen Spannungsabfall bei einem Lastsprung, einer hohen Unterdrückung der prinzipbedingten schaltfrequenten Harmonischen sowie der Begrenzung von Stromspitzen bei hohen Rechtecks-Ausgangspannungen zur Vermeidung von Überströmen in den Halbleiterschaltern. Es werden verschiedene Regelungskonzepte erarbeitet und auf ihre Praxistauglichkeit untersucht, zuerst theoretisch, anschließend unter Zuhilfenahme von gebräuchlichen Schaltungs-Simulatoren. Das aus diesen Untersuchungen hervorgehende optimale Konzept – mit Bessel-ähnlicher Sprungantwort – wird für die Realisierung verwendet.

Alle notwendigen Schaltungsteile des Aufbaus sind im Detail beschrieben, insbesondere auch die Dimensionierung einer speziellen 100µH-Glättungsinduktivität für die erste Filterstufe. Diese wurde mit Hilfe der Simulationssoftware FEMM hinsichtlich möglichst geringer Verluste in Bezug auf die auftretenden Spannungs- und Stromverläufe (100kHz/10A) optimiert. Weiters wurde eine neue Gate-Treiberstufe entwickelt, welche die SiC-MOSFETs unter Verwendung eines IC-Bausteins mit HF-Signalen potentialfrei ansteuert, anstatt der üblicherweise dafür verwendeten Optokoppler. Besonderes Augenmerk wurde auf eine möglichst niederinduktive Kontaktierung der Zwischenkreiskondensatoren mit den Halbleiterschaltern gelegt, um Schaltüberspannungen am Ausgang des Halbbrückenzweiges zu vermeiden.

Der entwickelte Verstärker wurde umfangreichen Tests unterzogen. Die praktischen Messungen stimmen sehr gut mit den simulierten Ergebnissen überein. Die Arbeit beinhaltet die Messresultate (Oszilloskop-Messungen), ebenso erfolgt eine Diskussion der bei der Realisierung aufgetretenen Problembereiche. Zur Vermeidung dieser wird eine Verstärkerstruktur vorgeschlagen, die aus zwei Halbbrücken-Stufen besteht. Damit ließen sich praktisch alle wesentlichen Nachteile der realisierten Schaltung beheben.

Der realisierte Leistungsverstärker stellt eine gutfunktionierende Spannungsquelle dar und bietet eine vielversprechende Grundlage für weitere Forschungen und Entwicklungen auf diesem Gebiet.

# Acknowledgement

My sincere thanks are given to Univ.Prof. Dr. Johann Ertl for giving me the opportunity to deal with this interesting and inspiring subject and for his advice and assistance in case of difficulties. I would like to express my gratitude to Helmut Votzi MSc. and Dipl.-Ing. Markus Makoschitz for their support in the laboratory.

Furthermore, I want to thank Thomas Mehofer MSc. and Dipl.-Ing. Franz Mehofer for discussions on the topic and above all for proofreading the manuscript.

Many thanks go to my parents Friederike and Franz Mehofer. They were always supporting me and encouraging me with their best wishes.

# Content

| 1 | Intro | ntroduction                                 |                                            |    |  |  |  |

|---|-------|---------------------------------------------|--------------------------------------------|----|--|--|--|

|   | 1.1   | Targe                                       | ts and Requirements                        | 1  |  |  |  |

|   | 1.2   | Guide                                       | Guideline through the Work                 |    |  |  |  |

| 2 | Fun   | indamentals and Current State of Technology |                                            |    |  |  |  |

|   | 2.1   | Ampli                                       | ifier Topology – Modulation Concept        | 3  |  |  |  |

|   | 2.2   | Analy                                       | sis of Different Low-Pass Filters          | 4  |  |  |  |

|   |       | 2.2.1                                       | Ideal Low-Pass Filter                      | 4  |  |  |  |

|   |       | 2.2.2                                       | Butterworth Filter                         | 5  |  |  |  |

|   |       | 2.2.3                                       | Bessel Filter                              | 6  |  |  |  |

|   |       | 2.2.4                                       | Filter Comparison, Assessment and Decision | 6  |  |  |  |

|   |       | 2.2.5                                       | LC Low-Pass Filter Basics                  | 7  |  |  |  |

|   | 2.3   | Switcl                                      | hes                                        | 10 |  |  |  |

|   |       | 2.3.1                                       | Switch Related Requirements                | 10 |  |  |  |

|   |       | 2.3.2                                       | State of the Art Si Switches               | 11 |  |  |  |

|   |       | 2.3.3                                       | SiC MOSFET Technology                      | 12 |  |  |  |

|   |       | 2.3.4                                       | Calculation of the Drift-Resistance        | 13 |  |  |  |

|   |       | 2.3.5                                       | SiC Diodes                                 | 15 |  |  |  |

|   |       | 2.3.6                                       | Comparison of MOSFET Alternatives          | 15 |  |  |  |

|   |       | 2.3.7                                       | Perspectives of SiC MOSFETs                | 17 |  |  |  |

|   | 2.4   | Assess                                      | sed Circuit Topology                       | 18 |  |  |  |

| 3 | Con   | cepts fo                                    | or Feedback Control Unit                   | 19 |  |  |  |

|   | 3.1   | Syster                                      | n Model                                    | 19 |  |  |  |

|   | 3.2   | Basic                                       | Control Considerations                     | 20 |  |  |  |

|   | 3.3   | Feedb                                       | ack Control Approaches                     | 23 |  |  |  |

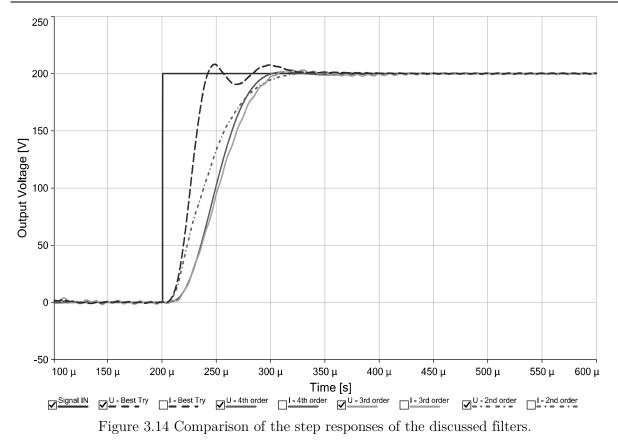

|   |       | 3.3.1                                       | Fourth-Order Bessel Filter                 | 23 |  |  |  |

|   |       | 3.3.2                                       | Approximated Third-Order Bessel Filter     | 26 |  |  |  |

|   |       | 3.3.3                                       | Approximated Second-Order Bessel Filter    | 29 |  |  |  |

|   |       | 3.3.4                                       | Free Designed Filter – Best Try            | 31 |  |  |  |

|   | 3.4   | Circui                                      | t Simulation – Comparison                  | 33 |  |  |  |

|   |       | 3.4.1                                       | Step Response                              | 33 |  |  |  |

|   |      | 3.4.2               | Load Response                            | 36 |  |  |  |  |

|---|------|---------------------|------------------------------------------|----|--|--|--|--|

|   |      | 3.4.3               | Rectangular Response                     | 37 |  |  |  |  |

|   | 3.5  | Contro              | oller Assessment and Decision            | 38 |  |  |  |  |

| 4 | Impl | ementa              | tion of Filter Unit                      | 39 |  |  |  |  |

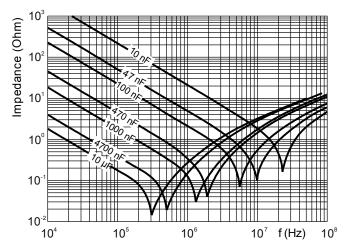

|   | 4.1  | 1 Capacitors        |                                          |    |  |  |  |  |

|   | 4.2  | Induct              | ors                                      | 39 |  |  |  |  |

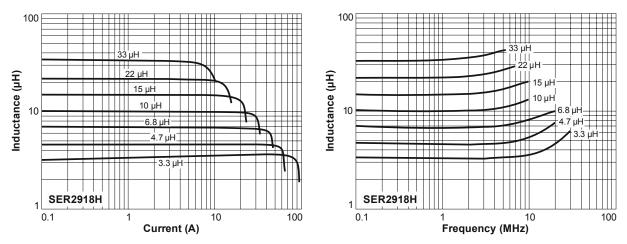

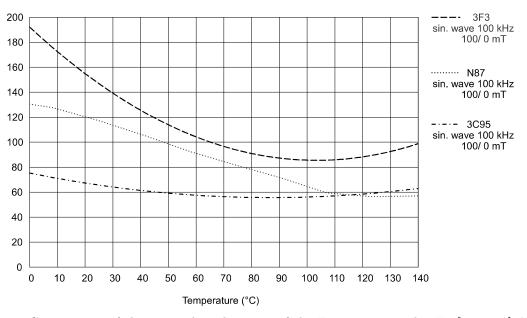

|   |      | 4.2.1               | Prefabricated Power Inductors            | 40 |  |  |  |  |

|   |      | 4.2.2               | Inductor Self-Design                     | 40 |  |  |  |  |

| 5 | Circ | Circuit Realisation |                                          |    |  |  |  |  |

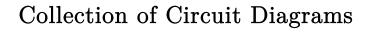

|   | 5.1  | 1 Half-Bridge       |                                          |    |  |  |  |  |

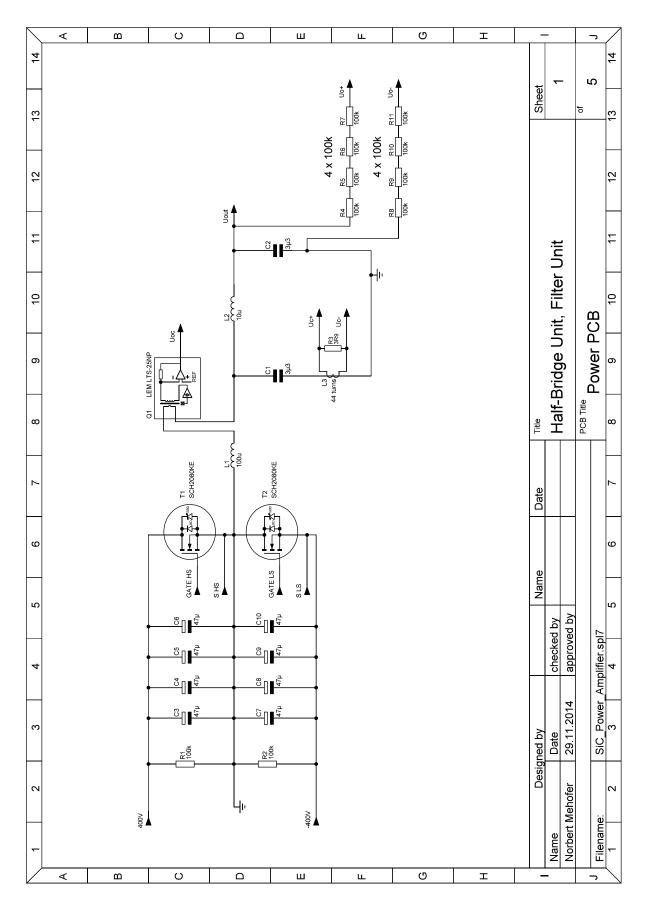

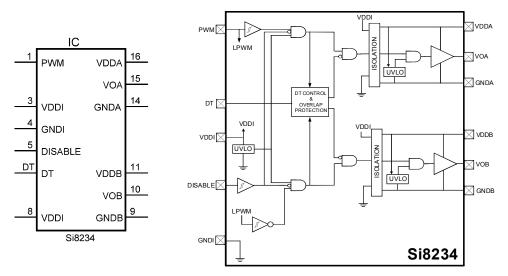

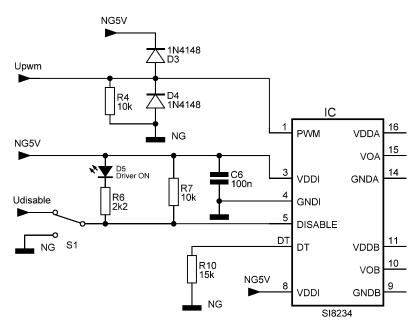

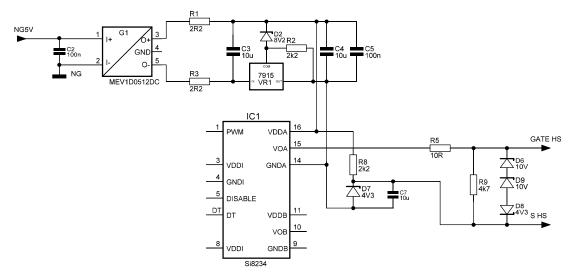

|   | 5.2  | MOSF                | ET Driver                                | 45 |  |  |  |  |

|   | 5.3  | Test F              | Procedures – Half-Bridge Unit            | 48 |  |  |  |  |

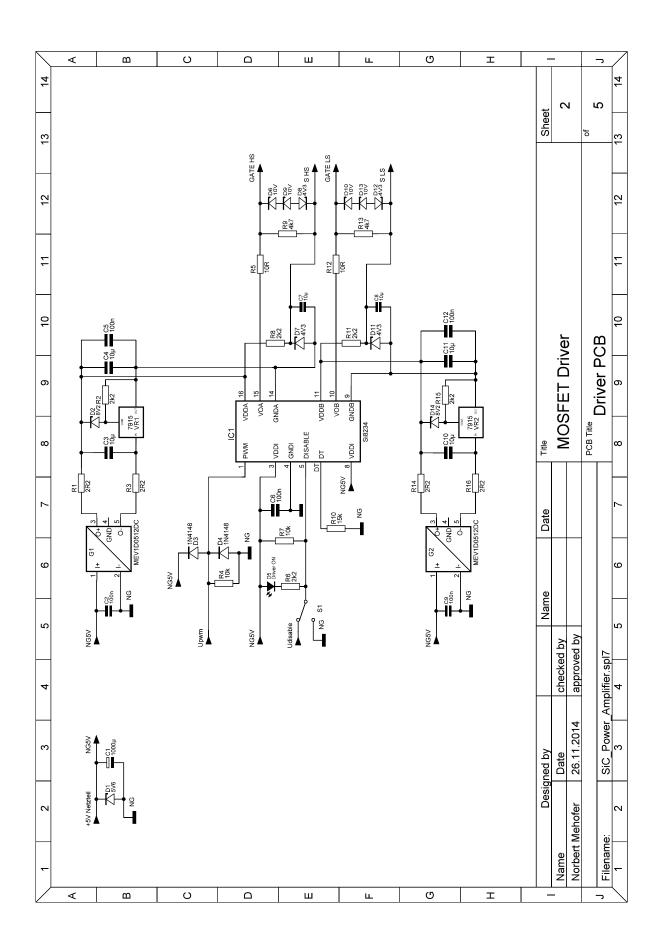

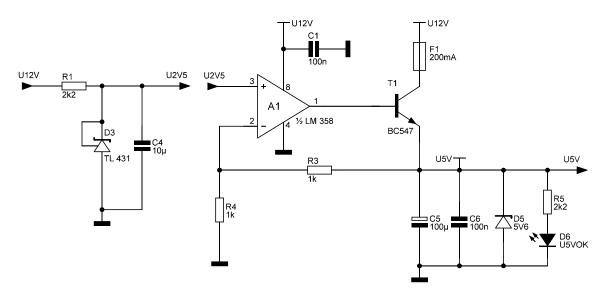

|   | 5.4  | Auxili              | ary Voltage Supply                       | 50 |  |  |  |  |

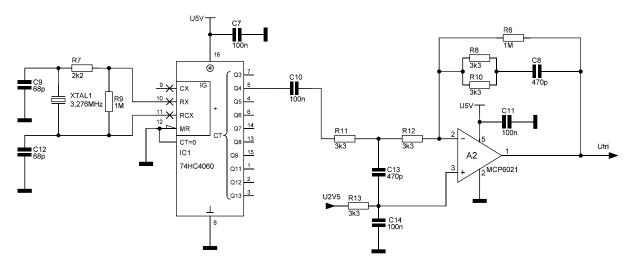

|   | 5.5  | Triang              | gular Wave Generator                     | 51 |  |  |  |  |

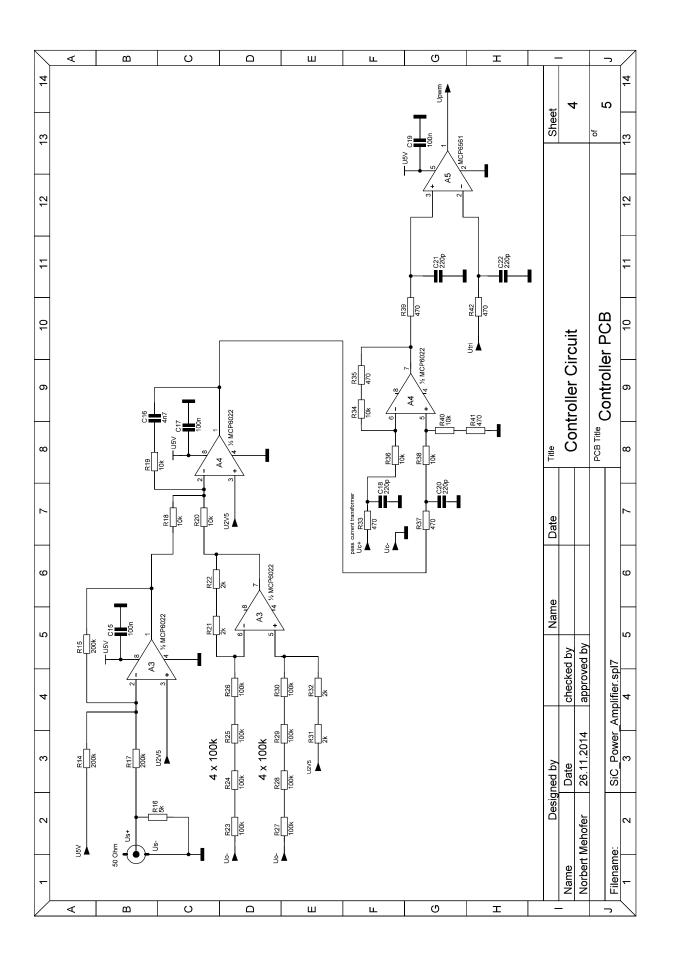

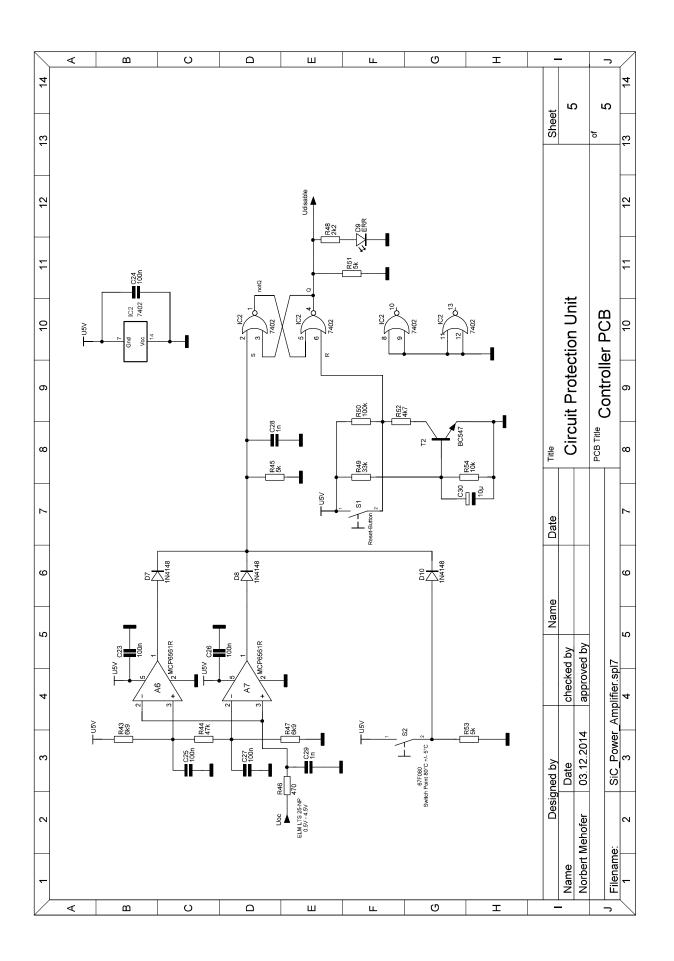

|   | 5.6  | Contro              | oller Circuit                            | 52 |  |  |  |  |

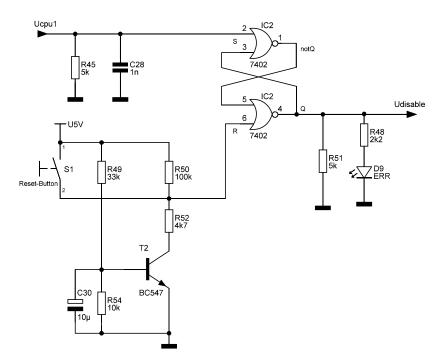

|   | 5.7  | Circui              | t Protection Unit                        | 54 |  |  |  |  |

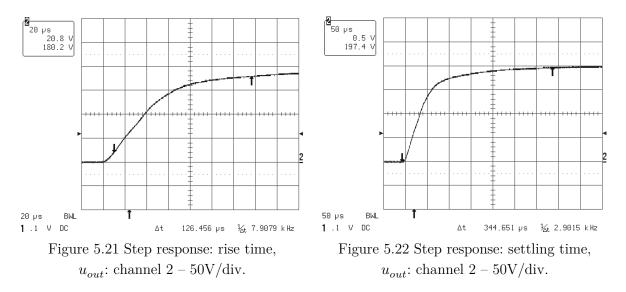

|   | 5.8  | Test F              | Procedures – Overall Implemented Circuit | 56 |  |  |  |  |

| 6 | Outl | ook and             | d Perspectives                           | 63 |  |  |  |  |

| 7 | Cond | lusion              |                                          | 68 |  |  |  |  |

# 1 Introduction

The objective of this master thesis is to develop a single-phase high efficiency class-D power amplifier. A half-bridge amplifier followed by a lossless filter form the basic topology. The upcoming silicon-carbide (SiC) technology is compared to the state-of-the-art silicon (Si) technology and if advantageous utilized instead of Si.

### 1.1 Targets and Requirements

The main application of the power amplifier is to provide a 230V 50Hz sine wave without remarkable harmonics for test procedures and laboratory needs.<sup>1</sup> It should form an alternative for the domestic power grid. So, no remarkable voltage drop at load steps is allowed.

Furthermore, it should work over a wide voltage and frequency range for each signal type, e.g. triangle, sine, rectangle, etc. Therefore, different requirements are defined, as summarized in Table 1.1. These values only describe the minimum requirements. The target is a device that achieves the best as technologically possible.

| Description                                                                 | Requirements                |

|-----------------------------------------------------------------------------|-----------------------------|

| Output voltage range                                                        | 95% of $U_{SV}{}^2$         |

| Maximum continuous output current                                           | $\pm 10 A$                  |

| Frequency range<br>(ideal amplification of sine wave)                       | 0 1kHz                      |

| Attenuation of switching harmonics <sup>3</sup>                             | min. 50dB                   |

| Maximum overshoot at full voltage step                                      | $<5\%$ of $U_\infty$        |

| Maximum voltage drop at full load step <sup>4</sup> at peak nominal voltage | $< 10\%$ of $\hat{U}_{nom}$ |

Table 1.1 Requirements for the power amplifier.

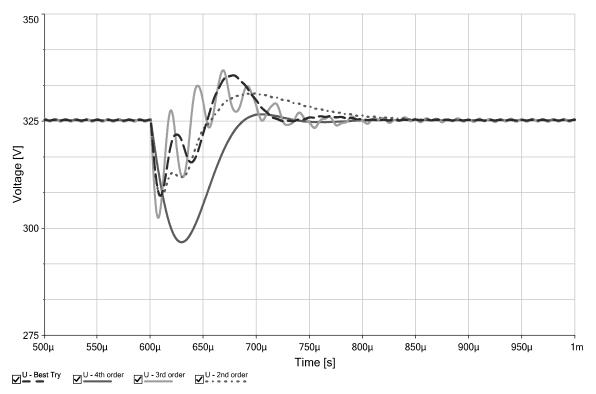

The last entry in the table above describes the test criterion for avoiding voltage drops at load steps. At peak nominal voltage  $\hat{U}_{nom}$ , a dynamic voltage drop of max.  $32,5V^5$  is allowed to comply with the requirements.

At the input side, two DC power supplies with a voltage up to 400V form the power supply for the device. The input signal that has to be amplified comes from an external waveform generator.

<sup>5</sup> 10% of  $\hat{U}_{nom} = 0.1 \cdot \hat{U}_{nom} = 0.1 \cdot \sqrt{2} \cdot 230 \text{V} = 0.1 \cdot 325.27 \text{V} \approx 32.5 \text{V}.$

$<sup>^{\</sup>scriptscriptstyle 1}$  This case is further described under nominal voltage  $U_{nom}.$

$<sup>^{2}</sup>$  The DC power supply voltage is called  $U_{SV}.$

$<sup>^3</sup>$  To meet the requirement "without remarkable harmonics" an attenuation of the switching harmonic of min. 50dB is defined.

<sup>&</sup>lt;sup>4</sup> A full load step is defined as a step from 0A to 10A.

Signals up to 1kHz with a maximum voltage amplitude of 2V are allowed. For auxiliary circuits a single power supply of +5V is utilized, to reduce external efforts. All input related parameters are noted in Table 1.2.

| Description                                    | Values      |

|------------------------------------------------|-------------|

| Supply voltage $U_{SV}$                        | $\pm 400 V$ |

| Input voltage range $\boldsymbol{u}_{in}$      | -2V +2V     |

| Input frequency range $f_{in}$                 | 0 1kHz      |

| Supply voltage for auxiliary circuits $U_{AV}$ | +5V         |

Table 1.2 Defined input parameters.

### 1.2 Guideline through the Work

After declaring the targets and requirements in section 1.1, chapter 2 first describes the theoretical basics of the used amplifier topology and following each part of the amplifier is analysed with regard to the requirements. Problems and tasks for realising a proper filter are brought out clearly. Differences between the Si and SiC technologies are pointed out and the most important facts are explained in detail. In addition, a short outlook in current semiconductor research activities is given.

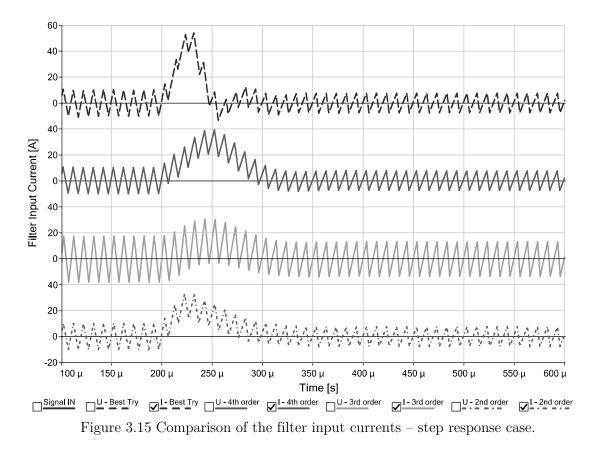

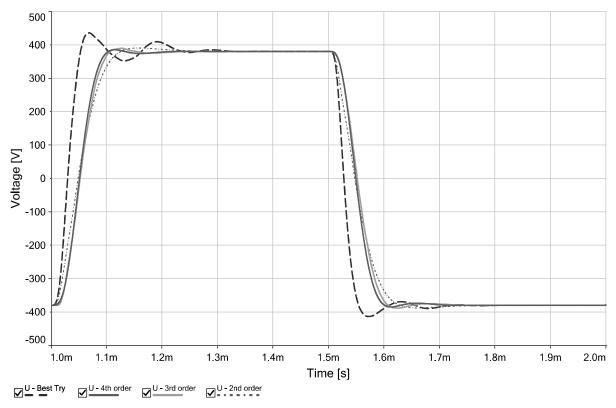

Chapter 3 provides four different design approaches for a feedback control that create the required transfer characteristic. Based on a theoretical analysis, the configuration with the most promising characteristics of each approach is simulated in a circuit simulator software. The most important parameters – step response rise and settling time, voltage drop, attenuation of the switching harmonic, peak value of the filter input current – are extracted and compared. The configuration with the best overall results is choosen for realisation.

Chapter 4 and chapter 5 describe the implementation of the overall system. Chapter 4 provides an overview of the filter related parts, especially the procedure for self-designing a power inductor is given more in detail. Chapter 5 shows all relevant circuit and sub-circuits and mentions the circuit design considerations. The overall circuit is tested extensively and the results are compared to the theoretic/simulated ones.

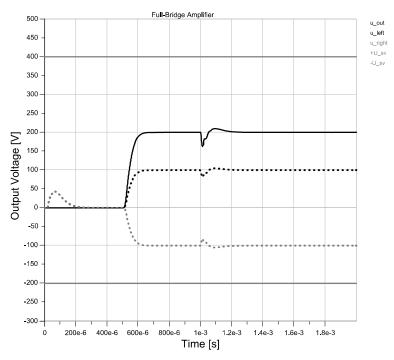

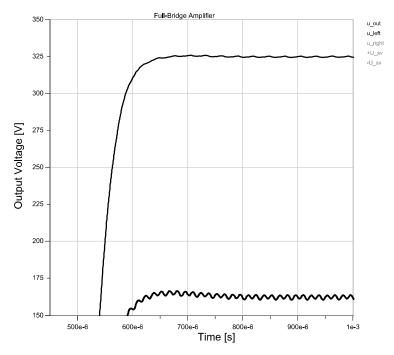

Chapter 6 picks up the appeared disadvantages and gives opportunities to improve the overall system. An extended circuit topology – based on the realised one – that eliminates most disadvantages is suggested and simulation results are presented to prove the assumptions.

# 2 Fundamentals and Current State of Technology

# 2.1 Amplifier Topology – Modulation Concept

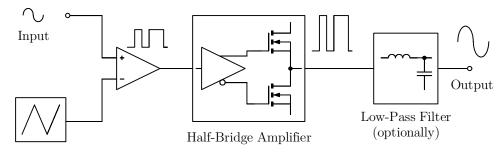

The amplifier topology is similar to a standard Class-D amplifier. An input signal is compared with a triangular signal generated by an on-board triangular wave generator. The comparator creates a rectangular signal with variable pulse width. Therefore, this concept is called Pulse-Width-Modulation (PWM).

Two switches in half-bridge topology amplify the resulting signal. At the end a low-pass filter is placed to attenuate the switching frequency harmonics. In cost sensitive devices, this filter may be omitted. See Figure 2.1.

Triangular Wave Generator

Figure 2.1 Block diagram of a Class-D Amplifier, based on [1, p. 2204].

This concept is proven, well established, and for instance today often used in the audio industry. There the PWM signal either is directly (without low-pass filter) or with a cheap low-pass filter connected to the loudspeaker. The first variant is possible because the loudspeaker dynamics and the human ear act as the required low-pass filter.

In case of this work, however, the output filter is essential to maintain an amplified output signal without substantial harmonics. Therefore, attention is turned especially to the filter design.

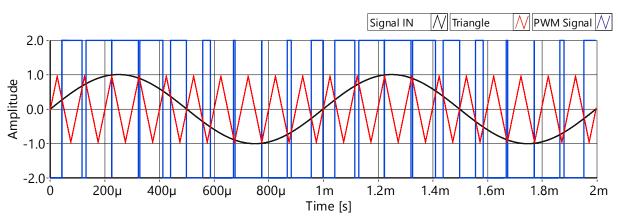

For better understanding of the modulation concept, Figure 2.2 shows a sine wave that is compared with a triangular signal and the generated amplified (by the factor of 2) PWM signal.

Figure 2.2 Illustration of the function principle of a Class-D amplifier.

The most attractive advantage is its high efficiency, e. g.  $\eta = 93\%$  of a 200W amplifier [2]. That means cost savings caused by reduced energy consumption and smaller heat sinks. This also leads to smaller amplifier devices, especially important in portable devices such as music players.

# 2.2 Analysis of Different Low-Pass Filters

As mentioned above, special effort has to be spent on the filter unit after the half-bridge amplifier to prevent high frequency switching harmonics on the output signal. In this section, different filters are analysed to match the defined requirements. First the frequency responses and the step responses are analysed and after this the realisation of the best match is described.<sup>1</sup>

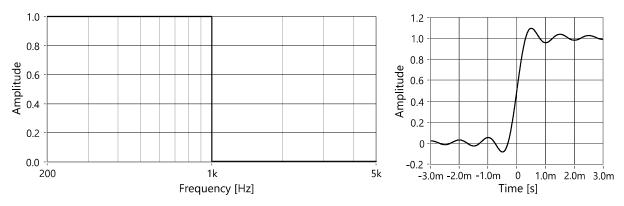

#### 2.2.1 Ideal Low-Pass Filter

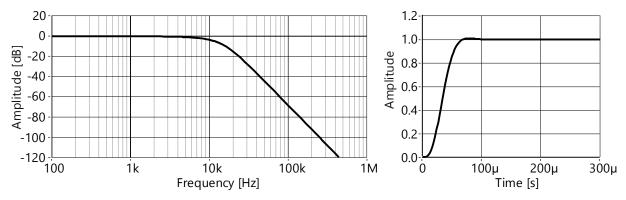

The frequency response of an ideal low-pass filter is characterized by a sharp edge at the cutoff frequency. So, the filter ideally rejects all higher frequency parts. It represents, however, a non-causal system – input signals of the future influence the present output signal. The step response is characterized by raising oscillations before the step is introduced – it is a non-causal system – an amplitude of 0.5 at the step and a decaying oscillation after the step, see Figure 2.3.

Figure 2.3 Ideal low-pass filter (cutoff frequency 1kHz) and its step response.

At a cutoff frequency of 100kHz the step response is equal, only the time range is divided by 100.

Figure 2.4 Ideal low-pass filter (cutoff frequency 100kHz) and its step response.

This filter cannot be realised due to its non-causal character. It gives, however, an overview about the dynamic of low-pass filters with cutoff frequencies between 1 and 100kHz. In the 100kHz case the step response shows a rise time of approximately  $8\mu$ s. For possible cutoff frequencies in the range of 10kHz therefore rise times of 80-100µs can be expected.

<sup>&</sup>lt;sup>1</sup> All filters are simulated with National Instruments's LabView 2013.

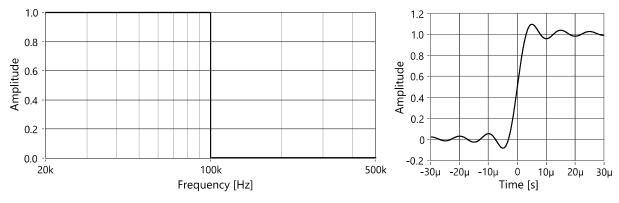

#### 2.2.2 Butterworth Filter

This filter is designed to have a frequency response as flat as possible in the passband, which is beneficial for a good amplitude response up to 1kHz. At the cutoff frequency<sup>1</sup>, the frequency response rolls off at multiples of -20dB/decade, depending on the order, e. g. -40dB/decade for a second order filter, see Figure 2.5.

Figure 2.5 Butterworth filter (2<sup>nd</sup> order, cutoff frequency 10kHz) and its step response.

The step response is much better than for the ideal low pass filter. Less overshoot of 1.05 of the desired amplitude is achieved. On the other hand, the attenuation of higher harmonics is not satisfying. A high switching frequency would be necessary. For instance, a 100kHz switching frequency will be attenuated only by  $\frac{1}{100}$ . At  $\pm 400$ V supply voltage, this means a sine wave with an amplitude of approximately 5V on the output signal. That is not acceptable as defined in the requirements. A solution could be an increase of the filter order. Figure 2.6 shows a 4<sup>th</sup> order Butterworth filter.

Figure 2.6 Butterworth filter (4<sup>th</sup> order, cutoff frequency 10kHz) and its step response.

Here the attenuation is -80dB/decade. Compared to the former example, now the amplitude of the 100kHz sine wave is only 50mV, which is excellent. In the step response, however, the overshoot increases at above 1.1 of the desired amplitude and the settling time nearly doubles to  $200\mu$ s.

<sup>&</sup>lt;sup>1</sup> Cutoff frequency is defined as the frequency for which the attenuation of the circuit is 3 dB.

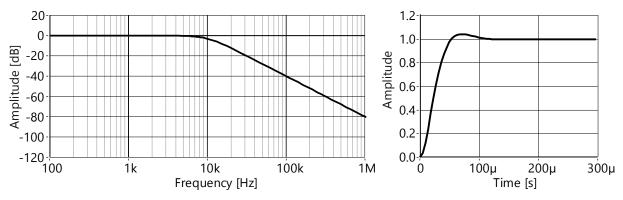

#### 2.2.3 Bessel Filter

A Bessel filter is an analogue linear filter with a maximally flat group/phase delay, which preserves the wave shape of filtered signals in the passband. It has nearly no overshoot which makes it interesting for this purposes. The frequency response is not as flat in the passband and the attenuation not as sharp in the stoppband as in the Butterworth filter. This means less than -20dB/decade per order. Figure 2.7 shows a 4<sup>th</sup> order Bessel filter of with a cutoff frequency of 10kHz.

Figure 2.7 Bessel filter (4<sup>th</sup> order, cutoff frequency 10kHz) and its step response.

At a switching frequency of 100kHz the attenuation is more than 60dB so that the requirement is met. That represents a 100kHz sine wave with an amplitude of 0.5V corresponding to the former example. The step response looks extremely good, with no remarkable overshoot in this resolution. The attenuation in the passband is also nearly zero for frequencies up to 1kHz.

#### 2.2.4 Filter Comparison, Assessment and Decision

The analysed filters with their characteristics are compared for allowing final decision.

| Parameters                               | Ideal Low-Pass<br>100kHz | ${ m Butterworth}\ 2^{ m nd} \ { m order}$ | $egin{array}{c} { m Butterworth} \ 4^{ m th} \ { m oder} \end{array}$ | Bessel<br>4 <sup>th</sup> order |

|------------------------------------------|--------------------------|--------------------------------------------|-----------------------------------------------------------------------|---------------------------------|

| Attenuation at 100kHz                    | ++                       | _                                          | +                                                                     | +                               |

| Voltage Step<br>Overshoot                | _                        | 0                                          | _                                                                     | +                               |

| Voltage Step<br>Curve Shape <sup>1</sup> |                          | 0                                          | _                                                                     | ++                              |

Table 2.1 Comparison of the analysed filter types

(++ excellent, + good, o fair, - weak, -- poor)

The Bessel filter complies with all requirements specified for the filter unit and therefore it is selected for the further activities.

<sup>&</sup>lt;sup>1</sup> The parameter "curve shape" describes a behaviour such as oscillations (damping factor, duration...) and the dynamic of the step response (rise time, settling time, ...).

#### 2.2.5 LC Low-Pass Filter Basics

For the realisation of the required filter some aspects have to be taken into account. First, it has to be a passive filter without operational amplifier, and second, resistors are prohibited to avoid remarkable losses.

Figure 2.8 shows a possible topology of such a filter, consisting of an inductor and a capacitor. Each of them represents an energy storage, so this basic element forms a second order filter.

Figure 2.8 Basic element of a 2<sup>nd</sup> order LC low-pass filter, based on [3, p. 2].

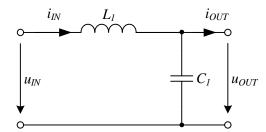

Equation (2.1) shows the circuit's transfer function. It looks similar to the well-known damped oscillation function, but the damping factor, here  $\xi$  is zero. Therefore, this structure represents an undamped oscillation with a defined resonance frequency  $\omega_0$ .

$$G(s) = \frac{U_{OUT}(s)}{U_{IN}(s)} = \frac{1}{1 + s^2 L_1 C_1} = \frac{1}{1 + 2\xi \frac{s}{\omega_0} + \frac{s^2}{\omega_0^2}} \quad \rightarrow \quad \xi = 0, \omega_0 = \frac{1}{\sqrt{L_1 C_1}} \quad (2.1)$$

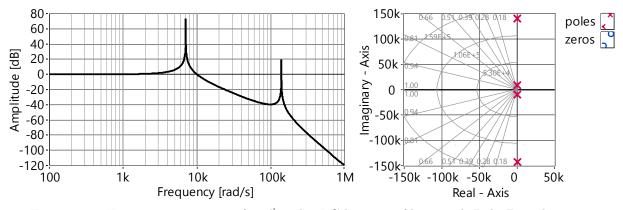

Figure 2.9 illustrates the frequency response for a filter with  $L_1 = 10$ mH,  $C_1 = 1\mu$ F. The resonance point is found at an angular frequency of 10krad/s. The poles of that marginally stable system are showed in the Pole-Zero diagram aside.

Figure 2.9 Frequency response of a 2<sup>nd</sup> order LC low-pass filter, with Pole-Zero diagram.

By changing the inductance or the capacitance, it is only possible to change the resonance frequency but not the curve shape. For stabilization reasons, however, it is necessary to change the transfer function. A possibility is to introduce damping resistors, but, as explained, this would lead to losses and because of that to a generation of undesired heat.

An important characteristic of the filter also is the input current  $i_{IN}^{1}$  in the step response case and the voltage drop of the output voltage in case of a load step.

<sup>&</sup>lt;sup>1</sup> The input current  $i_{IN}$  is that current which has to be delivered by the half-bridge amplifier.

Equation (2.2) shows the transfer function of the input current and equation (2.3) the related step response in time domain.

$$G(s) = \frac{I_{IN}(s)}{U_{IN}(s)} = \frac{1}{\sqrt{\frac{L_1}{C_1}}} \cdot \frac{s \cdot \frac{1}{\sqrt{L_1 C_1}}}{s^2 + \frac{1}{L_1 C_1}}$$

(2.2)

$$i_{IN}(\tau) = \frac{1}{\sqrt{\frac{L_1}{C_1}}} \cdot \sin\left(\frac{\tau}{\sqrt{L_1C_1}}\right) \quad \text{for } U_{IN}(s) = \frac{1}{s}V$$

(2.3)

The important parameter here is the characteristic impedance<sup>1</sup>  $\sqrt{\frac{L_1}{C_1}}$ , which determines the maximum current. If it is small, a high current will appear which might damage the semiconductor switches.

On the other hand, the voltage drop of the output voltage in case of a load step is analysed. The initial condition for this case is a charged capacitor at the value of the input voltage, so that the input current is equal to zero. Then a load step is introduced. Equation (2.4) shows the response in time domain.

$$u_c(\tau) - u_{IN} = -Z_1 \cdot \sin\left(\frac{\tau}{\sqrt{L_1 C_1}}\right) \qquad \text{for } I_{OUT}(s) = \frac{1}{s} \mathbf{A}$$

(2.4)

Again the term  $Z_1$  occurs, however here, a small value of  $Z_1$  is desired to maintain a small voltage drop. This might be a first constraint, holding the input current small by accepting a higher voltage drop at the output. Equation (2.5) summarizes the conflict.

$(input \ current \ consideration) \quad a < Z_i < b \quad (voltage \ drop \ consideration)$  (2.5)

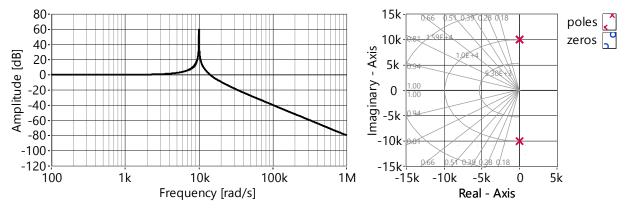

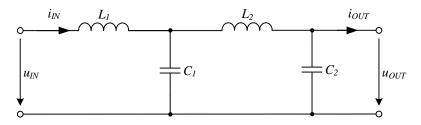

In section 2.2.3 a  $4^{\text{th}}$  order Bessel filter was proposed. Figure 2.10 shows a simple way to get a  $4^{\text{th}}$  order filter by doubling the basic filter element.

Figure 2.10 4<sup>th</sup> order passive LC-network.

Equation (2.6) shows the calculated frequency response.

$$G(s) = \frac{U_{OUT}(s)}{U_{IN}(s)} = \frac{1}{1 + s^2(L_1C_1 + L_2C_2 + L_1C_2) + s^4(L_1L_2C_1C_2)} = \frac{1}{\left(1 + \frac{s^2}{\omega_1^{-2}}\right)\left(1 + \frac{s^2}{\omega_2^{-2}}\right)}$$

(2.6)

Important is that  $\omega_1^2 \neq \frac{1}{L_1C_1}$  and  $\omega_2^2 \neq \frac{1}{L_2C_2}$ . It comes to a spread of the resonance frequencies. Figure 2.11 shows a filter with  $L_1 = 10$ mH,  $C_1 = 1\mu$ F,  $L_2 = 100\mu$ H,  $C_2 = 1\mu$ F. If this filter is

<sup>&</sup>lt;sup>1</sup> From now, the symbol  $Z_i$  is used instead of  $\sqrt{\frac{L_i}{C_i}}$ .

considered as two separate LC filters  $2^{nd}$  order, the resonance frequencies are located at 10krad/s and 100krad/s<sup>1</sup>. In the connected case, however, the new resonance frequencies are 7,06krad/s and 141,6krad/s.

Figure 2.11 Frequency response of a 4<sup>th</sup> order LC low-pass filter, with Pole-Zero diagram.

Beside  $Z_1$ , here also  $Z_2$  influences the input current and the voltage drop in the discussed response cases. Here, however, exists a possibility to solve that conflict by placing  $Z_1$  at the input side higher and  $Z_2$  at the output side lower. So  $C_1$  contributes its charge to hold the voltage drop lower in case of a load step. On the other hand,  $L_2$  holds the maximum input current lower in case of a voltage step.

Table 2.2 summarizes all filter related requirements. It is evident that there are three main factors. The transfer function, high switching frequency and the factors  $Z_i$ .

| Requirement                                               | Value                             | Key factors                               |

|-----------------------------------------------------------|-----------------------------------|-------------------------------------------|

| Stability                                                 | $\checkmark$                      | transfer function                         |

| Attenuation of the switching harmonic                     | min. 50dB                         | transfer function,<br>switching frequency |

| Amplification 0 1kHz                                      | const.                            | transfer function                         |

| Maximum overshoot at full voltage step                    | $<5\%$ of $U_\infty$              | transfer function                         |

| Maximum voltage drop at full load step at nominal voltage | $<$ 10% of $U_{nom}$              | $Z_i$                                     |

| Maximum input current at full voltage step                | See specifications<br>of switches | $Z_i$                                     |

Table 2.2 Filter requirements and key factors.

The terms  $Z_i$  can be easily adjusted by placing L and C. For the desired transfer function, however, an external controller is needed, because it is prohibited to influence the LC transfer function directly with resistors or other active elements.

A high switching frequency requires switches that can deal with them. How to find applicable switches will be discussed in the next chapter.

<sup>&</sup>lt;sup>1</sup> This consideration would only be valid if a voltage follower is placed between the filter elements.

#### 2.3 Switches

After the determination of the related requirements, switches are searched and compared. Later switches in SiC technology are analysed and the most suitable switches for this application are chosen.

#### 2.3.1 Switch Related Requirements

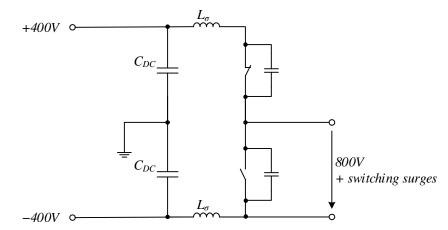

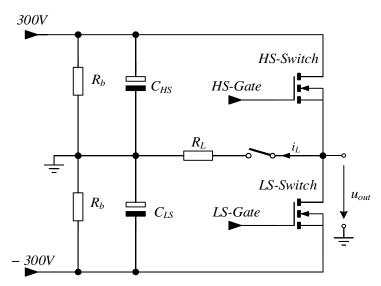

Two requirements are already identified: High switching frequency in the 100kHz range and high pulse current capability. A third important requirement is the Drain-Source voltage  $U_{DS}$ . Which value is necessary is pointed out in Figure 2.12.

Figure 2.12 Half-Bridge Topology, blocking voltage at worst-case scenario.

If the High-Side switch conducts, the full +400V lies at the output and so 800V at the Low-Side switch. Additionally, switching surges have to be considered. These oscillations occur because of parasitic inductances and capacities and have to be minimized<sup>1</sup>. Therefore, the challenge is to place the DC link capacitors  $C_{DC}$  as near as possible to the switches to reduce the wiring inductance  $L_{\sigma}$ . If necessary, there can be introduced different snubber circuits but this means also losses and so the aim is to well design the Printed Circuit Board (PCB) and avoid snubber. Nevertheless, oscillations have to be expected and therefore the MOSFET voltage stress is calculated with a factor of 1.5. That means a  $U_{DS}$  of 1200V.

Another criterion is the maximum continuous current. In the requirements  $\pm 10$ A are declared. For safety reasons the chosen switch should have at least an  $I_D$  of 15A.

The last criterion is a fast switching time. This criterion is derived by the first entry of Table 1.1. This requirement implies a maximum duty cycle of 95% or a minimum duty cycle of 5%. At a switching frequency of  $100 \text{kHz} - 10 \mu \text{s}$  per period -5% represents 500ns. To provide a rectangular shape, even in this case, a maximum switching time of 100ns is allowed.

Consequently, for the selection of a proper switch five values have to be considered.  $U_{DS} = 1200$ V,  $f_s = 100$ kHz,  $I_{PULSE}$  as high as possible,  $I_D > 15$ A and a switching time lower than 100ns.

<sup>&</sup>lt;sup>1</sup> Attention has to be paid to the analogy with the former discussed LC structure, where undamped oscillations have been discussed. In reality, also the conductive copper path forms a resistance, so that it is more a weakly damped oscillation.

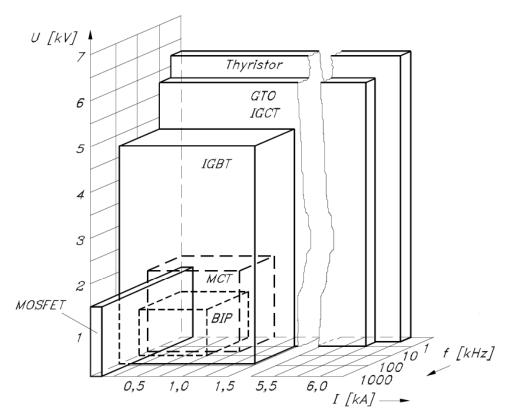

#### 2.3.2 State of the Art Si Switches

In Figure 2.13 typical area boundaries of Si switches are showed. In alignment with the requirements, the MOSFET or the IGBT technology can be used. The limit of the MOSFET technology may be the blocking voltage and for the IGBT the limit is the switching frequency. The IGBT's conduction losses are small and the switching losses are high compared to the MOSFET technology. For this reason, a MOSFET would be preferred, especially if there are types with low conduction resistance to reduce the related on-state losses.

Figure 2.13 Typical area boundaries of silicon semiconductor power switches [1, p. 631].

Table 2.3 shows values for the two selected technologies. Cleary visible is the high conduction resistance of the 1500V MOSFET technology. On the other hand, the IGBT works not loss-optimal at high frequencies and therefore it is only described till ~20kHz.

| Properties         | MOSFET 500V            | MOSFET 1500V            | IGBT                 |

|--------------------|------------------------|-------------------------|----------------------|

| Marinauna Valtana  | _                      | 0                       | +                    |

| Maximum Voltage    | 500V                   | 1500V                   | > 3500 V             |

| Maximum            | 0                      | _                       | +                    |

| Continuous Current | 75A                    | 8A                      | >1000A               |

| Maximum Switching  | +                      | +                       | 0                    |

| Frequency          | 100kHz                 | 100kHz                  | >20kHz               |

| Maximum Switching  | +                      | +                       | 0                    |

| Time               | 600 ns                 | 200 ns                  | 2300ns               |

| Conduction         | +                      | _                       | +                    |

| Resistance         | $100 \mathrm{m}\Omega$ | $1900 \mathrm{m}\Omega$ | $60\mathrm{m}\Omega$ |

Table 2.3 Comparison of silicon MOSFET and IGBT (+ good, o fair, - weak) [1, p. 630].

#### 2.3.3 SiC MOSFET Technology

In recent time, industry has introduced new SiC MOSFETs at acceptable prices. There are different crystal structures for SiC base material but now the 4H-SiC structure is commonly used to manufacture SiC MOSFETs. [4],[5] Table 2.4 compares the physical parameters.

| Properties                          | Si       | 4H-SiC    |

|-------------------------------------|----------|-----------|

| Bandgap $E_g$                       | 1.12     | 3.23      |

| [eV]                                |          | 0.20      |

| Lattice Const.                      | a = 5.43 | a = 3.09  |

| [Å]                                 | α = 0.10 | c = 10.05 |

| Critical Field ${\cal E}_c$         | 0.25     | 3         |

| [MV/cm]                             | 0.20     | 0         |

| Electron Mobility $\mu_n$           | 1450     | 900       |

| $[\mathrm{cm}^2/\mathrm{Vs}]$       | 1100     | 500       |

| Hole Mobility $\mu_p$               | 500      | 120       |

| $[\mathrm{cm}^2/\mathrm{Vs}]$       | 500      | 120       |

| Dielectric Constant $\varepsilon_r$ | 11.9     | 9.66      |

| [1]                                 | 11.9     | 9.00      |

| Thermal Conductivity                | 1.56     | 3.5-5.0   |

| [W/cmK]                             | 1.00     | 5.5-5.0   |

Table 2.4 Comparison of Si and SiC properties [6],[7].

The bandgap of SiC is nearly three times higher than the Si one, a disadvantage at the first sight, because of the expectable higher forward voltages at the basic pn junction. The biggest difference is the 10 times higher critical electric field strength. The carrier mobilities are worse but differ not as much as  $E_c$ .

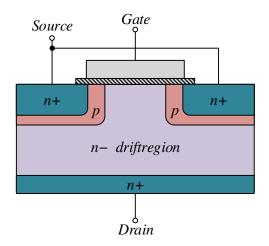

A look at the MOSFETs basics helps to understand which influences have all these differences. Figure 2.14 shows the basic vertical MOSFET structure.<sup>1</sup>

Figure 2.14 Vertical MOSFET with the blocking voltage determining n- driftregion.

$<sup>^{\</sup>rm 1}$  Without further information about the mode of action it is directly discussed the influence of  $E_c.$

The total blocking voltage is located at the n- drift region. It has to be built as long as necessary to block that voltage. This manner has significant influence to the conduction resistance  $R_{dson}$  of the MOSFET.

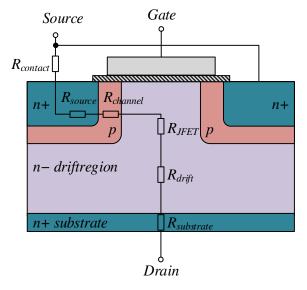

Figure 2.15 Illustration of the resistances in the vertical MOSFET, based on [1, p. 684]. The accumulation layer resistance and the intrinsic junction FET resistance is here combined as  $R_{JFET}$ .

In Figure 2.15, the individual resistance parts, which form the  $R_{dson}$ , are analysed. Literature studies show that  $R_{drift}$ , the resistance of the n- driftregion, counts for almost the whole resistance. The drift zone of a conventional power MOSFET with a blocking voltage of 600V counts for approximately 95% of the total  $R_{dson}$  [8]. So, this is the region which should initially be improved to reduce the overall resistance.

#### 2.3.4 Calculation of the Drift-Resistance

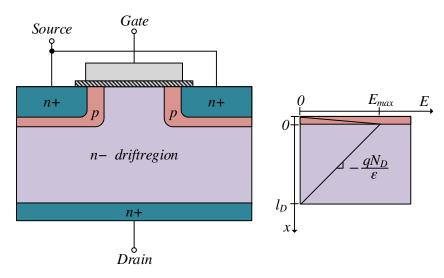

Figure 2.16 shows the basic vertical MOSFET structure with the electric field distribution inside homogenously doped regions.

Figure 2.16 Simplified illustration of the electric field gradient in the n- driftregion.

Based on the Poison equation

$$\Delta\varphi(x) = -\frac{\rho(x)}{\varepsilon} \tag{2.7}$$

the assumption of homogenous doping and the permission to reach the maximum electric field strength  $E_{max}=E_c$  results in

$$E(x) = -\frac{qN_D}{\varepsilon} \cdot x + E_c \ . \tag{2.8}$$

The Breakdown Voltage  $U_{BR}$  is defined as the integration of the electric field over the length of the driftzone, which is the represented as the area under the electric field curve.

$$U_{BR} = \int_0^{L_D} E(x) dx \tag{2.9}$$

After inserting of (2.8) in (2.9) follows

$$U_{BR} = E_c \cdot l_D - \frac{qN_D}{2\varepsilon} \cdot {l_D}^2 = \frac{E_c \cdot l_D}{2} . \qquad (2.10)$$

Without doping  $U_{BR}$  depends only on the length of the driftregion. A high  $N_D$  otherwise decreases  $U_{BR}$  but improves the conduction and so the resistance of the driftregion<sup>1</sup>.

Under the restriction of low resistance at a given  $U_{BR}$  first the resistance  $R_{drift}$  or better the factor  $R_{drift} \cdot A_{chip}$  is analysed [9, p. 14]

$$R_{drift} \cdot A_{Chip} = \frac{l_D}{q N_D \mu_n} \tag{2.11}$$

(2.10) inserted in (2.11) results in

$$R_{drift} \cdot A_{Chip} = \frac{l_D^3}{2\varepsilon q \mu_n (E_s l_D - U_{BR})}$$

(2.12)

According to C. Hu et al. [10]  $R_{drift} \cdot A_{chip}$  can be minimized with (2.13)

$$l_D = \frac{3 \cdot U_{BR}}{2 \cdot E_c} \tag{2.13}$$

to the following important relationship

$$R_{drift} \cdot A_{Chip} = \frac{27 \cdot U_{BR}^{2}}{8\varepsilon \mu_n E_c^{3}}$$

(2.14)

This equation shows that the resistance at a given  $U_{BR}$  is proportional to the inverse of the cube of  $E_c$ . For instance, that means if  $E_c$  increases by 10,  $R_{drift} \cdot A_{chip}$  decreases by the factor of 1000! Nearly this scenario is given in the comparison of Si and SiC. It was described that  $R_{drift}$ counts for ~95% of the whole  $R_{dson}$  in Si technology. Ideally considered in SiC technology this part is now in the range of the other resistance parts or even below. So the biggest disadvantage of a MOSFET at high breakdown voltage is eliminated.

<sup>&</sup>lt;sup>1</sup>  $N_D$  and  $l_D$  here interdepend.

# 2.3.5 SiC Diodes

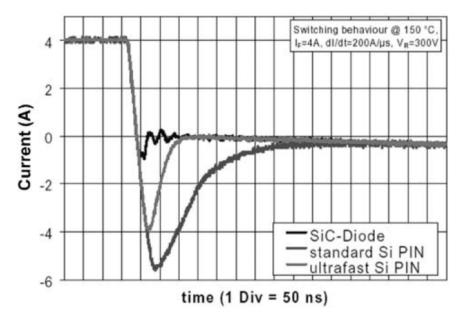

Forward voltage of a SiC pn junction is in the range of 2-3V [11]. Instead, SiC-Schottky-Diodes have a much lower forward voltage because of the lower barrier-height. Forward voltages of 1.5V can be achieved [10]. Figure 2.17 shows a comparison of Si and SiC diodes specified for 4A and 600V.

Figure 2.17 Comparison of the switching behaviour of three diodes with the same specifications 4A/600V [11, p. 689].

The advantage is evident. In the PIN diode cases first minority charge carriers have to be injected into the intrinsic zone for low conduction losses. At turn-off – see Figure 2.17 – these carriers have to recover which increases the turn-on losses of the MOSFET.

In the MOSFET case there exists a built-in body diode, a basic pn junction. It was mentioned that for this diode the forward voltage is in the range of 2-3V, higher than in the Si technology. At first view this is a disadvantage. At the second by placing antiparallel an external diode with lower forward voltage this represents a big advantage. The external diode SiC-Schottky-diode with much better characteristics conducts already at lower voltages and eliminates so the worse built-in diode.

Summarized, two major advantages of SiC MOSFETs compared to Si MOSFETs exist. First the lower  $R_{dson}$  because of the higher critical field strength and second the possibility to use an optimized external antiparallel diode to reduce switching losses.

Researchers and experts in the industry also support this expertise. For example, according to Schröder [11, p. 695] under 3kV SiC structures are strongly recommended.

# 2.3.6 Comparison of MOSFET Alternatives

Two SiC MOSFETs are selected for comparison. CREE's C2M0080120D combined with Cree's C4D08120 Schottky Diode and ROHM's SCH2080KE with built-in Schottky-Barrier-Diode (SBD). They are compared with an optimized Super Junction silicon MOSFET, STFW6N120K3 from ST Microelectronics, with equal breakdown Voltage  $U_{BR}$ .

| Properties                                                | C2M0080120D | SCH2080KE | STFW6N120K3 |

|-----------------------------------------------------------|-------------|-----------|-------------|

| Technology                                                | SiC         | SiC       | Si          |

| Drain-Source Voltage <sup>1</sup> $U_{DDS}$<br>[V]        | 1200        | 1200      | 1200        |

| Continuous Drain Current $I_D @~25^{\circ}\mathrm{C}$ [A] | 31.6        | 40        | 6           |

| Gate Source Voltage $U_{GS}$<br>[V]                       | -10 / +25   | -6 / +22  | $\pm$ 30    |

| Drain-Source ON Resistance $R_{dson}$<br>[m $\Omega$ ]    | 80          | 80        | 1950        |

| Total Gate Charge $Q_g$<br>[nC]                           | 49.2        | 106       | 39          |

| Turn ON Time<br>[ns]                                      | 41.6        | 70        | 42          |

| Turn OFF Time<br>[ns]                                     | 35.8        | 98        | 90          |

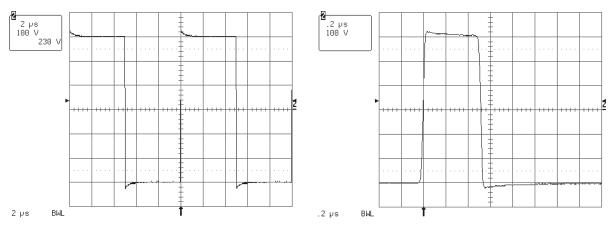

Table 2.5 Comparison of different 1200V MOSFETs [12] [13] [14].

The difference of the  $R_{dson}$  between the two SiC MOSFETs compared to the Si MOSFET is evident, but not as huge as expected. The ST-MOSFET, however, is a silicon Super Junction MOSFET, with many improvements compared to the simple vertical structure, so that the ratio is only 25. A second notable difference can be seen in the comparison of the antiparallel diode. The reverse recovery charge  $Q_{rr}$  is much higher than in the SiC variants, see Table 2.6. This leads to higher switching losses proportional to the difference of  $Q_{rr}$ . Between the individual SiC MOSFETs the differences are marginal compared to the Si MOSFET. The CREE part has lower turn-on and turn-off times and the half total gate charge. The extra diode has also better properties than the built-in one in the ROHM device. On the other hand, in the latter case only a single semiconductor device has to be considered in the layout and so it can be optimized with regard to disturbances produced by high  $\frac{du}{dt}$  values which may disturb the feedback control unit. The higher switching times of the ROHM device are not a big problem. Related to a maximum switching frequency of 100kHz – 10µs per period – <100ns turn off time is less than 1% and complies with the former declared requirements.

| Properties                                      | C4D08120 | SCH2080KE | STFW6N120K3 |

|-------------------------------------------------|----------|-----------|-------------|

| Forward Voltage $U_{SD}$<br>[V]                 | 1.5      | 1.3       | 1.6         |

| Forward Current $I_D @ 25^{\circ}C$<br>[A]      | 24.5     | 40        | 6           |

| Reverse Recovery Charge $Q_{rr}$ @ 400V<br>[nC] | 27       | 60        | 9000        |

Table 2.6 Comparison of the antiparallel Diode combined with the MOSFETs [13] [14] [15].

<sup>&</sup>lt;sup>1</sup> In datasheets often V is used for voltage instead of U. In this thesis always U is used for voltage.

#### 2.3.7 Perspectives of SiC MOSFETs

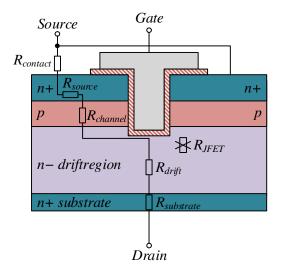

Section 2.3.4 showed that the resistance of the n- drift region in the SiC technology is in the range of the other resistance parts or even below. So, for a further reduction of  $R_{dson}$  the next challenge is to reduce the other resistance parts. One way is the introduction of a trench structure, as shown in Figure 2.18.

Figure 2.18 MOSFET with trench structure and eliminated  $R_{JFET}$ .

The main reason is the elimination of  $R_{JFET}$ . This is an already used and common structure, for example in Si-IGBTs [16]. There, the  $U_{CE,sat}$  could be reduced by 30% after introducing a gate trench structure.

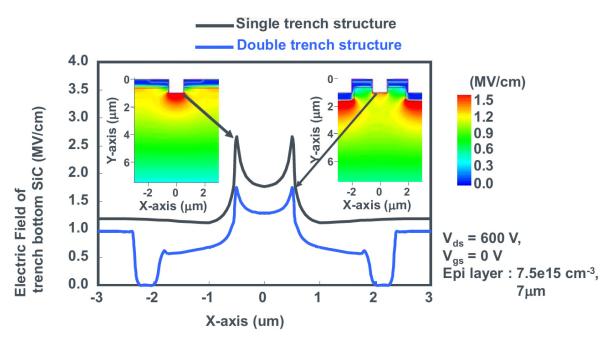

For MOSFETs in SiC technology the company ROHM has introduced a double trench structure in their 3<sup>rd</sup> generation SiC MOSFETs [17]. By using only a single trench the electric field strength locally would be too high, which would cause damages in the insulating layer, see Figure 2.19.

Figure 2.19 Comparison of single and double trench structures in a vertical MOSFET [17].

# 2.4 Assessed Circuit Topology

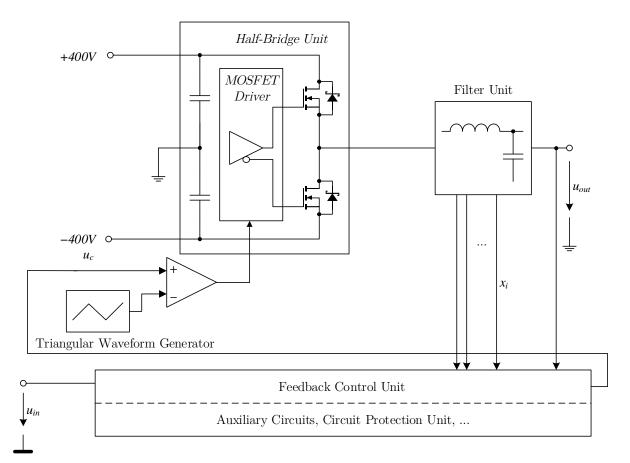

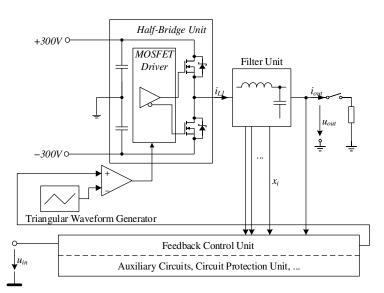

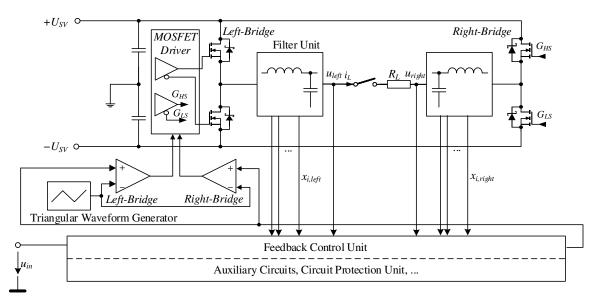

The considerations of chapter 2, result in the following circuit scheme.

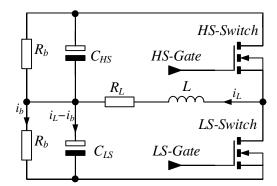

Figure 2.20 Resulting circuit topology with all related units.

The total device is split-up in three major units with their individual tasks:

| 0 | Half-Bridge Unit      | Power amplification of the input PWM signal                               |

|---|-----------------------|---------------------------------------------------------------------------|

| 0 | Filter Unit           | Lossless filtering of the switching harmonic                              |

| 0 | Feedback Control Unit | Stabilisation of the filter and generation of a desired transfer function |

Problems related with the Half-Bridge Unit und the Filter Unit have been already discussed. The most important challenge is to design an appropriate Feedback Control Unit.

The necessary electronic circuits are a triangular waveform generator, an appropriate comparator to generate the PWM signal and auxiliary circuits, e. g. voltage regulation circuits.

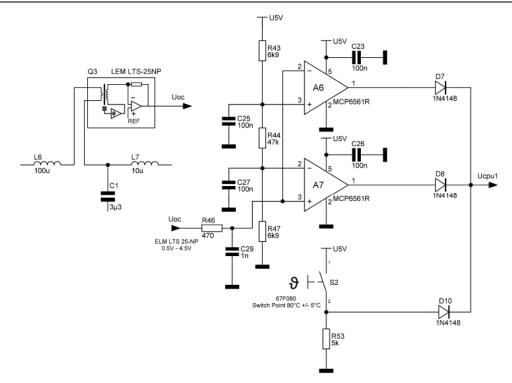

Additionally, a protection circuit is introduced. This part is used to protect the device against short circuit at the output terminals and against overload, which means a resulting overtemperature of the MOSFETs, respectively of the cooling element.

# 3 Concepts for Feedback Control Unit

In chapter 2 different filter types were discussed theoretically. The conclusion was that a 4<sup>th</sup> order Bessel filter complies with all the requirements. It was shown, however, that the realisation of such filter is not possible only by placing component (L and C) values. The proposed filter structure with inductors and capacitors does not represent a stable system. Therefore, it was suggested to introduce a feedback control.

In this chapter, different controller models are developed to stabilize the system and to create the desired transfer function. First the suggested circuit topology of section 2.4 is transformed into a system model and the related transfer function is given. After this, the control principle to stabilize the system is explained and the boundaries of the method are described. In the following section different filter concepts are developed and compared, first theoretically, then by using a circuit simulator leading to a final decision.

### 3.1 System Model

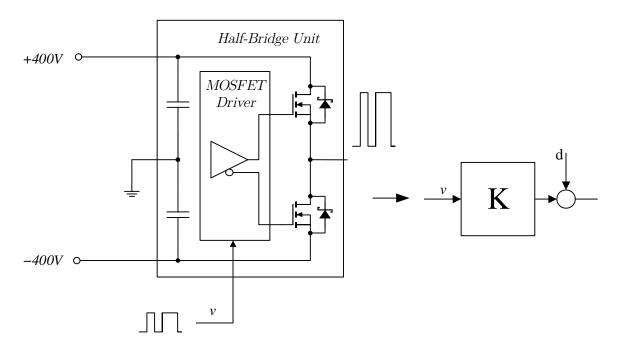

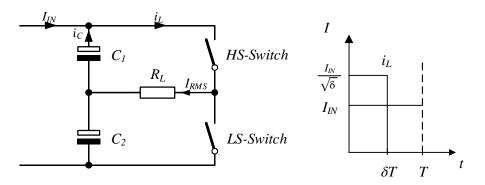

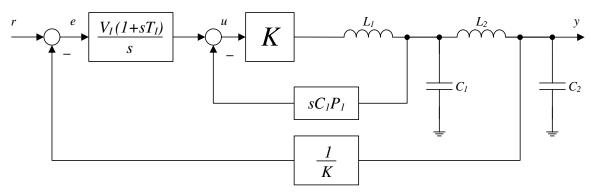

Before a feedback control can be developed, all significantly involved parts of the amplifier have to be transformed into an entire system model. Figure 2.20 shows the basic circuit topology with all relevant parts. The transfer function of the filter itself, the inductors and capacitors, was already calculated in Equation (2.6). The Half-Bridge Unit, ideally considered, can be transformed into a simple DC Gain. Figure 3.1 shows the Half-Bridge Unit with the input and output signal.

Figure 3.1 Transformation of the Half-Bridge Unit into a DC Gain.

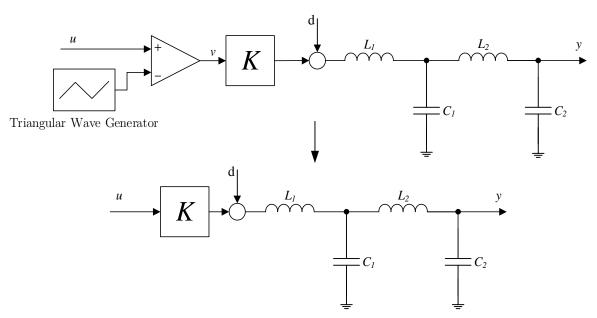

The input signal v is generated by the PWM comparator. The resulting PWM signal is amplified by a factor K considering the DC power supply (±400V). In addition, a summation node is introduced for calculating the transfer function for the amplified PWM signal. With this, the attenuation of the high frequency switching harmonics can be calculated. The next step includes the Triangular Wave Generator and the comparator of Figure 2.20, which form a naturally sampled modulator. This modulator transforms the information of the signal u, which is described by its amplitude and phase, into a duty cycle depended information. Ideally considered, the resulting high frequency harmonics are rejected in the filter. It was shown in [18] that such a modulator contributes zero phase lag. This implies that the signal is not changed by the modulation and an ideal filter, neither in the amplitude nor in the phase. Therefore, these parts can be treated as a Unity Gain block. This can only be done because the PWM frequency – here the switching frequency – is at least two times the highest frequency component of the input signal. Figure 3.2 shows the resulting system model.

Figure 3.2 Resulting system model of the plant.

Based on Figure 3.2, the transfer functions of interest are calculated.  $G_{u,y}(s)$  is the output transfer function related to the input u, which has to be changed into a Bessel transfer function.

$$G_{u,y}(s) = \frac{K}{1 + s^2(L_1C_1 + L_2C_2 + L_1C_2) + s^4(L_1C_1L_2C_2)}$$

(3.1)

$G_{d,y}(s)$  represents the transfer function, which is used to calculate the attenuation of the switching harmonics. In the uncontrolled model, it is equal to Equation (2.6).

$$G_{d,y}(s) = \frac{1}{1 + s^2(L_1C_1 + L_2C_2 + L_1C_2) + s^4(L_1C_1L_2C_2)}$$

(3.2)

#### 3.2 Basic Control Considerations

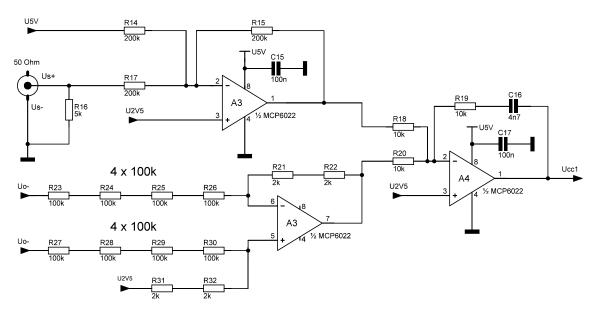

The DC Gain can be calculated by dividing the supply voltage  $U_{SV}$  by the amplitude of the triangular wave.

$$K = \frac{U_{SV}}{\hat{U}_{triangle}} \tag{3.3}$$

$U_{SV}$  is fixed to 400V. The amplitude of the triangular wave, however, can be chosen freely. In Table 1.2 the voltage for auxiliary circuits is fixed to +5V. Therefore, an amplitude of 2V with a DC offset of 2.5V is chosen. The full voltage of 5V is not utilized to avoid problems with operational amplifiers (OPA) at the supply rails. So the DC gain K results in  $K = \frac{400V}{2V} = 200 \frac{V}{V}$ .

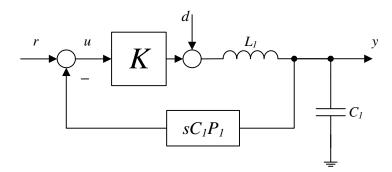

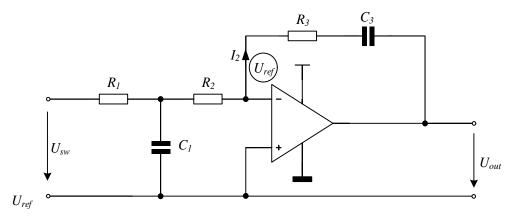

The basic control scheme for stabilizing the LC–filter is shown in Figure 3.3. There a feedback of the capacitors current is introduced.

Figure 3.3 2<sup>nd</sup> order LC-filter with capacitors' current feedback.

The important point is that this creates a term  $sKP_1C_1$  in the denominator of the transfer function. This significates that the damping factor  $\xi$  can be affected by the factor  $P_1$ . It also depends on the values of the inductor, the capacitor and the DC Gain. The resonance frequency, however, does not change.

$$G_{r,y}(s) = \frac{K}{1 + sKP_1C_1 + s^2L_1C_1} = \frac{K}{1 + 2\xi\frac{s}{\omega_0} + \frac{s^2}{{\omega_0}^2}} \to \ \xi = \frac{KP_1}{2}\sqrt{\frac{C_1}{L_1}}, \ \omega_0 = \frac{1}{\sqrt{L_1C_1}} \quad (3.4)$$

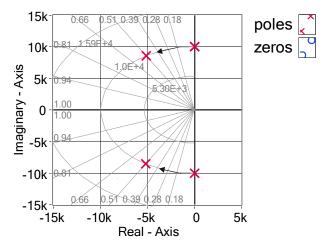

$P_1$  has to transform the current into a voltage. This can be realised by a resistor. The resistance then represents the value of  $P_1$ . Figure 3.4 shows the relationship in the Pole-Zero diagram for the 2<sup>nd</sup> order example in section 2.2.5 with  $L_1 = 10$ mH,  $C_1 = 1\mu$ F. By increasing  $P_1$  the poles can be pushed into the negative s-plane.

Figure 3.4 Influence of the capacitors current feedback to the poles of a 2<sup>nd</sup> order LC-filter.

This concludes in the result that the system can be stabilized easily and the damping factor  $\xi$  can be set theoretically to any value only by a feedback of the capacitors current.

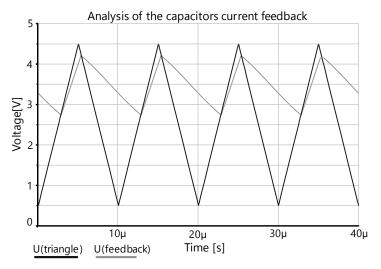

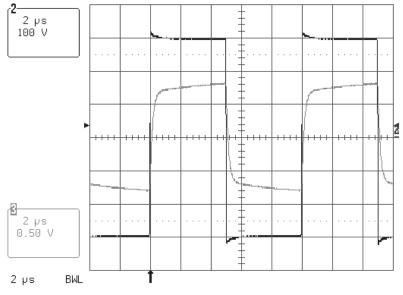

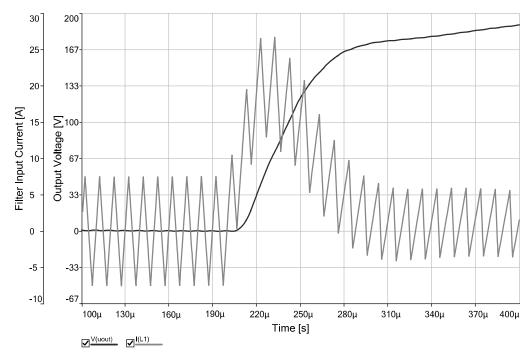

The model of Figure 3.3 is implemented in a circuit simulator<sup>1</sup> to prove its functional capability. Figure 3.5 shows a typical result of a simulation.

Figure 3.5 Curve analysis of a simulated filter with capacitors' current feedback.

The current of  $C_1$  here is already transformed into a voltage. This voltage is fed back and shown as U(feedback). If  $P_1$  reaches a certain value, the gradient of the feedback curve is higher than the gradient of the triangle curve U(triangle). In this case the feedback curve slides up the triangle curve caused by permanent on-off switching of the MOSFETs. The transfer function is no longer valid. Furthermore, the permanent switching actions means stress to the Half-Bridge Unit, which could lead to thermal damage. Therefore, this case has to be avoided.

To better understand the relationships, the critical value of  $P_1$  is calculated. This is the value where the gradient of the feedback curve is equal to the gradient of the triangle curve. Based on the relationship  $u_L = L \cdot \frac{di_L}{dt}$  the maximum feedback gradient for a certain value of  $P_1$  is calculated.

$$\hat{k}_{feedback} = P_1 \cdot \frac{\Delta i}{\Delta t} = \frac{P_1}{L_1} \cdot U_{L_1,max}$$

$$(3.5)$$

On the other hand, the triangle gradient depends on the triangle amplitude and the switching frequency.

$$k_{triangle} = \frac{\Delta u_{triangle}}{\Delta t} = U_{triangle, p-p} \cdot 2f_s \tag{3.6}$$

The condition for a safe operation is that the gradient of the feedback curve is smaller than the gradient of the triangle curve.

$$k_{feedback} < k_{triangle} \tag{3.7}$$

Equation (3.5) and Equation (3.6) inserted in Equation (3.7) leads to Equation (3.8). There the ratio  $\frac{P_1}{L_1}$  is expressed.

$$\frac{P_1}{L_1} < \frac{U_{triangle,p-p} \cdot 2f_s}{U_{L_1,max}} \tag{3.8}$$

<sup>&</sup>lt;sup>1</sup> National Instruments Multisim Circuit Simulator is used for this analysis.

The worst case, the highest gradient of the capacitors current, occurs when the output voltage of the amplifier is set near to the supply voltage and the output voltage of the filter is opposite. In this instant, the full 800V lies at the inductor. So,  $U_{L_1,max} = 800$ V. The switching frequency is defined as  $f_s = 100$ kHz and the peak-peak voltage of the triangle is  $U_{triangle,p-p} = 4$ V. This leads to a critical  $\frac{P_1}{L_1}$  ratio of  $\frac{P_1}{L_1} < 1000$ s<sup>-1</sup>.

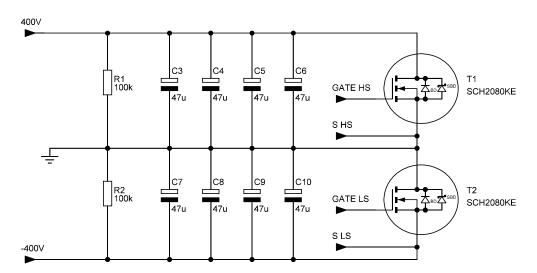

Another important point is the dimensioning of the inductor and capacitor values. It was described in section 2.2.5, that  $Z_i$ , the carcteristic impedances, should be small to maintain low voltage drop at a load step but high enough to limit the filter input current at step responses. The inductor value  $L_1$  in Figure 3.3, one part of the filter, limits the gradient of the filter input current. It also determines the maximum amplitude of the filter input current, because the switching frequency is constant. Therefore,  $L_1$  has to be dimensioned such that a certain limit of the filter input current is not exceeded. In the requirements a maximum output current of  $\pm 10A$  is specified. The ripple current amplitude shall not exceed this value. The highest ripple current occurs at a output voltage  $U_{out} = 0V$ . Generally the amplitude of the ripple current is defined as

$$\frac{di_L}{dt} = \frac{u_L}{L_1} \quad \to \quad \hat{I}_{ripple} = \frac{U_{SV} \cdot \Delta t}{2 \cdot L_1} \tag{3.9}$$

To limit the filter current amplitude to 10A the inductor value has to be higher than  $L_{1,min} = \frac{U_{SV} \cdot \Delta t}{2 \cdot I_{ripple}} = \frac{400V \cdot 5\mu s}{2 \cdot 10A} = 100 \mu$ H. This is already a high value. If, for instance, a characteristic impedance of 5 $\Omega$  has to be achieved, this means a 4 $\mu$ F capacitor, a charge of 1600 $\mu$ As is necessary for a voltage step of 400V. At typical rise times of 50 $\mu$ s, noticeable in the filter studies section 2.2, this leads to high current peaks, here 32A for 50 $\mu$ s. In reality, this is not a perfect rectangular shape, so that even higher current peaks are expected. The conclusion is that the inductor value of  $L_1$  has to be placed in the range of 100 $\mu$ H and the capacitor value in the range of 4 $\mu$ F.

# 3.3 Feedback Control Approaches

Based on the results of section 3.2 four different control approaches are examined. The first approach relies on a faithful reproduction of the theoretical  $4^{\text{th}}$  order Bessel filter. The second approach tries to improve the dynamic by leaving the principle of a perfect filter reproduction. There, an approximated  $3^{\text{rd}}$  order filter is designed. The third approach looks similar to the second but the calculation principle is different and more applicable than in the  $3^{\text{rd}}$  order approach. The fourth approach relies on the others but tries to improve the dynamic of the system by the usage of all discussed control possibilities.

#### 3.3.1 Fourth-Order Bessel Filter

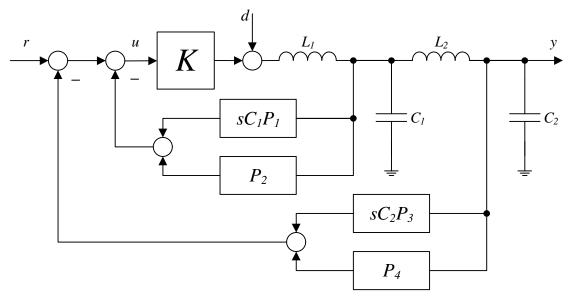

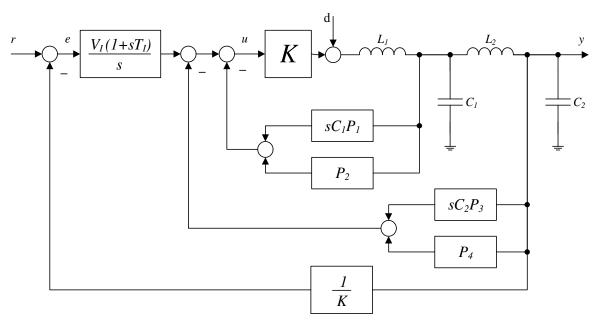

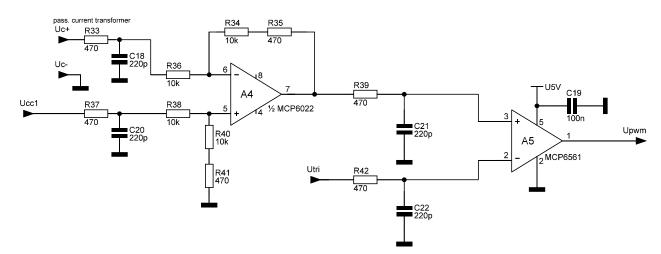

In this approach a perfect reproduction of a 4<sup>th</sup> order filter is analysed. It bases on a state feedback control. This is possible, because all state variables of the system can be measured easily. The voltages can be measured with OPA circuits such a differential amplifier and the current with current transformers and resistors. Figure 3.6 shows the resulting controller structure.

Figure 3.6 State feedback control structure.

All states that are fed-back can be affected by gains  $P_i$ . These gains can be realized by OPA circuits or directly by a resistor as shown in section 3.2. The resulting transfer function  $G_{r,y}(s)$  is shown in Equation (3.10). The essential point is that every term of the denominator can be set arbitrary, either by  $P_i$  or by an inductor or capacitor value

$$G_{r,y}(s) = \frac{K}{[1 + K(P_2 + P_4)] + s[K(C_1P_1 + C_2P_3)] + s^2[L_1C_1 + L_2C_2 + L_1C_2 + KP_2L_2C_2] + s^3[KP_1C_1L_2C_2] + s^4[L_1C_1L_2C_2]}$$

(3.10)

The transfer function  $G_{d,y}(s)$  looks similar to  $G_{r,y}(s)$ . Only the factor K is replaced by 1.

$$G_{d,y}(s) = \frac{1}{[1 + K(P_2 + P_4)] + s[K(C_1P_1 + C_2P_3)] + s^2[L_1C_1 + L_2C_2 + L_1C_2 + KP_2L_2C_2] + s^3[KP_1C_1L_2C_2] + s^4[L_1C_1L_2C_2]}$$

(3.11)

Generally normalized poles<sup>1</sup> are given for different filter types in filter design handbooks. This leads to a transfer function, which is shown in Equation (3.12).

$$G_{r,y}(s) = \frac{K}{\left(\frac{s}{p_1}+1\right) \cdot \left(\frac{s}{p_2}+1\right) \cdot \left(\frac{s}{p_3}+1\right) \cdot \left(\frac{s}{p_4}+1\right)}$$

(3.12)

The denominator of this equation, however, cannot be compared with the denominators of Equation (3.10) or Equation (3.11). Therefore, the denominator has to be expanded. This leads to a denominator with parameters A...D which can directly be compared to Equation (3.10) and Equation (3.11).

$$G_{r,y}(s) = \frac{K}{1 + As + Bs^2 + Cs^3 + Ds^4} \quad \rightarrow \quad P_2 = -P_4, \quad \frac{P_1}{L_1} = \frac{C}{K \cdot D} < 1000 \text{s}^{-1} \tag{3.13}$$

This leads to two results. First  $P_2 = -P_4$ , only the difference of  $u_{c_1} - u_{c_2} = u_{c_1} - y$  has to be fed back. This reduces one OPA in the circuit realisation. Second  $\frac{P_1}{L_1} = \frac{C}{K \cdot D} < 1000 \text{s}^{-1}$ . The essential point is that  $\frac{P_1}{L_1}$  does not depend on the setting of the other part values, e. g.  $C_1$ ,  $L_2$  or

<sup>&</sup>lt;sup>1</sup> For all calculations the normalized Bessel poles are extracted out of [3, p. 468]

$C_2$ . It depends only on the cutoff frequency of the Bessel filter. If the cutoff frequency is increased,  $\frac{P_1}{L_1}$  exceeds the limit of 1000s<sup>-1</sup> long before the attenuation of the switching frequency reaches the critical value of 50dB. Therefore,  $\frac{P_1}{L_1}$  represents the limiting factor in this case.

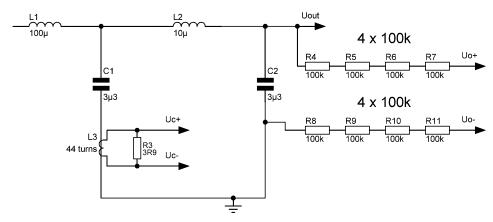

$\frac{P_1}{L_1}$  is set to a value near 1000s<sup>-1</sup> to reach the maximum dynamic.  $L_1$  is set to 100µH as described in section 3.2.  $C_1$  is set to 3.3µF. This increases the characteristic impedance by 10% but reduces the current peak in a step response case. The parameter  $P_2$  can be set to zero. Thus,  $L_2$  and  $C_2$ have to be calculated and cannot be set arbitrary. Table 3.1 shows all values and controller parameters for the 4<sup>th</sup> order Bessel filter attempt.

| $L_1$ [ $\mu$ H] | $C_1$      | $Z_1$      | $L_2$      | $C_2$      | $Z_2$      | $\mathbf{P}_1$ | P <sub>2</sub> | $P_3$        | P <sub>4</sub> |

|------------------|------------|------------|------------|------------|------------|----------------|----------------|--------------|----------------|

|                  | [ $\mu$ F] | $[\Omega]$ | [ $\mu$ H] | [ $\mu$ F] | $[\Omega]$ | $[\Omega]$     | [1]            | [ $\Omega$ ] | [1]            |

| 100              | 3.3        | 5.5        | 32.8       | 5.8        | 2.38       | 98.59m         | 0              | -12.34m      | 0              |

Table 3.1 Part values, characteristic impedances and controller parameters, 4<sup>th</sup> order Bessel filter approach.

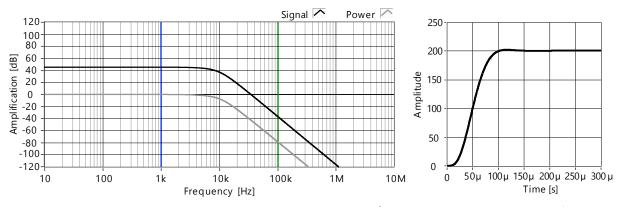

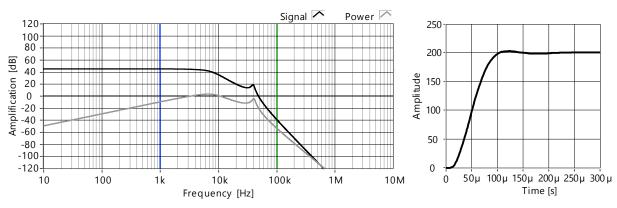

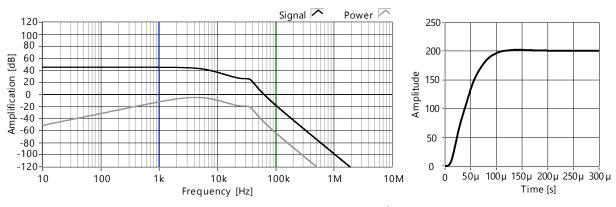

Figure 3.7 shows the related frequency response and step response. It is visible that the only difference between  $G_{r,y}(s)$  and  $G_{d,y}(s)$  is the gain K.

Figure 3.7 Frequency response and step response, 4<sup>th</sup> order Bessel filter approach<sup>1</sup>.

| The relevant data of | the | frequency | response is | summarized | in | Table 3 | 3.2. |

|----------------------|-----|-----------|-------------|------------|----|---------|------|

|----------------------|-----|-----------|-------------|------------|----|---------|------|

| Attenuation at $f_s$ | DC Amplification | Amplification at $f_m^2$ | Amplification Lack <sup>3</sup> at $f_m$ |

|----------------------|------------------|--------------------------|------------------------------------------|

| [dB]                 | [dB]             | [dB]                     | [dB]                                     |

| 79.8                 | 46.02            | 45.96                    | 0.06                                     |

Table 3.2 Frequency response analysis, 4<sup>th</sup> order Bessel filter approach.

The attenuation at  $f_s = 100$ kHz is excellent. Also the amplification lack at  $f_m$  is minimal. That means nearly the same amplification of all allowed input frequencies.

$<sup>^{1}</sup>G_{r,y}(s)$  is represented by the curve Signal and  $G_{d,y}(s)$  by the curve Power.

$<sup>^2</sup>$   $f_m$  is the highest frequency that is allowed in the input parameters,  $f_m = 1 \rm kHz.$

<sup>&</sup>lt;sup>3</sup> Amplification lack is the difference between the DC amplification and the amplification at  $f_m$ .

The step response looks good, as it is expected. The overshoot<sup>1</sup> is under 1%, which is better than required. The settling time<sup>2</sup> is in the range of 100 $\mu$ s. For a 1kHz rectangular input signal – 1ms per period – 20% of the half period is need to reach the set value. In a less strict consideration, the rise time can be used instead of the settling time. Compared to the former example the output only needs 10% of the time to reach the required value. Table 3.3 shows the data of the step response.

| St | eady State | Peak Value | Overshoot | $Peak Time^{3}$ | Settling Time | Rise $Time^4$ |

|----|------------|------------|-----------|-----------------|---------------|---------------|

|    | [V]        | [V]        | [%]       | $[\mu s]$       | $[\mu s]$     | $[\mu s]$     |

|    | 200        | 201.66     | 0.833     | 116             | 96.5          | 52.8          |

Table 3.3 Step response analysis, 4<sup>th</sup> order Bessel filter approach.

The limiting factor in this approach is  $\frac{P_1}{L_1}$  and not the attenuation at  $f_s$ . If it is possible to push the frequency response toward higher frequencies, higher dynamic can be achieved. This means faster settling and rise time. On the other hand, this decreases the attenuation. Lower attenuation, however, does not demonstrate a problem, because there is enough design margin. An attempt with higher order systems does not lead to better results.  $\frac{P_1}{L_1}$  decreases even more the cutoff frequency, which results in worse dynamic. Attempts with lower order systems are more promising because of lower  $\frac{P_1}{L_1}$  ratios. Therefore, an approximated Bessel filter 3<sup>rd</sup> order is developed.

#### 3.3.2 Approximated Third-Order Bessel Filter

In the 4<sup>th</sup> order Bessel filter approach  $\frac{P_1}{L_1}$  was the limiting factor. A lower filter order, however, allows to push the cutoff frequency towards higher frequency values. This behaviour is utilized in this approach. Equation (3.14) shows the design principle.

$$G_{r,y}(s) = \frac{K}{(1 + sA + s^2B + s^3C) \cdot \left(1 + \frac{s^2}{\omega_2^2}\right)} = G'_{r,y}(s) \cdot \frac{1}{\left(1 + \frac{s^2}{\omega_2^2}\right)}$$

(3.14)

First, a  $3^{\rm rd}$  order Bessel filter transfer function is designed. Afterwards, the second basic filter element is added to increase the attenuation at  $f_s$ . Important is, that the resonance frequency of the second basic filter element is obviously higher than the cutoff frequency of the designed  $3^{\rm rd}$  order Bessel filter. This changes the frequency response at higher frequencies but maintains the characteristic Bessel step response. Therefore, the resulting filter is only an approximated Bessel filter.

The whole Equation (3.14) demonstrates a system 5<sup>th</sup> order. That makes it necessary to introduce another circuit element. A simple way is the introduction of an integral element with a feedback of the output voltage.

<sup>&</sup>lt;sup>1</sup> Overshoot is defined as the ratio between the steady state value and the peak value in percent.

$<sup>^{2}</sup>$  Settling time is defined as the time from the begin of the step to the moment in which the output voltage rests within 1% of the steady state value.

<sup>&</sup>lt;sup>3</sup> Peak time describes the point in time when the peak value occurs.

$<sup>^4</sup>$  Rise time is the time interval between 10% and 90% of the steady state value.

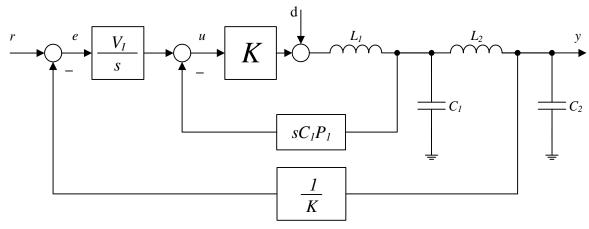

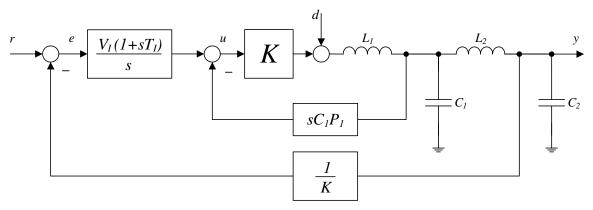

Another aim is to keep the whole system as simple as it is in the 4<sup>th</sup> order Bessel filter approach. It is tried to set  $P_2$  and  $P_4$  to zero again. It is also possible to set  $P_3$  to zero, because the Bessel filter design is carried out with only one basic filter element. The situation is comparable to the considerations in section 3.2, see also Figure 3.3. The point is that  $P_1$  damps the first and also the second basic filter element. Figure 3.8 shows the resulting system model.

Figure 3.8 Relevant system model, 3<sup>rd</sup> order Bessel filter approach.

The resulting transfer functions  $G_{r,y}(s)$  and  $G_{d,y}(s)$  of this system are shown in Equation (3.15) and Equation (3.16).

$$G_{r,y}(s) = \frac{K}{1 + s\left[\frac{1}{V_I}\right] + s^2\left[\frac{K}{V_I}C_1P_1\right] + s^3\left[\frac{1}{V_I}(L_1C_1 + L_2C_2 + L_1C_2)\right] + s^4\left[\frac{K}{V_I}P_1C_1L_2C_2\right] + s^5\left[\frac{1}{V_I}L_1C_1L_2C_2\right]}$$

(3.15)

$$G_{d,y}(s) = \frac{s}{V_I \cdot \left\{ \begin{aligned} 1 + s \left[ \frac{1}{V_I} \right] + s^2 \left[ \frac{K}{V_I} C_1 P_1 \right] + s^3 \left[ \frac{1}{V_I} (L_1 C_1 + L_2 C_2 + L_1 C_2) \right] + \right\}}{s^4 \left[ \frac{K}{V_I} P_1 C_1 L_2 C_2 \right] + s^5 \left[ \frac{1}{V_I} L_1 C_1 L_2 C_2 \right]} \end{aligned}$$

(3.16)

The design starts by setting  $L_2$  and  $C_2$  to zero. This leads to a simple  $3^{\text{rd}}$  order transfer function, shown in Equation (3.17).

$$G'_{r,y}(s) = \frac{K}{1 + s \left[\frac{1}{V_I}\right] + s^2 \left[\frac{K}{V_I} C_1 P_1\right] + s^3 \left[\frac{1}{V_I} L_1 C_1\right]}$$

(3.17)

Then the denominator polynomial is calculated for a promising cutoff frequency. After this,  $\frac{P_1}{L_1}$  is identified. The result is similar to the previous,  $\frac{P_1}{L_1} = \frac{B}{K \cdot C} < 1000 \text{s}^{-1}$ . Then  $V_I$  is determined as  $V_I = \frac{1}{A}$ .  $C_1$  is set arbitrary and  $L_1$  is calculated. In almost the same manner it is possible to set  $L_1$  arbitrary and calculate  $C_1$ . This leads to the transfer function  $G'_{r,y}(s)$ , which is drawn in a Bode plot to check the result. The next step is to add the second basic filter element.  $L_2$  and  $C_2$ , those who determine the resonance frequency of the second filter element, are set to reach the minimum attenuation specified in the requirements. The effect of different values of  $L_2$  and  $C_2$  is observed in the Bode plots of  $G_{r,y}(s)$  and  $G_{d,y}(s)$ . If the resulting attenuation is in the range

of 50...60dB the step response is checked. If needed, caused by a non-satisfying step response, the whole procedure is started again with an adjusted cutoff frequency of the 3<sup>rd</sup> order Bessel filter. The results for a promising attempt, the part values and controller parameters, are summarized in Table 3.4.

| $L_1$<br>[ $\mu$ H] | $\begin{array}{c} C_1 \\ [\mu \mathrm{F}] \end{array}$ | $\begin{matrix} Z_1 \\ [\Omega] \end{matrix}$ | $L_2$<br>[ $\mu$ H] | $C_2$<br>[µF] | $\begin{array}{c} Z_2 \\ [\Omega] \end{array}$ | $\begin{array}{c} \mathbf{P}_1 \\ [\Omega] \end{array}$ | P <sub>2</sub><br>[1] | $\mathbf{P}_3$<br>$[\Omega]$ | P <sub>4</sub><br>[1] | $V_I$ $\left[\frac{1}{s}\right]$ |

|---------------------|--------------------------------------------------------|-----------------------------------------------|---------------------|---------------|------------------------------------------------|---------------------------------------------------------|-----------------------|------------------------------|-----------------------|----------------------------------|

| 57                  | 3.3                                                    | 4.16                                          | 20                  | 1             | 4.47                                           | $32.25\mathrm{m}$                                       | 0                     | 0                            | 0                     | 18.9k                            |

Table 3.4 Part values, characteristic impedances and controller parameters, 3<sup>rd</sup> order Bessel filter approach.

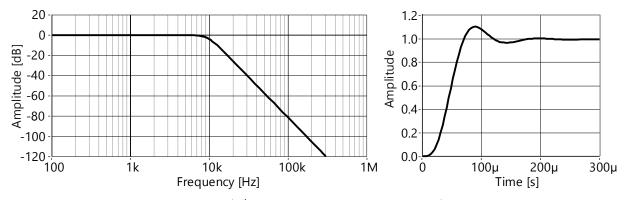

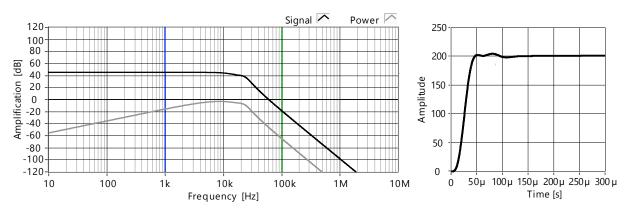

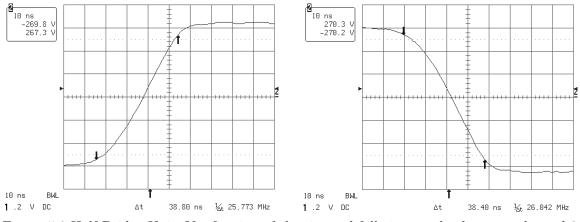

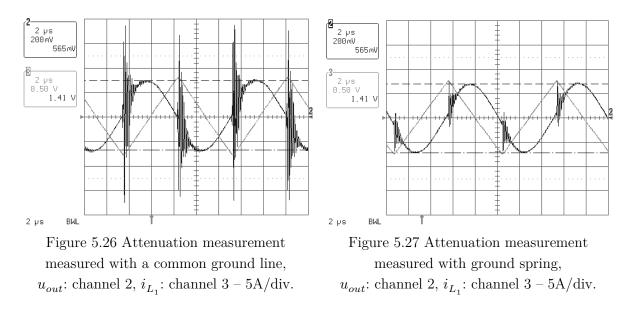

For the calculated polynomial,  $\frac{P_1}{L_1} = 565s^{-1} < 1000s^{-1}$ . This result shows that here is no problem with this factor. Figure 3.9 shows the frequency responses  $G_{r,y}(s)$  and  $G_{d,y}(s)$ .

Figure 3.9 Frequency response and step response, 3<sup>rd</sup> order Bessel filter approach.

In both frequency responses, the resonance frequency of the second filter element is visible. As expected, it is damped without any feedback of the second capacitor's current. The frequency response of  $G_{d,y}(s)$ , however, has a different curve shape, than the the frequency response of  $G_{r,y}(s)$ . The reason is visible in Equation (3.16). There a factor  $\frac{s}{V_I}$  occurs which means a +20dB/decade gradient of the curve with a pass through zero at  $\frac{V_I}{2\cdot\pi}$ . In this case  $\frac{V_I}{2\cdot\pi} \approx 3$ kHz. The attenuation at  $f_s$  of the rectangular signal is 53.68dB. The amplification lack is negligible.

| Attenuation at $f_s$ | DC Amplification | Amplification at $f_m$ | Amplification Lack at $f_m$ |

|----------------------|------------------|------------------------|-----------------------------|

| [dB]                 | [dB]             | [dB]                   | [dB]                        |

| 53.68                | 46.02            | 45.93                  | 0.09                        |

Table 3.5 Frequency response analysis, 3<sup>rd</sup> order Bessel filter approach.

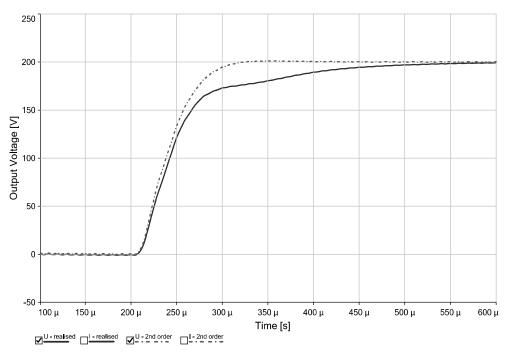

The analysis results of the step response is shown in Table 3.6. The results are sobering. There is achieved no significant improvement compared to the 4<sup>th</sup> order Bessel filter approach.

| Steady State | Peak Value | Overshoot | Peak Time | Settling Time | Rise Time |

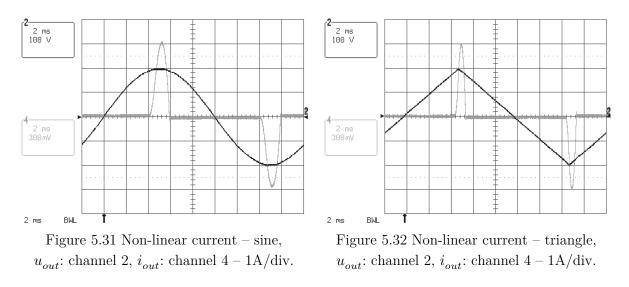

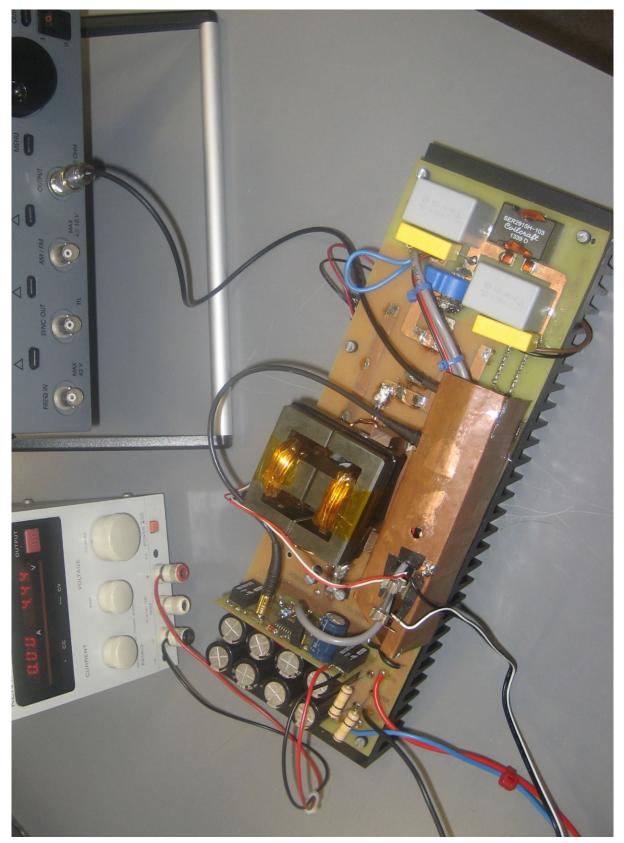

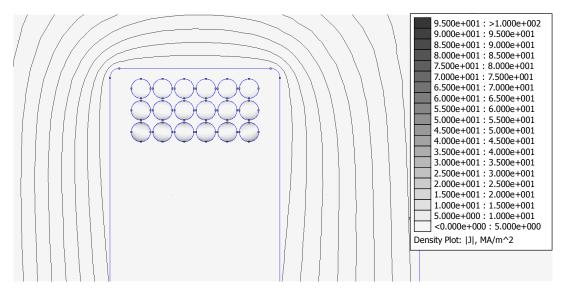

|--------------|------------|-----------|-----------|---------------|-----------|