DISSERTATION

## Modeling of Defect Related Reliability Phenomena in SiC Power-MOSFETs

zur Erlangung des akademischen Grades **Doktor der technischen Wissenschaften**

EINGEREICHT AN DER **Technische Universität Wien** Fakultät für Elektrotechnik und Informationstechnik

> VON Dipl.-Ing. **Christian Schleich**

UNTER BETREUUNG VON Univ.Prof. Dipl.-Ing. Dr.techn. **Tibor Grasser** UND Assistant Prof. Dipl.-Ing. Dr.techn. **Michael Waltl**

Wien, August 2022

# Acknowledgements

First and foremost I would like to thank PROFESSOR TIBOR GRASSER for giving me the opportunity to explore a scientific field in great detail, which became an invaluable experience, as well as for timely guidance whenever needed, while at the same time allowing me to pursue my studies on the topics I found to be most interesting.

Second, tribute goes to ASSISTENT PROFESSOR MICHAEL WALTL for providing all resources and funding<sup>1</sup> that have made this work possible as well as for sharing his experience.

A functional team is of fundamental importance to successfully take on upcoming opportunities and complete the challenges that a PhD study brings along. Even the hurdles of an outbreaking pandemic were manageable, as I have been lucky enough to work with so many excellent colleagues at the Institute for Microelectronics. My deepest gratitude goes to you, many of who have become friends over this interesting but fairly challenging period, named in arbitrary order:

BERNHARD STAMPFER, DOMINIC WALDHÖR, JAKOB MICHL, THERESIA KNOBLOCH, MARKUS JECH, AL-MOATASEM EL-SAYED, KONSTANTINOS TSELIOS and ALEKSANDR VASILEV

Thank you all, also for providing your critical feedback to this thesis.

Also, I would like to thank the colleagues from our industrial partners at Infineon Villach and Munich, KAI, imec and GTS. Without your unlimited experimental support and advise, this thesis would not have been possible:

KATJA PUSCHKARSKY, MAXIMILIAN FEIL, JUDITH BERENS, GREGOR POBEGEN, BERNHARD RUCH, MAGDALENA WEGER, GERHARD RZEPA, ALEXANDER GRILL and BEN KACZER

For providing a perfect working environment at the Institute special thanks go to MANFRED KATTERBAUER, DIANA POP, EWALD HASLINGER and JOHANN CERVENKA.

Besonderer Dank gilt auch allen Freunden und der gesamten Familie für die moralische Unterstützung, im Speziellen meiner Freundin MARLIES und meiner Mutter ERIKA.

<sup>&</sup>lt;sup>1</sup>The financial support by the Austrian Federal Ministry for Digital and Economic Affairs, the National Foundation for Research, Technology and Development, and the Christian Doppler Research Association are gratefully acknowledged.

## CHAPTER 0. ACKNOWLEDGEMENTS

# Abstract

The quality of the interface between semiconductor and insulator material has always played a major role for the functionality of a Metal Oxide Semiconductor Field-Effect Transistor (MOSFET). This also applies to silicon carbide (SiC) MOSFETs which show superior properties when used as switches in power conversion applications. However, electrically active defects on an atomic scale located near the SiC/SiO<sub>2</sub> interface determine the stability of the device parameters and increase its on-state losses due to a perturbation of the electrostatics upon being charged. The kinetics of these charge transfer processes are strongly influenced by the applied bias and surrounding temperature, hence summarized under the term Bias Temperature Instability (BTI). While the total defect density at the interface has been significantly reduced, by e.g., the introduction of nitrogen-containing post-oxidation anneals, which led to improved channel carrier mobility and stability of the threshold voltage, the exact nature of these defects is still unknown. Another detrimental effect caused by oxide defects are enhanced gate leakage currents, which are enabled by the traps acting as charge transition centers, termed Trap-Assisted Tunneling (TAT) currents. Since both effects are widely accepted to be caused by inelastic tunneling processes, the underlying charge transfer reactions can be described by the Non-Radiative Multi-Phonon (NMP) model. While the application of this model has revealed many details of the charge transfer kinetics and led to the identification of a few potential defect structures in Si MOSFETs, its application to SiC MOSFETs has not been successfully demonstrated. One reason for this is the large defect density, which hampers defect parameter extraction by conventional methods. Therefore, a novel Effective Single Defect Decomposition (ESiD) algorithm is applied in combination with the reliability simulation framework Comphy to simulate the measured transient threshold voltage shifts caused by charge transfer at a large ensemble of defects, which is characterized in various lateral channel MOSFETs. The obtained defect parameters are then compared for their consistency over several SiC technologies and with those reported from ab-initio calculations for suspected defect structures. Additionally, a new two-state NMP based TAT modeling approach is presented in this work, including charge hopping between defects. This novel model is then applied to successfully explain TAT currents obtained in SiC/SiO<sub>2</sub> MOSCAPs. Further verification of the model with widely studied TAT currents measured employing capacitors based on ZrO<sub>2</sub> allows to draw conclusions about the nature of these charge transition centers in both binary oxides. A defect parameter comparison to those obtained from DFT calculations of models from a defect class, so called polarons, results

in excellent agreement, rendering polarons a likely defect candidate responsible for TAT. Finally, features of both reliability threats, BTI and TAT, are reasonably well explained by two-state NMP charge transfer kinetics in SiC-based MOSFETs. The extracted defect parameters suggest a few structural defects as the root-cause of reliability issues in SiC MOSFETs due to their consistency with ab-initio based parameter extraction.

# Kurzfassung

Eine zentrale Rolle für die Funktionalität des Metal Oxide Semiconductor Field-Effect Transistors (MOSFET) spielt seit jeher die Qualität des Materialüberganges zwischen Halbleiter und Isolator. Das gilt auch für Silizium Carbid (SiC) basierte MOSFETs, welche herausragende Eigenschaften für die Verwendung als Schalter in Spannungsumrichtern mit sich bringen. Die Stabilität der Bauteilparameter wird dabei von mikroskopischen Defekten nahe dem SiC/SiO<sub>2</sub> Übergang beeinflusst, die sich elektrisch laden können, was zu einer Erhöhung des Leitungswiderstandes als Folge der elektrostatischen Störung führt. Die Kinetik dieser Ladungstransferprozesse wird dabei wesentlich von der angelegten Gate-Spannung und der Umgebungstemperatur beeinflusst, weshalb der Effekt als Bias Temperature Instability (BTI) bezeichnet wird. Obwohl die Defektdichte am Materialübergang durch einen Passivierungsprozess in Stickstoffmonoxid angereicherter Umgebung erheblich reduziert wird, wirken sich Defekte immer noch nachteilig auf die Lebenszeit von Transistoren aus. Trotz intensiver Forschung ist die chemische Struktur der elektrisch aktiven Defekte noch immer nicht geklärt. Eine weitere nachteilige Auswirkung von Oxiddefekten kann deren Rolle als Transmissionszentren für sogenannte Trap-Assisted Tunneling (TAT) Ströme sein. Beide Effekte, BTI und TAT, resultieren aus inelastischen Tunnel-Ladungsprozessen welche mit Hilfe der Non-Radiative Multi-Phonon (NMP) Theorie beschrieben werden können. Während dieses Model erfolgreich für die detailierte Beschreibung der Ladungstranferkinetik in Silizium basierten MOSFETs verwendet wurde und zur Identifikation zahlreicher struktureller Defektkandidaten geführt hat, blieb dessen Anwendung in SiC MOSFETs bisher aus. Einer der Gründe dafür ist die große Vielzahl und hohe Dichte an Defektstrukturen, die die Extraktion von Bauteil- und Defektparametern mit herkömmlichen Methoden erschweren. Aus diesem Grund wurde die sogenannte Effective Single Defect Decomposition (ESiD) für die Defektparameter Bestimmung in Kombination mit dem Zuverlässigkeitssimulator Comphy verwendet, um die gemessene zeitabhängige Schwellenspannungsverschiebung in verschiedenen lateralen MOSFETs zu reproduzieren. Die auf verschiedenen SiC MOSFET Technologien extrahierten Defektparameter werden anschließend mit Hilfe von Dichtefunktionaltheorie (DFT) berechneten Werten verglichen. Zusätzlich wurde im Rahmen dieser Dissertation ein neues zwei-Zustands-NMP Model zur Beschreibung von TAT Strömen entwickelt, welches den Ladungstransfer zwischen den Defekten berücksichtigt. Mit diesem Model können TAT-Ströme in SiC/SiO<sub>2</sub> MOSCAPs erfolgreich erklärt werden. Zusätzlich wird die Modellierung anhand von bekannten Tunnelströmen in Kondensatoren mit

Zirconiomoxid (ZrO<sub>2</sub>) als Dielektrikum verifiziert. In beiden Oxiden lassen sich die Tunnelströme mit Defekten erklären, deren NMP Parameter exzellent mit jenen die sich aus DFT Rechnungen für sogenannte Polaronen ergeben, übereinstimmen. Zusammenfassend lassen sich beiden Zuverlässigkeitsphänomene, BTI und TAT, in SiC MOSFETs durch Ladungstransfers zu und von Defekten anhand des NMP Models erklären. Die dabei verwendeten Parameter können auf Konsistenz mit DFT Rechnungen geprüft werden, wodurch eine Eingrenzung auf einige wenige Defektkandidaten ermöglicht wird.

# Contents

| A  | cknov   | wledge   | ments                                     |     | iii  |

|----|---------|----------|-------------------------------------------|-----|------|

| Al | bstrad  | ct       |                                           |     | v    |

| Kı | urzfa   | ssung    |                                           |     | vii  |

| Co | onten   | ts       |                                           |     | ix   |

| Li | st of : | Figures  | 5                                         |     | xiii |

| Li | st of ' | Tables   |                                           |     | xv   |

| Li | st of . | Abbrev   | viations                                  |     | xvii |

| 1  | Intr    | oductio  | on                                        |     | 1    |

|    | 1.1     | MOSE     | FETs in Power Conversion Applications     |     | 1    |

|    |         | 1.1.1    | Materials                                 |     |      |

|    |         | 1.1.2    | From MOSFETs to SiC Power Switches        |     | 5    |

|    |         | 1.1.3    | Silicon Carbide Material Properties       |     | 6    |

|    |         | 1.1.4    | Fabrication and Properties of SiC MOSFETs |     | 8    |

|    | 1.2     | Reliat   | pility of MOSFETs                         |     | 11   |

|    |         | 1.2.1    | Bias Temperature Instabilities            |     | 13   |

|    |         | 1.2.2    | Gate Leakage Currents and Oxide Breakdown |     | 15   |

|    |         | 1.2.3    | Hot Carrier Degradation                   |     | 16   |

|    | 1.3     | State of | of the Art, Motivation and Outline        |     | 18   |

| 2  | SiC     | MOSF     | FET Reliability Characterization          |     | 21   |

|    | 2.1     | Electr   | ical Characterization Methods             |     | 21   |

|    |         | 2.1.1    | Transfer Characteristics                  |     | 21   |

|    |         | 2.1.2    | Capacitance Voltage Measurements          | ••• | 23   |

|    |         | 2.1.3    | Measure-Stress-Measure Schemes            |     | 25   |

|    |         | 2.1.4    | Single Charge Transfer Measurements       |     | 27   |

|    | 2.2     | Peculi   | iarities of SiC MOSFET Characterization   |     | 30   |

|    | 2.3     | Measu    | urement Setups                            |     | 31   |

|    | 2.4     | Magn     | etic Resonance Methods                    |     | 32   |

| CONTENTS |

|----------|

|----------|

|   | 2.5 | Summary                                                    |

|---|-----|------------------------------------------------------------|

| 3 | Def | ects in SiC Field Effect Transistors 35                    |

|   | 3.1 | Defects in Bulk Silicon Dioxide                            |

|   | 3.2 | Defects at the Silicon Carbide / Silicon Dioxide Interface |

|   | 3.3 | The Role of Hydrogen 40                                    |

|   | 3.4 | Nitrogen Related Defects                                   |

|   | 3.5 | Summary                                                    |

| 4 | Mo  | deling of Charge Transfer Reactions 43                     |

|   | 4.1 | From State Diagrams to the Master Equation                 |

|   | 4.2 | The Shockley-Read-Hall Model                               |

|   | 4.3 | Non-Radiative Multi-Phonon Theory                          |

|   | 4.4 | Two-State NMP Model for Trap-Trap Interaction    52        |

|   |     | 4.4.1 Parameter Transformation                             |

|   |     | 4.4.2 Limitations                                          |

|   | 4.5 | Efficient Framework for MOS Gate Leakage Currents          |

|   |     | 4.5.1 Tsu-Esaki Model                                      |

|   |     | 4.5.2 Charge Hopping Model                                 |

|   | 4.6 | Compact Physics Framework (Comphy)                         |

|   |     | 4.6.1 Electrostatic Quantities                             |

|   |     | 4.6.2 Threshold Voltage Shift                              |

|   |     | 4.6.3 Gate Leakage Current Computation                     |

|   | 4.7 | The Multi-TAT Regime                                       |

|   | 4.8 | Effective Single Defect Decomposition                      |

|   | 4.9 | Summary                                                    |

| 5 | Mea | asurements, Simulations and Results 73                     |

| - | 5.1 | Bias Temperature Instabilities in SiC MOSFETs              |

|   |     | 5.1.1 Lateral Test Structures                              |

|   |     | 5.1.2 Comparison of different DMOS Technologies            |

|   |     | 5.1.3 Defect Parameters                                    |

|   |     | 5.1.4 Temperature Activation of Electron Emission          |

|   |     | 5.1.5 Capture and Emission Time Maps                       |

|   |     | 5.1.6 Reliable Prediction of $\Delta V_{\text{th}}$        |

|   |     | 5.1.7 Summary                                              |

|   | 5.2 | Trap-Assisted Tunneling Currents                           |

|   | 0.2 | 5.2.1 Tunnel Currents in SiC MOSCAPs                       |

|   |     | 5.2.2 Tunnel Currents in TZT Structures                    |

|   |     | 5.2.3 The Role of Polarons                                 |

|   |     | 5.2.4         Model Verification         105               |

|   |     |                                                            |

|   | 5.3 | 5                                                          |

|   | 5.5 | Conclusions                                                |

| 6   | Sum    | mary and Outlook | 111 |

|-----|--------|------------------|-----|

|     | 6.1    | Summary          | 111 |

|     | 6.2    | Outlook          | 112 |

| Re  | feren  | ces              | 113 |

| Lis | t of I | Publications     | 141 |

| Cu  | rricu  | lum Vitae        | 145 |

# **List of Figures**

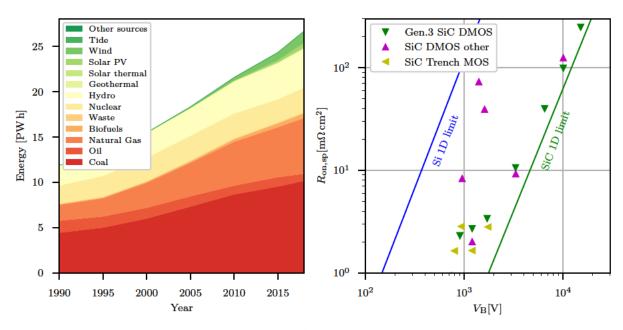

| 1.1  | Global electric energy consumption                                      | 2  |

|------|-------------------------------------------------------------------------|----|

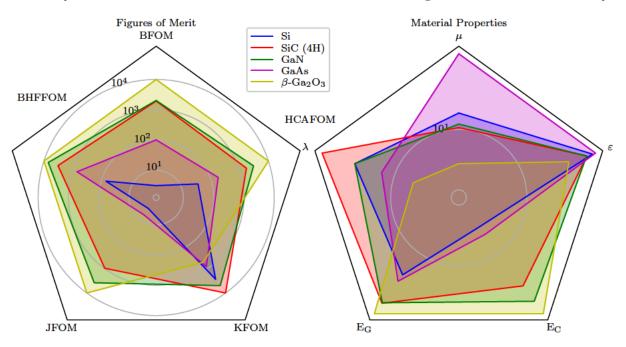

| 1.2  | Power device figure of merits                                           | 4  |

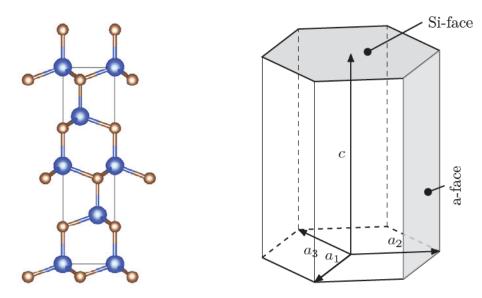

| 1.3  | Crystal structure and unit cell of 4H-SiC                               | 7  |

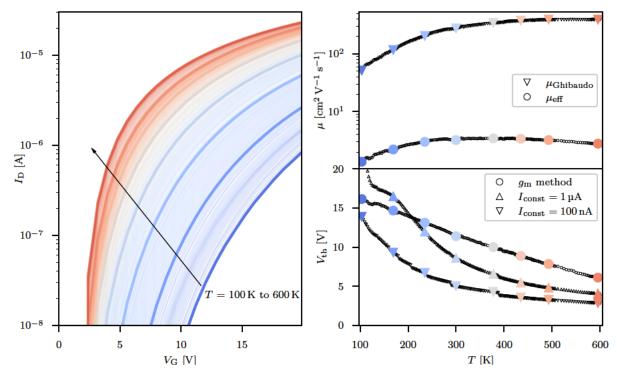

| 1.4  | Channel mobility as a function of temperature                           | 11 |

| 1.5  | DMOS and UMOS architectures for power switches                          | 12 |

| 1.6  | Reliability mechanisms in gate and drain bias space                     | 17 |

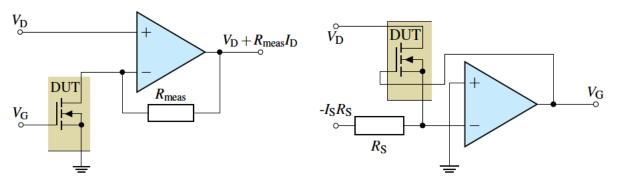

| 2.1  | Parameter extraction based on transfer characteristics                  | 22 |

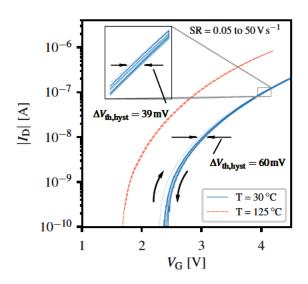

| 2.2  | Transfer characteristics hysteresis                                     | 24 |

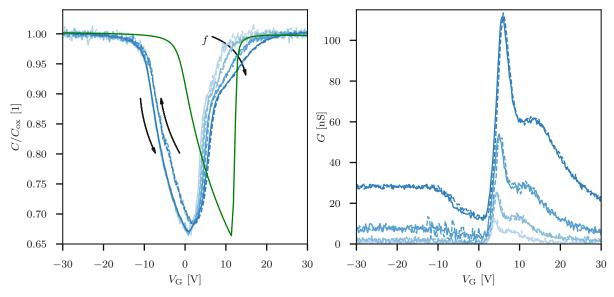

| 2.3  | Capacitance voltage measurement example on SiC/SiO <sub>2</sub> MOSFETs | 25 |

| 2.4  | Measure-Stress-Measure schemes                                          | 26 |

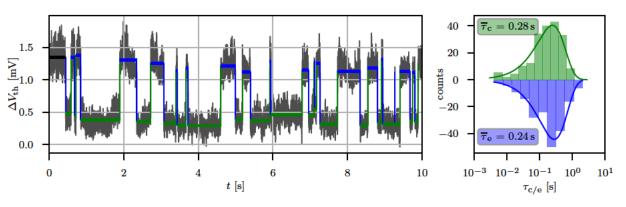

| 2.5  | Exemplary RTN measurement and analysis                                  | 28 |

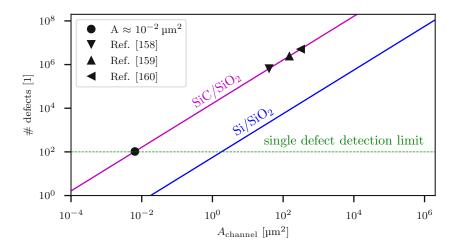

| 2.6  | Scaling requirements for electrical single defect characterization      | 29 |

| 2.7  | Techniques for channel conduction measurement                           | 32 |

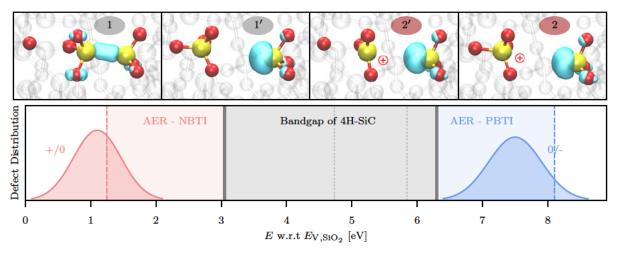

| 3.1  | Configurations and CTL distributions of OV                              | 37 |

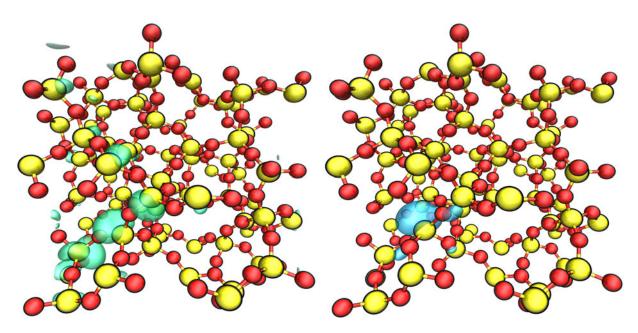

| 3.2  | Atomistic model of intrinsic electron trap                              | 38 |

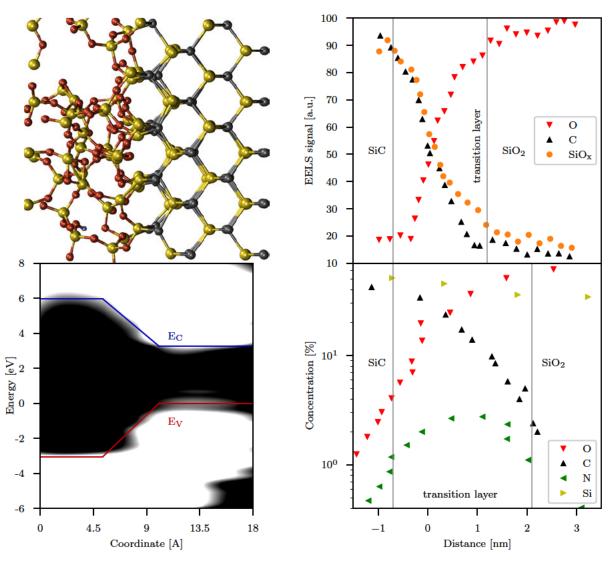

| 3.3  | Interface transition layer between SiC and $SiO_2$                      | 39 |

| 4.1  | Defect state diagrams                                                   | 44 |

| 4.2  | Classical and extended SRH models                                       | 47 |

| 4.3  | Potential energy curves of a two-state defect                           | 50 |

| 4.4  | Potential energy curves for defect/reservoir and defect/defect charge   |    |

|      | transfer                                                                | 53 |

| 4.5  | Coulomb coupling between defects                                        | 55 |

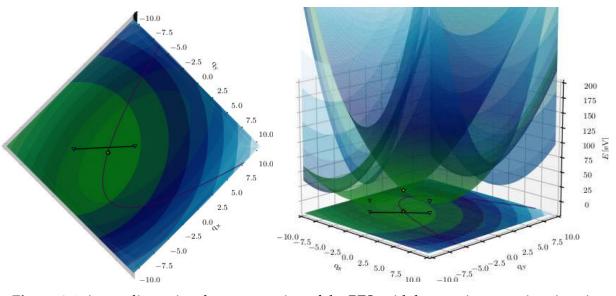

| 4.6  | Error due to a one dimensional PES representation                       | 56 |

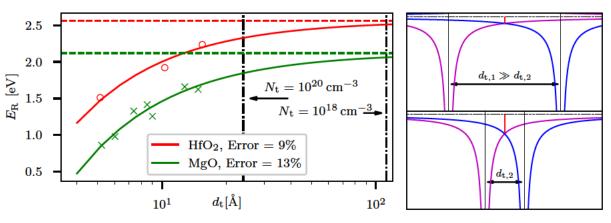

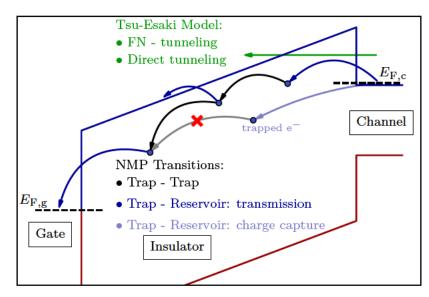

| 4.7  | Tunneling mechanisms in a MOS gate stack                                | 57 |

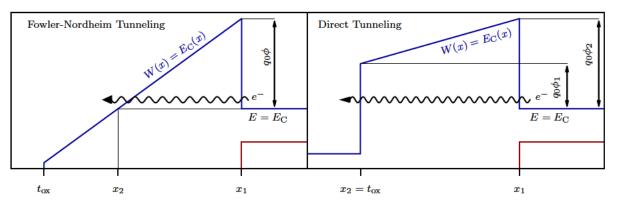

| 4.8  | Fowler-Nordheim versus Direct Tunneling                                 | 58 |

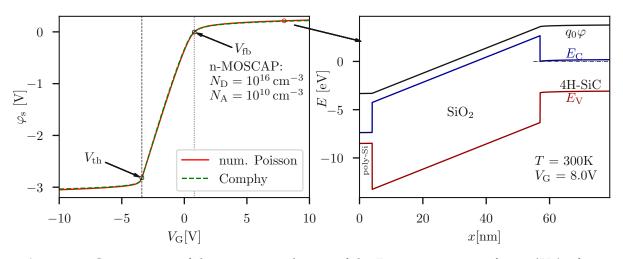

| 4.9  | Electrostatic calculation                                               | 62 |

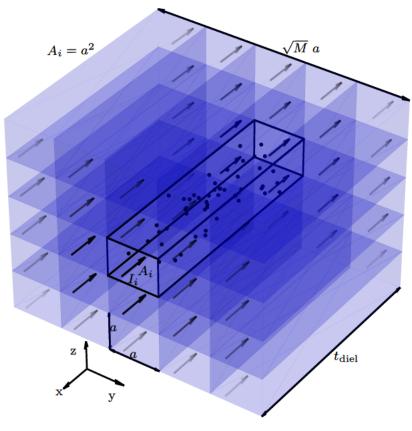

| 4.10 | Comphy simulation domain for TAT mode                                   | 63 |

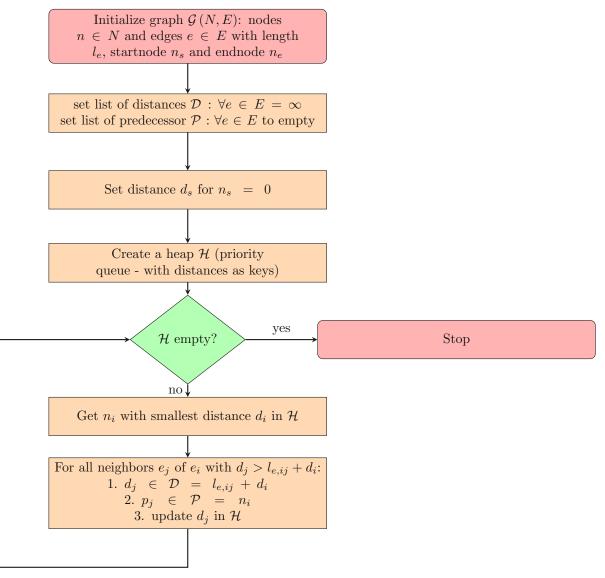

| 4.11 | Flow diagram of Dijkstras algorithm employing a heap                    | 65 |

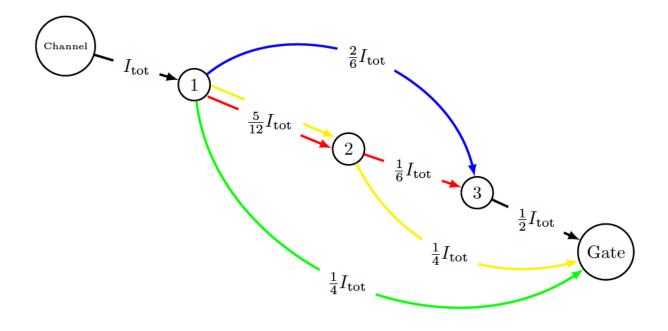

| 4.12 | Example of a graph for extraction of percolation paths                  | 67 |

| 4.13 | Average defect number in percolation paths                              | 68 |

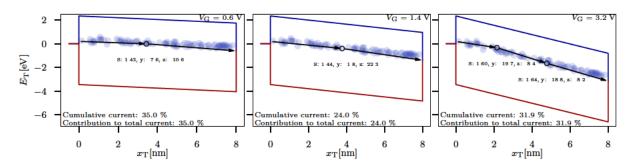

| 4.14 | Percolation path details at different gate bias regions                 | 69 |

| 4.15 | ESiD optimization results                                                         | 71  |

|------|-----------------------------------------------------------------------------------|-----|

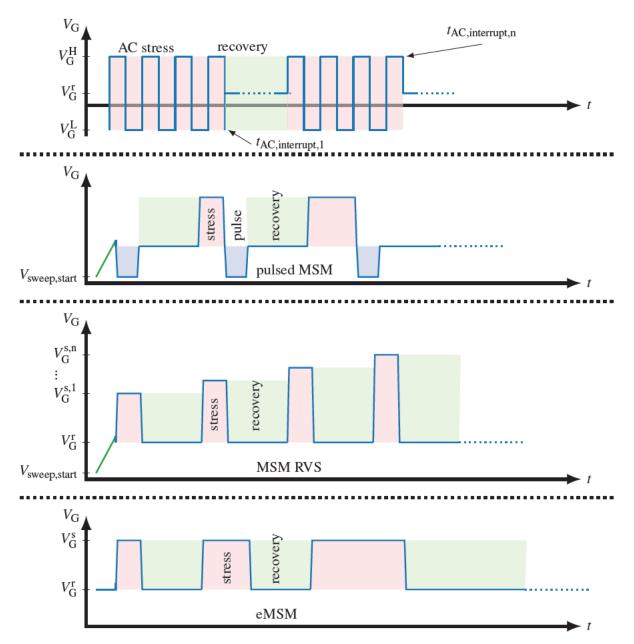

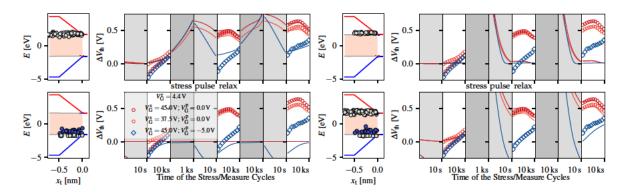

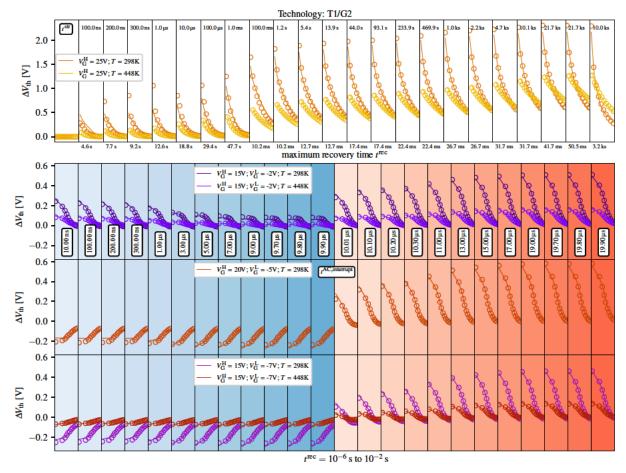

| 5.1  | MSM sequences for PBTI characterization of lateral MOSFETs                        | 76  |

| 5.2  | Pulsed-MSM sequence for separation of fast and slow $\Delta V_{\text{th}}$        | 77  |

| 5.3  | NBTI with RVS and temperature activation characterization with CVS                |     |

|      | MSM                                                                               | 78  |

| 5.4  | PBTI characterization of a Trench MOSFET                                          | 79  |

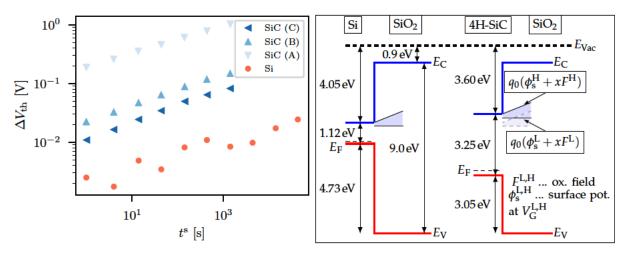

| 5.5  | Active energy region comparison in $Si/SiO_2$ vs. $SiC/SiO_2$                     | 80  |

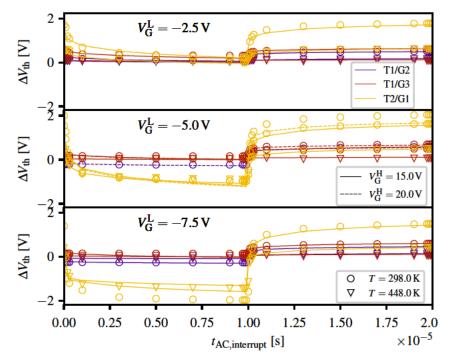

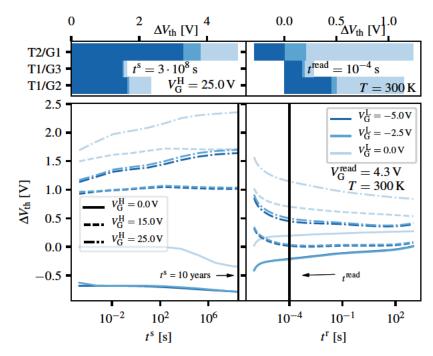

| 5.6  | Short term AC and long-term DC MSM data and simulation                            | 81  |

| 5.7  | Comparison of first points of all three DMOS AC stress sequences                  | 83  |

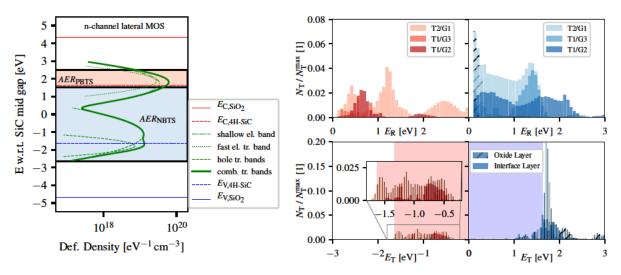

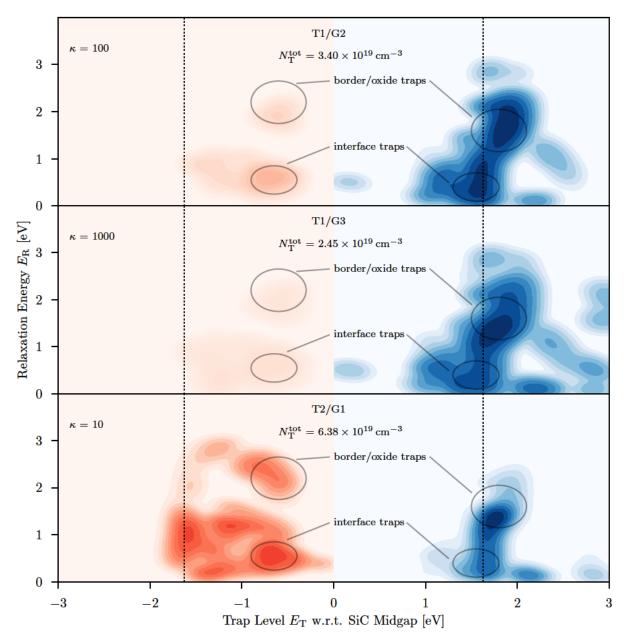

| 5.8  | Defect bands of lateral MOS and ESiD spectra of DMOS                              | 84  |

| 5.9  | CTLs of bulk SiO <sub>2</sub> , IL and bulk SiC defects                           | 85  |

| 5.10 | Trap level / relaxation energy maps of defects in different DMOS tech-            |     |

|      | nologies                                                                          | 86  |

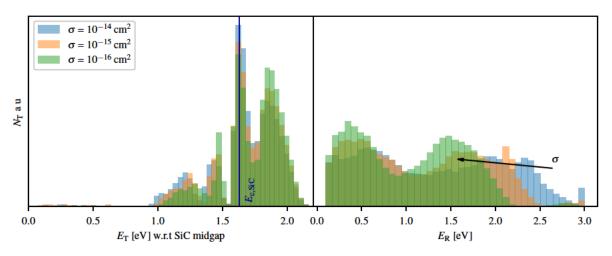

| 5.11 | Impact of the capture cross section on ESiD extraction                            | 87  |

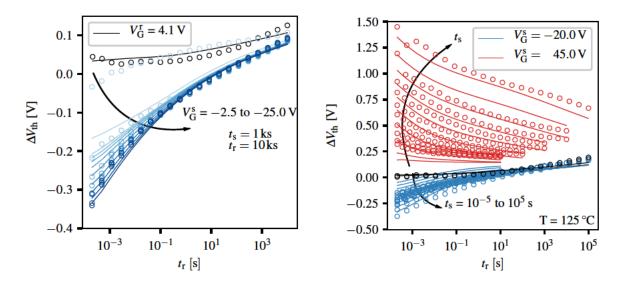

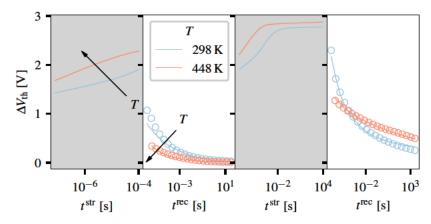

| 5.12 | Temperature activation of $\Delta V_{\text{th}}$ recovery                         | 88  |

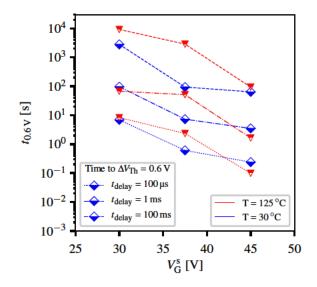

| 5.13 | Temperature and read-out delay dependence of $\Delta V_{\text{th}}$               | 88  |

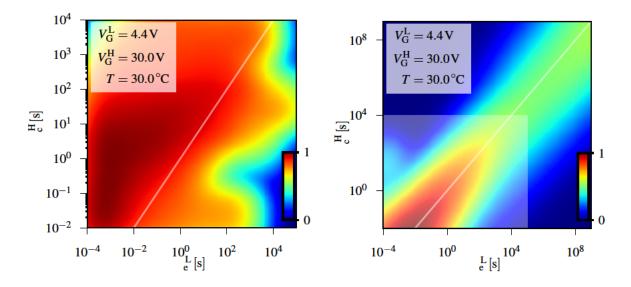

| 5.14 | Experimental and simulated CET maps of lateral MOSFETs                            | 89  |

| 5.15 | Unipolar and bipolar operation CET maps of DMOS                                   | 89  |

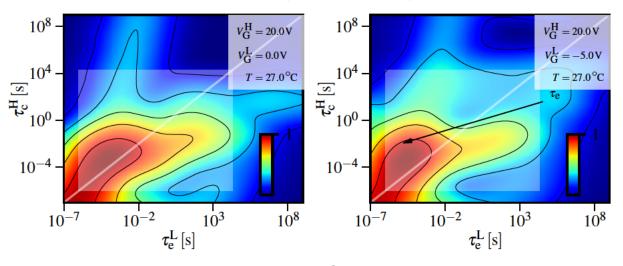

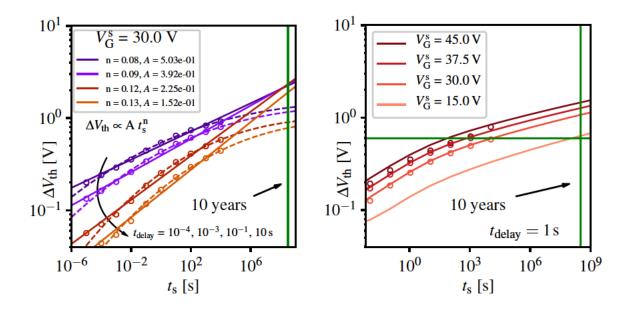

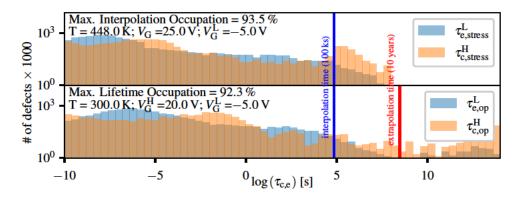

| 5.16 | Extrapolation via power-law versus physical model                                 | 90  |

| 5.17 | Time constant distribution for operation and stress conditions                    | 91  |

| 5.18 | Extrapolation of the threshold voltage shift after AC stress at different         |     |

|      | low bias levels                                                                   | 92  |

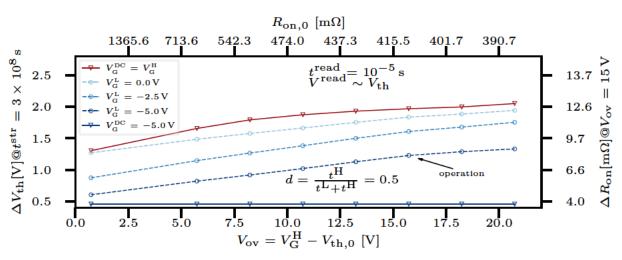

|      | Overdrive voltage dependence of $\Delta V_{\text{th}}$ and $\Delta R_{\text{on}}$ | 92  |

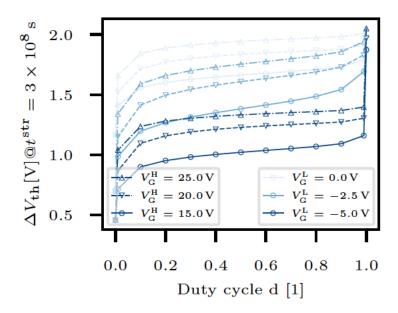

| 5.20 | Duty cycle dependence of $\Delta V_{\text{th}}$                                   | 93  |

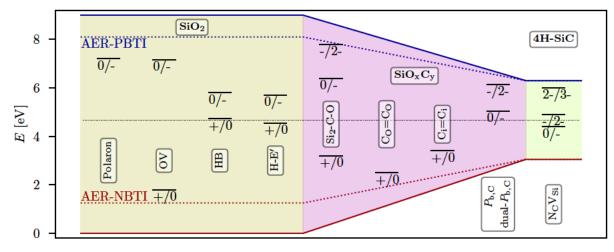

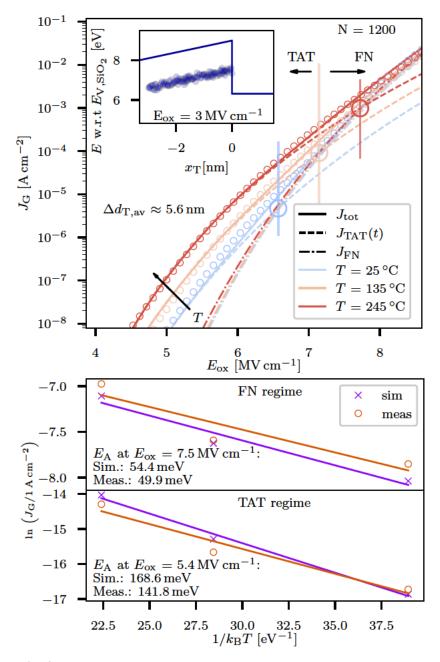

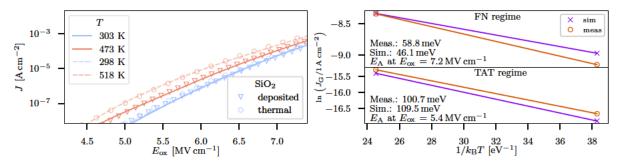

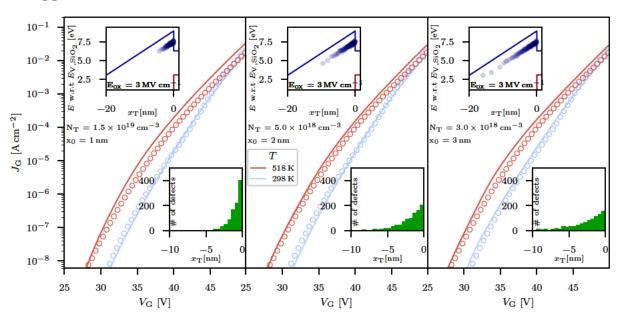

| 5.21 | Simulation versus measurement of tunneling currents in a SiC MOSCAP               | 95  |

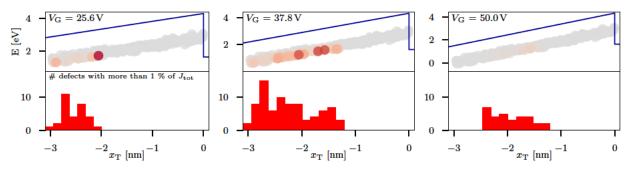

|      | Spatial distribution of current conduction via defects                            | 96  |

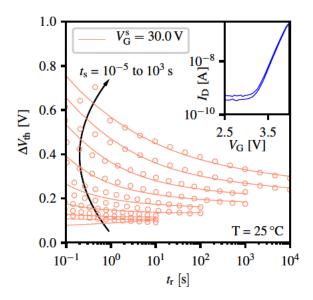

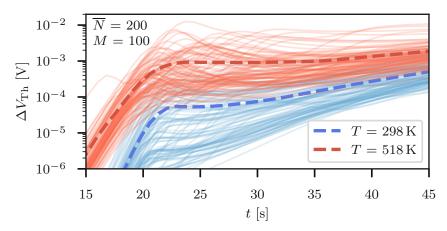

| 5.23 | Variation of transient threshold voltage shifts                                   | 97  |

|      | Comparison of tunneling currents in thermal and deposited oxides                  | 98  |

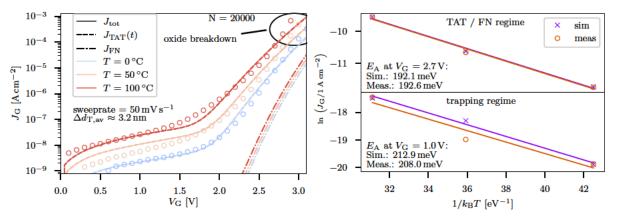

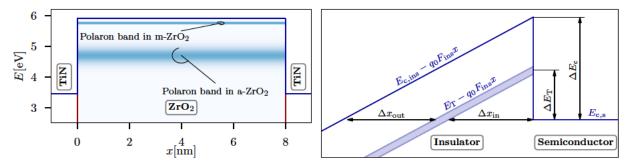

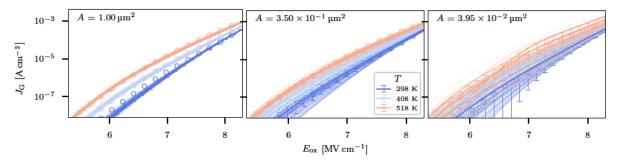

| 5.25 | Leakage currents in MIM capacitors based on $ZrO_2$                               | 99  |

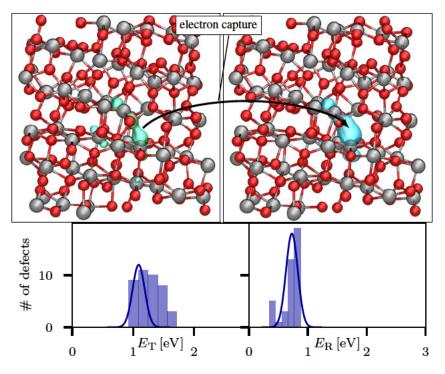

|      | Intrinsic electron trap parameters from DFT and Comphy simulation                 | 102 |

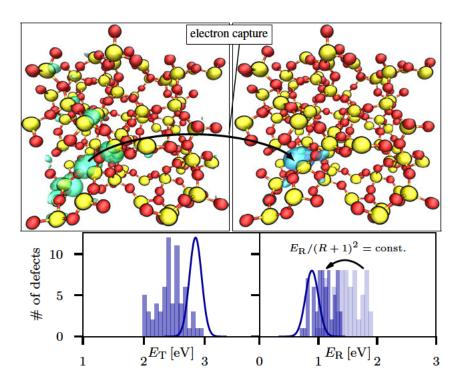

|      | ZrO <sub>2</sub> polaron parameters from DFT and Comphy simulation                | 103 |

|      | Generic requirements of defects for TAT                                           |     |

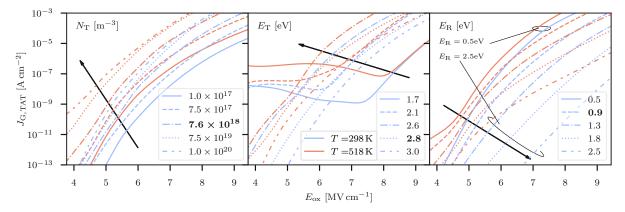

|      | NMP parameter variation impact on TAT currents                                    |     |

|      | Exponential spatial distributions                                                 |     |

|      | 0                                                                                 |     |

|      | Dominant percolation path details of MIM capacitors                               |     |

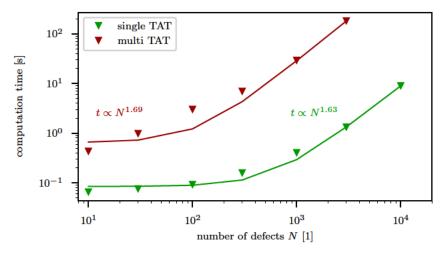

| 5.33 | TAT computation performance                                                       | 108 |

# **List of Tables**

| 1.1 | Comparison of power device substrate material parameters | • | • | • | • | 4   |

|-----|----------------------------------------------------------|---|---|---|---|-----|

| 4.1 | NMP defect parameters for multi-TAT evaluation           | • | • | • |   | 68  |

| 5.1 | 4H-SiC material parameters                               |   |   |   |   | 75  |

| 5.2 | Comphy insulator layer input quantities                  |   |   |   | • | 75  |

| 5.3 | Comphy grid parameters                                   | • | • | • | • | 75  |

| 5.4 | Defect parameters of lateral MOSFETs                     | • |   | • | • | 77  |

| 5.5 | Electrostatic parameters of SiC DMOS technologies        | • |   | • | • | 82  |

| 5.6 | Grid parameters for ESiD in SiC MOSFETs                  |   |   | • | • | 82  |

| 5.7 | NMP parameters of polarons in $SiO_2$                    |   |   | • | • | 97  |

| 5.8 | NMP parameters of polarons in $ZrO_2$                    | • | • | • | • | 100 |

|     |                                                          |   |   |   |   |     |

# List of Abbreviations

| AER  | Active Energy Region                        | MOS    | Metal Oxide Semiconductor              |

|------|---------------------------------------------|--------|----------------------------------------|

| BJT  | Bipolar Junction Transistor                 | MOSCAP | Metal Oxide Semiconductor Capacitor    |

| BTI  | Bias Temperature Instability                | MOSFET | Metal Oxide Semiconductor Field-Effect |

| CET  | Capture Emission Time                       |        | Transistor                             |

| CMOS | Complementary Metal Oxide                   | MSM    | Measure Stress Measure                 |

|      | Semiconductor                               | NMP    | Non-Radiative Multi-Phonon             |

| СР   | Charge Pumping                              | OTF    | On-The-Fly                             |

| CV   | Capacitance-Voltage                         | PDA    | Post Deposition Annealing              |

| DFT  | Density Functional Theory                   | PEC    | Potential Energy Curve                 |

| DPI  | Defect Probing Instrument                   | PES    | Potential Energy Surface               |

| DT   | Direct Tunneling                            | POA    | Post Oxidation Annealing               |

| DUT  | Device Under Test                           | RTN    | Random Telegraph Noise                 |

| EDMR | Electrically Detected Magnetic<br>Resonance | SiC    | Silicon Carbide                        |

| eMSM | extended Measure Stress Measure             | 4H-SiC | 4H-Silicon Carbide                     |

| EPR  | Electron Paramagnetic Resonance             | SILC   | Stress Induced Leakage Current         |

| ESiD | Effective Single Defect Decomposition       | SIMS   | Secondary Ion Mass Spectroscopy        |

| ESR  | Electron Spin Resonance                     | SNR    | Signal-to-Noise Ratio                  |

| FET  | Field-Effect Transistor                     | SRH    | Shockley-Read-Hall                     |

| FN   | Fowler Nordheim                             | TAT    | Trap-Assisted Tunneling                |

| HCD  | Hot Carrier Degradation                     | TCAD   | Technology Computer-Aided Design       |

| IGBT | Insulated Gate Bipolar Transistor           | TDDB   | Time-Dependent Dielectric Breakdown    |

| MEA  | Multi-Exponential Analysis                  | TDDS   | Time-Dependent Defect Spectroscopy     |

| MIM  | Metal Insulator Metal                       | WKB    | Wentzel-Kramers-Brillouin              |

| MIS  | Metal Insulator Semiconductor               | XPS    | X-ray Photoelectron Spectroscopy       |

## LIST OF ABBREVIATIONS

xviii

# Chapter 1 Introduction

The 2021 Intergovernmental Panel on Climate Change (IPCC) [1] report clearly states the urgent necessity to achieve a climate-neutral energy budget within the next decades. Hence, the ever-growing market of renewable energy production will further gain importance in the near future. Not only solutions for a carbon-free energy production but also approaches for a more efficient grid transport and therefore power conversion is among the highest priorities to meet the requirements of climate-neutrality with at the same time increasing power consumption. Electrical power conversion primarily requires a transformation of the voltage level and frequency, which is achieved by time-division of the input signal and transferring the energy into passive elements, e.g. an inductive coil on the output side. This signal partitioning requires an electrical switch, which is commonly realized by a Metal Oxide Semiconductor Field-Effect Transistor (MOSFET) or an Insulated Gate Bipolar Transistor (IGBT). Despite the significant improvements of the conversion efficiency that have been achieved in such devices based on silicon substrates, inevitable limits in the reduction of static and dynamic switching losses, as a consequence of the material properties of Si, have to be faced. These limits have been identified decades ago [2] and alternative substrate materials have attracted the attention of scientists and industry. These are so called wide-band gap semiconductors such as silicon carbide (SiC) and gallium nitride (GaN), that exhibit superior properties for power electronics to improve the conversion efficiency, have already made their way as substrate material into commercially available devices. Moreover, "exotic" substrate materials such as gallium oxide ( $Ga_2O_3$ ) or diamond (C) promise further improvement in terms of power conversion efficiency and may fully replace Si-based power switches in the near future.

## 1.1 MOSFETs in Power Conversion Applications

The growing importance of renewable energy in total power consumption, as shown in the left panel of Figure 1.1, requires high efficiency for converting the voltage and frequencies at the generation and/or consumer site, as for instance at locally installed photo voltaic (PV) panels, to those required for the power grid. The task of finding the

**Figure 1.1.** Electrical energy production (**left**) has more than doubled in the last 30 years, while renewable sources have increased their share of total energy production (data taken from [3]). Thus, advanced electronic systems become increasingly important. SiC MOSFETs when used as switches for power conversion circuits offer higher conversion efficiency (**right**), as a lower static on resistance can be achieved for a given voltage class, as shown for the third generation SiC DMOS technology of Cree Inc. [4] and for other SiC-DMOS and trench design SiC-MOSFETs (reproduced from [5]).

most suitable material for power conversion switches depends on many aspects of the application (e.g., voltage/power class, switching frequency) and eventually is limited by production costs, i.e. the economical feasibility of the production line that is used for the desired substrate material. Therefore, various materials and their impact on device properties have been studied in the past decades. A selection of the most important properties for power devices in general and those of SiC in particular are presented in the upcoming sections.

#### 1.1.1 Materials

The natural limit of the minimum static on-state losses of a power switch built from a semiconductor material is defined by the relation of the blocking voltage  $V_{\rm B}$ , that it is able to withstand, while at the same time sustaining a minimum (ideal) specific on-state resistance

$$R_{\rm on,sp} = \frac{4V_{\rm B}^2}{\varepsilon_s \mu_n E_{\rm C}^3}.$$

(1.1)

A comparison of the natural limits for Si and SiC substrates together with already available SiC MOSFET technologies that exceed the Si limit is presented in Figure 1.1.

By considering Baliga's figure of merit [6]

$$BFOM = \varepsilon_s \mu_n E_C^3 = \frac{4V_B^2}{R_{on,sp}},$$

(1.2)

which relies on the material parameters electrical permittivity  $\varepsilon_s$ , the electron mobility  $\mu_n$  and the critical field strength  $E_C$ , the static power handling capabilities of an ideal device employing different substrate materials can be compared. Additional to the static losses, in a switching mode device with area *A* the dynamic losses for a switching frequency *f* at gate bias  $V_G$  are added to the total conversion losses [2]

$$P_{\rm loss} = \underbrace{I^2 \frac{R_{\rm on,sp}}{A}}_{\rm static} + \underbrace{C_{\rm in,sp} A V_{\rm G}^2 f}_{\rm dynamic}$$

(1.3)

with the specific input capacitance  $C_{in,sp} = \varepsilon_s E_C / (2\sqrt{V_G V_B})$ . With these quantities Baliga defined a high frequency operating device figure of merit, termed Baligas high frequency figure of merit (BHFFOM), by [2]

$$BHFFOM = \frac{1}{R_{on,sp}C_{in,sp}}.$$

(1.4)

Johnson earlier formulated a FOM for the fundamental trade-off between a transition frequency within a channel length *L* and for a carrier saturation velocity  $v_{sat}$  with  $f_T = v_{sat} / (2\pi L)$  and the power handling capability defined by the breakdown voltage across the channel  $V_B = E_C L$  as [7]

$$JFOM = f_T V_B = \frac{v_{sat}}{2\pi E_C}.$$

(1.5)

Besides the electrical material properties, heat management plays an important role in order to operate the power switch in a feasible temperature regime. Therefore, Keyes defined a figure of merit as [8]

$$\text{KFOM} = \lambda \sqrt{\frac{cv_{\text{sat}}}{4\pi\varepsilon_s}} \tag{1.6}$$

with the specific thermal conductivity  $\lambda$  and the speed of light *c* to compare the heat dissipation limitations of the substrate material of power devices. Shenai *et. al* later proposed different thermal figures of merit depending on the heat dissipation coupling of the power device, rather than just taking bulk properties into account [9]. While Keys, Baligas, Johnsons and Shenais figures of merit mainly compare the bulk material properties of the substrate materials, Kim [12] tried to take the impact of the output capacitance in a conversion circuit with a certain input voltage into account to define a new high frequency figure of merit (NHFFOM) by extending the approach of Baliga [2]. Moreover, Huang [13] defined a figure of merit (HDFOM) for comparing unipolar

| Par.           | Si   | GaAs | SiC  | GaN  | β-Ga <sub>2</sub> O <sub>3</sub> [10] | C (diamond) | Unit                            |

|----------------|------|------|------|------|---------------------------------------|-------------|---------------------------------|

| ε <sub>r</sub> | 11.7 | 12.9 | 9.76 | 8.9  | 10                                    | 5.7         | 1                               |

| EG             | 1.12 | 1.42 | 3.26 | 3.39 | 4.85                                  | 5.5         | eV                              |

| E <sub>c</sub> | 0.3  | 0.4  | 1    | 4    | 8                                     | 10          | MV cm <sup>-1</sup>             |

| μ <sub>n</sub> | 1400 | 8500 | 900  | 1000 | 300                                   | 2000        | $V  cm^{-1}  s^{-1}$            |

| λ              | 1.5  | 0.55 | 3.7  | 2.1  | 0.2                                   | 6           | ${ m W}{ m cm}^{-1}{ m K}^{-1}$ |

Table 1.1. Comparison of relevant parameters for substrate materials considered in power conversion devices, also shown in Figure 1.2 (right). Si-based power MOSFETs are still widely manufactured, while SiC and GaN based devices steadily increase their market share in their respective voltage classes. Data taken from [10, 11].

switching devices based on the product of  $R_{on}$  and  $Q_{GD}$ , two quantities that can be obtained from measurements, assuming that the switching losses are dominated by the gate drain charge  $Q_{GD}$ . In the same work, also the Huang chip area FOM (HCAFOM) is defined as HCAFOM =  $\varepsilon \sqrt{\mu}E_c^2$ , whereby a higher FOM stands for less chip area necessary to sustain the same critical fields when conducting the same current density.

**Figure 1.2.** Figure of merits (**left**) and material properties (**right**) of different wide-band gap materials are compared. SiC and GaN as substrate materials offer advantages for applications in medium to high voltage and high frequency classes, respectively, and both have already been introduced in commercial devices. While novel materials such as  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> show record breaking FOMs, material processing is hindering their introduction in commercial devices, an aspect that is not taken into account by most FOMs. Note that for the spider diagram representation the FOMs and material properties have been normalized to the maximum value of each quantity (multiplied by a constant factor).

Most of the FOMs purely consider bulk material properties, as listed in Table 1.1 for mature conventional (Si, GaAs) and wide band-gap (SiC, GaN) as well as more exotic

semiconductor materials (C,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>), and do not take into account process-ability and properties arising from their compatibility to potential insulators. Apparently, SiC does not provide record breaking FOMs and also the bulk material properties are not exceeding those of e.g. GaN, except for heat conductivity, as shown in Figure 1.2. However, its ability to grow native SiO<sub>2</sub> and the availability of high quality substrates together with mature device processing techniques at reasonable cost outperforms GaN. Also, potential future candidates such as diamond within the medium to high blocking voltage class are far from large scale wafer level production at this point in time. For instance,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with its wider bandgap and higher critical field strength promises even better breakdown voltage to on-resistance ratio compared to both GaN and SiC. Therefore, it has been suggested as a suitable substrate material candidate for power devices within recent research works. However, p-doping of the material is particularly challenging due to the band-structure of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and has not been demonstrated yet [10]. With the largest bandgap and a high electron mobility as well as superior thermal conductivity, diamond is well suited for harsh conditions such as high temperatures and blocking voltages. However, the high chemical stability of the material leading to these properties poses severe challenges for device processing.

## 1.1.2 From MOSFETs to SiC Power Switches

A key step in the development of conventional MOSFETs has been the continuous improvement of the quality of the interface between the channel substrate material and the insulating layer. The electrically active "interface states" forming at the semiconductor-oxide transition region were the main reason that it took more than another three decades from Lilienfeld's discovery of the field effect [14] until the first working MOSFET was demonstrated [15]. Thus, bipolar junction transistors (BJT) were the first to be used for logic circuits. However, with the introduction of annealing process steps MOSFETs outperformed BJTs and stand today at the heart of almost every electronic application. The basic working principle of a MOSFET is to modulate the conductivity of a channel, i.e. the density of free minority charge carriers in a thin layer situated in between two contact regions with opposing doping concentration compared to the channel. These are termed source and drain contacts and the modulating terminal is known as gate contact. The "set-in" gate bias point for forming this inversion layer, which opens a percolation path between the source and drain terminals, is defined as the threshold voltage  $V_{\text{th}}$ . Interface traps and defects within the oxide in the vicinity of the channel, often referred to as near-interface traps (NITs) or border states, severely distort the device electrostatics and can lead to a drift of  $V_{\rm th}$  when charged. By passivation of the Si surface and the interface to its stable native oxide SiO<sub>2</sub>, stable device operation can be achieved which has led to the success of integrated Si/SiO<sub>2</sub> Complementary Metal Oxide Semiconductor (CMOS) processors.

An analogous development can be observed when looking at the history of the SiC MOSFET. Once SiC as bulk substrate material has been available in adequate quality for utilization in semiconductor devices in the 1990s [16, 17, 18], bipolar diodes were

available soon afterwards in 2001 [19]. However, it took almost another decade until the first commercially available SiC MOSFETs entered the semiconductor device market in 2010 [20]. Since then, SiC MOSFETs have gained significant market share in the sector for devices with 0.9 to 15 kV blocking voltage [4]. An important milestone for the sucess of Si-based MOSFETS has been the improvement of the Si/SiO<sub>2</sub> interface. Therefore, the interface properties have been studied over decades to optimize the interface carrier mobility and the threshold voltage stability by reducing the amount of electrically active defects, with e.g. forming gas anneals, in the vicinity of the channel. Such anneals have not shown to reduce the density of traps for SiC based MOSFETs with SiO<sub>2</sub> used as an insulator. Thus, efforts to reduce the defect densities have just recently been successful by improving the annealing process in nitrogen enriched ambient after oxide deposition [21]. Even though this led to a significant reduction of the SiC/SiO<sub>2</sub> interface defect densities, it is still the determining factor for power loss improvement, as scattering at the remaining interface and border states reduces the carrier mobility and thereby dominates *R*<sub>on</sub>. Thus, to date large efforts towards a more detailed understanding of the electrical properties of the defects at the interface region, such as presented within this work, have been made. Before discussing the reliability threats caused by defects in more detail, the bulk SiC properties and MOSFET device fabrication will be outlined in the next two sections.

## 1.1.3 Silicon Carbide Material Properties

Carborundum, as silicon carbide is termed natively, is stoichiometrically composed by an equal number of Si and C atoms. Among the various polytypes in which SiC can crystallize [22], the four layered hexagonal (4H-SiC) polytype has been instituted in commercially available SiC power-switches. In the notation of Ramsdell, the polytype is denoted by the number of Si-C bilayers within the unit cell, shown in Figure 1.3, and the crystal system (H for hexagonal), hence 4H-SiC. Due to its superior mobility and breakdown values, the 4H- has ousted the 6H-SiC polytype as substrate material for power MOSFETs [23]. Therefore, this polytype is referred to throughout this work, unless otherwise noted. The stacking sequence of SiC is shown together with crystal planes and translation vectors, which are technologically relevant for modern MOSFET architectures, in Figure 1.3. A 1/2 hexagonality can be seen for the 4H polytype, with half of the bilayers crystallyzing on hexagonal sites within the unit cell. The two lattice constants for the 4H crystal structure are given by  $a_0 = 3.0789$  Å,  $c_0 = 10.082$  Å. The covalent Si-C bond has a binding energy of  $E_b = 4.6$  eV, with a weak ionicity, as the valence electrons localize closer to the carbon atom (c.f. electro negativity: C: 2.5, Si: 1.8).

The electronic band structure of 4H-SiC exhibits an indirect bandgap of 3.26 eV [26] at room temperature from the  $\Gamma$  (top valence band) to M (minimum conduction band) point and features  $M_c$  = 3 conduction band minima within the first Brillouin-zone. The temperature dependence of the bandgap due to thermal expansion can be described by

**Figure 1.3.** Unit cell of 4H-SiC (**left**) with equal number of C (brown) and Si (blue) atoms, reproduced from [24, 25], is shown together with technologically relevant crystal planes in SiC MOSFETs and translation vectors (**right**). Note the Si-face (0001)-plane is typically the terminating surface in lateral and the a-face ( $11\overline{2}0$ )-plane in vertical MOSFETs.

the Varshni model [27]

$$E_{\rm G}(T) = E_{\rm G}(0) - \frac{\alpha T^2}{T + \beta}$$

(1.7)

with  $\alpha = 3.5 \times 10^{-4} \,\text{eV}\,\text{K}^{-1}$ ,  $\beta = 1.1 \times 10^3 \,\text{K}$  and  $E_{\text{G}}(0) = 3.285 \,\text{eV}$  [28, 29].

Due to the hexagonal crystal structure, the effective masses in the perpendicular and parallel planes to the c-axis exhibit a strong anisotropy. The parallel electron effective mass measured by cyclotron resonance is given by  $m_{\parallel} = 0.31m_0$ , while the perpendicular mass is given by  $m_{\perp} = \sqrt{m_{\rm MF}m_{\rm MK}} = 0.48m_0$ . Hole effective masses were extracted with  $m_{\parallel} = 1.75m_0$  and  $m_{\perp} = 0.66m_0$  [30, 31]. By applying the concept of density of states (DOS) effective masses for electrons and holes  $m_{\rm de,dh}^*$ , the effective DOS in conduction and valence band is given by [32]

$$N_{\rm C} = 2M_{\rm C} \left(\frac{m_{\rm de}^* kT}{2\pi\hbar^2}\right)^{3/2} \tag{1.8}$$

$$N_{\rm V} = 2 \left(\frac{m_{\rm dh}^* kT}{2\pi\hbar^2}\right)^{3/2}.$$

(1.9)

As the calculated effective DOS is not exactly proportional to  $T^{3/2}$ , the effective masses need to be modeled as temperature dependent too. The thermal DOS effective masses

calculated by using the  $k \cdot p$  method [33] have been fitted with polynomials [34]

$$m_{\rm de}^*(T) / m_0 = m_{\rm de}^*(0) + a_{\rm e}T + b_{\rm e}T^2 + c_{\rm e}T^3 + d_{\rm e}T^4$$

(1.10)

$$m_{\rm dh}^*(T) / m_0 = \frac{1 + a_{\rm h}T + b_{\rm h}T^2 + c_{\rm h}T^3 + d_{\rm h}T^4}{1 + e_{\rm h}T + f_{\rm h}T^2 + g_{\rm h}T^3 + h_{\rm h}T^4}$$

(1.11)

for the application in device simulations.

Moreover, the carrier mobilities show anisotropic values parallel and perpendicular to the c-axis, with about 20 % higher mobilities in the parallel direction. Note that at room temperature ionized impurity scattering is the limiting mechanism for mobility in bulk SiC and can be described by the Caughey-Thomas equation [35]

$$\mu_{e,h} = \frac{\mu_{0,e,h}}{1 + \left(\frac{N_{\rm D} + N_{\rm A}}{N_{e\,h}}\right)^{l_{e,h}}}$$

(1.12)

with  $\mu_{0,e} = 1020 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $\mu_{0,h} = 118 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ,  $N_e = 1.8 \times 10^{17} \text{ cm}^{-3}$ ,  $N_e = 2.2 \times 10^{18} \text{ cm}^{-3}$  and the doping ratio exponents  $l_e = 0.6$  and  $l_h = 0.7$ . Note that these values are given for high purity SiC grown by epitaxy and will be decreased in bulk SiC grown by sublimation due to scattering at the increased numbers of point and stacking defects. At higher temperatures the acoustic phonon and inter-valley scattering become the dominant scattering mechanisms and the doping concentration dependence of the mobilities decreases.

#### 1.1.4 Fabrication and Properties of SiC MOSFETs

A first step for the successful fabrication of commercially available SiC MOSFETs was the production of largely defect free SiC substrate wafers. A solution growth of large area bulk SiC ingots, which is the standard technique used for Si wafer production, imposes many challenges such as low solubility of C even at large temperature. Additionally, a high pressure (e.g. 100 bar) under inert Ar conditions is required and the reaction of the melt with the graphite crucible can not fully be omitted, which requires the development of other wafer production methods. Seeded-sublimation growth has been established to grow bulk ingots making reasonable quality SiC wafers of up to 150 mm diameter available. In this boule growth method, sintered poly-crystalline SiC is typically sublimed within a graphite crucible. The sublimed source species then move towards a seed crystal of the intended poly-type with high crystalline quality, due to a defined temperature gradient within the crucible. A surface reaction and crystallization step at the lower temperature seed crystal leads to the desired controlled poly-type crystal growth. The crucible is thereby heated to  $T \approx 2300$  to 2400 °C, while the seed temperature is about 100 °C lower. Exact process control is required during crystal growth as defect formation energies for stacking, dislocation, and point defects are relatively low for the desired 4H-SiC polytype. Inert gas is introduced during the crystal growth to minimize impurity incorporation and by consideration of reaction kinetics

and thermodynamics, performance-limiting defects in the bulk SiC have been significantly reduced in the past [36, 37]. However, to achieve the required crystal quality, i.e. defect free poly-type preserved grown SiC with controlled doping and thickness, homoepitaxy has become an essential growth technique for the production of SiC devices that can compete with their Si-based counterparts. The lightly doped drift layer on top of the heavy doped substrate used as the drain contact is grown by chemical vapor deposition (CVD) technique employing silane (SiH<sub>4</sub>) and propane ( $C_3H_8$ ) or ethylene ( $C_2H_4$ ) as precursors. The employment of a 4° off-axis angle on the substrate allows to perfectly rebuild the required stacking sequences of the hexagonal polytypes [38, 39].

With high quality substrates available, the most important process steps for the production of MOSFETs on SiC substrates are outlined further. High energy ion-implantation is used to form doping regions of n- and p-type conductivity, as a diffusion process is not applicable due to the significantly smaller diffusion constants of dopands within SiC [40] compared to Si. After the implantation, the damaged rough SiC surface is typically carbonized forming a carbon cap for subsequent mass production steps [41]. High-temperature post-implantation anneals are required for higher dose implantation for successful lattice recovery and doping activation. Aluminum is typically used as p-type dopand, while Phosphorus or Nitrogen are used for n-type doping. Al incorporates into the SiC lattice either on a hexagonal or cubic Si site with ionization energy  $E_A \approx 200 \text{ meV}$ , which results in only a fraction of dopands ionized even at room temperature. With  $E_D \approx 60 \text{ meV}$  for both, P substituting a Si on a cubic site and N for C on a hexagonal site, these dopands can be considered ionized at room temperature at low concentration (i.e.  $< 10^{16} \text{ cm}^{-3}$ ). The fraction of ionized dopands is given by

$$N_{\rm D}^{+} = \frac{N_{\rm D}}{1 + g_{\rm D} \exp\left(\frac{E_{\rm D} - E_{\rm F}}{k_{\rm B}T}\right)} \tag{1.13}$$

$$N_{\rm A}^{-} = \frac{N_{\rm A}}{1 + g_{\rm A} \exp\left(\frac{E_{\rm F} - E_{\rm A}}{k_{\rm B}T}\right)}.$$

(1.14)

with the degeneracy factors  $g_{A,D}$  determined by the band-structure of the host material and the Fermi level  $E_{F}$ .  $N_{A,D}$  denote the maximum electrically active doping concentration, i.e. the concentration of the fully ionized dopands.

A major advantage above other compounds, e.g. GaN, is that SiC can be thermally oxidized to form a high quality oxide, i.e.  $SiO_2$ , for MOS devices and a passivation layer for SiC surfaces. The dry oxidation process is described by the reaction

$$2SiC + 3O_2 \rightarrow 2SiO_2 + 2CO. \tag{1.15}$$

A similar amount of bulk SiC as for Si, namely 46 %, is consumed for the SiO<sub>2</sub> growth, i.e. 10 nm SiO<sub>2</sub> are grown by consuming 4.6 nm SiC. It has to be mentioned that a dry thermal oxidation of SiC is time consuming and it takes more than 6 h to grow a 50 nm thick SiO<sub>2</sub> layer, as typically required for power switches, on the (0001)-terminated face at T = 1150 °C [42]. The oxidation process is strongly anisotropic and about ten times

faster on the a-face surface at the same *T* when compared to the oxidation of Si-face surfaces. This implies also strong oxide thickness variation along a trench MOSFET, i.e. smallest thickness on top and bottom of the trench and thicker at the sidewalls. Besides the strong anisotropy in growing rate at different surfaces, dry thermal growth leads to increased carbon incorporation at the interface as O<sub>2</sub> in-diffusion and CO out-diffusion are reported to be the rate limiting mechanisms in thick SiO<sub>2</sub> layers [42]. Oxide growth via atomic layer deposition (ALD) can resolve the anisotropy problem and additionally increases the interface stability [43]. However, it is an unfeasible process step for economic power device processing due to the long duration required to grow thick oxides. Therefore, the oxide deposition via a low-pressure chemical vapor deposition (LPCVD) employing tetra-ethyl-ortho-silicate (TEOS) as a precursor [44, 45] offers an alternative with the additional benefit of a reduced thermal budget at the gate stack.

However, as is the case for silicon MOSFETs, the interfacial strain and stoichiometric disorder at the transition region to the bulk amorphous oxide leads to electrically active unsaturated dangling bonds, e.g.  $P_{b,0}$ -centers for Si/SiO<sub>2</sub>. In Si-MOSFETs, these defects are passivated by a forming gas (H<sub>2</sub>) ambient annealing process step, thereby reducing the number of interface traps from  $D_{it} \approx 10^{13} \text{ cm}^{-2} \text{ eV}^{-1}$  [46] to  $D_{it} < 10^{10} \text{ cm}^{-2} \text{ eV}^{-1}$  [47]. Unlike for Si surfaces and the Si/SiO<sub>2</sub> interface, hydrogen passivation has not shown to significantly reduce the interface trap density for SiC/SiO<sub>2</sub> MOS structures [48]. Only the implementation of a Post Oxidation Annealing (POA) or Post Deposition Annealing (PDA) step in nitrogen enriched ambient has lead to a sufficient reduction of interface traps at the SiC/SiO<sub>2</sub> transition region and enough stability for surface passivation [20]. Typically, nitridation of the interface can be achieved in ambients containing nitrous oxide NO<sub>2</sub>, nitric oxide NO or ammonia NH<sub>3</sub> at temperatures of above 1300 K. However, even with years of POA and PDA optimization, the  $D_{it} \approx 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$  observed in SiC MOSFETs is still two orders of magnitude higher than in Si-technologies.

The high interface trap density also dominates the channel electron mobility due to electron scattering at these charged defects. In bulk 4H-SiC the dominant scattering mechanisms are acoustic and intervalley scattering for lightly doped ( $N_D = 3.5 \times 10^{15} \text{ cm}^{-3}$ ) regions. For increased doping densities of  $N_D = 7.5 \times 10^{17} \text{ cm}^{-3}$ , as approximately used for channel doping concentrations, neutral impurity and invervalley scattering dominate at room temperature and above, resulting in an electron mobility of about  $\mu_e \approx 400 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at room temperature, as extracted by Hall measurements and theoretical calculations [49]. This value decreases to about  $50 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  at a temperature of 100 K. However, as shown in Figure 1.4, when extracting mobility values from  $I_D(V_G)$  characteristics at different temperatures for lateral (Si-face) MOSFETs, an opposing trend is observed, with increasing Ghibaudo mobilities [50] for higher *T* at significantly smaller absolute values. This behavior can mainly be explained by reduced Coulomb scattering at higher *T*, due to less interface charge trapped [51]. Also, a strong correlation of the reduced mobility with large interface trap densities has been extracted

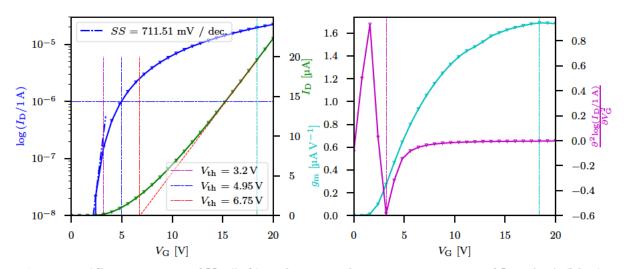

**Figure 1.4.**  $I_D(V_G)$  characteristics for lateral Si-face (0001) n-MOSFETs with L=8 µm, W=100 µm and  $d_{ox} = 70$  nm gate oxide with NO-POA for varying temperature in the range of 100 to 600 K (left). The channel mobilities (top, right) are extracted by the method of Ghibaudo [50] and with the effective mobility equation [23]. The threshold voltage is extracted by a constant current method and the maximum  $g_m$  method (bottom, right).

on different SiC surface termination planes at the interface to  $SiO_2$  [23]. Thus, it has been revealed that the a-face surface shows larger mobilities compared to the Si-face, due to reduced interface trap densities close to the SiC conduction band edge [52]. Therefore, UMOSFET (or trench) architectures with a vertical channel along the a-face crystal plane, contrary to DMOSFETs with channel planes along the Si-face as shown in Figure 1.5, have been introduced by manufacturers recently.

Additionally, channel counter doping by donor incorporation (for n-channel MOS-FETs) has been studied extensively, with e.g. N, P, Sb and Ba incorporated in a thin layer at the SiC/SiO<sub>2</sub> interface [53, 54]. The effect of these thin counter-doping layers is a electrostatic potential screening that leads to smaller field strengths required to build up the same inversion layer carrier density and also less surface scattering. In turn, higher low field channel mobilities can be observed, with diminishing effect at higher fields [53].

## **1.2 Reliability of MOSFETs**

As outlined in the previous section, the introduction of the forming gas anneal has established a process step to enable the passivation of the majority of interface defects between bulk Si and amorphous  $SiO_2$  (a- $SiO_2$ ), allowing the fabrication of highly stable MOSFETs. However, with the continuous down-scaling of CMOS transistors to

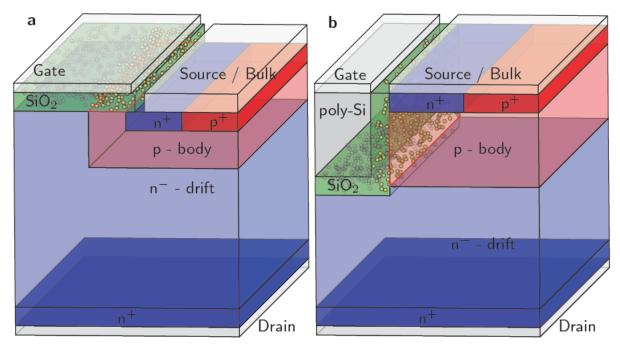

**Figure 1.5.** Sections of a DMOSFET (a) and an UMOSFET (b) are shown with cuts along the vertical symmetry axis of the devices. A tens of nm thick oxide is deposited on the trench sidewalls. The channel surface area along the SiC (0112) plane in the trench case and along the (0001) plane in the DMOSFET case are highlighted in red. While highest channel mobility values are reported along the vertical interface orientation, charge trapped at interface and bulk-oxide defects, schematically indicated by yellow balls, severely reduce channel mobility compared to bulk values at both surfaces. In order to simplify the device representations, details such as passivation doping and correct aspect ratios are spared out.

a few nanometer channel length and only a small number of atomic layers thin gate dielectrics, the impact of charges captured at single electrically active defects located in the vicinity of the channel has become more pronounced. Due to the perturbation of the electrostatics upon charge capture, a single defect can eventually lead to failure of a MOSFET. The device parameter alteration effects due to these charge trapping events are summarised under the term Bias Temperature Instability (BTI). Next to BTI, enhanced electric field strengths in the lateral channel direction from the source to drain contact can lead to breakage of previously passivated dangling bonds. This bond breakage is a result of carriers with high kinetic energies scattering at the interface region, thereby creating defect states which then can capture and emit charge. Thus, the mechanism is referred to as Hot Carrier Degradation (HCD). Also, the effect of carriers tunneling through the insulating layer via hopping at pre-existing oxide defects, termed Trap-Assisted Tunneling (TAT) leads to enhanced leakage current resulting in additional power losses. Furthermore, as a consequence of TAT, defects within the bulk oxide can be created or high energetic carriers multiply due to impact ionization at large stress oxide field strengths. These additional leakage current following from these events are referred to as Stress Induced Leakage Current (SILC) and eventually lead to oxide breakdown. This failure mechanism is typically characterized by TimeDependent Dielectric Breakdown (TDDB) experiments. In the following, the role of BTI, gate leakage currents and HCD on the reliability of MOSFETs will be briefly outlined and the state of the art of research on these topics will be discussed.

#### **1.2.1** Bias Temperature Instabilities

The alteration of the characteristic parameters of a MOSFET, e.g. flat band voltage  $V_{\text{fb}}$ , threshold voltage  $V_{\text{th}}$ , carrier mobility  $\mu$  and sub-threshold slope *SS*, is known to be accelerated by enhanced temperature and gate bias stress. Therefore, these deviation phenomena have been collected under the term Bias Temperature Instability (BTI) [55]. BTI has been first described in the late 1960s by Miura *et. al* [56]. The stabilization of silicon surfaces [57] was the main research focus at that time, and the first BTI characterization attempts have been related to the mechanisms of ion impurity diffusion and thermally assisted tunneling [58, 59]. The main features observed were the power-law like development of the shifts of the threshold voltage based on empirical parameters, i.e. a time exponent *n* of about 0.2, thermal activation with activation energies up to 0.2 eV and voltage acceleration with exponents *m* in the range of 2 to 3 [60, 61]. Based on these observations, an expression for  $\Delta V_{\text{th}}$  was given by [60]

$$\Delta V_{\rm th}\left(t, V_{\rm G}, T\right) = A t^n V_{\rm G}^m e^{\frac{L_{\rm A}}{k_{\rm B}T}} \tag{1.16}$$

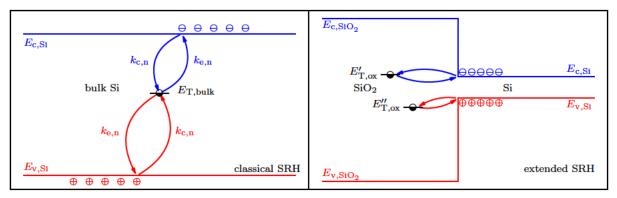

with a constant prefactor A and the activation energy  $E_A$  as fitting parameters. This method is easy to apply and is therefore still widely used, however, it fails to connect the degradation with the underlying physical mechanisms and additionally implies an infinite degradation trend because no saturation of the  $\Delta V_{\rm th}$  is considered. Moreover, the expression was derived from observations of negative BTI (NBTI) in Si-based pMOSFETs and cannot be generally applied to positive BTI (PBTI) or BTI observations on different technologies. For example, if more than one dominating trapping mechanism is prevalent, different slopes for the time evolution of  $\Delta V_{\rm th}$  may be observed which cannot be captured by this simple model. Therefore, in the past decades more sophisticated models have been developed to describe the underlying physical mechanisms more accurately. Heiman et. al connected threshold voltage shifts in Metal Oxide Semiconductor Capacitor (MOSCAP)s to charge trapped in the oxide [62], applying a Shockley and Read like kinetic statistics [63]. This modeling approach, however, only considers elastic tunneling of charge carriers from the channel to the defect. From the 1970s on, also reaction and diffusion limited regimes of the NBTI degradation were frequently proposed to originate the effect [64, 65]. In the latest version of this model, interface defect creation at high oxide field strengths has been proposed. This stems from hydrogen that is released causing additional dangling bonds at the interface (reaction), followed by hydrogen diffusion and accumulation in the oxide (diffusion) [66]. Since direct release of hydrogen is energetically unfavorable, a more realistic approach supported by DFT calculations suggests the release of hydrogen from a reservoir, e.g. dopands in the Si substrate, which can then lead to depassivation of the interfacial Si-H bonds [67].

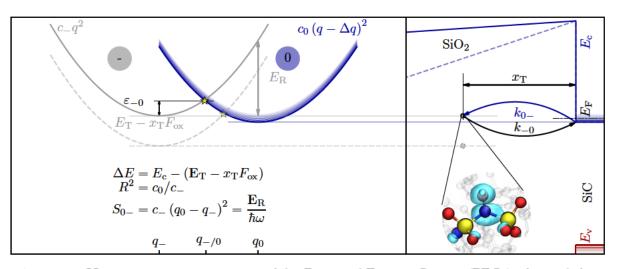

After correlating 1/f noise with discrete RTN signals in small area MOSFETs as discovered by Ralls *et. al* [68], a different approach to a reaction-diffusion model was presented by Kirton and Uren, who modeled the single defect charge transitions in the context of the Non-Radiative Multi-Phonon (NMP) framework [69, 70]. Tewksbury later first modeled threshold voltage shifts in MOSFETs applying the NMP theory to charge transitions involving oxide defects [71, 72]. Both, RTN and  $V_{\text{th}}$  shifts are therein explained by an inelastic tunneling process at pre-existing oxide defects. It took more than another decade until Grasser's two stage model [73] based on [74] was the first attempt to model both, a recoverable and a permanent component of BTI as observed in Si/SiO<sub>2</sub> systems. The recoverable part (stage 1) is explained by the formation of E'-centers from oxygen vacancies which can be charged and discharged. The permanent part (stage 2) is described with a 3-state model and caused by the de-passivation of P<sub>b,0</sub>-centers triggered by charged E'-centers.

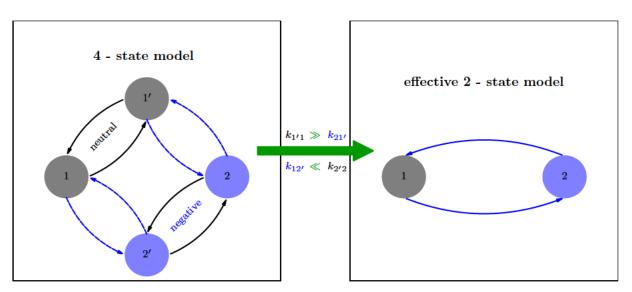

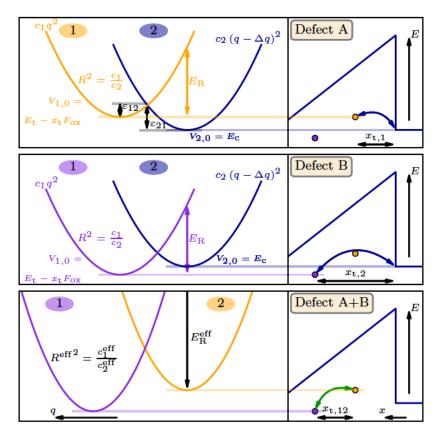

Further experimental observations on charge capture and emission events of single defects in small area devices such as Time-Dependent Defect Spectroscopy (TDDS) [75] studies and Random Telegraph Noise (RTN) [76] measurements initiated the refinement towards a four-state defect model for the recoverable component, which is able to explain both single charge transfer events in small area and the superposition of such in a defect ensemble in large area devices [77, 78]. This extension allowed for the description of phenomena like fixed/switching traps [79], and anomalous, temporary and reversal RTN [80]. The explanation of such details in RTN, i.e. charge trapping kinetics at a single defect, requires the existence of meta-stable defect states, which has been shown to be consistent with ab-initio studies for a number of suspected defect candidates [81]. Therefore, besides charge trapping is still not accepted as the unique mechanism causing BTI [82], the NMP model has provided deep physical insight into charge trapping as the origin of BTI.

BTI on SiC power MOSFETs has been characterized early after the development of wide-bandgap devices, with a focus on the time-dependence after bias-stress [83, 84] and its temperature dependence [85]. These works mainly extracted  $\Delta V_{\text{th}}$  after bias stress as a function of the stress time by evaluating the  $V_{\text{th}}$  based on post stress  $I_D(V_G)$ measurements, thereby acknowledging the strong read-out time dependence of  $V_{\text{th}}$  after a stress phase within in their measurements. Later Okayama *et. al* [86] discovered an accelerated recovery when negative bias stress is applied after a positive stress phase. This mechanism can be explained by reduced emission times of previously trapped electrons during the negative bias phase. Reduced  $\Delta V_{\text{th}}$  was also observed at elevated T, speculating that this effect evolves from ion diffusion [85], thereby neglecting the possibility of accelerated recovery at higher T [87]. The role of nitrogen passivation in NO containing ambient leading to an improved interface stability, i.e. less electron charge trapping, has been also studied [88] and the first structural defect candidates, i.e. interface states with more than 0.6 eV below the SiC conduction band together with nitrogen related defects and oxygen vacancies, have been proposed [89]. Switching bias stress experiments for equal positive and negative bias revealed negative  $V_{\rm th}$ shifts and therefore higher stability of trapped holes compared to a unipolar bias stress [90]. While comparisons between BTI in Si and SiC MOSFET are drawn frequently and might be valid due to the same nature of oxide defects [CSC1, CSC2], it was also emphasized that the interpretation of BTI measurements with state-of-the-art characterization methods developed for Si MOSFETs can be misleading [91, 92, CSJ1] when applied to SiC MOSFETs due to the wide distribution of the defect capture and emission time constants. Puschkarsky et. al conducted detailed BTI experiments under AC and DC gate bias stress, revealing accelerated temperature recovery [93] leading to seemingly less degradation at increased *T*. Furthermore, an accurate model to reproduce the extracted charge trapping kinetics with activation energy maps has been demonstrated [94, 87]. Additionally, recently a frequency independent switching cycle dependence of  $\Delta V_{\text{th}}$  at bipolar gate bias operation in trench MOSFETs has been reported [95, 96, 97], however, not been explained by a physical mechanism. Note that a similar effect has been noticed in Si-based MOS devices employing SiO<sub>2</sub> as an insulator before and has been explained by the gate-sided hydrogen release model [98, 99].

Besides the detailed experimental studies conducted to characterize BTI in SiC MOSFETs for more than a decade, a physical defect-centric modeling approach to consistently describe the charge trapping mechanisms at the device level has not been presented so far. This gap from experimental observation to device modeling with defect bands that can be compared to parameters obtained by ab-initio methods from defect candidates is aimed to be narrowed down within this thesis [CSC1, CSJ2, CSC3].

#### 1.2.2 Gate Leakage Currents and Oxide Breakdown

The charge blocking capability under electric fields of an ideal insulator within a MOSFET is intrinsically limited by its band offsets, i.e. the energetic barriers defined by the conduction and valence band edges of the substrate to those of the insulator, as well as the thickness of the dielectric layer. With ongoing scaling of insulators in CMOS technology Fowler Nordheim (FN) and direct tunneling (DT) currents, a result of charge carriers being able to tunnel through the energetic barrier given by the insulator, lead to detrimental on- and off-state losses. This intrinsic limitation can further be decreased by the presence of charge traps in real devices. Next to the capture of charge in the oxide and the resulting perturbation of the electrostatics across the MOS structure (c.f. BTI), defects in the insulator can also act as charge transition centers between the channel and the gate electrode. This so-called Trap-Assisted Tunneling (TAT) emerges from the same inelastic charge tunneling mechanism as in the case of BTI as will be outlined in the following.

Conduction via defects within the band gap of a semiconductor material acting as transition or recombination centers have been early studied and described by Mott [100]. The modeling efforts have later been extended by Miller and Abrahams to describe charge hopping in doped crystalline semiconductors [101]. While these early modeling

approaches considered purely elastic tunneling processes, Schenk *et. al* developed a model for defect with deep trap levels to band transitions accompanied by a multiphonon relaxation [102], which was later extended by Herrmann *et. al* to model leakage currents through MOSFETs used for memory applications [103]. This model represents to date the core of most TAT modeling approaches based on NMP theory [104, 105, 106, 107]. Later, the TAT model of Schenk *et. al* has been further refined and extended to model thermally activated leakage currents through high- $\kappa$  dielectrics used in MOSFETs by the group of Larcher [108, 109, 110, 111]. It should also be noted that a full quantum mechanical description of TAT currents within the NMP theory, as presented e.g. in [112, 113, 114], is most rigorous and necessary at for instance cryogenic temperatures [115]. However, its application on a device level simulation is often prohibitively expensive due to its large computational cost and often not necessary within the typical device operating temperature range, as will be discussed in Chapter 4.

In SiC MOS structures, thermally activated gate leakage currents below the FN regime have been observed recently [116, 117, 118] and were suspected to be trapassisted with further conduction to the insulator conduction band [119, 120]. Thereby, a "sweet spot" of a defect band in spatial and energetic dimension enables this current conduction via traps. A close investigation of this hypothesis by physical modeling of these charge transitions will be presented within this thesis.

Increased FN, DT, and TAT currents at high stress oxide fields can further lead to defect creation by high energetic carriers, e.g. impact ionization [121] within the oxide. The resulting increased defect density following the oxide field stress further exaggerates gate leakage currents, hence termed Stress Induced Leakage Current (SILC) [122, 123]. It was already discovered in the 1980s that the resulting current was caused by thermally assisted tunneling from the channel to newly created defects [124, 125, 126]. Thereafter, the ongoing oxide degeneration eventually leads to a breakdown of the insulating capability by forming permanently conducting filaments, which is typically characterized by transient current measurements at increased bias and temperature stress within the TDDB method. Already in 1973, defect creation was suggested to be the responsible mechanism for TDDB, with a distinct oxide thickness dependence, predicting a stronger impact for thinner oxides [127]. While modeling attempts have focused on impact ionization for both SILC and TDDB [128, 129], the structural reconfiguration of defects could also explain the formation of leakage paths in the oxide and was able to explain correlation of single steps in gate tunneling currents and drain currents [130].

## 1.2.3 Hot Carrier Degradation

Contrary to BTI, the more permanent device parameter ( $V_{\text{th}}$ ,  $\mu$ , SS) alteration due to HCD is attributed to defect creation at the Si/SiO<sub>2</sub> interface in Si-based MOSFETs. While the effects of BTI are extracted at high gate and low drain bias, which leads to a uniform oxide field distribution and low energetic carriers across the lateral MOSFET channel coordinate, HCD is typically characterized at the high drain bias and low gate bias regime, as shown in Figure 1.6. In this regime highly energetic, hence termed

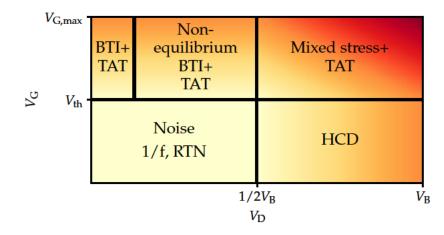

**Figure 1.6.** The different reliability mechanisms are shown for their relevance over the  $V_{\rm G}$  and  $V_{\rm D}$  regimes. Contrary to BTI which is typically studied for small  $V_{\rm D}$  and enhanced  $V_{\rm G}$ , HCD is observed at the opposite bias regimes, i.e. small  $V_{\rm G}$  at large  $V_{\rm D}$ . For both, small  $V_{\rm G}$  and  $V_{\rm D}$ , it is possible to characterize RTN in small area, and 1/f noise in large area devices, respectively. A mix of HCD and BTI is observed if both terminal biases are increased above their nominal operation values. Figure adapted from [131].

"hot" carriers, can exchange energy with the surrounding heat bath, i.e. excite certain phonon modes, which in turn can lead to the breakage of the Si-H passivation bond at the interface and therefore the creation of electrically active amphoteric dangling bond defects, the so called  $P_{b,0}$ -centers. As has been shown by Jech *et. al*, utilizing ab-initio calculations, this process needs to overcome high energetic barriers and thus can be explained by a resonant phonon mode excitation caused by non-equilibrium energetic carriers [132]. Also, the effect of high energetic non-equilibrium carriers in the interaction with oxide defects at BTI stress conditions has been investigated, resulting in a unified parameter free model for both BTI and HCD (mixed-mode) regimes [131]. The work of Jech *et. al* emphasized the importance of considering HCD and BTI for an accurate description of the Si/SiO<sub>2</sub> MOSFET degradation over typical device lifetimes.

While the impact of HCD in Si-based MOSFETs on device degradation is undisputed, only little attention has been paid to this effect in SiC MOSFETs. First studies on the effect of HCD stress in SiC MOSFETs revealed changes in the photon emission spectra of the investigated devices [133]. However, it was not possible to extract small relative changes of interface defect densities at already large absolute levels with electrical measurements after HCD stress. With the introduction of more stable NO annealed devices, a significant change of defect densities was observed after HCD stress by performing Charge Pumping (CP) measurements [134]. A clear identification of a defect candidate at the interface such as the  $P_{b,0}$ -center in Si/SiO<sub>2</sub> MOS structures or  $K_N$  at the insulator/Si interface of SiON devices [135] was not possible by Electrically Detected Magnetic Resonance (EDMR) measurements [136]. However, an N related defect was suggested to be responsible for the observed increase in the EDMR signal following hot-carrier stress. Determination of the HCD and the role of interface bond breakage in SiC MOSFETs is not as straight forward as in Si-based devices due to the

different nature of the interface and a multitude of possible defect configurations and therefore remains unclear to date [137].

## **1.3** State of the Art, Motivation and Outline

With the application of the NMP theory for oxide and interface defects in MOS devices in combination with device simulation in modern TCAD frameworks, charge trapping has been identified as the main mechanism responsible for BTI as well as TAT in mature Si based technologies. The investigation of single charge transfer events in small area devices allowed to consistently link these reliability threats to RTN and potential defect candidates that are responsible for charge trapping have been identified by parameter comparison with those obtained from ab-initio calculations. With many electrically active defects at the SiC/SiO<sub>2</sub> interface and an increased number of potential defect candidates due to the enhanced stoichiometric complexity compared to Si-based MOSFETs, electrically measured shifts of the threshold voltage  $\Delta V_{\text{th}}$  have not been linked to defect parameters and compared with such derived by ab-initio methods for SiC based devices yet. BTI in SiC MOSFETs, so far, has only been described by empirical power-law interpolation, completely lacking a physical interpretation. A more advanced approach by using activation energy maps can also not connect BTI to a specific physical mechanism and therefore create a link between the data and a potential defect candidate even though charge trapping is widely acknowledged as the main reason for BTI in SiC MOSFETs.

Therefore, in this work, BTI as well as TAT observed in different  $SiC/SiO_2$  MOS structures is characterized and reproduced by employing an efficient simulation framework with a physical charge trapping model. The obtained defect parameters are then compared to those calculated by ab-initio methods.

This Chapter 1 has provided an overview of the benefits of using SiC as substrate material in power MOSFETs at medium to high voltage classes by laying out its material properties. SiC MOSFET processing and state of the art architectures are briefly discussed, followed by the introduction of the most relevant reliability threads in MOSFETs in general and in particular due to the detriments of the SiC/SiO<sub>2</sub> interfacial region compared to the mature Si/SiO<sub>2</sub> system.

In Chapter 2 of this work, experiments to extract the charge transfer kinetics by electrical characterization methods are discussed with a special focus on the peculiarities that arise when applying methods established in Si technologies to SiC MOSFETs.

Chapter 3 contains an overview of defect candidates that have been identified in both bulk oxide and the transition region to bulk SiC with ab-initio methods. Suspected defect candidates that are located in the transition layer between these two materials include such that potentially form due to the introduction of N containing precursors during the interface annealing process step.

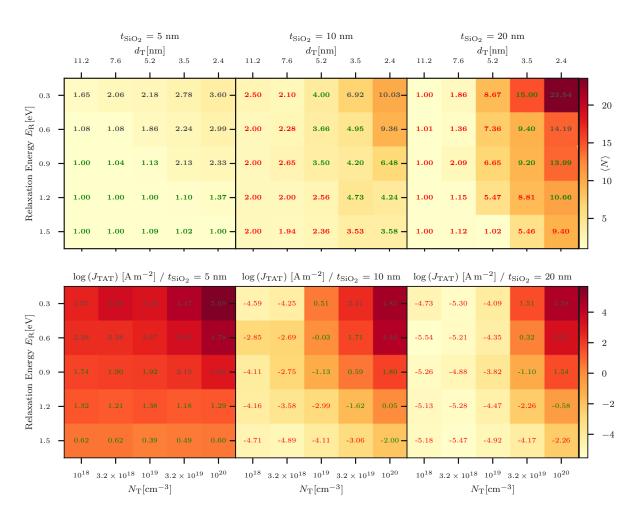

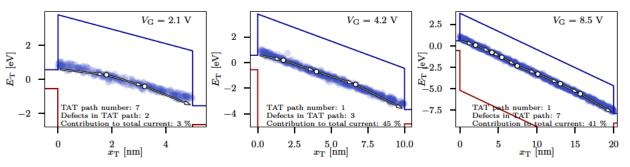

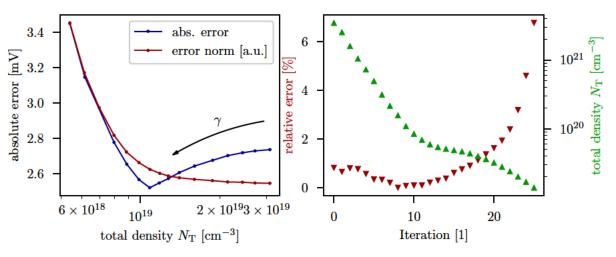

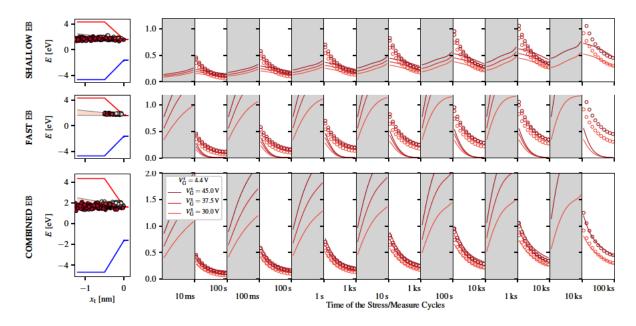

Within Chapter 4, the NMP model, which has widely been established for describing charge transfer reactions at defects in Si, SiGe and novel two-dimensional material based