# Concolic Testing of Concurrent Software in the Context of Weak Memory Models

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

## **Computational Intelligence**

eingereicht von

## **Martin Dobiasch**

Matrikelnummer 0828302

| an der<br>Fakultät für Informatik der Te                    | chnischen Universität Wien                                 |                          |

|-------------------------------------------------------------|------------------------------------------------------------|--------------------------|

| Betreuung: Univ.Prof. DiplI<br>Mitwirkung: DiplInf.(FH) Dr. | ng. Dr.techn. Helmut Veith<br>techn. Andreas Holzer, M.Sc. |                          |

|                                                             |                                                            |                          |

| Wien, 30.09.2014                                            |                                                            |                          |

|                                                             | (Unterschrift Verfasser)                                   | (Unterschrift Betreuung) |

# Concolic Testing of Concurrent Software in the Context of Weak Memory Models

## MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

## **Computational Intelligence**

by

## **Martin Dobiasch**

Registration Number 0828302

at the Vienna University of Technology

Advisor: Univ.Prof. Dipl.-Ing. Dr.techn. Helmut Veith

to the Faculty of Informatics

Assistance: Dipl.-Inf.(FH) Dr.techn. Andreas Holzer, M.Sc.

Vienna, 30.09.2014

(Signature of Author)

(Signature of Advisor)

# Erklärung zur Verfassung der Arbeit

| Mart | in Dobiasc   | h           |      |      |

|------|--------------|-------------|------|------|

| Ram  | perstorfferg | gasse 46/6, | 1050 | Wien |

| Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwende- |

|----------------------------------------------------------------------------------------------|

| ten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - |

| einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im   |

| Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Ent-  |

| lehnung kenntlich gemacht habe.                                                              |

| (0   D   )   |                          |

|--------------|--------------------------|

| (Ort, Datum) | (Unterschrift Verfasser) |

## Acknowledgements

I would like to thank Andreas Holzer for his continued support and valuable suggestions. Thank you also for teaching and explaining me a lot about scientific writing and research. Thank you for the countless hours you spent in meetings with me. They helped tremendously with the progress of this thesis.

Of course, I would like to thank my wonderful girlfriend Marion for all her support. Thank you for all the countless hours of listening to my gibberish about executions and uncommited values. Moreover, thanks for your humorous comments on my thesis and drawings in early drafts of it. They made writing this thesis a lot easier.

Last but not least, I would like to thank Professor Helmut Veith for giving me the opportunity to write this thesis in his FORSYTE group.

## **Abstract**

With software becoming ubiquitous and increasingly complex, software reliability also becomes more important. Research on software testing and verification tries to create automated solutions which exhaustively search for software bugs. One promising example for these research efforts is concolic testing, a testing technique that combines concrete with symbolic execution and which is implemented in various recent testing tools.

However, testing of concurrent software still remains a challenge. One of the main difficulties for testing concurrent software is determining the order in which the statements from different threads have to be executed. The reason for this being a challenge is that the number of possible executions can be intractably big. Furthermore, weak memory models, which describe the memory architectures of modern processors, can further increase the number of possible executions. Weak memory models allow certain deviations from the expected thread-local program order. For example, the effects of a write from one thread to a memory location might not become immediately visible in another thread which reads from this particular memory address. This results from modern memory hierarchies when computations are distributed over several computing cores. The consequence of such behaviours can be software bugs that are hard or even impossible to detect with conventional testing techniques. Most testing tools are based on the assumption of the Sequential Consistency model, i.e., that these effects cannot occur.

This thesis presents CONCRESTWMM, a concolic testing tool for concurrent software that is able to simulate the effects of weak memory models during an execution of a program under test. CONCRESTWMM is implemented as an extension of the tool CONCREST, a testing tool for concurrent software. As a central component, CONCRESTWMM adds a WMM-Scheduler. By using WMM-schedules it is possible to select a WMM and to trigger effects of this model at specific points during the execution of a test case. Thus, the tool CONCRESTWMM offers the possibility to discover bugs that can occur on real-world processor architectures that do not adhere to Sequential Consistency but to another WMM.

Two WMMs are implemented as part of this thesis. First, the WMM Sequential Consistency which can be used to simulate the behaviour of CONCREST and second, the Partial Store Order (PSO) WMM, a model which allows to delay the effect of a write event. Memory barriers are a common means to limit the deviation of executions from Sequential Consistency. By using memory barriers it is possible to force the effect of writes to become visible. Support for memory barriers is also implemented in CONCRESTWMM. Since many concurrent applications and data structures make use of a Compare and Swap (CAS) operation, a CAS operation is also implemented as part of CONCRESTWMM. The CAS operation updates a memory cell with a new value if the cell contains an expected old value. The built-in operation offers the

same semantics as the Boolean CAS operation offered by the compiler GCC and is atomic. Moreover, the built-in CAS operation is equipped with symbolic information. This enables CONCRESTWMM to search for test cases covering both branches of the CAS-operation, i.e., finding test cases where the value at the memory location is changed and test cases where the value is not changed.

To test the implementation of CONCRESTWMM and to show its capabilities, several experiments were performed. These examples are taken from the literature. The experiments show that on average CONCRESTWMM is only a constant factor of  $\sim 1.15$  slower than CONCREST when comparing both tools.

## Kurzfassung

Mit zunehmend komplexerer und gleichzeitig allgegenwärtig werdender Software wird die Verlässlichkeit von Software immer wichtiger. Forschung zu Testen und Verifikation von Software versucht automatisierte Lösungen zu finden, welche Software gründlich nach Fehlern durchsuchen. Ein Beispiel für Forschungserfolge ist Concolic Testing, eine Kombination aus konkretem und symbolischem Testen, welches in vielen aktuellen Test-Werkzeugen verwendet wird.

Allerdings ist das Testen von nebenläufiger Software nach wie vor ein offenes Problem. Eine der Hauptschwierigkeiten beim Testen solcher Software ist das Bestimmen der Reihenfolge in welcher die Befehle der verschiedenen Programmstränge ausgeführt werden sollen. Der Grund für die Schwierigkeit dahinter liegt in der Zahl der Reihenfolgen der verschiedenen Reihenfolgen welche unlösbar groß sein kann. Hinzukommen sogenannte Weak Memory Models (WMMs), welche Speicherarchitekturen beschreiben und die Zahl der Reihenfolgen weiter erhöhen können. Weak Memory Models erlauben Abweichungen von dem erwarteten Prozesslokalem Programmablauf. Zum Beispiel kann es passieren, dass der Effekt eines Schreibzugriffs von einem Programmstrang auf eine Speicheradresse in einem anderen Programmstrang, welcher von dieser Adresse liest, nicht sofort für alle andere Threads sichtbar wird. Der Grund für diese Abweichungen liegt in modernen Speicherhierarchien welche es erlauben, dass Berechnungen über mehrere Prozessor-Kerne aufgeteilt werden. Aus diesem abweichenden Verhalten können Fehler resultieren, welche mit konventionellen Testtechniken nur schwer wenn nicht sogar unmöglich zu finden sind. Die meisten Test-Werkzeuge basieren auf der Annahme, dass diese Effekte nicht auftreten können. Dieses Annahme wird auch als sequentielle Konsistenz bezeichnet

Diese Arbeit präsentiert CONCRESTWMM, ein Programm welches Concolic Testen verwendet um nebenläufige Software zu testen und welches in der Lage ist die Effekte von Weak Memory Models während der Ausführung von Tests zu simulieren. CONCRESTWMM wurde als eine Erweiterung von CONCREST, ein Test-Werkzeug für nebenläufige Software, implementiert. Der WMM-Scheduler bildet eine zentrale Komponente von CONCRESTWMM. Durch die Verwendung von WMM-Schedules ist es möglich die Effekte eines WMMs auszuwählen und an einem bestimmten Punkt während der Ausführung eines Testfalls auszuführen. Als Konsequenz daraus ist es möglich mit CONCRESTWMM Fehler, welche auf modernen sequentiell inkonsistenten Prozessoren auftreten können, zu entdecken.

Zwei Weak Memory Models werden als Teil dieser Arbeit präsentiert. Als erstes das WMM Sequential Consistency, welches verwendet werden kann um das Verhalten von CONCREST zu simulieren und als zweites das Partial Store Order (PSO) WMM, ein Model, welches es ermöglicht die Effekte eines Schreib-Events zu verzögern. Speicher-Barrieren sind ein gebräuchliches

Mittel um Abweichungen von sequentieller Konsistenz zu vermeiden. Durch die Verwendung von Speicher-Barrieren ist es möglich die Sichtbarkeit der Effekte von Schreib-Events sichtbar zu machen. Deshalb sind Speicher-Barrieren in CONCRESTWMM unterstützt. Da viele nebenläufige Programme und Datenstrukturen Compare and Swap (CAS) Operationen verwenden, ist sie auch in CONCRESTWMM realisiert. Die CAS Operation aktualisiert eine Speicheradresse mit einem neuen Wert sollte der Wert an der Adresse mit einem erwarteten Wert übereinstimmen. Die eingebaute Operation bietet die gleiche Semantik wie die vom GCC Compiler angebotene Boolsche CAS Operation und ist atomar. Zusätzlich ist die eingebaute CAS Operation mit symbolischer Information ausgestattet. Das ermöglicht es CONCRESTWMM nach Testfällen zu suchen welche beide Stränge der CAS Operation verwenden, d.h., dass Testfälle gesucht werden, welche den Wert an der Speicheradresse verändern und Testfälle welche dies nicht tun.

Um die Implementierung von CONCRESTWMM zu Testen und ihre Fähigkeiten zu demonstrieren werden mehrere Beispiele durchgeführt. Diese Beispiele stammen aus der Literatur. Die Experimente zeigen, dass im Durchschnitt CONCRESTWMM nur einen konstanten Faktor von  $\sim 1.15$  langsamer ist als CONCREST wenn die Werkzeuge verglichen werden.

## **Contents**

| 1 | Intr | oduction                                    | 1  |

|---|------|---------------------------------------------|----|

|   | 1.1  | Motivation & Problem Statement              | 1  |

|   | 1.2  | Results                                     | 3  |

|   | 1.3  | Organisation                                | 3  |

| 2 | CON  | NCREST and $(Con)^2$ colic Testing          | 5  |

|   | 2.1  | Glossary and Definitions                    | 5  |

|   | 2.2  | Concolic Testing                            | 6  |

|   | 2.3  | $(Con)^2$ colic Testing                     | 10 |

|   | 2.4  | CONCREST                                    | 15 |

| 3 | CON  | NCRESTWMM                                   | 21 |

|   | 3.1  | Architecture of CONCRESTWMM                 | 21 |

|   | 3.2  | Scheduling of Events for Weak Memory Models | 23 |

|   | 3.3  | Implemented Weak Memory Models              | 27 |

|   | 3.4  | Memory Barriers                             | 28 |

|   | 3.5  | Structure of a Program Run                  | 29 |

|   | 3.6  | Compare and Swap                            | 31 |

|   | 3.7  | Limitations and possible extensions         | 33 |

|   | 3.8  | Simulating Possible Effects                 | 34 |

|   | 3.9  | Limiting Impossible Effects                 | 35 |

| 4 | Exp  | eriments                                    | 37 |

|   | 4.1  | General Remarks                             | 37 |

|   | 4.2  | Message Passing                             | 39 |

|   | 4.3  | Relaxer1                                    | 42 |

|   | 4.4  | Relaxer2                                    | 43 |

|   | 4.5  | Non-Blocking Counter                        | 45 |

|   | 4.6  | Store-Buffering                             | 46 |

|   | 4.7  | Dekker's Algorithm                          | 48 |

|   | 4.8  | Benchmarks                                  | 49 |

| 5 | Rela | ited Work                                   | 51 |

| Bi | bliogr | raphy                 |  |  |  |  |  |  |  |  |  | 59 |

|----|--------|-----------------------|--|--|--|--|--|--|--|--|--|----|

| 6  | Con    | clusion & Future Work |  |  |  |  |  |  |  |  |  | 57 |

|    |        | RELAXER               |  |  |  |  |  |  |  |  |  |    |

CHAPTER 1

## Introduction

### 1.1 Motivation & Problem Statement

Software becomes more and more ubiquitous in our daily and, at the same time, the complexity of software increases. This poses a major challenge for the reliability of software. To mitigate this problem, research on software testing and verification tries to create automated solutions which exhaustively search for software bugs. Although there has been progress in developing automated testing tools for sequential testing [9], testing concurrent software still remains as a challenge. Concurrency increases the amount of possibilities for tests exponentially since the scheduling of statements from different threads adds an additional factor, i.e., it is also necessary to investigate in which order program statements are executed across different threads.

Weak Memory Models. Most of the test and verification tools for concurrent software rely on the assumption of sequential consistency. This means that the execution of a concurrent program is the same as if the statements from different threads had been brought to a sequential order and executed sequentially while the thread-local order remains unchanged for all threads. However, unlike sequential consistency, so-called *Weak Memory Models* (WMMs) allow certain deviations from a thread-local program order. For example on modern processors a write to a shared variable might be stored in a local buffer before it is stored in global memory. Thus, the executing thread can see the new value of this variable while other threads might still see the old value. We say that a write is committed when all threads see the new value. Another interesting aspect of modern CPUs is that they have multiple pipelines for commands to be executed. This stems from the fact that they have different processing units (e.g. for integer operations, for floating point operations, ...). Whenever an instruction is being processed but has not been finished yet, it is referred to as being in an *in-flight* state. As a result of WMMs, an instruction can remain in an in-flight state while other subsequent instructions have been committed already. By doing so the processor can save time since it does not have to wait for an instruction - like a write - to finish until the next instruction can be executed. This can result in a behaviour that for thread A it seems that another thread B does not respect the thread-local order. One aspect that

| Thread A                           | Thread B |  |  |  |  |  |

|------------------------------------|----------|--|--|--|--|--|

| x = 1                              | r1 = y   |  |  |  |  |  |

| y=1                                | r2 = x   |  |  |  |  |  |

| Initial state: $x = 0 \land y = 0$ |          |  |  |  |  |  |

| Forbidden: $r1 = 1 \land r2 = 0$   |          |  |  |  |  |  |

Figure 1.1: Message Passing Example from [12]

increases the difficulty of understanding these models of computation is that they are usually not published in a comprehensible manner but instead hidden in long technical documentations of a specific processor [12]. One major problem during testing is that testing a software on a machine with a WMM can lead to unexpected program results which are difficult to explain and are hard to reproduce since WMMs allow WMM-specific effects, but do not require the computation to perform the same effects again when running the program anew. In summary, WMMs can make identifying faults via manual code inspection extremely hard if not impossible.

Figure 1.1 shows an example with two threads. The first thread performs two writes on two shared variables x and y while the second thread reads the values from these two shared variables and writes them into two local variables r1 and r2. Moreover, the example defines a state which is infeasible when considering sequential consistency (denoted as 'forbidden'). In the initial state both x and y are initialised with the value 0. Under sequential consistency the forbidden state cannot be reached. However, this state is feasible for ARM and POWER architectures [12]. One possibility to reach this state is as follows: First thread A starts executing the write x = 1 but does not commit it. Then the second write y=1 is executed but this time the write is committed immediately. Next, thread B takes over reading the value of y(1) and writing it to r1. After this, it executes the second read, thus storing the initial value of x(0) to  $r^2$ . The forbidden state is thereby reached. From a technical point of view there are two possibilities for this scenario. The first possibility is that the compiler or processor performed an instruction reordering on thread A. As a consequence of this, the write y=1 is executed as first instruction from thread A. Next, thread B read the written value and stores it to r1 (r1 = y) and subsequently reads x = 0 and writes the value to r2 (r2 = x). Thus, a state  $r1 = 1 \land r2 = 0$  is reached. The second possibility is that the executing processor uses a store buffer. While x is buffered for thread A, y is written directly to the memory. As a consequence of this an execution will write 1 to the cache for xand 1 to the memory address of y. The cache for x is not cleared immediately, i.e., the memory still contains 0 as value for x. Thread B will thus read the values 1 for y and 0 for x and reach the forbidden state.

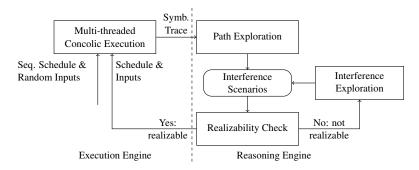

**Concolic Testing.** In past years various testing tools have been developed featuring concolic testing [9], a testing approach that combines the concrete execution of a program with a simultaneous symbolic execution. However, only a few of these tools [17] can test concurrent software. A testing approach derived from concolic testing which can test concurrent software is  $(con)^2 colic$  testing (concrete and symbolic execution of a concurrent program) [7]. Figure 1.2 illustrates the high-level architecture of  $(con)^2 colic$  testing which can mainly be divided into two parts: an execution engine and a reasoning engine. The execution engine gathers symbolic

Figure 1.2: Overview of  $(Con)^2$  colic Testing [7].

constraints which the reasoning engine then modifies to generate new execution paths. The reasoning engine explores interference scenarios by combining and modifying gathered constraint systems. The  $(con)^2$ colic algorithm works in the following way: First, the program under test is executed and (symbolic) information is collected. Based on gathered information alternate program runs are then generated and tested for their realisability. However, there could be an intractable amount of such alternate program runs. The tool CONCREST [7] implements  $(con)^2$ colic testing as an extension of CREST<sup>1</sup>. However, CONCREST has no means to test programs with respect to the effects of weak memory models and instead relies on sequential consistency. As a consequence of this, certain aspects of concurrent behaviour remain untested. The problem to be solved in this thesis was to add support for weak memory models in  $(con)^2$ colic testing.

### 1.2 Results

This thesis implemented the tool CONCRESTWMM which extends the execution platform of CONCREST with the capability to simulate effects of weak memory models. CONCRESTWMM provides an interface to enable the precise control of the effects of a WMM. To support exist different WMMs, CONCRESTWMM is configurable with regard to which WMM is used while performing program executions. Two WMMs have been implemented: *Sequential Consistency* as a default WMM-model which simulates the behaviour of CONCREST and the WMM *Partial Store Order* (PSO). CONCRESTWMM was designed to preserve CONCREST's feature to execute dynamic analysis tools, like Valgrind, in parallel to a test execution.

## 1.3 Organisation

In Chapter 2 (con)<sup>2</sup>colic testing and CONCREST an implementation of it are discussed. For this purpose first concolic testing is introduced in Section 2.2. Next, (Con)<sup>2</sup>colic is introduced in Section 2.3. CONCREST as an implementation of (con)<sup>2</sup>colic testing is then explained in detail in Section 2.4. Chapter 3 contains implementation details for the implemented simula-

<sup>1</sup>http://code.google.com/p/crest/

tor. First the architecture of CONCRESTWMM is described in Section 3.1. After a description of event scheduling in Section 3.2, the implemented memory models are discussed in Sections 3.3. Section 3.4 introduces memory barriers and discusses how they can be used with CONCRESTWMM. Next, Section 3.6 describes Compare and Swap and its implementation in CONCRESTWMM. Subsequently, the limitations and possible extensions of CONCRESTWMM are outlined in Section 3.7, followed by a discussion of the capabilities of CONCRESTWMM in Sections 3.8 and 3.9. The conducted experiments are outlined in Chapter 4. Additionally, benchmarks are presented in the last section of this chapter. In Chapter 5 an overview over related work is given. It contains a description of partial orders in Section 5.1 and furthermore how these orders are used within CBMC in order to perform bounded model checking for WMMs. Next, Section 5.2 presents RELAXER a testing tool which is able to simulate WMM-effects during the execution of a program under test. Finally, a conclusion and future work is given in Chapter 6.

CHAPTER 2

# ConCrest and (Con)<sup>2</sup>colic Testing

This chapter describes the testing approach  $(con)^2$ colic testing and the tool CONCREST which implements it. In Section 2.1 some basic definitions are introduced which are used throughout this chapter. In Section 2.3 the testing approach  $(con)^2$ colic testing is presented. Section 2.4 then presents CONCREST as an implementation of  $(con)^2$ colic testing.

## 2.1 Glossary and Definitions

**Program under test** is computer program which is subject to examined for included bugs. It can vary between a simple program consisting only of an entry point with some additional functions contained in a single source code file and a large scale application consisting of several source files.

**Propositional logical formulae** are formulae comprised of variables and constants over the symbols T (*true*) and F (*false*) while using (at least) the connectives  $\land$  and  $\neg$ . The evaluation of any syntactically correct formula results in either true or false. A formula is satisfiable iff there exists a variable assignment so that the evaluation of the formula under that assignment evaluates to true.

**First-Order Theory** First order logical formulas may be quantified by universal and existential quantifiers and contain functions and predicates. In addition to quantification a formula may make use of first-order theories extending the expressiveness to, for example, uninterpreted functions. A first-order theory provides a set of predicates and function symbols and additionally, axioms which hold on these introduced predicates and functions.

**Static Single Assignment** is used when data-flow in a program has to be modelled. For each write access to a variable a new variable-symbol is introduced. For example, the initialisation x = 0 gets transformed into  $x_0 = 0$ .

```

1 int abs(int x) {

2    if( x < 0 )

3     return -x;

4    if( x == 1 )

5     return -x;

6    return x;

7 }</pre>

```

Figure 2.1: Faulty implementation of a function returning the absolute value of its parameters. Adopted from [5].

**SAT solver** is a program which is able to decide whether a given formula is satisfiable or unsatisfiable. For satisfiable formulas it is furthermore able to provide evidence via a variable assignment.

**SMT solver** (Satisfiable Modulo Theory) is a program which is able to decide whether a given formula using a set of first-order theories is satisfiable or unsatisfiable modulo the used theories.

## 2.2 Concolic Testing

*Concolic* testing is the combination of *conc*rete and symbolic testing. Concolic testing was independently developed in several papers [5, 9, 20] which propose similar techniques. The technique has several other names such as *directed systematic test generation* [9] or *execution generated testing* [5].

One of the roots of concolic testing is another automatised approach called random testing where inputs for a program are guessed in order to generate test cases for the program under test. However, the approach of random testing has several problems for testing software in a comprehensive manner. For example for a program fragment like if(x==1) abort(); it is hard to reach the error state using random testing since there are  $2^{32}$  possible inputs, assuming x is an 32-bit integer and there are no further constraints on it. As a result of this it is quite impracticable to generate a test case which will follow a path through a program to this exact error/problem state. The problem is better illustrated in Figure 2.1 where an example of a faulty implementation of a function returning the absolute value of the function parameter is shown. The implementation returns an incorrect value only if the input is 1; for all other possible inputs the function is correct. While it is hard for random testing to generate a test case exploiting the bug, concolic testing, however, is able to detect a bug like this easily.

Figure 2.2 shows the concolic execution of the abs function defined in Figure 2.1. Prior to the first step no constraints are gathered and thus the random value 15 is chosen for x. The program is then executed visiting the statements in lines 1, 2, 4 and 6 and returning 15 as output value. During this execution the two path-constraints x < 0 and x = 1 are gathered. In the next step x = -1 is generated as a solution for the constraint x < 0. Thus, the program execution visits the lines 1, 2 and 3 returning -1. For the remaining constraint x = 1 is generated as

| Constraints | Input  | Execution                                                             |

|-------------|--------|-----------------------------------------------------------------------|

|             | x = -1 | $ \begin{vmatrix} 1, 2, 4, 6 \\ 1, 2, 3 \\ 1, 2, 4, 5 \end{vmatrix} $ |

Figure 2.2: Concolic execution of abs-function in 2.1.

input value. This causes the program execution to traverse lines 1, 2, 4 and 5. As a result of the outlined concolic testing of the abs function the three test cases x=15, x=-1 and x=1 are generated. When used by a testing tool which verifies the output of the abs function these test cases will exploit the bug of the function.

However, symbolic testing without using concrete values has limitations for certain classes of programs as can be observed when testing a simple example as shown in Figure 2.3. The branch created by the if statement in line 2 has a non-linear constraint, thus causing most symbolic testing tools to stop the test execution since most solvers are not able to reason about non-linear arithmetic [9]. Concolic testing tries to overcome the problems of random testing and symbolic testing by combining concrete and symbolic testing. As a result of this it is possible to use the concrete values as a fall-back and continue the (symbolic) execution when the symbolic execution fails to provide the values due to circumstances like limitations of the used solver or theory. Thus, it is possible for concolic testing to correctly examine the program in Figure 2.3 with the result that the abort statement in line 7 is not reachable but is reachable in line 4. The statement is not reachable since the  $x^3 <= 0$  branch can only be reached if x is negative. Thus it is not possible to find input values so that  $x > 0 \land y = 20$  is satisfied. However, as mentioned before, concolic testing will correctly report that the error state in line 4 is reachable.

```

void nonlinear(int x, int y){

1

2

if (x*x*x > 0){

3

if (x>0 \&\& y==10)

4

abort();

5

} else {

6

if (x>0 \&\& y==20)

7

abort();

8

}

9

}

```

Figure 2.3: Non linear path constraints. Taken from [9].

Another example where pure symbolic testing fails to discover the bug can be seen in Figure 2.4. When assuming that no symbolic information about the hash function is at hand a symbolic execution has to stop. Concolic testing, however, can just use the concrete value provided during the execution. Thus, the testing of the function could proceed as follows. The initial inputs of x=0 and y=0 are guessed and used for the next test case of the program.

```

1 int obscure(int x, int y) {

2    if( x == hash(y) )

3     abort();

4    return 0;

5 }

```

Figure 2.4: Obscure-Function. Taken from [8].

```

int obscure(int x, int y) {

2

LOAD(y);

3

tmp = hash(y);

4

STORE(tmp);

5

LOAD(x);

6

LOAD(tmp);

7

BRANCH(EQ);

8

if(x == tmp)

9

abort();

return 0;

10

11

}

```

| Input         | <b>Symbolic Information</b>   |

|---------------|-------------------------------|

| x = 0, y = 0  | $x = 0 \land y = 0$           |

|               | $\land (y = 0 \to tmp = 42)$  |

|               | $\wedge \neg (x = tmp)$       |

| x = 42, y = 0 | $x = 42 \land y = 0$          |

|               | $\wedge (y = 0 \to tmp = 42)$ |

|               | $\wedge (x = tmp)$            |

(a) Instrumented Code

(b) Symbolic Informatione

Figure 2.5: Concolic execution of obscure.

During this execution the evaluation of hash(0) delivers the concrete value 42. Thus, the *else*-branch is taken. In order to cover the *then*-branch the algorithm can now select 42 as input value for x. When executing the function again with the input values x=42 and y=0 the execution will take the *then*-branch<sup>1</sup> and discover the abort statement.

## **Working Principle**

Figure 2.5 illustrates a concolic execution of the obscure function. Most concolic testing tools (like [5,20]) work by first instrumenting a program in order to be able to gather symbolic information during the concrete execution of the program. This means that additional statements are added to the original source, thus generating a new source file. The instrumented code of obscure is presented in subfigure 2.5a. Some tools, like CREST, for example, also simplify or change the program statements (without changing the semantics of the program under test). For the instrumentation automatic tools like CIL [15] are used [5,17,20]. The instrumented program under test rather than the original program is then compiled and executed during the performed tests. During each test run the instrumented code will then gather the symbolic information while being executed and without changing the behaviour of the program under test. This symbolic information contains amongst other data constraints as well as path constraints. The gathered

<sup>&</sup>lt;sup>1</sup>Assuming a deterministic hash function.

constraint systems can then be used to generate new test cases. In subfigure 2.5b the gathered symbolic information for two test cases is illustrated for the obscure function. For each test case the symbolic information in the second column of the table shows in the first row input data constraints, in the second row data constraints and in the third path constraints.

Path constraints contain the information about the evaluation of branching conditions within the program. A path constraint thus can also be seen as an equivalence class for inputs since it describes exactly which elements will result in the same control flow, i.e., lie in the same class of inputs. In general, the solution to these constraints is not unique. The path constraints are usually constructed from branching conditions within the program under test. In order to cover all branches of the program under test a path constraint can be flipped and then be used for obtaining new input values. These input values should then guide the execution to the previously unvisited branch. However, the program run might fail to visit the predicted branch. This can happen, for example, if the program makes use of non-deterministic functions.

#### Limitations of concolic testing

One advantage from the developer's point of view of concolic testing over some other automated testing approaches, like random testing, is that once a bug is found using concolic testing the developer can be presented with a test case causing the bug and additionally also with a trace for this bug. Having a trace and a test case can often reduce the effort needed for analysing the problem.

A problem concolic testing suffers from is the dependence on deterministic programs. When, for example, the hash function from the example in Figure 2.4 is non-deterministic, concolic testing will probably fail to discover the bug. Moreover, an incomplete concolic testing approach could for other more complex programs claim that no bugs exists.

Another problem of concolic testing are irreversible functions like, for example, the hashing function MD5. Concolic testing makes always use to overcome this issue. However, the execution will not always discover new branches. For a simple program like the program in Figure 2.4 the fall-back concrete values can lead to new input values thus guiding the search to successfully testing the program. However, for other programs the concrete values might not be successful in triggering a new branch.

Due to the fact that most concolic testing tools rely on SMT solvers for solving path constraints and the like, concolic testing is incomplete. Currently there are several undecidable theories like non-linear arithmetic, integer division and modulo. The fact that they are undecidable affects symbolic testing and thus also concolic testing. However, as mentioned before concolic testing can try to overcome this problem by falling back on the concrete values recorded during the execution.

Finally, the design of most concolic testing tools is not yet suited for testing concurrent software.

## 2.3 $(Con)^2$ colic Testing

A testing approach that is able to test concurrent software is  $(con)^2 colic$  testing. The term  $(con)^2 colic$  testing assembles from the terms conc erete, symbolic and conc current.  $(Con)^2 colic$  testing is based on concolic executions of concurrent software. Based on the concolic executions of a program under test it derives inputs and schedules for the program so that its execution space is explored systematically [7].

### **Preliminaries**

In order to be able to describe  $(con)^2$  colic testing in more depth some more definitions have to be explained upfront.

**Coverage.** One of the main challenges for testing concurrent software is defining coverage of a concurrent program. While for sequential programs it is straight-forward to define useful criteria like condition, branch and statement coverage, for concurrent software it remains a hard problem with no commonly agreed standard solution. A reason for this is that in addition to the usual criteria mentioned above, interferences between processes have to be taken into account. This means that for shared variables it has to be taken into account in which order the various processes access (i.e., read or write) variables within the program under test. A brute force search to solve this problem would be intractable since the number of all possible program orders is exponential.  $(Con)^2$  colic testing provides a coverage guarantee over the space of program inputs and interleavings [7].

**Concurrent Programs.** A program usually consists of a finite sequence of program statements which are executed in some order. This order is of course not always from top to bottom since programs usually consist of conditional (e.g. branches and loops) and unconditional (e.g. function calls) jumps. A concurrent program consists of a countable amount of threads  $T = \{T_1, T_2, ... T_n\}$ , where each of these threads consists of a finite amount of program statements.

**Schedules.** As mentioned before the main challenge of testing concurrent software is to find the order of statements throughout the different threads causing a bug. On modern systems several statements can be executed at the same time, i.e., the execution of a program can be concurrent. However, there exists a total order over the statements. Using this total order the concurrent execution can be simulated by bringing the statements from the threads of the program under test into a sequential order. The way the statements from the different threads are aligned, i.e., the number of instructions a thread can perform before it has to wait for its next turn, is called a *schedule*  $\sigma$ . Hence, a schedule is a sequence of tupels  $(T_{ij}, n_j)$  where  $T_{ij}$  is a thread and  $n_j$  is the number of statements from this particular thread to be executed.

**Events.** In order to be able to track the relevant information of the execution the events  $tf(T_i)$ , ac(l), rel(l),  $br(\psi)$ , rd(x,r) and wt(x,val) are defined. The first event represents the forking of

```

1

int x, y;

2

int main() {

3

4

pthread_create(&thread1, NULL, Thread1, NULL);

5

}

6

7

8

int Thread1(void* param) {

9

LOAD(x);

10

LOAD(y);

11

BRANCH(EQ);

12

if(x == y)

13

LOAD(1);

14

STORE(X);

Line

Event

15

x = 1;

4

tf(Thread1)

16

} else

10

rd(x,x_0)

17

abort();

11

rd(y, y_0)

18

19

12

br(x_0 = y_0)

return 0;

14

20

}

wt(x,1)

(a) Instrumented Code

(b) Events

```

Figure 2.6: A small program which creates a second thread. In this thread the two shared variables x and y are compared. Depending on the outcome of the compare the program is aborted or the value of x is set to 1.

a thread. For example, line 4 in Figure 2.6a creates a new thread which is recorded as the event tf(Thread1). The next two events (ac and rel) are required to be able to deal with locks, i.e., acquiring and releasing a lock l. Whenever a program branches using a predicate  $\psi$  this information is recorded using the br event. The rd event represents a read from a shared variable x where the result/value of this read is represented by the symbolic value r. In Figure 2.6a the value of x has to be loaded before the comparison to y this is recorded as the event  $rd(x,x_0)$ . When a write to x using the symbolic value val is observed during the program execution it is represented by the write event wt. For example, setting x to 1 in line 15 is recorded as the event wt(x,1). Thus, a concurrent program consists of the set of threads T, the set of input variables IN, the set of shared variables SV, the set of local variables LV, and the set of locks L. To be semantically correct the information of all events are recorded using a Static Single Assignment (SSA). Using these events it is possible to track the flow of information between the various threads  $T_i$  of a program.

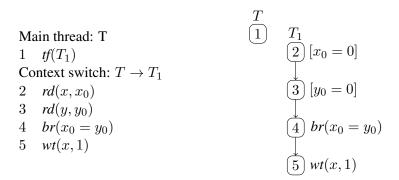

**Symbolic Traces.** When a concurrent program is executed concolically it will yield a finite string  $\pi$  containing the events of the program in their order of occurrence. Furthermore,  $\pi|_{T_i}$

Figure 2.7: Symbolic trace

denotes the events involving thread  $T_i$ . A symbolic trace for the program in Figure 2.6 is shown in Figure 2.7. The trace is computed for a program execution where x = 0 and y = 0.

Interferences. The interesting program runs are those where a thread  $T_j$  reads a value written by another thread  $T_i$ , i.e., an *interference* occurs. To systematically record and examine all interferences of interest  $(con)^2$  colic testing defines so-called *interference scenarios* IS. An interference scenario describes a class of program executions where the same interferences will happen during the program execution. An IS is a set of thread-local program executions (traces) extended with the information of interferences between them. The nodes in the IS represent the events from the program executions. The edges in the IS consist of two disjoint sets  $E_L$  and  $E_I$  where  $E_L$  is the set of thread local edges and  $E_I$  is the set of interference edges connecting two threads.  $E_L$  can further be subdivided into the disjoint sets  $E_{T_i}$  of the threads of the program. Each of these  $E_{T_i}$  induces a subforest  $G_{T_i}$  consisting only of nodes of the thread  $T_i$ . An interference scenario I is called a *realizable interference scenario* iff there exists a feasible partial program run where the extracted interference scenario from its symbolic trace coincides with I [7]. If the sink I of an interference scenario I is a branching event, i.e., I in I is called an interference scenario candidate (ISC) for I in the sink I is called an interference scenario candidate (ISC) for I is called an interference scenario candidate (ISC) for I in the sink I is the set of thread I interference scenario candidate (ISC) for I is called an interference scenario candidate (ISC) for I is called an interference scenario candidate (ISC) for I is a strained at the same interference and I is called an interference scenario candidate (ISC) for I is a strained at the same interference at the sam

#### **Constraint Systems**

In order to check whether an interference scenario is realisable two constraint systems are used: Data Constraints DC and Temporal-Consistency Constraints TC. The data constraints DC for an interference scenario consist of branch, interference and local constraints. The branch constraints ensure that the program execution will follow the desired path in the program, i.e., so that the evaluation of control statements, like if-statements within the program will result in the desired evaluation (truelfalse). An Interference constraint relates the read from a shared variable to the symbolic value of a write event. Any solution to the interference constraints will include the read-write interferences. In addition the local constraints are used to block out interferences from other threads for a read in a thread which should receive the value from a thread-local write. Thus, any solution to the data constraints of an interference scenario defines an input vector to the concurrent program.

```

Data Constraints

Branch: r_0 > 0 \land r_1 > 0

Interfere: DC_{match}(n_{2,1}, n_{1,6})

Thread1:

1

2

void t1() {

Local: DC_{match}(n_{1,1}, n_{1,3})

3

\Rightarrow r_0 = 1

4

5

Temporal Constraints

6

PO_{T_1}: t_{n_{1,1}} < t_{n_{1,2}} \wedge t_{n_{1,2}} < t_{n_{1,3}} \wedge

7

}

t_{n_{1,3}} < t_{n_{1,4}} \wedge t_{n_{1,4}} < t_{n_{1,5}} \wedge t_{n_{1,5}} <

8

9

Thread2:

\widetilde{WRC_{Inf}}: Coupled(n_{1,1}, n_{2,1}) \Rightarrow

10

void t2() {

t_{n_{2,1}} < t_{n_{1,5}} \land ((t_{n_{1,2}} < t_{n_{2,1}}) \lor (t_{n_{1,5}} < t_{n_{1,2}}))

WRC_{Local} : Coupled(n_{1,3}, n_{1,1}) \Rightarrow

11

12

}

(a) Program

t_{n_{1,1}} < t_{n_{1,3}}

Trace

Symbolic

(b)

(c) Constraint System

Interference Scenario

```

Figure 2.8: A small program with a concolic execution and a constraint system

Temporal-consistency constraints TC for an interference scenario, on the other hand, can be used to find schedules for a concurrent program. In order to relate events in a time-concerning manner a set of integer variables  $t_n$  is introduced encoding for every event n its index within the symbolic trace  $\pi$ . The TC constraints can further more be subdivided into four categories of constraints. The first category defines thread-local program-order consistency. Constraints from this category ensure that any potential schedule for the program needs to execute the statements from the various threads according to their order within the threads. The second category, the thread-fork consistency constraints, ensure that no thread can be scheduled before it has been created, i.e., forked by another thread. Lock consistency constraints define the third category of constraints ensuring that for every lock no pair of threads can acquire the lock at the same time. In order to do so for every lock acquisition event the corresponding lock release event is identified thus defining a lock block. For every lock it can then be guaranteed that in a potential schedule no overlapping blocks exist. Furthermore, it is ensured that for a lock which is never released in a schedule it is only acquired once all other threads have released this particular lock. The last category of constraints define write-read consistency within a potential schedule. For a pair of a read and write event a coupled block is defined in the constraints so that no other write or read event can occur between the events in a potential schedule. The coupled read-write events are formed from interferences and local read-write events.

Figure 2.8 shows an example for a constraint system. In Subfigure 2.8a a small program is outlined. It consists of two threads and two shared variables a and b. The first thread sets both a and b to 1 and then tests whether a > 0. If this is the case then b > 0 is asserted. The second thread contains a data race since it sets b to 0. Subfigure 2.8b shows a symbolic

trace of an execution of the program. This execution first executed thread 2 and subsequently thread 1. Thus, the assertion was not violated. Moreover, an interference scenario containing an interference from the write to b in thread 2 to the read of b required for verifying the assertion is shown. Subfigure 2.8c shows the constraint system constructed for the interference scenario. Note, that since the program does not contain any locks also the constraint system does not contain constraints for the lock. Moreover, since only a program stub is depicted thread-fork consistency constraints are also omitted.

## Algorithm

In this section a high level description of the  $(con)^2$  colic testing algorithm is outlined. The exact algorithm and more information can be found in [7]. The algorithm tries to iteratively increase branch coverage. During its iteration the number of interferences k is increased up to  $k_{max}$ .

The algorithm uses two list of sets: a list of worklists  $W^i$  for ISCs having degree i with  $0 \le i \le k_{max}$  and a list of ISCs  $UN^i$  for ISCs which are unrealisable having degree i with  $0 \le i \le k_{max}$ . Furthermore, an interference forest *forest* is used as a central data structure.

The algorithm starts off with an initial concolic execution of each thread of the program under test thus gathering a symbolic trace for every execution. These initial executions are performed using the same random values as inputs for all executions. Every execution uses a schedule where only one of the created threads will perform its operations; once this thread has finished its execution the program under test is terminated. From each of the gathered traces the set of ISCs is then extracted. All extracted ISCs form the initial set of  $W^0$ , the set of ISCs with no interferences. As a result of this the exploration can then start off with a set of ISCs for in depth exploration.

In its main loop the algorithm takes a candidate ISC C from the current worklist  $W^k$  and a realisability check is performed. If C is not realisable it is added to  $UN^i$  for later exploration since it might become realisable when more interferences have been introduced. However, C can still be used in this iteration to be extended to a set of ISCs which target the sink of C. In order to obtain a set of ISCs from C the write nodes of *forest* are used to introduce new interferences to read nodes in C. The obtained ISCs might have a degree d different from k and are thus added to their corresponding worklists  $W^d$  if d does not exceed  $k_{max}$ . If, on the other hand, C is realisable, inputs and a schedule are obtained by the realisability-check. The program under test is then executed concolically using the generated inputs and schedule. The resulting trace  $\pi$  is once more examined for further ISCs which are then added to the current worklist  $W^i$ . Newly discovered write nodes in  $\pi$  are used to analyse previously unrealisable ISCs. For this matter all ISCs from  $UN^i$  for  $0 \le i < k$  are examined for possible new ISCs. This is done by probing all read nodes from the ISC C to a newly discovered write node. If a read-write pair can be used to extend C the a new ISC C' is created by extending C with the interference (i.e., the read-write pair) and C' is added to the list of newly discovered ISCs. A newly discovered ISC isc is then, like for an unrealisable C, analysed for its degree d and added to  $W^d$  accordingly.

The presented algorithm is capable of achieving full branch coverage for a program P under the following conditions. First, standard assumptions for concolic testing have to be satisfied, i.e., P has to be deterministic, does not use non-linear arithmetic, and does not contain calls to external library functions. In practise concolic testing can, however, fall back to concrete values

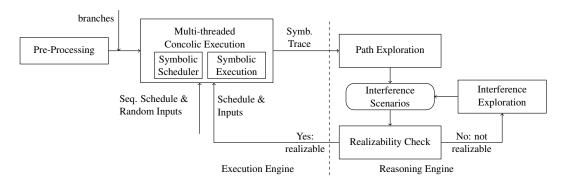

Figure 2.9: Architecture of CONCREST

and thus might successfully test P. Secondly, the number of interferences required to achieve full branch coverage does not exceed  $k_{max}$ .

### 2.4 ConCrest

The tool CONCREST [7] implements the (con)<sup>2</sup> colic testing approach as an extension of CREST. Figure 2.9 illustrates the high-level architecture of CONCREST. CONCREST can be divided into two parts: an execution engine and a reasoning engine. The execution engine is responsible for executing a program with given inputs and schedule. Additionally, it gathers information like symbolic constraint systems during the execution of the program. This information is then used to generate alternate program runs. Since there could be an intractable amount of them the previously mentioned interference scenarios are used to limit the number of possible alternate runs. Using the realisability checker it is checked whether a schedule for the threads in the program and inputs to the program exist so that the scenario can be realised.

Assertions are modelled as two branches. This means that in the instrumented program an *if*-statement is introduced where one branch models the violation of the assertion and the other one the affirmation. CONCREST will then try to traverse both branches introduced by the assertion. In case the assertion is violated this fact is also recorded in the information about the program execution before it is terminated. In addition to assertions CONCREST introduces *assumptions*. Like assertions, assumptions are modelled using two branches and CONCREST will try to cover both of them. If the assumption does not hold the program is terminated otherwise the program execution continues. Using assumptions it is possible to guarantee that certain statements are true when a program execution reaches a specific point. As a result of this the assume can be used, for example, to model a join of two threads, i.e., a thread waits until another thread terminates.

### **Pre-Processing**

CONCREST relies mostly on an instrumentation process for the pre-processing. In the first step the program under test is processed by the CIL tool suite [15]. The C Intermediate Language (CIL) is used in order to generate the instrumented program. Non-atomic statements

```

__CrestLoad(3, (unsigned long)(& b), (long long)b);

1

2

\_cil_tmp6 = b;

3

__CrestSchedulerAfter(3, (unsigned long )(& b));

4

__CrestLoad(4, (unsigned long )0, (long long )1);

5

\_CrestApply2(5, 0, (long long )(\_cil\_tmp6 + 1));

\_\_CrestSchedulerBeforeWrite (6\,,\ (\textbf{unsigned long })(\&\ a\,))\,;

6

7

__CrestStore(6, (unsigned long )(& a));

8

#line 1

9

a = \_\_cil\_tmp6 + 1;

10

__CrestSchedulerAfter(6, (unsigned long )(& a));

(a) Instrumented operation

1

b+1

(b) Empty stack

(c) Load b

(d) Load 1

(f) Store to a

(e) Apply +

```

Figure 2.10: Stack operations

within the program are split up into atomic operations thus modelling an assembler like execution. This means that, for example, a statement like a=b+1 is split up into the operations of loading the value of b and putting the value on the stack, putting 1 on the stack, adding the two values on the stack and writing the result of the addition to a. Figure 2.10 illustrates the pre-processing. In Subfigure 2.10a the instrumented version of a=b+1 is shown. The execution starts with an empty stack (Subfigure 2.10b). In line 1 b is loaded, i.e., put on the stack (Subfigure 2.10c) subsequently the current value of b is stored in a temporary variable (Line 2). The next load is performed in line 4 and puts 1 on the stack (Subfigure 2.10d. After that the operator is applied in line 5, thus removing two elements and putting the result on the stack (Subfigure 2.10e). In line 7 the result of the operation is stored to the symbolic variable a thus removing the result from the stack (Subfigure 2.10f). Finally, in line 9 the concrete result is computed and written to the concrete variable a. Additionally, every load and write operation within the translated program is guarded with the scheduling instructions

$\underline{\hspace{0.5cm}} \texttt{CrestSchedulerBeforeRead/} \underline{\hspace{0.5cm}} \texttt{CrestSchedulerBeforeWrite} \ \textbf{and} \\$

\_\_\_CrestSchedulerAfter. As mentioned earlier, true concurrency can be simulated by bringing the statements into a sequential order and executing the statements in this order. Technically, CONCREST does this by introducing a global lock gl, the token of execution. The instructions above will enable the execution engine to pass the token of execution between the threads of the program while keeping track of how many steps a thread has been executing. Moreover, information about the structure of the program, i.e. how the program can be traversed, is gathered. This means that the control flow graph CFG (written to the file cfg) of the program is generated using the tool suite. The CFG models precisely where in the program

branching positions and calls to functions are positioned. During the initial code analysis the process distinguishes between functions contained within the program under test (i.e. functions which are also subjected to tests) and built-in functions or external functions which are not tested explicitly. For built-in and external function no symbolic information is computed. Hence, there is no information about their branches. The information about the functions within the program under test is written to cfg\_func\_map. All computed information about the control flow is written to cfg.

During the start-up of CONCREST, i.e., before the exploration of the program under test starts, the CFG is parsed and analysed further. For every branch within the program all branches directly reachable in one step are computed using a bounded Dijkstra algorithm. The weights on the edges in the CFG are set to 0 if they do not end in a branching node or to 1 otherwise. As a result of this reachability computation the information about which branches can be visited next from a given branch is known. This information is then used during the exploration. The result of the computation is stored in the binary file cfg\_branches containing for every branch the list of branches reachable with cost 1.

#### **Execution**

As mentioned previously, the (con)<sup>2</sup> colic testing algorithm can be divided into two units, the execution engine and the exploration/reasoning engine. While the latter is responsible for the main part of the algorithm described in the previous section, the execution engine is responsible for executing the program under test with the desired input and schedule while gathering all relevant symbolic information.

#### **Program Initialisation**

In the first step the schedule and inputs generated by the reasoning engine are written to the files schedule and input. Subsequently, the instrumented program is launched and the exploration engine waits for the program under test to terminate. Due to its instrumentation the program will, as a first step, read the configuration (i.e., schedule and inputs) from the files. In order to achieve this, the instrumenter added a function \_\_globinit\_<name> to the code and a call to this function as the first operation in the main function of the program under test where this initialisation function itself performs a call to \_\_CrestInit, the initialisation of CONCREST. This function is responsible for enabling the concolic execution. In order to do so it first reads the inputs for the current test and passes them to the symbolic interpreter. Subsequently, a wrapper for the pthread library is enabled. The wrapper enables the execution engine to keep track of all thread-related events, like the creation of a thread. Furthermore, a handler for segmentation faults is created. By doing so any problems during the execution can be captured and no information should be lost. In a last step \_\_CrestAtExit is registered as an exit-callback.

#### Scheduling

One of the main parts of the execution engine is the execution of the program under test according to the provided schedule. This is done by the symbolic scheduler which is a central part of the execution engine of CONCREST. The symbolic scheduler has control over the token of execution gl. As mentioned previously, the instrumenter adds calls to the commands \_\_CrestSchedulerBeforeRead, \_\_CrestSchedulerBeforeWrite, and \_\_CrestSchedulerAfter to the translated program under test surrounding read and write operations. These commands contain calls to the symbolic scheduler of CONCREST which decides whether the token of execution has to be passed on to the next thread. Thus, the symbolic scheduler keeps track of the steps each thread has taken. In order to do so the symbolic scheduler keeps track of the threads the program has created and stores information about the environment they currently run in.

## **Gathering Symbolic Information**

Another feature of the execution engine is its ability to gather the symbolic information during the execution. For this sake the following commands are instrumented to the program under test.

- \_\_\_CrestLoad This command pushes a value to the symbolic stack of the current thread (Subfigures 2.10c and 2.10d). It takes always two parameters: a concrete value and an address. Doing so the symbolic interpreter is able to gather the information of both the load from a symbolic variable as well as the load of a concrete value. The latter case includes loading values from variables which are not examined by CONCREST as well as loading concrete values for operations like an increment. A \_\_\_CrestLoad command records a read event in the symbolic trace.

- \_\_\_CrestStore Is used to record the symbolic information of a write event. The command takes only one parameter namely the address of the shared variable. In order to record the information it pops a value from the symbolic stack of the current thread and uses it as value for the write to the symbolic variable representing the shared variable within the program under test (Subfigure 2.10f). A \_\_\_CrestStore command records a write event in the symbolic trace.

- \_\_\_CrestApply2 Whenever a condition needs to be checked this command is added by the instrumenter. It takes as parameters an operator which has to be applied and the concrete value of the condition. The operation pops two values from the symbolic stack and applies the desired operator on them. Subsequently the result is pushed back to the symbolic stack (Subfigure 2.10e). The implemented operations include arithmetic operations like addition, bitvector operations like left shift and compare operations like lower than. When a compare operation has been performed and both operands have had symbolic information a symbolic predicate is stored for later use by the symbolic interpreter. Otherwise only an empty predicate is stored.

- \_\_\_CrestBranch This command is used to gather symbolic information about the branching behaviour of the program under test. It pops a value from the symbolic stack, thus emp-

tying the stack. If a symbolic predicate has been recorded this predicate is logged as a path constraint for the current branch. Otherwise, only the information about entering a new branch is recorded. A \_\_\_CrestBranch command records a branching event in the symbolic trace.

\_\_\_CrestAssertionFailed As mentioned before CONCREST models assertions using two branches. On one branch the assertion is violated which is indicated using this command. The other branch is left empty besides a call to CONCREST's branching function. The assertion-failed command indicates the failed assertion by creating a file. Additionally, a debug message stating in which file and line the error has occurred is printed but no additional information is stored since CONCREST has all required information due to previous commands such as the branch command. After indicating the violated assertion by creating the file crest\_assertion\_violation\_found the program under test is terminated immediately.

Before the program terminates \_\_CrestAtExit is invoked. This function is used to safely terminate the execution of a test. Thus, it writes the recorded symbolic information about the execution to the file szd\_execution. Furthermore, the log-file for the current execution is written to concrest\_log.

Once the execution of the program under test has terminated the time required for the test is recorded. Subsequently, the information stored during the termination of the test is read back from the files and used to update the forest data structure of the algorithm. Moreover, it is checked whether the execution of the program under test reached the predicted branch. If the branch was not reached this misbehaviour is recorded.

#### **Exploration**

The exploration engine uses the gathered information about previous program executions and decides about the next step to be performed. It uses a predefined set of strategies in order to make its decisions.

The algorithm terminates whenever one of the following conditions is met. The timeout feature was enabled and a timeout has occurred. It is possible to test a program using CONCREST and limit the total execution time of CONCREST to a fixed amount of time. Whenever a program execution has finished CONCREST will check whether the total amount of time spent has exceeded the maximal value. In case the timeout was reached the exploration will stop. The second condition to be checked every iteration is the total number of iterations CONCREST has performed. Like the timeout, the maximum number of iterations can be specified as an option. The third condition checks whether the exploration strategy has decided to stop the testing. The exploration strategy will do this for example when all branches are covered and thus no further tests are necessary.

After checking the conditions for termination the exploration engine checks which operation has to be performed next. There are three operations the exploration can decide to perform during one iteration of the algorithm. The basic operation is to test an execution. Once enough information is gathered the exploration engine will decide to perform another test and hand over

control to the execution engine. The execution engine will be given exact instructions about which schedule and inputs have to be used for the execution. The second operation which can be chosen is to perform a realisability check for a given scenario. To do so the next ISC in the queue is selected. For this scenario the constraint systems are then generated and checked for their solutions. If a solution exists the scenario is realisable and a schedule and inputs to the program exists. Thus, an execution job using the schedule and inputs is created. Otherwise, the unrealisability is reported. Furthermore, the unrealisable ISC is examined for possible additional interferences which could make it realisable in a future iteration of the algorithm. In the affirmative case an interference exploration job is added. Otherwise, the failure to generate a schedule is reported and a counter for unrealisable ISCs is increased. The third operation which can be performed by the exploration engine is to do an inference exploration. During this interference exploration every thread in the execution forest is analysed for its possible interferences with other threads.

In order to check for completion CONCREST also tracks the coverage of the program under test. This is done using a predefined coverage measurement strategy. As mentioned previously, the statistics are updated after each (successful) execution of the program under test. For each branch in the program under test a flag is stored marking whether it has been visited or is still undiscovered by the test cases. The same is done for all functions within the program under test. Additionally, the timestamp of the first visit to the branch is recorded for every branch within the program under test.

## Con Crest WMM

This Chapter presents CONCRESTWMM, the tool implemented for this thesis. The following sections describe the different parts of the implemented tool and how they interact with CONCREST and also with each other. Section 3.1 describes the architecture of CONCRESTWMM. Next, in Section 3.2 the scheduling of WMM-events is discussed. The implemented weak memory models are shown in Section 3.3. Special aspects of these models, i.e., memory barriers and Compare and Swap are discussed in Sections 3.4 and 3.6. Limitations and possible extensions of the implementation of CONCRESTWMM are presented and discussed in Section 3.7. An overview of the capabilities of CONCRESTWMM with respect to its completeness for WMM-effects is outlined in Section 3.8. Finally, the ability to limit the execution to a desired behaviour is described Section 3.9.

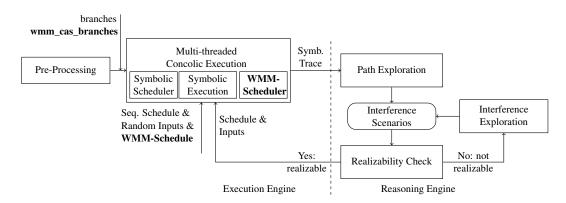

## 3.1 Architecture of ConCrestWMM

The architecture of the WMM-Support is kept simple with only a few ties to CONCREST. Thus, the WMM-Support can be turned off without changes to the behaviour of CONCREST. The WMM-Support was added to CONCREST by adding callbacks to certain functions of CONCREST. These functions are all functions which are instrumented to the program under test during the instrumentation process of CONCREST. Hence, they are no integral part of the execution or reasoning engine but rather its tools. Thus, CONCREST's working principle and its algorithms remain unchanged. Figure 3.1 illustrates the architecture of CONCRESTWMM.

#### WMMScheduler

The symbolic scheduler of CONCREST offers, as will be described in Section 2.4, the possibility to control the execution of the program under test. For this purpose the symbolic scheduler of CONCREST uses the token of execution gl which is passed to a thread of the program under test for the amount of steps the thread has to perform. In order to schedule the effects of a weak memory model a new scheduler, the WMM-Scheduler, was implemented. The WMM-Scheduler

Figure 3.1: Architecture of CONCRESTWMM

| Action                     | Description                                |

|----------------------------|--------------------------------------------|

| Store                      | Record a write event                       |

| Commit                     | Make a write effect visible to all threads |

| Load                       | Read a value                               |

| Compare & Swap             | Perform a compare and swap operation       |

| Memory Barrier Store-Store | Perform a Store-Store barrier              |

| Memory Barrier Store-Load  | Perform a Store-Store barrier              |

| Memory Barrier Load-Load   | Perform a Store-Store barrier              |

Table 3.1: Interface of a Weak Memory Model

offers the possibility to schedule an event at a given point of time, i.e., after a given amount of steps of the symbolic scheduler. This timing relation is realised through callbacks to the WMM-Scheduler which are embedded into the scheduling functions of CONCREST. Additionally these callbacks intercept all actions from the program under test. The WMM-Scheduler will then pass the actions to the desired WMM.

Additionally, the WMM-Scheduler offers the possibility to directly invoke events like compare and swap and memory barriers, as will be explained later. As a result of this, it will be possible to examine the behaviour of the program under test under different environments by simulating different systems and compilers through schedules and instrumentation. The instrumentation processes of CONCREST can also be seen as a pre-compilation/translation step. For example, a compiler might add a memory fence like a LWSYNC directive to the compiled program due to added constraints and directives in the program under test. Using schedules it is possible to imitate behaviour like this using CONCRESTWMM.

#### **WMM**

In order to handle the effects of a specific WMM a new class is introduced. Using object-oriented techniques various different models can be implemented. Like CONCREST the WMM keeps track of all changes to the declared shared variables. A copy of both the concrete and

symbolic memory is kept within the WMM-class. It is thus possible to analyse which value is written to which variable at which point of time during the execution of the program.

Table 3.1 shows the interface of a WMM. The three basic operations of a WMM are Store, Commit and Load. A store operation is performed for every write access to an address which was declared as shared variable. This operation executed whenever a \_\_CrestStore is performed in the instrumented program under test. Load operations are performed every time a read access from a shared variable occurs, i.e., a \_\_CrestLoad operation is performed in the instrumented program under test. The load operation has to return the value for the executing thread will observe for the address with respect to the modelled WMM. A commits are used to make the effect of a write visible to all threads. Hence, there is no corresponding operation in CONCREST. The Compare and Swap operation is command introduced by CONCRESTWMM which can be added to the program under test. A detailed description of the operation and its semantics are in Section 3.6. Memory barriers are inserted in programs in order to guarantee a certain state of the memory model with respect to uncommitted writes. Memory barriers and their effects are discussed in more detail in Section 3.4.

#### WMM-Wrapper

In order to comply with the standards of CONCREST the possibility to invoke functionality of the WMM-Scheduler directly from non-object oriented C-code had to be added. This was done in a similar fashion as it is done in CONCREST by creating a wrapper around the WMM-Scheduler. To do so a single reference to the WMM-Scheduler was introduced which is used over the whole runtime of CONCREST. However, since CONCREST currently does not use concurrency in its algorithms no data-races occur. Additionally, the program under test is only executed in a single threaded manner and all operations of the WMM-Scheduler can be seen as atomic. The reference is initialised using a created "Init"-function to which a callback was added to \_\_\_CrestInit.

#### **Building CONCRESTWMM**

The build script of new features for CONCRESTWMM was added to the existing build infrastructure of CONCREST. Thus, there are no high level changes in the build process.

Since all WMM related code within CONCRESTWMM is guarded using preprocessor directives the WMM-Support can be ruled out by removing the define of the USE\_WMM constant from the build process. Thus, a version of CONCREST will be built.

## 3.2 Scheduling of Events for Weak Memory Models

As described previously the WMM-Scheduler allows to schedule events during the execution of the program under test.

#### **Challenges for WMM-Schedules**

An event of the WMM-Scheduler, like a commit, needs in addition to its time-code the variable/address for which it has to be applied. However, one of the main challenges for developing a

scheduler was creating a way of declaring variables for which the scheduler should be able to examine WMM-effects and thus, using them in its schedules. The difficulty mainly arises from the fact that at the moment the generation of schedules for the WMM-Scheduler is not automatic. As a result of this schedules are written by hand to perform experiments in addition to the schedules generated by CONCREST. Thus, neither CONCREST nor the WMM-scheduler has information about the shared variables for which the simulation of effects is of interest. CONCREST already has a facility to declare shared variables. However, this facility is not enough at the moment. Shared variables are declared to CONCREST by explicitly stating this fact in the code by adding a statement like CREST shared int(x); for a variable x at the beginning of the program under test. The problem with this approach is that there is still no information about shared variables outside the code, i.e., the information is only available during runtime. Thus, at runtime only the addresses of shared variables were known to CONCREST, while the WMM-schedules needed some way of stating which variable has to be affected by a particular event in the schedule. The problem with addresses is of course that they are changing with each program run. Thus, if a schedule would be created using addresses it would not be applicable for a future re-run of the test case.

In order to solve this problem the WMM-Scheduler is equipped with the function <code>NewSharedVariable</code> mapping addresses to an identifier and a type. The identifiers are then substituted for concrete addresses when a call to the function <code>ReadSchedule</code> is performed. The function <code>NewSharedVariable</code> takes the parameters address, type, value and name. The name is a text representation of the variable name which can then be used to address this variable in a schedule for the WMM-Scheduler. However, it is not required that the name of the variable in the source code coincides with the name handed to the WMM-Scheduler via the declaration function. It has to be mentioned that in the current implementation the type parameter might seem to be unnecessary as it imitates the behaviour of CONCREST where the declaration function has to be chosen according to the data type of the variable. Nevertheless, the type parameter is necessary since the WMM-Support also deals with concrete values and thus needs to copy them, for which the type of the variable is needed. The value parameter of the function <code>NewSharedVariable</code> was introduced in order to pass the current value of the variable to the internal memory of the WMM-Scheduler.

The function ReadSchedule is intended to be invoked once all shared variables are declared. First it will check if there exists a schedule for the WMM-Scheduler. This check was introduced in order to enable the execution engine to execute tests without WMM-effects. In case no schedule file exists the WMM-Scheduler will load Sequential Consistency as default model and turn on the auto-commit functionality. This auto-commit functionality will invoke the commit operation of the WMM-Scheduler after each store operation. If there exists a schedule then the WMM-Scheduler will create a copy of this schedule and substitute all declared shared-variables for their addresses using the previously mentioned variable names. After this substitution the substituted schedule file is read line by line by the scheduler. While the first line specifies which memory model has to be used the remaining lines specify which effect of the selected WMM will happen at which point of time. Schedules entries are related to points of times. As a consequence of this WMM-schedules have to be created with respect to schedule for CONCREST. The schedule for CONCREST fixes when store and load operations will occur

| <b>Event ID</b> | Name                       | Description                                     |