# Compilation for Predictable Real-Time Systems

## **DIPLOMARBEIT**

zur Erlangung des akademischen Grades

# **Diplom-Ingenieur**

im Rahmen des Studiums

# **Software Engineering & Internet Computing**

eingereicht von

# **Ludwig Meier**

Matrikelnummer 0526541

| an der<br>Fakultät für Informatik der T | echnischen Universität Wien     |                          |

|-----------------------------------------|---------------------------------|--------------------------|

| Betreuung: Ao.Univ.Prof. Di             | plIng. Dr.techn. Peter Puschner |                          |

|                                         |                                 |                          |

|                                         |                                 |                          |

| Wien, 7. September 2014                 |                                 |                          |

|                                         | (Unterschrift Verfasser)        | (Unterschrift Betreuung) |

|                                         |                                 |                          |

# Compilation for Predictable Real-Time Systems

# MASTER'S THESIS

submitted in partial fulfillment of the requirements for the degree of

# **Master of Science**

in

# **Software Engineering & Internet Computing**

by

# **Ludwig Meier**

Registration Number 0526541

| to the Faculty of Informatics at the Vienna University of T | echnology                       |                        |

|-------------------------------------------------------------|---------------------------------|------------------------|

| Advisor: Ao.Univ.Prof. Di                                   | plIng. Dr.techn. Peter Puschner |                        |

|                                                             |                                 |                        |

|                                                             |                                 |                        |

|                                                             |                                 |                        |

| Vienna, September 7, 2014                                   | (Signature of Author)           | (Signature of Advisor) |

|                                                             |                                 |                        |

# Erklärung zur Verfassung der Arbeit

| Ludwig Meier                |   |

|-----------------------------|---|

| Klimtgasse 6/6/6, 1130 Wien | a |

|                             |   |

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

| (Ort, Datum) | (Unterschrift Verfasser) |

|--------------|--------------------------|

# Danksagung

Zuallererst danke ich meiner Partnerin Christiane, ohne deren Unterstützung und Motivation ich diese Arbeit wohl nie abgeschlossen hätte. Ebenso danke ich meiner Familie für Ihre Unterstützung. Meine Cousins Josef und Ferdinand, die zur selben Zeit mit mir studierten, waren mir mit ihrem Erfahrungsschatz eine große Hilfe während meines gesamten Studiums.

Außerdem danke ich Herrn Puschner für die Möglichkeit meine Diplomarbeit zu einer derart spannenden Thematik zu verfassen.

# Abstract

Real-Time systems require guarantees on the execution time of the executed programs, commonly at least a Worst-Case Execution-Time (WCET) bound. The complexity of today's computing architectures makes it difficult to predict the execution timing of a program.

The single-path programming scheme improves timing predictability by eliminating the selection of different execution paths depending on the input data provided to the program. Such programs execute the exactly same sequence of instructions for every invocation.

This document describes the automated transformation to a single-path program from annotated source code. The transformation consists of a dataflow analysis to identify the input-data dependent branches in the program and a transformation phase that replaces these branches by utilizing conditional execution, i.e., predicated instructions.

# Kurzfassung

Echtzeitsysteme benötigen Garantien zum Laufzeitverhalten der ausgeführten Programme, üblicherweise zumindest eine Schranke der maximalen Ausführungszeit (WCET). Die Komplexität heutiger Computer-Architekturen macht es allerdings schwierig das Laufzeitverhalten eines Programmes vorherzusagen.

Die Single-Path Programmier-Methodik vereinfacht die Vorhersage des Laufzeitverhaltens dadurch, dass vermieden wird, dass Eingangsdaten die Auswahl des Ausführungspfads beeinflussen. Derartige Programme führen bei jeder Ausführung exakt die gleiche Befehlssequenz durch.

Dieses Dokument beschreibt die automatische Übersetzung von annotiertem Quellcode in ein Single-Path Programm. Diese Übersetzung besteht aus einer Datenflussanalyse zur Bestimmung der eingangsdatenabhängigen Verzweigungen und einer Übersetzungsphase, die diese Verzweigungen durch bedingt ausgeführten Maschinencode ersetzt.

# Contents

| 1            | Intr            | roduction                           | 1   |

|--------------|-----------------|-------------------------------------|-----|

| 2            | The 2.1 2.2 2.3 | Single-Path Code                    | 4   |

| 3            | Inp             | ut-Data Dependencies                | 23  |

|              | 3.1             | Dataflow                            | 23  |

|              | 3.2             | Determining Input-Data Dependencies | 30  |

|              | 3.3             | Annotations                         | 42  |

| 4            | Tra             | nsformation                         | 45  |

|              | 4.1             | Transformation Overview             | 46  |

|              | 4.2             | Loops                               | 47  |

|              | 4.3             | Branches                            | 66  |

|              | 4.4             | Function Calls                      | 87  |

|              | 4.5             | Code Generation                     | 91  |

| 5            | Res             |                                     | 101 |

|              | 5.1             | Runtime                             | 101 |

|              | 5.2             | Cost Drivers                        | 109 |

| 6            | Con             | aclusion and Outlook                | 113 |

| $\mathbf{A}$ | App             | pendix                              | 116 |

|              | A.1             | Call Graphs                         | 116 |

|              |                 | Execution-Time Distributions        |     |

|              |                 | Listings                            |     |

| Bi           | bliog           | graphy                              | 137 |

CHAPTER 1

# Introduction

Real-Time systems require guarantees on the execution times of the programs executed. A common requirement for a program executed by a real-time system is the knowledge about its Worst-Case Execution-Time (WCET) bound. Only then it can be guaranteed that the real-time system meets its timing requirements. The complexity of today's computing-architectures makes it difficult to predict the execution timing of a program.

The single-path programming scheme improves timing predictability by eliminating the selection of different execution paths to depend on the input data provided to the program. It does so by replacing input-data dependent branches by input-independent branches and constant-time conditional expressions. The constant-time conditional expression allows to assign a condition, which controls the execution, to a program expression. The execution of the constant-time conditional expression is expected to take a single, constant execution time. As a consequence the execution time is predictable.

This document describes the automated generation of a single-path program from annotated source code. The single-path code generation is integrated into the LLVM compiler. Since the ARM¹ architecture targeted by this work does not immediately provide machine instructions forming constant-time conditional expressions, the transformation is implemented by using conventional conditional execution. The conditional execution used is not guaranteed to execute in constant time, therefore the resulting program is neither guaranteed to execute in constant time but the execution-time predictability is improved.

The transformed programs simplify the WCET-analysis since only a single execution path has to be considered in the analysis. Since this single execution path does not differ amongst program executions, timing anomalies [48] cannot arise from differing instruction-fetching patterns. And even without the availability of a constant-time conditional expression the absolute execution-time jitter is reduced.

Chapter 2 gives an introduction to single-path programs and explains how any WCET-bounded program may be automatically transformed into a single-path program.

<sup>&</sup>lt;sup>1</sup>Acorn RISC<sup>2</sup> Machines, later Advanced RISC Machines

As a prerequisite for the transformation the input-data dependent branches need to be identified. Therefore a dataflow-analysis pass has been implemented, which is described in Chapter 3.

The implementation of the single-path transformation is shown in Chapter 4. The initial transformation steps, in the target-independent portion of the compilation process, prepare the loops and branches so that in a later, target-specific transformation pass, it is easier to generate single-path code.

In Chapter 5 the impact this transformation has on the execution time of the transformed programs is evaluated.

# CHAPTER 2

# Theory

| Contents |                                               |

|----------|-----------------------------------------------|

| 2.1      | Single-Path Code                              |

| 2.2      | Single-Path Conversion                        |

| 2.3      | Single-Path Conversion from a CFG Perspective |

|          | 2.3.1 Reducible Control Flow                  |

|          | 2.3.2 Optimizations                           |

|          | 2.3.3 Irreducible Control Flow                |

|          |                                               |

# 2.1 Single-Path Code

Single-Path code [35] has the key property to show the same execution trace for each execution. In conventional programs the actual execution trace depends on the input data provided to the program. In single-path programs a unique execution trace exists, that is executed independent from the provided input data. This is achieved by replacing branches that depend on input data by input-data independent branches and the use of conditional expressions.

For timing predictability the use of a constant-time conditional expression [35] is suggested. The constant-time conditional expression is, as its name implies, expected to execute in constant time, independent from the actual condition value, and therefore has predictable execution timing.

## 2.2 Single-Path Conversion

The single-path conversion is a transformation scheme to generate single-path code from any WCET<sup>1</sup>-bounded program. A detailed set of transformation rules for a high-level language has been presented in [36]. These transformation rules are reproduced in Table 2.1.

| Construct S                                    |                      | Translated Construct $SP[\![S]\!]\sigma\delta$                                           |

|------------------------------------------------|----------------------|------------------------------------------------------------------------------------------|

| $\overline{S}$                                 | $\text{if }\sigma=T$ | S                                                                                        |

| <i>D</i>                                       | otherwise            | $(\sigma)S$                                                                              |

| $S_1; S_2$                                     |                      | $SP[[S_1]]\sigma\delta;$                                                                 |

|                                                |                      | $SP[[S_2]]\sigma\delta$                                                                  |

| if $cond$ then $S_1$                           | if $ID(cond)$        | $guard_{\delta} := \sigma;$                                                              |

| $\mathtt{else}\ S_2$                           |                      | $SP[[S_1]]\langle \sigma \wedge guard_{\delta}\rangle\langle \delta+1\rangle;$           |

|                                                |                      | $SP[[S_2]]\langle \sigma \wedge \neg guard_{\delta} \rangle \langle \delta + 1 \rangle$  |

|                                                | otherwise            | if $cond$ then $SP \llbracket S_1  rbracket{ } \llbracket \sigma \delta$                 |

|                                                |                      | else $SP \llbracket \ S_2 \  rbracket^{\sigma \delta}$                                   |

| while $cond$                                   | if $ID(cond)$        | $end_{\delta} :=$ false                                                                  |

| $\maxN{\rm times}$                             |                      | for $count_\delta := 1$ to $N$ do begin                                                  |

| $\mathtt{do}\ S$                               |                      | $SP[\![$ if $\neg cond$ then $end_{\delta}$ := true $[\![]\sigma\langle\delta+1\rangle;$ |

|                                                |                      | $SP \llbracket$ if $\lnot end_\delta$ then $S$                                           |

|                                                |                      | end                                                                                      |

|                                                | otherwise            | while $cond$ do $SP \llbracket \ S \ \rrbracket \sigma \delta$                           |

| call proc $p(pars)$                            | $\text{if }\sigma=T$ | call proc $p(pars)$                                                                      |

|                                                | otherwise            | call proc $p	ext{-sip}(\sigma, pars)$                                                    |

| $\overline{\hspace{1.5cm}}$ def proc $p(pars)$ |                      |                                                                                          |

| S                                              |                      | $\texttt{def proc} \ p\text{-}\texttt{sip}(pcnd, \ pars)$                                |

|                                                |                      | $SP[[S]]\langle pend\rangle\langle 0\rangle$                                             |

Table 2.1: Single-Path Transformation Rules, taken from [36] p. 388

The rules presented in Table 2.1 show a mapping from source constructs S to the single-path transformed construct  $SP[S]\sigma\delta$ . Whereby  $\sigma$  denotes a boolean execution condition and  $\delta$  is used to create a unique numbering for the different execution conditions. The function ID(cond) maps to true, when the condition cond depends on input data, to false otherwise.

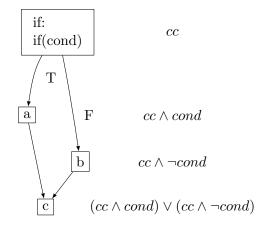

## 2.3 Single-Path Conversion from a CFG Perspective

This section takes an alternative view of the single-path transformation. Instead of the procedural approach from Section 2.1 the observations described in this section are based on the control-flow graph representation of a program.

<sup>&</sup>lt;sup>1</sup>Worst-Case Execution Time

**Motivation** As stated in [35] the single-path conversion is applicable to any program for which a WCET bound is computable, i.e., an upper bound for the number of loop iterations can be determined. This section should clarify why this is the case by showing a transformation that is applicable to all programs which have reducible control flow. The remaining programs, having irreducible control flow, may be transformed into reducible ones in a preprocessing step by using an algorithm like node splitting.

#### 2.3.1 Reducible Control Flow

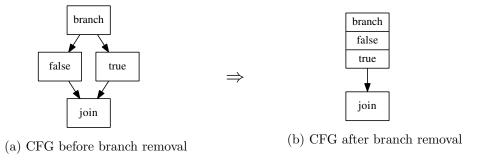

In this section it is shown how the single-path transformation [35] can be applied to programs with reducible control flows. In the conventional description of the single-path transformation the rules used to describe the transformation are based on an imperative language. These rules can be found in [36] on Table 1. The CFG<sup>2</sup> representation has the advantage of a much simpler structure than the source-code representation. Additionally, when restricting to reducible control flows, it has been shown that the entire CFG can be processed by two transformations  $T_1$  and  $T_2$ . The transformations  $SPT_1$  and  $SPT_2$ , which are based on  $T_1$  and  $T_2$ , are described below. The original description of if-conversion is also limited to reducible control flows as described in the section about backward branches in [3] on page 183 ff.

Reducible graphs [1] have the property that the repeated generation of maximum intervals [6] (sometimes called Allen-Cocke intervals) and the replacement of these intervals by a single node leads to a graph with only one node remaining. An alternative reducibility test is described in [42].

Reducible graphs also have the property of collapsibility [18].

Collapsibility Collapsibility represents the fact that repeated application of the two transformations  $T_1$  and  $T_2$  results in a single remaining node on reducible graphs. The following paragraphs give a short summary of these transformations. For the detailed description please refer to [18] on page 249.

$T_1 = removal \ of \ self-loops$

$T_2 = collapsing \ of \ a \ node \ with \ a \ single \ direct \ ancestor \ into \ that \ ancestor$

Collapsibility transformations as defined in [18] on page 249

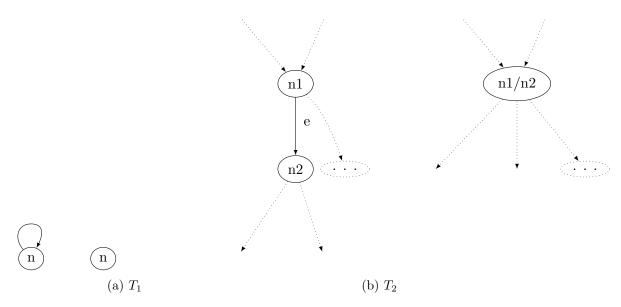

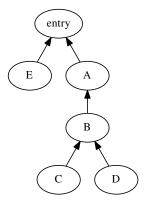

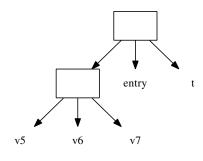

The transformations  $T_1$  and  $T_2$  are shown in a graphical notation in Figure 2.1a and Figure 2.1b.

<sup>&</sup>lt;sup>2</sup>Control-Flow Graph

Figure 2.1: Collapsibility transformation rules

#### Modifying the Collapsibility Test to Determine Execution Conditions

Here a modified collapsibility test is used to show that it is possible to determine execution conditions for all nodes in reducible control-flow graphs.

The Results The algorithm presented here yields a modified CFG that is branch free with the exception of loop-back-edge branches. Essentially creating a chain of all the nodes in the CFG. Additionally an execution condition is calculated for each CFG node. These conditions compensate the fact that the execution of the program with the modified control flow will process nodes that it would not in the original program.

**The Algorithm** The modified collapsibility test SPT() is shown as Algorithm 2.1. As the original variant it repeatedly executes 2 sub-procedures. These sub-procedures  $SPT_1(n)$  and  $SPT_2(n_1, n_2)$  are presented in Algorithm 2.3 and Algorithm 2.4.

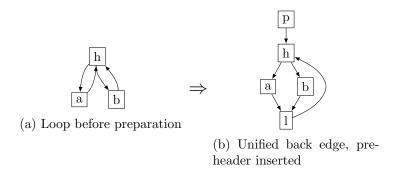

As a preprocessing step for the following algorithm all loops must have been modified so that they have exactly one back edge. This may be achieved by inserting a new loop-latch node.

Then the modified collapsibility test is applied to the CFG. It computes an execution predicate for every node in the CFG. After the modified collapsibility test has been applied, for every CFG node n the variable  $\sigma_n$  holds the predicate under which n shall execute. When the reducibility test completely reduces a graph, every node except the initial node must have been used as node n2 on transformation  $T_2$ . Since the modified variant of  $T_2$  does the predicate calculation, every node except the initial one has an execution predicate calculated. The initial node's predicate will remain true unless it is also a loop-header node and has therefore a loop-termination predicate assigned. Since the program execution always enters a function in its entry point represented by the

initial node in the CFG this node will always be executed. Therefore no execution condition is expected for the initial graph node.

The following algorithm analyzes the conditions that determine which control-flow path is taken during program execution. Assuming that two nodes u and w are adjacent, for any edge from node u to node w,  $C_{uw}$  denotes the condition that must hold for the edge from u to w being executed. When u has only one outgoing edge,  $C_{uw} \equiv \top$ . Note that  $C_{uw}$  only contains the conditions local to the basic-block u, i.e. the condition required for node w to be executed if node u is executed.

Note that parts of the algorithm that are tagged with [code] are not executed with the algorithm, but denote additions to the transformed program's code.

```

Algorithm 2.1: SPT(G)

\overline{\text{Input}}: A reducible program with CFG G = (N, E)

Output: A CFG G_{SP} = (N_{SP}, E_{SP}) of a corresponding single-path program and

a set of execution-conditions \Sigma_{SP} for the nodes in N_{SP}

Data: N_{SP}, E_{SP}, \Sigma_{SP}

1 SP_{INIT}();

2 while |N| > 1 do

if \exists e = \langle n_1 \rightarrow n_2 \rangle \in E, n_1 \equiv n_2 then

3

/* node with a self loop */

SPT_1(n);

4

else if \exists n_2 \in N, where n_2 only has incoming edges from n_1 then

5

SPT_2(n_1, n_2);

/* node with an unique predecessor */

6

7

else

ERROR, input CFG is not reducible;

end

9

10 end

11 CreateLoopCounters();

12 return G_{SP} = (N_{SP}, E_{SP}), \Sigma_{SP};

```

**Analysis Results** The results of the analysis presented in this section are:

$N_{SP}$  The set of nodes for the single-path program. This is the same set as given in the input CFG.

$E_{SP}$  The set of edges for the single-path program.

$\Sigma_{SP}$  An execution condition  $\sigma_n$  for every node  $n \in N_{SP}$ .

The resulting CFG  $G_{SP} = (N_{SP}, E_{SP})$  is a single-path program. The edges in  $E_{SP}$  form a chain with the nodes in  $N_{SP}$ . The only branches remaining in  $G_{SP}$  are those forming loops. When executing the program, the nodes in  $N_{SP}$  must only be executing when their corresponding execution condition in  $\Sigma_{SP}$  is met.

#### Initialization

Initially the condition  $\sigma_n$  for the start node is set to true, for each other node to false.

$$\forall n \in CFG : \sigma_n = \begin{cases} \top, & \text{if } n = \text{start node} \\ \bot, & \text{otherwise} \end{cases}$$

Additionally, each node n has a loop-membership label L attached, which is initialized to  $\emptyset$ , meaning that the node does not yet belong to any loop. This label is subsequently used to store the header node of the innermost loop that contains node n.

$$\forall n \in CFG : n.L = \emptyset$$

Further all graph edges are annotated by the labels S and T, whereby label S holds a reference to the edge's source node and label T that hods the edge's target node.

```

Algorithm 2.2: SPT_{INIT}

```

```

1 Remove the edge n \to n Introduce new loop-termination variable \gamma_h;

2 forall the nodes n \in CFG do

n.L \longleftarrow \varnothing;

/* loop membership */

if n \equiv START then

4

\sigma_n \longleftarrow \top;

5

6

\sigma_n \longleftarrow \bot;

7

8

9 end

10 forall the edges e = \langle u \to w \rangle, e \in CFG do

e.S \longleftarrow u;

/* source label */

e.T \longleftarrow w;

/* target label */

12

e.E \longleftarrow w;

/* exiting edge */

13

14 end

15 N_{SP} \longleftarrow \emptyset;

/* nodes in the SP-Program */

16 E_{SP} \longleftarrow \emptyset;

/* edges in the SP-Program */

```

### $SPT_1$

The transformation  $SPT_1(n)$ , as well as the original transformation  $T_1(n)$ , removes self loops of node n. The loop back edge  $e_{back} = \langle n \to n \rangle$  at the application time of  $SPT_1()$  may have different endpoints than the back edge had in the initial graph. The original start and end nodes are stored in edge labels. With the original start node  $u \equiv e_{back}.S$  and the original target node  $h \equiv e_{back}.T$

The loop is extended by an additional loop termination variable  $\gamma_h$ . The loop is considered active, as long as  $\gamma_h \equiv \varnothing$ . When the loop is left,  $\gamma_h$  identifies the edge through which the loop exited. The lines in Algorithm 2.3 that are prefixed with [code] are not considered to be executed with the algorithm. Instead the resulting program should be extended with these code snippets. These code snippets will manipulate  $\gamma_h$  at the program execution time.

The loop termination variable is initialized when the loop header h is entered from outside the loop. An implementation may append this assignments at the end of each node originating an edge incoming to h. Let  $E_{in}$  be the set of entering edges  $e_{in}$  targeting the loop header h excluding the back edge, with  $i \equiv e_{in}.S$  and  $h \equiv e_{in}.T$  being the edge endpoints in the original graph.

$$\gamma_h = \begin{cases} \varnothing, & \text{if } \sigma_i \wedge C_{ih} \\ \bot, & \text{otherwise} \end{cases}$$

Let  $E_{exit}$  be the set of exit edges  $e_{exit}$  leaving the node n except the back edge, with  $u_e \equiv e_{exit}.S$  and  $w_e \equiv e_{exit}.S$  being the edge endpoints in the original graph. The source node  $u_e$  of the exit edge is part of the loop, the node  $w_e$  is not contained within the loop. Set the loop termination variable to the following node outside the loop, whenever the loop is left through any of the exiting edges. For each edge  $\langle u_e, w_e \rangle \in E_{exit}$ , at the end of  $u_e$  set  $\gamma_h = w_e$  when  $C_{u_ew_e}$  is met.

For each node originating an exiting edge, store the loop membership in the loop tags attached to each node by setting them to the loop header. Existing loop memberships are not overwritten. This way the loop membership tag refers to the innermost loop containing the node.

$$\forall e \in E_{exit} : E.S.L \longleftarrow h$$

Set the execution condition of the loop header to regard the new loop termination variable. Since the loop header had the loop back edge as an incoming edge until now, it has not yet set another execution condition by  $SPT_2$ .

$$\sigma_h = \gamma_h \equiv \varnothing$$

Replace the back edge  $u \to h$  by a input-independent loop enclosing u and w.

#### Algorithm 2.3: $SPT_1(n)$

```

1 e_{BACK} \leftarrow \langle n \rightarrow n \rangle;

/* back edge */

\mathbf{2} \ h \longleftarrow e_{BACK}.T;

/* loop header */

/* loop latch */

s l \leftarrow e_{BACK}.S;

4 E = E \setminus e_{BACK};

/* remove the edge e_{BACK} */

5 Introduce new loop-termination variable \gamma_h;

6 forall the edges e_{in} = \langle i \rightarrow n \rangle, e_{in} \in IN(n) do

/* when the control flow follows e_{in} */

7 | [code] \gamma_h \leftarrow \varnothing;

8 end

9 forall the edges e_{EXIT} = \langle u_e \rightarrow w_e \rangle, e_{EXIT} \in OUT(n) do

/* When this loop is terminated by e_{EXIT}

*/

[code] \gamma_h \longleftarrow w_e;

/* when the control flow follows e_{EXIT} */

10

if w_e.S.L \equiv \emptyset then

11

w_e.S.L \longleftarrow h;

/* innermost loop containing w_e.S */

12

end

13

14 end

/* In case an edge originating from an inner loop also terminated

this loop

/* when \neg \sigma_l \wedge \gamma_h \equiv \varnothing */

15 [code] \gamma_h \longleftarrow \bot;

16 h.L \longleftarrow h;

17 \sigma_h \longleftarrow \gamma_h;

/* \gamma_h holds all conditions controlling loop execution */

18 E_{SP} \longleftarrow E_{SP} \cup \langle n.E \rightarrow n \rangle;

/* loop back edge in the SP-Program */

```

### $SPT_2$

Whenever the transformation  $T_2$  is applied to the nodes  $n_1$  and  $n_2$ , let E be the non-empty set of edges from  $n_1$  to  $n_2$ .

The condition  $\sigma_{n_2}$  of node  $n_2$  is set to:

$$\sigma_{n_2} = \sigma_{n_2} \vee \bigvee_{e(u,w) \in E} \begin{cases} \bot, & \text{if } w.L \equiv w, \text{ incoming edge is expected to set } \gamma_w \\ \gamma_{u.L} \equiv w, & \text{if } u.L \not\equiv \varnothing, \text{ loop exiting edge} \\ \sigma_u \wedge C_{uw}, & \text{if } u.L \equiv \varnothing \end{cases}$$

Note that the edges  $e = \langle n_1 \to n_2 \rangle$  keep references to their original source and destination nodes in the labels e.S and e.T denoted as u and w here, even when these nodes got collapsed by an earlier application of  $SPT_2$ . In the example below these nodes are shown as labels next to edge endpoints.

### Algorithm 2.4: $SPT_2(n_1,n_2)$

```

1 forall the multi-edges e \in E(n_1, n_2) do

u \longleftarrow e.S;

w \longleftarrow e.T;

3

if w.L \equiv w then

4

do nothing;

5

else if u.L \not\equiv \emptyset then

6

\sigma_{n_2} \longleftarrow \sigma_{n_2} \lor (\gamma_{u.L} \equiv w)

7

8

\sigma_{n_2} \longleftarrow \sigma_{n_2} \vee (\sigma_u \wedge C_{uw})

9

10 end

11 forall the edges e = \langle u, w \rangle, e \in OUT(n_2) do

E \longleftarrow E \setminus e \cup \langle n_1 \rightarrow w \rangle;

/* copy labels from e to the new edge */

13 end

14 N \longleftarrow N \setminus n_2;

/* remove n_2 */

15 E_{SP} \longleftarrow E_{SP} \cup \langle n_1.E \rightarrow n_2 \rangle;

16 n_1.E \longleftarrow n_2.E;

```

#### **Evaluating the Execution Conditions**

The execution conditions  $\sigma_n$  calculated for any node n are not globally valid. Instead they have to be evaluated right before node n is entered and must keep its value until the next execution of node n. Any further condition evaluation, that refers to  $\sigma_n$ , has to use this stored value because a re-evaluation could yield different results due to modifications to the variable space done in the meantime.

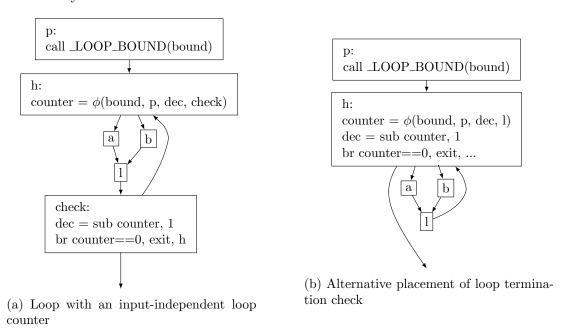

**Update Control Flow** When no further applications of  $SPT_1$  and  $SPT_2$  are possible, the applications of  $SPT_2$  established a chain of nodes in  $E_{SP}$ . The only branches remaining are the loop-back edges introduced by  $SPT_1$ . These loops are transformed into loops executing for an input-data independent iteration number by the execution of CreateLoopCounters().

In addition, the single-path transformation requires a so called constant-time conditional expression as presented in Section 3.1 of [35].

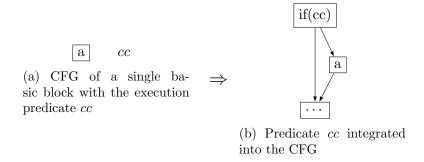

After application of the modified collapsibility test, the constant-time conditional expression can be applied to all nodes n except the new loop nodes created by Cre-ateLoopCounters(), whereby  $\sigma_n$  is the condition that controls execution. The other side of the constant-time conditional expression remains empty.

### **Algorithm 2.5:** CreateLoopCounters( $N_{SP}$ , $E_{SP}$ )

```

1 forall the back-edges e_{BACK} = \langle h \rightarrow l \rangle, e_{BACK} \in E_{SP} do

E_{SP} \longleftarrow E_{SP} \setminus e_{BACK};

/* remove e_{BACK} */

/* create a new loop-header h^\prime */

N_{SP} \longleftarrow N_{SP} \cup h';

3

/* Integrate h' into the control-flow

e_o = \langle l \rightarrow n_o \rangle \longleftarrow OUT(l); /* There is at most one outgoing edge */

4

E_{SP} \longleftarrow E_{SP} \setminus e_o;

\mathbf{5}

E_{SP} \longleftarrow E_{SP} \cup \langle h' \rightarrow n_o \rangle;

6

forall the edges e_i = \langle n_i \to h \rangle, l_o \in IN(h) do

7

E_{SP} \longleftarrow E_{SP} \setminus e_i;

8

E_{SP} \longleftarrow E_{SP} \cup \langle n_i \rightarrow h' \rangle;

9

end

10

E_{SP} \longleftarrow E_{SP} \cup \langle h' \rightarrow h \rangle;

11

E_{SP} \longleftarrow E_{SP} \cup \langle l \rightarrow h' \rangle;

12

/* h' should take the branch h' 	o h as long as the input-data

independent iteration bound is not hit. Afterwards the edge

h' \rightarrow n_o is executed.

13 end

```

The Need for WCET Boundedness When transforming a program to an SP<sup>3</sup>-program, loops need to be modified so they show a unique iteration pattern regardless of the program's input data. This may be achieved by always iterating the loop for its iteration upper-bound. Such an upper bound must exist when the program is WCET-Bounded, although it may not be easy to determine.

**Properties of the Resulting Control Flow** The resulting control flow has no branches, except the ones introduced when transforming the loops. Since the loops are guaranteed to execute the same iteration count pattern for every call, the execution path for every call must be the same since no other branches exist in the program.

#### **Example Transformation**

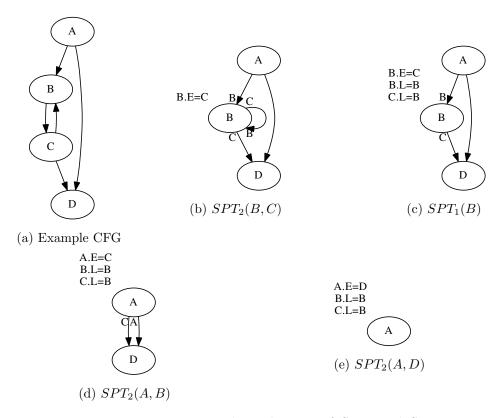

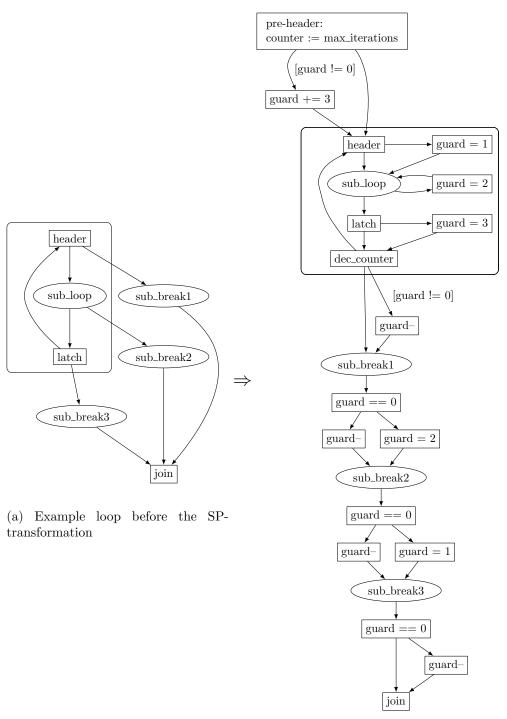

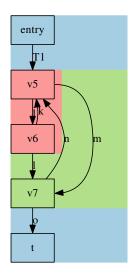

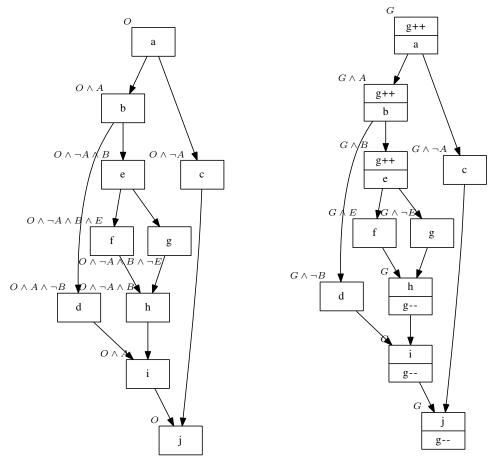

The example in Figure 2.2 illustrates the application of the modified collapsibility test to a simple CFG.

<sup>&</sup>lt;sup>3</sup>Single-Path

Figure 2.2: Example application of  $SPT_1$  and  $SPT_2$

| Trans-<br>formation |            |                               |                          |                                                       |                      |

|---------------------|------------|-------------------------------|--------------------------|-------------------------------------------------------|----------------------|

| Step                | $\sigma_A$ | $\sigma_B$                    | $\sigma_C$               | $\sigma_D$                                            | addition to $E_{SP}$ |

|                     | Т          | Τ                             |                          | Τ                                                     |                      |

| $SPT_2(B,C)$        | Т          |                               | $\sigma_B \wedge C_{BC}$ | Τ                                                     | $B \rightarrow C$    |

| $SPT_1(B)$          | Т          | $\gamma_B \equiv \varnothing$ | $\sigma_B \wedge C_{BC}$ | Τ                                                     | $C \rightarrow B$    |

| $SPT_2(A,B)$        | Т          | $\gamma_B \equiv \varnothing$ | $\sigma_B \wedge C_{BC}$ | Τ                                                     | $A \rightarrow B$    |

| $SPT_2(A,D)$        | Т          | $\gamma_B \equiv \varnothing$ | $\sigma_B \wedge C_{BC}$ | $(\gamma_B \equiv D)$ $\vee (\sigma_A \wedge C_{AD})$ | $C{ ightarrow} D$    |

Table 2.2: Calculation of the execution-conditions in the example shown in Figure 2.2

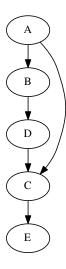

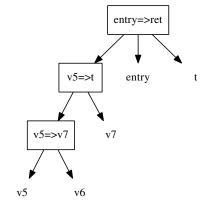

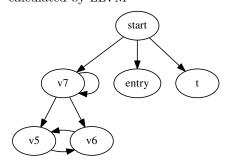

**Update Control Flow** The result of the analysis phase for the example given in Figure 2.2 are:

$$\begin{split} N_{SP} &= \{A, B, C, D\} \\ E_{SP} &= \{B \rightarrow C, C \rightarrow B, A \rightarrow B, C \rightarrow D\} \\ \Sigma_{SP} &= \{\sigma_A = \top, \sigma_B = \gamma_B \equiv \varnothing, \sigma_C = \sigma_B \land C_{BC}, \sigma_D = (\gamma_B \equiv D) \lor (\sigma_A \land C_{AD})\} \end{split}$$

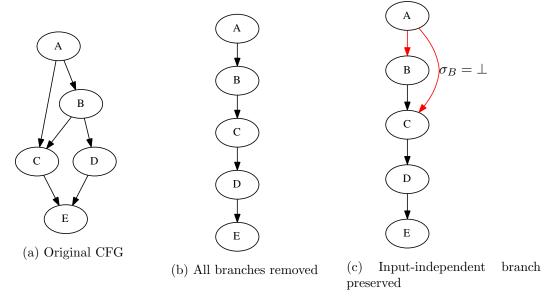

In Figure 2.3 the graph is shown after having created the edges according to the analysis results.

Figure 2.3: The example from Figure 2.2 before application of CreateLoopCounters()

Figure 2.4: The result of applying CreateLoopCounters() to the CFG shown in Figure 2.3

When all the conditions are established, remove all branches except the loop back edges and introduce new branches as specified in  $E_{SP}$ , so that the nodes are lined up in the order they got merged by  $T_2$ .

#### 2.3.2 Optimizations

In the following, modifications to the transformation are described which should reduce the execution runtime of the transformed program.

## Application Order of $SPT_1$ and $SPT_2$

Strive to apply  $SPT_2$  to nodes with the least possible application number of  $SPT_1$ . That means, for applications of  $SPT_1$ , that self loops are only removed for collapsed nodes that only consist of previously collapsed nodes belonging to the natural loop and no other nodes outside the loop. After the transformation is completed, nodes that are not part of the natural loop would require computing time with each loop iteration, whereby the execution predicates for these nodes will evaluate to false for each except the last iteration.

With the SP-Transformation as described Algorithm 2.3 the application of this optimization is mandatory. This is because the resulting algorithm is simpler when the application order of  $SPT_1$  and  $SPT_2$  is constrained as described here. A modified version of the SP-Transformation that allows arbitrary application orders of  $SPT_1$  and  $SPT_2$  can be created by additionally tracking, for each node, the last node that has been col-

lapsed into it by an application of  $SPT_2$ . When  $SPT_1$  is creating back edges as shown in Algorithm 2.3 on line 18 this additionally tracked node shall be used as the originating node of the back edge.

#### Keep Input-Independent Branches

Branches that do not depend on input data may be preserved by the transformation. Compared to the transformation shown in the paragraph *Update Control Flow*, these branches may skip some nodes in the CFG during execution.

Advantage As a result, when executing the transformed program, on occasion program parts are skipped by the preserved branches, resulting in a shorter execution time. Removing these branches instead and disable the effects of the now executed program parts by an application of the constant-time conditional expression to these program parts would yield the same result, but would make the program's execution more computationally expensive.

With the unoptimized transformation any node n of the CFG has to be executed, if the evaluation of  $\sigma_n$  immediately before the execution of n yields true during program execution. When the evaluation of  $\sigma_n$  yields false and the evaluation result does not depend on input-data, the program flow still passes through n. In this case later transformation steps are responsible for isolating the modifications performed in n from the remainder program.

Correctness The optimized transformation presented here is guaranteed to not modify the program's behavior since all nodes that are effectively executed in the unoptimized variant are still executed in the same order. Therefore the preserved branches must not skip any nodes that should be executed, modify the execution order amongst executed nodes, modify the loop termination or introduce new loops.

Algorithm Modification Keeping some of the branches is done by a slightly different modification of the CFG than shown in the paragraph *Update Control Flow*. The modification of the control flow after the analysis phase starts by removing all branches except loop back edges and edges originating from an input-data independent branch. Otherwise the control-flow modifications are performed like shown in Algorithm 2.1. When the control-flow modification would insert an edge that has not been removed, the existing edge is kept.

Result The resulting CFG will at least contain all edges it would after applying the CFG modifications shown in Algorithm 2.1, but possibly containing some additional edges originating from nodes with input-data independent branches. Note, that the edges originating from these branches, which exist in both control flow variants, behave differently in the optimized variant. When their source node is executed, control flow is now only conditionally following these edges. Without the optimization the source node

would have had only one outgoing edge, therefore the control flow always had to follow this edge after executing the source node.

The calculation of the execution conditions has to be adapted to handle these new graph edges. Because nodes can be skipped, it is no longer guaranteed that for any node n the execution condition  $\sigma_p$  has been evaluated for every predecessor node p when the execution reaches node n. When such an edge is executed, it is obvious that any nodes skipped by this edge are not executed. Their execution conditions have therefore to be assumed to evaluate to false.

**Skipped Nodes** The nodes skipped can be derived by examining the applications of  $SPT_2$  in more detail. The result is a set of skipped nodes  $V_{skipped}(E)$  for every edge E originating from an input-independent branch.

Initially the set of skipped nodes  $V_{skipped}(E)$  is empty for all edges E. Additionally for each input-independent branch b a set of all nodes targeted  $V_t(b)$  by this branch is tracked, which initially contains all nodes targeted by outgoing edges from b.

When applying the modified collapsibility test, at some point there will be an application of  $b' = SPT_2(b, n_{to})$  with b being an input-independent branch node and some other node  $n_{to}$  as the second. Remove  $n_{to}$  from the set of branch targets  $V_t(b) = V_t(b) \setminus n_{to}$ . The edge  $b \to n_{to}$  is the outgoing edge from b that would also have been inserted in the unoptimized version of the transformation. When b has been collapsed by an application of  $SPT_1$  or  $SPT_2$  before, use the original branching block whenever referencing  $V_t$ .

For every application of  $SPT_2(n, n_t)$  with  $n_t \in V_t(b)$  and any node n, let N be the set of nodes collapsed into n. Add the nodes in N to the set of skipped nodes by the other outgoing edges from branching node b. When n is the branching node  $n \equiv b$  or a node that "contains" b, only add the nodes collapsed into n after b.

$$\forall n_o \in V_t(b) : V_{skipped}(\langle b, n_o \rangle) = V_{skipped}(\langle b, n_o \rangle) \cup N$$

(2.1)

The list of skipped nodes for the edge  $b \to n_t$  is now complete, so remove  $n_t$  from the set of branch targets  $V_t(b) = V_t(b) \setminus n_t$ . When the set  $V_t(b)$  is empty, the list of skipped nodes for all outgoing edges of branch b is complete.

Adapting Execution Conditions When all branch targets have been removed  $V_t(b) \equiv \emptyset$ ,  $V_{skipped}(n)$  contains the set of skipped nodes for every outgoing edge of the branching node b, with target node n.

With the set of nodes skipped by an edge, one can think of executing the edge  $E = \langle b, n_{to} \rangle$  as setting the skipped nodes execution conditions to false,  $\forall_{s \in V_{skipped}(n_{to})} : \sigma_s = \bot$ , as shown in Figure 2.5c.

Alternatively, whenever any of the execution conditions refers to  $\sigma_s$  where node s is a node skipped by an edge  $E = \langle b, n_{to} \rangle$  branching from node b to the target node  $n_{to}$ , i.e.  $s \in V_{skipped}(E)$ , replace  $\sigma_s$  by  $\sigma_s \wedge \neg(\sigma_b \wedge C_{bn_{to}})$ . So, whenever  $\sigma_s$  would not have been initialized because it was skipped by the edge E, the expression  $\neg(\sigma_b \land C_{bn_{to}})$ evaluates to false. In this case the conjunction with  $\sigma_s$  will always evaluate to false, independent from the value of  $\sigma_s$ .

**Update Control Flow** The control flow modification applied afterwards is very similar to the one presented in Algorithm 2.1, with some additional handling of the now preserved branches. When all the conditions are established, remove all edges except loop-back edges and edges originating from input-data independent branches. Introduce new edges so that the nodes are lined up in the order they got merged by  $SPT_2$ . For every application of  $SPT_2(n1, n2)$  create an edge  $n1.n_{exit} \rightarrow n2.n_{enter}$ .

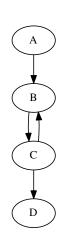

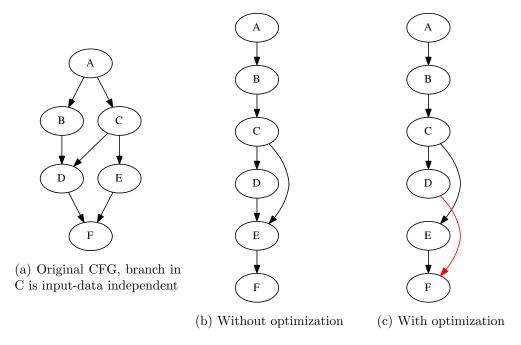

**Example** In the example shown in Figure 2.5a the branching condition in node A is considered being input-data independent, whereas the branching condition in node B is input-data dependent.

Figure 2.5b shows the result of an application of the control-flow modification that does not consider the input dependency of branches, as presented in Algorithm 2.1. In contrast Figure 2.5c finally shows the result of the optimized transformation shown in the previous paragraphs. The process of the execution-condition determination is documented in Table 2.3.

Figure 2.5: Control-Flow modification with preserved branches

|            | Without optimization                                     | Branch preserve optimization                                                                   |

|------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------|

| $\sigma_A$ | Т                                                        | Т                                                                                              |

| $\sigma_B$ | $\sigma_A \wedge C_{AB}$                                 | $\sigma_A \wedge C_{AB}$                                                                       |

| $\sigma_C$ | $(\sigma_A \wedge C_{AC}) \vee (\sigma_B \wedge C_{BC})$ | $(\sigma_A \wedge C_{AC}) \vee ((\sigma_B \wedge \neg(\sigma_A \wedge C_{AC})) \wedge C_{BC})$ |

| $\sigma_D$ | $\sigma_B \wedge C_{BD}$                                 | $(\sigma_B \wedge \neg(\sigma_A \wedge C_{AC})) \wedge C_{BD}$                                 |

| $\sigma_E$ | $(\sigma_C \wedge C_{CE}) \vee (\sigma_D \wedge C_{DE})$ | $(\sigma_C \wedge C_{CE}) \vee (\sigma_D \wedge C_{DE})$                                       |

Table 2.3: Execution-conditions calculation for the example shown in Figure 2.5

Figure 2.6: Control-Dependence Graph for the example shown in Figure 2.5a

Improved Application Order of  $SPT_1$  and  $SPT_2$  in case of Preserved Branches To reduce the programs execution time it is beneficial to skip as many nodes as possible with the branches that remain in the transformed program.

Again, assume an input-independent branch originating from node  $n_{branch}$ , with  $V_t(n_{branch})$  being the set of nodes targeted by this branch. Let  $n'_{branch}$  be the node  $n_{branch}$  or a collapsed node containing  $n_{branch}$ . Similarly let  $n'_{to}$  be a node  $n_{to} \in V_t(n_{branch})$  or a collapsed node containing  $n_{to}$ . Let out(n) return the set of all outgoing edges of node  $n_{to} \in V_t(n_{branch})$  denotes the set of outgoing edges from  $n_{branch}$ .

The nodes that may potentially be skipped by an edge  $e = n_{branch} \rightarrow n_{to}$ , are at most all the nodes that are guaranteed not to be executed after the edge e was executed, without executing  $n_{branch}$  again, i.e., they may be executed in a future loop iteration. These nodes are a subset of the nodes that are control-dependent on  $n_{branch}$ . Skipping any other nodes that may later on turn out to require execution would require the introduction of additional back edges or additional executions of existing back edges.

The nodes that may be skipped are determined by the control dependencies in the program. Several different forms to express control dependencies have been described in the literature. The one that seams most convenient to determine the set of nodes that may be skipped is the set cd as defined in [31] on page 464 to determine this set of nodes. This set cd defines control dependencies on edges.

$V_{nx}(n,e)$  is the set of nodes that may not be executed when edge e is executed to leave node n. e is an outgoing edge of  $n_{branch}$ .

$$V_{nx}(e) = \bigcup_{e_{other} \in out(n) \setminus e} cd(e_{other}), e = \langle n, m \rangle$$

(2.2)

In other words, when an outgoing edge e from some branching node is executed, all other outgoing edges will not be executed. As a result all nodes that would require any of the other outgoing edges being executed, will not be executed.

Let  $V_{sk}(n)$  be the set of nodes that are skipped by all incoming edges to node n.

$$V_{sk}(n) = \bigcap_{e \in in(n)} V_{nx}(e) \tag{2.3}$$

Whenever selecting nodes for an application of  $SPT_2$ :

- Prefer n"<sub>branch</sub> = SPT<sub>2</sub>(n'<sub>branch</sub>, n<sub>sk</sub>), n<sub>sk</sub> ∈ V<sub>sk</sub>(n'<sub>branch</sub>) whenever possible.

Otherwise try to apply n'<sub>branch</sub> = SPT<sub>2</sub>(n'<sub>branch</sub>, n<sub>t</sub>), n<sub>t</sub> ∈ V<sub>t</sub>. Remove the edge from E<sub>out</sub>, recalculate V<sub>sk</sub>. Prefer n<sub>t</sub> yielding maximal V<sub>sk</sub>.

In Figure 2.6 the control-dependence graph for the example given in Figure 2.5a is shown. For the detailed definition of control dependence see [10] on page 323.

When comparing the control-dependence graph given in Figure 2.6 to the conversion result in Figure 2.5c one notices that only node B is skipped by the edge  $A \to C$ . Apparently this is only a very small subset of the set of nodes that are control-dependent on node A, which is  $C_{dep}(A) = \{B, C, D\}$ . Figure 2.7 shows the result of applying  $SPT_2$ in an optimized order. The edge  $A \to C$  is now skipping all nodes in  $C(A \to B) \equiv$  $\{B,D\}.$

Figure 2.7: Improved application order of  $SPT_2$

### Optimized Control-Flow Modifications in case of Preserved Branches

The applications of the transformation  $SPT_2$  impose a total order to all CFG nodes. The unoptimized variant of the transformation shown in section 16 is generating a program that executes all nodes in exactly this order. The control flow modification used in case of preserved branches as described in the previous paragraphs introduces some additional branches. The control-flow modification can take advantage of the additional control flow branches which result from keeping input-data independent branches. In the previous transformation variants the control flow was always transferred to the next node in order, when a node was left. Since a node may now be skipped by the additional branches, occasionally it may be legal to transfer the control flow to a node further away in node order. This is the case when the following node is targeted by one of the additional branches in every case its execution is required.

**Algorithm Modification** When introducing the new edges in the application order of  $SPT_2(n1, n2)$  and n2 is one of the nodes targeted by an input-data independent branch, for the first application with node n1, remember n1 and the original branching node b and create the edge  $n1.n_{exit} \rightarrow n2.n_{enter}$  as above.

For further applications of  $SPT_2(o, p)$ , with p being another target node of the branch from n1, do not create the edge. Instead remember o. Note, there is already an edge from  $b \to p$ , this is one of the unconditional branches that has not been removed before.

Check if node p may not be executed if the branch  $b \to n2.n_{enter}$  was executed, by using control dependencies as done to determine  $V_{sk}$  in Formula 2.3. Repeat this check in the order the nodes are connected until the first node  $n_x$ , for which this condition does not hold, is encountered. Create the edge  $o \to n_x$ . If the end of connected nodes is reached, defer further checks until the node becomes connected to its successor. Also consider nodes as connected when the connections get suppressed by this optimization. Obviously here is another optimization opportunity by choosing the application order of  $SPT_2$  in a way that maximizes the number of successive nodes that match the above condition.

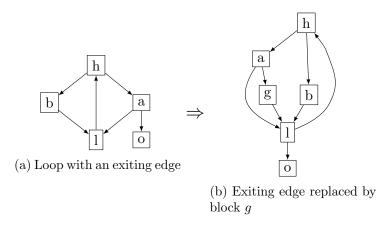

**Example** An example of this optimization is given in Figure 2.8a. This example is slightly extended compared to the previous ones to illustrate the different handling of input-data dependent and independent branches. The branch in node A is considered input-data independent, the branch in node C is considered to depend on input-data. Figure 2.8b shows the transformation result without the optimization described here. The optimized result is depicted in Figure 2.8c. The edge  $D \to E$  is replaced by the optimized edge  $D \to F$  because the node  $E \in V_{sk}(D)$ .

#### 2.3.3 Irreducible Control Flow

The transformation shown in Section 2.3.1 is only applicable to reducible control flows as it is based on collapsibility and, as shown in section 5 of [18], only reducible graphs are collapsible.

Many real programs are reducibly anyway. In the 1970s Allen [2] found, for 75 FORTRAN<sup>4</sup> programs analyzed, that over 90% had reducible control-flows. Similarly Knuth (see [23] on page 110) analyzed a random sample of 50 FORTRAN programs out of 440 for reducibility, and found all of them to be reducible.

Fortunately, in a preprocessing step, every irreducible graph can be transformed into a reducible one [44]. One approach to convert irreducible graphs into reducible ones is based on node splitting.

<sup>&</sup>lt;sup>4</sup>The IBM Mathematical FORmula TRANslating System

Figure 2.8: Further reduction of executed nodes

**Node Splitting** A basic node splitting algorithm is described in [43] on page 817f. An optimized variant generating fewer nodes is presented in [44]. There they also have shown by the application of the optimized node splitting algorithm to several programs that node splitting was increasing the size of the resulting code between 2% and 12%. Whereby larger programs tended to show less relative growth.

Note however, that node splitting may come at the cost of an exponential growth in graph size for certain graphs, as shown in [5].

# Input-Data Dependencies

| Contents |                                     |                                              |    |

|----------|-------------------------------------|----------------------------------------------|----|

| 3.1      | Dataflow                            |                                              |    |

|          | 3.1.1                               | Control Dependencies                         | 24 |

|          | 3.1.2                               | Data Dependencies                            | 24 |

|          | 3.1.3                               | Alias Analysis                               | 25 |

|          | 3.1.4                               | Benefits of Context-Sensitive Alias-Analysis | 26 |

| 3.2      | Determining Input-Data Dependencies |                                              |    |

|          | 3.2.1                               | Data-Flow Analysis                           | 30 |

|          | 3.2.2                               | Persisting Analysis Results                  | 38 |

|          | 3.2.3                               | Input-Data Dependency as an IFDS Problem     | 39 |

| 3.3      | Annotations                         |                                              |    |

|          | 3.3.1                               | Input-Data Dependencies                      | 42 |

|          | 3.3.2                               | Loop Bounds                                  | 42 |

|          | 3.3.3                               | Functions to Ignore                          | 44 |

# 3.1 Dataflow

The goal of the SP-Transformation is to remove input-data dependent branches from the program. Dataflow analysis allows the automated identification of these branches. Since the purpose of the SP-transformation is to generate a program whose execution traces are the same for each execution, input dependence in the sense of the SP-transformation refers to data that may differ amongst executions. Branches that are based on these data cause the execution trace to vary.

In the following a short overview over different program representations that can aid dataflow analysis is given.

# 3.1.1 Control Dependencies

During program execution, if a certain basic block is executed or not depends on the path selected by control-flow branches executed earlier. A basic block is said to be control dependent on those branches, which may affect the execution of this basic block.

```

Let G be a control flow graph. Let X and Y be nodes in G. Y is control dependent on X iff

(1) there exists a directed path P from X to Y with any Z in P

(excluding X and Y) post-dominated by Y and

(2) X is not post-dominated by Y.

Definition of control dependence, from [10], page 323

```

Control dependencies can cause input dependencies as shown in the example in Listing 3.1. Assume x being input data. After execution of Listing 3.1 isEven holds a truth value depending on the value of x, without directly using x to calculate the value. Instead the two assignments to isEven are control dependent on the value of x.

```

1 bool isEven;

2 if (x % 2 == 0)

3 isEven = true;

4 else

5 isEven = false;

```

Listing 3.1: Control Dependence Example

# Control-Dependence Graph

A control-dependence graph is a directed graph that contains vertices for each basic block and an additional root vertex. Edges go from controlling basic blocks to control-dependent basic blocks. Additional region nodes, as shown in [10], may summarize common control conditions.

#### 3.1.2 Data Dependencies

The effect of program statements may, and usually does, depend on input data. Also statements may produce output data. Any two statements accessing the same data location are data dependent. An overview over different types of representations that may be used to represent data dependencies is given in the following paragraphs.

#### Dependence Graph

Dependence graphs [24] show dependence relations amongst program components. Besides loop dependencies, the dependencies covered by this type of graphs are caused by

read and write accesses to variables. For serially executed program statements, where statement i is followed by statement j the following dependence types have been identified in [24] on page 209.

# Dependence Types:

**Output Dependent** i and j write to the same variable.

**Anti-Dependent** i reads a variable written by j.

**Flow Dependent** A variable written by i is read by j, where no statement may modify the variable between execution of i and j.

**Input Dependent** Both, i and j read the same variable.

A dependence graph is a directed graph with the program components as its vertices and directed arcs for dependencies between them.

# Program Dependence Graph

The Program Dependence Graph [10] combines data- and control-dependencies into a single graph.

# GSA-Form and the Program Dependence Web

The Program Dependence Web [30] is based on an SSA<sup>1</sup> representation of the program. It explicitly states control and data dependencies for each value calculated by adding gating functions. Annotating a program with only a subset of these gating functions, those corresponding to  $\phi$ -functions in the SSA form, yields the GSA<sup>2</sup> form.

#### Thinned Gated Single-Assignment

The Thinned Gated Single-Assignment [13] form is like GSA also based on the SSA representation of a program, and extending that by gating functions. The TGSA<sup>3</sup>-form is defined for any programs with a reducible CFG.

# 3.1.3 Alias Analysis

When a program is in SSA-form, direct data dependencies are usually obtainable by querying the def-use chains. Def-Use chains allow to efficiently determine where the variables used by an instruction may have been defined. An exact definition of def-use chains can be found in [20]. The information of the input-dependence state of the definitions is then combined to derive the input dependence for the use, as is shown later on in Section 3.2.

When a program is not in pure SSA-form, as is the case for LLVM<sup>4</sup>s IR<sup>5</sup>, not all data dependencies may be represented by def-use chains. In the case of LLVM arbitrary

<sup>&</sup>lt;sup>1</sup>Static Single Assignment (form)

$<sup>^2 {\</sup>it Gated \ Single-Assignment}$

<sup>&</sup>lt;sup>3</sup>Thinned Gated Single-Assignment [13]

<sup>&</sup>lt;sup>4</sup>The LLVM-Project

<sup>&</sup>lt;sup>5</sup>LLVM Intermediate-Representation

memory access is possible by the use of the load and store instruction, as is described in [27] on page 16. It is also possible to access memory locations that have not been explicitly declared earlier in the program. The dataflow analysis presented later on still requires to gather information about the data from these non-SSA memory locations. This is done by linking load instructions to the store instructions that may have written to the same memory location earlier by the use of alias analysis. Since alias analysis has been shown to be undecidable in the general case [25], the analysis will usually not be able to find the exact set of stores that may have created the value loaded at a certain program point. In these cases a safe over estimation of store instructions will be considered by the analysis implementation.

# 3.1.4 Benefits of Context-Sensitive Alias-Analysis

This section shows why the single-path transformation may benefit from context sensitivity in the data-flow analysis used to determine input-data dependencies. The context sensitivity may originate from the implementation of the data-flow analysis itself or from the usage of a context-sensitive alias-analysis.

With the results of a context-sensitive data-flow analysis the SP-Transformation may obtain differing input-data dependence information for differing call sites.

When context-sensitive results of the input-dependency analysis are available, the execution time of the transformed program may benefit from using that information by introducing branches that may skip parts of the code that would otherwise always be executed after SP-Transformation.

```

void foo() {

bar(exprInDep);

bar(exprNonDep);

void bar(int condition) {

if(condition) { //input-dependent branch

expensive_calculation;

}

}

```

Listing 3.2: Example that may benefit from context-sensitive dataflow-analysis

```

void foo(bool pcnd) {

bar(pcnd, exprInDep);

bar(pcnd, exprNonDep);

}

void bar(pcnd, int condition) {

guard₁ = pcnd;

SP[expensive_calculation] ⟨pcnd ∧ condition⟩⟨2⟩;

}

```

Listing 3.3: Result of applying the SP-transformation to the code from Listing 3.2

The branch where context-sensitive data-flow analysis makes a difference when transforming the code from Listing 3.2 is the branch in line 7. It is input-data dependent when executing the call from line 2 and input-data independent when called from line 3, given that *exprInDep* is input-data dependent and *exprNonDep* is not.

In the following the effect of the single-path conversion to the execution trace of function foo as given in Listing 3.2 is examined. The transformation result is given in Listing 3.3. When executing the function foo, with exprInDep and exprNonDep both evaluating to false, the execution trace would be 2, 7, 3, 7 before the single-path transformation is applied and 2, 7, 8, 3, 7, 8 after the application of the SP-Transformation. Note that before application of the single-path transformation the expensive\_calculation is not executed and that after the single-path transformation expensive\_calculation would be executed twice when only context-insensitive analysis-results are used. When the transformation implementation regards the context-sensitive data-flow analysis results it is able to create a program that has the run-time penalty of the SP-Transformation only in case the argument is actually input-data dependent. The transformed program may still contain the branch for the call with the input-independent argument exprNonDep.

# **Multiple Function Instances**

As an optimization one could create different machine code that is used for different call paths reflecting the differing input dependencies calculated for different call paths. The result of applying this scheme to the example given in Listing 3.2 is shown in Listing 3.4.

This transformation could be added as a preprocessing step that does not interact with the SP-transformation. The following example shows the application at source level, but an implementation at the compilers IR level should also be possible.

To distinguish the function implementations generated for different sets of inputdependencies a string encoding the input-dependencies is appended to the function names.

To generate this string, first the list of all branches that are possibly input-data dependent on any call path, but are known to be input-data independent on at least one call path, is determined. When creating a function instance for a particular set of input-dependent branches  $B_{id}$ , for each branch in the branch list, I is appended to the function name if this branch is in  $B_{id}$ , otherwise N is appended.

```

1

void foo() {

2

barI(exprInDep);

3

barN(exprNonDep);

4

5

6

void barI(int condition) {

7

if (condition) { //input-dependent branch

8

expensive_calculation;

9

10

}

11

12

void barN(int condition) {

if (condition) { //non input-dependent branch

13

14

expensive_calculation;

15

16

}

```

Listing 3.4: Example that may benefit from context-sensitive dataflow-analysis

```

1

void foo(bool pcnd) {

2

barI(pcnd, exprInDep);

3

barN(pcnd, exprNonDep);

4

5

void barI(bool pcnd, int condition) {

6

7

guard_1 = pcnd;

8

SP[expensive\_calculation] \langle pcnd \wedge condition \rangle \langle 2 \rangle;

9

10

11

void barN(bool pcnd, int condition) {

if (condition) { //non input-dependent branch

12

13

SP[expensive\_calculation]\langle pcnd\rangle\langle 2\rangle;

14

15

}

```

Listing 3.5: Result of applying the SP-transformation to the code from Listing 3.4

The execution trace for a call of the function foo as given in Listing 3.4 is now compared to execution trace after the transformation. The resulting code from the SP-transformation is shown in Listing 3.5. When exprInDep and exprNonDep both evaluate to false the execution trace would be 2, 7, 13 before the single-path transformation is applied and 2, 7, 8, 13 after application of the SP-Transformation. Note that the expensive\_calculation from line 14 is not executed in this case.

**Optimization** To reduce the number of method instances, exclude branches that do not result in runtime expensive code when SP-transformed from  $B_{id}$  and always SP-transform these branches. Also it is possible to create multiple instances only for those methods that appear most profitable. Possible measures for profitability may be the loop nesting depth of the method calls or the runtime profile of a previous execution.

#### **Guarded Branches**

As an alternative to the creation of multiple functions, it is possible to create branches that are used in the input-independent case only. When the branch is input-dependent predicated code would be used. Therefore it is necessary to distinguish if a branch is input-data dependent or not during execution. Given that this property will change for different executions of the same piece of code the input-dependency state is encoded within the data.

In the example given in Listing 3.6 the function is augmented by an additional parameter. This parameter carries the information if the sole branching instruction should be considered input-data dependent or not. In this example a boolean value *isID* is passed to the called function whose value is true if *condition* depends on input-data and false if not. The code resulting from an application of the SP-Transformation is shown in Listing 3.7.

At the call sites the value passed for this parameter will be chosen based on the dependency state for the corresponding branch. Of course the input-data dependency analysis requires to be implemented in a context-sensitive manner to yield differing result for the individual call sites.

The set of input-dependent branches that may have parameters added to function calls is the same than  $B_{id}$  in the previous paragraphs.

```

1

void foo() {

2

bar(true, exprInDep);

3

bar(false , exprNonDep);

4

5

6

void bar (bool is ID, int condition) {

if (isID || condition) { //considered non input-dependent

7

8

if (condition) { //input-dependent

9

expensive_calculation;

10

11

12

```

Listing 3.6: Example that may benefit from context-sensitive dataflow-analysis

```

1

void foo(bool pcnd) {

2

bar(pcnd, true, exprInDep);

3

bar(pcnd, false, exprNonDep);

4

5

void bar (bool pend, bool is ID, int condition) {

6

if (isID || condition) { //considered non input-dependent

7

8

guard_1 = pcnd;

9

SP[expensive\_calculation ]\langle pcnd \wedge condition \rangle \langle 2 \rangle;

10

11

}

```

Listing 3.7: Result of applying the SP-transformation to the code from Listing 3.6

The execution trace for a call of the function foo after the transformation as given in Listing 3.6 is now compared to execution trace before the transformation. When exprInDep and exprNonDep again both evaluate to false the execution trace would be 2, 7, 8, 3, 7 before the single-path transformation is applied and 2, 7, 8, 9, 3, 7 after the application of the SP-Transformation. Note that the expensive\_calculation is only executed once. As a prerequisite it is required that the branch in line 7 has been preserved by the SP-Transformation. This is possible by forcing it to be considered not input-data dependent, regardless of its usage of the actually input dependent value condition.

# 3.2 Determining Input-Data Dependencies

To avoid the need of a manual attribution of each input-dependent branch in the program dataflow analysis is used to derive the input-dependent branches from annotations elsewhere in the program. This identification of input-dependent branches requires the support of a dataflow analysis implementation. The still necessary annotations of input-dependent data have to be placed in a manner that allows the dataflow analysis to derive input-data dependency for all input-dependent branches. Ideally the dataflow analysis is applied to the whole program, requiring annotations only at the program boundaries, i.e., wherever input-dependent data first is processed by the program. When applying the dataflow analysis to sub-portions of the program, e.g., on module level, the annotations have to be placed at least at all source locations where input data enters the unit of analysis.

This section describes the way used to determine which of the program's branches are input-data dependent and which are not.

The single-path transformation relies on the information which branches in the program are input dependent and which are not. Therefore an iterative data-flow analysis that determines for every instruction if it is dependent on input data has been implemented.

#### 3.2.1 Data-Flow Analysis

To determine which branches in a program depend on input data, an iterative dataflow analysis at the level of the LLVM IR has been implemented. Within the LLVM instruction set the only way to access data from the system memory, be it on the heap or on the stack, is through usage of the load- and store instructions, as stated in [26], section 3.4. With these instructions it is necessary to rely on alias-analysis to determine possible data flows. This is because these memory accesses are not in SSA-form. The remaining data flow, which is in SSA form, may be deduced from the def-use chains and thus is a lot easier to handle.

The data-flow analysis is done in two steps. In a first step, detailed in paragraph Summarizing the Effects of Function Execution, the effect of each function to the set of input-data dependent memory locations is summarized. Building on these results in a second step, presented in paragraph Iterative Analysis, the iterative data-flow analysis is performed.

The architecture of LLVM enables easy global/inter-procedural analysis and optimization. For an overview description of LLVM's architecture refer to [26], section 2. Being able to do inter-procedural optimizations on the entire program was one of the original design goals of LLVM. The enabling part for the inter-procedural data-flow analysis is the LLVM linker which is provided with the LLVM set of tools. The LLVM linker allows linking of some/all modules available in LLVM IR, yielding one large IR module. The data-flow analysis is then performed on this linked module, thus avoiding any references to external functions that may not have been analyzed before linking.

# Summarizing the Effects of Function Execution

The effect that calling a function has to the set of possible input-data dependent memory locations may be calculated once for each function. This calculation yields a mapping of function inputs to function outputs. In detail it is mapping inputs to those outputs that contain input-dependent data after function execution, when the input was input-data dependent.

An algorithm that yields similar results is presented in [38] with the method *BackwardTabulateSLRPs(WorkList)*. To obtain the same result the algorithm presented in the following can be executed once for every output of the analyzed function.

Analysis Order In the first analysis phase, the functions are evaluated in a bottomup order as imposed by the call graph. That means that functions that do not contain function calls themselves are analyzed first. The current implementation does not support recursive function calls, which guarantees that the call graph is cycle free, so there always exist functions that do not call any other functions. From these functions on the call graph is processed towards the program entry, always analyzing functions that have all their callees already analyzed.

#### Inputs of a function considered by this analysis:

- The parameters passed to the function

- Load instructions

#### Outputs are:

- The function's return instructions

- Store instructions

- Arguments to calls of the functions \_ID and \_NID

The outputs that are in any case input-data dependent after a function call and those that are known to be not input-data dependent after a function call are also part of the analysis result. Those are stored in two sets separated from the other dependencies. So there are not special input symbols representing always-ID and never-ID that these outputs could depend on. And because both of these sets have the subsumption property as described in section 3.1 of [37], there are no other dependencies for outputs that are part of one of these two sets. Additionally, it is not possible for any output to be part of both sets at the same time.

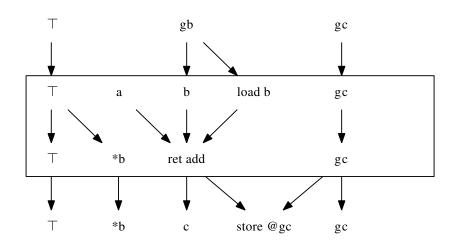

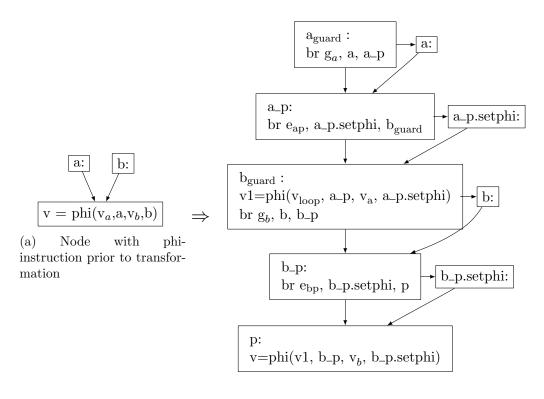

Graphical Notation The graphs given in Figure 3.1a and 3.2a show the inputs to a function on the top. The outputs are placed on the bottom. An edge from an input item to an output item means that this output has to be considered input-data dependent if the input may be input-data dependent. To keep the graphs simple, the outputs that are known to be always input-data dependent are shown as if there was a special input item true on which they depend. Any outputs that are known to not depend on any input data after the function execution are placed amongst the outputs but they do not have any incoming edges. Inputs that do not affect any outputs are not part of the graphs.

```

define i32 @callee(i32 %a,i32* %b){

1

2

int callee(int a, int* b) {

3

\%0 = load i32 * \%b

2

int r = *b;

\%call = call i32 @_ID (i32 * %b)

4

3

_ID(b);

\%add = add nsw i32 \%0, \%a

5

4

return a + r;

6

ret i32 %add

5

```

Listing (3.8) Example Source to calculate a dependency matrix

Listing (3.9) C-Source for Listing 3.8

(a) Dependency matrix calculated for Listing 3.8

Figure 3.1: Dependency matrix example

When a function has been analyzed there is no need to analyze this function again when another call to this function is encountered during creation of the dependency matrix of another function. Instead, the previously determined dependency matrix for the called function can be integrated by the application of simple rules. These rules are similar to those used in the iterative dataflow analysis as described in paragraph Function Calls, but instead of propagating input dependencies, the callee's dependence matrix is integrated into the caller's dependency matrix. Figure 3.2a shows an example combination of the dependency matrices.

# Dependency integration rules:

- Arguments passed to the callee are matched with the function parameters in the callee's dependency matrix.

- Load instructions in the callee are matched with any stores from the caller that may alias to them.

- When the callee's return value is used, the dependencies of all return instructions in the callee's matrix are added as dependencies of the return value.

- All other entries from the callee's dependency matrix are copied into the currently calculated dependency matrix.

```

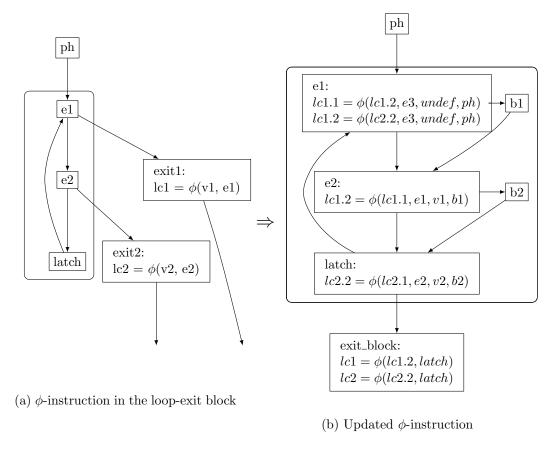

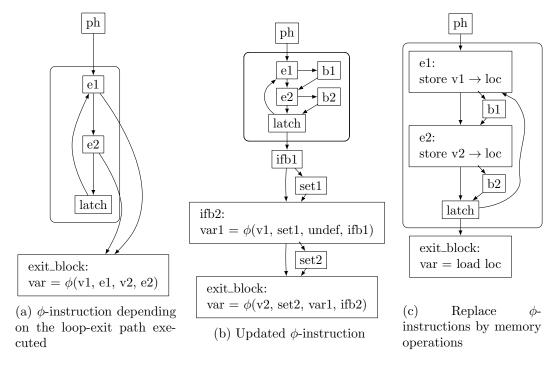

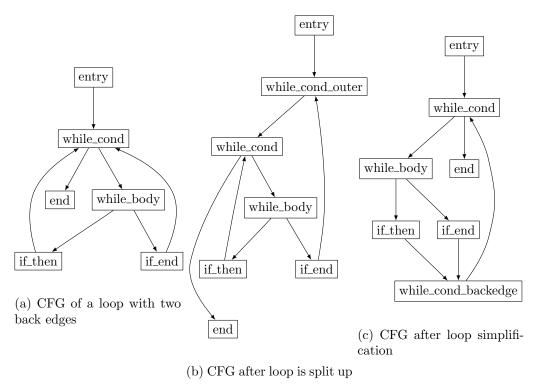

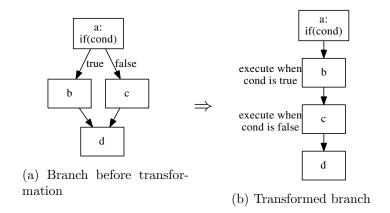

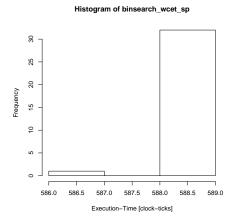

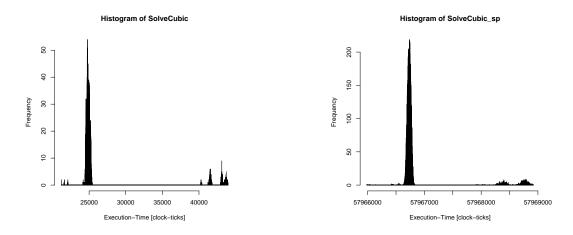

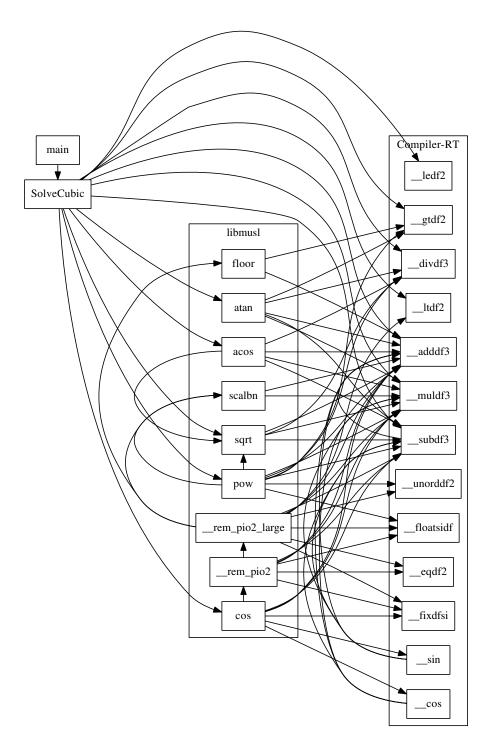

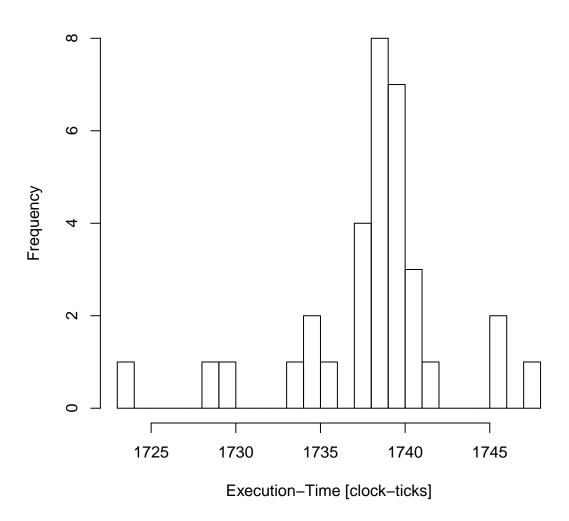

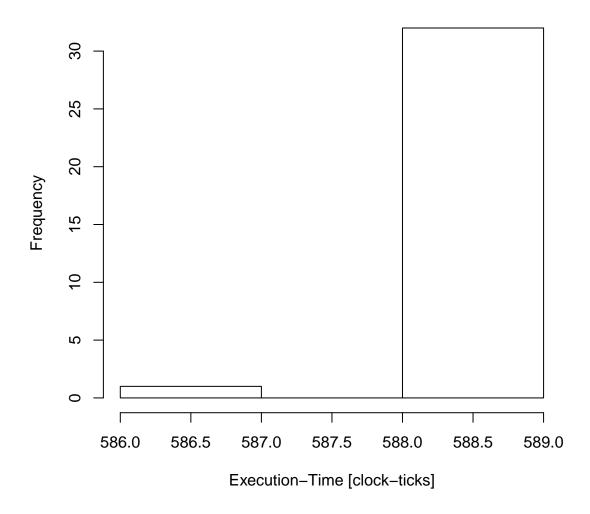

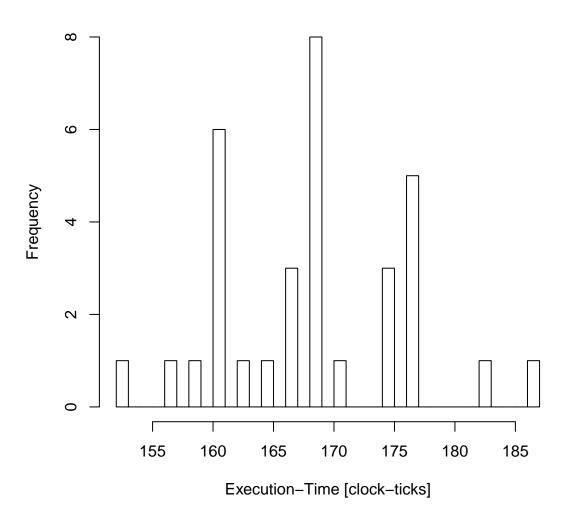

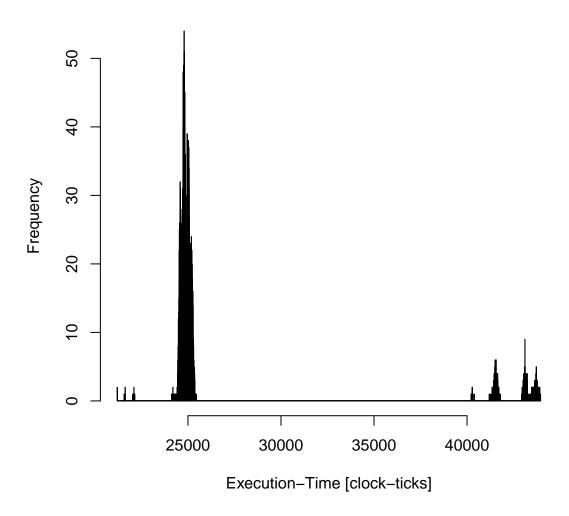

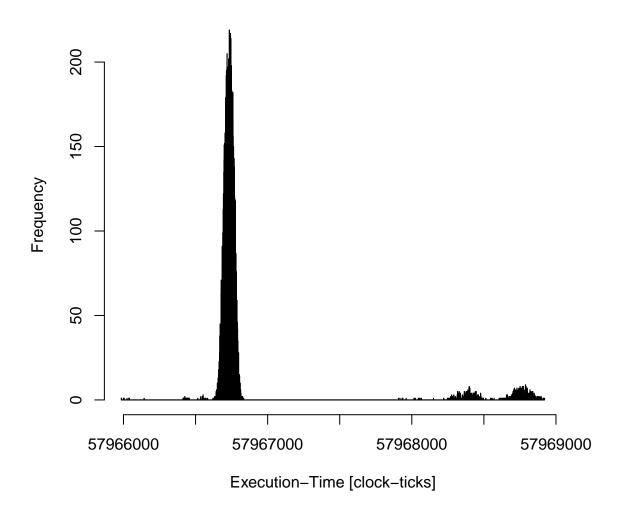

1 int gb, gc;