The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

# DISSERTATION

# A Model for Distributed Computing in Real-Time Systems

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

unter der Anleitung von

Univ.Prof. Dr. Ulrich Schmid

Institut für Technische Informatik (E182)

eingereicht an der Technischen Universität Wien Fakultät für Informatik von

# Heinrich Moser

Matr.Nr. 9925866 Pülslgasse 22/4 1230 Wien

Wien, am 11. Mai 2009

# Kurzfassung

Diese Dissertation stellt ein neues, fehlertolerantes Modell für verteile Datenverarbeitung in Echtzeitsystemen vor, das sowohl die Perspektive der klassischen verteilten Datenverarbeitungsmodelle als auch die der Echtzeitsystemforschung berücksichtigt. Üblicherweise wird bei der Analyse von verteilten Algorithmen die vereinfachende Annahme getroffen, dass Rechenschritte in Nullzeit durchgeführt werden. Unser Modell basiert auf den bisher gängigen Modellierungstechniken verteilter System, lässt jedoch im Unterschied dazu die Nullzeitannahme fallen. Diese Vorgehensweise erlaubt größtmögliche Wiederverwendbarkeit existierender Ergebnisse, eröffnet jedoch auch die bisher verschlossene Möglichkeit, Scheduling-Analysen durchzuführen. Mit Hilfe der in dieser Arbeit vorgestellten Transformationsalgorithmen untersuchen wir die Beziehung zwischen dem klassischen synchronen Systemmodell und unserem Echtzeitmodell: Wir zeigen, wie Algorithmen von einem in das andere Modell übergeführt werden können und welche Eigenschaften echter Computersysteme durch die Nullzeitannahme bisher nur verfälscht wahrgenommen wurden.

Um diesen Unterschied anhand eines konkreten Beispiels zu demonstrieren, untersuchen wir das Problem der deterministischen Uhrensynchronisation in fehlerfreien Systemen mit perfekter Ganggenauigkeit und zeigen, dass – in unserem Echtzeitmodell – kein Algorithmus existieren kann, der optimale Synchronisationsgenauigkeit bei konstanter Laufzeit sicherstellt. Da jedoch ein solcher Algorithmus im klassischen Systemmodell bekannt ist, haben wir hier ein Beispiel, bei dem die klassische Analyse zu optimistische Ergebnisse liefert. Wir zeigen, dass das Erreichen optimaler Synchronisationsgenauigkeit einen Zeitaufwand von  $\Omega(n)$  erfordert und präsentieren einen dazu passenden O(n)-Algorithmus.

Allgemein gilt, dass bei diesem Synchronisationsproblem die Anzahl der Nachrichten, die von einem Algorithmus benötigt werden, in Abhängigkeit von der Synchronisationsgenauigkeit steht. Dieses Ergebnis führt uns einerseits zu der oben erwähnten Schranke von  $\Omega(n)$ für optimale Genauigkeit, erlaubt jedoch auch Aussagen über den nicht-optimalen Fall: Es zeigt sich, dass nicht-optimale Synchronisationsgenauigkeit auch von einem Algorithmus mit konstanter Laufzeit erreicht werden kann, allerdings nur dann, wenn das darunterliegende Netzwerksystem Broadcasts in konstanter Zeit erlaubt.

Auch die Synchronisation von Uhren mit Gangabweichung wird in dieser Arbeit unter dem Echtzeitaspekt behandelt. Konkret untersuchen wir das Teilproblem, den aktuellen Wert einer auf einem anderen Computersystem befindlichen Uhr so genau wie möglich zu schätzen, präsentieren einen Algorithmus, der dieses Problem löst, und beweisen, dass keine bessere Schätzgenauigkeit erzielt werden kann. Abschließend zeigen wir, wie diese Schätzmethode mit einer optimalen Konvergenzfunktion in einem hochpräzisen, fehlertoleranten Uhrensynchronisationsalgorithmus kombiniert werden kann.

# Abstract

This work introduces a fault-tolerant real-time distributed computing model for messagepassing systems, which reconciles the distributed computing and the real-time systems perspective: By just replacing instantaneous computing steps with computing steps of non-zero duration, we obtain a model that both facilitates real-time schedulability analysis and retains compatibility with classic distributed computing analysis techniques and results. We provide general simulations and validity conditions for transforming algorithms from the classic synchronous model to our real-time model and vice versa, and investigate whether/which properties of real systems are inaccurately or even wrongly captured when resorting to zero step-time models.

We revisit the well-studied problem of deterministic drift- and failure-free internal clock synchronization for this purpose, and show that no clock synchronization algorithm with constant running time can achieve optimal precision in our real-time model. Since such an algorithm is known for the classic model, this is an instance of a problem where the standard distributed computing analysis gives too optimistic results. We prove that optimal precision is only achievable with algorithms that take  $\Omega(n)$  time in our model, and present a matching O(n) algorithm.

As a more general result, we provide a lower bound on the number of messages required to obtain a certain clock synchronization precision. In the case of optimal precision, this leads to the aforementioned bound of  $\Omega(n)$ . With respect to non-optimal precision equal to the message delay uncertainty, our result implies that constant time complexity is possible if, and only if, the system allows for constant-time broadcasts.

As a first step towards worst-case optimal deterministic clock synchronization with drifting clocks in real-time systems, which is an open problem even in classic distributed computing, we define and prove correct an optimal remote clock estimation algorithm, which is a pivotal function in both external and internal clock synchronization, and determine a matching lower bound for the achievable maximum clock reading error. Moreover, we show how to combine our clock estimation method with an optimal convergence function, resulting in a high-precision fault-tolerant clock synchronization algorithm.

This work has been supported by the Austrian Science Foundation (FWF) under grants P17757 and P20529.

# Contents

| 1. | Introduction |                       |    |  |  |  |  |

|----|--------------|-----------------------|----|--|--|--|--|

|    | 1.1.         | Computing Models      | 1  |  |  |  |  |

|    | 1.2.         | Clock Synchronization | 10 |  |  |  |  |

|    | 1.3.         | Roadmap               | 13 |  |  |  |  |

# Part I. Computing Models

| 2. | Clas                            | sic Dis          | stributed Computing                                                                                                                                                         | 17 |  |  |

|----|---------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|    | 2.1.                            |                  | inaries                                                                                                                                                                     | 17 |  |  |

|    | 2.2.                            |                  | n Model                                                                                                                                                                     | 18 |  |  |

|    | 2.3.                            | •                | are Clocks                                                                                                                                                                  | 19 |  |  |

|    | 2.3.                            |                  | ions                                                                                                                                                                        | 20 |  |  |

|    | 2.4.                            |                  | 10hs                                                                                                                                                                        | 20 |  |  |

|    | 2.3.                            | System           | 15                                                                                                                                                                          | 21 |  |  |

| 3. | Tow                             | ards th          | ne Real-Time Computing Model                                                                                                                                                | 23 |  |  |

|    | 3.1.                            | System           | 1 Model                                                                                                                                                                     | 23 |  |  |

|    | 3.2.                            | Real-ti          | me Runs                                                                                                                                                                     | 26 |  |  |

|    |                                 |                  | 18                                                                                                                                                                          | 28 |  |  |

| 4. | Adm                             | nissibil         | ity of Executions and Real-Time Runs                                                                                                                                        | 31 |  |  |

|    | 4.1.                            |                  | ges                                                                                                                                                                         | 31 |  |  |

|    | 4.2.                            |                  | • Models                                                                                                                                                                    | 32 |  |  |

|    | 1.2.                            |                  | Prerequisites                                                                                                                                                               | 32 |  |  |

|    |                                 | 422              | -                                                                                                                                                                           | 33 |  |  |

|    |                                 | 4.2.3.           |                                                                                                                                                                             | 34 |  |  |

|    |                                 |                  | <i>f</i> -BYZANTINE                                                                                                                                                         | 35 |  |  |

|    |                                 | 4.2.4.           | $\int -\mathbf{D} \mathbf{I} \mathbf{Z} \mathbf{A} \mathbf{V} \mathbf{I} \mathbf{I} \mathbf{U} \mathbf{L}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 55 |  |  |

| 5. | Problems, Algorithms and Proofs |                  |                                                                                                                                                                             |    |  |  |

|    | 5.1.                            |                  |                                                                                                                                                                             |    |  |  |

|    | 5.2.                            | 2. st-problems   |                                                                                                                                                                             |    |  |  |

|    |                                 | 5.2.1.           |                                                                                                                                                                             | 39 |  |  |

|    |                                 | 5.2.2.           | State Transitions                                                                                                                                                           | 39 |  |  |

|    |                                 | J.Z.Z.           |                                                                                                                                                                             | 37 |  |  |

|    |                                 | 5.2.2.<br>5.2.3. |                                                                                                                                                                             | 41 |  |  |

|    |                                 |                  |                                                                                                                                                                             |    |  |  |

|    | 5.3. | Proofs                             |                                        | 45 |  |  |  |

|----|------|------------------------------------|----------------------------------------|----|--|--|--|

|    | 5.4. | Notation for Specifying Algorithms |                                        |    |  |  |  |

|    | 5.5. | Time C                             | Complexity                             | 46 |  |  |  |

| 6. | Trar | Transformations                    |                                        |    |  |  |  |

|    | 6.1. | Problem                            | m Transformations                      | 47 |  |  |  |

|    |      | 6.1.1.                             | Shuffles                               | 48 |  |  |  |

|    |      | 6.1.2.                             | Simulation-Invariant Extensions        | 49 |  |  |  |

|    |      | 6.1.3.                             | Examples                               | 50 |  |  |  |

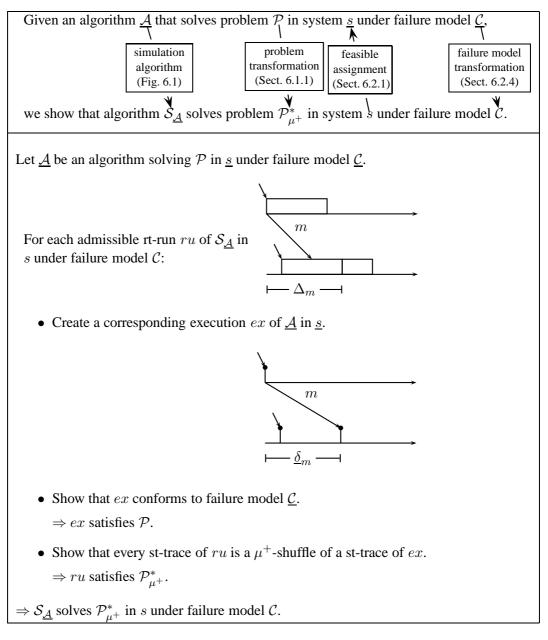

|    | 6.2. | Reusin                             | g Classic Computing Model Algorithms   | 51 |  |  |  |

|    |      | 6.2.1.                             | Feasible Assignment                    | 52 |  |  |  |

|    |      | 6.2.2.                             | Scheduling/Admission Policy            | 53 |  |  |  |

|    |      | 6.2.3.                             | Transformation $T_{R \to C}$           | 53 |  |  |  |

|    |      | 6.2.4.                             | Failure Model Compatibility            | 55 |  |  |  |

|    |      | 6.2.5.                             | Transformation Proof                   | 59 |  |  |  |

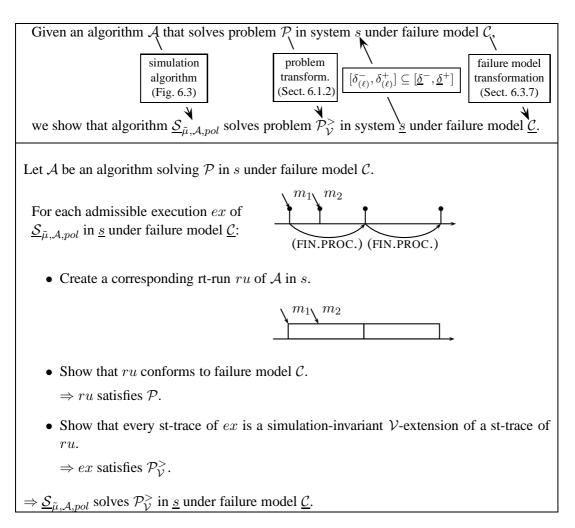

|    | 6.3. | Reusin                             | g Real-Time Computing Model Algorithms | 61 |  |  |  |

|    |      | 6.3.1.                             | Algorithm                              | 62 |  |  |  |

|    |      | 6.3.2.                             | Failure Model Requirements             | 63 |  |  |  |

|    |      | 6.3.3.                             | Algorithm Properties                   | 65 |  |  |  |

|    |      | 6.3.4.                             | Transformation $T_{C \rightarrow R}$   | 66 |  |  |  |

|    |      | 6.3.5.                             | Special Case: Timer Messages           | 69 |  |  |  |

|    |      | 6.3.6.                             | Validity of the Constructed Rt-run     | 69 |  |  |  |

|    |      | 6.3.7.                             | Failure Model Compatibility            | 71 |  |  |  |

|    |      | 6.3.8.                             | Transformation Proof                   | 73 |  |  |  |

|    |      | 6.3.9.                             | Generalization                         | 75 |  |  |  |

|    |      |                                    |                                        |    |  |  |  |

# Part II. Clock Synchronization

| 7. | Opti | mal Dr  | ift-Free Clock Synchronization                               | 79 |

|----|------|---------|--------------------------------------------------------------|----|

|    | 7.1. | Algorit | hms                                                          | 8  |

|    |      | 7.1.1.  | Generalization of Existing Results                           | 8  |

|    |      | 7.1.2.  | Optimality for Broadcast Systems                             | 82 |

|    |      | 7.1.3.  | Optimality for Unicast Systems                               | 83 |

|    | 7.2. | Lower   | Bounds                                                       | 87 |

|    |      | 7.2.1.  | Shifting                                                     | 87 |

|    |      | 7.2.2.  | Environment                                                  | 88 |

|    |      | 7.2.3.  | Message Graph Diameter                                       | 88 |

|    |      | 7.2.4.  | Message Complexity                                           | 89 |

|    |      | 7.2.5.  | Time Complexity                                              | 90 |

|    | 7.3. | Achiev  | able Precision for $o(n^2)$ Messages                         | 9  |

|    |      | 7.3.1.  | Algorithm With Least Number of Messages                      | 9  |

|    |      | 7.3.2.  | Algorithm With Constant Bound on Number of Sent Messages per |    |

|    |      |         | Processor                                                    | 92 |

#### Contents

| 8. | Opti            | mal Re   | emote Clock Estimation                  | 93  |  |

|----|-----------------|----------|-----------------------------------------|-----|--|

|    | 8.1.            | Interval | l-Based Notation                        | 93  |  |

|    | 8.2.            | Estimat  | ting a Remote Clock                     | 94  |  |

|    |                 | 8.2.1.   | System Model                            | 94  |  |

|    |                 | 8.2.2.   | Algorithm                               | 95  |  |

|    |                 | 8.2.3.   | Schedulability Analysis                 | 97  |  |

|    |                 | 8.2.4.   | Proof of Correctness                    | 99  |  |

|    | 8.3.            | Lower    | Bound                                   | 101 |  |

|    |                 | 8.3.1.   | System Model                            | 102 |  |

|    |                 | 8.3.2.   | Proof                                   | 102 |  |

|    |                 | 8.3.3.   | System Model Revisited                  | 107 |  |

| 9. | Exa             | nples d  | of Fault-Tolerant Clock Synchronization | 109 |  |

|    |                 | -        | al Clock Synchronization                | 109 |  |

|    | 9.2.            |          | l Clock Synchronization                 |     |  |

|    |                 | 9.2.1.   | -                                       | 110 |  |

|    |                 | 9.2.2.   | Booting                                 | 112 |  |

|    |                 | 9.2.3.   | Algorithm                               | 112 |  |

|    |                 | 9.2.4.   | Analysis                                | 114 |  |

| 10 | 10. Conclusions |          |                                         |     |  |

# 10. Conclusions

Contents

The first part of this thesis, starting with Chapter 2, will present a novel framework for modeling executions of algorithms in distributed real-time systems. In the second part, starting with Chapter 7, the usefulness of this model is demonstrated by applying it to some well-known clock synchronization problems and comparing the results with those obtained by classic modeling techniques. Hence, some knowledge in the areas of distributed computing, real-time systems and clock synchronization is vital to the understanding of this thesis.

This introductory chapter shall familiarize the reader with the required basics of these lines of research, outlines the structure and the results of this thesis and compares them to similar approaches in dedicated *related work* sections.

# 1.1. Computing Models

A *distributed system* consists of a set of individual *processors* capable of exchanging information. The *distributed computing* line of research is concerned with the study of algorithms solving a given *problem* in such a distributed system, preferably in an efficient manner.

#### **Distributed State Machines**

Obviously, lots of abstraction and simplification are necessary to reduce an arrangement of CPUs, network controllers and transmission media to a mathematical model that allows to reason about generic results in distributed computing.

*Processors* (CPUs, or computers in general) are represented by *state machines*: Given a set of variable names (e.g. {*participants*, *free\_places*}), a *state* can be seen as values assigned to these variables; for example, {*participants* = {Peter, Martin}, *free\_places* = 3} would be a valid state. The processor can perform *state transitions*, i.e., it changes from one state to another. In general, the processor cannot make arbitrary state transitions, but rather runs some kind of *algorithm*. The algorithm specifies the initial state (e.g. {*participants* = {}, *free\_places* = 5}) and the *state-transition function*, which can be seen as a set of rules describing which state transitions are allowed, formalized as a function mapping a state and, possibly, some kind of *input*, to a new state and, possibly, also to some kind of *output*. For example, a state transition function representing the code

- 2 if  $free_places > 0$  and  $name \notin participants$ :

- $3 \qquad free\_places \leftarrow free\_places 1$

- 4  $participants \leftarrow participants \cup \{name\}$

- 5 send "subscription confirmed"

<sup>1</sup> **upon** receiving "subscribe name":

would map ({ $participants = {Daniel}$ ,  $free_places = 4$ }, "subscribe Josef") to the new state { $participants = {Daniel, Josef}$ ,  $free_places = 3$ } and to the output "subscription confirmed".

A *distributed system* consists of a set of such processors and some means of communication. Thus, the distributed system also specifies how processors receive their input and what happens to their output. Common examples include

- *a message bus*: Once a processor outputs some message, all other processors receive this message as input some time later.

- *shared memory*: All processors can read and modify a common pool of registers; changes by one processor can be seen by all other processors immediately.

- *point-to-point communication*: Some processors are connected through communication links. The output of the transition function consists of messages sent over specific links, e.g., "send message A to processor p and message B to processor q".

In this thesis, we will restrict our attention to message-based point-to-point communication in fully-connected networks. *Fully-connected* means that every processor can send a message to every other processor.

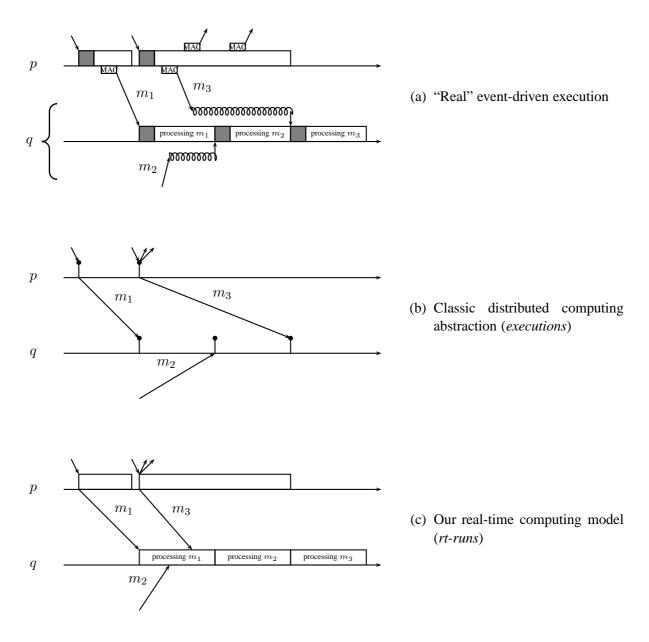

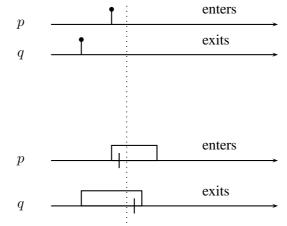

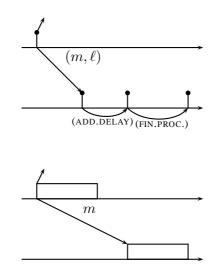

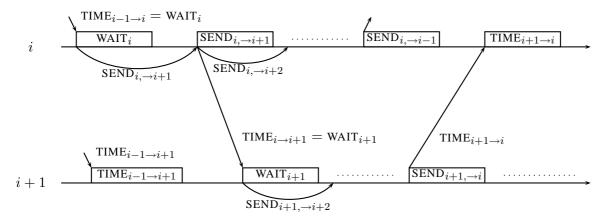

An *execution* or *run* of an algorithm in such a distributed system can be visualized as a *space-time diagram*, such as the ones found in Figures 1.1 and 1.2. A horizontal line represents a processor and arrows symbolize messages being sent and delivered. With respect to state transitions (also known as *computing steps*), "ticks" stand for atomic, immediate state transitions at this exact time, whereas boxes (e.g. in Fig. 1.2(c)) more generally specify that some code is being executed, with the exact times of state transitions unknown. Note that messages are always sent during a computing step.

When processors deviate from their specified behavior, they are considered *faulty*. The following list contains a few well-known examples of ways in which a processor can fail:

- *Clean crash*: A processor eventually stops working, i.e., after some point in time, no more computing steps occur on this processor.

- Unclean crash: A processor crashes in the middle of a computing step, i.e., at some point in time, the processor executes a *part* of a computing step and then stops working completely. This case is more difficult to tolerate, since a processor might only send a subset of its outgoing messages while crashing—contrary to the clean crash case, where a computing step is either completed in full or does not occur at all.

- *Byzantine* or *arbitrary* faults: A Byzantine faulty processor can behave arbitrarily; its computing steps do not have to conform to the algorithm's state transition function. For example, it can send out messages with arbitrary, misleading information, manipulate messages while forwarding them or just stop working like in the crash failure case. This failure model applies to "broken" processors sending out nonsensical data as well as to malicious processors deliberately trying to prevent the distributed algorithm from reaching its goal.

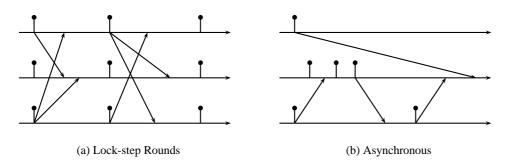

Figure 1.1.: Lock-step Synchronous and Asynchronous Model

A *fault-tolerant algorithm* is an algorithm which solves a given problem despite a certain number of processors being faulty.

#### **Classic Distributed Computing Models**

Since the algorithm specifies the state transitions the processor may carry out, the question remains as to *when* these transitions are performed. Together with timing bounds on message transmission, the answer to this question determines the *synchrony* of the computing model. To understand the wide variety of models available, let us look at the two extreme cases [Lyn96, AW04]:

- The synchronous lock-step model (Figure 1.1(a)) splits the execution into rounds: In every round, (1) one message can be sent from every processor to every neighbor, (2) all these messages arrive, and (3) each processor makes a state transition using the received messages as input. Note that, in the figure, the same computing step performs the state transition for round k as well as the message sending for round (k + 1).

- At the other end of the spectrum, there is the *asynchronous model* (Figure 1.1(b)), which does not bound (neither relative nor absolute) processing speeds or message transmission times in any way. The only restriction is that every message eventually gets delivered and every processor takes an infinite number of computing steps.

Both models have their advantages and their drawbacks: The strong assumptions of the synchronous lock-step model make it easy to design algorithms: The developer can be sure that during some processor's round k computing step, all other processors have already performed their round (k - 1) steps and all round (k - 1) messages have already arrived. However, there are lots of real-world systems where these assumptions just do not hold. The assumptions of the asynchronous system, on the other hand, are so weak that they are easily satisfied by real-world computer systems. At the downside, many well-known problems are very hard or even impossible to solve in the asynchronous model [FLP85].

There is a wide range of *partially synchronous* models, which attempt to find a compromise between these two extreme cases: They bound, for example, the relative processing speeds of processors (that is, between two computing steps of one processor, another processor may not perform more than x computing steps) or the message transmission delay (that is, no message

transmission may take less than y or more than z time units). A few examples from literature will be outlined in the *related work* section below.

However, these models still suffer from one common problem, which we will illustrate by comparing a real-world execution with its simplified representation in one of the "classic" distributed computing models. Figure 1.2(a) gives an (already considerably simplified) glimpse of what happens in a real-world system. Consider the second message arriving at processor p: This message triggers the scheduler, requiring some CPU overhead (= the gray box) for switching to the correct task responsible for processing that message. This task starts a job (= the white box), which performs some computations and eventually sends out a few messages via some communication medium. This sending causes some media access control overhead (= the MAC box), which might very well occur in parallel to the CPU, if MAC is performed by a separate network controller. The first message sent by that job (=  $m_3$ ) eventually arrives at processor q, which is currently busy with processing  $m_1$ ; thus,  $m_3$  is enqueued (= the coiled arrow) until the scheduler of q decides that the CPU is ready to process it.

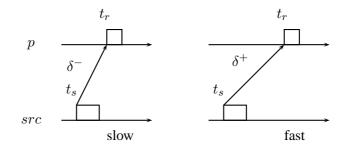

Figure 1.2(b) shows the same situation, using the *message-driven synchronous (non-lock-step) system model*: The execution of the distributed algorithm is represented by a sequence of atomic computing steps that are triggered by an incoming message and executed in zero time. All timing-related factors that occur in the real-world system, such as scheduling overhead, processing time, queuing time or network delays are encapsulated in the *end-to-end delay*, i.e., in the time between the zero-time action sending a message and the one receiving it. With respect to timing assumptions, the synchronous model assumes that these end-to-end delays are bounded: There is a constant lower bound ( $\delta^-$ ) as well as a constant upper bound ( $\delta^+$ ).

With this assumption, it does not make a difference, for example, whether messages arrive at a processor simultaneously or nicely staggered in time: the messages are processed instantaneously when they arrive. The zero step-time abstraction is, hence, very convenient for analysis, and a wealth of distributed algorithms, impossibility results and lower bounds have been developed for models that employ this assumption [Lyn96].

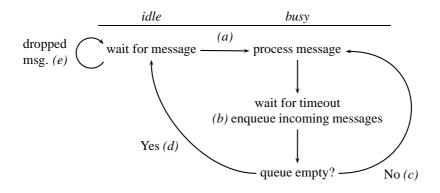

#### Scheduling Theory

In real systems, however, computing steps are neither instantaneous nor arbitrarily preemptable: A computing step triggered by a message arriving in the middle of the execution of some other computing step is usually delayed until the current computation is finished. This results in queuing phenomenons, which depend not only on the actual message arrival pattern but also on the queuing/scheduling discipline employed.

Traditionally, such problems are the central topic of a separate line of research, devoted to real-time systems [But97]. Let a *job* be defined as a small unit of work to be performed by a CPU, characterized by (at least)

- an *arrival time*, the time by which this job is ready for execution,

- a *computation time* (also known as *worst-case execution time*), the time span required to execute this job on the CPU, and

- a *deadline*, the latest time by which this job must have finished.

Figure 1.2.: Modeling distributed system executions

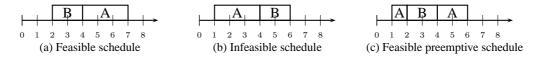

The goal of *uniprocessor real-time scheduling* is to create a *schedule*, which assigns these jobs to a processor in a way such that all jobs meet their deadlines. For example, consider the job set  $\{(A : 1, 3, 7); (B : 2, 2, 5)\}$ , with the numbers denoting the arrival time, the computation time and the deadline, respectively. Figure 1.3 shows (a) a feasible schedule, in which both jobs meet their deadlines, and (b) an infeasible schedule, in which job *B* misses its deadline. If the jobs cannot be interrupted, it is plain to see that (a) is the only solution. Otherwise, if *preemption* is permitted, other assignments, such as (c), are possible. More advanced examples include *precedence relations* among jobs, e.g., some job *A* must be (completely) executed before job *B* may start, or *shared resources*, e.g., *A* and *B* may require exclusive access to the same resource, possibly causing schedules such as the one in Figure 1.3(c) to become infeasible.

Figure 1.3.: Real-time schedules

Usually, jobs are not declared individually but rather summarized into *tasks*: A task consists of an infinite sequence of jobs, all having the same execution time and relative deadline (= the time span between (absolute) arrival and (absolute) deadline). The arrival time of the jobs is specified by the *arrival pattern* of the task: The jobs of a *periodic* task arrive at regular, constant intervals; *sporadic* tasks release their jobs irregularly, but with some minimum time (*sporadicity interval*) in between job arrivals; and *aperiodic* tasks do not specify any arrival restriction.

Determining whether a feasible schedule exists or not can be surprisingly difficult: For example, the general *feasibility analysis* problem is NP-hard, even in the case of only periodic task sets (with arbitrary deadlines) [BHR90]. Thus, many analysis techniques are pessimistic (sufficient but not necessary) and/or only apply to special cases (such as relative deadlines being equal to the period) [SAA<sup>+</sup>04]. *Worst-case response time analysis* is a generalization of feasibility analysis: Rather than finding out whether all jobs meet the a-priori given deadline, the worst-case difference between the arrival of some particular job and its completion is determined.

*Multiprocessor real-time scheduling* is a natural generalization: Instead of only one CPU, jobs can be scheduled to multiple processing units in parallel. Although multiprocessor scheduling is not yet as well understood as the uniprocessor case, a lot of results and heuristics do exist (again, cf. [SAA<sup>+</sup>04] for an overview).

Unfortunately, real-time scheduling in loosely-coupled distributed systems, i.e., scheduling involving multiple processors connected through a network, has only been addressed for very restricted types of problems: Informally speaking, the concept of tasks with a-priori known arrival patterns has been extended to *information flows*, starting at some processor (again, with some known arrival pattern) and then traveling through the network in a linear fashion. For example, some external signal could arrive at processor p, causing a job to be executed, then travel to processor q over a communication link, again causing a job execution, and finally

arriving at processor r, initiating the last job. *Holistic scheduling* [TC94] or the *trajectory approach* [MMG04] allow to determine the overall worst-case response time of such a flow.

Nevertheless, many problems in distributed computing do not exhibit such a linear flow of information, starting with some sensor and ending in some actuator or data aggregation node. In particular, fault-tolerance often requires a set of "equal" processors exchanging messages on a regular basis (*rounds*)—well-known examples are distributed agreement problems, such as Byzantine consensus or non-blocking atomic commitment, and synchronization problems, such as tick synchronization or clock synchronization. In these cases, the arrival patterns of messages might not be known in advance; often, there is even a circular dependency: The arrival pattern of some round k messages determines the queuing delays, which in turn influence the time at which round (k + 1) messages are sent, and thus, the arrival pattern of these messages. Although the approaches mentioned above are a promising start for extending schedulability analysis to loosely-coupled distributed systems, so far, no suitable generic modeling framework for analyzing queuing effects of distributed algorithms exists.

#### **Related Work**

We are not aware of much existing work in the distributed computing area of research that also addresses real-time aspects. Somewhat an exception is the work by Neiger & Toueg [NT93], which identifies general problems and conditions that preserve the correctness of a solution based on perfectly synchronized clocks when logical clocks are used instead. The underlying model assumes non-zero step times, but considers them sufficiently small to completely ignore queuing effects. Moreover, in contrast to our work, they restrict their attention only to problems whose specification can be written in a way which does not refer to real time. Another example of a non-zero step time model is the remote memory reference (RMR) model for shared-memory systems [AY96, AKH03] by Anderson et. al. It assumes computing step times which depend on the number of conflicting shared memory accesses. The RMR model has been used for deriving several algorithms, e.g. for mutual exclusion, and related lower bounds. Since it is not applicable to message-passing systems, however, our results are not comparable.

Another branch of research where distributed computing and real-time systems issues are combined are modeling frameworks [AD94, LV95, LV96, MMT91, SGSAL98, KLSV03]. Such frameworks allow formal modeling and analysis of complex distributed real-time systems. A representative example are Timed I/O Automata (TIOA) [KLSV03], which can change state both via ordinary discrete transitions and via continuous trajectories. TIOAs facilitate hierarchical composition, abstraction, and proofs of safety and liveness properties. However, none of the above modeling frameworks supports non-zero step times and thus real-time schedulability analysis of distributed algorithms. By contrast, our work addresses exactly this issue.

Apart from those lines of research, we are not aware of too many distributed computing papers that incorporate real-time scheduling issues at all: In [HLL02], for example, Hermant and Le Lann demonstrate the power of such an integrated approach by introducing fast failure detectors, which facilitate very fast detection times and thus quickly terminating asynchronous consensus algorithms.

Turning our attention to distributed system models, the partially synchronous DLS model [DDS87, DLS88] extends the asynchronous model by adding an absolute upper bound  $\Delta$  on message transmission delays and an upper bound  $\Phi$  on the relative computing speed of any two processors. Formally, it is assumed that every processor takes at least one and at most  $\Phi$  computing steps during any real-time interval of duration  $\Phi$ ; note that the unit of real-time is actually the computing step time of the fastest processor in the system here. A send step sends one message to one recipient, a receive step makes some messages that arrived so far available to the processor. A single computing step can be either a send step or a receive step, but not both. Hence, receiving a message and sending a response is not possible in zero time here. Additionally, sender queuing (but not receiver queuing) is modeled explicitly by allowing only one message per send step.

The semi-synchronous model [ADLS94, Mav92, PS92] uses a similar approach; however, there is no need for separate send and receive steps, and computing steps can send out multiple messages at once. [ADLS94] does not normalize the real time units to the speed of the fastest processor, i.e., the real time between two consecutive steps of one processor is within some fixed interval  $[c_1, c_2]$ . [Mav92] assumes that  $c_2 = 1$ , i.e., the slowest processor determines the time base.

Both the DLS model and the semi-synchronous model conveniently abstract away queuing effects at the receiving processor, since a single receive event (DLS model) or a single computing step (semi-synchronous model) can process all messages received so far. As Chapter 7 of this thesis will show, this issue can make an important difference. Moreover, both models lack a lower bound on the message transmission delay. In the context of clock synchronization, this is an important difference to our model: In the case of drifting clocks, not only the message delay uncertainty but also the absolute bounds on message transmissions affect the achievable precision (cf. Chapter 8).

The partially synchronous Theta model [LLS03, WLLS05, HW05a] as well as the Asynchronous Bounded-Cycle model (ABC model) [RS08] are mentioned here, since they provide an additional motivation for our line of research. Both models are based on the assumption that, due to the dynamic nature of distributed algorithms and the corresponding queuing effects, it is not feasible to assume fixed a-priori bounds on the end-to-end delay of messages. They retain the zero step-time assumption but bound *ratios*, either on the end-to-end delay of messages simultaneously in transit (Theta model) or on the number of forward and backward edges in certain message chain cycles (ABC model). Clearly, such assumptions only hold if there is a strong relationship between the queuing delays in different parts of the system, either at the same physical instant of time (in case of the Theta model) or within a "causally related" region of the space-time diagram (in case of the ABC model). Due to lack of appropriate analysis techniques, the claim that this relationship holds in real systems has only been verified experimentally [Alb05]. We believe that the real-time distributed computing model presented in this thesis is a mandatory prerequisite for any attempt to verify this assumption analytically.

There are also a few approaches in the real-time systems community that aim at an integrated schedulability analysis in distributed systems. One notable example combining local processor scheduling with network communication issues is *holistic scheduling*, introduced in [TC94]: Assuming synchronized clocks, end-to-end delay bounds of "information flows" across a shared network bus can be derived by means of recurrence relations based on the (a-priori known) bounds on the worst-case frequency of all tasks and messages. In [PGGGGH98], this work is extended by adding a best-case analysis, improving the accuracy of the estimated jitter. However, contrary to the modeling requirements of many distributed algorithms, they assume a strictly linear sequence of actions in the system, i.e., within one flow, every computing action on a processor sends a message to at most one other destination processor. The *trajectory approach* [MMG04] provides bounds on the end-to-end delays which are less pessimistic; however, they also model a flow as a fixed, linear path through the network.

#### The Gap

This brief overview demonstrates that the distributed computing view on system models on one hand and the scheduling results obtained by the real-time community on the other hand operate at entirely different levels of abstraction and solve different problems: Whereas the former is concerned with the correctness of algorithms, usually expressed by some predicate on the internal state of the processors involved, the latter is only interested in the ability of an algorithm to meet some a-priori defined deadlines.

However, as we show in the second part of this thesis by means of the clock synchronization problem, queuing issues *can be* relevant for the correctness of an algorithm and/or the tightness of a lower bound. Bridging this gap and analyzing these effects requires a model which,

- on the one hand, is "compatible" with the classic distributed computing models, such that the wealth of existing results can be reused, but,

- on the other hand, explicitly models queuing effects, thereby allowing us to incorporate real-time scheduling issues and to perform a worst-case response time analysis.

Consequently, the first part of this thesis introduces a real-time distributed computing model for message-passing systems, which reconciles the distributed computing and the real-time systems perspective: By just replacing the zero step-time assumption with non-zero step times, we obtain a real-time distributed computing model that admits real-time analysis without invalidating standard distributed computing analysis techniques and results.

Consider the example in Figure 1.2(c): Introducing the processing delay as an additional system parameter allows us to split the end-to-end delay into

- the message delay (= the arrow),

- the queuing delay (= the distance between the arrow head and the start of the corresponding box), and

- the processing delay (= the box).

This model hence enables us to demonstrate the impact of queuing effects on distributed algorithms (in particular, on clock synchronization), while keeping most of the mathematical simplicity of the classic distributed computing abstraction (Figure 1.2(b)).

Thus, in the resulting real-time computing model, a system can be specified by bounding the message and the processing delay; the queuing delay, however, is not a system parameter here but rather depends dynamically on the message pattern of the algorithm and the *scheduling policy*, i.e., on the order, in which queued messages are processed. In fact, this is a major advantage of our approach: In the classic computing model, comparing algorithms running in "the same system", i.e., with the same bounds on the end-to-end delay, can be misleading, since it ignores the fact that the message pattern of the algorithm itself influences the queuing delays, and, thus, the end-to-end delays.

# 1.2. Clock Synchronization

Apart from making distributed algorithms amenable to real-time analysis, our model also allows us to address the interesting question whether/which properties of real systems are inaccurately or even wrongly captured when resorting to classic zero step-time models. In the second part of this thesis, we revisit the well-studied problem of deterministic clock synchronization for this purpose.

The term *clock synchronization* spans a wide range of distributed computing challenges. All of these try to *synchronize* actions on processors in a distributed systems, since added synchrony allows a lot of distributed computing problems to be solved in a much simpler way. Clock synchronization does not necessarily require real clocks: For example, Lamport clocks [Lam78] or vector clocks [Fid88, Mat88] use integer values, messages tagged with these values and a simple maximum function to obtain an ordering of events in an execution, which is applicable even in completely asynchronous systems. If there is some degree of synchrony already present in the system, more sophisticated *tick synchronization* algorithms [ST87, Mav92] can be used, which cause the processors in a distributed system to increment their counter variables "as simultaneously as possible".

In this thesis, however, we are mainly interested in "classic" clock synchronization, in systems where the processors are equipped with local, possibly *imperfect* hardware clocks. Imperfect clocks exhibit some kind of *drift*, meaning that they do not run at the same rate as real time but rather a bit slower or a bit faster. The goal is to adjust the local clock values of different processors to satisfy some clock synchronization condition. In particular, *external clock synchronization* is concerned with minimizing the difference between the adjusted local clocks and some external reference clock such as GPS time, at all points in time. In contrast, *internal clock synchronization* does not assume access to an external time source but rather aims at minimizing the difference between the adjusted local clocks of any pair of processors (for all possible pairs, at all points in real time).<sup>1</sup> These adjusted clocks must satisfy some *progress* condition, usually requiring the clocks to stay within a linear envelope of real time.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>To ease presentation, we will use the well-established term *precision* for this difference, although we are aware that "imprecision" would be more appropriate, technically. Thus, we will try to avoid misleading phrases such as "high precision" (usually referring to a small difference) and "low precision" (usually referring to a large difference) in the formal parts of this work and use unambiguous terminology instead.

<sup>&</sup>lt;sup>2</sup>Interestingly, only requiring the adjusted clocks to increase without bound is not sufficient, since it allows for impractical solutions such as logarithmically increasing clocks (Theorem 1 of [DHS86]).

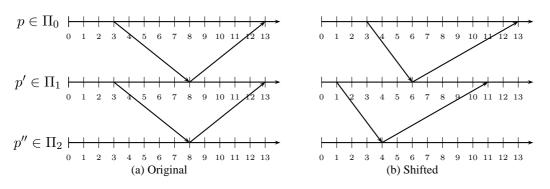

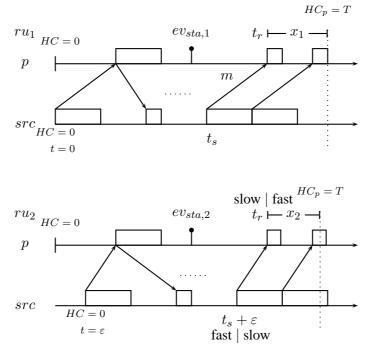

Like many other works in this area of research, much of this thesis builds on the foundations laid by Lundelius and Lynch [LL84b]. They established a tight bound of  $(1 - \frac{1}{n})\underline{\varepsilon}$  on the achievable clock synchronization precision in a drift- and fault-free scenario, with  $\underline{\varepsilon}$  denoting the end-to-end delay uncertainty (i.e., the difference between maximum and minimum end-to-end delay) and n the number of processors. Their work, which assumes a fully-connected network in which every processor can directly communicate with every other processor, was later generalized to arbitrary networks [HMM85], with [BW01] providing closed-form upper and lower bounds for some specific topologies. In Chapter 7, we will examine the problem of drift- and fault-free internal clock synchronization in a fully-connected network in our real-time distributed computing model.

With respect to fault-tolerance, it should be noted that internal clock synchronization is unsolvable if at least one third of the processors is Byzantine faulty [DHS86]; recall that a Byzantine faulty processor can behave arbitrarily, in particular, it may lie about its current clock value. In general, optimal-precision clock synchronization with drifting clocks is an open problem even in classic distributed computing: Optimal results are only available in case of a-priori given message patterns ("passive" clock synchronization) [PSR94, OPS99]; unfortunately, optimal message patterns and hence optimal "active" clock synchronization algorithms cannot be inferred from this research.

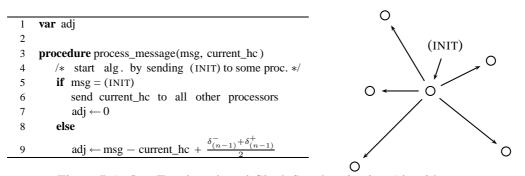

Interestingly, existing drift- and fault-tolerant internal clock synchronization algorithms can be reviewed in terms of a generic structure [Sch86]: Periodically, the algorithm detects the need for resynchronization. Then, information is gathered about the clock values of the other processors, usually by exchanging messages. After this data has been collected, a new local clock value is calculated based on some *convergence function*. To our surprise, the second step—a problem known as *remote clock estimation*—had not been solved optimally yet. In Chapter 8, we present a tight bound on the achievable estimation error, again using our realtime computing model.

For calculating a new clock value based on the remote clock estimations, an optimal convergence function using *fault-tolerant averaging* has been presented by Fetzer and Christian [FC95a, FC95b]. In a fully-connected system with n processors, f of which can be faulty, the main idea of fault-tolerant averaging is, for each processor p, to take all n clock readings (as estimated by p), discard the f largest and the f smallest values, and then calculate the arithmetic mean of the remaining interval [WL88]. The *differential fault-tolerant midpoint function* of [FC95b] extends this approach by slightly modifying this interval and bounding the maximum correction value, resulting in an optimal convergence function. Chapter 9 of this thesis provides a sample implementation that combines their convergence function with our clock reading method in one algorithm.

#### **Related Work**

Lots of results already exist for external as well as internal clock synchronization in classic distributed computing models. A comprehensive summary would go far beyond the scope of this work; [SLWL90] provides an exhaustive overview of fundamental results in this area of research, whereas [AP98] classifies existing clock synchronization algorithms according to their internal structure. A special issue of the Real-Time Systems journal assembles results

with a focus on global time in large scale distributed real-time systems [Sch97]. Many recent discoveries can be found in the area of clock synchronization in wireless sensor networks [SBK05].

The main results of the second part of this thesis are lower and upper bounds on clock synchronization (or subproblems thereof) while considering the need to schedule message processing steps. Actually, this is a known problem: In [WL88], for example, Welch and Lynch mention that implementing their clock synchronization algorithm in a real-world setting required staggering the broadcast of messages (which would otherwise be sent almost at the same time), to avoid the situation that too many messages arrive simultaneously at the same processor. Still, this topic has not received much attention in literature. In fact, we are aware of only two papers that consider deterministic clock synchronization in connection with real-time scheduling:

- Basu and Punnekkat [BP03] propose simple variants of Srikanth & Toueg's tick synchronization algorithm [ST87]. Their algorithms stop the local clock while the resynchronization is in progress, thereby avoiding the problems that usually occur when the clocks being synchronized are also used to schedule tasks in heavily loaded real-time systems.

- Mavronicolas [Mav92] provides a lower bound for the precision achievable in a "singleshot" version of tick synchronization in the semi-synchronous model. This model differs in various significant ways from the one used in this thesis: Computing step duration and clock drift are directly related, the lower bound on the message transmission delay is always zero, and, like in the partially synchronous model of [DLS88], a single computing step can process multiple incoming messages. As outlined in the previous section, this last point conveniently abstracts away queuing issues; however, as Chapter 7 of this thesis will show, this issue can make an important difference. Thus, our results are not directly comparable.

To the best of our knowledge, other papers dealing with clock synchronization in real-time systems do not incorporate queuing issues at all [MFNT00], assume a-priori given bounds on the receiver queue length [VRC97], circumvent this problem by delegating the task of timestamping or processing messages to special-purpose low-level hardware [KO87, SL96, SR87], or restrict the precision analysis to empirical evaluations [ZSSZ08].

The subproblem of remote clock estimation is handled/analyzed sub-optimally or abstracted away entirely in the wealth of existing research on clock synchronization: Most papers employ trivial clock estimation algorithms only, based on a one-way or round-trip time-transfer via messages [EK73], and provide a fairly coarse analysis that (at best) incorporates clock drift [Cri89] and clock granularity [SS97]. Alternatively, as in [FC95a, FC95b], remote clock estimation is considered an implementation issue and just incorporated via the a-priori given maximum clock reading error. Hence, to the best of our knowledge, optimal deterministic clock estimation has not been addressed in the existing literature.

Since we are aiming at deterministic algorithms here, we do not consider probabilistic clock synchronization [Cri89, Arv94], statistically optimal estimations [EK73, MST99] and similar topics. Likewise, gradient clock synchronization [FL04, LLW08], which analyzes the effect

of the network graph diameter on the synchronization precision between neighboring nodes, is out of the scope of our work.

#### Clock Synchronization in the Real-Time Distributed Computing Model

As it turns out, clock synchronization is a particularly suitable choice for analysis under our real-time distributed computing model, since the achievable synchronization precision is known to depend on the end-to-end delay uncertainty. Since non-zero computing step times are likely to affect end-to-end delays, one may expect that some results obtained under the classic model do not hold under the real-time model—if there are such effects at all.

Our analysis confirms that this is indeed the case: We show that even in the drift-free case no clock synchronization algorithm with constant running time can achieve optimal precision in our real-time model. Since such an algorithm has been given for the classic model [LL84b], this is an instance of a problem where the standard distributed computing analysis gives too optimistic results. Actually, we show that optimal precision is only achievable with algorithms that take  $\Omega(n)$  time, even if they are provided with a constant-time broadcast primitive.

Obviously, clock synchronization in the drift-free case is a one-shot problem: After the clocks have been synchronized to a certain precision, they stay synchronized forever. Thus, time complexity does not really matter. However, since clock drift is practically unavoidable, the situation changes when generalizing these algorithms to real systems. In the extreme case of clocks with very high drift rates, a sub-optimal algorithm with low time complexity might perform better than a drift-free-optimal algorithm with high time complexity, since the former algorithm can be executed more frequently.

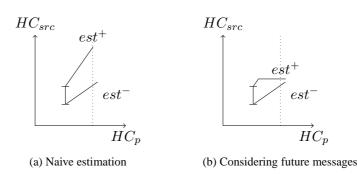

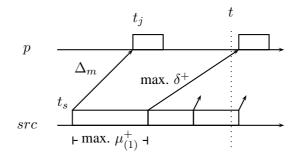

Contrary to the drift-free case, we do not solve the problem of internal clock synchronization with drifting clocks in real-time systems conclusively in this work—recall that this is even an open problem in the (probably easier) case of classic zero step-time distributed computing models. However, as a first step towards this goal, we examine the (deceptively simple) subproblem of *remote clock estimation* in the real-time computing model. Our results, consisting of an algorithm and a matching lower bound, precisely quantify the effect of system parameters such as clock drift, message delay uncertainty and step duration on optimal remote clock estimation.

Based on the classic round-based resynchronization scheme, where processors with drifting clocks initiate a clock synchronization protocol every time their clocks reach a multiple of some predefined time span, denoted the *resynchronization period*, we combine our remote clock reading method with the optimal convergence function of [FC95b] and determine an upper bound on the precision achievable with this algorithm.

## 1.3. Roadmap

This section explains the structure of this thesis and gives a brief overview of each chapter.<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>Preliminary versions of this work have been published in [MS06a], [MS06b], [MS08] and [Mos09].

#### **Computing Models**

In Chapter 2, we formalize the *classic computing model* ( $\underline{\mathcal{M}}$ ), based on the well-known synchronous non-lock-step computing model for message-passing systems (both point-to-point and broadcast-based).

In Chapter 3, we define our *real-time computing model* ( $\mathcal{M}$ ), which differs from  $\mathcal{M}$  by just providing atomic computing steps of non-zero duration. Consequences of this change, such as the need for scheduling, queuing and admission control, are discussed.

In Chapter 4, we introduce the concept of *failure models*. This ensures a strict separation between (a) generic validity conditions that every instance of  $\underline{\mathcal{M}}$  or  $\mathcal{M}$  has to satisfy, and (b) specific failure models, which determine to what extent the system has to adhere to its specification.

In Chapter 5, we discuss the challenges of designing a formal notation for *distributed computing problems* and present, as a solution, a framework for explicitly modeling state transitions in the real-time computing model.

In Chapter 6, we analyze the relationship between the classic and the real-time computing model by providing *transformations* in both directions: We show that a system adhering to some particular instance of  $\mathcal{M}$  can simulate a system that adheres to some particular instance of  $\mathcal{M}$  (and vice versa). Consequently, certain distributed algorithms designed for a classic computing model can be run under the real-time computing model, for example.

#### **Clock Synchronization**

In Chapter 7, we revisit *deterministic internal clock synchronization* in synchronous systems, in the absence of failures and clock drift. It is known that the local clocks of n fully-connected processors cannot be synchronized with precision less than  $(1 - 1/n)\varepsilon$  when using messages with end-to-end delay uncertainty  $\varepsilon$ . A constant time algorithm achieving this bound in the classic computing model also exists [LL84b].

We show that this is not true in the real-time computing model: optimal precision is only achievable with algorithms that take  $\Omega(n)$  time. On the other hand, achieving a sub-optimal precision of  $O(\underline{\varepsilon})$  is achievable in constant time, if, and only if, a constant-time broadcast primitive is available.

In Chapter 8, we provide an optimal solution for the problem of how to continuously estimate a source processor's clock in the case of drifting clocks. The *remote clock estimation* algorithm is complemented by a matching lower bound on the achievable maximum clock reading error.

In Chapter 9, we give examples of how to apply this remote clock reading technique in external as well as fault-tolerant internal clock synchronization.

In Chapter 10, we summarize our results and conclude with an outlook on further work and open issues.

# Part I.

# **Computing Models**

# 2. Classic Distributed Computing

In clock synchronization research [LL84a, BW01, PSR94, AHR93, LL84b], system models are considered where the uncertainty comes from varying message delays, failures, and drifting clocks. Denoted "Partially Synchronous Reliable/Unreliable Models" in [SLWL90], such models are nowadays called (non-lock-step) synchronous models in literature. In order to solely investigate the effects of non-zero step-times, our real-time computing model will be based on the zero step-time synchronous model commonly used in clock synchronization research, e.g., in [LL84b]. Here it will be referred to as the *classic computing model*.

Note that the model described in this chapter is *message-driven*, i.e., computing steps are always triggered by messages [HW05b, BW06]. We do, however, retain compatibility to time-driven models through the concept of *timer messages*, which always arrive when the hardware clock reaches a certain value.

## 2.1. Preliminaries

Let *seq* be a sequence whose elements are totally ordered by some relation  $\prec^{seq}$ . Within this work, the notion of *causal dependency* will be used for various elements (actions, jobs, receive events, drop events, aj-events, st-events) of such a sequence. Every such element x has an associated processor proc(x). There can be two types of dependencies between these elements (cf. *happened before* relation, [Lam78]).

- Message dependency (x → x'): One element x sends or inserts a message which is received or processed by x'. This is further formalized in the following sections.

- Local dependency  $(x \xrightarrow{L} \stackrel{seq}{\to} x')$ : Both elements occur on the same processor and x appears before x' in the sequence seq, formally:  $x \xrightarrow{L} \stackrel{seq}{\to} x' :\Leftrightarrow proc(x) = proc(x') \land x \prec^{seq} x'$ .

Causal dependency  $(x \rightarrow^{seq} x')$  is defined as the transitive closure of both types of dependency, i.e.,

$$x \to^{seq} x' :\Leftrightarrow x \xrightarrow{M} x' \lor x \xrightarrow{L}^{seq} x' \lor (\exists x^* : x \to^{seq} x^* \land x^* \to^{seq} x').$$

**Definition 2.1.** Some sequence *captures message causality* if the ordering of its elements  $(\prec^{seq})$  is consistent with the message dependency relation, formally:  $\forall x, x' \in seq : x \xrightarrow{M} x' \Rightarrow x \prec^{seq} x'$ .

Let seq' be a reordering of some sequence seq. seq' is *causally consistent* with seq if the order of causally dependent elements is maintained, formally:  $\forall x, x' \in seq : x \rightarrow^{seq} x' \Rightarrow x \prec^{seq'} x'$ .

#### 2. Classic Distributed Computing

**Observation 2.2.** If seq captures message causality, seq' is a reordering of seq and seq' is causally consistent with seq, then seq is also causally consistent with seq'.

## 2.2. System Model

We consider a network of *n* processors  $\Pi$ , which communicate by passing unique<sup>1</sup> messages, using either a unicast, multicast or broadcast primitive. The system-wide set of messages in transit will be denoted *intransit\_msgs*. Each processor *p* is equipped with a CPU, some local memory, a hardware clock  $HC_p$ , and reliable, non-FIFO links to all other processors. The hardware clock  $HC_p : \mathbb{R}^+ \to \mathbb{R}^+$  maps dense real-time<sup>2</sup> to dense clock-time; it can be read but not changed by its processor.  $HC_p$  is hence not part of the local state  $state_p$ , but considered separately.

The CPU is running an *algorithm*  $\underline{A}$ , which is specified as (a) a mapping from processor indices to a set of initial states and (b) a transition function. Processor p's set of *initial states* is denoted  $Init_p(\underline{A})$ . The *transition function* takes the processor index p, one incoming message (taken from the current  $intransit\_msgs$ ), receiver processor p's current local state *oldstate* and hardware clock reading  $HC_p$  as input, and yields a list of states and *messages to be sent*, e.g. [oldstate, msg, int.st.<sub>1</sub>, int.st.<sub>2</sub>, newstate], as output. The intermediate states,  $int.st._1$ and  $int.st._2$  in our example, are usually neglected in the classic computing model, as the state transition from *oldstate* to *newstate* is instantaneous anyway. We explicitly model these states to retain compatibility with our real-time computing model, where they will become more important.

Formally, a notation such as  $\underline{A}(m, oldstate, T) = [oldstate, \dots, newstate]$  will be used to refer to the output of the transition function of algorithm  $\underline{A}$  when a message m arrives on a processor with state oldstate at hardware clock time T. For ease of presentation, we will omit the processor index since, in our model, it is implicitly contained in the message (cf. Section 4.1).

Every message arrival (also called message reception) simultaneously causes the message to be removed from *intransit\_msgs* and the receiver processor to change its state and send out all messages according to the transition function (by adding those to *intransit\_msgs*). Such a *computing step* (also called *message processing step*) will be called an *action* in the following. The complete action (message arrival, processing and sending messages) is performed instantly, i.e., in zero time.

Actions can be triggered by three different types of messages: ordinary messages, timer messages and input messages. Ordinary messages are transmitted over the links. The message delay  $\underline{\delta}$  is the difference between the real-time of the action sending the message and the real-time of the action receiving the message. There is a lower bound  $\underline{\delta}^-$  and an upper bound  $\underline{\delta}^+$  on the message delay of every ordinary message.<sup>3</sup>

<sup>&</sup>lt;sup>1</sup>Note that uniqueness is only required for analysis, cf. Section 4.1.

<sup>&</sup>lt;sup>2</sup>We assume that there is some dense Newtonian reference time, referred to as real-time, which is of course only available for analysis purposes.

$<sup>{}^{3}\</sup>underline{\delta}^{-}$  and  $\underline{\delta}^{+}$  are called  $\mu$  and  $\nu$  in [LL84b]. To disambiguate our notation, systems, parameters (like message delay bounds), and algorithms in the classic computing model are represented by underlined variables (usually  $\underline{s}, \underline{\delta}^{-}, \underline{\delta}^{+}, \underline{A}$ ).

*Timer messages* are used for modeling time(r)-driven execution in our message-driven setting: Typical clock synchronization algorithms setup one or more local timers in a computing step, the expiration of which triggers the execution of another computing step. A processor setting a timer is modeled as sending a timer message (to itself) in an action, and timer expiration is represented by the reception of a timer message. Note that timer messages do not need to obey the message delay bounds, since they are received when the hardware clock reaches (or has already reached) the time specified in the timer message.

*Input messages* arrive from outside the system. These messages are exempt from the requirement of having been sent by some processor in the system, and need not satisfy the delay bounds. (As the send time is unknown, this could not be verified anyway.) Usually, the problem specification (see Section 5.2.4) will define restrictions on input messages, e.g., which types of input messages can arrive and their arrival pattern.

**Booting** We assume that every processor p in the system is in some initial state  $istate_p \in Init_p(\underline{A})$  right from the system start, at real-time t = 0. Clearly, in our message-driven setting, at least one input message is required to trigger the first action in an execution. For simplicity, we assert that the *algorithm* may specify whether it requires only one such message or one message for each processor. We will assume that all of these *init messages* arrive within a sufficiently short time interval, so that the initialization uncertainty does not significantly affect the time complexity of our algorithms. On the other hand, we consider the initialization uncertainty to be large enough to prohibit system-wide initial synchronization.

## 2.3. Hardware Clocks

The hardware clock of any processor p starts with some arbitrary initial value  $HC_p(0)$  and then increases strictly, continuously and without bound. Depending on the problem under consideration, some additional restriction on the hardware clock is usually specified. For example,

- in Section 6.3, we assume that the hardware clocks are able to measure some real-time duration within a given interval  $[\mu^-, \mu^+]$ , i.e., we assume that there is some known value  $\tilde{\mu}$ , such that waiting for  $\tilde{\mu}$  clock time units results in a real-time duration no shorter than  $\mu^-$  and no longer than  $\mu^+$ ;

- in Chapter 7, we study the problem of drift-free clock synchronization and, thus, assume that all clocks progress at the same rate as real time.

A common assumption, which we also use in Chapter 8, is that each clock  $HC_p$  has a bounded drift rate of  $\rho_p$ , i.e., t real-time units correspond to at least  $(1 - \rho_p)t$  and at most  $(1 + \rho_p)t$  clock-time units. Formally, for all  $p, t > t' \ge 0$ :

$$(t - t')(1 - \rho_p) \le HC_p(t) - HC_p(t') \le (t - t')(1 + \rho_p)$$

With respect to the notation used in this work, when talking about *time units*, we mean *real-time units*, unless otherwise noted.

## 2.4. Executions

An execution in the classic computing model is a sequence ex of actions and an associated set of n hardware clocks  $HC^{ex} = \{HC_p^{ex}, HC_q^{ex}, \ldots\}$ . An action ac occurring at real-time tat processor p is a 5-tuple, consisting of the processor index proc(ac) = p, the received message msg(ac), the occurrence real-time time(ac) = t, the hardware clock value HC(ac) = $HC_p^{ex}(t)$  and the state transition sequence  $trans(ac) = [oldstate, \ldots, newstate]$  (including messages). Let states(ac) be defined as the list (= sequence) of all states and sent(ac) as the list of all messages in trans(ac). The abbreviations oldstate(ac) and newstate(ac) will be used for the first and the last entry in states(ac).

As an execution is a *sequence* of actions, there is a well-defined total order  $\prec^{ex}$  on actions. We will omit the superscripts of  $\prec^{ex}$  and  $HC_p^{ex}$  if the associated execution is clear from context. A message dependency ( $ac \xrightarrow{M} ac'$ ) between two actions ac and ac' exists if  $msg(ac') \in sent(ac)$ .  $intransit_msgs(ac)$  denotes the set of messages in transit after action ac has sent all its messages but before any following action  $ac' \succ ac$  in ex has had the opportunity to send or process messages.

Formally, a valid execution of an algorithm  $\underline{A}$  must satisfy the following properties:

- EX1 ex must be a sequence of actions with a well-defined total order  $\prec^{ex}$ . The sequence must capture message causality (cf. Definition 2.1) and time(ac) must be non-decreasing.

- EX2 Processor states can only change during an action, i.e., if there are two actions  $ac \prec ac'$ on the same processor p and there is no action on p between ac and ac', newstate(ac) = oldstate(ac').

- EX3 The first action ac at every processor p must occur in an initial state (denoted  $istate_p^{ex}$ ) of  $\underline{A}$ , i.e.,  $istate_p^{ex} = oldstate(ac) \in Init_p(\underline{A})$ .

- EX4 The hardware clock readings of actions must be consistent with the hardware clock associated with the execution, i.e.,  $HC(ac) = HC_{proc(ac)}^{ex}(time(ac))$ . The hardware clock readings must increase strictly  $(\forall t, t', p : t < t' \Rightarrow HC_p^{ex}(t) < HC_p^{ex}(t'))$ , continuously and without bound.

- EX5 Messages must be unique, i.e., there is at most one action sending some message m and at most one action receiving it. Message sending and receiving must be in the correct causal order. Messages can only be sent by and processed by the processor specified in the message.

- EX6 Every non-input message that is received must have been sent.

Note that these properties do not require, for example, that all ordinary messages obey the message delay bounds or that all state transitions are in accordance with the transition function of  $\underline{A}$ . These conditions will be specified by the *failure model* (see Section 4.2).

## 2.5. Systems

A classic system  $\underline{s} = (n, [\underline{\delta}^-, \underline{\delta}^+])$  is a system adhering to the classic computing model defined in Section 2.2, parameterized by the system size n and the interval  $[\underline{\delta}^-, \underline{\delta}^+]$  specifying the bounds on the message delay. The uncertainty  $\underline{\varepsilon}$  is defined as  $\underline{\delta}^+ - \underline{\delta}^-$ .

In [MS06a] and [Mos09], the notion of *s*-admissible executions was used: An execution is <u>s</u>-admissible w.r.t. some system  $\underline{s} = (n, [\underline{\delta}^-, \underline{\delta}^+])$ , if the execution comprises *n* processors and the message delay for each ordinary message stays within  $[\underline{\delta}^-, \underline{\delta}^+]$ . This definition was useful for modeling failure-free executions; however, in the context of this work, it has been replaced with the more powerful concept of "failure models". Informally speaking, a failure model specifies additional properties that an execution must satisfy, for example, "no message takes more than  $\underline{\delta}^+$  time units to be delivered".

Claiming that an algorithm  $\underline{A}$  solves a certain problem  $\mathcal{P}$  for a classic system  $\underline{s}$  under a given failure model  $\underline{C}$  means that all possible executions of  $\underline{A}$  that satisfy  $\underline{C}$  must also satisfy the properties required by  $\mathcal{P}$  (see Chapter 5). The task of finding such an algorithm can be seen as providing a winning strategy to a player in an execution-creation game against an adversary, where the player provides the sets of initial states and the state transition function and the adversary chooses one initial state and the hardware clocks for every processor and controls the message delays (within the bounds  $[\underline{\delta}^-, \underline{\delta}^+]$  provided by the system) as well as other factors permitted by the failure model. Note carefully that it is the system/the adversary and not the algorithm that determines the actual message delays in the classic computing model.

2. Classic Distributed Computing

# 3. Towards the Real-Time Computing Model

At a first glance, zero step-time computing models appear to be a good choice for modeling real-world systems, where message delays are often much higher than message processing times. There are applications like high speed networks, however, where this is not the case. Additionally, and more importantly, the zero step-time assumption inevitably ignores message queuing at the receiver: It is possible, even in the case of large message delays, that multiple messages arrive at a single receiver at the same time. This causes the processing of some of these messages to be delayed until the processor is idle again. Common practice so far is to take this queuing delay into account by increasing the upper bound  $\underline{\delta}^+$  on the message delay. This approach, however, has two disadvantages: First, a-priori information about the algorithm's message pattern is needed to determine a parameter of the system model, which creates cyclic dependencies. Second, in lower bound proofs, the adversary can choose an arbitrary message delay within  $[\underline{\delta}^-, \underline{\delta}^+]$ —even if this choice is not in accordance, i.e., not possible, with the actual message arrival pattern. This could lead to overly pessimistic lower bounds.

It is, of course, not the goal of this work to explicitly model all the phenomenons (receiver queuing, network queuing, scheduling overhead, ...) usually hidden within some adversary-controlled value. Rather, our aim was to find a suitable tradeoff between model complexity and model coverage. Explicitly modeling just non-zero step times and the resulting effects turned out to be an appropriate choice. Other effects, which depend more on the underlying hardware (e.g. network queuing) or which are unsuitable/too detailed for meaningful lower bounds (e.g. different processing times for different messages) are still abstracted away in (overly conservative) system parameters and thus subject to inappropriate exploitation by the adversary.

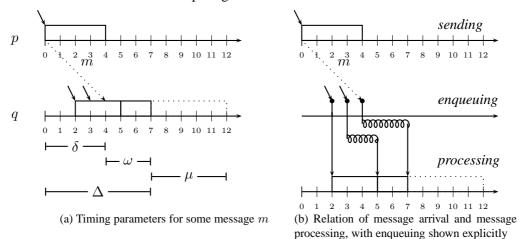

# 3.1. System Model

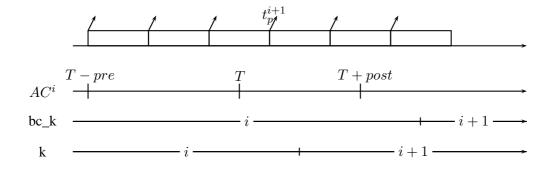

The system model in our real-time computing model is the same as in the classic computing model, except for the following change: A computing step in a real-time system is executed non-preemptively<sup>1</sup> within a system-wide lower bound  $\mu^-$  and upper bound  $\mu^+$ . Note that we allow the processing time and hence the bounds  $[\mu^-, \mu^+]$  to depend on the number of messages sent in a computing step. In order to clearly distinguish a computing step in the