Die approbierte Originalversion dieser Dissertation ist an der Hauptbibliothe der Technischen Universität Wien aufgestellt (http://www.ub.tuwien.ac.at).

The approved original version of this thesis is available at the main library of the Vienna University of Technology (http://www.ub.tuwien.ac.at/englweb/).

#### DISSERTATION

# Semiconductor devices and integrated circuits under short electrical stress

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften

unter der Leitung von

a.o. Univ.-Prof. Dipl.-Ing. Dr. Dionyz Pogany Institut für Festkörperelektronik

eingereicht an der

Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

Dipl.-Ing. Michael Heer Matrikelnummer 9326477 Anton Böck-Gasse 6/1/9, 1210 Wien

| Wien | im Februar 2012 | <br> |

|------|-----------------|------|

To my mother and in memory of my father

#### **Kurzfassung**

Die Fortschritte bei der Verkleinerung der internen Strukturen in modernen elektronischen Geräten und der einhergehenden Verringerung der Betriebsspannungen von integrierten Schaltkreisen haben zu einer Erhöhung der internen Belastungen während elektrostatischer Entladungen (ESD) geführt. Deshalb müssen Schutzstrukturen, welche die auftretenden Überspannungen während ESD auf unkritische Werte begrenzen, ständig verbessert werden, um die zuverlässige Funktion von integrierten Schaltkreisen und elektronischen Systemen zu garantieren. Ebenso stellt die Vermeidung von Latch-up – eine Bezeichnung für unkontrollierbaren Stromfluss in der Stromversorgung – eine fortwährende Herausforderung für integrierte Schaltkreise dar. Mit jedem Verkleinerungsschritt werden die Abstände der internen Strukturen kleiner und deshalb steigt die Latch-up-Empfindlichkeit an. Trotz heutiger Simulationsmöglichkeiten ist in vielen Fällen eine experimentelle Untersuchung des internen Bauteilverhaltens unerlässlich. Dies ermöglicht ein besseres Verständnis des eingetretenen Verhaltens und erlaubt darüber hinaus eine Anpassungen der Simulationsmodelle.

Das transiente interferometrische Abbildungsverfahren (TIM), welches am Institut für Festkörperelektronik an der TU-Wien entwickelt wurde, erlaubt den experimentellen insitu Zugriff von der Bauteilrückseite auf die interne freie Ladungsträger- und Temperaturverteilung in Halbleiterbauelementen. Mit diesem Verfahren konnten die gleichförmige Aktivierung sowie die Skalierungseigenschaften von einzel- und multifinger ESD-Schutzstrukturen untersucht werden. Entdeckte Puls-zu-Puls Instabilitäten in der Bauteilspannung und die Stromdichteverteilung innerhalb der Transistorfinger konnten detailliert von kleinen Strömen bis über die Belastungsgrenze hinaus analysiert werden. Die Ursache der auftretenden Stufen in den Strom-Spannungskurven konnten Instabilitäten im Aktivierungsmuster zugeordnet und mit Simulationen verifiziert werden.

Im Rahmen dieser Arbeit wurden die Messeinrichtungen unter anderem um die Möglichkeit von transienten Latch-up-Tests erweitert, um den Stromfluss im Substratmaterial als Ursache für externes transientes Latch-up eingehend untersuchen zu können. Für unterschiedliche Anordnungen und Ladungsträgerpolaritäten wurde die freie Ladungsträgerkonzentration analysiert und mit Simulationen ergänzt. Gebiete mit latch-up-kritischer freier Ladungsträgerkonzentration konnten lokalisiert, Optimierungsvorschläge erarbeitet und ein Fallbeispiel eines transienten Latch-up-Problems in einem kommerziellen Stromregelungsbaustein eingebracht werden. Die dargestellten Experimente erklärten den dynamischen Latch-up-Mechanismus und die höhere Latch-up-Empfindlichkeit für kurze Pulse.

Abschließend wurden inhomogenitäten in der Temperaturverteilung in einem geöffneten H-Brücken-Treiberbaustein während seines Betriebs in einem Beispielschaltkreis aufgedeckt. Es wurde festgestellt, dass die Ausgangstransistoren von der eingebauten Temperaturschutzschaltung nicht ausreichend geschützt wurden.

#### Abstract

Ongoing progress in down-scaling internal features in modern electronic devices and the corresponding lowering of operating voltages in integrated circuits have led to an increase in internal stress during electrostatic discharge (ESD) events. Thus, protective structures which clamp transient voltages during ESD to safe levels need to be continuously improved to guarantee reliable function of integrated circuits and electronic systems. Furthermore, prevention of latch-up – a synonym for an uncontrollable current flow in the power supply – is a continuing challenge for bulk silicon integrated circuits. The distances of the internal structures decrease with down-scaling, and consequently the sensitivity to latch-up increases. Even with state-of-the-art possibilities for device simulation, an experimental investigation of the internal behavior of semiconductor devices is inevitable in many cases. The experimental results allow a better understanding of the occurring device behavior and adjustments to the simulation models.

The transient interferometric mapping (TIM) method, which was developed at the Institute of Solid State Electronics at the Vienna University of Technology, provides in-situ experimental access to the internal excess charge carrier and temperature distribution from the backside of semiconductor devices. Based on this method, the triggering uniformity as well as the scaling behavior could be investigated in single and multi-finger ESD protection devices. The observed pulse-to-pulse instabilities in device voltage and the current distribution within the fingers of the transistors were analyzed in detail, from low currents up to the destruction level. The origin of observed steps in the pulsed current-voltage (I-V) characteristics could be related to instabilities in the triggering pattern. This finding was verified by device simulations.

Additionally, the TIM setups were adapted and enhanced with a facility for transient latch-up (TLU) testing to perform intensive analysis of substrate current flow acting as a trigger for possible external transient latch-up. The transient excess carrier concentration was studied for various layout configurations and injection carrier types and the results were complemented with device simulations. Regions with latch-up critical excess carrier concentration were identified and hints for layout optimizations were prepared. A case study of a transient induced latch-up problem in a commercial power control device was presented. The experiments revealed the dynamic latch-up triggering mechanism and the higher latch-up sensitivity for short pulses.

Finally, hot spots in an opened H-bridge driver IC were uncovered in-situ during full operation in an application board. It was found, that the output transistors were not sufficiently protected by the built-in thermal shutdown circuit.

#### Acknowledgements

I would like to acknowledge all those, who assisted me with information and advices at various stages of this thesis and who made this period a very fruitful and memorable time for me. In particular I am very thankful for the opportunity to work in such a high sophisticated research unit at the Institute of Solid State Electronics, which is lead by Prof. Dr. Emmerich Bertagnolli, at the Vienna University of Technology.

I am grateful to Prof. Dr. Dionyz Pogany for supervising this thesis with profound knowledge, for his valuable suggestions and guidance as well as for always being available for consultation throughout the course of this work.

I thank Infineon Technologies, ST Microelectronics, X-FAB Semiconductor Foundries, Fraunhofer-IZM, Diodes Incorporated and Atmel for providing test structures, ESD circuits and even prototypes of commercial integrated circuits (ICs). The contributions of Krzysztof Domański, Lorenzo Cerati, Horst Gieser, Mike Street, Peter Grombach, Jürgen Teichmann, Gaudenzio Meneghesso and Winfried Soppa to the presented experiments are highly acknowledged.

I am indebted to my colleagues Viktor Dubec, Wasinee Mamanee, Georg Haberfehlner, Jan Kuzmik, and – especially – Sergey Bychikhin for sharing their experience by providing thoughtful background information, for their helpful cooperation and for our insightful discussions.

The administrative support of Christine Brendt, Silvia Pflug and Ms Dietlinde Egger as well as the support of the technicians Wolfgang Schramek, Johannes Prinzinger, Peter Kröll and Erich Riegler is gratefully acknowledged.

Thank is owed to my brother Rudolf, Larissa Blaimschein, Helmut Mayrhofer and Thomas Pötsch for valuable suggestions and corrections.

Finally, I want to thank my family for their support and patience.

# Contents

| K            | urzia | ssung   |                                        | 1            |

|--------------|-------|---------|----------------------------------------|--------------|

| $\mathbf{A}$ | bstra | ıct     |                                        | iii          |

| $\mathbf{A}$ | ckno  | wledge  | ements                                 | $\mathbf{v}$ |

| 1            | Intr  | oducti  | ion                                    | 1            |

|              | 1.1   | Motiv   | ation                                  | 1            |

|              | 1.2   | Scope   | and Outline                            | 3            |

|              | 1.3   | Silicor | n technologies                         | 5            |

|              |       | 1.3.1   | CMOS bulk silicon technology           | 5            |

|              |       |         | Parasitic SCR structures               | 6            |

|              |       |         | Thermal issues                         | 7            |

|              |       | 1.3.2   | Silicon-on-insulator technology        | 8            |

|              | 1.4   | Electr  | ostatic discharge                      | 10           |

|              |       | 1.4.1   | ESD models                             | 11           |

|              |       |         | Human body model                       | 11           |

|              |       |         | Machine model                          | 12           |

|              |       |         | Charged device model                   | 12           |

|              |       | 1.4.2   | ESD protection levels                  | 14           |

|              |       |         | ESD protection at chip level           | 14           |

|              |       |         | System level ESD protection            | 17           |

|              |       |         | ESD protection at production           | 18           |

|              |       |         | ESD protection at the consumer         | 18           |

|              | 1.5   | Latch-  | -up in bulk CMOS circuits              | 19           |

|              |       | 1.5.1   | Latch-up types                         | 19           |

|              |       |         | Internal latch-up                      | 19           |

|              |       |         | External latch-up                      | 19           |

|              |       |         | Static latch-up                        | 20           |

|              |       |         | Transient latch-up                     | 20           |

|              |       | 1.5.2   | Latch-up protection in CMOS technology | 20           |

viii CONTENTS

|          |      |         | Distances                                               |

|----------|------|---------|---------------------------------------------------------|

|          |      |         | Well resistances                                        |

|          |      |         | Guard-rings                                             |

|          | 1.6  | Electri | cal testing methods                                     |

|          |      | 1.6.1   | Transmission line pulse generators                      |

|          |      | 1.6.2   | Solid-state pulse generators                            |

|          | 1.7  | Optica  | l investigation method                                  |

|          |      | 1.7.1   | Contribution of the thermo-optical effect               |

|          |      | 1.7.2   | Contribution of the plasma-optical effect               |

|          |      | 1.7.3   | Optical phase shift                                     |

| <b>2</b> | ESI  | ) Inves | etigations 35                                           |

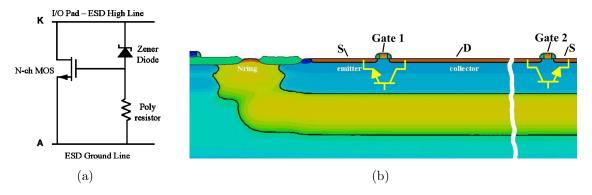

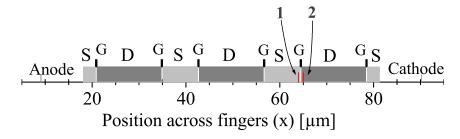

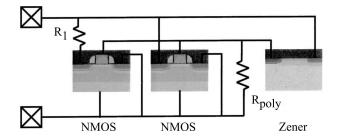

|          | 2.1  |         | ption of the investigated devices                       |

|          | 2.2  |         | mental details                                          |

|          |      | 2.2.1   | Stressing scheme                                        |

|          |      | 2.2.2   | Optical methods                                         |

|          |      | 2.2.3   | Device simulation                                       |

|          | 2.3  | Electri | cal characterization                                    |

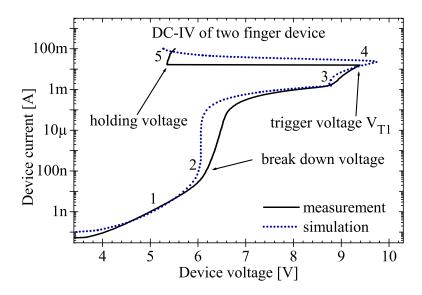

|          |      | 2.3.1   | DC characteristics                                      |

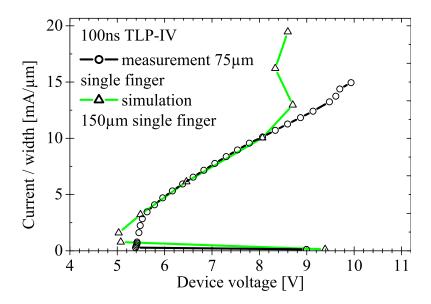

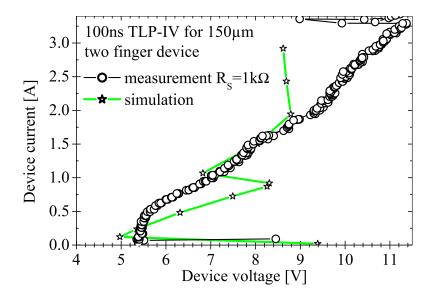

|          |      | 2.3.2   | Pulsed I-V characteristics                              |

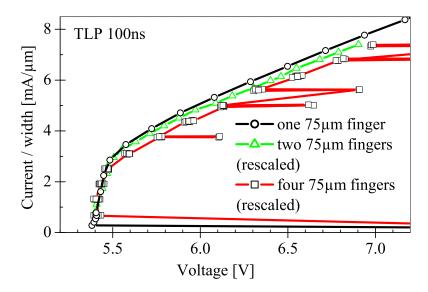

|          |      |         | Single and two-finger devices                           |

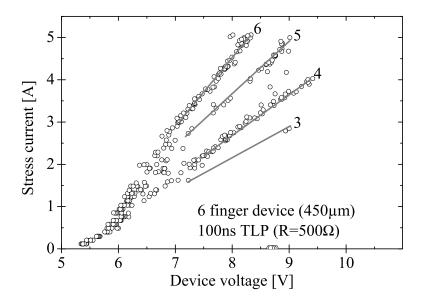

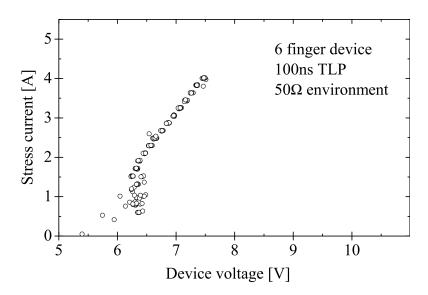

|          |      |         | Four and more finger devices                            |

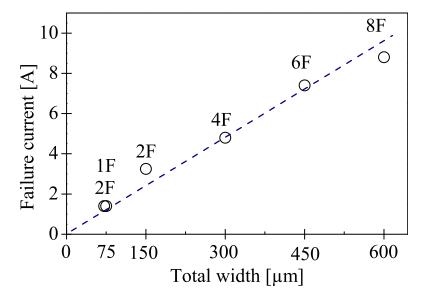

|          |      |         | Failure current                                         |

|          | 2.4  | Interna | al device behavior                                      |

|          |      | 2.4.1   | Inhomogeneous triggering                                |

|          |      | 2.4.2   | Homogeneous triggering                                  |

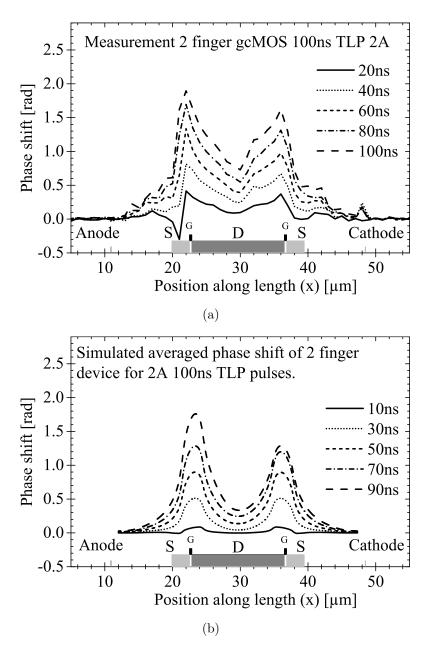

|          |      |         | Single and two-finger devices                           |

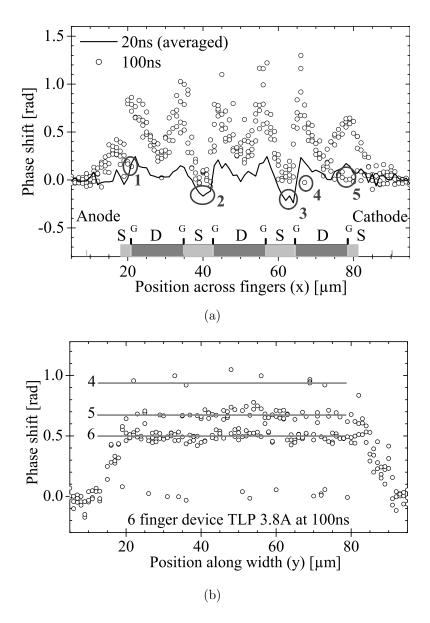

|          |      |         | Four and more finger devices                            |

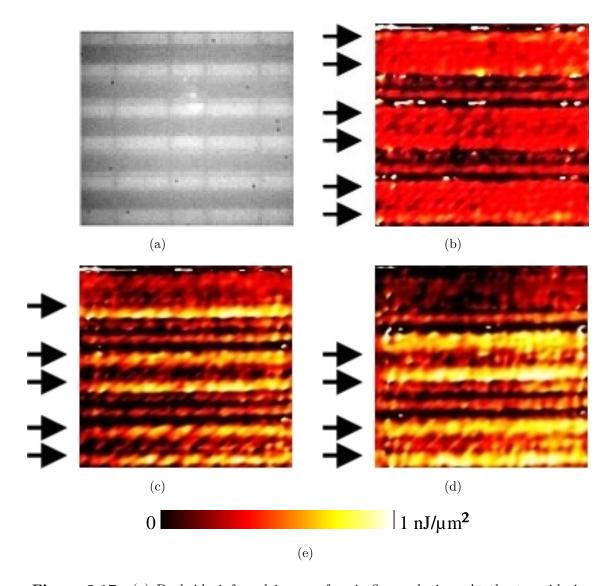

|          |      | 2.4.3   | Destructive ESD pulses                                  |

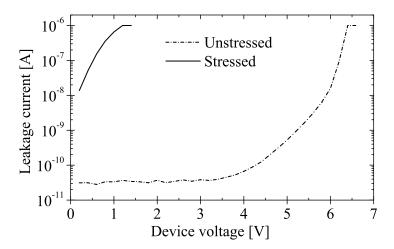

|          |      | 2.4.4   | Failure analysis                                        |

|          | 2.5  | Summ    | ary of ESD investigations                               |

| 3        | Late | ch-up i | nvestigations 57                                        |

|          | 3.1  | -       | al transient injection                                  |

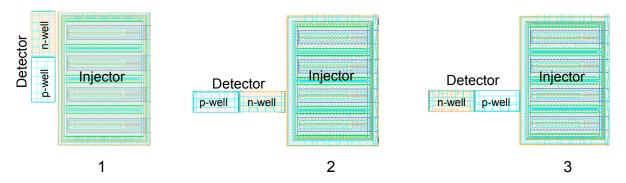

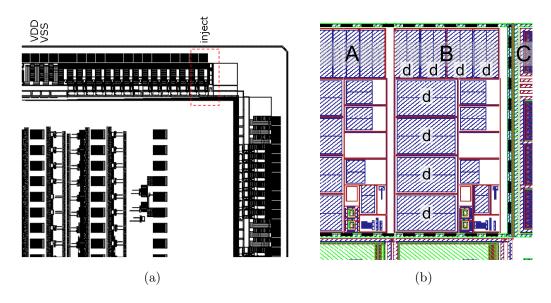

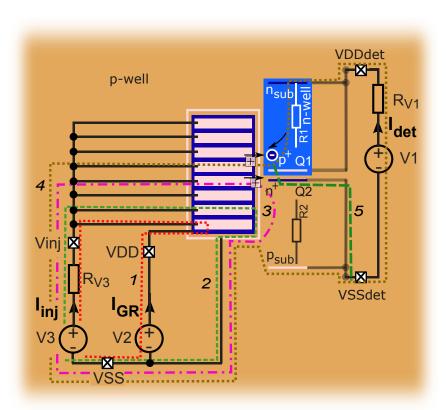

|          |      | 3.1.1   | Description of test structures and I/O cells            |

|          |      |         | Latch-up detector structure                             |

|          |      |         | Test structures for external latch-up investigations 61 |

|          |      |         | Commercial I/O cells                                    |

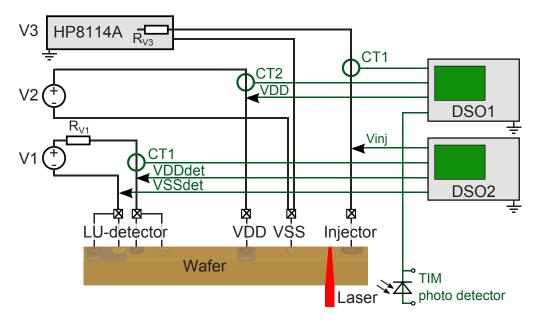

|          |      | 3.1.2   | Experimental details and setup customization            |

|          |      |         |                                                         |

CONTENTS

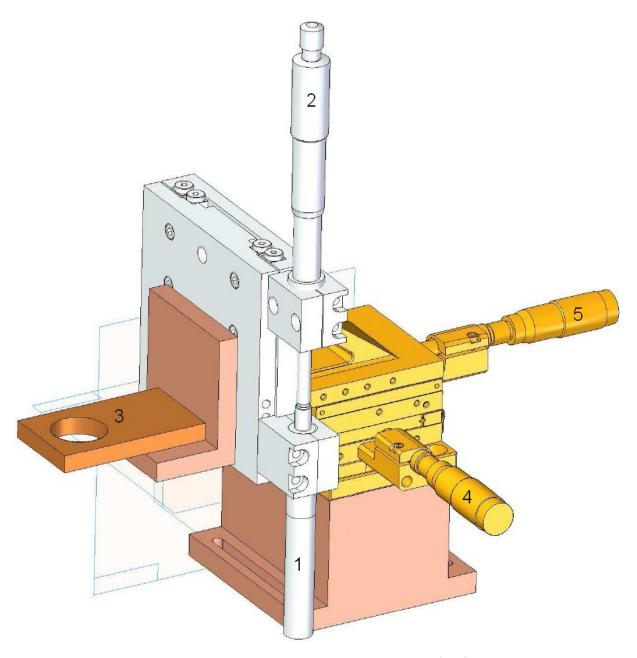

|   |        |                | Hardware                                                          |

|---|--------|----------------|-------------------------------------------------------------------|

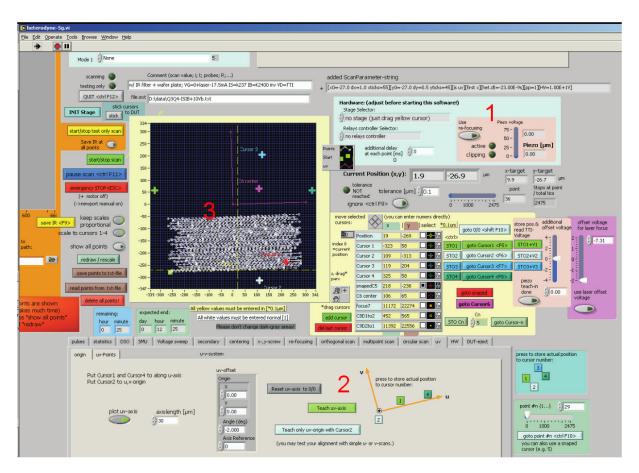

|   |        |                | Automation software                                               |

|   |        |                | TCAD Simulation                                                   |

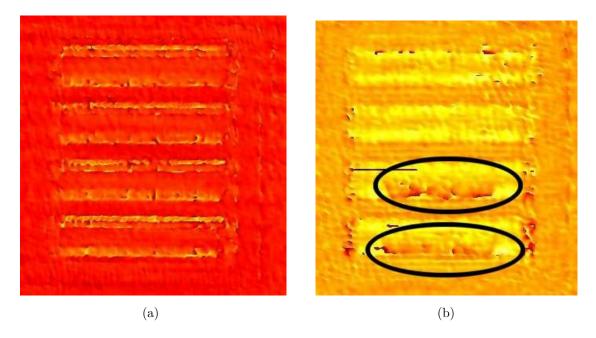

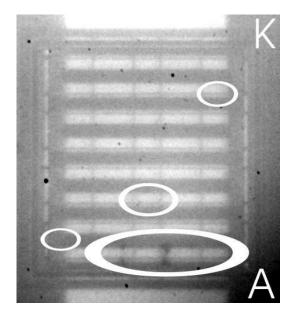

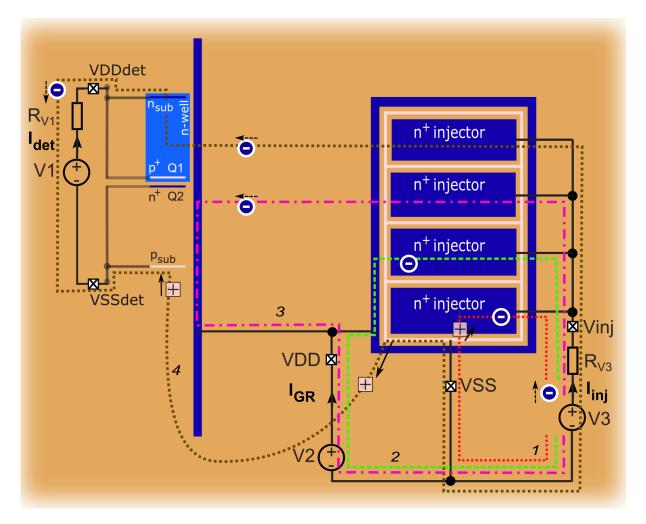

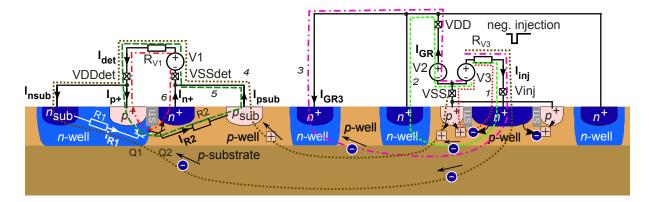

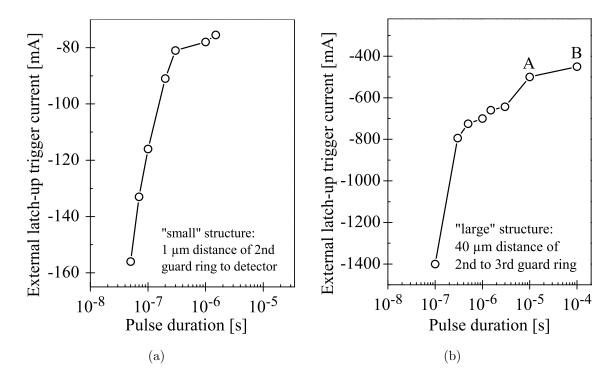

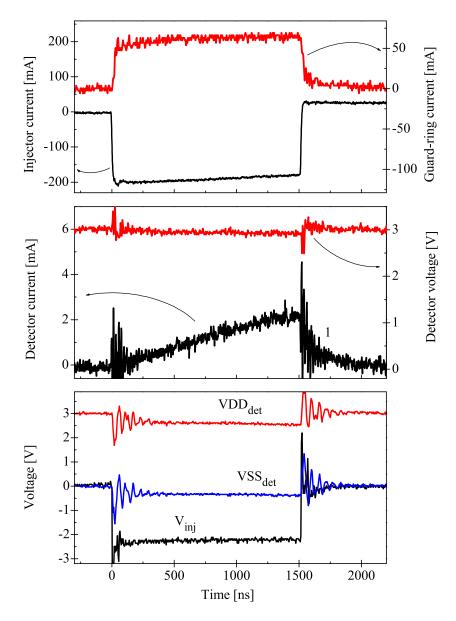

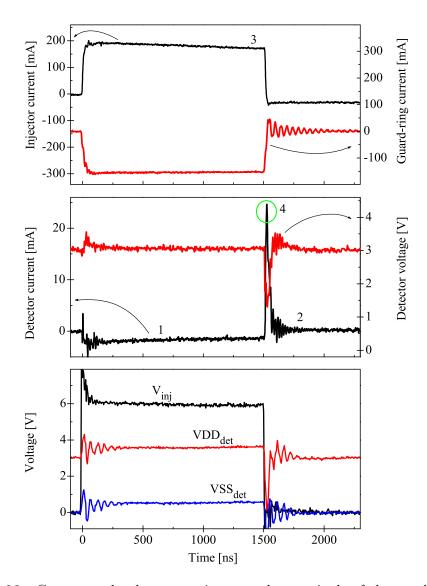

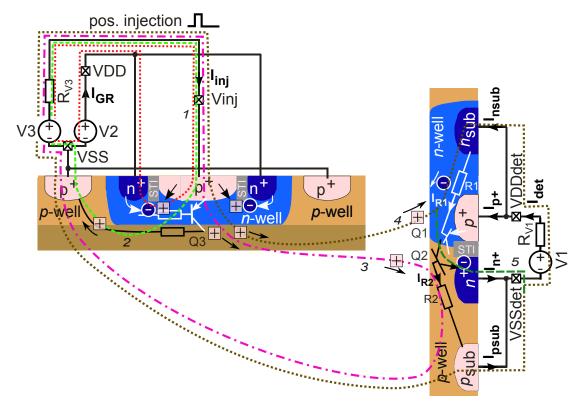

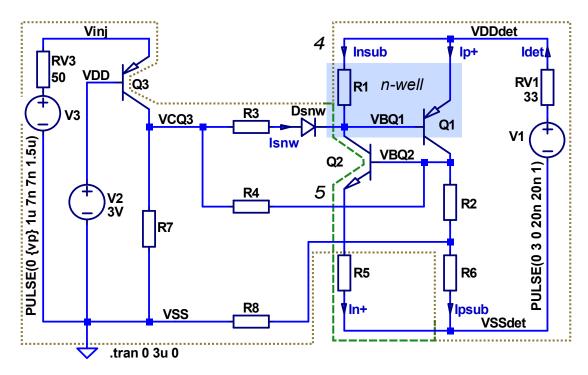

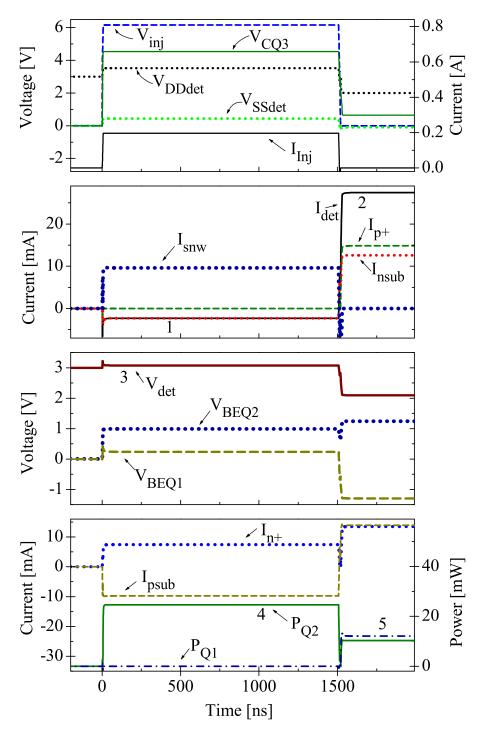

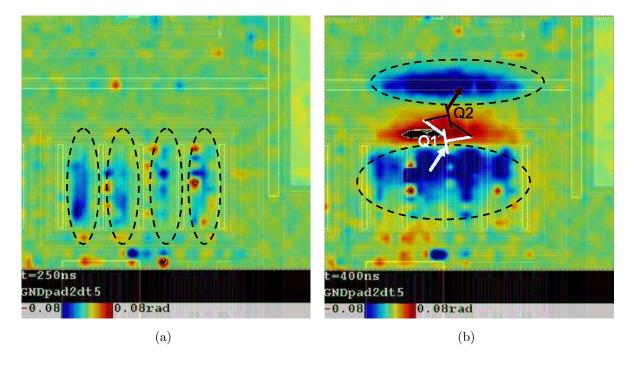

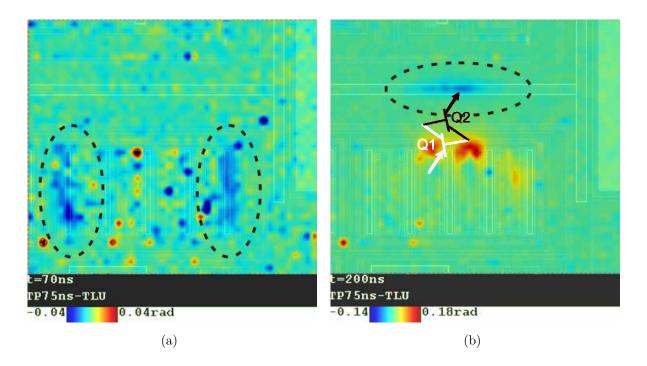

|   |        | 3.1.3          | Investigation of negative carrier injection at test structures 67 |

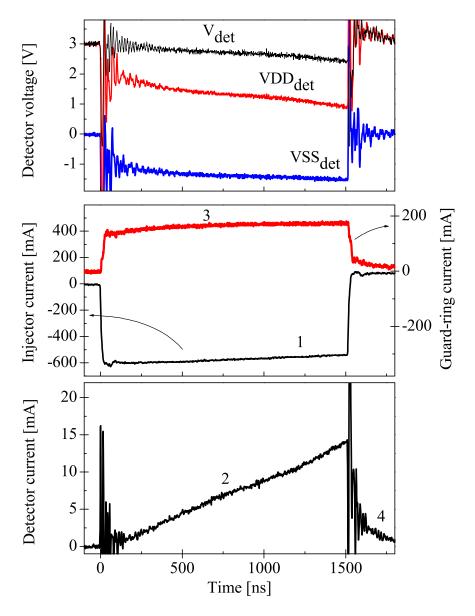

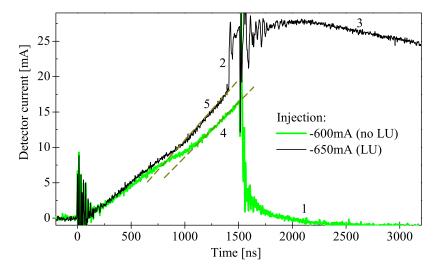

|   |        |                | Latch-up identification                                           |

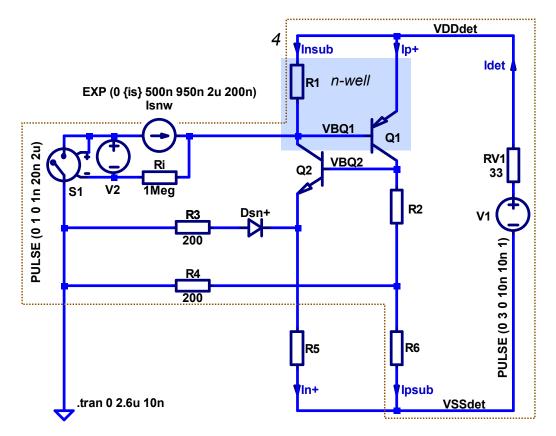

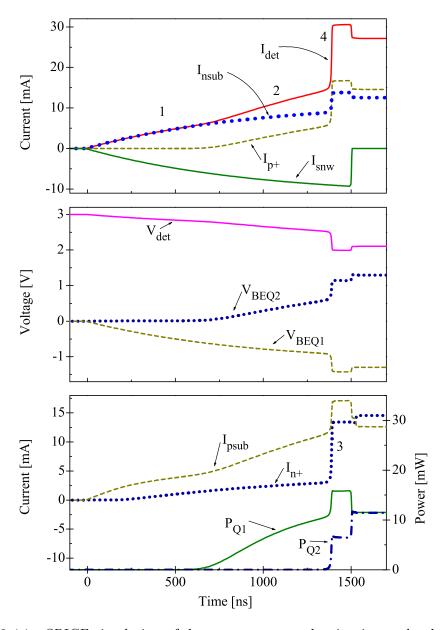

|   |        |                | SPICE modeling of negative injection                              |

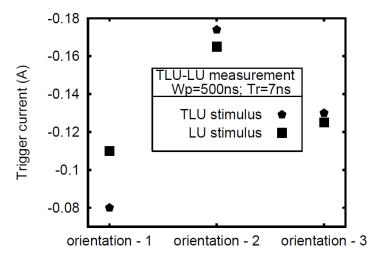

|   |        |                | Trigger current characteristics for negative injection            |

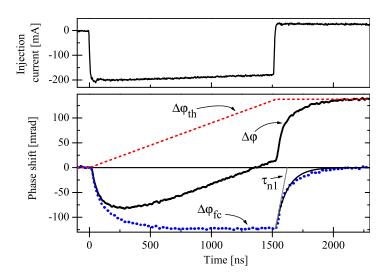

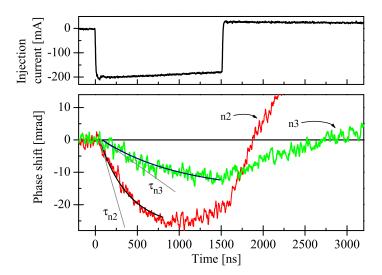

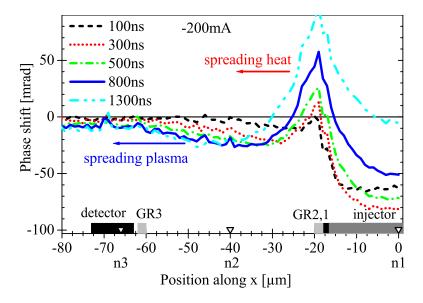

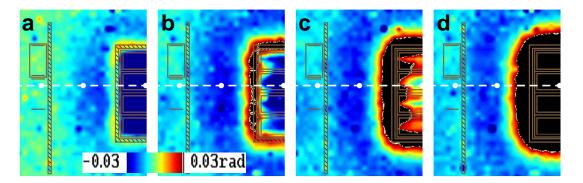

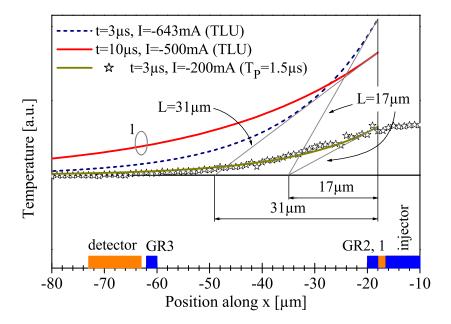

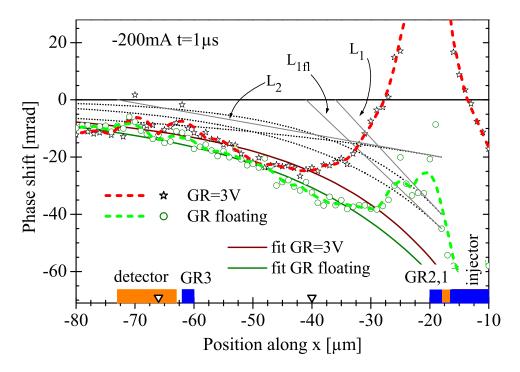

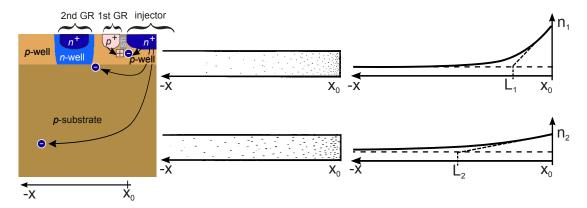

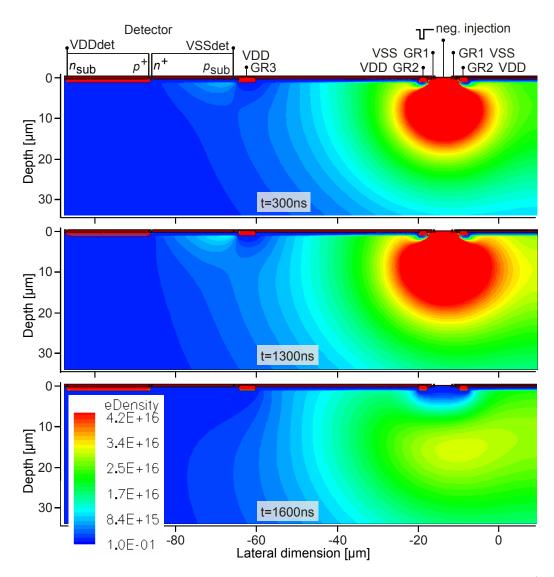

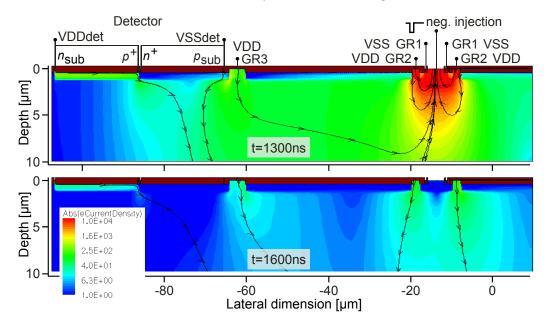

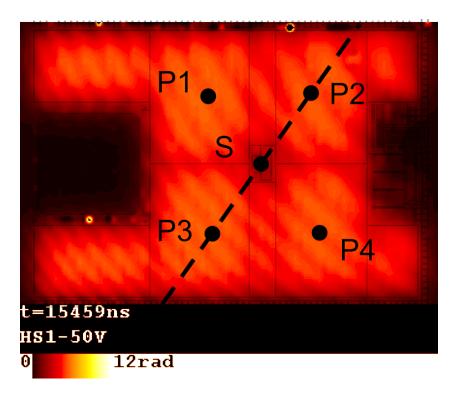

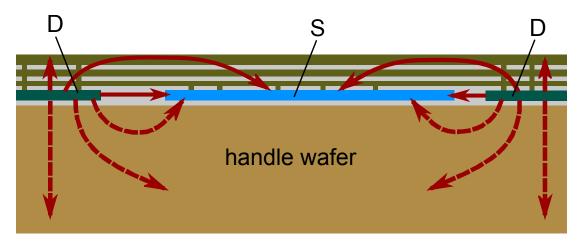

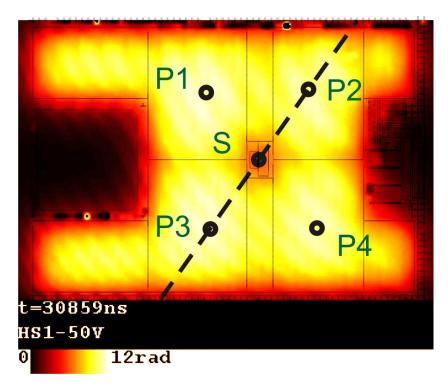

|   |        |                | Excess carrier and heat spreading during negative injection       |

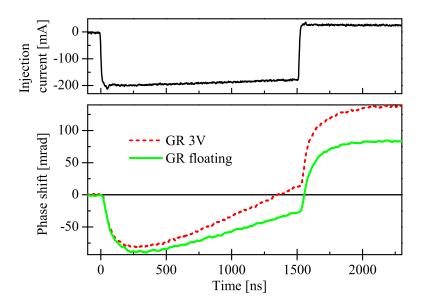

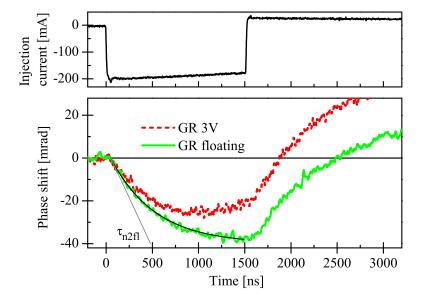

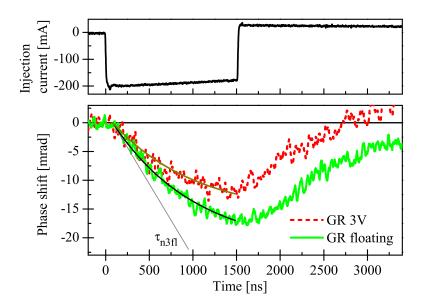

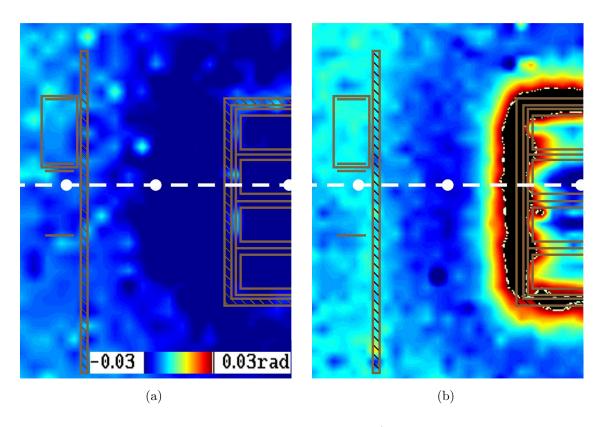

|   |        |                | Effect of guard-rings on carrier spreading                        |

|   |        |                | Comparison to TCAD simulations and discussion                     |

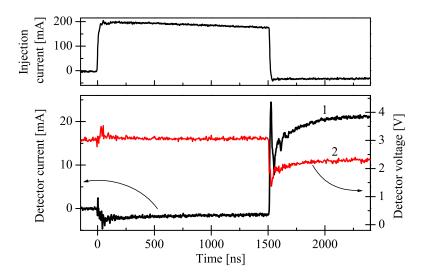

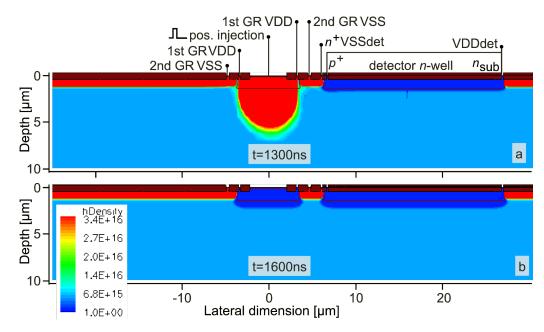

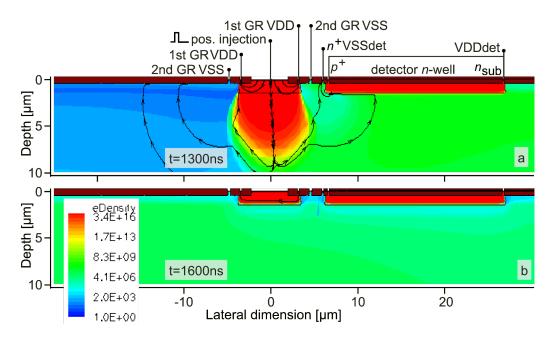

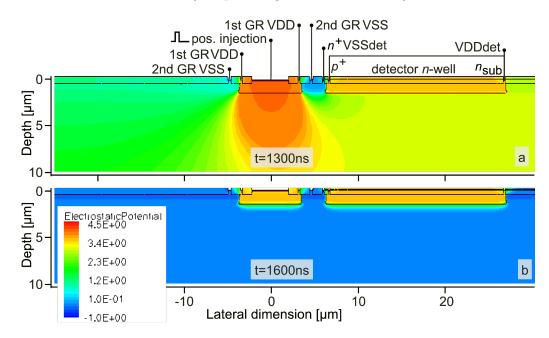

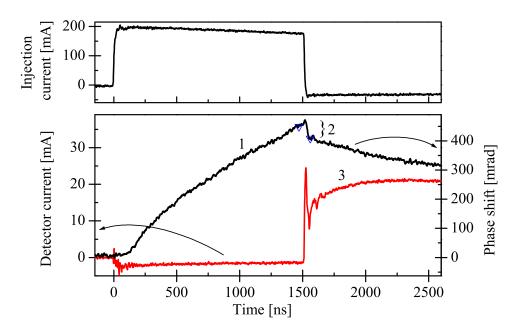

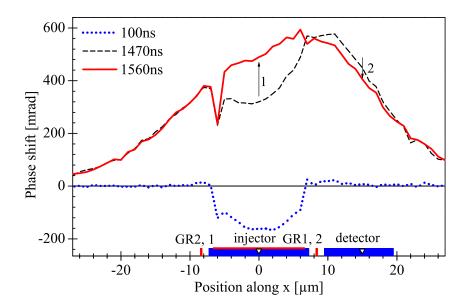

|   |        | 3.1.4          | Investigation of positive carrier injection at test structures 92 |

|   |        |                | Latch-up identification                                           |

|   |        |                | Trigger current characteristics for positive injection 94         |

|   |        |                | Excess carrier and heat spreading below latch-up condition 94     |

|   |        |                | SPICE modeling of positive injection                              |

|   |        |                | Comparison to TCAD simulations                                    |

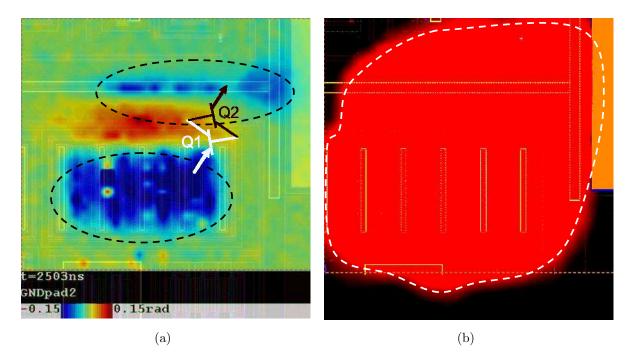

|   |        |                | Transition to the latched state                                   |

|   |        | 3.1.5          | Investigation of proximity effects                                |

|   |        |                | Test structure case                                               |

|   |        |                | Investigation of a commercial I/O cell                            |

|   | 3.2    | Latch-         | -up in a commercial power control device                          |

|   |        | 3.2.1          | Description of investigated devices                               |

|   |        | 3.2.2          | Experimental details                                              |

|   |        |                | Stressing scheme                                                  |

|   |        |                | Refocusing system                                                 |

|   |        | 3.2.3          | Latch-up identification                                           |

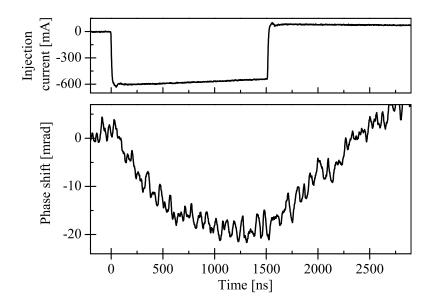

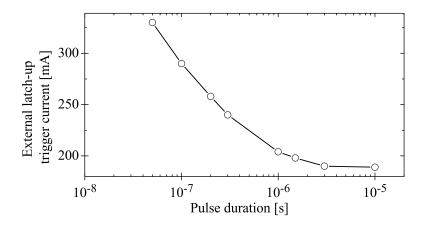

|   |        | 3.2.4          | Effect of pulse duration on transient latch-up                    |

|   |        | 3.2.5          | Latch-up onset under negative stress voltages at VIN              |

|   |        | 3.2.6          | Latch-up onset under positive stress voltages at VIN              |

|   |        | 3.2.7          | Improvement of the latch-up robustness                            |

|   | 3.3    | Summ           | tary of latch-up investigations                                   |

| 4 | TT - 4 |                | *- 1 -1(1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1                         |

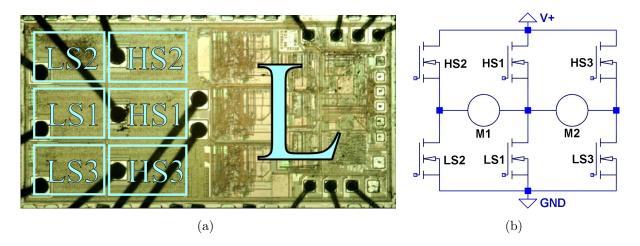

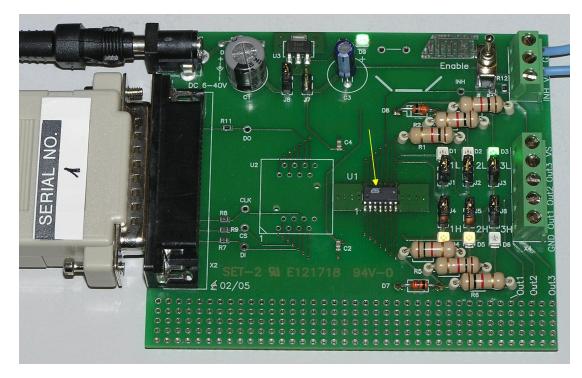

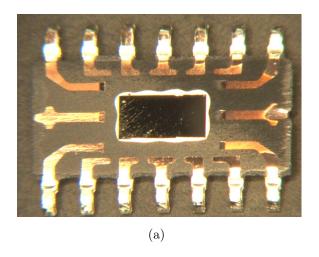

| 4 |        | -              | in half bridge IC  133                                            |

|   | 4.1    |                | e description                                                     |

|   | 4.2    | -              | Device preparation 126                                            |

|   |        | 4.2.1<br>4.2.2 | Device preparation                                                |

|   |        |                | Electrical methods                                                |

|   |        | 4.2.3          | Optical methods                                                   |

|                  | 4.3                    | Electrical characterization of thermal shutdown | 137 |

|------------------|------------------------|-------------------------------------------------|-----|

|                  | 4.4                    | Internal behavior during thermal shutdown       | 139 |

|                  | 4.5                    | Comparison to electrothermal simulations        | 146 |

|                  | 4.6                    | Summary of hot spot investigations              | 147 |

| 5                | Cor                    | aclusion and prospects                          | 149 |

| $\mathbf{A}_{]}$ | ppen                   | dices                                           | 153 |

| $\mathbf{A}$     | TIN                    | $\Lambda$ setups                                | 153 |

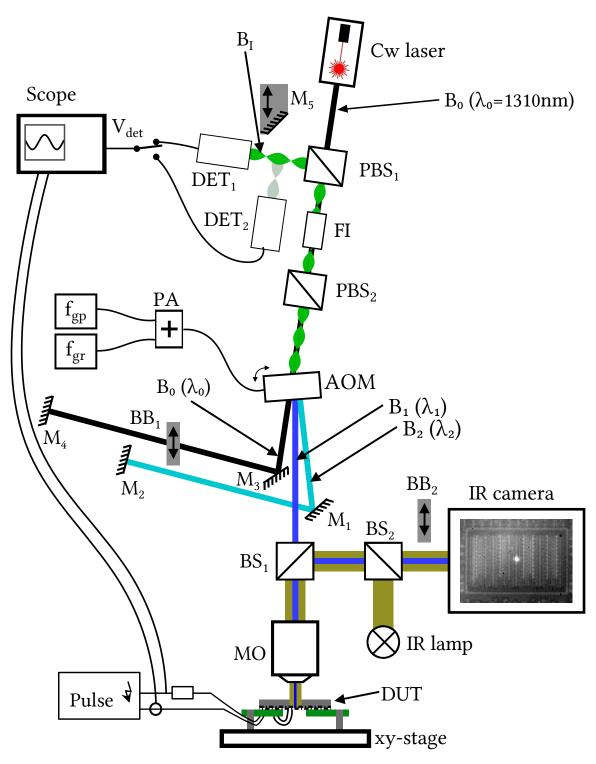

|                  | A.1                    | Scanning TIM setup                              | 153 |

|                  |                        | A.1.1 Setup description                         | 155 |

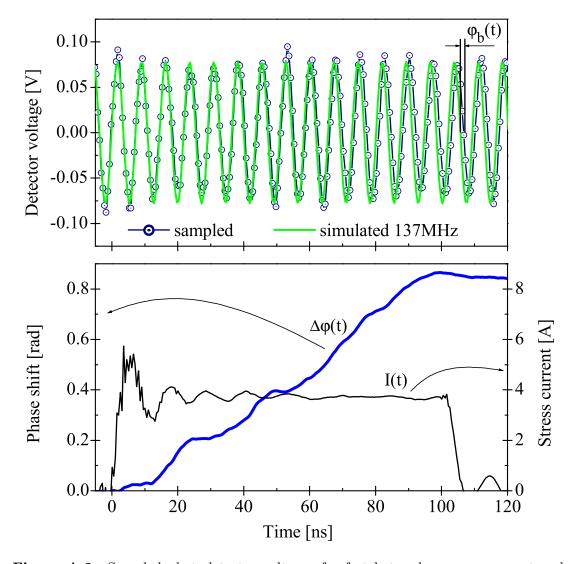

|                  |                        | A.1.2 Phase shift extraction                    | 157 |

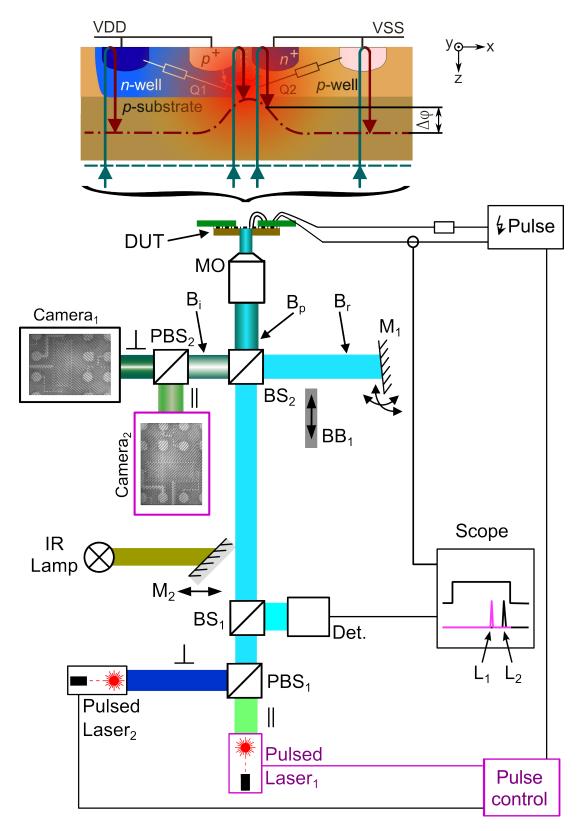

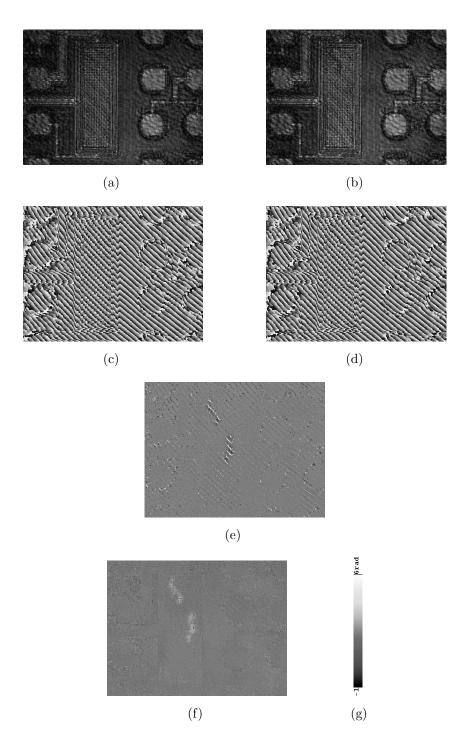

|                  | A.2                    | Holographic TIM setup                           | 160 |

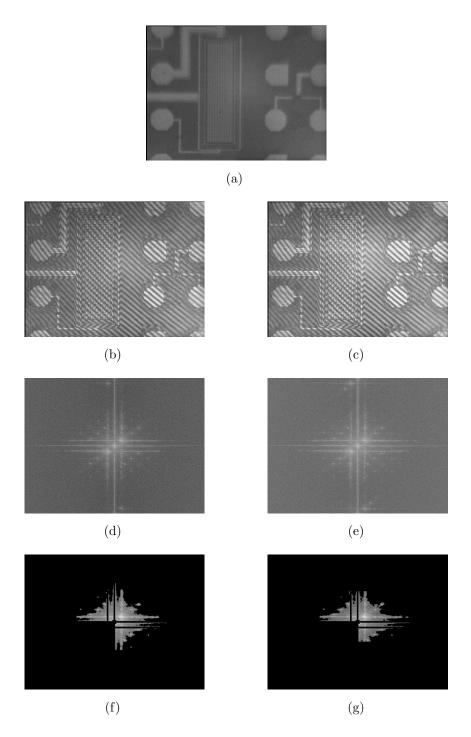

|                  |                        | A.2.1 Two-dimensional interferometry            | 162 |

|                  |                        | A.2.2 Phase shift extraction                    | 163 |

| В                | Ref                    | ocusing system                                  | 169 |

| A                | crony                  | yms                                             | 173 |

| Li               | $\operatorname{st}$ of | frequently used symbols                         | 177 |

| Li               | $\operatorname{st}$ of | Tables                                          | 179 |

| Li               | $\operatorname{st}$ of | Listings                                        | 179 |

| Li               | $\operatorname{st}$ of | Figures                                         | 181 |

| Bi               | bliog                  | graphy                                          | 187 |

| Li               | $\operatorname{st}$ of | Publications                                    | 199 |

| Tn               | dov                    |                                                 | 203 |

# Chapter 1

# Introduction

Nowadays, microelectronic devices are widely accepted and appreciated by society and they are used nearly everywhere in modern life. Due to mass production and down-scaling internal features from micro- to nanometer-scale, integrated circuits (ICs) get continuously cheaper and higher functionality. They make our life easier (e.g. mobile phones), more comfortable (e.g. remote controls) and safer (e.g. electronic stability control in automobiles).

## 1.1 Motivation

Consumer electronics are often exposed to unknown handling in an unknown environment. If the consumers are electrostatically charged – e.g. after walking along carpets – and touch a contact pin of a device electric discharge occurs through the touched pin. Such discharge process is called electrostatic discharge (ESD) and the local power density in an integrated circuit during such a discharge is very high<sup>1</sup>. Electrostatic discharge may lead to malfunction of the stressed pin – or in worst case – to damage of the whole device (e.g. ESD-induced latch-up). Therefore, microelectronics needs to be protected by special ESD protection structures, which prevent damage during such discharges by clamping the transient voltages to safe levels. Ongoing progress in down-scaling internal features in modern electronic devices and the corresponding lowering of operating voltages in integrated circuits have led to an increase in internal stress during ESD events. Thus, protective structures which clamp transient voltages during ESD to safe levels need to be

The later presented ST-5 device sustains 75 W for 100 ns in  $\sim 600 \,\mu\text{m} \times 3 \,\mu\text{m} \times 3 \,\mu\text{m}$  – resulting in roughly  $10^{16} \,\text{W/m}^3$ .

continuously improved to guarantee reliable function of integrated circuits and electronic systems.

With increasing number of input/output (I/O) pins the occupied chip area of the corresponding ESD protection elements gets more relevant and smaller protection elements are desirable. Improvements of already qualified ESD protection circuits are necessary when:

- ➤ Next scaling of lithography process is launched smaller area leads to higher power density.

- > Next lower operating voltage is introduced lower trigger voltage is required.

- ➤ Higher demands on device robustness are planned (e.g. in automotive industry) higher failure currents are necessary.

Another important driving force for improving device robustness are expensive recalls and follow-up costs, if devices mounted in valuable or safety-relevant products (e.g. trigger circuits for airbags) fail in the field. Even with state-of-the-art possibilities for device simulation, an experimental investigation of the internal behavior of semiconductor devices is inevitable in many cases. The experimental results allow a better understanding of the occurring device behavior and adjustments to the simulation models.

The transient interferometric mapping (TIM) method, which was developed at the Institute of Solid State Electronics at the Vienna University of Technology, provides in-situ experimental access to the internal excess charge carrier and temperature distribution from the backside of semiconductor devices. Nano-second time resolution and micrometer space resolution make this method well suited for investigations in the ESD regime. Based on this method, the triggering uniformity as well as the scaling behavior of prototypes for new single and multi-finger ESD protection devices should be investigated. The current distribution within the fingers and current sharing over all fingers of the transistors should be analyzed from low currents up to the destruction level.

Furthermore, prevention of latch-up – a synonym for an uncontrollable current flow in the power supply – is a continuing challenge for bulk silicon integrated circuits. The distances to parasitic silicon-controlled rectifier (SCR) structures decrease with down-scaling, and consequently the sensitivity to latch-up increases. Latch-up occurs, when a conductive path (e.g. a parasitic SCR structure or a parasitic bipolar transistor) between the voltage-supply and ground is activated in a circuit. The triggering mechanisms are often substrate currents originating from overshoots due to impedance mismatch, coil discharge, electrostatic discharge or electrical over-stress events. Generally, latch-up leads

to destruction of the circuit – unless the current is sufficiently fast limited by external devices. Thus, a lot of effort is made to reduce substrate currents and to prevent latch-up. Nowadays latch-up protection concepts with various guard-ring structures lead to complex layouts, which cannot be simulated in all details with reasonable effort. Consequently, experimental verification – and in case of problems experimental failure location – is essential.

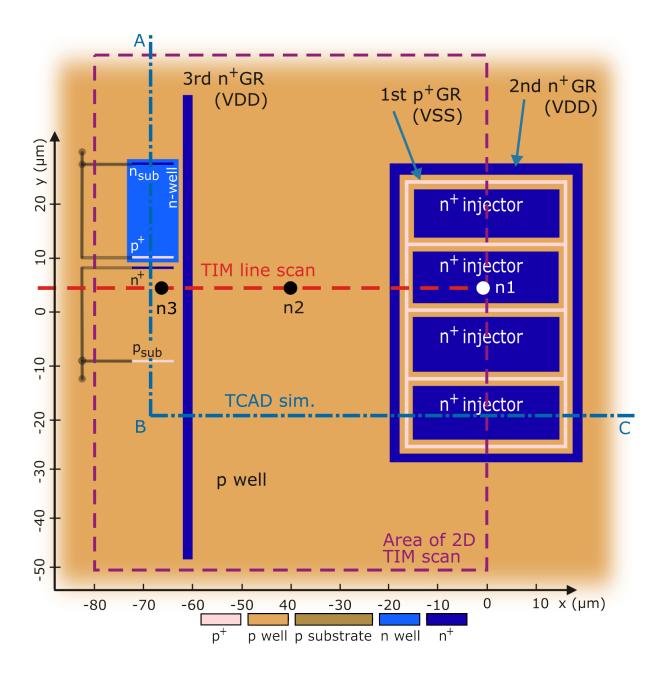

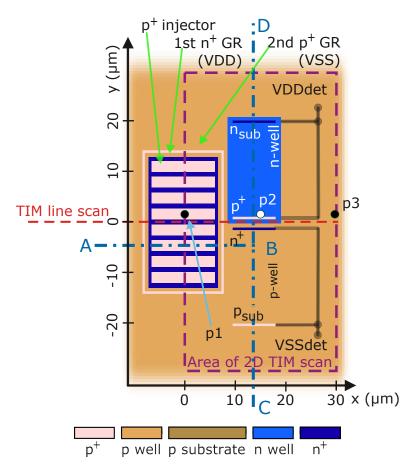

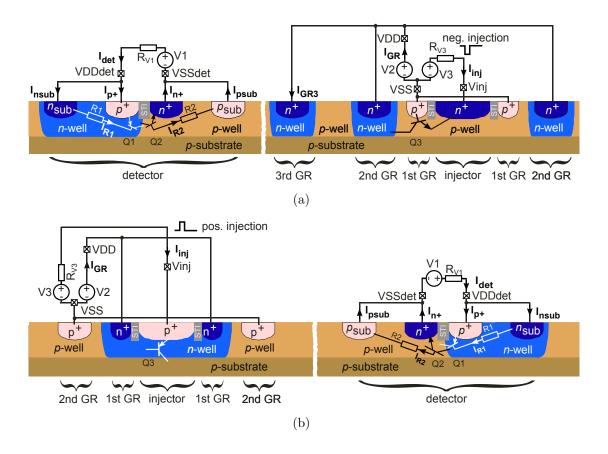

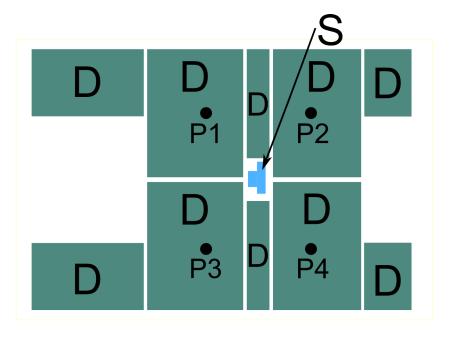

Substrate currents causing external latch-up should be experimentally analyzed in the most prone test structures of K. Domański, who performed basic electrical experiments on many different latch-up test structures and stripped-down two-dimensional simulations. The higher sensitivity of these test structures for transient latch-up (TLU) – a three dimensional triggering mechanism is supposed – should be explained by analysis of the substrate current distribution using the TIM method. Therefore, the TIM setup needs to be adapted and enhanced with a facility for transient latch-up testing to perform intensive analysis of substrate current flow acting as a trigger for possible external transient latch-up. The transient excess carrier concentration should be studied for various layout configurations and injection carrier types under several guard-ring bias conditions. Furthermore, commercial I/O cells should be analyzed and hints for layout optimizations should be prepared.

With increasing device complexity, the simulation of integrated circuits gets more and more difficult. The behavior of complex chips cannot be simulated and predicted in all details. Therefore, small units are designed, simulated and for final qualification experimentally verified. The qualified units are collected in libraries for designing more complex integrated circuits. In some cases it might happen that problems occur due to interaction between library elements and the circuit does not behave as expected. Then electrical and optical measurement methods are essential to localize the failure position and analyze its origin. A case study of a transient induced latch-up problem in a commercial power control IC should demonstrate the ability of substrate current analysis in (for us) unknown device layouts. Finally, suspected hot spot problems during reliability tests of an H-bridge driver IC need to be investigated in-situ during full operation in an application board.

# 1.2 Scope and Outline

In the first Chapter a brief introduction to silicon technologies, electrostatic discharge, latch-up as well as to the state-of-the-art electrical and optical testing methods is given.

The verification of new ESD protection structures ( $\sim 400 \, \mu m^2$ ) for ESD libraries is presented in the second Chapter. In the third Chapter, the experiments get more complex with latch-up investigations under several bias conditions and layout configurations with distributed devices. Then, unknown area is entered with latch-up failure analysis of a complete power control device with unknown activity of its circuit elements. A hot spot case study of an opened H-bridge driver IC ( $\sim 4\,000\,000\,\mu m^2$ ) during full operation in an application board is presented in Chapter 4. Finally, Chapter 5 concludes the investigations and shows prospects for future development.

# 1.3 Silicon technologies

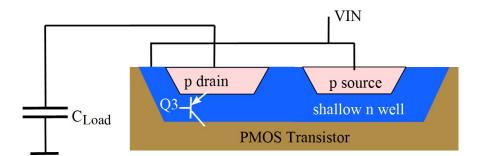

The investigated devices are fabricated in bulk silicon technology and in silicon-on-insulator (SOI) technology. These technologies provide various device types [1] such as diodes, bipolar transistors, p-channel metal oxide semiconductors (PMOS) and n-channel metal oxide semiconductors (NMOS), SCRs etc.

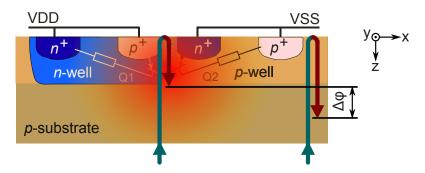

### 1.3.1 CMOS bulk silicon technology

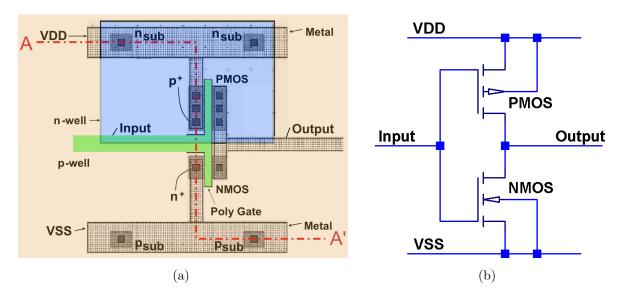

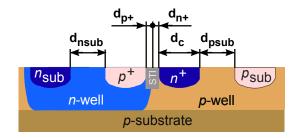

CMOS (complementary MOS) bulk silicon technology is mostly based on low doped p substrate, where p and n regions are created by diffusion or implantation processes. This technology allows the use of NMOS transistors, which can be placed directly at p substrate or in higher doped p wells as well as the use of PMOS transistors, which are placed in n wells. An exemplary layout section of a usual inverter structure in CMOS technology is shown in Figure 1.1a [2]. The corresponding circuit diagram is shown in Figure 1.1b [3]. The Figures show the PMOS transistor at the top, which can switch the output to VDD and at the bottom they show the NMOS transistor, which can switch the output to VSS. Both gates are connected to the input and the drain contacts are connected to the output.

**Figure 1.1:** CMOS inverter (a) typical layout (after [2]), (b) circuit diagram (after [3]).

The wells of the transistors must be connected to potentials in such a way, that any forward current flow between p and n wells is prevented. This is achieved by reverse

biasing (blocking) these parasitic junctions. This gives the method the name junction isolation. The p substrate and the p wells are usually connected with a  $p_{\text{sub}}$  diffusion<sup>2</sup> to the lowest potential (VSS) and the n wells with an  $n_{\text{sub}}$  diffusion to the highest potential (VDD).

#### Parasitic SCR structures

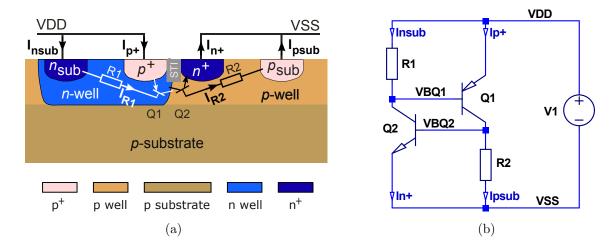

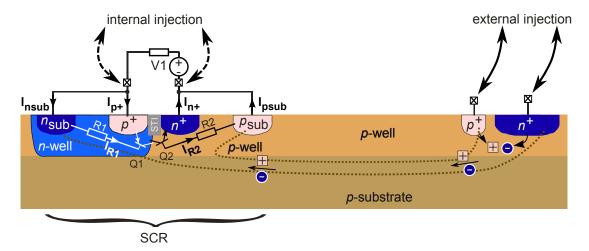

The schematic cross section along A–A' of the layout of Figure 1.1a shows in Figure 1.2a the parasitic pnp transistor  $Q_1$  and npn transistor  $Q_2$  with their corresponding base resistances  $R_1$  and  $R_2$ . The collector of pnp transistor  $Q_1$  is the base of npn transistor  $Q_2$  and the collector of npn transistor  $Q_2$  is the base of pnp transistor  $Q_1$ . This forms a parasitic pnpn junction (SCR structure), which is unavoidable and always present in bulk silicon CMOS circuits. The equivalent circuit is shown in Figure 1.2b. The two bipolar transistors are normally inactive. Thus, no current flow occurs and the base-emitter voltages are negligible.

**Figure 1.2:** (a) Schematic cross section along A–A' of CMOS inverter in Figure 1.1a with parasitic pnp (Q<sub>1</sub>) and npn (Q<sub>2</sub>) transistor forming an SCR [4]. (b) Equivalent circuit of parasitic SCR with pnp transistor Q<sub>1</sub> and npn transistor Q<sub>2</sub>.

Under certain circumstances the bipolar transistors might be activated – e.g. if a current<sup>3</sup> across  $R_1$  or  $R_2$  is high enough the corresponding transistor gets active ( $V_{\rm BE2} \simeq 0.6 \, {\rm V}$  or  $V_{\rm BE1} \simeq -0.6 \, {\rm V}$ ). When the resulting voltage drop at the other resistor gets high enough, the second transistor will be activated as well. If the total gain ( $\beta_{\rm pnp} \cdot \beta_{\rm npn}$ ) is larger than one, transistor  $Q_2$  keeps transistor  $Q_1$  active and transistor  $Q_1$  keeps transistor  $Q_2$  active

<sup>&</sup>lt;sup>2</sup> Short for p substrate (p well) contact.

<sup>&</sup>lt;sup>3</sup> E.g. avalanche current, injected current or displacement current.

– even if the activating event is stopped. That means self-sustaining current flow occurs. This situation is called latch-up and it is usually visible as abrupt increase of supply current<sup>4</sup>. If this latch-up current is not limited sufficiently, the chip will be destroyed. Latch-up types and latch-up protection methods will be discussed in Section 1.5 and Chapter 3.

#### Thermal issues

A significant advantage of bulk silicon technology is the good thermal conduction of silicon substrate, which allows efficient cooling of devices through the silicon substrate. Some important (temperature dependent) properties of silicon around 300 K [5, 6] are the thermal conductivity  $\kappa = 157 \, \mathrm{W \, m^{-1} \, K^{-1}}$ , the mass density  $\rho = 2300 \, \mathrm{kg \, m^{-3}}$  and the specific heat  $C = 700 \, \mathrm{J \, kg^{-1} \, K^{-1}}$ . These thermal properties are in the range of aluminum ( $\kappa = 235 \, \mathrm{W \, m^{-1} \, K^{-1}}$ ,  $\rho = 2700 \, \mathrm{kg \, m^{-3}}$ ,  $C = 897 \, \mathrm{J \, kg^{-1} \, K^{-1}}$ ,  $D = 9.7 \cdot 10^{-5} \, \mathrm{m^2 \, s^{-1}}$ ).

The thermal diffusivity can be calculated with

$$D = \frac{\kappa}{\rho C} \tag{1.1}$$

and results in  $D = 9.8 \cdot 10^{-5} \,\mathrm{m^2 \, s^{-1}} \,\, (0.98 \,\mathrm{cm^2 \, s^{-1}}).$

Using the model of a one dimensional heat diffusion into a homogeneous material [7]

$$\frac{\partial T}{\partial t} = D \frac{\partial^2 T}{\partial x^2} - \frac{T - T_a}{\tau} \tag{1.2}$$

leads for steady state condition  $\left(\frac{\partial T}{\partial t} = 0\right)$  to

$$D\frac{\partial^2 T}{\partial x^2} = \frac{T - T_a}{\tau}. (1.3)$$

With the thermal boundary condition of the temperature  $T_{x0}$  at x = 0 and the ambient temperature  $T_a$  the solution is

$$T(x) = T_{a} + (T_{x0} - T_{a})e^{-x/L}$$

(1.4)

with the spatial decay constant (thermal diffusion length L) of

$$L = \sqrt{D\tau}. (1.5)$$

<sup>&</sup>lt;sup>4</sup> An exemplary SPICE simulation of the triggering process is shown in Figure 3.14.

At the distance of the diffusion length L the excess temperature drops to 1/e ( $\sim 37\%$ ). A simplified approximation for silicon is

$$L_{\rm Si} \simeq 0.3\sqrt{t\,[\rm ns]}\cdot[\mu \rm m].$$

(1.6)

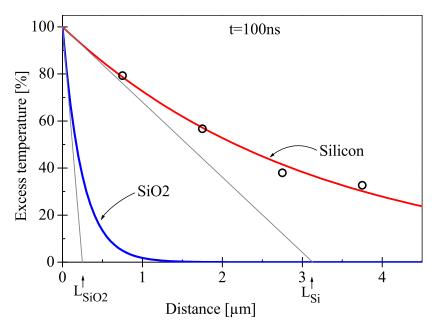

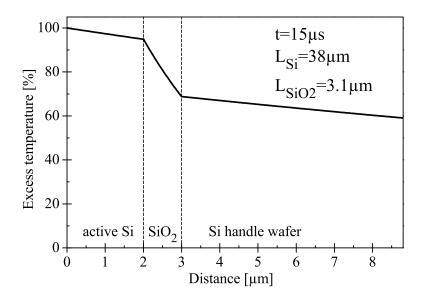

For example, the thermal diffusion length in silicon at  $t = 100 \,\mathrm{ns}$  is  $L_{\mathrm{Si}} = 3.1 \,\mathrm{\mu m}$  – see sketched and measured heat diffusion for silicon in Figure 1.3.

Figure 1.3: Schematic heat diffusion at  $t=100\,\mathrm{ns}$  in silicon (diffusion length  $L_{\mathrm{Si}}=3.1\,\mathrm{\mu m}$ ) and silicon dioxide (diffusion length  $L_{\mathrm{SiO2}}=0.25\,\mathrm{\mu m}$ ). Symbols represent measured phase shift data of silicon (see 0.1 A curve in Figure 2.12).

# 1.3.2 Silicon-on-insulator technology

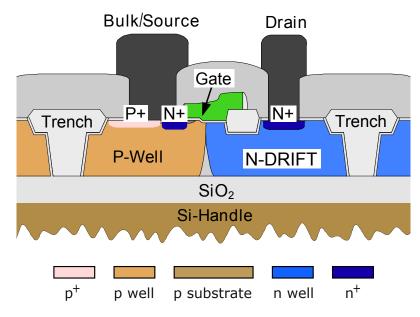

In silicon-on-insulator technology the doped wells for the transistors are laterally isolated by trenches (trench isolation) and vertically isolated by a silicon dioxide (SiO<sub>2</sub>) layer (see Figure 1.4). Thus no junction isolation is required and latch-up problems due to parasitic SCR structures and substrate currents are avoided [8]. The isolation from the bulk silicon reduces the parasitic capacitances and the layout can be realized denser than in bulk silicon technology.

The silicon dioxide layer (buried oxide, BOX) is either created with an oxygen ion beam implantation process and annealing or with wafer bonding.

Some important (temperature dependent) properties of silicon dioxide around 300 K [5, 6]

Figure 1.4: Cross section of one finger of a lateral SOI DMOS transistor. The active silicon layer is typically in the range of  $2\,\mu m$  and the  $SiO_2$  layer is typically  $\sim 1\,\mu m$ .

are the thermal conductivity  $\kappa = 1.4 \,\mathrm{W\,m^{-1}\,K^{-1}}$ , the mass density  $\rho = 2270 \,\mathrm{kg\,m^{-3}}$  and the specific heat  $C = 1000 \,\mathrm{J\,kg^{-1}\,K^{-1}}$ . The thermal conductivity of silicon dioxide is  $\sim 112$  times lower than of silicon. The thermal diffusivity yields with Equation (1.1) to  $D = 6.2 \cdot 10^{-7} \,\mathrm{m^2\,s^{-1}}$ , this is even  $\sim 160$  times lower than for silicon.

A simplified approximation of Equation (1.5) for the thermal diffusion length of silicon dioxide is

$$L_{\rm SiO2} \simeq 0.025 \sqrt{t \,[\rm ns]} \cdot [\mu \rm m].$$

(1.7)

For example, the thermal diffusion length in silicon dioxide at  $t = 100 \,\text{ns}$  is  $L_{\text{SiO2}} = 0.25 \,\mu\text{m}$ , which is twelve times lower than for silicon – see sketched heat diffusion for silicon dioxide in Figure 1.3.

In respect to bulk silicon technology, the heat transport through the buried oxide to the substrate (handle wafer) is very low due to the low thermal conductivity of silicon dioxide. As example for a buried oxide layer thickness of  $1 \,\mu m$  nearly no heat will diffuse to the handle wafer at  $t = 100 \,\mathrm{ns}$  (see SiO<sub>2</sub> curve at  $1 \,\mu m$  in Figure 1.3). Cooling will occur through the top side of the chip (vias and metal layers). Because of this enhanced self-heating effect, special focus should be taken to thermal optimization of SOI power devices [9–11].

# 1.4 Electrostatic discharge

Electrostatic charge can be generated by simple charge separation. The capacity C decreases with increasing distance l of the separated charge Q (i.e. the capacity of a plate-type capacitor with area A and permittivity  $\epsilon$  is  $C = \epsilon \frac{A}{l}$ ). Consequently, increasing distance leads to increasing electrostatic voltage

$$V = \frac{Q}{C} \,. \tag{1.8}$$

Some electrostatic voltages under several cases of charge separation are listed in Table 1.1 [12]. Besides the dissimilarity of the involved materials, the level of the electrostatic voltage depends very much on the relative humidity (%RH) of the surrounding atmosphere – the dryer the air the higher is the electrostatic voltage.

| Origin of electrostatic voltage          | Static voltage  | Static voltage       |

|------------------------------------------|-----------------|----------------------|

|                                          | at 20 %RH       | at $80\%\mathrm{RH}$ |

| Walking on synthetic carpet              | $35\mathrm{kV}$ | $1.5\mathrm{kV}$     |

| Picking up polyethylene bag              | $20\mathrm{kV}$ | $0.6\mathrm{kV}$     |

| Sliding styrene box on carpet            | 18 kV           | $1.5\mathrm{kV}$     |

| Arising from foam cushion                | 18 kV           | $1.5\mathrm{kV}$     |

| Shrinkable film on printed circuit board | 16 kV           | $3.0\mathrm{kV}$     |

| Aerosol circuit freeze spray             | 15 kV           | $5.0\mathrm{kV}$     |

| Walking on vinyl floor                   | 12 kV           | $0.3\mathrm{kV}$     |

| Triggering vacuum solder remover         | 8 kV            | $1.0\mathrm{kV}$     |

**Table 1.1:** Electrostatic voltages depending on relative humidity of surrounding atmosphere [12].

In assembly lines, as well as during manipulation by hand, often insulated tools handle electronic components and thus inherent electrostatic charge cannot be drained. As well operators or handling tools can be electrostatically charged.

The discharge of electrostatically generated charge (electrostatic discharge, ESD) is a serious danger for microelectronic devices. For this reason ESD sensitive devices are commonly labeled with a triangle, a reaching hand and a slash through the reaching hand<sup>5</sup> (Figure 1.5a), which means *caution*, *don't touch*. ESD protective materials – such as wrist straps, mats etc. – are indicated with an arc around a reaching hand in a triangle

<sup>&</sup>lt;sup>5</sup> ANSI ESD S8.1-1993 – ESD awareness symbols.

**Figure 1.5:** Standardized ESD awareness symbols. (a) ESD susceptibility symbol. (b) ESD protective symbol. (c) ESD common point ground symbol.

(Figure 1.5b). The common point ground for ESD protective materials is identified with a yellow disk (Figure 1.5c) labeled with ESD common point ground.

#### 1.4.1 ESD models

The processes of electrostatic discharge are very complex and stochastically distributed [13]. For industrial tests schematic models are defined to make repeatable electrostatic discharges possible. The most important ESD models distinguish the origin of discharge by men (human body model), by machines (machine model) and by the devices themselves (charged device model) [12]. The first two ESD models show similar failure mechanisms due to internal energy dissipation (melting of junctions). The failure mechanisms of the third model are mainly breakdowns of gate oxide in field effect transistors due to internal voltage distributions. Further models are developed to describe i.e. cable discharge events [14] or system-level ESD stress [15].

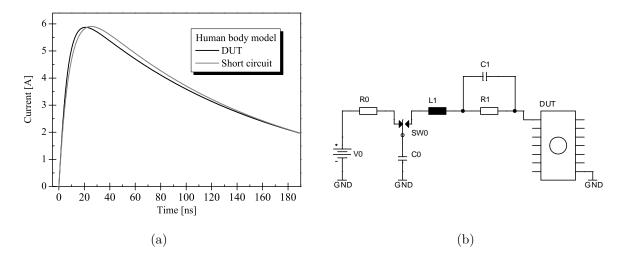

#### Human body model

The human body model (HBM) describes the discharge of a standing electrostatically charged man through a pointing finger into a grounded component. A typical discharge waveform with a rise-time<sup>6</sup> of 10 ns is shown in Figure 1.6a for a  $50\,\Omega$  ||  $10\,\mathrm{pF}$  device under test (DUT) and a short circuit.

The discharge process is modeled with a 100 pF capacitor  $(C_0)$ , the approximated capacity of a standing man, which is charged by a 10 kV high voltage source  $(V_0)$  and a 10 M $\Omega$  series resistor  $(R_0)$  and discharged over a 12  $\mu$ H inductor  $(L_1)$  and a 1.5 k $\Omega$  series resistor  $(R_1)$  with a parasitic stray capacity of 1 pF  $(C_1)$  into the DUT. The equivalent circuit

$<sup>^6</sup>$  10% to 90% of peak level.

**Figure 1.6:** Human body model. (a) Waveforms for 10 kV pulses. (b) Schematic diagram [16].

diagram is shown in Figure 1.6b. A simulation with SPICE [17] gives a pulse duration<sup>7</sup> of 126 ns for a DUT with 50  $\Omega$  and 10 pF impedance.

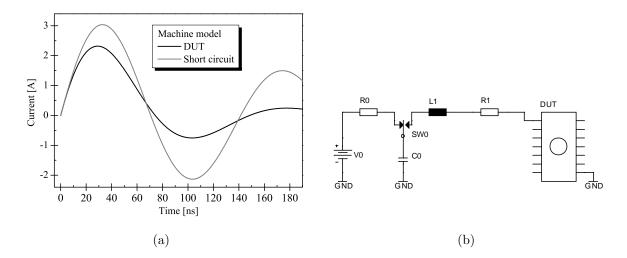

#### Machine model

The machine model describes the discharge of a charged handling tool into a grounded component. A typical current through the DUT with a rise time of 18 ns and an oscillating rate of 6.7 MHz is shown in Figure 1.7a. The values of the series resistor and the inductor are much lower than in the human body model. The machine model circuit can be described with a 200 pF capacitor ( $C_0$ ) discharging by a 2.5 µH inductor ( $L_1$ ) and a 25  $\Omega$  series resistor ( $R_1$ ) followed by the DUT (Figure 1.7b).

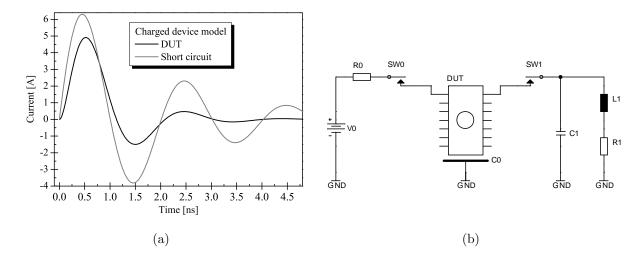

#### Charged device model

Devices can be charged during picking them from plastic packages or by sliding over insulators. The charged device model describes the discharge of a device by machines, mostly pick-and-place machines, to ground. Due to the very low inductance the current waveforms show a rise time below 1 ns (Figure 1.8a).

The simplified equivalent circuit diagram in Figure 1.8b is based on a 5 pF capacitor  $(C_0)$  discharging the DUT into a current probe, which consists of a 10 nH inductor  $(L_1)$  and a  $10 \Omega$  series resistor  $(R_1)$  with a stray capacity of 5 pF  $(C_1)$ .

<sup>&</sup>lt;sup>7</sup> 50% of peak level.

**Figure 1.7:** Machine model. (a) Waveforms for 400 V pulses. (b) Schematic diagram [16].

**Figure 1.8:** Charged device model. (a) Waveforms for 500 V pulses. (b) Schematic diagram [16].

#### 1.4.2 ESD protection levels

Possible ESD stress increases from production of integrated circuits over ESD protected assembly of systems in factories to unknown handling of the final consumers. This is described with different ESD protection levels and ESD test methods. A good introduction to ESD protection in analog circuits with case studies of various scenarios is shown in [15].

#### ESD protection at chip level

Electrostatic discharge can occur at packaged integrated circuits only at the pins, because the package is well isolating. The pins of the lead frame are usually connected with bond wires to the (bond) pads on the semiconductor die<sup>8</sup>. ESD protection on chip level focuses on limiting the voltages at the I/O pads and on providing a discharge path over the ground circuitry of the integrated circuit [18]. An ESD protection unit has to absorb this discharge pulse and protect the rest of the integrated circuit from high voltages [19]. Protection elements limit the voltage reaching the core of the chip. High voltages at pads might cause permanent damage due to breakdown of isolations or gate dielectrics. High discharge currents might melt metal traces, vias or even silicon. The ESD protection circuits need to clamp transient voltages during ESD events to safe levels and to sustain the occurring currents. Their response must be fast enough and they should not influence normal operation of the integrated circuit – e.g. they should have very low parasitic capacitances.

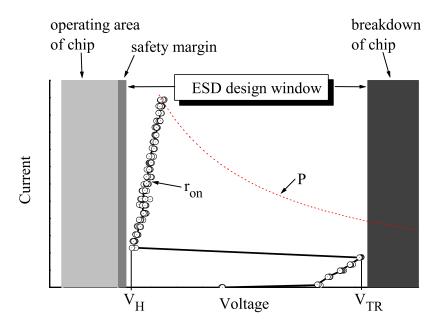

The operating range of the protection element has to be designed in a way, that the trigger voltage ( $V_{TR}$ ) is below the oxide breakdown voltage and the holding voltage ( $V_{H}$ ) is higher than the supply voltage range plus a 10% safety margin to avoid clamping the voltage below the applied supply voltage – which would result in latch-up and the damage of the chip (Figure 1.9) [20]. After activation – in the so called conductive mode – the differential resistance ( $r_{on}$ ) of the protection device should be very low to keep the power dissipation and the heating of the protection device in an acceptable range. Therefore, many ESD protection devices show s-shaped characteristics.

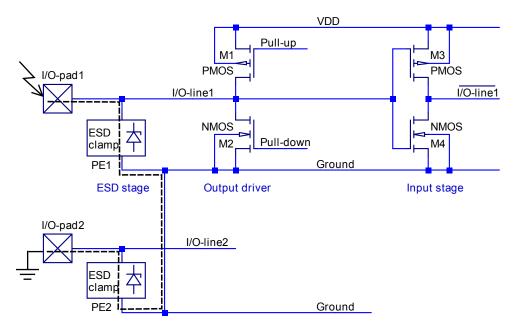

Local ESD protection at every I/O pad. Every I/O pad is protected with a dedicated ESD protection unit, which drains the discharge current to ground. Figure 1.10 shows on the left the I/O pad, the ESD protection stage, an output driver and the input

<sup>8</sup> In flip-chip technology balls connect the pads to the contacts of the package.

**Figure 1.9:** ESD design window with lower limit above the operating voltage of the chip plus a safety margin and upper limit below breakdown (destruction) of the chip. The dashed line P denotes a line of constant power.

stage which is connected to the core logic of the chip. If the output driver is activated by the pull-up or pull-down signal, the I/O pad acts as an output and the pad is forced either to VDD or to ground. The input stage converts a signal from the pad to an inverted binary (high/low) signal for the logic circuitry.

An exemplary discharge event is sketched with the dashed line in Figure 1.10, where a positive discharge pulse is applied at I/O-pad1 and ground is applied to I/O-pad2. The ESD pulse activates the ESD protection element PE1, which drains the ESD pulse to the ground network. From the ground network the current flows across the forward biased ESD protection element PE2 to the grounded I/O-pad2.

Every I/O pad can be individually protected according to the allowed voltages and parasitic capacitances. A disadvantage of this concept is, that chips with many pins cover a lot of space with ESD protection units. The protection units need to be robust (i.e. large) enough to absorb the energy of the ESD pulse without any degradation. The simplest ESD protection element is a Zener diode [21], which is operated in breakdown. NMOS transistors allow more flexibility in design. Active clamps use a gate coupling circuit to open the channel of a MOS transistor during the ESD event, which will drain the major discharge current. Grounded gate NMOS transistors use the parasitic bipolar transistor for snap-back operation [22]. Silicon-controlled rectifiers combine high trigger

Figure 1.10: Schematic I/O cell with I/O-pad1, ESD protection element PE1, output transistors (M1 and M2) and input stage (transistors M3 and M4). I/O-pad2 and ESD protection element PE2 are related to the neighboring I/O cell.

voltages with very low clamp voltages around 2 V. After qualification the developed ESD protection units are merged in ESD-libraries, which are provided to chip designers.

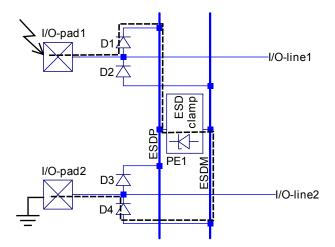

ESD protection rails. In integrated circuits with many I/O pins, chip area can be saved by using only small diodes (D1–D4) at every single I/O pad, which connect the ESD stress to ESD rails as sketched in Figure 1.11 [15, 23]. ESDM denotes the negative (minus) rail and ESDP the positive (plus) rail. These diodes are operated in forward direction. That results in low power dissipation during ESD events. The voltage on the rails is limited with a few big ESD protection clamps, which are usually distributed along the ESD protection rails in the chip and not at every single I/O pad. An ESD pad ring with several ESD clamps is placed around the core circuitry of the chip.

The dashed line in Figure 1.11 indicates an exemplary discharge from I/O-pad1 over diode D1 to the ESDP rail. The ESD clamp in the rail limits the voltage and drains the current to the ESDM rail. From the ESDM rail the current flows across the forward biased diode D4 to the grounded I/O-pad2. Most of the energy of the ESD event is absorbed in the ESD protection clamp and only a part in the forward biased diodes D1 and D4. The voltage drop in the rails must be kept low during the ESD events.

**Figure 1.11:** Simplified ESD protection network with common positive rail ESDP and common negative (minus) rail ESDM. Several I/O pads are connected with (small) diodes to a common (large) ESD clamp (after [15]).

**Self protection of output drivers.** Some output drivers are designed for ESD self-protection without special ESD protection elements. Previous investigations on VDMOS output drivers [16, 24–26] showed the activity of parasitic bipolar transistors, which limit effectively the voltage at the output pad.

#### System level ESD protection

A careful design of systems consisting of PCBs, integrated circuits, discrete components, I/O-connectors etc. is necessary to achieve high ESD robustness of the total system. A lot of effort is made to withstand with on-chip ESD protection the system level ESD stress [27]. At system level sensitive connector pins often need to be protected by additional discrete ESD protection components, which are soldered to the PCB (e.g. transient voltage suppressors (TVS) or filters) [28]. These discrete protection components need to respond fast enough and their trigger voltage must be smaller than the trigger voltage of the protection elements of the ICs – otherwise the energy of the ESD pulse is dissipated in the integrated circuit rather than in the discrete protection elements.

System level ESD tests are usually done with an "ESD-gun" [29], which generates pulses with a two-peak waveform (IEC ESD pulse [30]). A sharp high peak is followed by a slower HBM-like peak [31]. For preliminary tests at wafer-level the effect of application PCBs can be modeled with a human metal model (HMM) networks [15]. During plug-in of cables interface pins are often exposed to discharge of cables. This type of ESD stress is described with the so called cable discharge event (CDE) [14].

#### ESD protection at production

The production and assembly of electronic systems are usually done in a well known ESD protected area (EPA) [15]. Excessive ESD stress is avoided by the use of conductive mats, wrists, ESD-boxes and controlled humidity. Typical ESD stress of human handling is modeled and tested with the human body model. The machine model is relevant for e.g. pick-and-place machines and the effect of slides for components in feeding systems are described with the charged device model.

#### ESD protection at the consumer

At the consumer the well controlled ESD protected area is left and electronic systems are exposed to unknown handling in an unknown environment. Consequently, implicit ESD protection is essential. Special attention has to be paid to the (few) exposed interface pins because charge equalization between two objects (e.g. plugs) occurs through the first connected contact – this should be the shield or ground. Therefore, longer pins for shield or ground are desired. Demonstrative examples are the widely used universal serial bus (USB) plugs. The first contact is usually the connection to the shield (see Figure 1.12a). Some memory modules omit the shield – then the longer ground and power pins are contacting first – see Figure 1.12b.

Figure 1.12: USB plug (a) with shield contacting first and (b) longer power and ground pins.

ESD induced latch-up can be avoided by powering off before plugging. Controlled – and especially in winter increased – humidity reduces significantly the electrostatic voltages – see Table 1.1.

# 1.5 Latch-up in bulk CMOS circuits

An uncontrollable current flow in the power supply of an integrated circuit is called latch-up. Generally, latch-up leads to destruction of the circuit – unless the current is sufficiently limited by external devices. Latch-up occurs, if a conductive path in the power supply of a circuit (e.g. parasitic SCR structure or parasitic bipolar transistor) is activated. Triggering could be due to injection of positive or negative currents. If the holding voltage is below the supply voltage (see operating area in Figure 1.9), current flow occurs even after the end of the trigger pulse.

Latch-up is a continuing risk for bulk silicon CMOS integrated circuits<sup>9</sup> because unavoidable parasitic SCR structures are always present and consequently a potential risk for latch-up [4, 32–36]. Under certain circumstances they can be activated and lead to latch-up [34, 37, 38]. The triggering mechanisms are often substrate currents originating from overshoots due to impedance mismatch, coil discharge, electrostatic discharge or electrical over-stress events. The sensitivity of integrated circuits to electrical disturbances in operation is worse with scaling down due to the smaller feature size and the lowering of operating voltage. Therefore, nowadays a lot of effort is done to reduce substrate currents [23, 39–42] and to prevent latch-up [2, 4].

# 1.5.1 Latch-up types

#### Internal latch-up

Latch-up, which is triggered by injection of current directly to the terminals of the SCR is called *internal* latch-up (see left part and dashed arrows in Figure 1.13) [43]. Overshoots during gate switching of MOS transistors [44] could also lead to short injection currents.

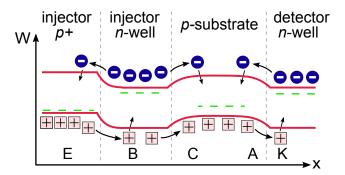

#### External latch-up

In an external latch-up event, triggering of a parasitic SCR structure is caused by carriers injected from distant diffusions (substrate currents), which are connected to I/O pads (see solid arrows in Figure 1.13) [43]. These diffusions could be related to ESD protection elements or output drivers. Carriers reaching the bases of the parasitic SCR structure might activate it and cause latch-up.

We have seen already four latch-up damaged notebooks and PCs during the last years – a result of the faster I/O ports with lower allowed parasitic capacitances.

**Figure 1.13:** Schematic cross section showing on the left an SCR together with internal current injection at the  $p^+$  and  $n^+$  diffusions of the SCR (dashed arrows) and on the right external current injection (solid arrows). Carriers reaching the bases of the SCR might activate it and cause latch-up. In p substrate, minority carriers (electrons,  $\odot$ ) are shielded by majority carriers (holes,  $\boxplus$ ) [1].

#### Static latch-up

Triggering latch-up with constant current (or very low slew rates) is called *static* latch-up. A common test method is injecting constant current with positive and negative polarity into each pin of the device under test (JEDEC JESD78A specifies a trigger current higher than  $I_{\text{nom}} + 100 \,\text{mA}$ ).

#### Transient latch-up

Triggering latch-up with fast transients is called *transient* latch-up (TLU). Such pulses can be caused for instance by ESD events or rapid discharges of coils [4, 45–47]. Displacement currents could assist triggering of latch-up, consequently transient latch-up is very important for circuits with short rise times and high slew rates (e.g. digital circuits with dV/dt > 1 V/ns).

# 1.5.2 Latch-up protection in CMOS technology

Several approaches to prevent activation of parasitic SCR structures are proven. The measures comprise layout as well as materials (e.g. doping concentration), but the latch-up problem is not completely vanished in modern bulk CMOS devices. As a last resort the design could be processed in (the more expensive) silicon-on-insulator technology.

#### **Distances**

Latch-up robustness could be improved by increasing distances inside the parasitic SCR structure (e.g. bases) and by increasing the distance between injection source and parasitic SCR structure (see Figure 1.13).

#### Well resistances

The decrease of well and substrate resistances lead to higher latch-up immunity. This could be achieved by increasing the contact density in the wells or increasing the doping concentration in the wells. Lower well (base) resistance of the parasitic bipolar transistors results in lower voltage drop.

#### **Guard-rings**

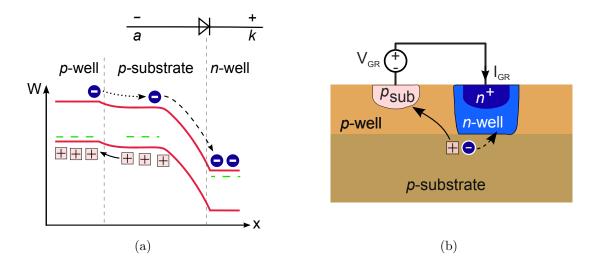

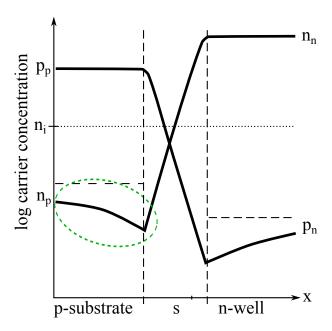

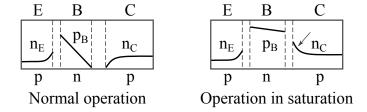

Guard-rings for collection of excess carriers are widely used in CMOS and Smart Power technologies. Such guard-rings can be floating [39], (locally) grounded [40, 41] or biased [15]. Excess holes are collected by p guard-rings and excess electrons by n guard-rings. The principle of the collection of excess electrons with biased n guard-rings (GRs) for latch-up protection is shown in Figure 1.14. Excess electrons<sup>10</sup> ( $\odot$ , minority carriers in p substrate) are collected by positive biased n wells (n guard-rings, see dashed arrow). Excess majority carriers ( $\boxplus$ , holes), which shielded these minority carriers, are released and collected by the  $p_{\text{sub}}$  contacts (p guard-rings, see solid arrow) [1]. The  $p_{\text{sub}}$  contacts are usually at lowest potential (ground). The intensive use of p guard-rings improves the substrate connection to ground and therefore reduces the distributed substrate resistance. Reverse biasing of the p substrate/n well junction cause a minority carrier concentration below the thermal equilibrium (see ellipse in Figure 1.15).

# 1.6 Electrical testing methods

Basic device characterizations are performed with DC measurements in the low current (low power) regime, where no significant self-heating occurs and no cooling is required. In the high current (high power) regime the devices are characterized with short pulses. Sufficient time for cooling of the sample after each stress pulse is ensured to avoid early

<sup>&</sup>lt;sup>10</sup> E.g. injected electrons or optically generated electron-hole pairs.

**Figure 1.14:** (a) Simplified schematic energy band diagram of the reverse biased  $p \text{ well } / p \text{ substrate } / n \text{ well junction showing the collection of carriers. Electrons } (<math>\odot$ ) are collected by positive biased n wells (see dashed arrow). Holes ( $\boxplus$ ) are collected by grounded p diffusions (see solid arrow). (b) Schematic cross section of a p guard-ring and an n well guard-ring in a p substrate wafer.

**Figure 1.15:** Schematic carrier concentration in reverse biased p substrate/n well junction (n guard-ring) showing reduction of minority carrier concentration (see ellipse) in p substrate (after [1]). The space charge region is denoted with "s", the electron (minority carrier) concentration in p substrate is denoted with " $n_p$ " and the hole (majority carrier) concentration in p substrate is denoted with " $p_p$ ".

degradations due to excessive self-heating. The DC measurements (e.g. leakage currents) are performed with the Keithley source measure units K2410 [48] and K237 [49].

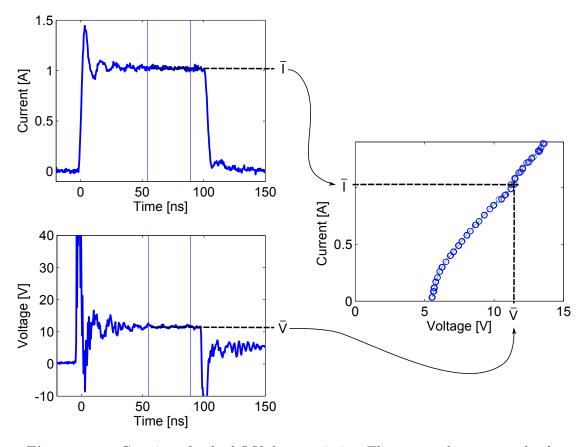

Different types of pulse generators are used for measurements of pulsed current-voltage (I-V) characteristics and for pulsed excitation during the TIM experiments. The devices are stressed by pulse generators, which provide (nearly) square current pulses. The voltage and current transients of each stress pulse are acquired with an oscilloscope and processed with the Matlab [50] program tlpiv.m [51] to get the pulsed I-V characteristics. The acquired voltage and current waveforms are averaged over a certain time interval. These averaged values  $\overline{I}$  and  $\overline{V}$  give one point in the pulsed I-V characteristics – see arrows in Figure 1.16. For a stress pulse amplitude sweep, the pulse current is increased in small steps, where several pulses can be applied at each stress level to reveal pulse-to-pulse instabilities.

**Figure 1.16:** Creation of pulsed I-V characteristics. The averaged current and voltage values  $(\overline{I}, \overline{V})$  give one point in the pulsed I-V characteristics.

### 1.6.1 Transmission line pulse generators

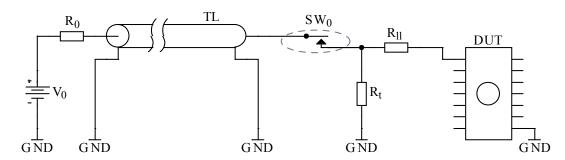

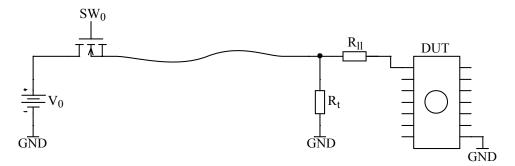

A useful approximation for HBM-ESD pulses is the pulse creation with a transmission line pulse generator (TLP), which schematic diagram is shown in Figure 1.17. Here, the generated square pulses are easy to reproduce and can reach rise times below 2 ns. A coaxial cable with  $50\,\Omega$  characteristic impedance and length l according to the desired pulse duration  $T_{\rm p}$  is used as transmission line, which is charged with the  $10\,{\rm M}\Omega$  resistor  $R_0$  using the high voltage source  $V_0$

$$l = \frac{v_{\rm p}T_{\rm p}}{2}.\tag{1.9}$$

Figure 1.17: Pulse generation with a transmission line pulse generator. The load line resistance is determined with resistor  $R_{\rm ll}$ . Resistor  $R_{\rm t}$  is used for proper termination of the transmission line (TL).

When the reed relay SW<sub>0</sub> is closed, the voltage at switch SW<sub>0</sub> is halved<sup>11</sup>, because of the potential divider of the internal impedance of the transmission line and the  $50\,\Omega$  termination resistor  $R_{\rm t}$ .

The imposed current on the DUT is determined by the load line resistor  $R_{\rm ll}$  and the voltage  $V_0$

$$I = \frac{1}{2} \frac{V_0}{R_{\text{ll}} + R_{\text{DUT}}} \simeq \frac{1}{2} \frac{V_0}{R_{\text{ll}}} \,.$$

(1.10)

The current pulse stops, when the – on the open end<sup>12</sup> reflected – voltage wave in the transmission line returns to the switch. This issues the factor 1/2 in (1.9). With the propagation speed  $v_{\rm p} \simeq 200 \cdot 10^6 \, {\rm m/s}$  of the wave, the pulse duration is approximately 10 ns per meter transmission line. The disadvantage of a transmission line pulse generator is the fixed pulse duration – for each pulse duration a separate transmission line length is necessary.

$<sup>^{11}</sup>$   $R_{\rm ll}$ , which is usually much larger than  $50\,\Omega$ , is neglected.

$<sup>^{12}</sup>$   $R_0$  with  $10\,\mathrm{M}\Omega$  is negligible.

### 1.6.2 Solid-state pulse generators

Solid-state pulse generators have the advantage of adjustable pulse duration, but often the drawback of longer rise time compared to TLP-systems. For currents up to 2 A the programmable solid-state pulse generator HP8114A from Agilent is used [52]. It provides output voltages from  $-100\,\mathrm{V}$  to  $100\,\mathrm{V}$  into  $50\,\Omega$  with a rise time of 7 ns. The baseline option allows biasing of the output in the range of  $\pm 30\,\mathrm{V}$ .

For higher stress currents the gate of a special solid-state switch is controlled with a digital delay and pulse generator (DG535 [53]). The SV4000-p modulator from DEI [54] is used as high voltage switch, which is powered by a Glassman high voltage source [55] (Figure 1.18).

**Figure 1.18:** Pulse generation with a solid-state switch (SW<sub>0</sub>). The load line resistance is determined with resistor  $R_{\rm ll}$ . Resistor  $R_{\rm t}$  is used for proper termination of the coaxial cable.

This solid-state switch is capable to switch up to  $4 \,\mathrm{kV}$  with minimal 150 ns pulse duration. The current through the DUT, which is limited by the load line resistor  $R_{\mathrm{ll}}$ , is

$$I = \frac{V_0}{R_{\rm ll} + R_{\rm DUT}} \simeq \frac{V_0}{R_{\rm ll}}$$

(1.11)

The termination-resistor  $R_{\rm t}$  prevents reflections from the DUT back to the solid-state switch.

## 1.7 Optical investigation method

The optical investigation method is based on monitoring transient refractive index changes of silicon due to variations of temperature and carrier concentrations. This non-destructive investigation method uses optical interferometers and is called transient interferometric mapping method (TIM) [56, 57]. This technique is a powerful tool to analyze internal temperature and free carrier distribution in ESD protection devices [58–60] and power devices on bulk silicon [61] or SOI substrates [62]. Triggering homogeneity, current flow instability [63] and current filamentation [26, 64, 65] have been investigated in ESD protection devices and circuits with nanosecond time and micrometer space resolution. Other non-destructive optical investigation methods like free carrier absorption, internal laser deflection, photon emission (EMMI), time resolved photon emission (TRE), seebeck effect imaging (SEI), optical beam induced resistance change (OBIRCH), and pulsed optical beam induced current (P-OBIC) are reviewed by *R. Thalhammer* in [66] and *F. Essely* in [67].

The refractive index n describes the ratio of the speed of light in free space  $c_0$  and in a medium c [68]

$$n = \frac{c_0}{c} = \frac{\sqrt{1/(\mu_0 \epsilon_0)}}{\sqrt{1/(\mu_0 \mu_r \epsilon_0 \epsilon_r)}} = \sqrt{\mu_r \epsilon_r}.$$

(1.12)

$\mu_0$  and  $\epsilon_0$  are the permeability and permittivity of free space,  $\mu_r$  and  $\epsilon_r$  are the relative permeability and permittivity of the medium. Refractive index variations influence the speed – and consequently the phase – of optical probing beams.

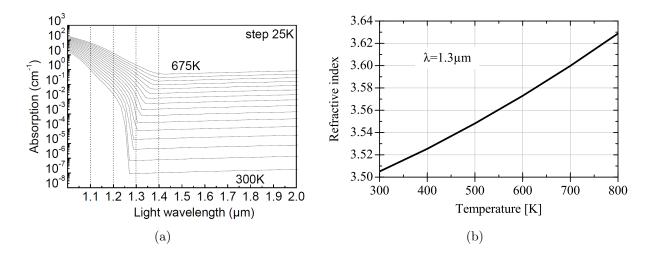

The absorption coefficient of silicon depending on wavelength and temperature is shown in Figure 1.19a [69]. The diagram shows that silicon gets transparent for infrared (IR) light with a wavelength longer than 1.27  $\mu$ m. For the optical investigations an infrared laser with a wavelength of 1.31  $\mu$ m is used. The wavelength  $\lambda$  in a medium is given by Equation (1.13), where f is the frequency of the used laser source.

$$\lambda = \frac{c_0}{fn} = \frac{\lambda_0}{n} \tag{1.13}$$

The local temporal change of refractive index of silicon  $\Delta n$  is described as the difference of the stressed  $(n_{\rm str})$  and the initial situation  $(n_0)$

$$\Delta n(\vec{r}, t) = n_{\text{str}}(\vec{r}, t) - n_0(\vec{r}, t_0). \tag{1.14}$$

The refractive index of silicon depends on temperature by the thermo-optical effect [70] and on the excess carrier concentration by the plasma optical effect [56, 58, 71]. Thus, the local variation of the refractive index is composed of a thermo-optical component and a plasma-optical (free carrier) component

$$\Delta n = \Delta n_{\rm th} + \Delta n_{\rm fc}. \tag{1.15}$$

Figure 1.19: (a) Silicon absorption coefficient depending on wavelength and temperature [69]. (b) Refractive index of silicon depending on crystal temperature for a wavelength of  $\lambda = 1.3 \, \mu \text{m}$ .

### 1.7.1 Contribution of the thermo-optical effect

The refractive index dependency of silicon on crystal temperature is investigated in [70]. Figure 1.19b shows the temperature dependency of the refractive index in silicon<sup>13</sup> for a wavelength of  $\lambda = 1.3 \,\mu\text{m}$ . The change of the refractive index  $\Delta n_{\text{th}}$  depends on the temperature dependent  $\frac{\mathrm{d}n}{\mathrm{d}T}$  and the temperature change  $\Delta T$

$$\Delta n_{\rm th}(\vec{r}, t) = \frac{\mathrm{d}n}{\mathrm{d}T} \Delta T(\vec{r}, t). \tag{1.16}$$

The temperature change is the difference of the temperature distribution  $T(\vec{r}, t)$  at instant t and the initial temperature distribution  $T(\vec{r}, t_0)$

$$\Delta T(\vec{r}, t) = T(\vec{r}, t) - T(\vec{r}, t_0). \tag{1.17}$$

The thermo-optic coefficient of silicon is  $\frac{d_n}{dT} = 1.93 \cdot 10^{-4} \,\mathrm{K}^{-1}$  for temperatures around 320 K. In contrast, the thermo-optic coefficient for silicon dioxide is one decade lower  $(10^{-5} \,\mathrm{K}^{-1})$ .

<sup>&</sup>lt;sup>13</sup> The refractive index of silicon dioxide at 1.5µm wavelength is around 1.45.

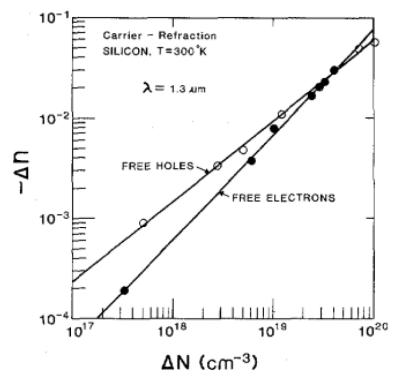

## 1.7.2 Contribution of the plasma-optical effect

A concentration change<sup>14</sup> of electrons  $\Delta N_{\rm n}$  and holes  $\Delta N_{\rm p}$  influences the refractive index  $(\Delta n_{\rm fc})$  due to the plasma-optical effect as shown in Figure 1.20 [71].

**Figure 1.20:** Carrier refraction in Silicon for  $\lambda = 1.3 \,\mu\text{m}$  [71].

The relation of the carrier concentration change to the refractive index change is described with

$$\Delta n_{\rm fc}(\vec{r},t) = k_{\rm n} \Delta N_{\rm n}(\vec{r},t)^{\alpha} + k_{\rm p} \Delta N_{\rm p}(\vec{r},t)^{\beta}. \tag{1.18}$$

The concentration change of electrons is the deviation from the static electron concentration  $n_{\rm e}$

$$\Delta N_{\rm n}(\vec{r}, t) = n_{\rm e}(\vec{r}, t) - n_{\rm e}(\vec{r}, t_0). \tag{1.19}$$

The concentration change of holes is the deviation from the static hole concentration  $p_h$

$$\Delta N_{\rm p}(\vec{r}, t) = p_{\rm h}(\vec{r}, t) - p_{\rm h}(\vec{r}, t_0). \tag{1.20}$$

For a wavelength of  $\lambda = 1.3 \,\mu\text{m}$  the approximated parameters are  $\alpha = 1.05, \beta = 0.805,$

To distinguish the carrier concentration change from the refractive index n, it is denoted with  $\Delta N$ .

$k_{\rm n} = -7.6 \cdot 10^{-23} \, {\rm cm}^3$  and  $k_{\rm p} = -4.9 \cdot 10^{-18} \, {\rm cm}^3$ . For charge neutrality<sup>15</sup> ( $\Delta N_{\rm n} = \Delta N_{\rm p}$ ) holes have the dominant effect on the refractive index. Remark that *drift current* does not change the carrier concentration ( $\Delta N = 0$ ) and so  $\Delta n_{\rm fc} = 0$  (but it could cause heating).

## 1.7.3 Optical phase shift

The refractive index variations cause an optical phase shift  $\Delta \varphi$  of a probing laser beam, which passes the active region of a DUT. The beam is reflected at the metalization layers and passes again the active region (see Figure 1.21). The optical phase shift of the reflected beam can be transformed with interferometers to amplitude variations, which can be measured with photodetectors or cameras.

Figure 1.21: Cross section of DUT with incident laser beams and reflected laser beams. At hot silicon (red shaded) the reflected beam is delayed (increased refractive index).

The electric field of the reflected electromagnetic probe beam  $\underline{\vec{E}}_{p}$  can be described as one-dimensional transversal wave spreading in z direction [68, 72]<sup>16</sup>

$$\underline{\vec{E}}_{p}(z,t) = E_{p0} e^{j(\omega_{p}t - k_{p}z + \varphi_{0})} \vec{e_{p}}. \tag{1.21}$$

$\vec{e_p}$  is the polarization direction and  $E_{p0}$  is the amplitude of the reflected probe beam, which might be modulated due to temporal change of light absorption.  $\varphi_0$  is the zero phase angle,  $\omega_p$  is the angular frequency of the probe beam and the corresponding wave number is

$$k_{\rm p} = 2\pi/\lambda_{\rm p}.\tag{1.22}$$

<sup>&</sup>lt;sup>15</sup> Excess minority carrier concentrations are compensated (shielded) by majority carriers (quasi-neutrality) [1].

<sup>&</sup>lt;sup>16</sup> Some publications and books denote the instantaneous phase inverted  $\Phi = kz - \omega t + \varphi$  [73].

The real part can be written in the form

$$E_{p}(z,t) = \Re(E_{p0} e^{j(\omega_{p}t - k_{p}z + \varphi_{0})}) = E_{p0} \cos(\omega_{p}t - k_{p}z + \varphi_{0}). \tag{1.23}$$

For calculation of the total optical phase shift of the probe beam  $(\varphi_p)$  with inhomogeneous refractive index distribution the product  $k_p z$  is replaced by an integral along the beam path  $k_p z \to \int k_p(z) dz$ . This gives with (1.22)  $\int \frac{2\pi}{\lambda_p(z)} dz$  and with (1.13)  $\int \frac{2\pi}{\lambda_0} n(z,t) dz$ .

Using the change of the refractive index (1.14) and the zero phase angle results in

$$\varphi_{\mathbf{p}}(t) = \int \frac{2\pi}{\lambda_0} \Delta n(z, t) \, \mathrm{d}z + \int \frac{2\pi}{\lambda_0} n_0(z, t_0) \, \mathrm{d}z - \varphi_0. \tag{1.24}$$

In this notation a longer optical path (increasing refractive index) causes a positive phase of the probe beam  $(\varphi_p)$ . Equation (1.24) expresses the influence of the refractive index changes  $(\Delta n)$ , the initial refractive index  $(n_0)$  and the zero phase angle  $(\varphi_0)$  to the optical phase of the probe beam. To simplify further notations the initial refractive index and the zero phase angle are combined to  $\varphi_p(t_0)$

$$\varphi_{\mathbf{p}}(t) = \Delta \varphi_{\mathbf{p}}(t) + \varphi_{\mathbf{p}}(t_0). \tag{1.25}$$

This gives with Equation (1.21) for the probe beam at the photodetector

$$\underline{E}_{p}(z,t) = E_{p0} e^{j(\omega_{p}t - \varphi_{p}(t))} = E_{p0} e^{j(\omega_{p}t - \Delta\varphi_{p}(t) - \varphi_{p}(t_{0}))}.$$

(1.26)

The real part can be written in the form

$$E_{\rm p}(t) = E_{\rm p0} \cos \left(\omega_{\rm p} t - \Delta \varphi_{\rm p}(t) - \varphi_{\rm p}(t_0)\right). \tag{1.27}$$

The reflected probe beam passes again the silicon substrate with thickness l – consequently the phase shift is doubled

$$\Delta\varphi_{\mathbf{p}}(t) = 2 \int_{0}^{l} \frac{2\pi}{\lambda_{0}} \Delta n(z, t) \, dz.$$

(1.28)

A combination of (1.16) and (1.18) in (1.28) results in the total optical phase shift

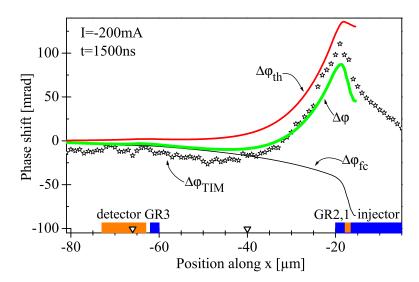

$$\Delta\varphi(t) = \frac{4\pi}{\lambda_0} \int_0^l \left( \frac{\mathrm{d}n}{\mathrm{d}T} \Delta T(z,t) + k_\mathrm{n} \Delta N_\mathrm{n}(z,t)^\alpha + k_\mathrm{p} \Delta N_\mathrm{p}(z,t)^\beta \right) \mathrm{d}z. \tag{1.29}$$

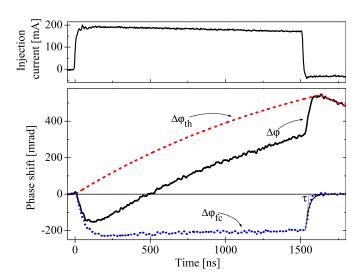

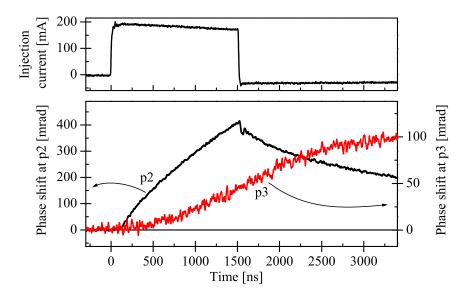

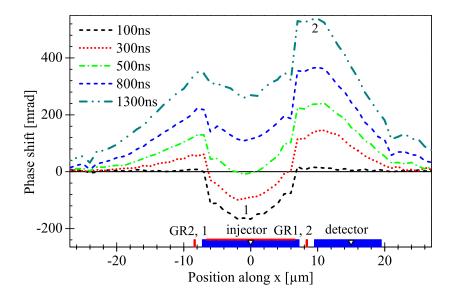

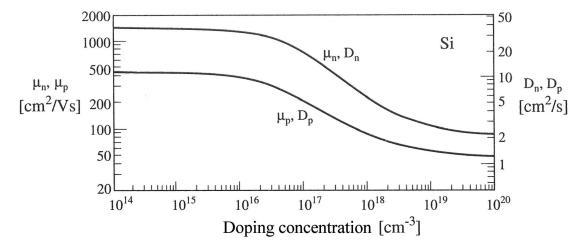

The phase shift  $\Delta \varphi$  in Equation (1.29) has a positive temperature related component  $\Delta \varphi_{\rm th}$  and a negative free-carrier related (plasma-optical) component  $\Delta \varphi_{\rm fc}$

$$\Delta \varphi = \Delta \varphi_{\rm th} + \Delta \varphi_{\rm fc}. \tag{1.30}$$

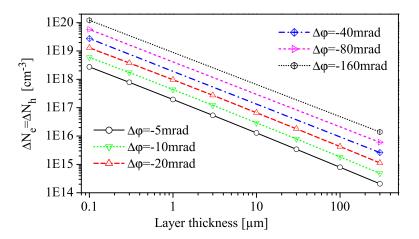

The phase shift due to the change of free carriers (plasma component) is calculated from Equation (1.29) for a homogeneous distribution along the z axis and charge neutrality  $(\Delta N_{\rm n} = \Delta N_{\rm p})$ . The phase shift curves are shown in Figure 1.22 up to the resolution limit of the later presented scanning TIM setup of  $\sim 5$  mrad.

**Figure 1.22:** Phase shift of a homogeneous excess carrier concentration vs. layer thickness.

At high dissipated power the thermal contribution dominates the phase shift and the plasma-optical contribution can be neglected

$$\Delta \varphi'(t) = \frac{4\pi}{\lambda_0} \int \frac{\mathrm{d}n}{\mathrm{d}T} \Delta T(z, t) \, \mathrm{d}z. \tag{1.31}$$

In this case the phase shift in Equation (1.31) can be interpreted in a first approximation proportional to the stored energy in substrate<sup>17</sup>. The lateral two-dimensional (2D) energy

<sup>&</sup>lt;sup>17</sup> Neglecting heat transfer through the surface, neglecting non-linearities etc.

distribution  $W_{\rm 2D}$  is

$$W_{2D}(x, y, t) = \int W(x, y, z, t) dz = c_{\rm v} \int \Delta T(x, y, z, t) dz.$$

(1.32)

The volume specific heat  $c_v$  for silicon is  $1.63 \cdot 10^6 \,\mathrm{JK^{-1}m^{-3}}$ . Substitution of the integral of Equation (1.32) with a conversion of Equation (1.31) results in the two-dimensional energy distribution [58, 59]

$$W_{\rm 2D}(x,y,t) = \frac{\lambda_0 c_{\rm v}}{4\pi \frac{\mathrm{d}n}{\mathrm{d}\tau}} \Delta \varphi(x,y,t). \tag{1.33}$$

For moderate temperature variations and the shown (temperature dependent) coefficients a rough approximation of the two-dimensional energy distribution is

$$W_{\rm 2D}(x, y, t) \simeq 0.88 \Delta \varphi(x, y, t) \, [\text{nJ/}\mu\text{m}^2].$$

(1.34)

This approximation can be used for a rough estimation of the expected phase shift in a homogeneous area using the dissipated power  $(V \cdot I)$ , time (t) and size  $(l \cdot w)$

$$\Delta\varphi(x,y,t) \simeq a \frac{V \cdot I \cdot t}{l \cdot w}.$$

(1.35)

The coefficient  $a = 1.127 \cdot 10^{-3} \,\mathrm{m^2 \, J^{-1}}$  is empirically decreased to consider slight heat diffusion to metal layers and to lateral side of real integrated circuits.

For short pulses and small temperature changes (adiabatic condition) the temperature profile for heat diffusion into silicon substrate with diffusion length L can be calculated with Equation (1.4). The phase shift is calculated with Equation (1.31) and results with

$$\int_{0}^{\infty} e^{-z/L} dz = L \tag{1.36}$$

to

$$\Delta \varphi'(t) = \frac{4\pi}{\lambda_0} \frac{\mathrm{d}n}{\mathrm{d}T} \Delta T_0 L. \tag{1.37}$$

Replacing the thermal diffusion length L with Equation (1.5) allows to express the bound-

ary temperature  $\Delta T_0$

$$\Delta T_0 = \frac{\Delta \varphi}{\frac{4\pi}{\lambda_0} \frac{\mathrm{d}n}{\mathrm{d}T} \sqrt{Dt}}.$$

(1.38)

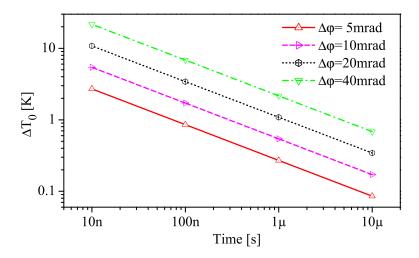

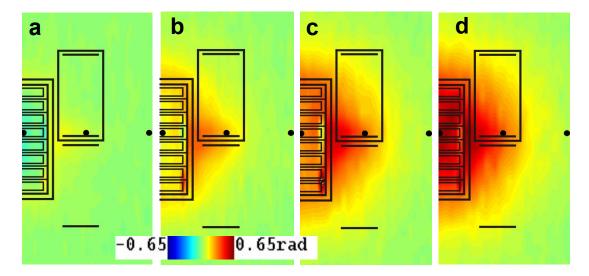

The phase shift curves for adiabatic heat diffusion into substrate are shown in Figure 1.23 for various instants. For the phase resolution of the later described scanning TIM setup of  $\sim$ 5 mrad the expected temperature resolution is in the order of 1 K.

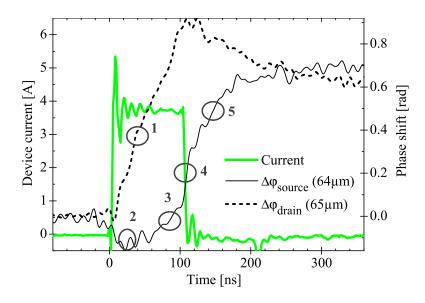

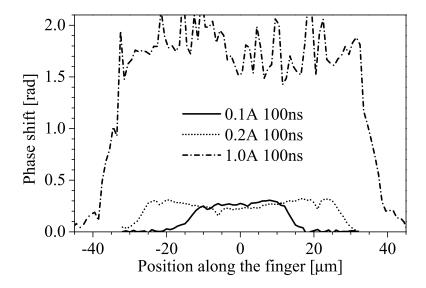

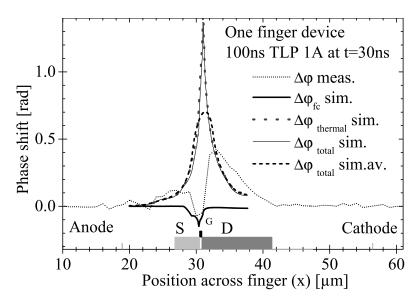

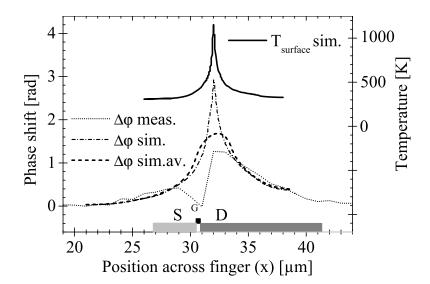

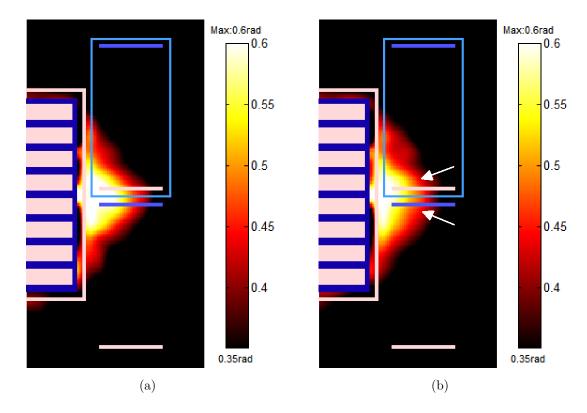

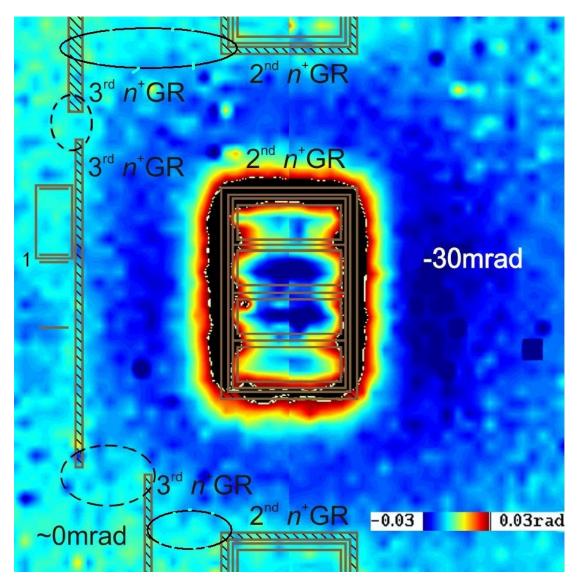

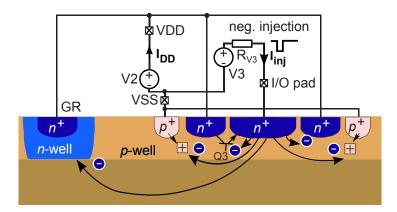

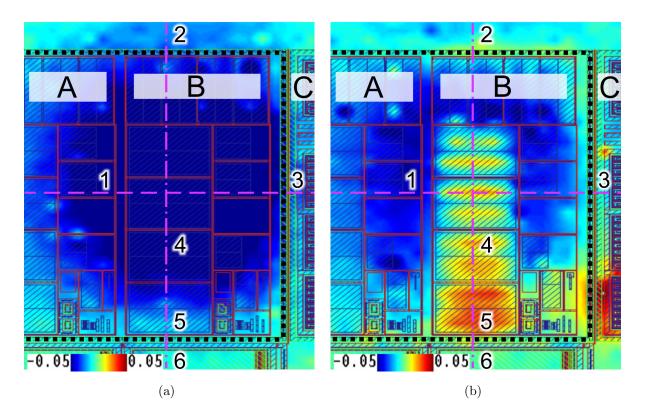

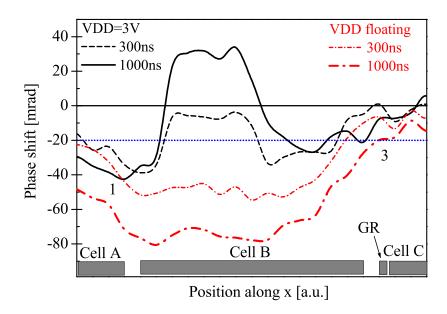

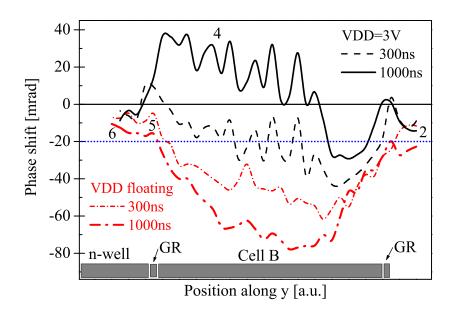

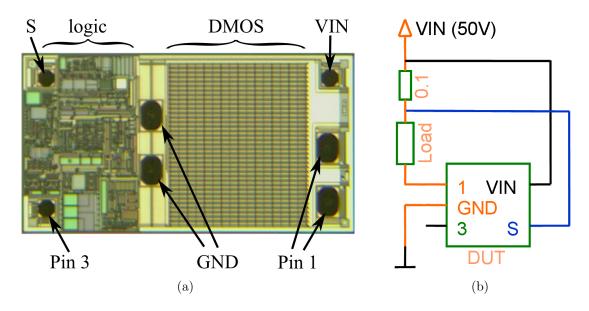

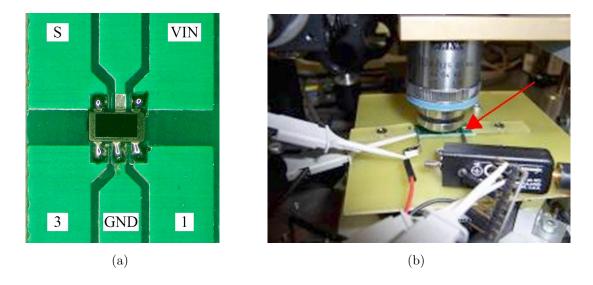

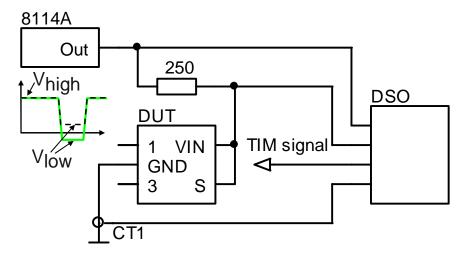

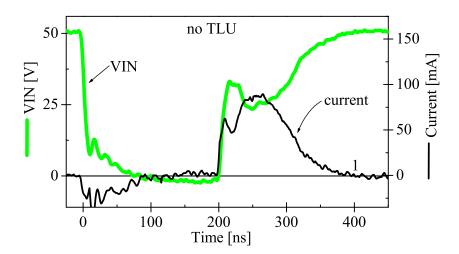

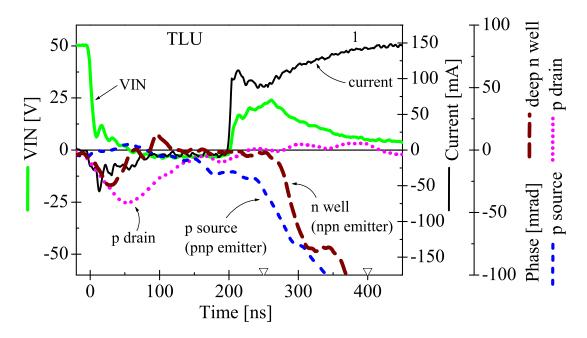

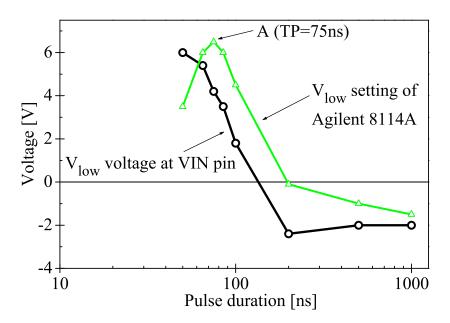

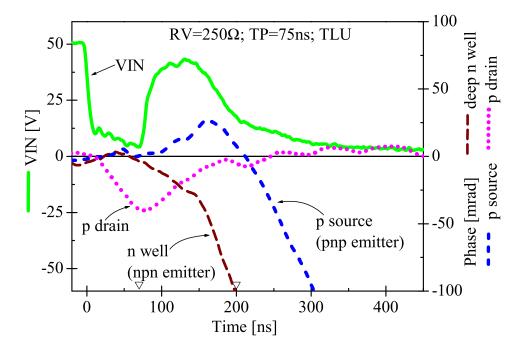

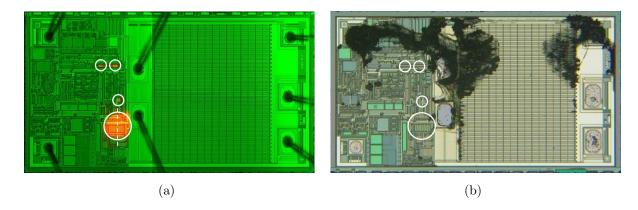

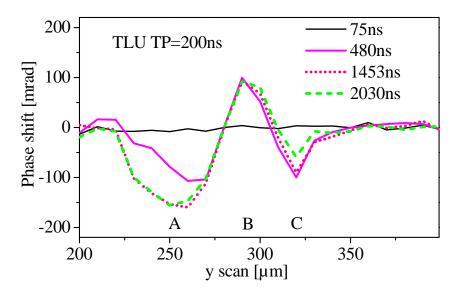

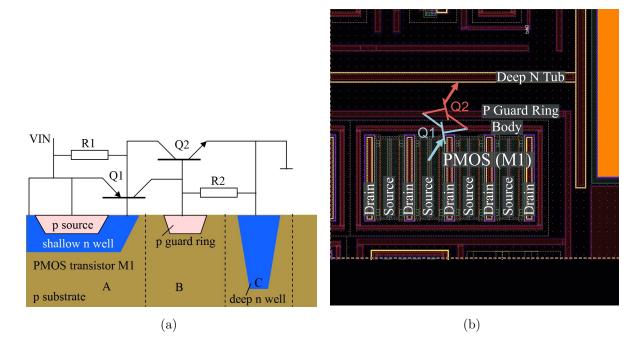

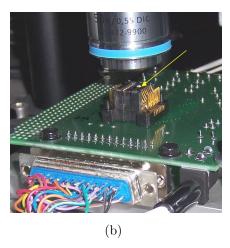

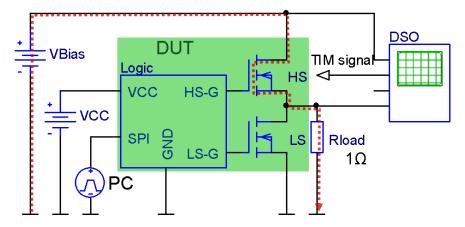

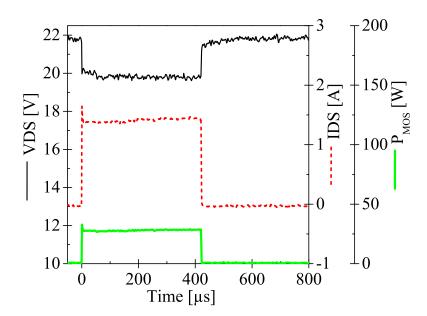

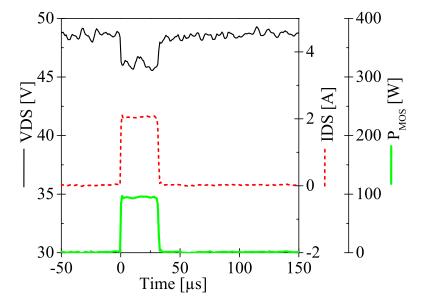

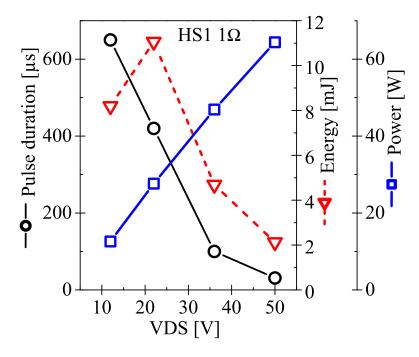

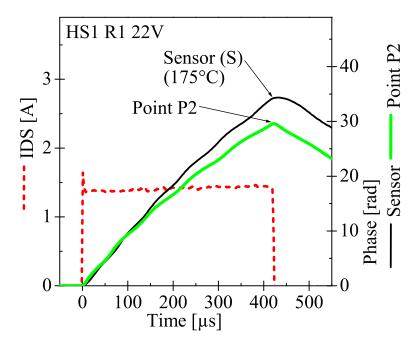

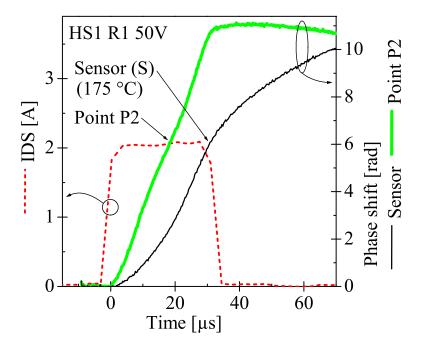

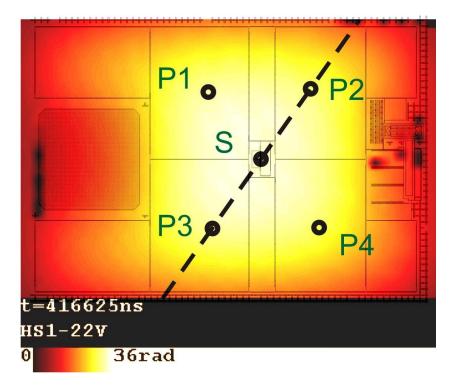

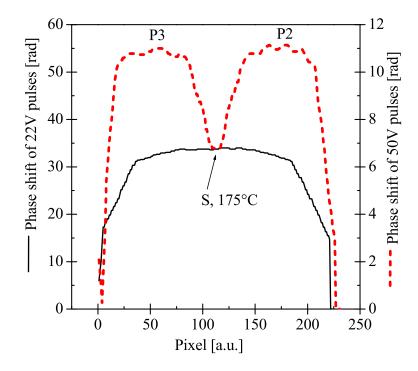

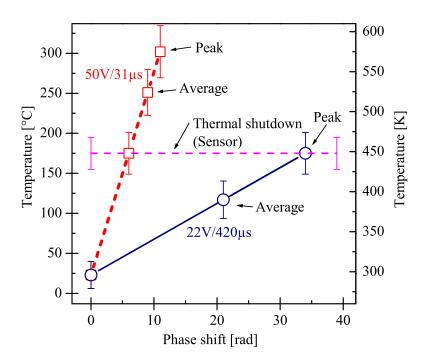

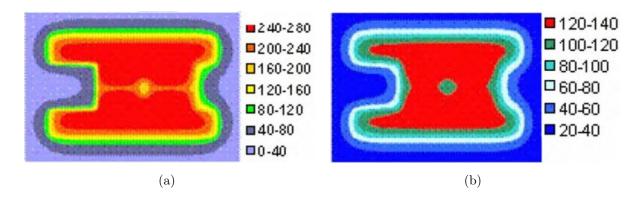

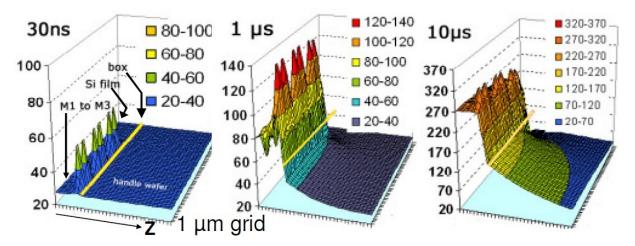

Figure 1.23: Phase shift for adiabatic heat diffusion in silicon vs. time.